# **UCLA**

# **UCLA Electronic Theses and Dissertations**

## **Title**

Silicide/Silicon Heterointerfaces, Reaction Kinetics and Ultra-short Channel Devices

## **Permalink**

https://escholarship.org/uc/item/5h11c288

## **Author**

Tang, Wei

# **Publication Date**

2012

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

# Los Angeles

# Silicide/Silicon Heterointerfaces, Reaction Kinetics and Ultra-short Channel Devices

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Materials Science and Engineering

by

Wei Tang

© Copyright by

Wei Tang

# ABSTRACT OF THE DISSERTATION

#### Silicide/Silicon Heterointerfaces, Reaction Kinetics and Ultra-short Channel Devices

by

## Wei Tang

Doctor of Philosophy in Materials Science and Engineering

University of California, Los Angeles, 2012

# Professor King-Ning Tu, Chair

Nickel silicide is one of the electrical contact materials widely used on very large scale integration (VLSI) of Si devices in microelectronic industry. This is because the silicide/silicon interface can be formed in a highly controlled manner to ensure reproducibility of optimal structural and electrical properties of the metal-Si contacts. These advantages can be inherited to Si nanowire (NW) field-effect transistors (FET) device. Due to the technological importance of nickel silicides, fundamental materials science of nickel silicides formation (Ni-Si reaction), especially in nanoscale, has raised wide interest and stimulate new insights and understandings. In this dissertation, *in-situ* transmission electron microscopy (TEM) in combination with FET device characterization will be demonstrated as useful tools in nano-device fabrication as well as in gaining insights into the process of nickel silicide formation. The shortest transistor channel length (17 nm) fabricated on a vapor-liquid-solid (VLS) grown silicon nanowire (NW) has been demonstrated by controlled

reaction with Ni leads on an *in-situ* transmission electron microscope (TEM) heating stage at a moderate temperature of 400 °C. NiSi<sub>2</sub> is the leading phase, and the silicide-silicon interface is an atomically sharp type-A interface. At such channel lengths, high maximum on-currents of 890 ( $\mu$ A/ $\mu$ m) and a maximum transconductance of 430 ( $\mu$ S/ $\mu$ m) were obtained, which pushes forward the performance of bottom-up Si NW Schottky barrier field-effect transistors (SB-FETs). Through accurate control over the silicidation reaction, we provide a systematic study of channel length dependent carrier transport in a large number of SB-FETs with channel lengths in the range of (17 nm – 3.6  $\mu$ m). Our device results corroborate with our transport simulations and reveal a characteristic type of short channel effects in SB-FETs, both in on- and off-state, which is different from that in conventional MOSFETs, and that limits transport parameter extraction from SB-FETs using the conventional field-effect transconductance measurements.

In addition to application of silicide in Si NW devices, the fundamental materials science of Ni-Si reaction is also of interest, and *in-situ* TEM has been shown to be a useful tool in obtaining dynamical phase transformation information and therefore providing insights into the new phase formation process. By using in-situ TEM techniques, a new gold catalyzed solid-liquid-solid (SLS) silicide phase growth mechanism in Si NWs is observed for the first time, which shows the liquid mediating growth can be also used in synthesis of metallic silicide nanowires. SLS is analogous to the VLS in both being liquid-mediated, but is fundamentally different in terms of nucleation and mass transport. In our SLS growth at 700 °C, the Ni atoms are supplied from remote Ni particles by interstitial diffusion through Si NW

into the pre-existing Au particle at the tip. Upon supersaturation of both Ni and Si in Au, octahedral shape of Ni disilicide phase nucleates in the middle of the Au liquid alloy, which thereafter sweeps through the Si NW and transform Si into NiSi<sub>2</sub>. Dissolution of Si by Au(Si,Ni) liquid mediating layer and growth of NiSi<sub>2</sub> are shown to proceed in different manners.

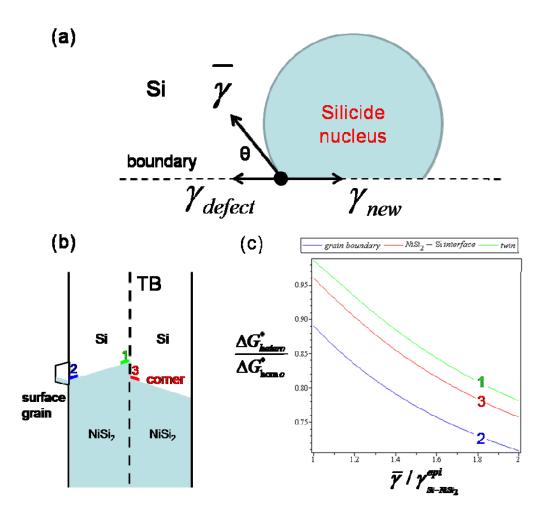

Using *in-situ* TEM technique, we also have the chance to present direct evidence that Si (111) twin boundaries and Si grain boundaries on Si NW surface can be efficient heterogeneous nucleation site for the silicide growth. By analyzing the nucleation site favorability, unlike other typical FCC materials like Cu or Si, we infer (111) twin defects in NiSi<sub>2</sub> may have high interfacial energy. These results may provide valuable insights into the MOSFET source/drain (S/D) contact silicide formation process when defects are either unintentionally formed during the process or intentionally introduced to engineering the strain along the channel.

The dissertation of Wei Tang is approved.

Yu Huang

Ya-Hong Xie

Chi On Chui

King-Ning Tu, Committee Chair

University of California, Los Angeles

2012

This thesis is dedicated to my parents.

# TABLE OF CONTENTS

| ABSTRACT OF THE DISSERTATIONii                                          |

|-------------------------------------------------------------------------|

| TABLE OF CONTENTSvii                                                    |

| LIST OF FIGURESx                                                        |

| LIST OF TABLESxvii                                                      |

| ACKNOWLEDGEMENTS xviii                                                  |

| VITAxx                                                                  |

| PUBLICATIONSxx                                                          |

| Chapter 1 : Introduction1                                               |

| 1.1 Nickel silicide technology in VLSI devices2                         |

| 1.1.1 Self-aligned (Salicide) silicide process                          |

| 1.1.2 Nickel silicide phase formation sequence4                         |

| 1.1.3 Nickel silicide as fully silicide metal gate6                     |

| 1.2 Nickel silicide in Si nanowire devices7                             |

| 1.2.1 Nickel silicide as source/drain extension to nanowire FET device7 |

| 1.2.2 Kinetics of nickel silicide growth in Si nanowire9                                         |

|--------------------------------------------------------------------------------------------------|

| 1.3 References12                                                                                 |

| Chapter 2 : Ultra-short Channel Silicon Nanowire Transistors with Nickel Silicide                |

| Source/Drain Contacts                                                                            |

| 2.1 Introduction                                                                                 |

| 2.2 Material Considerations in Nanochannel Silicidation:                                         |

| 2.3 Device Analysis of Ultra-short Channel SB-FETs:24                                            |

| 2.4 Conclusions34                                                                                |

| 2.5 Supporting Informations35                                                                    |

| 2.6 References                                                                                   |

| Chapter 3 : Gold Catalyzed Nickel Disilicide formation: A New Solid-Liquid-Solid                 |

| Phase Growth Mechanism46                                                                         |

| 3.1 Introduction                                                                                 |

| 3.2 Experimental48                                                                               |

| 3.3 Results and discussion50                                                                     |

| 3.3.1 Solid-Liquid-Solid (SLS) NiSi <sub>2</sub> growth process52                                |

| 3.3.2 Nucleation NiSi <sub>2</sub> in Au (Ni,Si) ternary liquid alloy and initial growth stage58 |

| 3.3.3 Dynamical movement of Au/Si and Au/NiSi <sub>2</sub> interfaces63                          |

| 3.3.4 Reduction of NiSi <sub>2</sub> formation temperature by Au68                        |

|-------------------------------------------------------------------------------------------|

| 3.4 Conclusion                                                                            |

| 3.5 Supporting information70                                                              |

| 3.6 References70                                                                          |

| Chapter 4 : Defect induced heterogeneous nucleation of nickel silicide in Si nanowires 72 |

| 4.1 Introduction                                                                          |

| 4.2 Experimental74                                                                        |

| 4.3 Results and Discussion75                                                              |

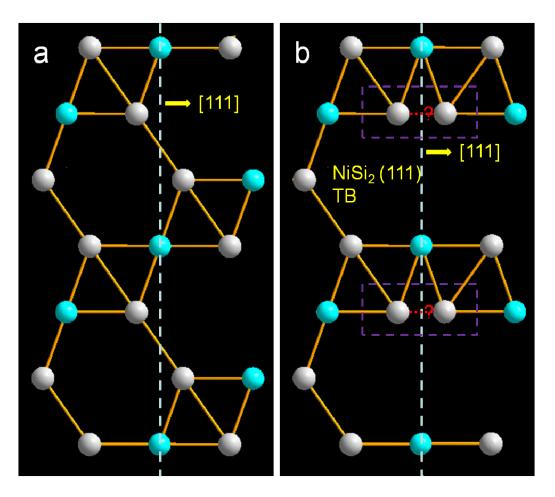

| 4.3.1 NiSi <sub>2</sub> growth in Si NWs with TB running in the center75                  |

| 4.3.2 NiSi <sub>2</sub> growth in Si NWs with both TBs and surface GBs79                  |

| $4.3.3\ NiSi_2$ growth and step development between leading and lagging interfaces84      |

| 4.3.4 Models of the nucleation barrier at different nucleation sites87                    |

| 4.3.5 Stochastic model of the silicide growth process in a twinned Si NW94                |

| 4.4 Conclusion                                                                            |

| 4.5 Supporting information:99                                                             |

| 4.6 References100                                                                         |

| Chapter 5 : Summary and future work102                                                    |

# LIST OF FIGURES

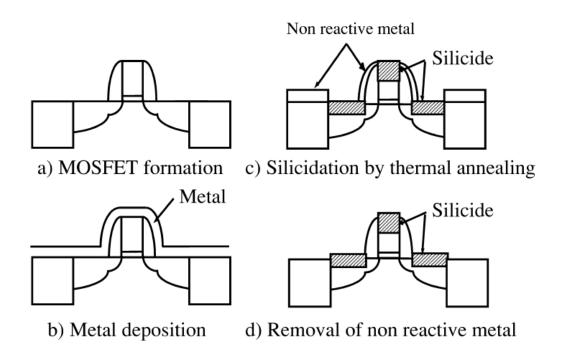

| Figure 1.1 Schematics for salicide process [1].                                                                     |

|---------------------------------------------------------------------------------------------------------------------|

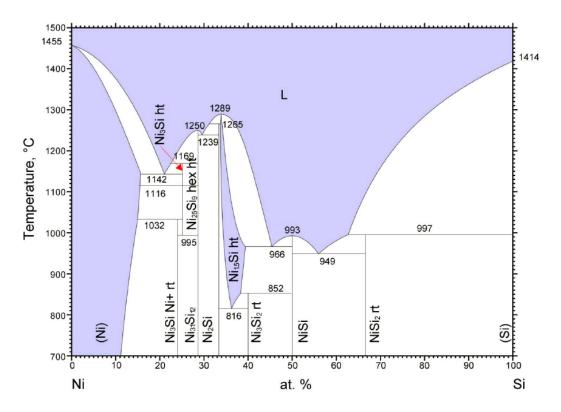

| Figure 1.2 Ni-Si phase diagram                                                                                      |

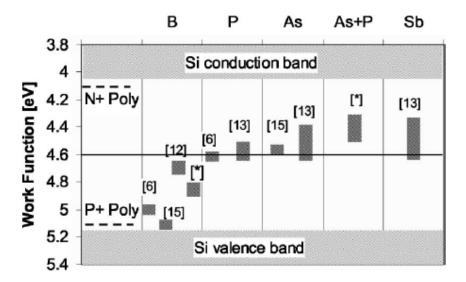

| Figure 1.3 From Ref [14], work function tuning of NiSi formed on pre-doped poly-Si with                             |

| different dopant types. Refer to Ref [14] for citation used in the figure                                           |

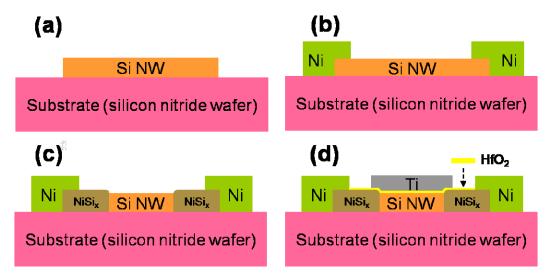

| Figure 1.4 Nickel silicide source/drain Si NW FET fabrication process (a) Si NW dispensing                          |

| (b) Ni contact definition (c) Nickel silicide formation at elevated temperature (d) Gate                            |

| dielectric layer deposition and metal gate definition9                                                              |

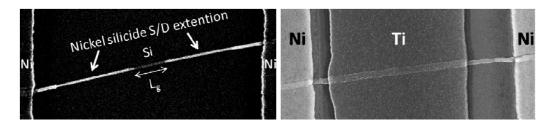

| Figure 1.5 (a) Si NW channel with nickel silicide S/D extension (b) $\Omega$ -gate Si NW FET9                       |

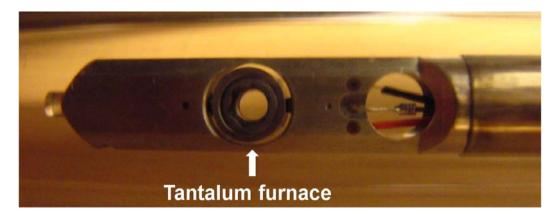

| Figure 1.6 Gatan Single Tilt Heating Holder 628 with Tantalum furnace                                               |

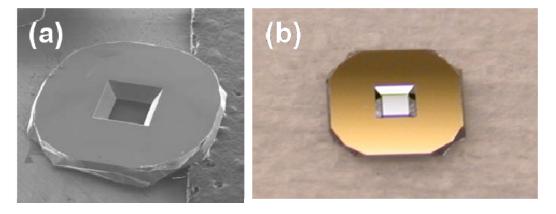

| Figure 1.7 TEM silicon nitride membrane window (a) SEM image (b) optical image10                                    |

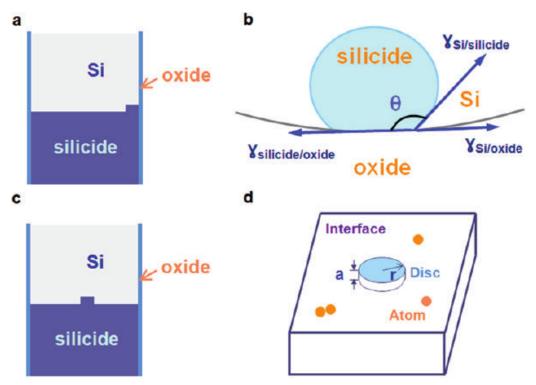

| Figure 1.8 (a) Heterogeneous nucleation of a 2D silicide step at the Si/oxide interface (b)                         |

| top-view of (a). (c) Homogeneous nucleation of a 2D silicide step in the center of the Si NW                        |

| (d) schematics of a homogeneously formed disk.[31]11                                                                |

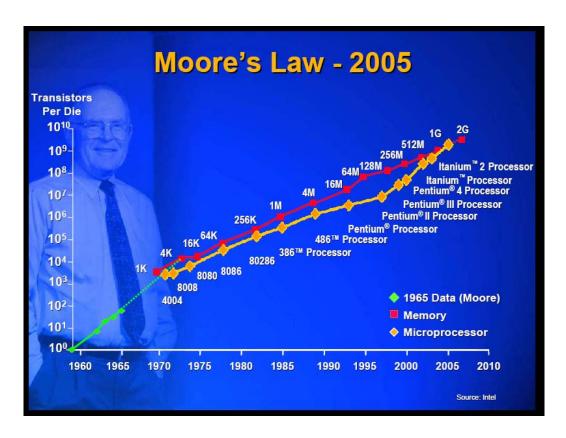

| Figure 2.1 Moore's law showing the trend of device miniaturization                                                  |

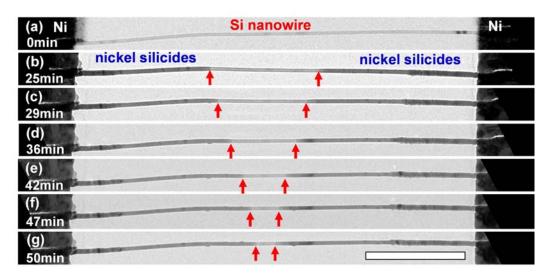

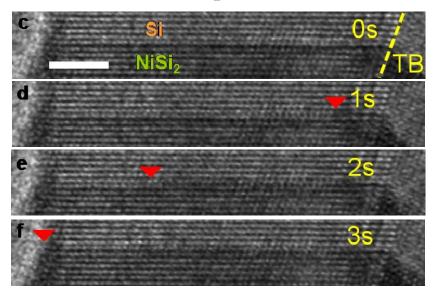

| Figure 2.2 (a-g) Series of <i>in-situ</i> TEM snapshots showing the growth of nickel silicide from                  |

| S/D Ni electrodes and narrowing of the middle silicon segment. The red arrows indicate the                          |

| silicide/silicon reaction front. Scale bar is 1 μm                                                                  |

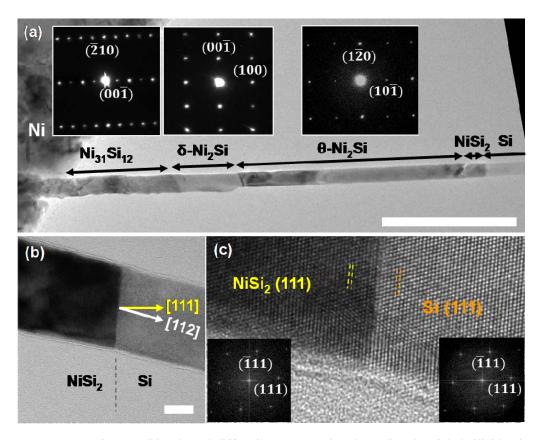

| Figure 2.3 (a) TEM image with selected diffraction patterns that determine the nickel                               |

| silicide phase sequence: Between Ni and Si, several phases are formed including Ni <sub>31</sub> Si <sub>12</sub> , |

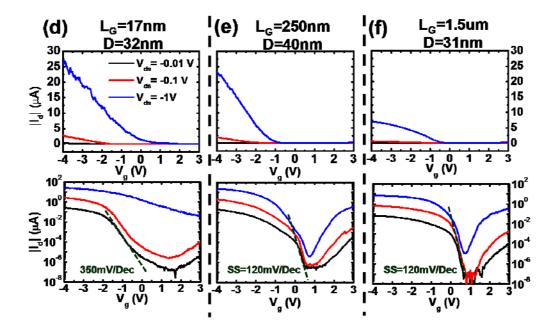

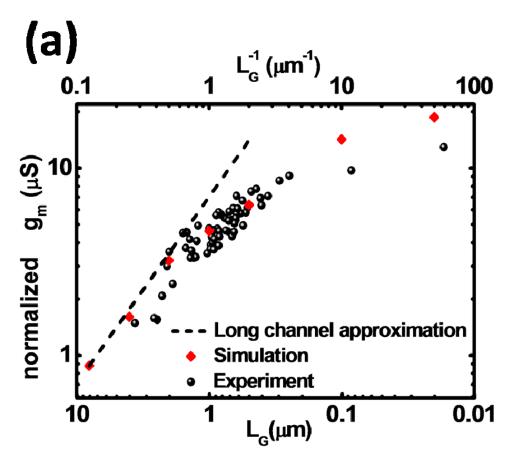

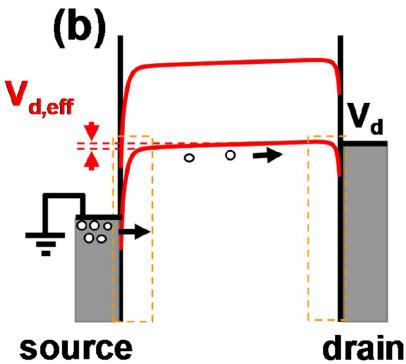

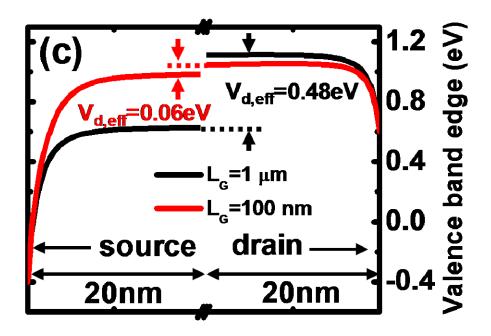

δ-Ni<sub>2</sub>Si<sub>2</sub>θ-Ni<sub>2</sub>Si and NiSi<sub>2</sub>. Zone axes for inset diffraction patterns from left to right are [120], [010], and [212], respectively. The scale bar is 400 nm. (b) Zoom-in TEM image of the NiSi<sub>2</sub>/Si interface, showing the reaction front is Si (111) plane even in a <112> grown silicon NW. The scale bar is 20 nm (c) HRTEM image of the atomically flat NiSi<sub>2</sub>/Si interface. The crystal orientation across the interface corresponds to a type A interface. The epitaxial Figure 2.4 (a) Schematics of the top-gate FET device with ultra-short silicon channel (Si nanogap) (b) TEM image of a 17 nm silicon channel. Scale bar is 20 nm. (c) TEM bright field image of a top gate Si NW SB-FET fabricated on silicon nitride membrane. (d-f) Transfer curves with both linear (top panels) and log (bottom panels) for devices with channel length of 17 nm, 250 nm and 1.5 µm, and diameters of 32 nm, 40 nm and 31 nm, respectively. The V<sub>ds</sub> in each plot from low to high are -0.01 V (black), -0.1 V (red) and -1 V (blue)......26 Figure 2.5 (a) Double log plot of normalized maximum transconductance as a function of channel length. Each black small circle represents measured transconductance from an individual experimental device, and large red diamonds represent extracted transconductance from simulated devices with different channel lengths. The dashed line describes the trend predicted by the long channel approximation from (Equation (2.1)). (b) Axial band diagram near the surface of a 100 nm channel device in the on-state. The valence band profile can be divided into 3 regions (from left to right): source SB region, channel region, and drain SB region. Both of the SB regions are highlighted by dashed boxes. The voltage drop across the channel region is denoted as V<sub>d,eff</sub> (c) Comparison of the valence band profile at the

| source/drain SB region (i.e., the part of the device highlighted by dashed boxes in (b)) of                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| devices with 100nm and 1 $\mu$ m channel lengths during on-state operation (V <sub>ds</sub> = -1 V, V <sub>g</sub> = -4                          |

| V). $V_{d,eff}$ in the 100nm channel length device is a small fraction of the total source/drain                                                 |

| bias                                                                                                                                             |

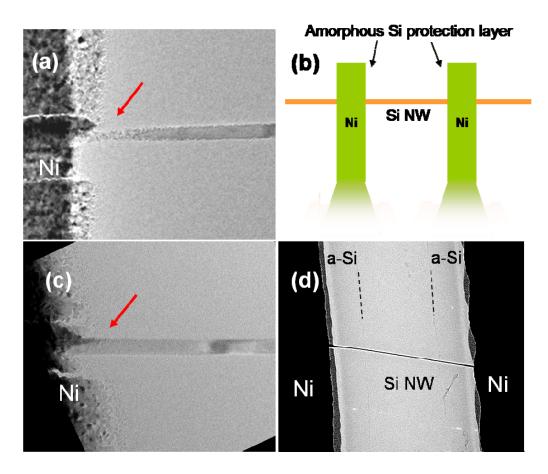

| Figure 2.6 (a) The unprotected segment of the Si NW close to the Ni contact is etched during                                                     |

| a BOE dip. (b) Top-view cartoon illustrating the use of a PECVD amorphous silicon layer to                                                       |

| protect Ni from the BOE etchant. (c) With an amorphous Si protection layer, the Si NW                                                            |

| remains intact after a BOE dip as highlighted by the red arrow, which contrasts the situation                                                    |

| of the unprotected NW in (a). (d) A low magnification TEM image showing the a-Si                                                                 |

| protection layer whose boundary is highlighted with dashed black-lines                                                                           |

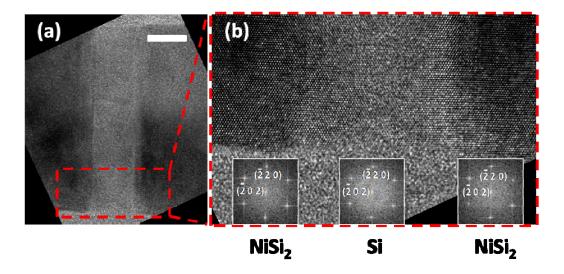

| Figure 2.7 (a) a short Si channel. The scale bar is 10nm. (b) HRTEM image of the                                                                 |

| source/channel and drain/channel interface, showing the leading phase is $NiSi_2$ even when the                                                  |

| channel is very short                                                                                                                            |

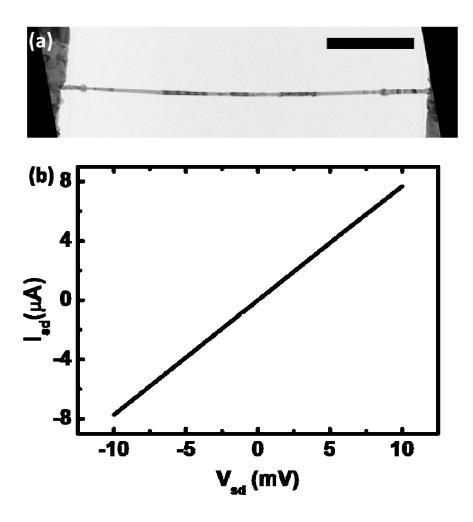

| Figure 2.8 (a) a fully silicided Si NW. The scale bar is $1\mu m$ (b) Corresponding two terminal                                                 |

| IV39                                                                                                                                             |

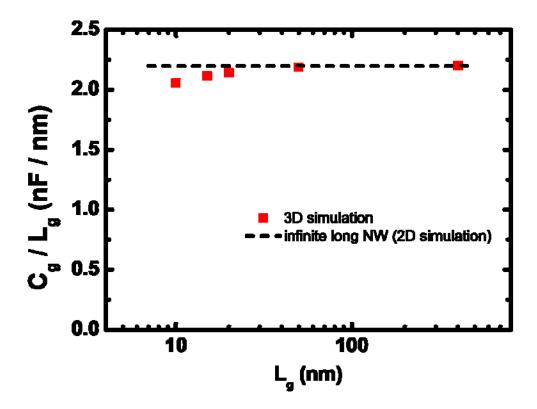

| Figure 2.9 The gate capacitance per length obtained from full 3D simulation of NW with                                                           |

| different channel lengths and the asymptotic limit of infinite long NW by 2D simulation40                                                        |

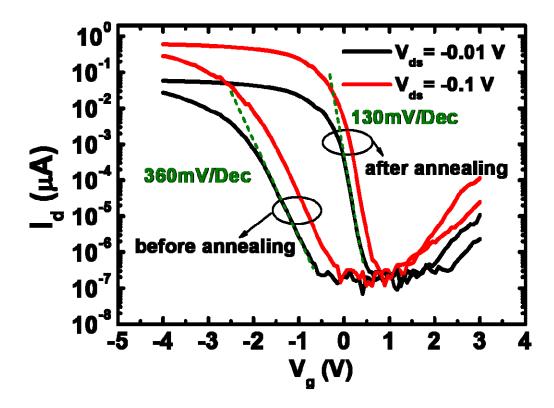

| Figure 2.10 Post-metal-gate annealing in forming gas at 300°C for 1min helps to improve                                                          |

| on-current and inverse subthreshold slope. The channel length is 0.83 $\mu m$ and the NW                                                         |

| diameter is 35 nm                                                                                                                                |

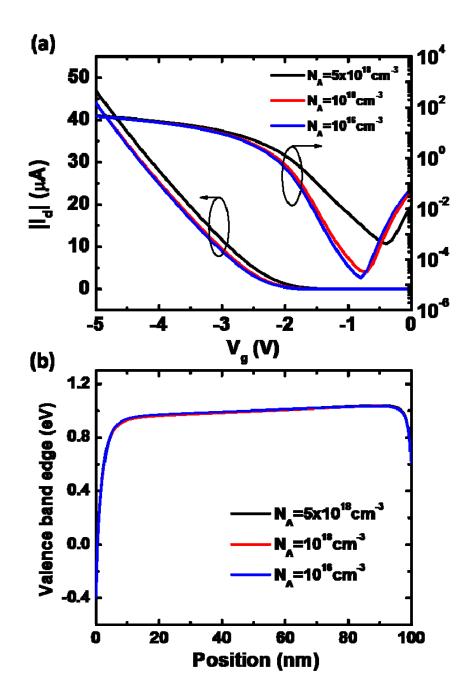

| Figure 2.11 Comparison of simulated devices with $10^{16}$ cm <sup>-3</sup> , $10^{18}$ cm <sup>-3</sup> and $5 \times 10^{18}$ cm <sup>-3</sup> |

| p-type doping densities: (a) Transfer curves, and (b) valence band-edge profiles in the                    |

|------------------------------------------------------------------------------------------------------------|

| on-state ( $V_{ds}$ =-1V, $V_{g}$ =-4V)                                                                    |

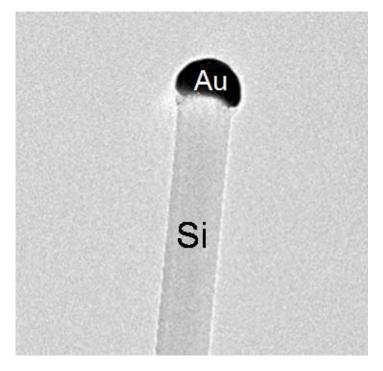

| Figure 3.1 Gold tip on a VLS grown Si NW                                                                   |

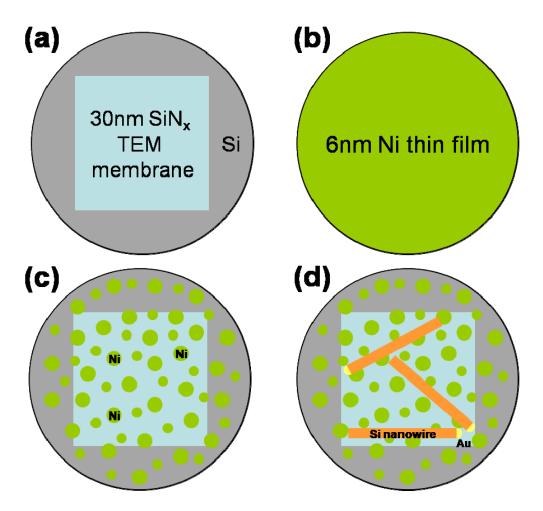

| Figure 3.2 (a) 30 nm thick silicon nitride TEM membrane (b) Deposition of 6 nm Ni thin film                |

| by e-beam evaporation (c) Annealing of Ni thin film at 650 °C and breaking it into Ni                      |

| nanoparticles (d) dispensing Si NWs in random contact with Ni nanoparticles. The tip have a                |

| drop of Au                                                                                                 |

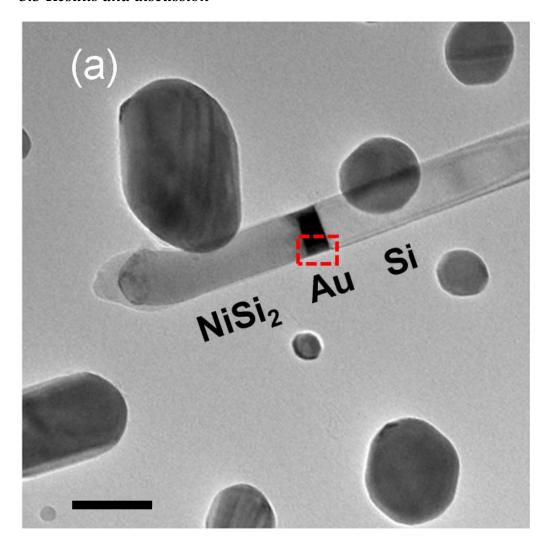

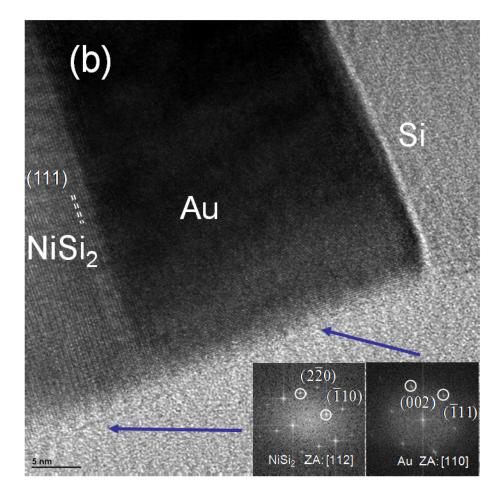

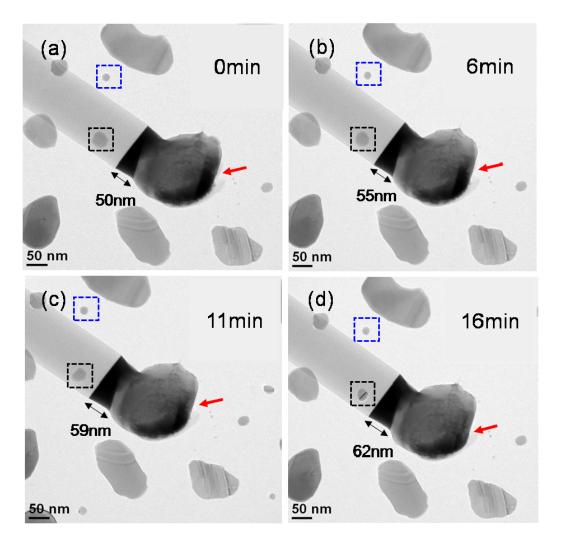

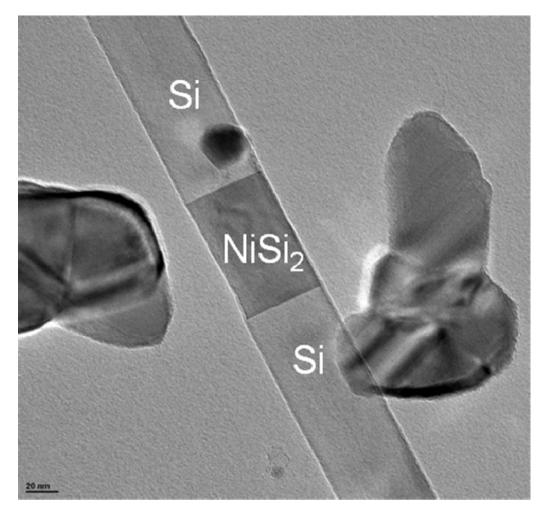

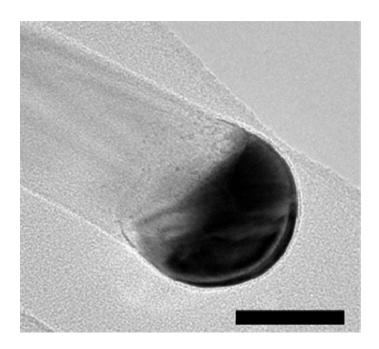

| Figure 3.3 (a) TEM bright field image showing NiSi <sub>2</sub> forms from the tip of the nanowire with    |

| gold moving towards the opposite end. Scale bar is 100 nm (b) HRTEM image of the area                      |

| around Au. The reaction front is NiSi <sub>2</sub> (111) plane51                                           |

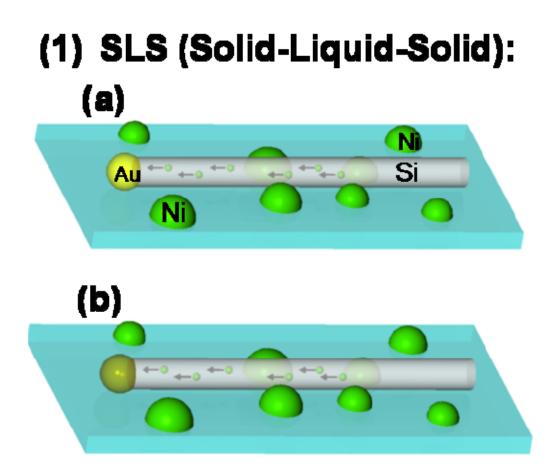

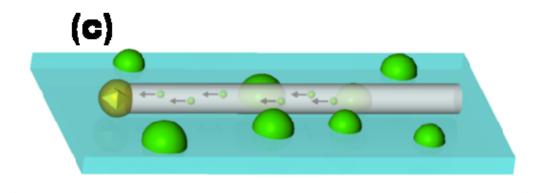

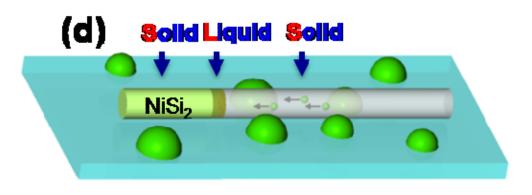

| Figure 3.4. (1) SLS growth (a) Ni diffusion and accumulation in the Au-Si eutectic alloy. (b)              |

| Formation of a liquid Au-Ni-Si ternary alloy at the Si NW tip (c) Nucleation of a single NiSi <sub>2</sub> |

| crystallite (d) Continuous growth of NiSi2 in a steady state (e) Schematics of Ni                          |

| concentration and chemical potential when SLS growth reaches a steady state (2) VLS                        |

| growth (f) Eutectic alloying between Au particle and Si substrate (g) Supersaturation and                  |

| nucleation of a Si step in Au-Si eutectic alloy (h) Continuous growth of Si NW in the steady               |

| state;                                                                                                     |

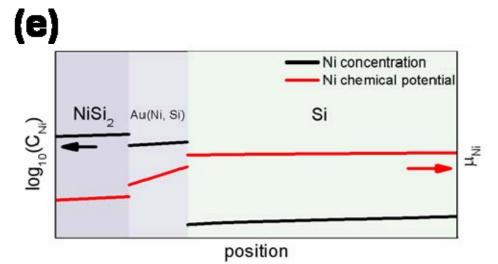

| Figure 3.5. (a-c) Emerging and growth of octahedral shape of NiSi <sub>2</sub> crystallite from the Au     |

| liquid ternary alloy (d) Schematic of a octahedron bounded by 8 {111} facets57                             |

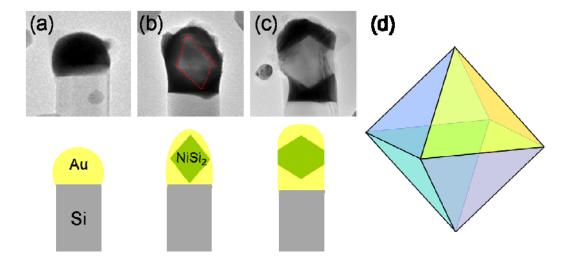

| Figure 3.6. (a-d) <i>In-situ</i> TEM snapshots showing (i) Gradual disappearance of Au at the tip          |

| indicated by red arrow (ii) Growth of Au liquid mediating layer in length, marked by xiii                  |

| double-headed arrow. (iii) Shrinkage of Ni particle in contact with Si NW, which are marked                          |

|----------------------------------------------------------------------------------------------------------------------|

| by black dashed box. (iv) No size change for the Ni particle not in contact with Si NW, which                        |

| are marked by blue dashed box                                                                                        |

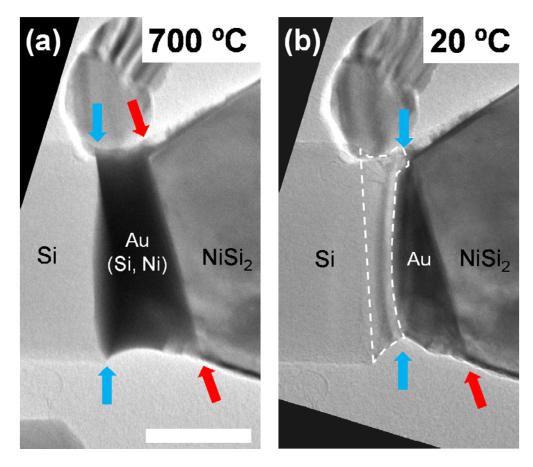

| Figure 3.7. Au mediating layer before (a) and after (b) quenching from 700 °C. The Au/NiSi <sub>2</sub>              |

| interface indicated by red arrow does not move, while the Si/Au interface marked by blue                             |

| arrow contracts with Si (highlighted by white dash) precipitated out from Au. Scale bar is 50                        |

| nm                                                                                                                   |

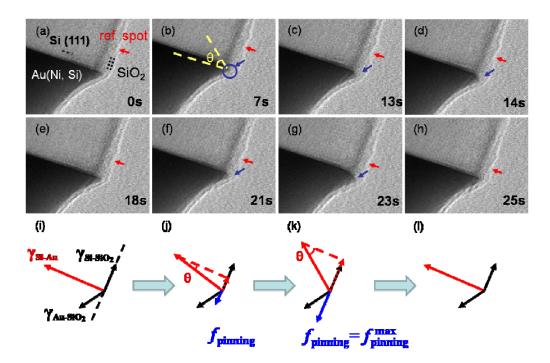

| Figure 3.8. (a-h) <i>In-situ</i> TEM snapshots showing two cycles of contact angle oscillation at the                |

| triple junction point. Red arrow indicates a reference spot on the NW surface. Blue arrow                            |

| indicates curvature develops at the triple junction point. (i-l) Force analysis of the mechanism                     |

| of contact angle oscillation at the triple junction point, corresponding to the sub-panel images                     |

| (e-h)64                                                                                                              |

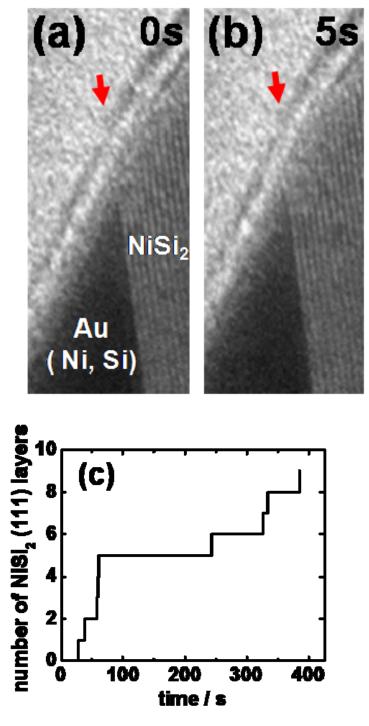

| Figure 3.9. (a-b) Growth of a single NiSi <sub>2</sub> (111) layer. (c) Plane-wise growth of NiSi <sub>2</sub> (111) |

| layer over time                                                                                                      |

| Figure 3.10. NiSi <sub>2</sub> homogeneously nucleates in Si NW at 800 °C                                            |

| Figure 3.11 Si NW with oxide capsulated Au tip                                                                       |

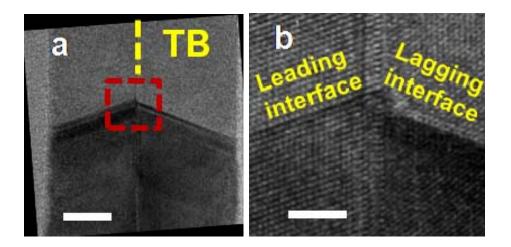

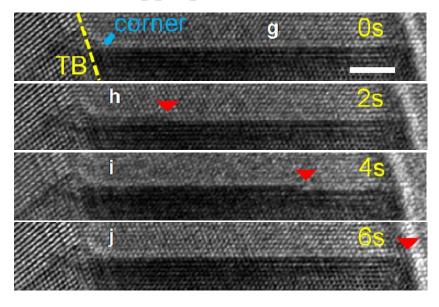

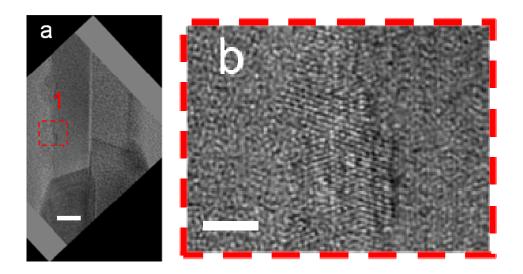

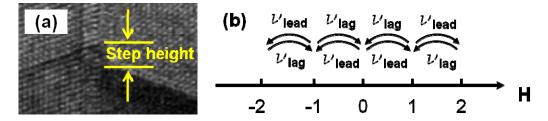

| Figure 4.1 (a) Si NW with a TB running down its center. Scale bar is 10 nm (b) Zoom-in                               |

| image of the dash box in (a) showing asynchronical growth of leading interface and lagging                           |

| interface. Scale bar is 3 nm (c-f) Nucleation and propagation of a (111) NiSi <sub>2</sub> plane at the              |

| leading interface from the TB. Scale bar is 3 nm (g-j) Nucleation and propagation of a (111)                         |

| NiSi <sub>2</sub> plane at the lagging interface from the "corner". Scale bar is 3 nm                                |

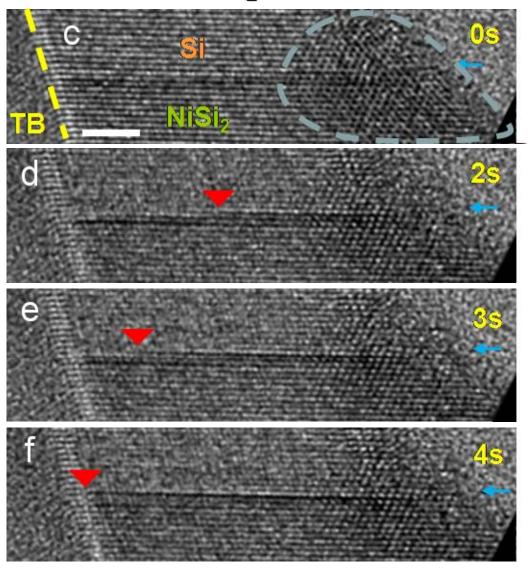

| Figure 4.2. (a) Si NW with TB running down the center and surface GBs. Scale bar is 10 nm.                                  |

|-----------------------------------------------------------------------------------------------------------------------------|

| (b) Zoom-in of several surface grains that have different orientation with respect to the NW                                |

| stem. Scale bar is 3 nm (c-f) Nucleation and propagation of a (111) NiSi <sub>2</sub> plane at the leading                  |

| interface from the surface GB. Scale bar is 3 nm. (g-j) Nucleation and propagation of a (111)                               |

| NiSi <sub>2</sub> plane at the lagging interface from the surface GB. Scale bar is 3 nm81                                   |

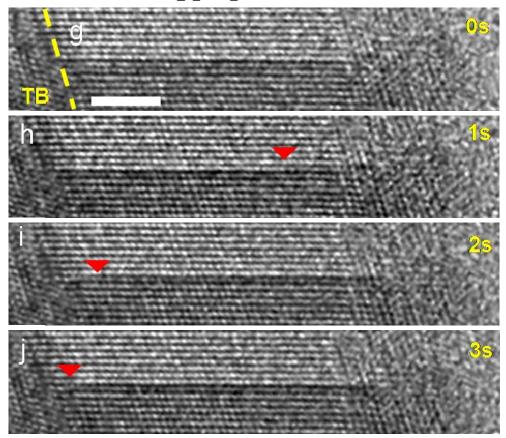

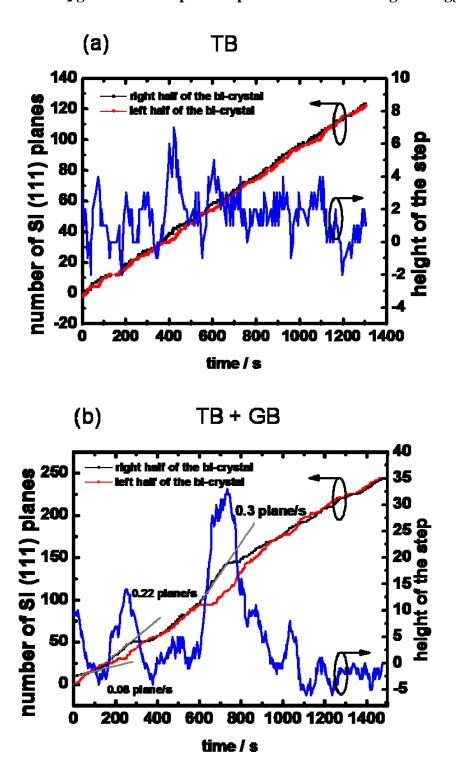

| Figure 4.3. Growth of NiSi <sub>2</sub> (111) plane and step height between leading/lagging interfaces in                   |

| Si NW with (a) TB and (b) both TB and GB                                                                                    |

| Figure 4.4. (a) Top view of a NiSi <sub>2</sub> 2D partial disk heterogeneously nucleate at certain                         |

| boundary. (b) Schematics of three different heterogeneous nucleation sites (c) Reduction of                                 |

| nucleation barrier at different heterogeneous sites                                                                         |

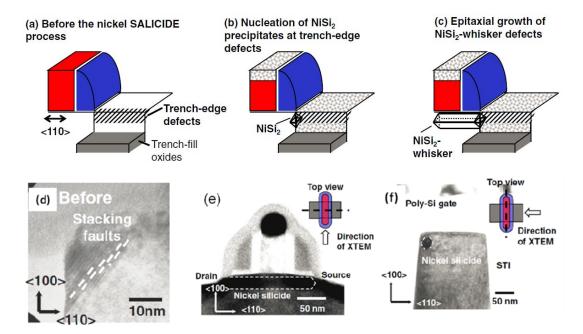

| Figure 4.5 From Ref. [22]. (a) Trench edge defects formed after S/D dopant activation                                       |

| process when they are bounded by trench oxide fill. (b) NiSi <sub>2</sub> nucleation at those trench-edge                   |

| defects (c) Growth of NiSi2 whisker into the channel and failure of the device. (d) TEM                                     |

| images showing stacking faults as the trench-edge defects. (e-f) Cross-section TEM image                                    |

| along different direction showing NiSi <sub>2</sub> whisker grown into Si channel92                                         |

| Figure 4.6 From Ref [24] (a-c) Stress memorization technology (d) TEM picture of stacking                                   |

| fault formed in S/D area. (e) Schematics of the mechanism of tensile strain in the channel                                  |

| induced by the stacking fault. 93                                                                                           |

| Figure 4.7 Biased random walk in H space                                                                                    |

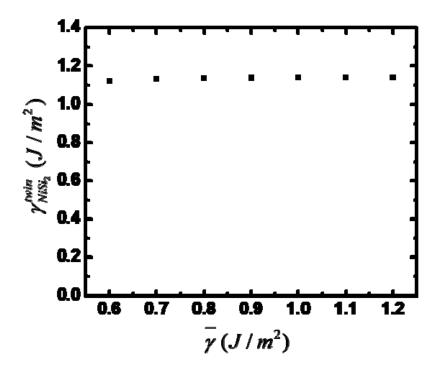

| Figure 4.8 Dependence of $\gamma_{NiSi_2}^{twin}$ on $\overline{\gamma}$                                                    |

| Figure 4.9. (a) $(\overline{1}10)$ plane in a perfect NiSi <sub>2</sub> crystal. Si atoms are grey and Ni atoms are $_{xv}$ |

green. (b) A possible structure of  $NiSi_2$  ( $\overline{1}10$ ) plane when (111) twin is present. New chemical bonds across the TB may form between nearby Si atoms.......99

# LIST OF TABLES

| Table 2.1Structural data and electrical resistivity of various type of nickel silicide phase38 |

|------------------------------------------------------------------------------------------------|

| Table 4.1 Summary of interfacial energetic parameters used in the nucleation model for al      |

| three cases9                                                                                   |

| Table 4.2 Interfacial energy parameters for leading and lagging interface growth in a twinner  |

| Si NW90                                                                                        |

#### ACKNOWLEDGEMENTS

Finishing this thesis is impossible without the help and support from the kind people around me. I would like to take this opportunity to express my sincere gratitude and appreciation to them.

First of all, I have been always grateful to my advisor Professor King-Ning Tu. His knowledge, open mind, way of thinking is always a source of wisdom. His continuous support and encouragement is important for me to accomplish any work done in this thesis. I would like to extend my gratitude to my other committee members: Professor Ya-Hong Xie, Professor Yu Huang, Professor Chi On Chui for their helpful comments in my work.

I feel lucky to have obtained the privilege to work in Center for Integrated Nanotechnologies (CINT). I would like to express my sincere gratitude to my host Dr. Tom Picraux. Under his coordination, I was able to make the best use of resources and my time in CINT. His keen interest in the progress of my research and sharp scientific insight are also great encouragement. I would like to thank Dr. Shadi Dayeh, who is my closest mentor and friend in CINT. His broad knowledge in electronic devices always inspired me to look at my results in different ways. It cannot be a more enjoyable experience to work with Shadi and even working with him itself was a miracle. I would like to thank Dr. Blythe Clark in Sandia National Lab, who allows me to use the TEM heating stage, even during the time when the stage is also in high demand at her end.

I would like to thank my gratitude to my supervisor Professor Ning Wang in Hong Kong

University of Science and Technology (HKUST). I had the first exposure to research in nanotechnology during my visit to HKUST and received rigorous training of TEM from him. I would like to extend my gratitude to Dr. Yuan Cai, Dr. Tailun Wong, Dr. Chun Cheng, Dr. Yao Cheng, and Mr. Tze Kin Cheung.

I would like to thank Dr. Tian Tian for her assistance in sample preparation, Dr. Jung-Kyu Han and Dr. Di Xu for their help in equipment setup, and Dr. Daechul Chui for his tea at 1:00am.

I would like to thank my parents for their unconditional support, encouragement and appreciation.

The list does not mean to be exhaustive and I would like to thank all other people who have helped me but are not mentioned above.

## VITA

Summer 2007 B.S. Physics

Peking University, Beijing, China

Fall 2007 Chancellor's Fellowship

Dept. Materials Science and Engineering

University of California, Los Angeles

Summer 2008 – Winter 2009 Visiting Research Assistant

Hong Kong University of Science and Technology

Summer 2010 – Winter 2011 Visiting Facility User

Center for Integrated Nanotechnologies

Albuquerque, New Mexico

# **PUBLICATIONS**

# JOURNAL PAPERS

- Wei Tang, Shadi A. Dayeh, S. Tom Picraux, Jian Yu Huang, King-Ning Tu, "Ultrashort Channel Silicon Nanowire Transistors with Nickel Silicide Source/Drain Contacts", Accepted by Nano Letters, to be published ASAP

- Wei Tang, Shadi A. Dayeh, S. Tom Picraux, Xiaohua Liu, Jian Yu Huang, King-Ning Tu,

"Gold Catalyzed Ni Disilicide Formation in Si Nanowires: A New Solid-Liquid-Solid

- (SLS) Phase Growth Mechanism", in preparation

- 3. Wei Tang, Shadi A. Dayeh, S. Tom Picraux, Jianyu Huang, King-Ning Tu, "Effect of defects on nickel disilicide nucleation in silicon nanowires", *in preparation*

- Jinkyoung Yoo, Bonghwan ChonWei, <u>Wei Tang</u>, Taiha Joo, Dang Le Si, Gyu-Chul Yi,

"Excitonic origin of enhanced luminescence quantum efficiency in MgZnO/ZnO coaxial nanowire heterostructures", *Applied Physics Letters*, 100, 223103 (2012)

- Kai Chen, N. Tamura, <u>Wei Tang</u>, M. Kunz, Yi-Chia Chou, K. N. Tu and Yi-Shao Lai, "High precision thermal stress study on flip chips by synchrotron polychromatic X-ray Microdiffraction", *Journal of Applied Physics*, **107**, 063502 (2010)

# CONFERENCE PRESENTATIONS

- Wei Tang, Shadi A. Dayeh, S. Tom Picraux, Xiaohua Liu, Jianyu Huang, King-Ning Tu,

"Gold Catalyzed Ni Disilicide Formation in Si Nanowires: A New Solid-Liquid-Solid

(SLS) Phase Growth Mechanism", Oral presentation, MRS Spring meeting, San

Francisco, CA, April 2012

- 2. <u>Wei Tang</u>, Shadi A. Dayeh, S. Tom Picraux, Xiaohua Liu, Jianyu Huang, King-Ning Tu, "Gold Catalyzed High Temperature Silicide formation in Si Nanowires: A New Solid-liquid-Solid (SLS) Phase Growth Mechanism within a Solid Matrix", Oral presentation, Physics and Chemistry of Surfaces and Interfaces, Santa Fe, NM, Jan 2012

- 3. Wei Tang, Shadi A. Dayeh, S. Tom Picraux, King-Ning Tu, "Si Nanowire Schottky

Barrier Transistors with Short Channels formed by Controlled Si/Silicide Interfaces

- Movement", Oral presentation, Physics and Chemistry of Surfaces and Interfaces, Santa Fe, NM, Jan 2012

- Wei Tang, Shadi Dayeh, Tom Picraux, King-Ning Tu, "FET devices with ultra-short channel length built on silicide/silicon/silicide heterostructures", Oral presentation, 2011

Materials Research Society Fall meeting, Boston, Massachusetts, December 2011

- Wei Tang, Shadi Dayeh, Tom Picraux, King-Ning Tu, "Silicide/silicon/silicide nanowire heterostructures and devices", Oral presentation, 2011 Electronic Materials Conference, Santa Barbara, CA

# **Chapter 1: Introduction**

Nickel silicides have been a critical element in the microelectronic products because they forms the metal/semiconductor interface to semiconductor devices. Historically, silicide with low resistivity and high temperature stability has been examined as the metal-semiconductor contact materials. Silicide technologies have moved from Ti silicide, Co silicide and eventually to Ni silicide due to demands on increased process compatibility and decreased resistivity. This chapter aims at provide a general review of the silicide technology in modern VLSI device fabrication process, materials science in the silicide formation, and transits to application of silicide in Si nanowire (NW) devices.

# 1.1 Nickel silicide technology in VLSI devices

# 1.1.1 Self-aligned (Salicide) silicide process

Figure 1.1 Schematics for salicide process [1].

We will first look at the role of nickel silicide in VLSI devices. Nickel silicide is used as the electrical contact material to both heavily doped source/drain (S/D) and gate through a self-aligned silicide process (salicide). After formation of MOSFET (Figure 1.1a), blanket Ni film is deposited on the Si wafer (Figure 1.1b). Nickel silicide is selectively formed in the contact openings during thermal treatment (Figure 1.1c) and unreacted Ni is removed (Figure 1.1d). Since Ni is the dominant diffusing specie in the Ni-Si reaction[2], the bridging effect that otherwise shorts the gate and S/D (e.g. in TiSi<sub>2</sub> case) is eliminated. Also, NiSi has the

advantage of low formation temperature (about 400 °C). Compared with their counterpart C54-TiSi<sub>2</sub> (850 °C) and CoSi<sub>2</sub> (800 °C) in the previous technology generation[1]. Besides, with the downscaling of MOSFET channel length and therefore the contact line width, TiSi<sub>2</sub> and CoSi<sub>2</sub> contacts were subjected to sheet resistance degradation (narrow line effect) successively at the technology node 180 nm and 90 nm due to difficulty in nucleation of the low resistivity phase and grain agglomeration at high temperature [3]. The requirement of shallow junction formation also favors NiSi, because to form silicide line with the same resistivity, NiSi consumed the least Si. Therefore, nickel silicide is the choice of contact metal for current deep sub-100nm technology node. We explored the use of nickel silicidation reaction as an approach to form the contact to ultra-short channel Si NW transistor and the results will be discussed in details in Chapter 2.

# 1.1.2 Nickel silicide phase formation sequence

Figure 1.2 Ni-Si phase diagram

According to the phase diagram of Ni-Si system, multiple nickel silicide phases are stable at room temperature, including NiSi<sub>2</sub>, NiSi, Ni<sub>3</sub>Si<sub>2</sub>,  $\delta$ -Ni<sub>2</sub>Si, Ni<sub>31</sub>Si<sub>12</sub>, Ni<sub>3</sub>Si. In the reaction of bulk Ni-Si vertical[4] and lateral [5, 6] diffusion couple, multiple above phases are observed. However, in the reaction of Ni film (in the range of several hundred nanometers) with Si wafer, the resulted nickel silicide phase follows a well define phase sequence as temperature ramps up:  $\delta$ -Ni<sub>2</sub>Si is the first phase formed at a temperature as low as 200 °C, and transformed to NiSi as the temperature is raised above 350 °C, and finally converts to NiSi<sub>2</sub> at above 750 °C [7].

To understand the absence of multiple phase formation in the thin film reaction, a comprehensive kinetic model for competing growth of multiple phase was proposed[8] In this model, after the first diffusion controlled phase (δ-Ni<sub>2</sub>Si in the Ni-Si case) is formed, growth of the second phase does not start until the thickness of the first phase segment reaches a "critical thickness". This critical thickness was defined when the atomic fluxes of the dominant diffusion specie to and away from the interface between two competing phases are equal. In other words, regarding the growth of the first phase (diffusion controlled), it grows fast when its thickness is small and the growth rate gradually decreases as its thickness increases. Now consider the formation of a potential second phase (NiSi in the Ni-Si case). If it is interfacial reaction controlled and its growth rate is lower than the first phase, this potential second phase does not appear and there is only a single phase in this diffusion couple. When the growth rate of the potential second phase is higher than the first phase, the second phase will be observed, resulting in simultaneous multiple phase growth, which corresponds to a bulk diffusion couple case. The critical thickness was estimated to be about 2µm in the temperature range of 300 °C to 430 °C. Since the thickness of silicide contact is much less than 2 µm, the kinetic reasoning explains the "single phase growth" phenomenon in contact reactions. Therefore, all the contacts on the Si chip are the same. This can also explain the multiple phase growth in a Ni pad to Si NW reaction, in which the reaction is closer to the thermodynamic limit. This will be discussed in details in Chapter 2.

It has been suggested [9-11] the selection criteria for the first phase is the one that degrades system Gibbs free energy at a maximum rate (i.e. maximize  $-\frac{d\Delta G}{dt}$ ). Note the

relation  $-\frac{d\Delta G}{dt} = -\frac{d\Delta G}{dX}\frac{dX}{dt}$ , where  $\frac{d\Delta G}{dX}$  is the driving force and  $\frac{dX}{dt}$  is the growth rate of this phase. Therefore, the selection of the first phase is determined by both thermodynamic and kinetic factors.

#### 1.1.3 Nickel silicide as fully silicide metal gate

Downscaling of effective oxide thickness (EOT) of the gate dielectric is critical in advancing technology node in improving the MOSFET performance and alleviating short channel effect. When SiO<sub>2</sub> is scaled down to a few atomic layer thick, direct tunneling from the gate to the channel will cause device failure. High-k dielectric materials such as HfO<sub>2</sub> has been used because to achieve a small EOT, the physical thickness of HfO<sub>2</sub> can be thicker due to its much higher dielectric constant (26) than SiO<sub>2</sub> (3.9). However, when poly-Si gate is used with typical high-k material, the channel is subjected to remote phonon scattering (RPS) [12] and carrier mobility is severely degraded, especially under high field. Metal gates have to be used with high-k dielectric materials because the high carrier density in metals will screen out RPS. Also, using metal gate can eliminate poly-Si depletion effect. [13]

The metals to be used for PMOS and NMOS should have different work functions to meet their different switching requirement. It has been found that the work function of NiSi formed after transforming poly-Si gate can be tuned by adjusting doping levels and dopant types in the original poly-Si gate. [14]

Figure 1.3 From Ref [14], work function tuning of NiSi formed on pre-doped poly-Si with different dopant types. Refer to Ref [14] for citation used in the figure.

Generally speaking, n-type dopant shifts NiSi Fermi level above Si midgap and p-type dopant shifts that below Si midgap, which tunes the work function of the NiSi to the same direction as doping poly-Si gate (Figure 1.3). The mechanism of this work function modulation by dopants was attributed to interfacial dipoles formed by dopants pileup (snow-plow effect) during NiSi formation process. However, there is a recent debate [15] arguing the work function modulation is a bulk instead of an interface effect.

## 1.2 Nickel silicide in Si nanowire devices

#### 1.2.1 Nickel silicide as source/drain extension to nanowire FET device

Si NW FET fabricated by top-down [16-20] or bottom-up [21] method has been intensively investigated as alternative device structure to replace the traditional planar

MOSFET. Its advantage lies in that the nanowires are inherent 3D objects and  $\Omega$ -shape gates or gate-all-around structures can easily form to maximize the gate control over the channel and relieve short channel effect. Due to superior property of nickel silicides (e.g. clean metal/semiconductor interface, reproducible electronic characteristics), they (or their counterpart germanide in Ge device) were also used in nanowire FET device [22-25].

One unique aspect of using silicide as the contact material is its formation process. A typical fabrication process of Si NW FET with nickel silicide as source/drain materials is described in Figure 1.4. After Ni contact annealing, nickel silicide S/D extension forms from Ni pad and grows into the Si NW (Figure 1.4c and Figure 1.5a). The channel length L<sub>g</sub> can be tuned by controlling this reaction process. We utilized and monitored the reaction on an *in-situ* TEM heating stage and achieved a 17nm Si channel (Chapter 2). The silicide S/D contact formed in this way allows a metal top-gate to fully cover the Si channel and maximize the electrostatic gate control over the channel.

Figure 1.4 Nickel silicide source/drain Si NW FET fabrication process (a) Si NW dispensing (b) Ni contact definition (c) Nickel silicide formation at elevated temperature (d) Gate dielectric layer deposition and metal gate definition

Figure 1.5 (a) Si NW channel with nickel silicide S/D extension (b)  $\Omega$ -gate Si NW FET

## 1.2.2 Kinetics of nickel silicide growth in Si nanowire

It is important to understand the kinetics of nickel silicide growth in Si NW in order to achieve reproducible control over the contact and Si channel formation in Si NW FET device. The growth kinetics itself is also an interesting topic from the aspect of fundamental materials science. For studies of kinetic in phase transformation phenomena in NWs, *in-situ* TEM has

been a useful tool in capturing dynamical structure change information and providing insights into the phase transformation process. [26-29]

Figure 1.6 Gatan Single Tilt Heating Holder 628 with Tantalum furnace

Figure 1.7 TEM silicon nitride membrane window (a) SEM image (b) optical image

The *in-situ* TEM is well-versed in investigation phase transformation under various external conditions, e.g. heating, mechanical stressing, electrical stressing etc, depending on the TEM holder used. In studies of Ni-Si reaction, we used a TEM heating stage (Figure 1.6, Gatan Single Tilt Heating Holder 628) to heat up Ni sources and Si NWs on silicon nitride

TEM membranes (Figure 1.7) and observe the nickel silicide formation process dynamically. Similar setups are also used by other investigators.

Lu *et al* first obtained HRTEM images of nickel silicide growth in Si NW on an *in-situ* TEM heating stage.[30] The Si NW is in contact with multiple Ni NWs and nickel silicide was formed from the two ends of the Si NW and gradually transformed Si NW into nickel silicide NWs. HRTEM imaging combined with temperature tuning of the heating stage allows for precise control of the reaction at atomistic scale, and a Si gap as short as 2 nm was achieved. Our approach to fabricate ultra-short channel Si NW FETs (Chapter 2) inherits and develops the methodology in this work.

Figure 1.8 (a) Heterogeneous nucleation of a 2D silicide step at the Si/oxide interface (b) top-view of (a). (c) Homogeneous nucleation of a 2D silicide step in the center of the Si NW (d) schematics of a homogeneously formed disk.[31]

Chou et al found when CoSi<sub>2</sub> grows into Si NW, the reaction front proceeds in a stepwise manner. [32] In-situ HRTEM was used to track the step propagation, and emerging of each new step implies repeating 2D nucleation of a single CoSi<sub>2</sub> layer. Further investigation showed that the new silicide step nucleates homogeneously in the center of the Si NW and then propagates to the edge of it.[31] Homogeneous nucleation was very rarely observed because the nucleation barrier is high and usually new phase can first heterogeneously nucleate at certain interfaces in the system associated with a lower nucleation barrier. A comparison of homogeneous and heterogeneous nucleation of a 2D silicide step is summarized in Figure 1.8. The reason for absence of 2D heterogeneous nucleation here is that, to form a silicide step at the edge of the Si NW, a high energy Si/silicide interface will replace the low energy Si/oxide interface, which is energetically unfavorable. Therefore the new 2D silicide step has to nucleate homogeneously at the center of the Si NW. This result closely resembles our observation (to be discussed in more details in Chapter 3) that NiSi<sub>2</sub> nucleate homogeneously in the middle of Au-Ni-Si ternary alloy, due to a similar mechanism in selecting nucleation sites. Besides, in Chapter 3, change of 2D silicide nucleation site in Si NW, when defects are present, will be further discussed in Chapter 4.

# 1.3 References

- 1. Iwai, H., T. Ohguro, and S.i. Ohmi, *NiSi salicide technology for scaled CMOS*. Microelectronic Engineering, 2002. **60**(1): p. 157-169.

- 2. Weber, E.R., *Transition-Metals in Silicon*. Applied Physics a-Materials Science & Processing, 1983. **30**(1): p. 1-22.

- 3. Chen, L.J., Silicide technology for integrated circuits. 2004, London: Institution of

- Electrical Engineers. xviii, 279 p.

- 4. Gulpen, J.H., A.A. Kodentsov, and F.J.J. Vanloo, *GROWTH OF SILICIDES IN NI-SI AND NI-SIC BULK DIFFUSION COUPLES*. Zeitschrift Fur Metallkunde, 1995. **86**(8): p. 530-539.

- 5. Chen, S.H., et al., *Transmission electron microscopy studies on the lateral growth of nickel silicides*. Journal of Applied Physics, 1985. **57**(2): p. 258-263.

- 6. Zheng, L.R., L.S. Hung, and J.W. Mayer, *Silicide formation in lateral diffusion couples*. Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films, 1983. **1**(2): p. 758-761.

- 7. Tu, K.N., et al., *Epitaxial-Growth of Nickel Silicide Nisi2 on Silicon*. Japanese Journal of Applied Physics, 1974: p. 669-672.

- 8. Gosele, U. and K.N. Tu, *Growth kinetics of planar binary diffusion couples:* "Thin-film case" versus "bulk cases". Journal of Applied Physics, 1982. **53**(4): p. 3252-3260.

- 9. Gosele, U. and K.N. Tu, *``Critical thickness'' of amorphous phase formation in binary diffusion couples.* Journal of Applied Physics, 1989. **66**(6): p. 2619-2626.

- 10. Hesse, D., et al., Interfacial reaction barriers during thin-film solid-state reactions: The crystallographic origin of kinetic barriers at the NiS<sub&gt;2&lt;/sub&gt;/Si(111) interface. Applied Physics A: Materials Science & Processing, 1993. 57(5): p. 415-425.

- 11. Bene, R.W., A kinetic model for solid-state silicide nucleation. Journal of Applied Physics, 1987. **61**(5): p. 1826-1833.

- 12. Robertson, J., *High dielectric constant gate oxides for metal oxide Si transistors*. Reports on Progress in Physics, 2006. **69**(2): p. 327-396.

- 13. Taur, Y. and T.H. Ning, *Fundamentals of modern VLSI devices*. 1998, Cambridge: Cambridge University Press. xxii, 469 p.

- 14. Maszara, W.P., *Fully Silicided Metal Gates for High-Performance CMOS Technology: A Review.* Journal of The Electrochemical Society, 2005. **152**(7): p. G550-G555.

- 15. Nakayama, T., et al. Theory of workfunction control of silicides by doping for future Si-nano-devices based on fundamental physics of why silicides exist in nature. in Electron Devices Meeting (IEDM), 2010 IEEE International. 2010.

- 16. Jing, Z., et al., *High-Performance Si Nanowire Transistors on Fully Si Bulk Substrate From Top-Down Approach: Simulation and Fabrication.* Nanotechnology, IEEE Transactions on, 2010. **9**(1): p. 114-122.

- 17. Peng, J.W., et al., *Improved carrier injection in gate-all-around Schottky barrier silicon nanowire field-effect transistors*. Applied Physics Letters, 2008. **93**(7).

- 18. Tan, E.J., et al., *Demonstration of Schottky barrier NMOS transistors with erbium silicided source/drain and silicon nanowire channel.* Ieee Electron Device Letters, 2008. **29**(10): p. 1167-1170.

- 19. Jiang, Y., et al., Nickel Salicided Source/Drain Extensions for Performance Improvement in Ultrascaled (Sub 10 nm) Si-Nanowire Transistors. Ieee Electron Device Letters, 2009. **30**(2): p. 195-197.

- Singh, N., et al., Ultra-narrow silicon nanowire gate-all-around CMOS devices: impact of diameter, channel-orientation and low temperature on device performance.

2006 International Electron Devices Meeting (IEEE Cat No. 06CH37807C), 2006: p. 4 pp.-4 pp.4 pp.

- 21. Cui, Y. and C.M. Lieber, Functional nanoscale electronic devices assembled using silicon nanowire building blocks. Science, 2001. **291**(5505): p. 851-853.

- 22. Lin, Y.C., et al., Single crystalline PtSi nanowires, PtSi/Si/PtSi nanowire heterostructures, and nanodevices. Nano Letters, 2008. **8**(3): p. 913-918.

- 23. Appenzeller, J., et al. *Dual-gate silicon nanowire transistors with nickel silicide contacts*. in *Electron Devices Meeting*, 2006. *IEDM '06. International*. 2006.

- 24. Hu, Y., et al., Sub-100 Nanometer Channel Length Ge/Si Nanowire Transistors with Potential for 2 THz Switching Speed. Nano Letters, 2008. **8**(3): p. 925-930.

- 25. Weber, W.M., et al., *Silicon-nanowire transistors with intruded nickel-silicide contacts*. Nano Letters, 2006. **6**(12): p. 2660-2666.

- 26. Huang, J.Y., et al., *In Situ Observation of the Electrochemical Lithiation of a Single SnO2 Nanowire Electrode.* Science, 2010. **330**(6010): p. 1515-1520.

- 27. Zheng, H., et al., *Observation of Transient Structural-Transformation Dynamics in a Cu2S Nanorod.* Science, 2011. **333**(6039): p. 206-209.

- 28. Xin, H.L. and H. Zheng, *In Situ Observation of Oscillatory Growth of Bismuth Nanoparticles*. Nano Letters, 2012. **12**(3): p. 1470-1474.

- 29. Zheng, H., et al., *Discrete plasticity in sub-10-nm-sized gold crystals*. Nat Commun, 2010. **1**: p. 144.

- 30. Lu, K.C., et al., In situ control of atomic-scale Si layer with huge strain in the nanoheterostructure NiSi/Si/NiSi through point contact reaction. Nano Letters, 2007. 7(8): p. 2389-2394.

- 31. Chou, Y.-C., et al., *Homogeneous Nucleation of Epitaxial CoSi2 and NiSi in Si Nanowires*. Nano Letters, 2009. **9**(6): p. 2337-2342.

- 32. Chou, Y.-C., et al., *In-situ TEM Observation of Repeating Events of Nucleation in Epitaxial Growth of Nano CoSi2 in Nanowires of Si.* Nano Letters, 2008. **8**(8): p. 2194-2199.

## Chapter 2: Ultra-short Channel Silicon Nanowire Transistors with Nickel Silicide Source/Drain Contacts

## 2.1 Introduction

Vapor liquid solid (VLS) grown semiconductor nanowires (NWs) have been intensively investigated as candidates of electronic devices due to their decent crystal quality[1], easiness of control over lateral confining dimension[2, 3], and potential for bottom-up self-assembled circuits[4-6]. Field-effect transistors (FETs) built on VLS grown Si, Ge and SiGe heterostructure NWs have shown high carrier motilities and excellent transistor characteristics comparable to or better than those fabricated by top-down processing approaches[7, 8].

Enhanced FET performance is enabled with ever-smaller channel lengths that can provide high on-current drives or reduced power consumption. The microelectronic industry has been pursuing smaller and faster devices since it was established half a century ago. The trend of devices miniaturization follows the prediction by Moore's law (Figure 2.1). Si NW FETs have been considered as a candidate structure for extremely scaled transistors. The primary advantages for using NWs are the fact that their gates can be formed in a  $\Omega$ -gate or gate-all-around geometries, and therefore have superior electrostatic coupling between gate and channel over other device architectures and able to relieve short channel effect, including drain-induced-barrier lowering (DIBL) and degradation in sub-threshold slope [9].

Figure 2.1 Moore's law showing the trend of device miniaturization

The NW transistor channel length is usually defined by the metal gate width, or the distance between its source/drain (S/D) electrodes, both of which are limited by lithography patterning tools. With continual transistor down-scaling, the demands on the critical dimension (CD) control in lithography tools steadily increases. For CD below 20nm, very expensive e-beam lithography tools or sophisticated photolithography technologies (extreme ultraviolet source, double patterning, etc) are needed[10].

By extending earlier works [11, 12] on controlled silicide formation in *in-situ* TEM experiments, we developed a process that can overcome the resolution limit posed by lithography technologies in defining transistor channels. Using this technique, we

demonstrate SB-FETs with ultra-short channel lengths down to 17nm on VLS grown Si NWs. Compared with the conventional MOSFET, a SBFET has naturally abrupt junctions and is not limited by lateral doping profiles, which are determined by the doping/activation techniques[13, 14] and become increasingly difficult for ultra-short channel devices. Our investigation also includes the silicidation reaction fundamentals (phase formation and growth kinetics), which is important to achieve a fine control over transistor channel lengths previously not achieved with VLS NW FETs. The controlled channel formation using this technique enabled us to access a new domain of SB-FET operation and to identify a performance transition between long channel and short channel regions in SB-FETs with an overall transport performance that is in excellent agreement with our transport simulations. This is because in NW FETs, the contacts are non-ohmic because the NW is undoped. Further, our systematic transport studies elucidates the essential role of Schottky barriers in charge transport in ultra-short channel FETs and demonstrate that transport parameter extraction using conventional transconductance methods from SB-FETs may not be accurate. The implications of this analysis can be generalized to other NW SB-FETs.

#### 2.2 Material Considerations in Nanochannel Silicidation:

Nickel silicides are the standard metal contacts used in the semiconductor industry for both NMOS and PMOS devices and are regarded as 'mid-gap' metals with a hole Schottky barrier height (SBH) of ~ 0.4 eV on p-Si[15, 16]. Moreover, nickel silicides (or their counterparts, nickel germanides in germanium devices) have been extensively explored as nanoscale contacts for semiconductor NWs[17-21] and therefore our choice as the electrical contacts to

Si NW devices. In the Ni-Si reaction, Ni is the dominant diffusing species (DDS), and multiple nickel silicide phases could form[22]. Different nickel silicide phases have different Ni concentration and diffusivity[23], and growth of a more Ni-rich phase by consuming a less Ni-rich phase also needs Ni supplies from the metal contact reservoir. The phenomenon of simultaneous growth of multiple phases complicates the kinetics analysis that uses the data of silicided segment length versus time. To better understand and control the Ni-Si reaction kinetics for the fabrication of ultra-short channel FETs, we examine first the nickel silicide phases in our silicided NW segments and provide a detailed analysis on the silicide/silicon interface structure and quality that can have direct impact on formed silicide/silicon barrier heights and charge injection.

Our SB-FET devices were fabricated on 50 nm thick silicon nitride TEM membranes with a window size of 250  $\mu$ m  $\times$  250  $\mu$ m. Source/drain Ni contacts were defined by photolithography, followed by 100 nm e-beam evaporated Ni layer. The native oxide on the Si NWs at contact openings is removed before metallization. After S/D metallization, and to avoid creation of defects in the native oxide layer on the Si channel during the subsequent high energy electron radiation (300 keV) in TEM (Tecnai F30), we went through a special procedure[24] to remove this native oxide layer.

Annealing of the sample was performed on an *in-situ* TEM heating stage (Gatan 628 single tilt heating holder) at 425 °C, and the reaction was monitored in real-time. Initially, nickel silicide formed at the source/drain Ni/Si contact, grew inward by transforming Si NWs. The remaining Si segment of the NW shrinks as the reaction proceeds.

Figure 2.2 (a-g) shows a series of TEM snapshots during the reaction process. If not interrupted, the whole Si NW would be fully converted into a metallic nickel silicide NW. However, we are interested in using this process to demonstrate that we can dynamically control the length of Si segment and use it as the channel in FET devices. When the length of the Si segment (referred as Si channel thereafter) reaches a desired length, we stop heating the sample, which thereafter cools down quickly (~10 °C/s) and the interface is frozen. To fabricate ultra-short Si channel, very precise control of the reaction process or the silicide growth rate is required. In the final stage of Si channel length tuning, the silicide growth rate was reduced to about 0.05 nm/s at 375 °C, which allows for sub-nanometer fine control over the channel length.

Figure 2.2 (a-g) Series of *in-situ* TEM snapshots showing the growth of nickel silicide from S/D Ni electrodes and narrowing of the middle silicon segment. The red arrows indicate the silicide/silicon reaction front. Scale bar is 1 μm.

We find that there are multiple phases formed on the Si NW as the reaction front swept through (Figure 2.3a). The phases are determined by electron diffraction patterns and fast Fourier transformation (FFT) of high resolution (HR) TEM images obtained from at least two different zone axes. The leading phase in direct contact with Si is NiSi2, which is immediately followed by θ-Ni<sub>2</sub>Si within a distance of 50 nm. Going further outwards in the direction to the Ni leads, the  $\theta$ -Ni<sub>2</sub>Si is followed by a  $\delta$ -Ni<sub>2</sub>Si segment. Then, a more nickel-rich phase Ni<sub>31</sub>Si<sub>12</sub> follows in direct vicinity with the Ni leads. During the process of silicidation, Ni diffuses into the Si crystal, and the resulting Ni-Si compound volume is generally greater than the original Si volume, which appears with diameter expansion compared with the as-grown Si NW diameter (Figure 2.3a). The only exception of volume expansion resides in the NiSi<sub>2</sub> phase because of its close similarity in crystal structure and lattice parameter with Si. We observe diameter expansion when Si is transformed to  $\theta$  -Ni<sub>2</sub>Si, δ -Ni<sub>2</sub>Si or Ni<sub>31</sub>Si<sub>12</sub>. This phase sequence is in contrast with the results obtained in a thin film reaction between planar Si and Ni thin films, which were established from in-situ XRD and resistance measurements during the temperature ramp up[25]. We recall that in thin film studies,  $\delta$  -Ni<sub>2</sub>Si is the first phase formed at a temperature as low as 200 °C, and transformed to NiSi as the temperature is raised above 350 °C, and finally converts to NiSi<sub>2</sub> at above 750 °C[26]. The expected NiSi phase was not observed in our experiments, which corroborates with earlier results from the reaction between Ni pads and Si NWs at 550 °C[27], 450 °C[28] and 360 °C[29], and from the reaction between Ni thin films and Si wafers at 450 °C[30, 31], all of which showed  $NiSi_2$  as the leading phase at temperatures well below 750 °C. It has been suggested that the interfacial oxygen may play a role in mediating NiSi2 formation at low temperature[31], however, there is currently no definite explanation of the mechanism of low temperature formation of NiSi<sub>2</sub>. Another silicide phase θ -Ni<sub>2</sub>Si, which follows NiSi<sub>2</sub> in the upstream direction towards the Ni leads, has a hexagonal lattice structure (a=3.836 Å, b=4.948 Å). According to Ni/Si phase diagram, θ-Ni<sub>2</sub>Si is a high temperature phase, which is stable above 825 °C. However, recent studies on Ni and Si NW reaction have also found  $\theta$ -Ni<sub>2</sub>Si formed at a low temperature[32]. Moreover, in-situ X-ray diffraction studies of Ni-Si reaction shows that  $\theta$  -Ni<sub>2</sub>Si is a transient phase, which appears first at low temperatures, but disappears as the temperature is increased[33]. This is in good agreement with our results in that  $\theta$  -Ni<sub>2</sub>Si is also quickly consumed by  $\delta$  -Ni<sub>2</sub>Si after it forms. Another experiment[34] to test the stability of this phase shows that the  $\theta$ -Ni<sub>2</sub>Si phase formed at high temperatures transforms into  $~\delta$  -Ni $_2Si$  and  $~\epsilon$  -Ni $_3Si_2$  as predicted by the phase diagram as it is cooled down below its stable temperature 825 °C. On the other hand, θ-Ni<sub>2</sub>Si formed at a low temperature (460 °C) does not decompose during temperature cool down even to room temperature. These experiments suggest that although  $\theta$  -Ni<sub>2</sub>Si is a high temperature phase, it has certain type of stability at low temperatures, likely due to high kinetic barriers for phase transformation.

Figure 2.3 (a) TEM image with selected diffraction patterns that determine the nickel silicide phase sequence: Between Ni and Si, several phases are formed including Ni<sub>31</sub>Si<sub>12</sub>,  $\delta$ -Ni<sub>2</sub>Si,  $\theta$ -Ni<sub>2</sub>Si and NiSi<sub>2</sub>. Zone axes for inset diffraction patterns from left to right are [120], [010], and [212], respectively. The scale bar is 400 nm. (b) Zoom-in TEM image of the NiSi<sub>2</sub>/Si interface, showing the reaction front is Si (111) plane even in a <112> grown silicon NW. The scale bar is 20 nm (c) HRTEM image of the atomically flat NiSi<sub>2</sub>/Si interface. The crystal orientation across the interface corresponds to a type A interface. The epitaxial relationship is established as NiSi<sub>2</sub> (111) // Si (111) and NiSi<sub>2</sub> [110] // Si [110].

Among all the phases and interfaces formed along the NW axial direction, the NiSi<sub>2</sub>/Si interface is the metal-semiconductor contact interface. It is interesting to observe that the

Ni-Si reaction front is Si (111) plane, even in a [112] grown Si NW (Figure 2.3b-c). The HR TEM image in Figure 2.3c shows that the interface is atomically sharp, and the epitaxial relationship established from the image is NiSi<sub>2</sub> (111) // Si (111) and NiSi<sub>2</sub> [110] // Si [110]. The slanted interface observed here has a larger area compared with a cross-sectional plane that is perpendicular to the NW growth direction. The fact that the silicide-silicon NW system chooses to form a larger interfacial area implies that the Si(111)/NiSi<sub>2</sub>(111) interface has lower energy than that of all other possible interface configurations. In a reaction between Ni thin film and Si (001) wafer, inverted NiSi<sub>2</sub> pyramids[31, 35, 36] with {111} facets form inside the Si wafer, showing the same reaction front as we observe here. It is known that the NiSi<sub>2</sub>/Si interface is among the best quality metal semiconductor interfaces[37], because the two crystals share the same cubic structure and a very close lattice constant (a<sub>Si</sub>=5.430 Å, a<sub>NiSi2</sub>=5.406 Å). The interfacial electronic properties are determined by the detailed structure of the NiSi<sub>2</sub>/Si interface. Two types of NiSi<sub>2</sub>/Si interfaces can form with a difference in their crystal orientations across the interface. NiSi<sub>2</sub> has the same orientation with Si in a type-A interface, while it is rotated 180° about the interface normal axis with respect to Si in a type-B interface. It is known [38] that these two interfaces have different SBH with n-Si (0.65 eV on type-A and 0.78 eV on type-B). In a large area thin film reaction [36], usually the NiSi<sub>2</sub>/Si interface is a mixture of type-A and type-B. In contrast, throughout the high resolution transmission electron microscopy (HRTEM) characterization of our nanoscale contacts, we consistently observe atomically sharp type-A NiSi<sub>2</sub>/Si interface, which guarantees the reproducibility of the electronic properties of the metal/semiconductor contact.

### 2.3 Device Analysis of Ultra-short Channel SB-FETs:

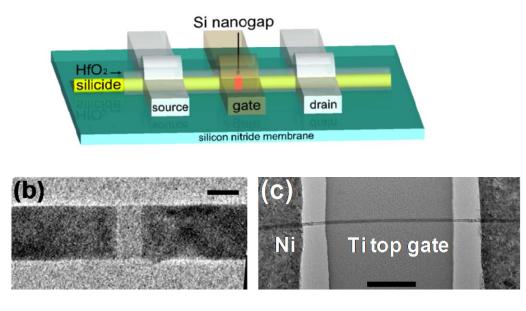

With this thorough understanding of formation, structure, and expected electronic properties of our silicide-Si NW interface, we are able to precisely scale down the channel length of a NiSi<sub>2</sub>-Si NW transistor and explain its carrier transport characteristics. The silicide growth rate can be controlled by carefully tuning the temperature at the final stage of the silicidation reaction. Schematic of our top-gated Si FET device structure is shown in Figure 2.4a, with ultra-short channel (Si nanogaps) highlighted on the Si NW. We have obtained a 17 nm Si channel on a VLS grown Si NW (Figure 2.4b) at a temperature of 375 °C. HfO<sub>2</sub> gate dielectric (10nm) was conformally deposited on the Si NW devices using atomic layer deposition at 200 °C. At this temperature, no further silicidation was observed, and the Si channel length was retained at the desired value. Finally, 100nm Ti was deposited as the top-gate electrode. Figure 2.4c shows a TEM bright field image of the fabricated device on the 17 nm Si NW channel (Figure 2.4b). NiSi<sub>2</sub> is still the leading phase in such very short Si NW channels (Figure 2.7, supporting information). In our devices, the leakage current from gate electrode to S/D nickel silicide extensions is small (<1pA when  $V_g=-4$  V) and we are only interested in DC characteristics of the device, so the gate-S/D overlapping was not of concern. To better gauge the characteristics of the Si FET with ultra-short channel, we have also fabricated devices with longer Si channels with the same gate dielectric layer. As suggested in ref. [39], we perform a post-metal-gate annealing step for 60 seconds in forming gas at 300 °C to passivate the interface traps at the Si/HfO2 interface. This treatment step consistently improves the gate control on the channel so that both the on current and inverse

subthreshold slope (SS<sup>-1</sup>) were substantially improved (see supporting information Figure 2.10 for a comparison).

Transfer curves (both in linear scale and log scale) of Si NW FET with channel lengths,  $L_G$ =17 nm, 250 nm and 1.5  $\mu$ m are shown in Figure 2.4d-f. As the transistor channel length is scaled down, the on-current  $I_{on}$  at  $V_{ds}$ = -1 V increases from 7uA ( $L_G$ =1.5  $\mu$ m) to 23uA ( $L_G$ =250 nm) and finally to 27 uA ( $L_G$ =17 nm). This trend is intuitively expected, since we are measuring current from a shorter Si segment at the same bias; this trend however does not scale linearly as we will discuss below. The series resistance of the nickel silicide S/D extension can be neglected even in our shortest channel devices, based on electrical measurement of a fully silicided Si NW of the same length as well as calculation of the resistance using known resistivity values of nickel silicides from literature (see Table 2.1 and Figure 2.8 in supporting information for more details).

Figure 2.4 (a) Schematics of the top-gate FET device with ultra-short silicon channel (Si nanogap) (b) TEM image of a 17 nm silicon channel. Scale bar is 20 nm. (c) TEM bright field image of a top gate Si NW SB-FET fabricated on silicon nitride membrane. (d-f) Transfer curves with both linear (top panels) and log (bottom panels) for devices with channel length of 17 nm, 250 nm and 1.5  $\mu$ m, and diameters of 32 nm, 40 nm and 31 nm, respectively. The  $V_{ds}$  in each plot from low to high are -0.01 V (black), -0.1 V (red) and -1 V (blue).

The increase in on-current is desirable because it allows faster operation of logic circuits (or lower power consumption if the current is held constant at a reduced supply voltage). On the other hand, the SS<sup>-1</sup> degrades from 120 mV/Dec for  $L_G$ =250 nm channel device to 350 mV/Dec for  $L_G$ =17 nm ultra-scaled channel device. The off-state leakage current also increases in the 17 nm device. The  $I_{off}$  and SS<sup>-1</sup> degradation are attributed to insufficient gate control over the NW channel electrostatics in such devices with close proximity of S/D when

switching the device off. We note here that our NW has a diameter of 30 nm. Both  $SS^{-1}$  and  $I_{off}$  are expected to be improved if a thinner NW (thin body) was used.

Higher on-state conduction is one of the motivations that drive the semiconductor industry to devote increasing endeavors in down-scaling of the MOSFET channels. To assess the on-state performance as a function of channel length, we use the maximum transconductance  $g_m$  ( $V_{ds}$ = -1 V) as a figure-of-merit and compare experimentally extracted values from 64 devices with those obtained from transport simulations. In long channel approximation,  $g_m$  is inversely proportional to  $L_G$  and is given by

$$g_m = \frac{\mu_h V_d C_G}{L_G^2} \tag{2.1}$$

where  $g_m$  is the maximum transconductance of an individual device,  $\mu_h$  is the hole mobility,  $L_G$  is the channel length,  $V_d$  is the drain bias and  $C_G$  is the gate capacitance. To correlate the geometrical factors of the gate capacitance, we developed an empirical formula for  $\Omega$ -gate capacitance,  $C_G^{\Omega}$ , by curve fitting to capacitance values obtained from finite element simulations,

$$C_G^{\Omega}(h,r) = L_G \left[ 2\pi - 2 \operatorname{acos} \left( \frac{1 - h/r}{1 + h/r} \right) + a \cdot (h/r) + b \cdot (h/r)^2 \right] \varepsilon_0 \varepsilon_r / \ln[1 + h/r]$$

(2.2)

Here, r is the radius of the NW, h is the dielectric layer thickness,  $\varepsilon_r$  is the relative dielectric constant of the gate insulator layer. In a top-gated NW FET, the gate covers a portion of the surface of the NW. The term  $2a\cos\left(\frac{1-h/r}{1+h/r}\right)$  accounts for the central angle of the uncovered circular sector of the NW cross-section by the gate metal.  $a \cdot (h/r)$  and  $b \cdot (h/r)^2$  are first and second order correction terms of the tangential fringing fields.

Equation (2.2)reduces the well known cylindrical capacitance  $C_G(h,r) = 2\pi L_G \varepsilon_0 \varepsilon_r / \ln[1 + h/r]$  with a fully surrounded gate (first two terms in brackets of Equation  $(2.2)=2\pi$ ), and in the absence of asymmetric fringing fields (a=b=0). For the case of thin dielectrics in a  $\Omega$ -gate configuration (h/r < 1), the fringing field parameters were found to be a = 2.086 and b = 0.852 which yields capacitance values that are within 2% error of those obtained from 2D simulations. In the extreme of  $h/r \ll 1$ , the gate capacitance can be approximated by a parallel plate capacitor with curved surfaces, and therefore the tangential fringing fields can be neglected. In the simulation, we found that the gate capacitance increases by only 2.6% when the substrate dielectric constant increases from 3.9 to 22, which implies that the substrate (nitride TEM membrane) stray capacitance is not important. The axial fringing fields may affect the gate capacitance when the channel is very short (or S/D electrodes are very close). However, the change of capacitance per unit length due to axial fringing fields is less than 3% even when the channel length shrinks down to 15 nm (Figure 2.9, supporting information). Therefore, our comprehensive simulations ensure a wide applicability of Equation (2.2). To compare different devices whose diameters vary in the range of 30 – 50 nm, we normalize our experimental transconductances with respect to the gate capacitance of a virtual reference device (40nm in diameter, top gate device with 10nm HfO<sub>2</sub> gate dielectric) using the formula:

$$g_m^{normalized} = g_m \frac{C_G^{ref}}{C_G}$$

(2.3)

where  $C_G^{ref} = C_G^{\Omega}(h = 20nm, r = 20nm)$ , and  $C_G = C_G^{\Omega}(h, r)$ .

Figure 2.5 (a) Double log plot of normalized maximum transconductance as a function of channel length. Each black small circle represents measured transconductance from an individual experimental device, and large red diamonds represent extracted transconductance from simulated devices with different channel lengths. The dashed line describes the trend predicted by the long channel approximation from (Equation (2.1)). (b) Axial band diagram near the surface of a 100 nm channel device in the on-state. The valence band profile can be divided into 3 regions (from left to right): source SB region, channel region, and drain SB region. Both of the SB regions are highlighted by dashed boxes. The voltage drop across the channel region is denoted as  $V_{\rm deff}$  (c) Comparison of the valence band profile at the source/drain SB region (i.e., the part of the device highlighted by dashed boxes in (b)) of devices with 100nm and 1 $\mu$ m channel lengths during on-state operation ( $V_{\rm deff}$  -1  $V_{\rm deff}$  in the 100nm channel length device is a small fraction of the total source/drain bias.

To validate the on-state characteristic trend observed in the experimental devices, we

have performed device simulations for the same experimental channel length range using Silvaco Atlas software package. The transport model for Schottky contact is essential in this simulation, and it implements the model described in ref. [40], which treats the tunneling current through the Schottky barrier as carrier generation and recombination process in the barrier region, and the model can be extended for sub-50 nm channels. Diffusion-drift model, along with energy balance equations, which account for hot carrier effects, were solved for both carriers. The mobility model is taken after ref. [41], which accounts for velocity saturation at high parallel fields (along channel length), and surface roughness scattering as a function of perpendicular field, which was calibrated against the Si universal mobility curve. We assumed a gate-all-around geometry for gate capacitance in the simulation, and  $C_G = \frac{2\pi\varepsilon_r\varepsilon_0}{\ln(1+h/r)}$  was used in Equation.(2.3) to normalize simulated devices to the reference device. The normalized maximum transconductance  $g_m^{normalized}$  as a function of channel length for both measured and simulated devices is plotted in Figure 2.5a. Each black circle represents a  $g_m^{normalized}$  for a single experimental device (in total 64 devices with different channel lengths), and the larger red diamonds are data points extracted from simulations. The trend predicted by the long channel approximation (Equation (2.1)) using  $C_G^{ref} = C_G^{\Omega}(h = 20nm, r = 20nm)$ , is represented by a dashed line in Figure 2.5a. Both of the experimental and simulated devices show deviation from the predicted enhancement of  $g_m^{normalized}$  according to Equation (1), with shorter channel lengths. While this deviation is expected in conventional short channel FET devices (e.g. due to S/D series resistance), it manifests itself in a different and more significant physical behavior in SB-FETs.

To explain the origin of maximum transconductance deviation from long channel approximation in SB-FETs, we plot the energy band-edge diagrams along the NW axis in Figure 2.5b, extracted near the surface of devices under on-state bias. In Figure 2.5b, we divide the NW along the axial direction into 3 regions: source SB region, channel region, drain SB region, where the valence band part of the S/D SB regions are highlighted by dashed boxes. For these undoped NWs, the channel region is the part of the device where the potential drops almost linearly (in a band diagram, potential drop manifests in the way of band energy increase). This potential drop is defined as effective voltage drop (denoted as V<sub>d,eff</sub>) across the channel, which maintains the channel field to drive carriers but is reduced to only a fraction of total S/D bias V<sub>ds</sub>. Quantitatively, we plot in Figure 2.5c the valence band energy profile for devices with different channel lengths (1 µm and 100 nm) along the first 20 nm from both S/D SB regions at  $V_{ds}$ = -1 V and  $V_g$ = -4 V (on-state). The  $V_{d,eff}$  for  $L_G$ =1  $\mu m$ and 100 nm are 0.48 V and 0.06 V, respectively, with the latter only 6% of the applied V<sub>ds</sub>. In contrast to the channel region, the majority of V<sub>ds</sub> drops across the source SB for the short channel device, which implies that the contact resistance at the source is dominant in such a device. This is due to the fact that the source Schottky junction is under reverse bias. In the 100 nm channel device, only a small portion of the voltage drops across the channel while most of the voltage drops in the S/D SB region, which leads to a thinner SB compared to that of the 1 µm channel device.

Existence of both source and drain SBs poses a limiting factor on the on-current gain from scaled SB FETs. While the thickness of the SB might be controlled by doping, our