## **UC Irvine**

## **UC Irvine Electronic Theses and Dissertations**

## **Title**

Analytical State Depended Timing Model for Voltage Scaled Circuits & Delay-Based Physically Unclonable Function

## **Permalink**

https://escholarship.org/uc/item/5ff3s3qs

#### **Author**

Pirbadian, Aras

## **Publication Date**

2016

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA IRVINE

Analytical State Depended Timing Model for Voltage Scaled Circuits &

Low Overhead Delay-Based Physically Unclonable Function

## **DISSERTATION**

submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

In Electrical Engineering and Computer Science

By

Aras Pirbadian

Dissertation Committee: Associate Professor: Ahmed M. Eltawil, Chair Professor Fadi J. Kurdahi Associate Professor Rainer Doemer

## Dedicated to:

My beloved wife, Sara

And to my beloved parents Parisima and Ali

## TABLE OF CONTENTS

## **Contents**

| LIST OF FIGURES                               | V    |

|-----------------------------------------------|------|

| LIST OF TABLES                                | VI   |

| ACKNOWLEDGEMENT                               | VII  |

| CURRICULUM VITAE                              | VIII |

| ABSTRACT OF THE DISSERTATION                  |      |

| PART I: TIMING MODEL FOR VOLTAGE SCALED CIRCU |      |

|                                               |      |

| CHAPTER I: OVERVIEW                           | 1    |

| I. Introduction                               |      |

| II. MANUFACTURING PROCESS VARIATION           |      |

| III. VOLTAGE AND FREQUENCY SCALING            |      |

| IV. TIMING ANALYSIS                           |      |

| A. Static Timing Analysis (STA)               |      |

| B. Statistical Static Timing Analysis (SSTA)  |      |

| C. Dynamic Timing Analysis (DTA)              |      |

| A. Advanced On-Chip Variation (AOCV)          |      |

| B. Statistical On-Chip Variation (SOCV)       |      |

| •                                             |      |

| CHAPTER II: ANALYTICAL STATE DEPENDENT TIMING |      |

|                                               | 19   |

| I. Introduction                               | 19   |

| II. Methodology                               | 20   |

| A. State Dependent Model                      |      |

| B. Gate Look-Up Tables                        |      |

| C. Intermediate Transitions                   |      |

| D. Error Injection Model                      |      |

| III. MODEL VERIFICATION                       |      |

| IV. CASE STUDY 2P-IDFT                        |      |

| V. Assumptions and Limitations                |      |

| CHAPTER III: IMPLEMENTATION                   | 33   |

| I. Introduction                               | 33   |

| II. RIPPLE CARRY VS CARRY SELECT ADDER        | 33   |

| III SIMULATION SETUP                          | 38   |

| CHAPTER IV: RESULTS                   | 40              |

|---------------------------------------|-----------------|

|                                       | N               |

| CHAPTER V: CONCLUSION                 |                 |

|                                       |                 |

|                                       |                 |

| CHAPTER VI: OVERVIEW                  | ANCE COMPARISON |

|                                       |                 |

|                                       |                 |

|                                       |                 |

| •                                     |                 |

|                                       |                 |

|                                       |                 |

|                                       |                 |

|                                       |                 |

| · · · · · · · · · · · · · · · · · · · |                 |

| •                                     |                 |

|                                       |                 |

|                                       |                 |

| H. Scan PUF                           | 57              |

| CHAPTER VII: IMPLEMENTATION           | ON 58           |

| I. Introduction                       | 58              |

|                                       |                 |

|                                       |                 |

| IV. CHALLENGE-RESPONSE SPACE          | 61              |

| CHAPTER VIII: EVALUATION              |                 |

| I. SIMULATION SETUP                   | 63              |

|                                       |                 |

| •                                     |                 |

| · · · · · · · · · · · · · · · · · · · |                 |

| •                                     |                 |

| CHAPTER IX: CONCLUSION                | 73              |

| BIBLIOGRAPHY                          | 74              |

| APPENDIX A                            | 79              |

## LIST OF FIGURES

| Figure 1. Classification of variation parameters [4].                                        | 3      |

|----------------------------------------------------------------------------------------------|--------|

| Figure 2. Inter-die and intra-die process variation [4].                                     | 4      |

| Figure 3 (a) Block based vs (b) Path Based SSTA [21]                                         | 13     |

| Figure 4. Cascaded logic gates                                                               | 24     |

| Figure 5. Timing diagram of logic nets                                                       | 24     |

| Figure 6. 11 to 00 transitions for the XOR circuit.                                          | 24     |

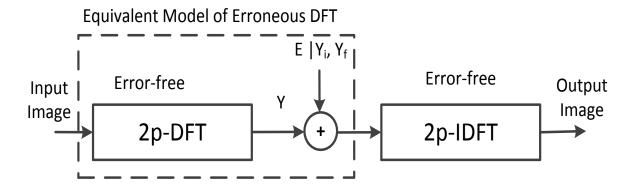

| Figure 7. Equivalent model of erroneous voltage scaled circuit                               | 27     |

| Figure 8. A sample of the error density function                                             | 28     |

| Figure 9. Hspice/Monte Carlo simulation results (bars) versus proposed statistical model (   | Solid  |

| lines) for (A) XOR circuit on top and (B) adder on bottom                                    | 29     |

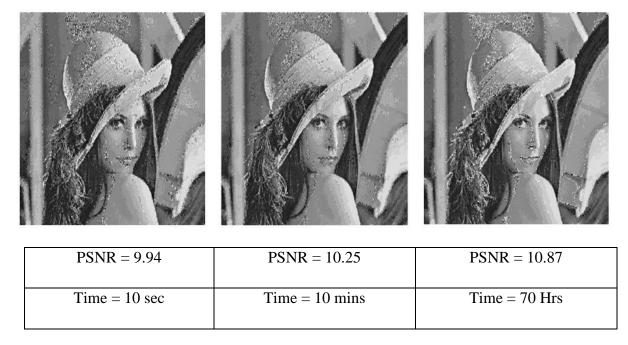

| Figure 12. Picture quality, PSNR, and timing of HSPICE simulation on right, Monte Carlo i    | in the |

| middle and the proposed method on left                                                       | 31     |

| Figure 10. Block diagram of the case study                                                   | 31     |

| Figure 11. Two point DFT block diagram                                                       |        |

| Figure 13. Proposed reconfigurable design methodology.                                       |        |

| Figure 14. State dependent error model for reconfigurable 2p-DFT in an image compre          |        |

| technique                                                                                    |        |

| Figure 15. Images with different features                                                    |        |

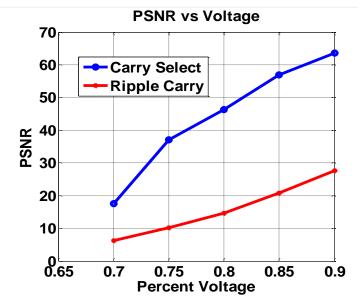

| Figure 16. PSNR versus supply voltage for different adders of image at Figure 15(A)          |        |

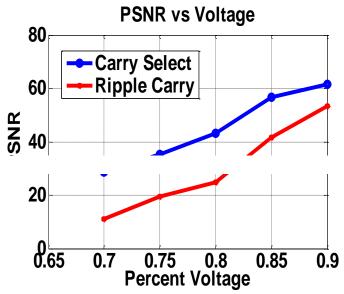

| Figure 17. PSNR versus supply voltage for different adders of image at Figure 15(B)          |        |

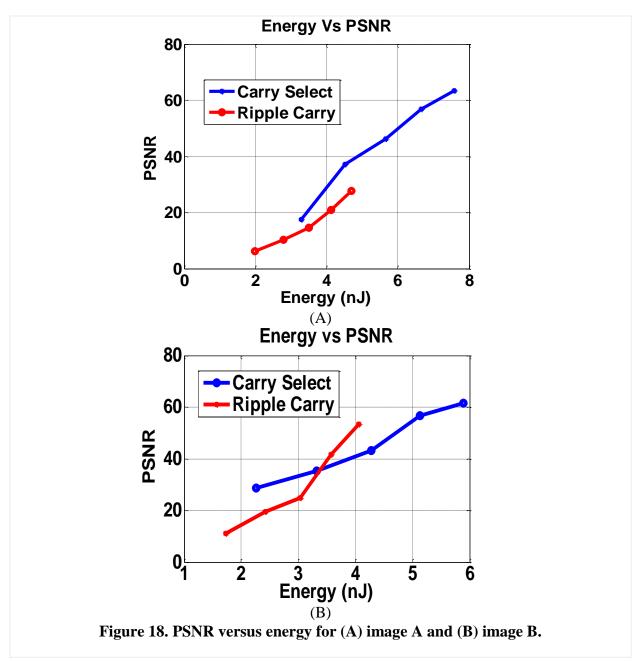

| Figure 18. PSNR versus energy for (A) image A and (B) image B                                |        |

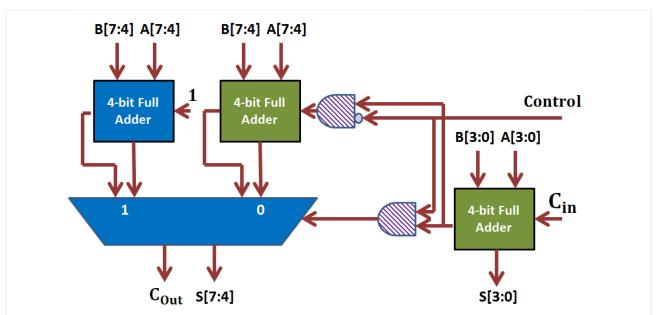

| Figure 19. Reconfigurable carry select-ripple carry adder. The green (light) color represent |        |

| circuitry for the ripple carry adder. Blue (dark) color represents the extra hardware need   |        |

| configure a carry select adder and purple (shaded) color is the controlling gates            |        |

| Figure 20. The circuitry for the controller                                                  |        |

| Figure 21. PSNR versus energy for the DFT with reconfigurable adder for image with h         | iigher |

| frequency of changes                                                                         |        |

| Figure 22. Inter and intra distributions and determination of the detection threshold [49]   |        |

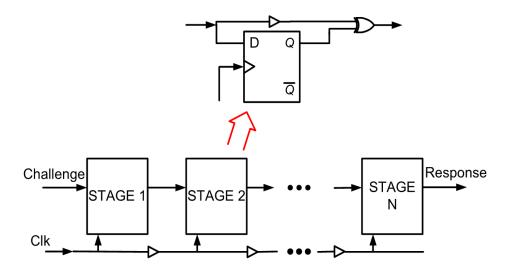

| Figure 23. The concept of the Arbiter PUF [49]                                               |        |

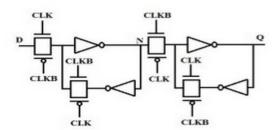

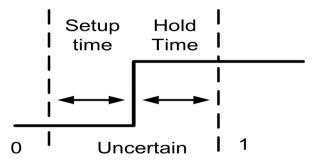

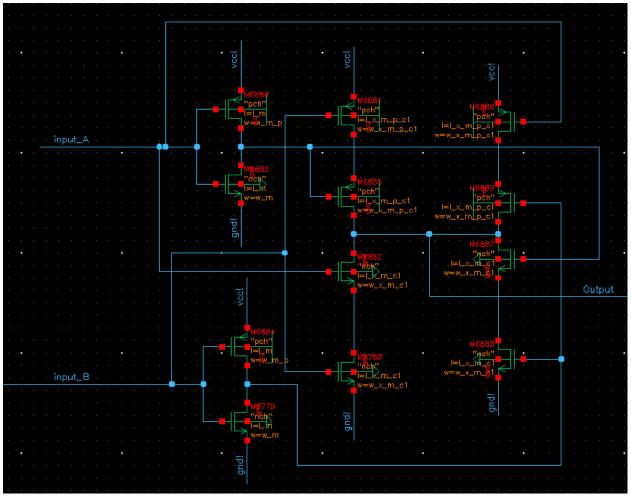

| Figure 24. Schematic of a DFF                                                                |        |

| Figure 25. Uncertain region with respect to the clock                                        |        |

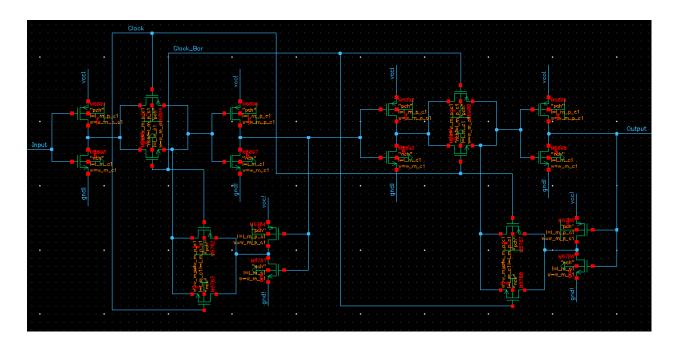

| Figure 26. Schematic of the proposed PUF                                                     |        |

| Figure 27. D-Flip-Flop implementation used                                                   |        |

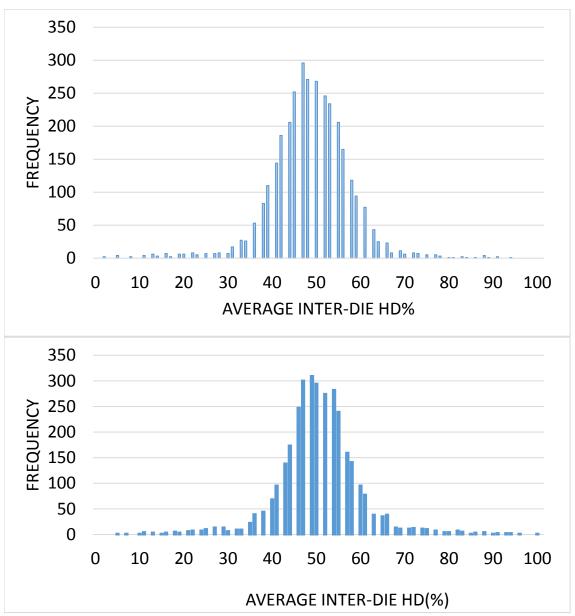

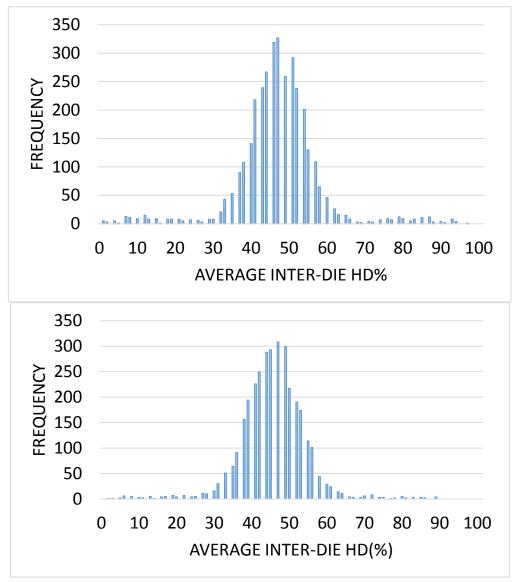

| Figure 28. Schematic of the XOR used                                                         |        |

| Figure 29. Average Inter-Die Hamming Distance for different challenges                       |        |

| Figure 30. Average Inter-Die Hamming Distance for different challenges                       |        |

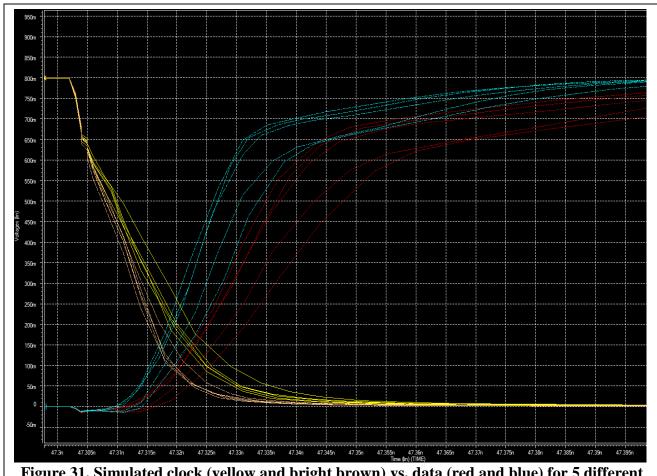

| Figure 31. Simulated clock (yellow and bright brown) vs. data (red and blue) for 5 different | chips  |

|                                                                                              | 71     |

## LIST OF TABLES

| Table 1. Predictions of the international Roadmap for Semiconductors [1] | 5  |

|--------------------------------------------------------------------------|----|

| Table 2. Run time comparison                                             | 30 |

| Table 3. Mean, Standard Deviation and Percent of ones of responses       | 70 |

## **ACKNOWLEDGEMENT**

Firs and for most, I would like to express my appreciation and praise to my PhD advisor professor Ahmed Eltawil for his continuous patience, understanding and support during my graduate studies. My sincere thanks must also go to my co-advisor professor Fadi Kurdahi for his invaluable guidance and thoughtfulness during those years.

I am also most grateful to my best friend and wife Sara, for her encouragement, dedication and love during my PhD years. Her tremendous support, confidence and inspiration throughout my PhD was in the end what made this dissertation possible.

Also, my beloved parents, Parisima and Ali receive my deepest gratitude for their many years of unconditional trust, encouragement, endless patience, sacrifice and love. There is no way to express how much their support meant to me.

Finally, I can never forget my parents-in-law Roshanak and Ali, who I am always grateful for their generous inspiration and their firm believe in me.

## **CURRICULUM VITAE**

| 2007 | B.S in Electrical and Computer Engineering,<br>Isfahan University of Technology          |

|------|------------------------------------------------------------------------------------------|

| 2009 | M.S in Electrical and Computer Engineering,<br>California State University Los Angeles   |

| 2016 | Ph.D. in Electrical Engineering and Computer Science,<br>University of California Irvine |

## FIELD OF STUDY

Wireless Systems and Circuits

## **PUBLICATIONS**

A. Pirbadian, M. S. Khairy, A. M. Eltawil and F. J. Kurdahi, "State dependent statistical timing model for voltage scaled circuits," *2014 IEEE International Symposium on Circuits and Systems (ISCAS)*, Melbourne VIC, 2014, pp. 1432-1435.

doi: 10.1109/ISCAS.2014.6865414

## ABSTRACT OF THE DISSERTATION

Analytical State Depended Timing Model for Voltage Scaled Circuits &

Low Overhead Delay-Based Physically Unclonable Function

By

#### Aras Pirbadian

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Irvine, 2016

Associate Professor Ahmed Eltawil, Chair

With the continued scaling of chip manufacturing technologies, the significance of process variation in performance of the systems is increasing. Specifically, process variation results in growing voltage and frequency overhead margins required to ensure error free operation of circuits. However, the traditional practice of overdesigning the systems to cover process variation is no longer an efficient design methodology in an age with high demands for processing power and limited energy supplies. In this dissertation, a novel analytical model is proposed to predict the required margin accurately in the early stages of design space exploration. The model can be used to optimize the system overhead in error free calculations or to release the bound by full correctness in error tolerant parts of systems and optimize the energy vs. performance trade-off. Additionally, this model also considers the statistics of the inputs of the circuit as compared to other existing efforts enabling it to achieve close predictions of full circuit simulation results in a short time. This model is finally used in an adaptive carry select/ripple carry adder configuration to demonstrate the potential achievable power savings.

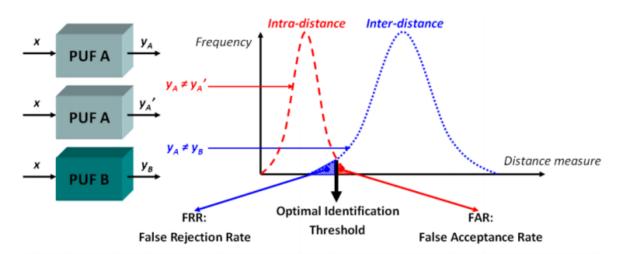

Growing variation in newer technology nodes is not always a negative side effect. The increased inherent randomness in the process manufacturing technology can be utilized to develop unique physically unclonable functions (PUFs). These functions are irreproducible hardware-based authenticating systems, which do not require memory-based storage. A low overhead delay-based PUF using the variation of the silicon manufacturing is also proposed in the second part of this work. The proposed PUF uses a simple and efficient structure to convert the randomness of the manufacturing process into random responses to fixed challenges in identically designed circuits.

## **PART I: Timing Model for Voltage Scaled Circuits**

**CHAPTER I: OVERVIEW**

#### I. Introduction

With the shrinkage of the geometries in the newer silicon manufacturing technologies, the effects of process variation gain prominence in affecting the system and circuit's performance and reliability. To overcome the challenge of making reliable systems in the smaller technology nodes, overdesigned and conservative systems have been used, which despite being reliable are not very power efficient. These designs, in general, add redundancy to the systems in a variety of forms to ensure correctness in all the calculating and storing components. However, there are many applications that by nature or by design tolerate some degree of error. As an example, wireless systems face the errors caused by the effects of their communicating channel. They are also designed to recover from such errors using a forward error correction (FEC) component. Even human eyes are largely insensitive to the pixel size color variations in an image when the frequency of such variation is small. Consequently, a system transmitting data over the air or an image compression or decompression algorithm does not necessarily need to be an error-free system as long as the inaccuracies do not exceed acceptable limits. In this work, a fast mathematical methodology has been proposed to quickly model the timing alterations resulted from the variations on the underlying circuitry of a system. Using this model, it is possible to predict the potential timing violation errors and to adjust the resources available to a system to achieve a more efficient system while not exceeding the desired acceptable error level.

## **II.** Manufacturing Process Variation

The attributes of transistors fabricated on a chip are typically different from designed transistors due to the variations in their manufacturing process. The transistors' performance is also a function of the physical parameters of the fabricated transistors as well as their operating environment. Recently, there is a great amount of attention and concern about the effects of variations of transistors on the yield and performance of the newer technology chips. These effects are so drastic that they have practically limited the development speed of the new technologies and have been indicated as major challenges for the semiconductor industry [1].

The environment of transistors can also have unexpected changes and its variations are categorized into supply voltage and temperature variation. The main source of supply voltage variation is the voltage drop across the resistance of the interconnections. Typically, many consumer units across a chip share the same supply voltage and its paths. These connections can have physical alterations due to process variation and sharing them on narrower metal layers in newer technologies worsens the supply voltage fluctuations. This is because the variation in the width of the connection is a larger percent of its total width. Additionally, the supply voltage variation directly affects the propagation delays of transistors, which will be discussed further in the next section. Alternatively, the main source of temperature variation is the changes in the neighboring transistors' switching frequency and it will affect the transistor threshold voltages.

Transistors physical parameter alteration, which is a direct result of process variation on each transistor, can also be divided into systematic and non-systematic. Systematic variation signifies the deterministic portion of the process variation. This component of the variation is predicted from the relative distance of the devices as well as the location on the wafer or the patterns of the surrounding areas. This variation, which is caused by chemical mechanical

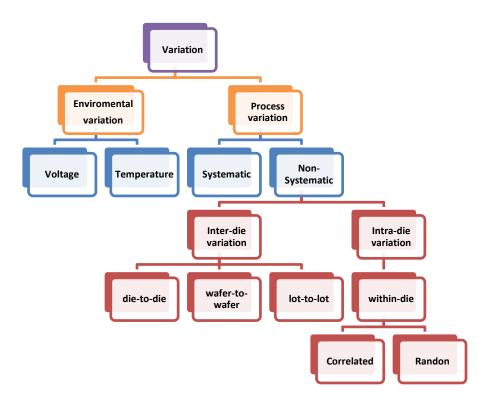

**Figure 1.** Classification of variation parameters [4].

polishing and proximity-based lithography, can be resolved by accurate modeling of the process [2] [3].

The non-systematic variation represents the unpredicted portion of the process variation and has a stochastic behavior. Smaller transistor gate sizes and increases in the number of transistors per unit area reduce the chances of manufacturing matching transistors. The limitations of the manufacturing equipment as well as other interfering mechanisms introduce these unfavorable stochastic variations into the process.

**Figure 1** illustrates different categories of variation [4].

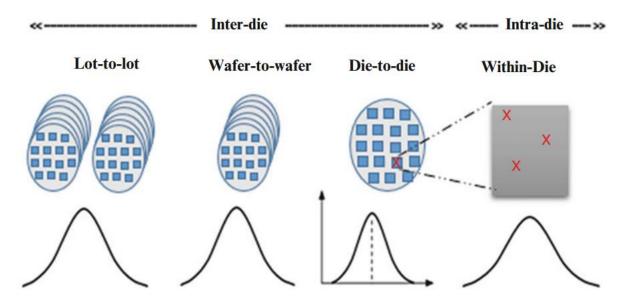

Non-systematic variation is also characterized depending on whether it is between multiple copies of the same transistor or if it is on two identically designed transistors on the same die. The first type, which is named inter-die variation, can be observed on transistors on different lots, from a wafer to the next or on multiple copies of the die on the same wafer. The key cause of inter-die

Figure 2. Inter-die and intra-die process variation [4].

variation is the technological restrictions, which result in the absence of sufficient control on the manufacturing process. The second type of non-systematic variation, which is named intra-die variation, diversifies the performance of identically designed transistors on a single chip. Despite being non-systematic, intra die variation can be correlated or random. The spatial correlation would be observed when closely spaced transistors show more similar variations than those placed far away [5] [6]. Sources of this variation such as etching, layout information, and lithographic effects can be modeled to reduce the effects of these correlations. Alternatively, the random portion of the intra-die variation does not have any meaningful spatial behavior. This variation results from random dopant variation and gate line edge roughness and is inevitable with the current manufacturing technology.

The process variation effects on transistors are observed on the physical parameters such as gate length, width, oxide thicknesses, threshold voltage, and numerous other physical parameters of a transistor [7] [8] [9]. The process variations effects can also be observed on the chip connections. Capacitance, resistance, and inductances of the interconnections in a die are also

changed due to the process variation causing differences in the propagation delays of the signals.

Table 1 summarizes the variations of different technology nodes as it was expected by the

International Technology Roadmap for Semiconductors [1].

| Year of production                                                                                       | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |

|----------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|

| Normalized mask cost from public and IDM data                                                            | 1.0  | 1.3  | 1.7  | 2.3  | 3.0  | 3.9  | 5.1  | 6.6  | 8.7  |

| % V <sub>dd</sub> variability: % variability seen in on-chip circuits (%)                                | 10   | 10   | 10   | 10   | 10   | 10   | 10   | 10   | 10   |

| % $V_{\rm th}$ variability: doping variability impact on $V_{\rm th}$ (minimum size devices, memory) (%) | 31   | 35   | 40   | 40   | 40   | 58   | 58   | 81   | 81   |

| % $V_{\text{th}}$ variability: includes all sources (%)                                                  | 33   | 37   | 42   | 42   | 42   | 58   | 58   | 81   | 81   |

| % $V_{\text{th}}$ variability: typical size logic devices, all sources (%)                               | 16   | 18   | 20   | 20   | 20   | 26   | 26   | 36   | 36   |

| % CD variability (%)                                                                                     | 12   | 12   | 12   | 12   | 12   | 12   | 12   | 12   | 12   |

| % Circuit performance variability circuit comprising gates and wires (%)                                 | 46   | 48   | 49   | 51   | 60   | 63   | 63   | 63   | 63   |

| % Circuit total power variability circuit comprising gates and wires (%)                                 | 56   | 57   | 63   | 68   | 72   | 76   | 80   | 84   | 88   |

| % Circuit leakage power variability circuit comprising gates and wires (%)                               | 124  | 143  | 186  | 229  | 255  | 281  | 287  | 294  | 331  |

These variabilities in the device level cause some unwanted effects that require significant attention in the design process. The more random the physical variation in the device parameters, the more care will need to be given to the design. One of the key parameters of the transistor that is affected by the process variation is the threshold voltage. Transistor threshold voltage has been

especially sensitive to the technology scaling because the random dopant fluctuations constitute the largest contributor of its variation and the number of dopants on newer technologies has dropped to tens of dopants. This has made transistors sensitive to the distribution and density of dopants and further spreads their performance. A change in the threshold voltage of a transistor will affect both the on and off currents. Transistors with different threshold voltages will turn on with varied currents at a fixed voltage. Since the leakage current also exponentially diverges by a varied threshold voltage, the ratio of the on to off currents of the transistors is also severely affected. A chip component that has transistors with diversified threshold voltages is also more likely to be extra sensitive to the supply voltage variations. In this case, variations in the supply voltage will cause the transistors to turn on and off with further diversified currents. The combination of these effects increases the probability of having transistors with unusual performances. Also, on a chip with a smaller technology node and multi-million transistors, a significant drop in the yield would be observed.

The most popular and the simplest form of handling the process variation is avoiding it by the use of excessive redundancy in various forms such as higher input voltage or slower operating frequencies. This method will ensure the correct performance of the circuit even in the face of variations in the transistor parameters and environment. However, it is becoming more difficult with the new technologies to disregard variation effects, and it also means the acceptance of lower yields. Therefore, such techniques would be wasteful in using resources.

Various other techniques have been proposed in the literature to model or analyze process variation and avoid low yield and performance. Specifically, three classes of techniques can be identified depending on the stage at which they have focused their effort. The first group is the set of techniques that attempts to model the statistical distributions of the circuit performance

parameters and design the circuit to meet the required constraint. Techniques such as statistical static timing analysis (SSTA) and on-chip variation (OCV) fit into this category [10] [11]. These techniques will be further discussed in greater detail in the later sections. The second category consists of the techniques that detect the performance of the circuit after manufacturing process and adopt the frequency, supply voltage, or clock skew accordingly [12][13] [14]. Finally, the last category is techniques that avoid variation by synthesizing the circuits by characterizing the delay failures caused due to variation and dynamically changing the operation condition [15]. This technique can be further extended to the techniques that relax the system-wide correctness of the calculations [16][17] [18] [19] [20] [21] [22]. Such techniques argue that there is not always a need for correctness in all the calculations. There are parts of systems that are not very sensitive to small or infrequent inaccuracies, or they can be corrected later. One of the simplest of these techniques utilizes an error tracking mechanism that measures the rate of error on a voltage scaled circuit and redoes the operation when it exceeds the limits [23].

In this work, a combination of the first and last techniques are used to model the performance of an accuracy-relaxed system in a voltage- or frequency-scaled environment in the design phase. Such a model can be utilized to design a highly efficient system that is very conservative in using the resources and, therefore, power-performance efficient. The next section will discuss the voltage and frequency scaling of systems and their effects.

## III. Voltage and Frequency Scaling

With exponentially growing appeal for processing power, increased number of portable devices, and crucial limitation of energy supply in battery operated devices, significant challenges are faced to meet the tight power per operation budget. Furthermore, the small size of many embedded systems limits the amount of acceptable heat dissipation. An increase of 15 degrees

Celsius in the temperature doubles the device failure rate by up to a factor of two [24]. This rate is even more vital in embedded devices used for medical purposes. In addition, it is estimated that information and communication technology (ICT) contributes 3% of the world's overall carbon footprint and any reduction in this figure would help to have a greener environment [25]. Also, the creation of devices with lower power consumption allows the use of smaller battery sizes, reducing the weight, area, and cost. To meet these demands, an efficient power management technique is required [26]. One solution, dynamic voltage and frequency scaling (DVFS), was initially introduced by Wiser et al. [27]. In their paper, Wiser et al., introduce a metric to measure the performance of a CPU per energy unit consumed and suggest a dynamic adjustment of the voltage and frequency. Using this metric, they show that it is possible to save up to 50% of power consumption under conservative circuit design assumptions. These are savings on top of the obvious methods of stopping the CPU in the idle loops.

The following equations show the relationship between the power consumption, supply voltage, and the frequency of operation on a transistor

$$P_{Total} = C_{avg}V_{DD}^2f + P_{Static}$$

[1]

$$P_{Static} = I_{leak} V_{DD}$$

[2]

where  $C_{avg}$  is the summation of the gate, diffusion, and wire capacitances and  $I_{leak}$  is the leakage current [26] [28]. This equation indicates that a reduction in the supply voltage or the frequency of operation can reduce power consumption. However, an increase in the frequency of the operation of a circuit will result in possible timing failures on paths that have propagation delays longer than the new clock period. Furthermore, a reduction in the supply voltage will extend the

propagation delays of logic gates and it can also result in timing violations. The following equation shows the relationship between the propagation delay time and the voltage scaling [29].

$$t_{pd} = \frac{C}{(v - v_t)^{\alpha}}$$

[3]

Here, C and  $\alpha$  are constants found by curve fitting the change of the propagation delay relative to the scaled voltage and  $v_t$  is a technology dependent constant. These equations indicate that any adjustment on the voltage or frequency of operation must be with full awareness of changes on the propagation delay and possible timing failures.

With the power consumption quadratically dependent on the supply voltage, dynamic voltage scaling (DVS) has emerged as a simpler technique used to solely adjust the supply voltage according to the necessary throughput. The basic idea behind this method is that not all parts of a system are always fully utilized. Additionally, each particular chip, depending on its wafer corner, has specific capabilities. Conventional DVS takes these differences into consideration and by maintaining a safety margin to ensure full correctness, scales the voltage of less demanded components of a system to conserve power. This margin is required to cover for changes resulting from variation and to ensure timing failures do not occur. However, with the scaling of geometries in the new technologies and higher variations on the transistors and interconnecting paths, the required margin is growing. This increased margin translates into larger voltage overhead and maintaining this safe boundary proves to be energy inefficient. A more robust approach named variation-aware DVS first proposed by [4] suggested to eliminate this bound by correctness. It is shown then that by monitoring the rate of inaccuracies caused by a dynamically-scaled voltage a system can achieve an optimized power consumption. This technique usually consists of performance manager software, which predicts the future performance needs of the system and

adjusts the supply voltages accordingly. In this method, by having multiple levels of supply voltage, for sensitive and non-sensitive operations, the power consumption is controlled dynamically.

A similar method can also be pursued solely by adjusting the frequency of operation or dynamic frequency scaling (DFS) [30]. When parts of the system are not fully utilized, reducing the rate of charge or discharge of the capacitors on the system or, in other words, its clock frequency reduces the power consumption. As an example, when the rate of access to a memory unit drops, a reduction in the clocking frequency can provide a power saving while causing no interruption to the normal operation of the system. Similar to DVS, the requirement of full correctness on all operations can be dropped in a DFS, in this case, causing the propagation delay of non-synchronized operations to be possibly longer than the scaled clock period. This will result in inaccuracies; their effects need to be considered using error-aware techniques.

The three process variation handling techniques discussed in the last section can utilize the DVFS to achieve efficient systems in smaller technology nodes. Among the three methods, modeling the performance of signals under variation effects allows the designer to have a better understanding of the circuit behavior at the design phase. Timing analysis (TA) and on-chip variation (OCV) techniques are the most widely used techniques to model the circuit behavior. The next two sections discuss different flavors of these techniques in greater detail.

## IV. Timing Analysis

Every fabricated sequential integrated circuit has a highest clock frequency under which it can operate correctly in a given environment. As the circuits become more complicated, finding this highest operating frequency at the design phase is becoming a more challenging task. Timing analysis techniques are simulation-based approximation methods to determine the expected delay

time for the output of a combinational circuit to stabilize without the need for a full circuit analysis or tracing of all paths. In other words, they are design automation algorithms that offer a faster alternative solution for timing problems in logic circuits, which can save significant redesign and rebuild time. These algorithms, which were first developed as part of the design verification of IBM 3081, find out if all the design paths meet the required timing criteria [31]. That is that the data signals arrive at synchronized components early enough to satisfy the required setup time but not too early to interrupt the previous clock cycle of the next component. As an output of the algorithm, timing analysis produces a slack time at each block, which is the difference between the latest time a signal can arrive at a certain node and the actual latest arrival time of to that node. This slack time can then be used to determine the highest possible operating frequency with the presence of variation or to change the design where needed to increase the highest clock frequency. Timing analysis can be characterized into two categories of static timing analysis (STA) and dynamic timing analysis (DTA). STA is also further extended into two categories of deterministic static timing analysis (DSTA) and statistical static timing analysis (SSTA) [32] [33]. The next sections will discuss these techniques in more details.

## A. Static Timing Analysis (STA)

Static timing analysis (STA) or deterministic STA is one of the simplest and widely adopted timing analysis algorithms, which ensures the correct operation of the fabricated chip. This algorithm validates all possible paths of a digital circuit for a timing violation. STA simplifies the calculations by the assumption of the fixed process parameters such as temperature, voltage, gate length, oxide thickness, and etc. which allows the analysis of circuits with multi-million transistors. It also overestimates the delay of the longest path and underestimates the delay of the shortest path, which guarantees that the design will operate at least as fast as predicted and

effectively addresses false path and multiple cycle path issues. Combined with the simplicity of STA and its linear increase of the runtime with the increase of the circuit size, these factors are the main reasons for its popularity [34]. However, at the nanometer scales, process variation causes the underlying deterministic assumption of the STA to be challenged while STA is unable to incorporate the process variations. In addition to this, for every process parameter the STA algorithm needs to run separately. Therefore, as the number of variability sources increases, this corner-based technique is becoming computationally expensive. Furthermore, STA generates no information to simplify the given design specifications [32]. To address these issues with the deterministic STA the statistical STA (SSTA) has been proposed. The next section will review the SSTA in greater detail.

## B. Statistical Static Timing Analysis (SSTA)

STA was an effective tool to analyze the timing of the circuits and to find the highest frequency of operation for many years. However, with the increased variation in the gate delays due to the process voltage and temperature (PVT) variations, the deterministic nature of the STA is no longer a viable assumption. To address this matter, statistical STA (SSTA) has been recently proposed [10] [35] [32]. The strength of SSTA, which is divided into two categories of parametric and Monte Carlo methods, is that it models the process variation parameters as random variables with known distribution. Unlike STA, which propagates the deterministic gate values and finds a

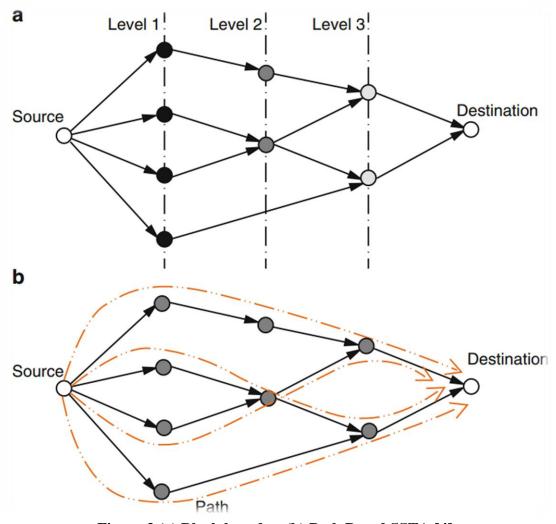

Figure 3 (a) Block based vs (b) Path Based SSTA [4]

one value delay and a fixed slack, parametric SSTA propagates the distribution of the falling and rising edges of the delays, therefore, arriving at a distribution for the last falling or rising edge of a signal and a distribution for the slack. Parametric SSTA can be divided into two categories, blockbased SSTA and path based SSTA. Figure 3 shows these two approaches. As shown in Figure **3Error! Reference source not found.** (a) in the block-based SSTA the circuit is analyzed in a hierarchical fashion. In this approach, each interconnection is taken as blocks. At each block, a statistical max operation is applied between all of the paths arriving. When all of the branches and nodes have been considered, a distribution for the max delay is achieved. The runtime in this method is linear, which makes it a fast operation capable of running on larger circuits. The other technique in the parametric SSTA is the path-based approach. In this method, a set of possibly critical paths is identified. A statistical analysis of the delay of each path is then performed by convolving the delay distributions of all the edges of each path and then taking the statistical max of all paths at the sink node. The challenge of this method is to find all the paths with some chance of being a critical path, which could result in an exponential increase in the runtime, especially in the more balanced circuits. The two approaches in the parametric SSTA differ in the precision and the computational cost. The block-based approach is a faster method while the path-based approach is more accurate [34]. It is important to note here that even though parametric SSTA is capable of finding the statistical distribution of the last falling or rising edge of the most critical path, it is not designed to report any timing distribution before the last edge. This is due to the use of the statistical max operation at each node, which only takes the distribution of the last change in the signal [10]. However, voltage and frequency over scaled circuits require knowing the signal distribution before the last edge more accurately to determine the optimum voltage or frequency operating point, which is the point that the circuit uses the minimum power with the least tolerable error rate.

Circuits that do not have an analytical description such as simulations of circuits with the existence of process variation can be processed using the Monte Carlo method. In this technique, using the probability distribution of the process variation, the samples of gate delay distribution parameters are drawn. These parameters are then used to run a simulation iteration of the Monte Carlo process for the specific circuit modeled to obtain the distribution of the delay of the circuit outputs. This method is very accurate since it is based on the actual simulation of the circuit. However, since many iterations of the simulation are required before the distribution is known, it is a very slow process. Therefore, its application is limited to small and medium size circuit [36]

## C. Dynamic Timing Analysis (DTA)

Static timing analysis (STA) checks static delays of a circuit's signals without considering the input or output vectors. In other words, STA ignores the dependence of the circuit timing to the change in the values. However, in practice, the gate delays are dependent on the input and output values or states of the circuit. Dynamic timing analysis (DTA) is a full simulation timing analysis method that increases the accuracy of the statistics by considering the effects of the input and output states in its analysis [4]. This will reduce the pessimism incorporated in the STA and is especially suitable for circuits that clock cross multiple domains. DTA uses full circuit simulation for different input vectors, which is a slow process and limits the application of DTA in many larger size circuits.

## V. On-Chip Variation (OCV) Analysis

As discussed in the previous section, statistical STA attempts to find the statistical distribution of the signal's arrival time by considering the effects of random process variations on each path and gate. Nevertheless, it ignores the deterministic variation in these components. As an example, designers typically analyze the circuit for different corners of the wafer without modeling variation effects that are observed on the same gates within a die. They have also historically used variation variables uniformly across the chip disregarding the physical information of the gate or path being modeled. However, integrators of larger and more complex chips have started examining the effect of deterministic variation on the overall performance. On larger size chips, the paths typically change layers more frequently. Since the layers are deposited independently, one layer might have a high delay characteristic while the next would be a fast one. Due to these effects, even under extreme cases, a long path would see more averaging effects than a best or worst case scenario might predict. This will make SSTA predictions more pessimistic than the real propagation delays. An alternative modeling method to the constant distributions used in STA quantifies the deterministic effects of the variation to change the distributions further across the die. The deterministic variation can be predicted from the location on the wafer or the pattern of the adjacent components and relate to the proximity effects, density effects, the relative distance of devices and gradients specific to each processing tool [37].

To model these non-random effects on-chip variations (OCV), techniques use derating factors in the static timing analysis to slow down or speed up certain gates or interconnects depending on their physical information. These derating factors are based on empirical measurements on silicon and indicate how variations are related to the device locations [38]. Different OCV techniques are under development to analyze the circuit behavior accurately.

Advanced OCV, which is the most established variation, will be discussed in the next section.

## A. Advanced On-Chip Variation (AOCV)

Advanced OCV or location-based OCV is an easy to adopt solution to close the gap between the measured and predicted timing performance of the circuits by considering the location of the component and the surrounding patterns. The basic idea is to vary the distribution of the gates and nets in the analysis depending on the neighboring parts or the loading effects, which will lead to reduced timing slacks, less timing violation, and longer timing closure cycles. AOCV determines the best derating values by finding how much a specific path in a design is affected by the process variation [37]. As an example, in a normal timing analysis method, all buffers of a buffer chain with a nominal delay of 20ns will be treated equally, and a derating factor of one will be assigned resulting in a delay of 20ns xN at stage N. However, statistical HSPICE models and Monte Carlo analysis show that the deeper timing paths have less variation. AOCV assigns different derating factors to the stages of this chain buffer modifying the distributions of delays at each stage. Another effect measured by simulations of the variations in circuits is the relation between the variation and the number of transistors. It has been observed that cells with many transistors will exhibit less variation. Therefore, their derating is reduced in AOCV. In addition to the derating of the gates and nets timing distributions, it is possible to specify derate for guard bands to model non-process related effects such as voltage drops across paths. The total derating factor is then the multiplication of both derating factors [37] [39].

The next section will cover a more complex version of OCV, which allows additional timing margin by taking more factors into consideration and is especially needed for lower technology nodes.

#### B. Statistical On-Chip Variation (SOCV)

With further reduction in gate sizes the variation increases so much that unless an accurate timing characterization is implemented, the benefit of reducing the gate length can be questioned. Despite the good efforts of AOCV to predict the timing performance of the signals with derating factors, it only accounts for the variation purely based on the stage number and the type of the gate. In other words, it disregards the dependence of variation on slews and loading of the gates. Furthermore, gates on paths with relatively more complex components will likely behave differently than on a path with simple gates. Another improvement on SOCV is the variation on the slew, especially at lower voltages. Variations in slew rates have effects both on the delay through the cell as well as the output slew rate. Moreover, SOCV captures the setup and hold time variation, which changes the statistics of the available timing slack [40].

Overall, SOCV is capable of providing a better timing distribution by capturing more effects into account and accurately processing all statistical calculations in a reasonable time. However, it is a tool primarily designed for determining the best clock frequency at lower gate sizes. In addition, it is not the purpose of its creators to capture the timing distributions before the last event of the most critical paths. Therefore, it is not the preferred tool for a voltage or frequency scaled circuit, which intentionally pushes the circuit into regions with some inaccuracies.

## CHAPTER II: ANALYTICAL STATE DEPENDENT TIMING MODEL

#### I. Introduction

Along with technological advances in shrinking silicon manufacturing dimensions, the variation of the physical parameters of the new technology chips have increased considerably. This effect is so substantial in smaller technology nodes that it has led to questioning the practicality of smaller gate sizes. In fact, the effect of variation in the performance, combined with the extra costs associated with manufacturing chips in higher technologies, has challenged further reduction of the gate sizes. Meanwhile, due to the high demand for devices consuming less energy, new techniques such as dynamic voltage and frequency scaling (DVFS) have gained significant momentum. Such techniques can be used to decrease the growing voltage or frequency margin needed to avoid variation effects and save energy. However, better use of such techniques requires accurate modeling of the distributions of the signals to optimize the energy savings. This work presents an energy reduction strategy, which rapidly and accurately models the full delay distribution of combinational circuit signals. This model can reduce the excessive margin used in the overdesigned circuits by accurately modeling the slack time between the signal and clock. However, it goes one step further compared to other similar modeling efforts in the literature with incorporating the effects of input transition into the analysis. It was shown previously in [42] that the propagation delay of gates vary according to the input state transition of logic gates. Incorporating these changes enables this analytical model to match the full circuit simulation delay distribution of signals in a small fraction of the time. This is because of the relative speed of analytically propagating the signals through the circuits compared to a Monte Carlo based simulation running the entire circuit for every sample picked. This increased speed allows the

proposed model to be used for larger circuits. There are some similar SSTA work as in [43] considering input vector to exercise false paths and the Monte Carlo approaches running the entire circuit many times. However, to the best knowledge of the author, none of these techniques and no other similar work considered the input vector state dependency for deriving timing distribution with an analytical approach.

#### II. Methodology

There have been many previous works indicating that the distribution of propagation delays of gates under voltage scaling can be estimated accurately with a Gaussian distribution [44]. The mean and variance of this distribution depends on the previous and current states of the inputs to the gate and can be obtained at the characterization phase. Consequently, for a sample gate with n inputs, there would be  $2^{2n}$  possible input transition sets, which correspond to  $2^{2n}$  sets of mean and variance for the Gaussian distribution for every voltage. Furthermore, [42] proposed a method for obtaining the propagation delays of arithmetic circuits such as adders and multipliers under voltage scaling, which shows a very close match compared to HSPICE circuit simulation while achieving a speed gain by several orders of magnitude. However, this model employs dynamic timing analysis (DTA) combined with a Monte Carlo approach, which still requires an excessively long time to obtain the timing distribution for large circuits. As an example, for an 8-bit adder, an input vector set of size 4-gigabit input samples is required to cover all possible input combinations. This is a major concern for more complex circuits. In this work, an analytical approach is proposed to rapidly obtain accurate timing propagating delays of circuits under voltage scaling and achieving a speed gain of one to two orders of magnitude as compared to [42].

#### A. State Dependent Model

A state-dependent analytical, statistical model for the propagation delay of logic circuits is proposed here. The model uses the input transition states coupled with the logic function of the gate to obtain the timing distribution of the output transitions. For an output transition from i to j ( $i \rightarrow j$ ;  $i,j \in \{0,1\}$ ),  $T_y^{i \rightarrow j}$  is defined as the timing distribution of output y for the transition from i to j. For a simple logic gate with two inputs and one output there are sixteen different input transitions (when considering current state and next state) and four possible transitions at the output. Of these four output transitions, two correspond to  $1 \rightarrow 1$  or  $0 \rightarrow 0$  changes and, therefore, result in zero propagation delay. This can be represented by a delta function such as

$$T_{\nu}^{0\to 0} = \delta(t), T_{\nu}^{1\to 1} = \delta(t)$$

[4]

The timing distribution of the other two transitions can be modeled as a sum of scaled Gaussian distributions

$$T_y^{0\to 1} = \sum_i \beta_i^{0\to 1} \times N(\mu_i, \sigma_i)$$

[5]

$$T_y^{1\to 0} = \sum_i \beta_i^{1\to 0}{}_i \times N(\mu_i, \sigma_i)$$

[6]

where N ( $\mu_i$ ,  $\sigma_i$ ) is the normal distribution with mean  $\mu$  and standard deviation  $\sigma$  of the  $i^{th}$  input transition that will change the output from 0 to 1. Note that the proposed model can be extended to assume non-Gaussian input distributions.  $\beta_i^{0\to 1}$  represents the probability of occurrence of the  $i^{th}$  input change. Using these output timing distributions, the total propagation delay distribution is the weighted sum of all four transitions, which can be represented as:

$$T_{y} = \sum_{j} \sum_{j} \alpha_{i \to j} \times T_{y}^{i \to j}$$

[7]

where  $\alpha_{i \to j}$  is the weight of the output transition  $i \to j$  which can be obtained via knowledge of the logic function of the gate, probability and number of input transitions that generate the  $i \to j$  transition at the output.

#### B. Gate Look-Up Tables

The N ( $\mu_i$ ,  $\sigma_i$ ) in the aforementioned equations is the Gaussian distribution of the propagation delay of the  $i^{th}$  input transition. This distribution will need to be known prior to use of the above equation and is gate and input transition dependent. To obtain this distribution an HSPICE simulation is setup to simulate the effects of transistor variation on the gate propagation delay distribution. In this model all transistors are assigned a threshold voltage with normal distribution variation and standard variation according to the following equation:

$$\sigma_{vth} = \frac{C}{\sqrt{W*L}}$$

[8]

and a mean that is equal to the threshold voltage in the absence of the variation [44]. L and W in the above equation are the length and width of the transistor respectively, and C is a technology-dependent constant. To obtain N ( $\mu_i$ ,  $\sigma_i$ ) for all inputs a Monte Carlo simulation is set up to characterize the distribution of delays for all  $2^{2n}$  possible input vectors with n being the number of inputs to the gate. This input vector space will consider all of the possible transitions from the previous state to the current state of the input. The simulation measures and stores the propagation delay of each run of the circuit with a given input. The mean and standard deviation of all runs with a given input transition are then extracted and used in the row number i of a look-up table

(LUT) with  $2^{2n}$  rows. Since the propagation delay of gates are voltage dependent, there would be one LUT for each voltage of each gate covering all possible input transitions for that gate. The key in this simulation is that since the LUTs are made per gate, the number of inputs and transitions is significantly smaller than the number of inputs in a circuit. Therefore, this characterization would use significantly less time compared to a circuit-level Monte Carlo simulation. Moreover, the characterization would be performed only once per implementation of the gate and circuits can be modeled using the proposed model afterward.

#### C. Intermediate Transitions

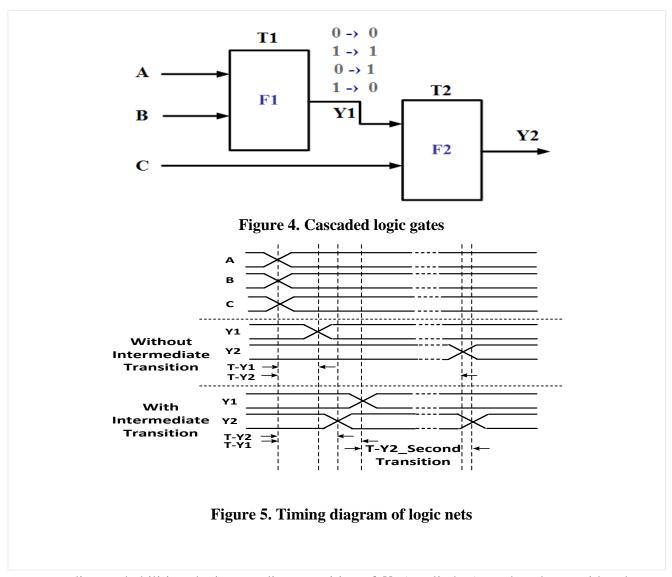

Digital logic circuits are implemented as cascaded chains of individual logic gates. The previous section explained the statistical timing distribution of a standalone logic circuit. In this section, we consider cascaded logic blocks. As an example, consider the two cascaded logic gate blocks shown in Figure 4. To determine the timing distributions of the transitions of  $Y_2$  and their

corresponding probabilities, the intermediate transition of  $Y_2$  (or glitches) needs to be considered. Generally, there are two possible scenarios for the output  $Y_2$  transition: 1)  $Y_2$  does not experience an intermediate state and the change in  $Y_2$  is solely dependent on  $Y_1$  delay and  $F_2$  gate delay, and

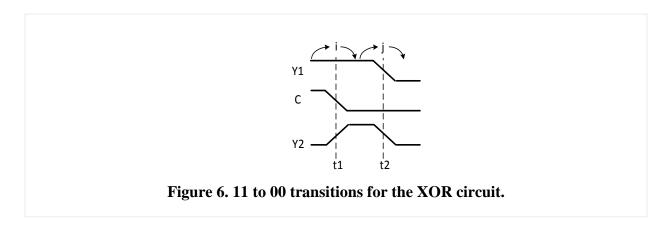

2) Y<sub>2</sub> experiences an intermediate state due to other input changes prior to settling to a final state due to a change in Y1. In the first case, as explained by the cascaded circuit in Figure 5 and its timing diagram in Figure 5, the total delay timing of the output is the addition of the timing delay of both blocks. Equivalently, the timing distribution can be expressed as the convolution of delay timing distributions of both gates. An example showing the second case, where  $Y_2$  experiences a glitch, is shown in Figure 6. The timing delay in this scenario is somehow complicated and will be explained further with an example. To better explain the timing model with intermediate states and without loss of generality, we consider an example of a two XOR circuit where the blocks of Figure 4 are replaced with XOR gates. Figure 6 shows a case where the inputs of the logic gate F2 go through a  $[(Y_1C); 11 \rightarrow 00]$  transition. In this figure,  $t_1$  is the transition time of C and  $t_2$  is the time of the  $Y_1$  transition. The transition for  $Y_2$  shown in the figure is hypothetical and assumes zero propagation delay in the  $F_2$  gate. Although the output should not change for such a transition, an intermediate state will occur. To identify the timing distribution for all possible  $1 \rightarrow 0$  transitions, including those contributed by glitches, one must account for the relative delays of the two gates. To do so, the timing distribution of F<sub>1</sub> is multiplied with a step function centered at the mean of the timing distribution of  $F_2$ . Thus the following equation is the contribution of the  $11 \rightarrow 00$ transition at  $F_2$ 's input to the output  $1 \rightarrow 0$  transition.

$$N(\mu_i, \sigma_i) * U(\mu_i) \times T_{v_1}^{1 \to 0}$$

[9]

where  $T_{y1}^{1\to 0}$  is the timing distribution of the output  $Y_1$  transition from  $1\to 0$  as calculated by (3) and \* is the convolution operation.  $U(\mu_i)$  is a step function rising at the mean of the second gate's transition and  $N(\mu_j, \sigma_j)$  is the  $F_2$ 's Gaussian timing distribution for the given inputs. In the  $11\to$

00 transition shown in the figure the values i and j represent the indices of the gate  $F_2$  input transitions of  $11 \rightarrow 10$  and  $10 \rightarrow 00$  respectively.

The total distribution for a given output transition is the addition of the timing distributions of both scenarios and can be expressed as:

$$T_{y2}^{1\to 0} = \sum_{i,j} N(\mu_{j}, \sigma_{j}) * U(\mu_{i}) \times T_{y1}^{1\to 0}$$

$$+ \sum_{i} N(\mu_{j}, \sigma_{j}) * T_{y1}^{1\to 0}$$

[10]

The previous equation can be simplified as expressed in (7).

$$T_{y2}^{1\to 0} = \sum_{i,j} T_{y1}^{1\to 0} * (1 + U(\mu_i)) \times N(\mu_j, \sigma_j)$$

[11]

Finally, the total output distribution is calculated as in equation (4). Considering that all input values for the XOR circuit are equally likely, then all possible input transitions at  $F_2$  will be equally likely and the weights would be equal to 1/16.

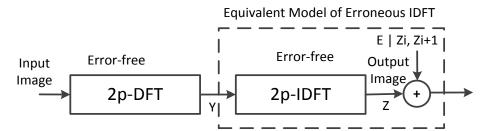

#### D. Error Injection Model

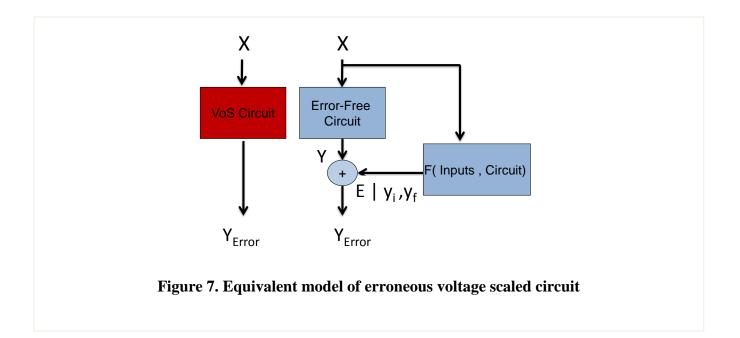

The main objective of this statistical model is to find the possible timing violations and reflect them as errors into the logic circuit model when it is voltage scaled. Figure 7 illustrates the equivalent model consisting of an error-free circuit combined with an error injector such that the final output statistics match those of the voltage-scaled circuit. The model derives the distribution of the voltage-scaled logic circuits based on the initial and final values of the input and the output bits and injects the error by flipping the output bit whenever the signal requires a longer time than that assigned.

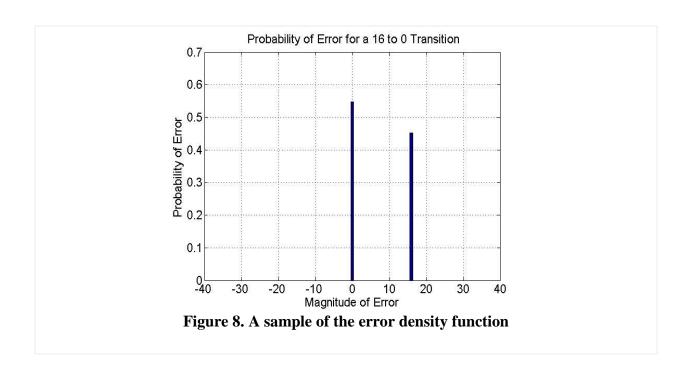

Consider as an example a 4-bit adder; the delay distribution per each output bit transition is obtained based on the proposed analytical model. The probability of error per output word is then calculated by considering all of the possible bit combinations. The errors are then injected at the output of the adder based on the probability of each magnitude of error for the given initial and final values of the output. Figure 8 shows the probability of each magnitude of error based on our model for a 16 to 0 output transition for 100ps clock frequency.

## **III.** Model Verification

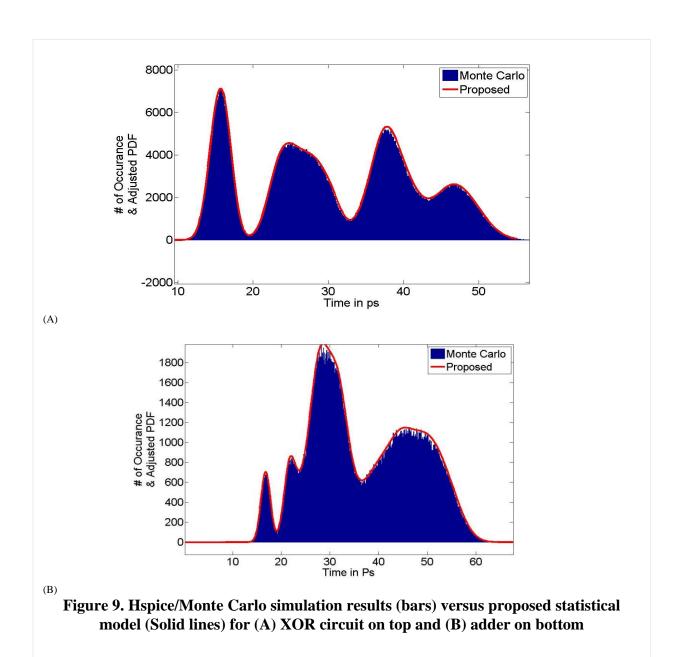

To verify the accuracy of the proposed model, different logic circuits have been tested. We illustrate a comparison between the timing distributions obtained by the Monte Carlo method used in [42] and the proposed statistical model for (a) two cascaded XOR gates and (b) a two-bit adder.

Figure 9 (A) illustrates the close match between the timing distributions of propagation delays using the analytical method displayed as a solid line versus the Monte Carlo method, displayed as histogram bars for the XOR circuits. Figure 9 (B) provides the results for the last carry bit of a two-bit adder. Again, the analytical method accurately predicts the timing distribution at the output. One of the major advantages of the analytical method is the increase in processing

speed as shown in Table 2, which illustrates a comparison of the processing time for the HSPICE simulation, Monte Carlo method suggested in [42], and our proposed method for various circuits.

# IV. Case Study 2p-IDFT

To demonstrate the proposed model at the application level, we consider an image compression application (e.g. JPEG) illustrated in Figure 11 utilizing a 2-point discrete Fourier transform (DFT). The 2-point DFT is essentially an addition and subtraction of two inputs as shown in Figure 12. A sample image is quantized, and every 2 pixels are fed into an error-free 2-point DFT. The error probabilities are then calculated based on the initial and final values of the DFT output. Error magnitudes are chosen based on the error probabilities calculated by the proposed model. These errors are added to the output of each DFT output. The error-free inverse DFT and de-quantization are generated to reconstruct the sample image.

**Table 2. Run time comparison**

|                                               | XOR       | Full Adder | 8-bit ripple adder |

|-----------------------------------------------|-----------|------------|--------------------|

| Proposed Model                                | 7 Sec     | 10 sec     | 25 sec             |

| Monte CarloError! Reference source not found. | 6 minutes | 8 minutes  | 35 minutes         |

| Spice                                         | 10 hours  | 53 hours   | 215 hours          |

Figure 11. Block diagram of the case study

Figure 12. Two point DFT block diagram

To confirm the accuracy of the proposed method, the same input picture was processed through the Monte Carlo method [42], as well as HSPICE simulations, with 32nm technology and

Figure 10. Picture quality, PSNR, and timing of HSPICE simulation on right, Monte Carlo in the middle and the proposed method on left.

1V nominal voltage [45]. All tests were performed at a fixed voltage of 70% of the nominal supply voltage (or 0.7V) and a fixed clock period of 100ps. Figure 10 shows the resulting picture quality for the three methods. To mathematically quantify the quality of the pictures, the peak signal to noise ratio (PSNR) of the output pictures was computed and is displayed below each picture. The processing time for each method is also indicated. The proposed algorithm achieves a speed gain in processing time by a factor of 60 and 25,200 as compared to Monte Carlo [42] and SPICE respectively. Alternatively, the proposed model gives a slightly more pessimistic PSNR result, which is appropriate in case the application designer needs to come up with error mitigation algorithms at the application layer (e.g. median filters). In this case, there is a higher likelihood that these mitigation algorithms will improve the image considerably when implemented.

### V. Assumptions and Limitations

The model proposed here is calculated based on the assumption that the variation in the threshold voltage of the transistors will result in the gate propagation delay distributions with Gaussian distribution. Even though the concept of the proposed model has the capability to be used for non-Gaussian distributions, the equations presented here are based on the Gaussian distribution assumption. In theory, one can further increase the accuracy of the proposed model by incorporating the non-Gaussian PDFs and propagate the analytical distributions throughout the circuit.

### **CHAPTER III: IMPLEMENTATION**

#### I. Introduction

Adders have typically been considered good representatives of combinational logic circuits to evaluate DVS effects due to their long carry chains. Many efforts can be found in the literature that characterize the performance of different types of adders under voltage scaling [46]. However, adders are traditionally simulated for a random set of data, and the input dependency of the circuits and timing delays are not considered. Therefore, the characteristics of different applications with the correlation between the input states have not been exploited. In this work, the analytical method proposed is used to demonstrate its application in optimizing the energy error performance of dynamic voltage-scaled adders. In this example, the proposed model is used to switch dynamically between a ripple carry and a carry select adder depending on the performance needed.

## II. Ripple Carry Vs Carry Select Adder

In this work, the analytical method proposed is used to exploit the input vector statistics to reconfigure a circuit based on the current operational conditions and optimize the power performance based on the block diagram shown in Figure 13. The implementation is

**Error! Reference source not found..**

Figure 13. Proposed reconfigurable design methodology.

Figure 14. State dependent error model for reconfigurable 2p-DFT in an image compression technique

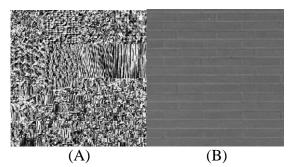

Figure 15. Images with different features

demonstrated on a reconfigurable adder that can switch between a carry-select and a ripple-carry adder within the context of a 2p-IDFT architecture. It is shown that each adder architecture has different tradeoffs that are highly dependent on the input picture statistics.

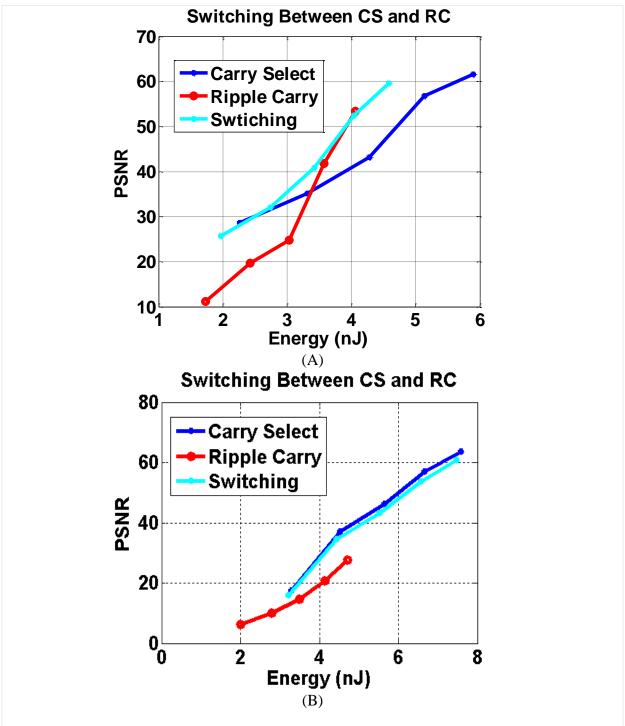

To better quantify the dependency on the input statistics a simulation system was set up, as described in Figure 14 and simulations were performed using two images with different characteristics. The test images are shown in Figure 15 where the left image (A, random noise) has frequent high variations between pixels while the right image (B, brick-wall) has less frequent changes. Considering image Figure 15 (A) with higher pixel variations, Figure 16 presents a comparison between the performances of the two adders in terms of the picture PSNR versus the amount of voltage scaling. In this figure, the carry select represents a significantly higher PSNR under all levels of voltage scaling.

However, the two curves show a smaller PSNR difference in Figure 17, which represents the same PSNR vs. voltage graph for image in Figure 15 (B) with fewer pixel variations. Comparing the two graphs, the lower frequency of variations in the inputs presented a smaller functional load to the adders. Therefore, the extra hardware in the carry select has not been utilized as efficiently as the hardware permits. This has caused the PSNRs of the image with less frequent variations to have closer values.

Figure 16. PSNR versus supply voltage for different adders of image at Figure 15(A).

Figure 17. PSNR versus supply voltage for different adders of image at Figure 15(B).

Furthermore, Figure 18 shows a comparison between the performances of the two adders versus their energy consumption for the two images shown in Figure 15. For the image depicted in Figure 15 (A) (high frequency of input variations), the carry select performs better for any given PSNR value shown in Figure 18(A). However, when considering the image in Figure 15 (B), depending on the required PSNR, the ripple carry adder presents better PSNR-performance points for higher energy consumption as shown in Figure 18(B). If the input vector is constantly changing

Figure 19. Reconfigurable carry select-ripple carry adder. The green (light) color represents the circuitry for the ripple carry adder. Blue (dark) color represents the extra hardware needed to configure a carry select adder and purple (shaded) color is the controlling gates.

(i.e. Figure 15(A), the carry select will be a better choice since it can calculate the results in a shorter time. Then again, in the case with less frequent changes in the pixel values, the extra hardware of the carry select architecture will not be utilized effectively to justify the extra static energy used. Therefore, the ripple carry will show a better PSNR for the same energy consumption.

## **III.** Simulation Setup

As a case study for the proposed model and to demonstrate its ability to save energy, a reconfigurable 2p-IDFT structure is presented where the adder that implements the 2p-IDFT is depicted in Figure 19. The control signal in the figure will determine whether the adder is configured as a ripple carry (control equal to zero) or a carry select (control equal to one). When used in ripple-carry mode, operand isolation can be applied to the input of the leftmost adder to eliminate dynamic power. The IDFT is used to perform an image decompression using an erroneous IDFT while the compression is performed with an error-free DFT as shown in Figure 14. The erroneous IDFT is modeled as an error-free IDFT and an error injector that introduces errors to the system based on the proposed timing model.

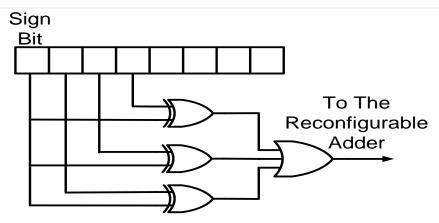

In Figure 20, the input statistics block presents a measure of the rate of change of the input vectors. This measure can be readily generated depending on the target application. For example, one way to generate this is via a simple sign bit rate of change counter. For more advanced standards, such as video compression standards, the information can be inferred from readily available measures such as motion vectors, etc. Based on the frequency of change of the input vectors, a controller could then be used to decide on the best hardware architecture for the

Figure 20. The circuitry for the controller

processing unit. In the case of the proposed reconfigurable hardware, the 2p-DFT is an addition and a subtraction of its two inputs. The subtraction of the image pixels provides a measure of change within the picture. The proposed reconfigurable method uses this measure to decide the appropriate type of adder using the circuit illustrated in Figure 20. This controller circuit uses the result of the DFT subtraction stored in a register as its input. The controller finds the one's complement of the measured value if it is negative with a series of XOR gates with one input connected to the sign bit. Then it checks whether the value is larger than half the register size with an OR gate as shown in Fig 10. This is because the carry select has two segments and the first part of the adders share the same hardware. The output of the OR gate is directly connected to the control signal of the reconfigurable adder circuit.

### **CHAPTER IV: RESULTS**

#### I. Introduction

To demonstrate an application of the proposed timing model in optimizing the power vs. performance tradeoff, a reconfigurable carry-select/ripple carry adder has been proposed. The proposed timing model is used to characterize the PSNR vs. energy performance of the two adders, and it was established that the optimum performance of the adders would be a function of their input statistics, meaning that a certain adder might be the optimum choice under certain input statistics while the other adder would excel under different input statistics. In this section, the suggested circuitry for switching between the adders is used to switch dynamically between the two adders and achieve the power optimized performance.

## **II.** Performance Comparison

The Pareto-optimal choice of an adder based on the input picture statistics can be made by switching between the two adders as the characteristics of the image change. This will stop the carry select from draining too much energy when there is no need for fast computations. Then again, when there is a higher variation in the image the extra capability of the carry select will help to increase the PSNR of the resulting image. The resulting PSNR vs. energy figures for images in Figure 15 (A) and Figure 15 (B) are shown in Figure 21 (A) and Figure 21 (B) respectively. The figures indicate that the image with less frequent changes switching between the two adders will significantly improve the energy performance of the adders. However, in the case of more random

inputs, the carry select will remain the adder with the best energy PSNR performance and the proposed switching adder will perform very closely.

Figure 21. PSNR versus energy for the DFT with reconfigurable adder for image with higher frequency of changes

## **CHAPTER V: Conclusion**

A fast and accurate analytical, statistical state-dependent model is presented to calculate the timing distributions of the output bits of voltage scaled logic circuits. The mathematical foundation for the model is explained, and its accuracy has been verified. Additionally, an additive statistical error model based on the timing violations has been obtained. Furthermore, to determine the accuracy of the model a case study of a two-point DFT employing the model was conducted, and the output picture quality in terms of PSNR has been compared to HSPICE circuit simulation.

To further demonstrate the power of the model in saving energy and the importance of the input statistics, a reconfigurable design methodology employing the statistics of the circuit input vectors is presented. Based on the proposed timing model, an input-dependent reconfigurable carry-select/ripple-carry adder is designed and demonstrated in a reconfigurable 2p- IDFT to trade-off image quality and energy consumption. The proposed architecture achieves a significantly better performance for the lower variation images and matches the performance of the optimal adder for the images with higher variations.

### I. Summary

The challenge of designing systems with optimized energy consumption in the presence of growing variation has been identified. The current practice of overdesigning systems and disregarding variation effects on the system performance or major approximations on the currently available modeling techniques has resulted in inefficient systems and overusing resources. To address this problem, the effects of variations in propagation delays of circuits have been analyzed, and a fast analytical model for the propagation delays have been proposed. The model can provide timing data for a combinational circuit based on the operating supply voltage. The model considers the input state of the circuits as an additional measure to ensure exact prediction of the propagation delays. The proposed model is verified by comparison to Monte Carlo simulation on HSPICE platform. The analytical nature of the model also assures one or two orders of magnitudes faster speed compared to similar modeling efforts. The proposed model can be used to reduce system overhead by releasing the bond by full correctness in error tolerant parts of systems and optimizing the energy vs. quality trade-off. The model is further demonstrated to accurately predict the timing violation errors of a case study voltage over scaled ripple carry adder utilized in the image compression circuitry.

Furthermore, to illustrate the energy saving possibilities with the proposed state dependent model, the model is used in a reconfigurable carry select/ripple carry adder configuration. It was shown in the implementation that such a model is capable of saving energy when it is used to switch between the adders depending on the changes in the input statistics.

The proposed state-dependent analytical model empowers circuit designers to explore different circuits and generate fast estimations for signal delays. The model can also be used to understand the propagation delay failures within the circuit and to improve the uniform utilization of the circuit and available timing. The designer can further compare different design architectures

to find the least sensitive to the variation or consider its effects even under extreme voltage or frequency-scaled conditions.

## II. Future Work

Future work on the presented research can perform the following:

- incorporate the fan out of the gates in the look-up tables used,

- consider the location of the gate within the die and change the standard deviation of the distribution used according to the relative location,

- development of other error tolerant mechanisms such as communication systems and studying the effects on system-level performance, and

- use of non-Gaussian distribution to further improve the accuracy of larger systems.

## PART II: Low Overhead Delay-Based Physically Unclonable Function

**CHAPTER VI: Overview**

#### I. Introduction

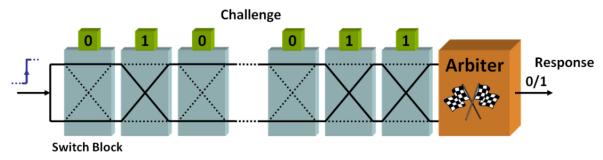

Rising incidents of counterfeiting electronic chips have posed a threat to the semiconductor industry. Counterfeit ICs typically lack the performance and material quality but are sold as genuine and could result in serious reliability issues as well as reputation or revenue loss. Additionally, security has emerged as a significant parameter in IC design and designers are required to consider the possibility of reverse engineering, counterfeiting, and tampering attacks. The current best countermeasure when verification is possible is to verify the authenticity by producing a number of secret keys only known to the verifier and the genuine party. The key is then encrypted and placed into nonvolatile EEPROM or SRAM with a supplying battery. These secret keys securely authenticate the parties communicating. However, these approaches have proved to be costly due to the design area used. Also, manufacturing a tamper evident memory to preserve such a key is a challenge and will have a high power consumption. This power is drained to keep the data and to provide mechanisms to detect and prevent attacks. Moreover, such systems are vulnerable to a potential communication intercepting attack. Physical unclonable functions (PUFs) have recently emerged as an innovative measure to address this issue by providing a vector space of the keys and mapped responses through the use of an unclonable chip. PUFs map the random variations in silicon manufacturing technology from device parameters such as channel length and threshold voltage to circuit level randomness. In these PUFs, a repeatable key can be generated from the random digital response of the PUF circuit to a challenge bit stream without it ever being stored into any memory. In this work a simple, efficient and low overhead delay-based

PUF is presented. This PUF is based on the random characteristics of the setup and hold time violation of FFs, which fluctuate with variations in the fabrication process. Use of this randomness in multiple stages will ensure a key response vector space that is diverse enough to be unpredictable and it is unique to the specific chip used.

### **II.** Physically Unclonable Function (PUF)