### **UC San Diego**

#### **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Improved Physical Design and Signoff Methodologies for Better Integrated Circuit Design Quality

#### **Permalink**

https://escholarship.org/uc/item/59z0584c

#### **Author**

Li, Jiajia

#### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Improved Physical Design and Signoff Methodologies for Better Integrated Circuit Design Quality

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Jiajia Li

#### Committee in charge:

Professor Andrew B. Kahng, Chair Professor Chung-Kuan Cheng Professor Rajesh Gupta Professor Patrick Mercier Professor Tajana Rosing Professor Steven Swanson

Copyright

Jiajia Li, 2017

All rights reserved.

| The dissertation of Jiajia Li is approved, and it is accepta | ıble |

|--------------------------------------------------------------|------|

| in quality and form for publication on microfilm and el      | lec- |

| tronically:                                                  |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

|                                                              |      |

| Chi                                                          | air  |

University of California, San Diego

2017

#### DEDICATION

I dedicate this thesis to my loving parents. Without their encouragement and support this thesis would not have been finished.

#### TABLE OF CONTENTS

| Signature Page  | e       |                                                                          | ii  |

|-----------------|---------|--------------------------------------------------------------------------|-----|

| Dedication      |         |                                                                          | iv  |

| Table of Conte  | ents .  |                                                                          | v   |

| List of Figures | s       |                                                                          | vii |

| List of Tables  |         |                                                                          | χV  |

| Acknowledgm     | nents . |                                                                          | xvi |

| Vita            |         |                                                                          | xix |

| Abstract of the | e Diss  | ertation                                                                 | xxi |

| Chapter 1       |         | duction                                                                  | 1   |

|                 | 1.1     | Slowdown of Density Scaling and Need for Design-Based Equivalent Scaling | 1   |

|                 | 1.2     | Challenges in Physical Design and Signoff                                | 3   |

|                 | 1.2     | 1.2.1 Complex Operating Conditions and Corner Explosion                  | 2   |

|                 |         | 1.2.2 Demand for Low-Power Designs                                       | -   |

|                 |         | 1.2.3 Growing Design Margins                                             | ć   |

|                 | 1.3     | This Thesis                                                              | 6   |

| Chapter 2       | Mult    | ti-Mode Multi-Corner Optimization                                        | 10  |

|                 | 2.1     | Optimization of Overdrive Signoff in High-Performance and                |     |

|                 |         | Low-Power ICs                                                            | 11  |

|                 |         | 2.1.1 Dominance of Modes                                                 | 13  |

|                 |         | 2.1.2 Problem Formulation                                                | 15  |

|                 |         | 2.1.3 Efficient Exploration of Design Space                              | 16  |

|                 |         | 2.1.4 Methodology                                                        | 19  |

|                 |         | 2.1.5 Experimental Results                                               | 22  |

|                 |         | 2.1.6 Conclusion                                                         | 24  |

|                 | 2.2     | A Global-Local Optimization Framework for Simultaneous                   |     |

|                 |         | Multi-Mode Multi-Corner Clock Skew Variation Reduction                   | 27  |

|                 |         | 2.2.1 Related Work                                                       | 28  |

|                 |         | 2.2.2 Problem Formulation                                                | 29  |

|                 |         | 2.2.3 Optimization Framework                                             | 30  |

|                 |         | 2.2.4 Experimental Results                                               | 39  |

|                 |         | 2.2.5 Conclusion                                                         | 44  |

|                 | 2.3     | Comprehensive Optimization of Scan Chain Timing During                   | •   |

|                 |         | Late-Stage IC Implementation                                             | 45  |

|                 |         | 2.3.1 Related Work                                                       | 48  |

|                 |         | 2.3.2 Methodology                                                        | 49  |

|           |     | 2.3.3   | Experimental Results                                        | 58  |

|-----------|-----|---------|-------------------------------------------------------------|-----|

|           |     | 2.3.4   | Conclusion                                                  | 60  |

|           | 2.4 | Ackno   | owledgments                                                 | 61  |

| Chapter 3 | Low | -Power  | Optimization                                                | 62  |

|           | 3.1 | Floorp  | olan and Placement Methodology for Improved Energy          |     |

|           |     | Reduc   | tion in Stacked Power-Domain Design                         | 63  |

|           |     | 3.1.1   | Related Work                                                | 66  |

|           |     | 3.1.2   | Methodology                                                 | 68  |

|           |     | 3.1.3   | Experimental Results                                        | 77  |

|           |     | 3.1.4   | Conclusion                                                  | 84  |

|           | 3.2 | Impro   | ved Flop Tray-Based Design Implementation for Power         |     |

|           |     | Reduc   | tion                                                        | 85  |

|           |     | 3.2.1   | Related Work                                                | 88  |

|           |     | 3.2.2   | Methodology                                                 | 90  |

|           |     | 3.2.3   | Experimental Results                                        | 101 |

|           |     | 3.2.4   | Conclusion                                                  | 105 |

|           | 3.3 | An Im   | proved Methodology for Resilient Design Implementation      | 107 |

|           |     | 3.3.1   | Related Work                                                | 110 |

|           |     | 3.3.2   | Methodology                                                 | 112 |

|           |     | 3.3.3   | Experimental Results                                        | 127 |

|           |     | 3.3.4   | Conclusion                                                  | 135 |

|           | 3.4 | Ackno   | owledgments                                                 | 137 |

| Chapter 4 | Mix | ed-Fabr | ic Optimization                                             | 138 |

| •         | 4.1 |         | n Implementation with Non-Integer Multiple-Height Cells for |     |

|           |     | _       | ved Design Quality in Advanced Nodes                        | 139 |

|           |     | 4.1.1   | Related Work                                                | 141 |

|           |     | 4.1.2   | Problem Formulation                                         | 142 |

|           |     | 4.1.3   | Methodology                                                 | 143 |

|           |     | 4.1.4   | Experimental Results                                        | 157 |

|           |     | 4.1.5   | Conclusion                                                  | 162 |

|           | 4.2 | NOLC    | ): A No-Loop, Predictive Useful Skew Methodology for        |     |

|           |     |         | ved Timing in IC Implementation                             | 164 |

|           |     | 4.2.1   | Methodology                                                 | 168 |

|           |     | 4.2.2   | Experimental Results                                        | 173 |

|           |     | 4.2.3   | Conclusion                                                  | 177 |

|           | 4.3 | Reliab  | oility-Constrained Die Stacking Order in 3DICs Under        |     |

|           |     |         | facturing Variability                                       | 179 |

|           |     | 4.3.1   | Modeling                                                    | 182 |

|           |     | 4.3.2   | Problem formulation                                         | 188 |

|           |     | 4.3.3   | Methodology                                                 | 189 |

|           |     | 4.3.4   | Experimental Results                                        | 192 |

|           |     | 4.3.5   | Conclusion                                                  | 200 |

|           | 4.4 | Impro   | ved Performance of 3DIC Implementations Through             |     |

|           |     | _       | ent Awareness of Mix-and-Match Die Stacking                 | 201 |

|              |     | 4.4.1     | Related Work                       | 203 |

|--------------|-----|-----------|------------------------------------|-----|

|              |     | 4.4.2     | Problem Formulation                | 205 |

|              |     | 4.4.3     | ILP-Based Partitioning Methodology | 205 |

|              |     | 4.4.4     | Heuristic Partitioning Methodology | 208 |

|              |     | 4.4.5     | Experimental Results               | 213 |

|              |     | 4.4.6     | Conclusion                         | 218 |

|              | 4.5 | Ackno     | wledgments                         | 219 |

| Chapter 5    | Con | clusion a | and Future Directions              | 220 |

| Bibliography |     |           |                                    | 224 |

#### LIST OF FIGURES

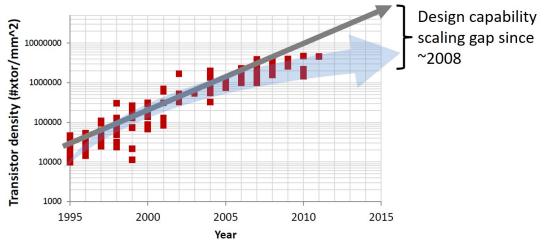

| Figure 1.1:             | Gap between "available" density scaling (gray arrow) and "realizable" density scaling in MPU products (red squares), adapted from [100]                                                                                                                                         | 2   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

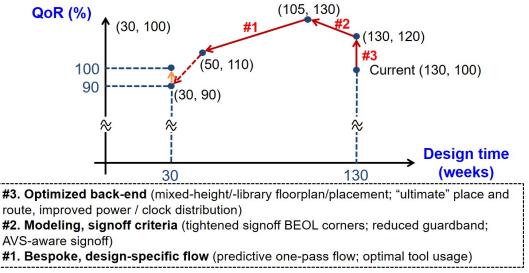

| Figure 1.2:             | Three hypothesized steps to reduce the design time of complex mixed-signal SoCs in sub-20nm technologies from 130 weeks to 30 weeks [219]                                                                                                                                       | 3   |

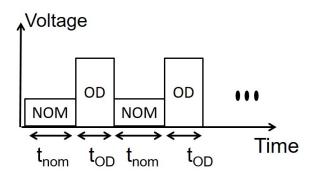

| Figure 1.3:             | Example of multi-mode operation. OD = overdrive mode. NOM = nominal mode                                                                                                                                                                                                        | 4   |

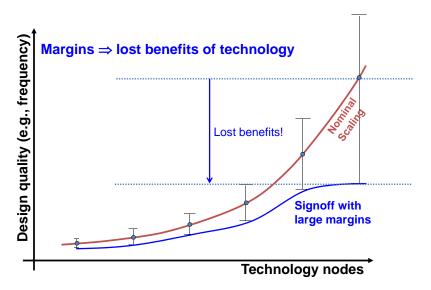

| Figure 1.4:             | Growing design margins degrade the benefits of technology scaling                                                                                                                                                                                                               | 6   |

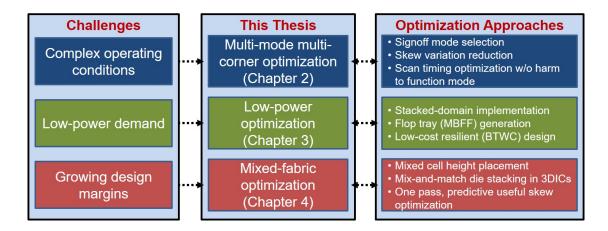

| Figure 1.5:             | Scope and organization of this thesis                                                                                                                                                                                                                                           | 7   |

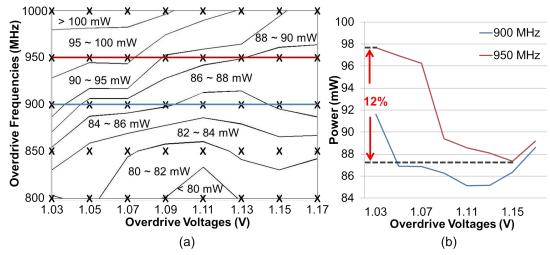

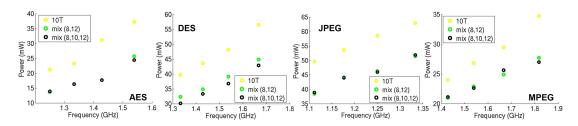

| Figure 2.1:             | $P_{avg}$ of circuits signed off at the same nominal mode (500 $MHz$ , 0.9 $V$ ) but 40 different overdrive modes. Design: <i>AES</i> [230]. Technology: foundry 65 $nm$ . Corner: FF/125° $C$ . $r = 10\%$                                                                     | 12  |

| Figure 2.2:             | Illustration of the design cone of mode $A$ (the shaded region)                                                                                                                                                                                                                 | 13  |

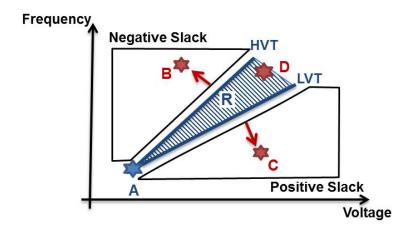

| Figure 2.3:             | Four modes exhibit equivalent dominance. The desired design space is the                                                                                                                                                                                                        |     |

| E: 2.4                  | line <b>D-A-B-C</b>                                                                                                                                                                                                                                                             | 15  |

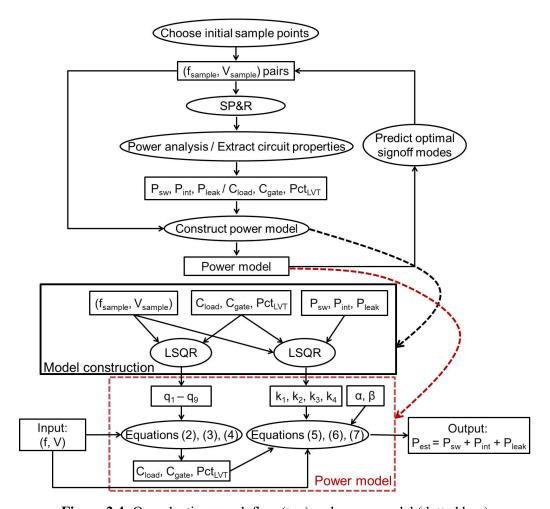

| Figure 2.4: Figure 2.5: | Our adaptive search flow (top) and power model (dotted box) (a) Projection of mode $\boldsymbol{B}$ to mode $\boldsymbol{B}'$ for circuit property modeling. (b) $\lambda(V_{nom})$ calculation, where $\lambda(V_{nom}) = \Delta V 1/\Delta V 2$ . $V_{HVT}$ and $V_{LVT}$ are | 17  |

|                         | defined by the intersections of $f_{OD}$ and the design cone                                                                                                                                                                                                                    | 20  |

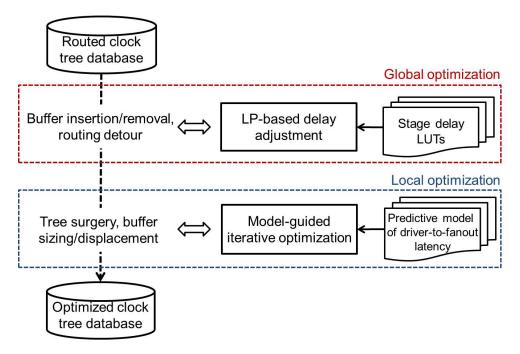

| Figure 2.6:             | Overview of our optimization framework                                                                                                                                                                                                                                          | 31  |

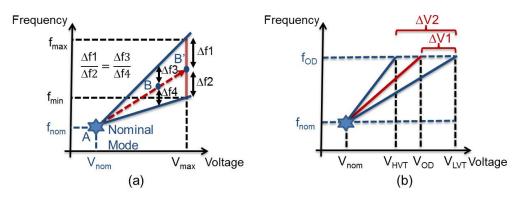

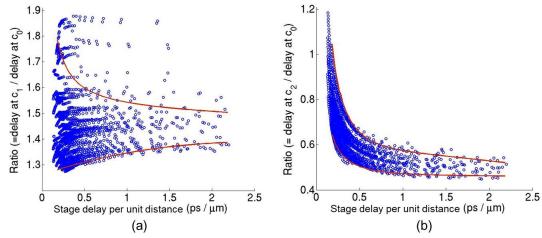

| Figure 2.7:             | Delay ratios between $(c_1, c_0)$ and $(c_2, c_0)$ , respectively. $c_0 = (SS, 0.9V, -25^{\circ}C, Cmax)$ , $c_1 = (SS, 0.75V, -25^{\circ}C, Cmax)$ and $c_2 = (FF, 1.1V, 125^{\circ}C, Cmax)$                                                                                  | 51  |

|                         | Cmin)                                                                                                                                                                                                                                                                           | 34  |

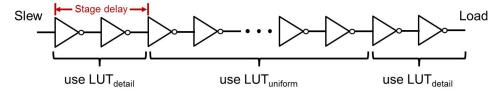

| Figure 2.8:             | $LUT_{detail}$ is characterized with various input slews and fanout loads capacitance; $LUT_{uniform}$ contains average stage delay with particular gate size                                                                                                                   | 2.5 |

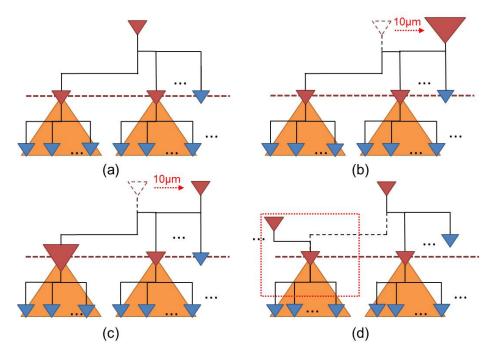

| Figure 2.9:             | and routed wirelengths between consecutive inverters Local optimization moves used in our flow. (a) Initial subtree; (b) sizing and/or displacement; (c) displacement and sizing of child node; and (d) tree                                                                    | 35  |

|                         | surgery, i.e., driver reassignment.                                                                                                                                                                                                                                             | 37  |

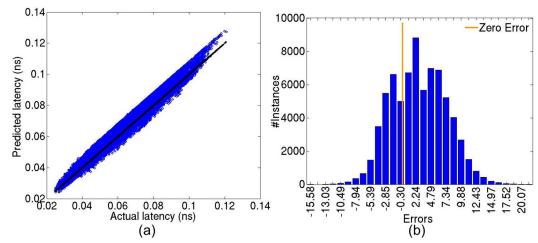

| Figure 2.10:            | Examples of (a) predicted vs. actual latencies, and (b) percentage error                                                                                                                                                                                                        | 31  |

| 1 1guic 2.10.           | histograms from our model for $c_3$ corner in Table 2.10                                                                                                                                                                                                                        | 38  |

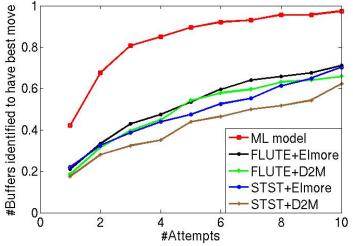

| Figure 2.11:            | Accuracy comparison between our learning-based model and analytical models. An attempt is an ECO. There are 114 buffers, and each buffer has 45                                                                                                                                 | 50  |

|                         | candidate moves. In one attempt, the learning-based model (resp. analytical                                                                                                                                                                                                     |     |

|                         | models) can identify best moves for $40\%$ (resp. up to $20\%$ ) of the buffers                                                                                                                                                                                                 | 38  |

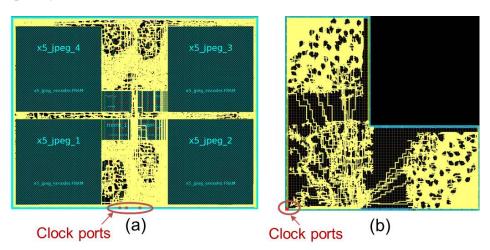

| Figure 2.12:            | Floorplans of (a) CLS1v1, and (b) CLS2v1. In yellow are routed clock nets.                                                                                                                                                                                                      | 40  |

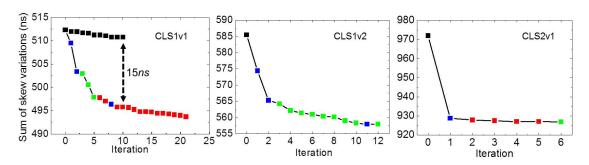

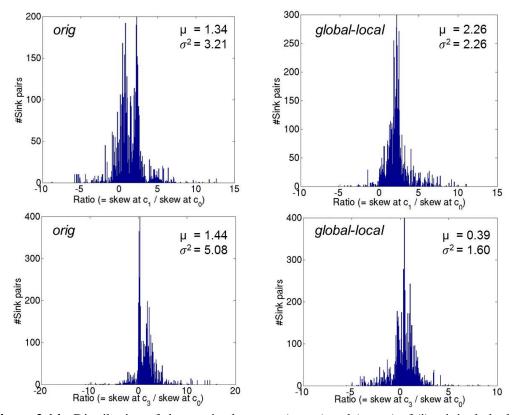

| Figure 2.13:            | Sum of skew variations reduces during the local iterative optimization. In blue are type-I moves, in red are type-II moves, and in green are type-III                                                                                                                           |     |

|                         | moves                                                                                                                                                                                                                                                                           | 43  |

| Figure 2.14:            | Distribution of skew ratios between $(c_1, c_0)$ and $(c_3, c_0)$ of (i) original clock                                                                                                                                                                                         |     |

|                         | tree, and (ii) optimized clock tree for <i>CLS1v1</i>                                                                                                                                                                                                                           | 43  |

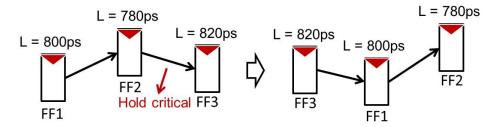

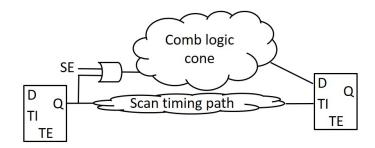

| Figure 2.15:            | Illustration of skew-aware scan ordering that removes hold violation. $L$ is                                                                                                                                                                                                    |     |

|                         | clock latency                                                                                                                                                                                                                                                                   | 46  |

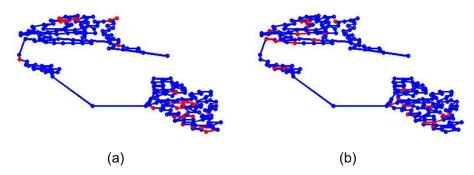

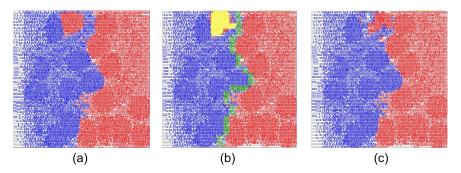

| Figure 2.16: | Hold-critical scan timing paths vary between (a) post-placement stage and          |    |

|--------------|------------------------------------------------------------------------------------|----|

|              | (b) post-routing stage. In red are the top 10% of the hold-critical paths. In      |    |

|              | blue are the non-critical paths. Design: <i>LEON3MP</i> . Technology: 28LP         | 46 |

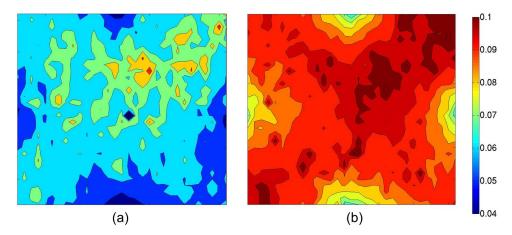

| Figure 2.17: | Dynamic voltage drop (DVD) varies between (a) post-placement stage and             |    |

| _            | (b) post-routing stage. Design: <i>LEON3MP</i> . Technology: 28LP                  | 47 |

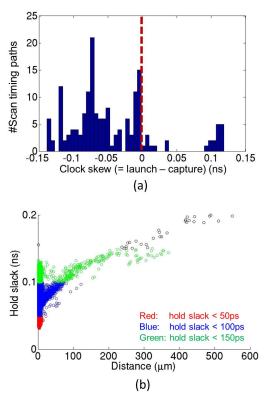

| Figure 2.18: |                                                                                    |    |

| C            | timing paths with hold buffers inserted. (b) Distances between consecutive         |    |

|              | scan cells versus hold timing slacks. Design: <i>LEON3MP</i> . Technology: 28LP.   | 51 |

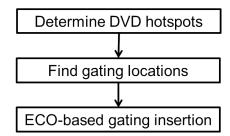

| Figure 2.19: | Optimization flow for gating insertion to optimize DVD-aware timing slacks.        | 53 |

| _            | Illustration of gating insertion with an OR gate                                   | 54 |

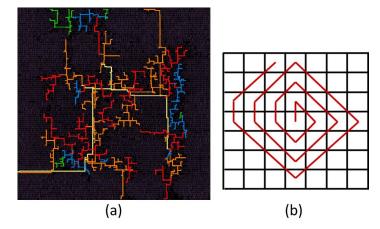

| Figure 2.21: | (a) Layout of scan enable (SE) nets. Different colors indicate different levels    |    |

| 8            | from the SE port. (b) Illustration of spiral search for SE nets in neighbor grids. | 56 |

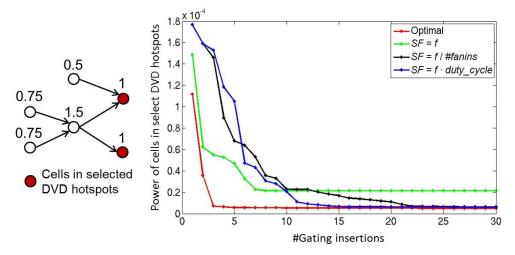

| Figure 2.22: | Performance of different sensitivity functions. Left figure shows an example       |    |

| 8            | of sensitivity function $SF = f/\#fanins$ , where each cell within DVD             |    |

|              | hotspots has one unit of power.                                                    | 57 |

|              | notified into the unit of power.                                                   | ٥, |

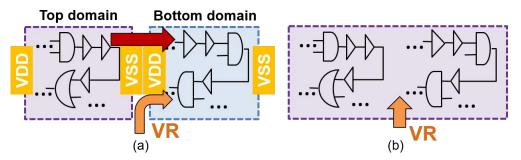

| Figure 3.1:  | Comparison between (a) stacked power-domain design, versus (b) conven-             |    |

|              | tional design. VR indicates voltage regulator. The orange arrows indicate          |    |

|              | current from voltage regulators. The red arrow indicates stacked current           | 63 |

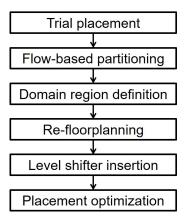

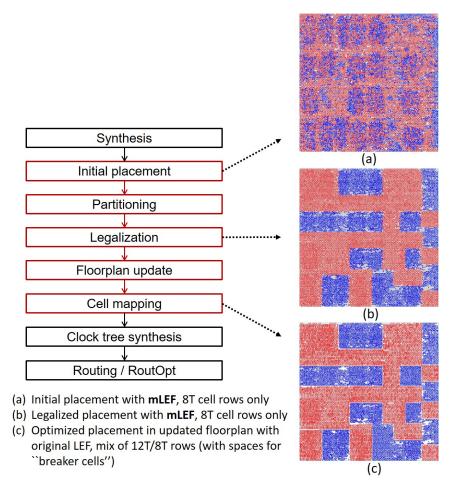

| Figure 3.2:  | Overall optimization flow                                                          | 68 |

| Figure 3.3:  | Example of optimization: (a) layout-aware partitioning, (b) region definition      |    |

|              | of power domains, and (c) level shifter insertion in the updated floorplan.        |    |

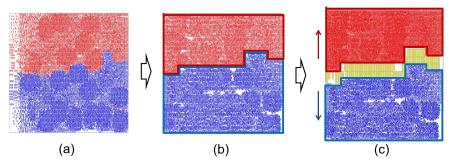

|              | Design: AES (~11K instances). Technology: 28LP                                     | 69 |

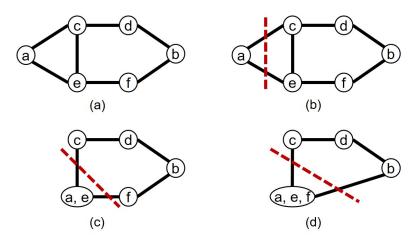

| Figure 3.4:  | Flow-based partitioning. a and b are source and sink, respectively. All            |    |

|              | vertices have the same weight. Red dotted lines indicate cuts. (a) Initial flow    |    |

|              | network. (b) First max-flow min-cut computation. (c) Clustering operation.         |    |

|              | (d) Second max-flow min-cut computation                                            | 70 |

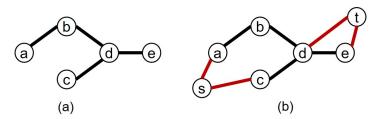

| Figure 3.5:  | (a) Choosing a / b, or c / d, or d / c as source / sink cannot lead to a balanced  |    |

|              | solution. (b) Adding a supersource (s) and a supersink (t) resolves the issue.     |    |

|              | Edges in black have unit capacities. Edges in red have infinite capacities         | 71 |

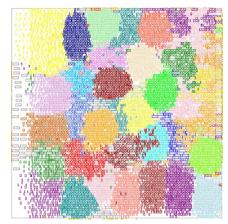

| Figure 3.6:  | HEM clustering solution. Different clusters are indicated by different col-        |    |

|              | ors. #Clusters = 200. Levels of clustering = 18. Clustering ratio at each          |    |

|              | level = 0.76. Design: AES. Technology: 28LP                                        | 72 |

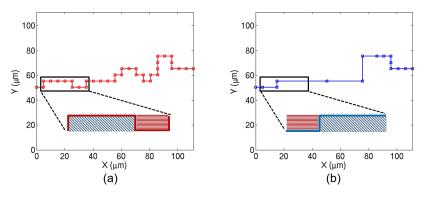

| Figure 3.7:  | FM-based grid movement. (a) Initial placement solution. (b) In yellow are          |    |

|              | outliers of the top domain. In green are neighboring grids of the top domain.      |    |

|              | (c) Post-movement placement, where each domain has a continuous region.            |    |

|              | Design: AES. Technology: 28LP                                                      | 73 |

| Figure 3.8:  | Boundary optimization. (a) Original boundary. (b) Optimized boundary               |    |

|              | with smaller length. An example of segment optimization is shown. Opti-            |    |

|              | mized segments have smaller total length while maintaining the same area           |    |

|              | in each power domain. Design: AES. Technology: 28LP                                | 75 |

| Figure 3.9:  | Example of level shifter insertion. (a) Level shifter (in blue) placement          |    |

|              | after first matching. (b) Placement blockage (in red) insertion. (c) Level         |    |

|              | shifter placement after second matching. (d) Clumping of level shifters. (e)       |    |

|              | Placement legalization applied to nearby standard cells                            | 77 |

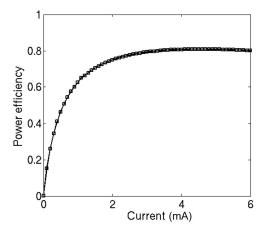

| Figure 3.10: | Power efficiency of switched-capacitor voltage regulator used in [19]              | 78 |

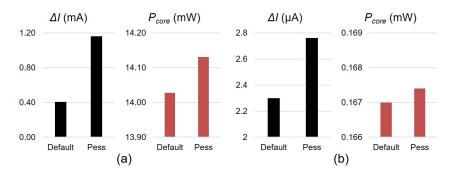

| Figure 3.11: | Impact of level shifter delay, area and power on design QoR in (a) function mode and (b) sleep mode. Design: <i>TC1</i> . Technology: 40nm                                                                                     | 80  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

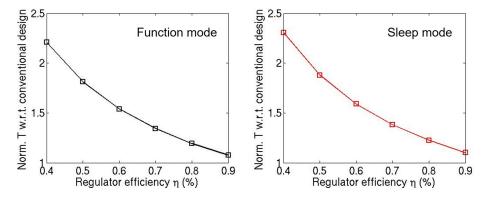

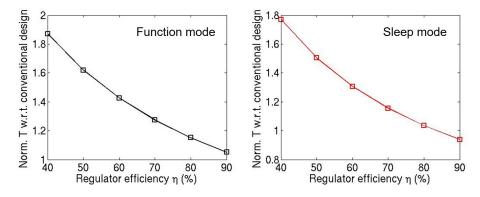

| Figure 3.12: | Impact of voltage regulator efficiency on battery lifetime improvement. De-                                                                                                                                                    |     |

|              | sign: $TC1$ . Technology: $40nm$                                                                                                                                                                                               | 81  |

| Figure 3.13: | Impact of voltage regulator efficiency on battery lifetime improvement. De-                                                                                                                                                    |     |

|              | sign: $TC2$ . Technology: $40nm$                                                                                                                                                                                               | 81  |

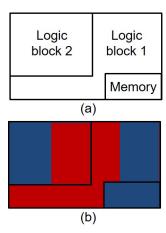

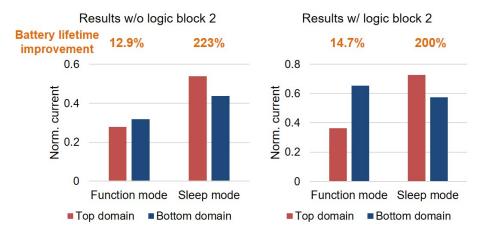

| Figure 3.14: | (a) Approximate layout of $TC2$ . (b) Approximate partitioning solution of $TC2$ (in red are top domains, in blue are bottom domains)                                                                                          | 83  |

| Figure 3.15: | Block-aware partitioning solution, evaluated in both scenarios (with and without logic block 2). Current values are normalized to the total current of the conventional design including both logic block 1 and logic block 2. |     |

|              | Battery lifetime improvements are with respect to the conventional design.                                                                                                                                                     | 84  |

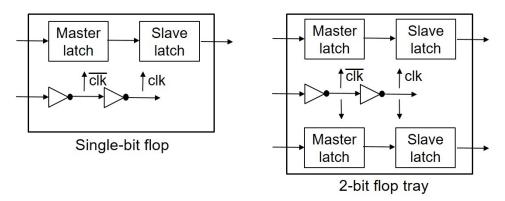

| Figure 3.16: | Two inverters for the clock signal are shared between the two flops in a 2-bit                                                                                                                                                 | ٠.  |

| 8            | flop tray.                                                                                                                                                                                                                     | 86  |

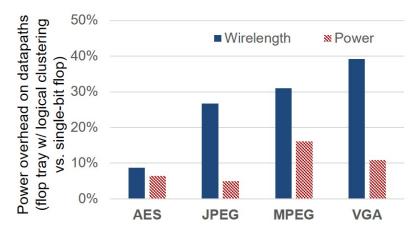

| Figure 3.17: | Wirelength and power overheads on datapaths due to flop tray-based implementations compared to implementations using only single-bit flops. Tech-                                                                              |     |

|              | nology: 28FDSOI. Designs are from <i>OpenCores</i> website [230]                                                                                                                                                               | 86  |

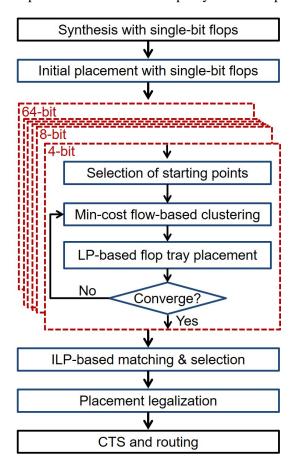

| Figure 3.18: | Overall optimization flow of flop tray generation                                                                                                                                                                              | 91  |

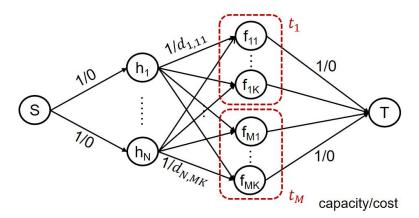

| -            | Example of min-cost flow with K-bit flop trays                                                                                                                                                                                 | 93  |

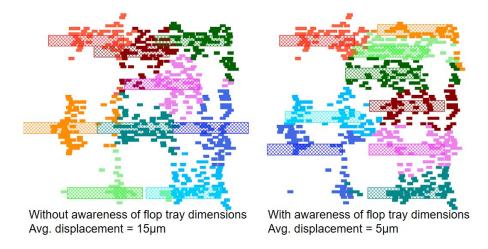

| Figure 3.20: |                                                                                                                                                                                                                                |     |

|              | aspect ratio and dimensions, and (ii) with awareness of flop tray aspect ratio                                                                                                                                                 |     |

|              | and dimensions. Design: AES (530 single-bit flops). Technology: 28FDSOI.                                                                                                                                                       | 94  |

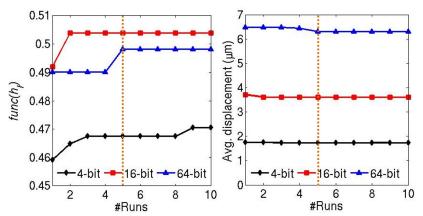

| Figure 3.21: | Best clustering solution (i.e., $func(h_l)$ (left) and displacement (right)) with multiple runs (numbers of runs are shown in the x-axis)                                                                                      | 95  |

| Figure 3.22: | Example of our ILP-based optimization.                                                                                                                                                                                         | 96  |

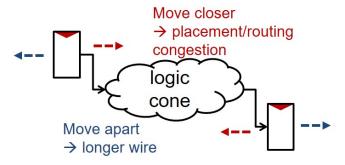

| -            | Illustration of the timing impact due to relative displacement between timing-                                                                                                                                                 |     |

|              | critical start-end flop pairs                                                                                                                                                                                                  | 99  |

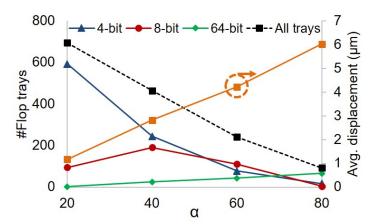

| Figure 3.24: | Number of flop trays and average displacement of flops change with differ-                                                                                                                                                     |     |

|              | ent $\alpha$ values. Design: <i>JPEG</i> . Technology: 28FDSOI                                                                                                                                                                 | 99  |

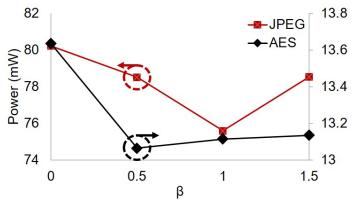

| Figure 3.25: | Power change with various $\beta$ values. Designs: <i>AES</i> , <i>JPEG</i> . Technology:                                                                                                                                      |     |

| T. 2.26      | 28FDSOI                                                                                                                                                                                                                        | 100 |

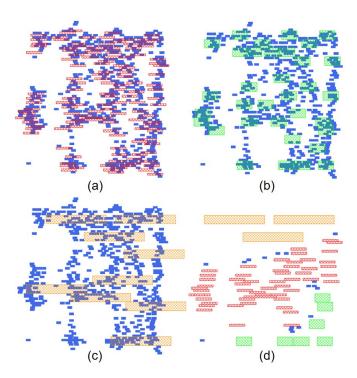

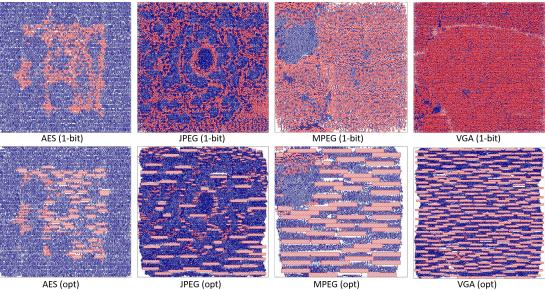

| Figure 3.26: | Layout comparison between implementations with only single-bit flops and with optimized flop trays. In the flop tray-based solutions, the candidate                                                                            |     |

|              | flop tray sizes are 4-bit, 8-bit, 16-bit, 32-bit and 64-bit                                                                                                                                                                    | 103 |

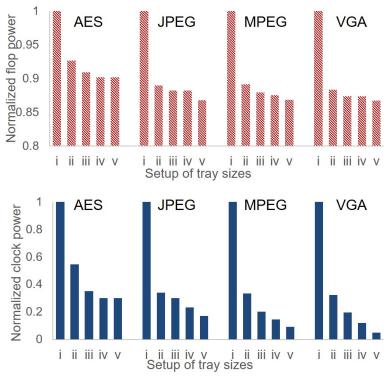

| Figure 3.27: | Flop (tray) power and clock power of designs with various flop tray sizes.                                                                                                                                                     |     |

|              | Candidate tray sizes are 4-bit, 8-bit, 16-bit, 32-bit and 64-bit                                                                                                                                                               | 104 |

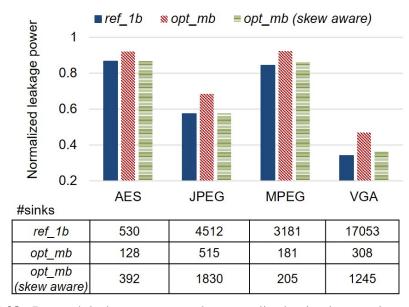

| Figure 3.28: | Datapath leakage power results, normalized to implementations with only                                                                                                                                                        |     |

|              | single-bit flops                                                                                                                                                                                                               | 105 |

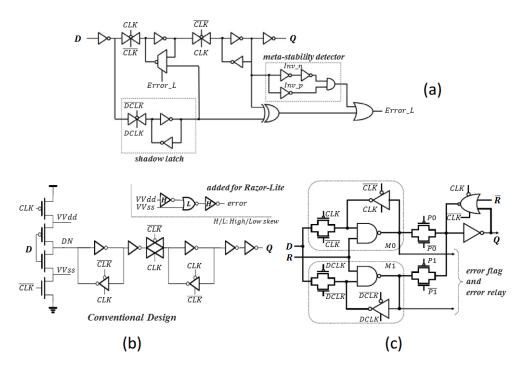

| Figure 3.29: | Structure of (a) Razor, (b) Razor-Lite, and (c) TIMBER flip-flops                                                                                                                                                              | 108 |

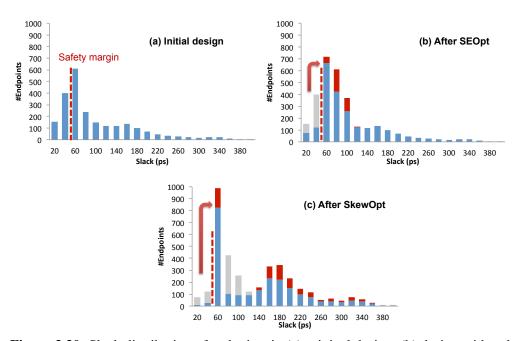

| Figure 3.30: | Slack distribution of endpoints in (a) original design; (b) design with only selective-endpoint optimization; and (c) design with combined selective-endpoint and useful skew optimization. Red dotted lines indicate required |     |

|              | safety margin. Design: FPU. Technology: 28nm FDSOI                                                                                                                                                                             | 112 |

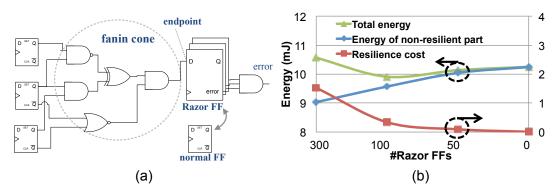

|              | sarcty margin. Design. F1 0. reciniology. 201111 FD301                                                                                                                                                                         | 114 |

| Figure 3.31: | (a) Illustration of the tradeoff between cost of resilience and cost of data path optimization. (b) With reduced number of Razor flip-flops, resilience cost decreases but power of data paths increases. Design: <i>FPU</i> (OpenSPARC                                                  |            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | T1). Technology: 28nm FDSOI                                                                                                                                                                                                                                                              | 114        |

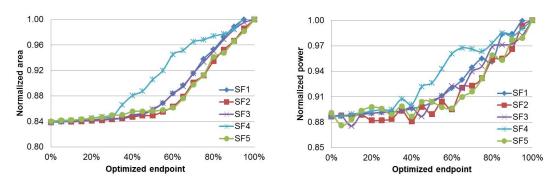

| Figure 3.32: | Cell area and total power resulting from selective-endpoint optimization with different sensitivity functions. Design: <i>FPU</i> (OpenSPARC T1). Technology: 28nm FDSOI                                                                                                                 | 116        |

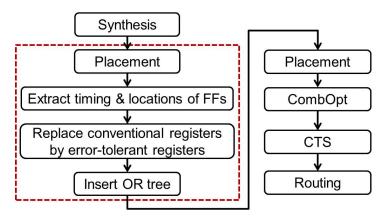

| Figure 3.33: | Implementation flow. OR tree insertion flow is indicated by the red dotted box                                                                                                                                                                                                           | 121        |

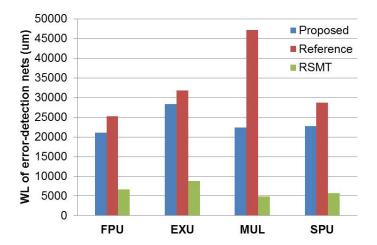

| Figure 3.34: | Our proposed OR tree insertion flow achieves an average of 29% wirelength reduction for the error-detection network, as compared to a reference flow. RSMT cost is a (loose) lower bound.                                                                                                | 121        |

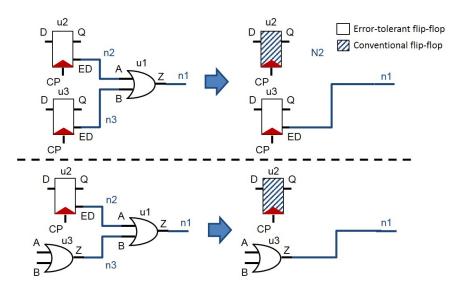

| Figure 3.35: | Replacement of an error-tolerant flip-flop with a conventional flip-flop for u2. Note that for readability, nets connected to D, Q and CP pins of flip-flops                                                                                                                             |            |

| Figure 3.36: | are not shown                                                                                                                                                                                                                                                                            | 123        |

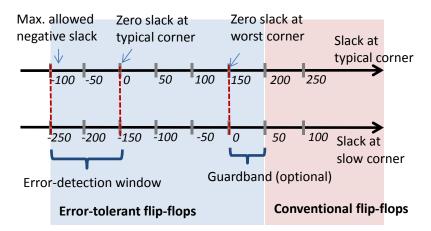

| Figure 3.37: | FDSOI                                                                                                                                                                                                                                                                                    | 124        |

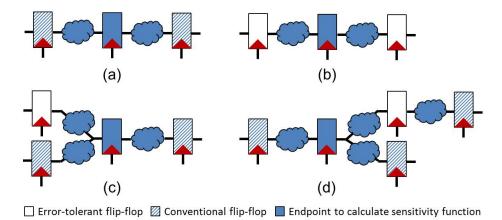

|              | flops                                                                                                                                                                                                                                                                                    | 127        |

| •            |                                                                                                                                                                                                                                                                                          | 128        |

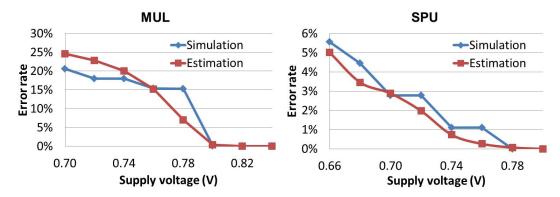

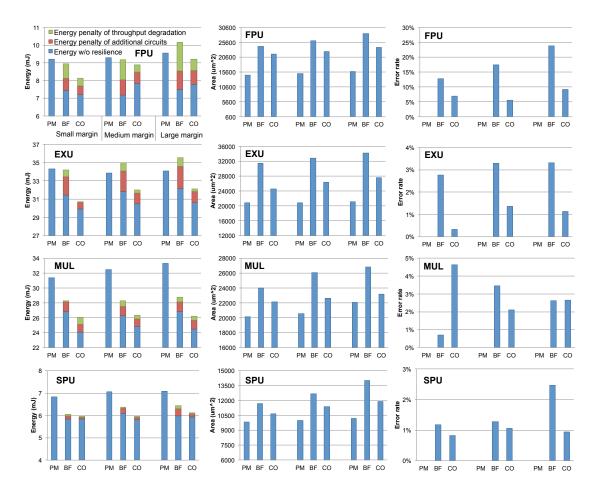

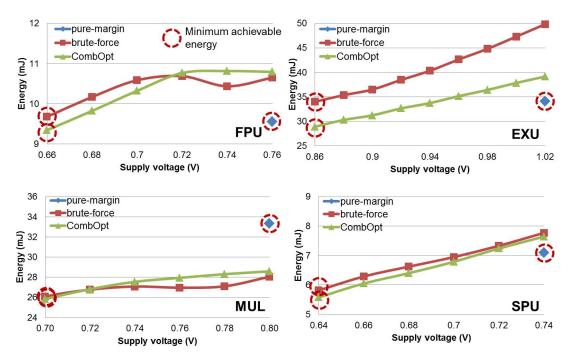

| Figure 3.39: | Energy and area results from different implementation methodologies – pure-margin (PM), brute-force (BF), and CombOpt (CO)                                                                                                                                                               | 130        |

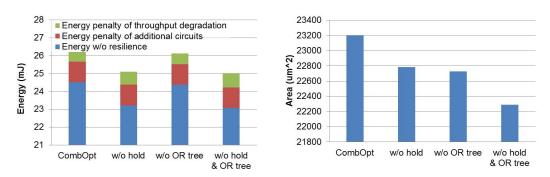

| Figure 3.40: | Impacts of hold margin and error-detection network. Design: <i>MUL</i> (OpenSPAT1). Technology: 28nm FDSOI                                                                                                                                                                               | ARC<br>132 |

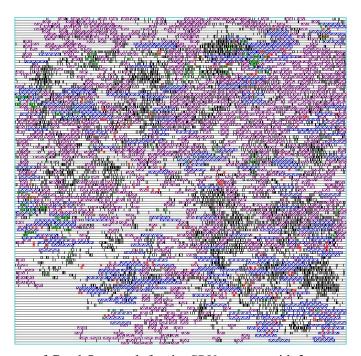

| Figure 3.41: | Layout of CombOpt result for the $SPU$ testcase with $3\sigma$ corner. Razor flip-flops are in blue; conventional flip-flops are in purple; OR gates are in red;                                                                                                                         | 120        |

| Figure 3.42: | and hold buffers are in green                                                                                                                                                                                                                                                            | 132        |

| 8            | (OpenSPARC T1). Technology: 28nm FDSOI                                                                                                                                                                                                                                                   | 134        |

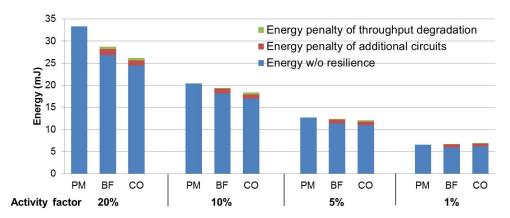

| Figure 3.43: | Energy consumption with voltage scaling, and minimum achievable energy                                                                                                                                                                                                                   |            |

|              | for each method                                                                                                                                                                                                                                                                          | 136        |

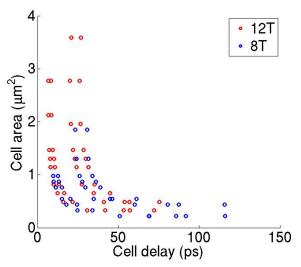

| Figure 4.1:  | Delay-area tradeoff of 8T and 12T buffers/inverters in $28nm$ LP foundry libraries. Load cap = FO4 + $20\mu m$ M3 wire                                                                                                                                                                   | 139        |

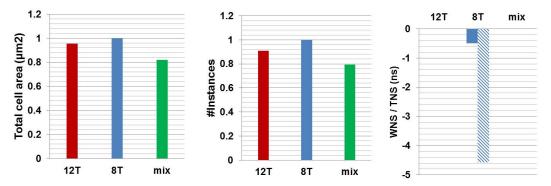

| Figure 4.2:  | Post-synthesis netlist with mixed cell heights has significant area reduction compared to 12T-only and 8T-only netlists. Technology: $28nm$ LP. Design: <i>AES</i> . Frequency: $1.5GHz$ . Corner: (SS, $0.95V$ , $125^{\circ}C$ )                                                       | 140        |

| Figure 4.3:  | Area cost of "breaker cells"                                                                                                                                                                                                                                                             | 144        |

| Figure 4.4:  | Overall flow of our optimization. In the example, the maximum cut number                                                                                                                                                                                                                 |            |

| <i>G</i>     | $(K) = 30. \dots \dots$                                                                                                                                                            | 145        |

| Figure 4.5:  | (a) Contour map of power cost function. (b) Contour map of delay cost function. (c) Partitioning solution with $\beta = 1$ , $\lambda = 0.8$ , $\eta = 0.2$ . (d) Partitioning solution with $\beta = 1$ , $\lambda = 0.7$ , $\eta = 0.3$ . (e) Partitioning solution with $\beta = 0.7$ |            |

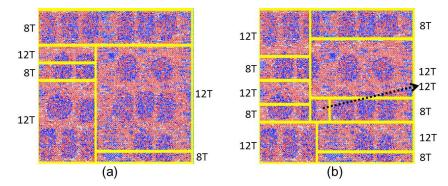

|              | 1, $\lambda = 0.6$ , $\eta = 0.4$ . Design: AES. Technology: $28nm$ LP                                                                                                                                                                                                                   | 147        |

| Figure 4.6:  | Examples of partitioning solutions for the AES testcase. In red are 12T cells                                    |      |

|--------------|------------------------------------------------------------------------------------------------------------------|------|

|              | (with <b>mLEF</b> ); and in blue are 8T cells. Yellow lines are cuts. The cell                                   |      |

|              | height of a partition is marked on its side. $\beta = 1$ , $\lambda = 0$ and $\eta = 0$ . (a) Cut                | 1.40 |

| E: 4.7       | number = 5, cost = $4818\mu m^2$ . (b) Cut number = 10, cost = $4584\mu m^2$                                     | 148  |

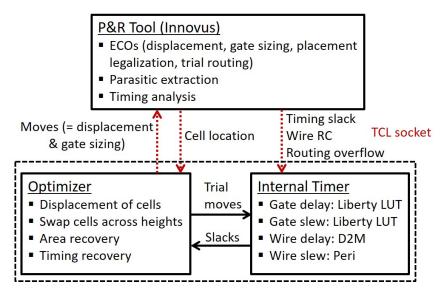

| Figure 4.7:  | Framework of our optimization.                                                                                   | 150  |

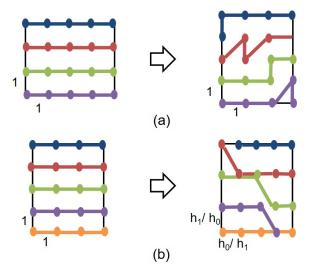

| Figure 4.8:  | Illustration of graph embedding (a) from [59], and (b) for proposed cell                                         |      |

| T: 4.0       | mapping. Vertical connections are not shown.                                                                     | 155  |

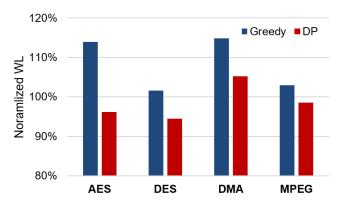

| Figure 4.9:  | Wirelength comparison between our dynamic programming-based optimiza-                                            |      |

|              | tion versus a greedy optimization in [55]. Wirelength values are normalized                                      | 1.55 |

| F: 4.10      | to the wirelength before cell mapping                                                                            | 157  |

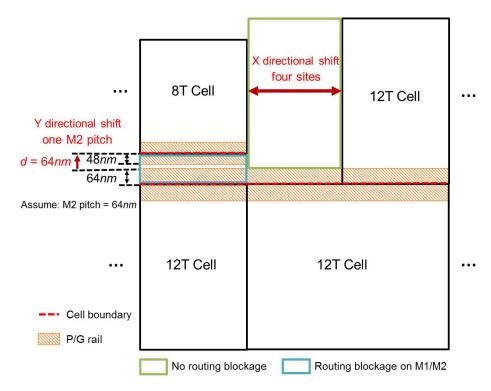

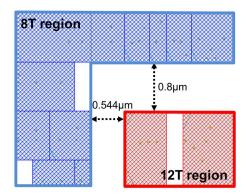

| Figure 4.10: | Inserted space on the boundaries between 12T and 8T regions to model the                                         | 150  |

| F: 4 11.     | cost of breaker cells                                                                                            | 159  |

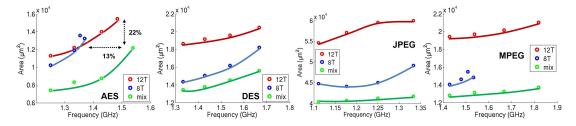

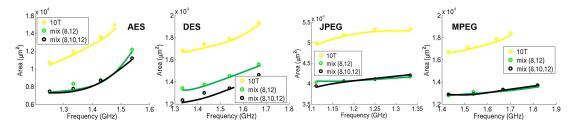

| Figure 4.11: | Pareto curves of performance-area tradeoff for implementations with 8T-                                          | 160  |

| Fig. 4.12    | only, 12T-only and mixed cells.                                                                                  | 160  |

| Figure 4.12: | Iso-performance power comparison with voltage scaling among implementations with ST only 12T only and wined only | 160  |

| Eigung 4 12. | tations with 8T-only, 12T-only and mixed cells                                                                   | 160  |

| Figure 4.13: | Pareto curves of performance-area tradeoff for implementations with 10T-only and mixed (8T and 12T) cells        | 161  |

| Figure 4.14: | Iso-performance power comparison with voltage scaling among implemen-                                            | 101  |

| 11guie 4.14. | tations with 10T-only and mixed (8T and 12T) cells                                                               | 161  |

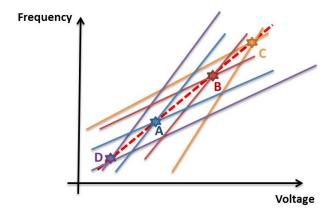

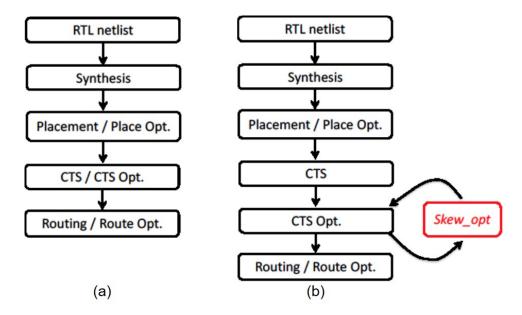

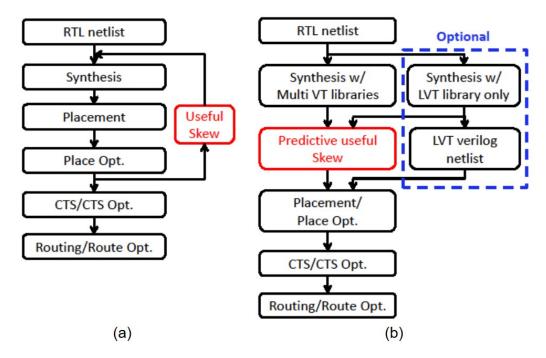

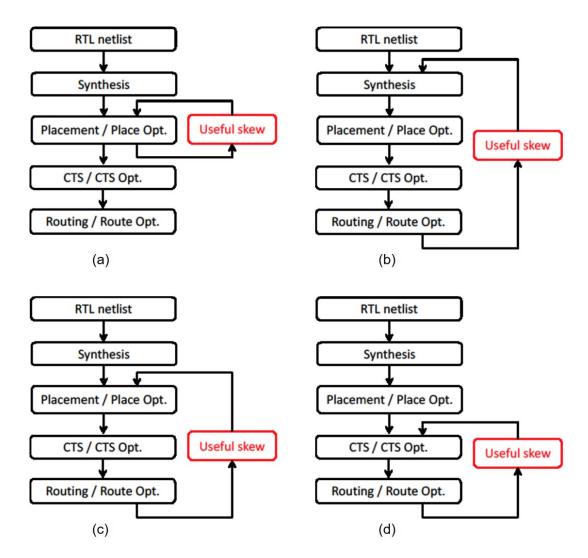

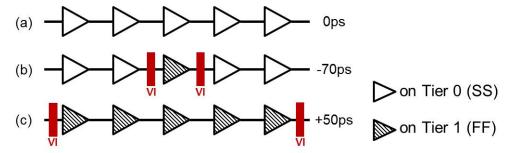

| Figure 4 15: | (a) A conventional zero-skew chip implementation flow ( <i>zero-skew flow</i> ).                                 | 101  |

| 11guic 4.13. | (b) A standard useful skew flow ( <i>typical useful skew flow</i> )                                              | 165  |

| Figure 4.16: | (a) A chip implementation flow with useful skew back-annotation (back-                                           | 103  |

| riguic 4.10. | annotation flow). (b) Our predictive NOLO ("no-loop") useful skew flow                                           |      |

|              | (prediction flow)                                                                                                | 167  |

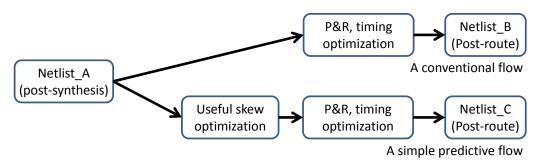

| Figure 4 17. | Overview of two basic implementation flows                                                                       | 168  |

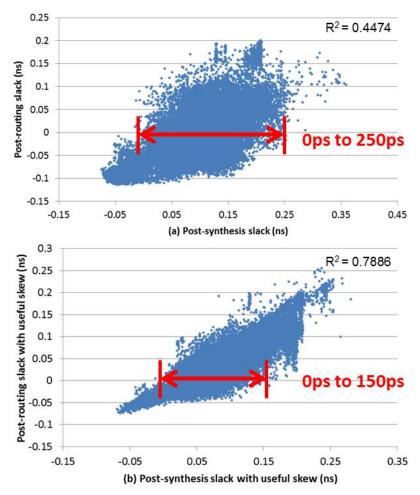

| Figure 4.17: | Timing slacks at post-synthesis versus timing slacks at post-routing stage:                                      | 100  |

| riguic i.io. | (a) without useful skew, and (b) with useful skew. Paths are extracted from                                      |      |

|              | the $MPEG$ testcase with $0.4ns$ clock period (Table 4.5)                                                        | 169  |

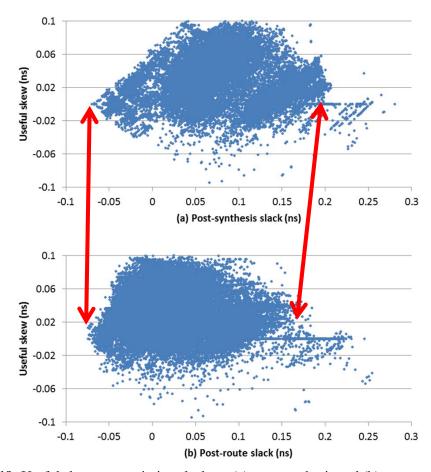

| Figure 4 19  | Useful skew versus timing slacks at (a) post-synthesis and (b) post-routing                                      | 10)  |

| rigare       | stages. Paths are extracted from the <i>MPEG</i> testcase with 0.4ns clock period                                |      |

|              | (Table 4.5)                                                                                                      | 170  |

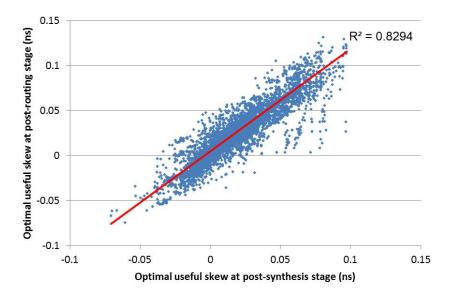

| Figure 4.20: | Optimal useful skews (obtained from MMWC) based on timing information                                            |      |

| Z.           | at post-synthesis and post-routing stages have good correlation                                                  | 171  |

| Figure 4.21: | (a) BA-I flow. (b) BA-II flow. (c) BA-III flow. (d) BA-IV flow                                                   | 175  |

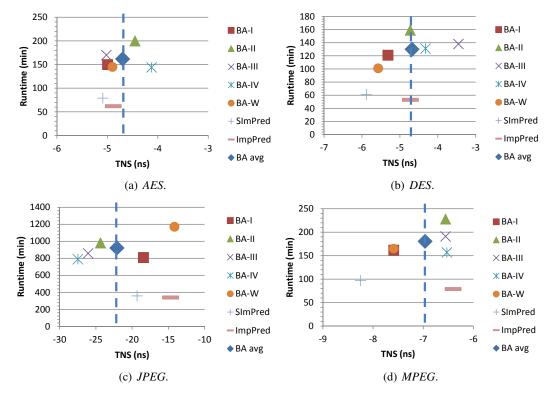

| Figure 4.22: | Comparison among useful skew flows. Our <b>ImpPred</b> flow achieves better or                                   |      |

|              | similar TNS but with 66% runtime reduction compared to back-annotation                                           |      |

|              | flows                                                                                                            | 178  |

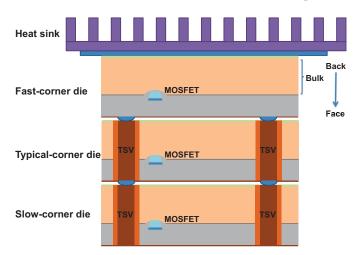

| Figure 4.23: | "STF" stack in which a slow-corner die is located on the bottom tier, a                                          |      |

|              | typical-corner die in the middle, and a fast-corner die on the top tier (adja-                                   |      |

|              | cent to the heat sink)                                                                                           | 180  |

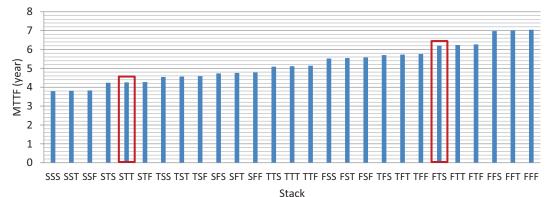

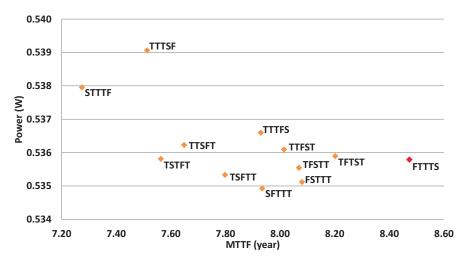

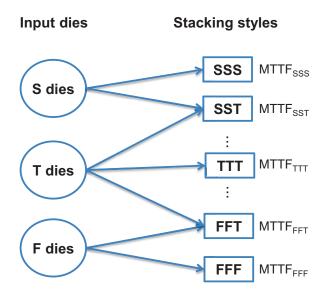

| Figure 4.24: | MTTF of 3-tier stacks with different stacking styles. Letters S, T and F                                         |      |

|              | indicate the (slow, typical, fast) process corners to which individual dies                                      |      |

|              | belong. Strings over {S, T, F} indicate stacking styles (left-to-right in the                                    |      |

|              | string corresponds to bottom-to-top in the stack)                                                                | 181  |

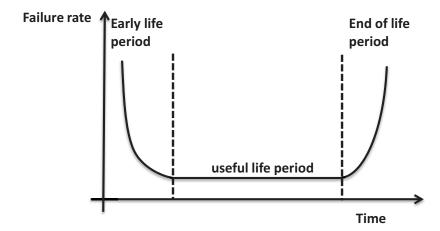

| Figure 4.25: | Reliability "bathtub curve"                                                                                      | 183  |

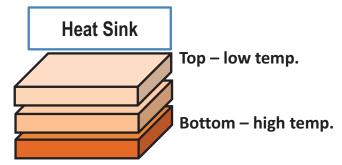

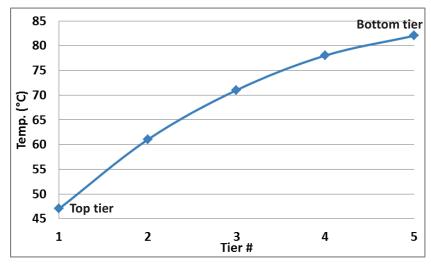

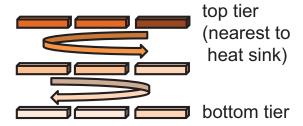

| Figure 4.26:  | Temperature gradient. The top-tier die is in direct contact with the heat sink, and thus has the lowest temperature. Due to intervening dies that block thermal conduction to the heat sink, dies in bottom tiers have higher tem- |             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 4.27:  | perature                                                                                                                                                                                                                           | 186         |

| 118010271     | ence between the peak temperatures in the bottom-tier die and the top-tier die can reach $35^{\circ}C$ .                                                                                                                           | 186         |

| Figure 4.28:  |                                                                                                                                                                                                                                    | 187         |

| Figure 4.29:  | Allowed assignments in ILP-based stacking optimization method                                                                                                                                                                      | 189         |

| Figure 4.30:  | Zig-zag method: stack dies from slow to fast, from top tiers to bottom tiers.                                                                                                                                                      | 191         |

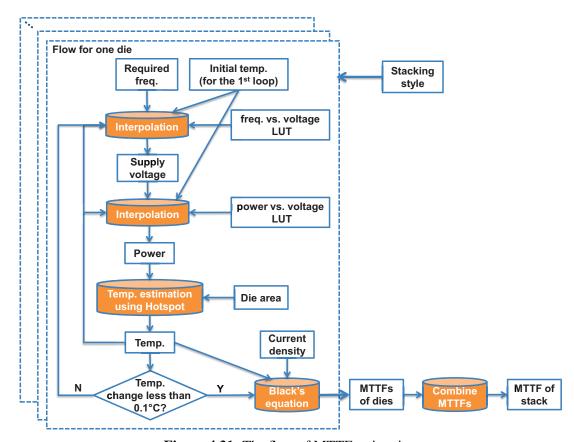

| Figure 4.31:  | The flow of MTTF estimation                                                                                                                                                                                                        | 193         |

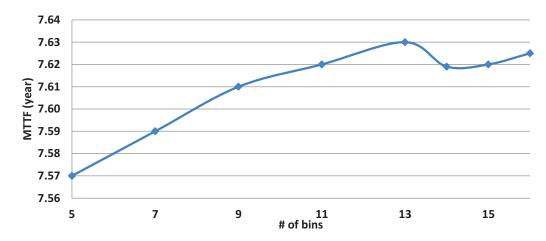

| Figure 4.32:  | As the number of process bins increases, MTTF of stacks increases. The results approach optimality when the number of bins is equal to 13, noise                                                                                   | 175         |

|               | appears after that.                                                                                                                                                                                                                | 195         |

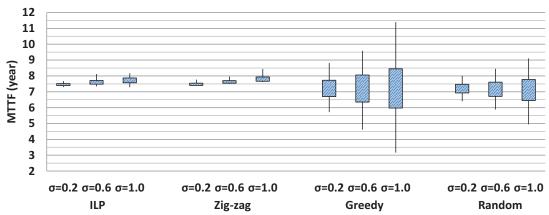

| Figure 4.33:  | Stacking optimization using the ILP-based method and the zig-zag method helps increase the minimum MTTF of output stacks, while reducing the                                                                                       |             |

|               | variation in MTTFs                                                                                                                                                                                                                 | 196         |

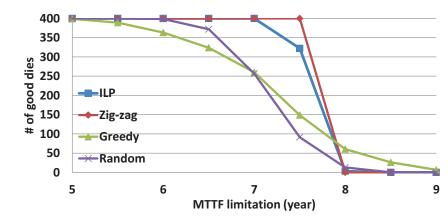

| Figure 4.34:  | Yield decreases with MTTF limitation. The ILP-based and the zig-zag heuristic methods help increase the yield of 3DICs compared to the random                                                                                      | 100         |

| F: 4.25       | case                                                                                                                                                                                                                               | 198         |

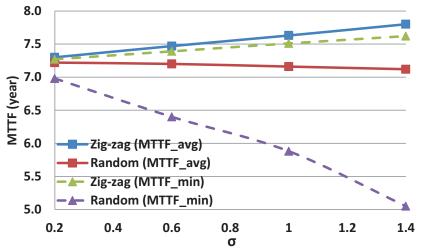

| Figure 4.35:  | The solid lines and dotted lines indicate the average and the minimum MTTF                                                                                                                                                         | 100         |

| F: 4.06       | of stacks, respectively.                                                                                                                                                                                                           | 199         |

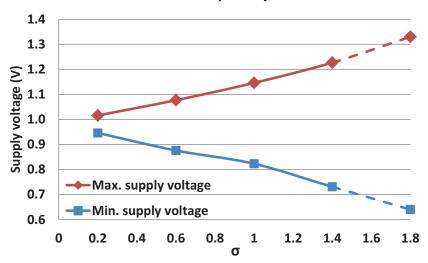

| Figure 4.36:  | The maximum supply voltage of stacks increases with process variation,                                                                                                                                                             |             |

|               | while the minimum voltage decreases. The solid line corresponds to our                                                                                                                                                             | 100         |

| Ei 4 27.      | experimental results. The dashed line is an extrapolation of the trend                                                                                                                                                             | 199         |

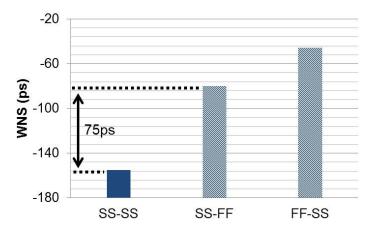

| Figure 4.37:  | Worst negative slack (WNS) of design AES [230] at 28FDSOI technology.                                                                                                                                                              |             |

|               | Clock period = $1.2ns$ . The <i>AES</i> implementation was simply bipartitioned                                                                                                                                                    | 201         |

| Eigung 4 20.  | for minimum net cut using MLPart [25][229]                                                                                                                                                                                         | 201         |

| Figure 4.38:  | Partitioning solutions affect a design's performance in the regime of mix-<br>and-match stacking.                                                                                                                                  | 202         |

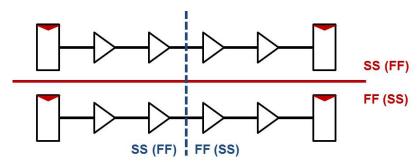

| Figure 4.39:  | and-match stacking                                                                                                                                                                                                                 | 202         |

| 11guie 4.39.  | (30 stages) which respectively minimize (a) delay of path A-C ( $D_{AC}$ ), (b)                                                                                                                                                    |             |

|               | delay of path B-C $(D_{BC})$ , (c) worst-case delay over the two paths, and (d)                                                                                                                                                    |             |

|               | worst-case delay over the two paths with large VI delay impact $(d_{VI})$                                                                                                                                                          | 204         |

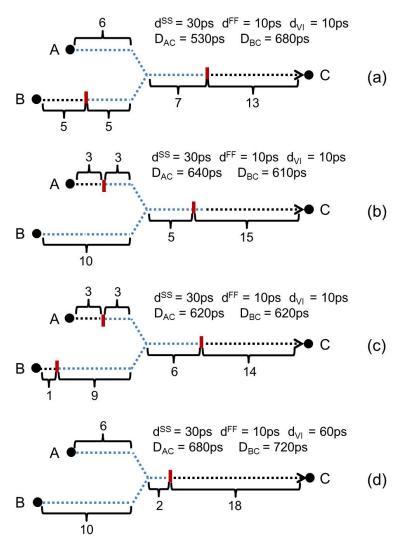

| Figure 4.40:  | Example of maximum-cut partitioning of the sequential graph. Types of                                                                                                                                                              | 204         |

| 11guic 4.40.  | paths are shown in edge labels. The dotted line indicates the final maximum-                                                                                                                                                       |             |

|               | cut solution. We assume the same weight for all edges                                                                                                                                                                              | 210         |

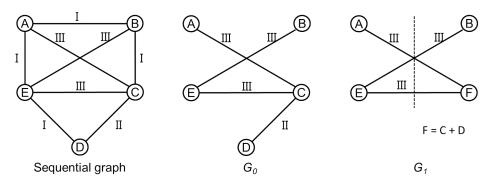

| Figure 4.41:  | Example to optimize a cell with a negative gain value. (a) Initial path with                                                                                                                                                       | 210         |

| riguic 4.41.  | zero slack. (b) Moving one cell to Tier 1 degrades the slack by 70ps due to                                                                                                                                                        |             |

|               | VI insertions. (c) Further optimization on the shown segment improves the                                                                                                                                                          |             |

|               | slack by $50ps$                                                                                                                                                                                                                    | 211         |

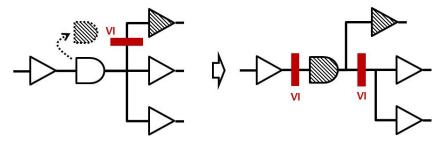

| Figure 4.42.  | Example of VI insertion/removal due to cell movement across tiers. Shaded                                                                                                                                                          | <b>~</b> 11 |

| 1 15010 1.12. | cells are on Tier 1 and the others are on Tier 0                                                                                                                                                                                   | 212         |

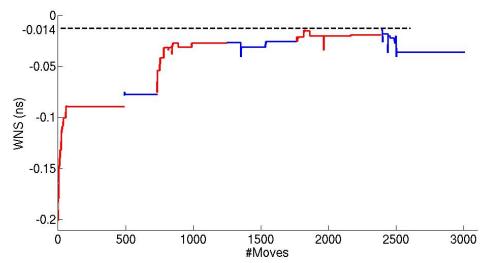

| Figure 4.43: | An example of our multi-phase FM optimization. Design: AES. Technol-     |     |

|--------------|--------------------------------------------------------------------------|-----|

|              | ogy: 28FDSOI. WNS improves from $-200ps$ to $-14ps$ . Runtime = 565 sec- |     |

|              | onds on a 2.5GHz Intel Xeon server                                       | 214 |

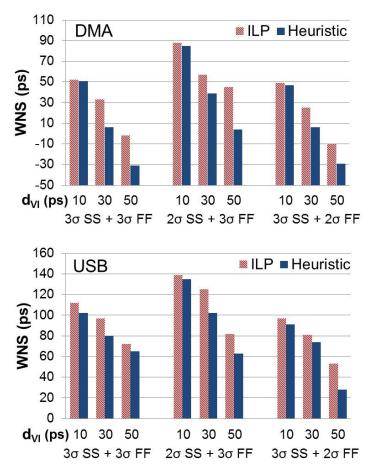

| Figure 4.44: | Comparison of solution qualities between the ILP-based method (which is  |     |

|              | near-optimal) and the heuristic method                                   | 217 |

#### LIST OF TABLES

| Table 2.1:  | Experimental setup for the FIND_OD problem                                                 | 23  |

|-------------|--------------------------------------------------------------------------------------------|-----|

| Table 2.2:  | Metrics of circuits implemented for the FIND_OD problem                                    | 24  |

| Table 2.3:  | Experimental setup for the FIND_VOLT problem                                               | 25  |

| Table 2.4:  | Metrics of circuits implemented for the FIND_VOLT problem                                  | 25  |

| Table 2.5:  | Experimental setup for the FIND_FREQ problem                                               | 20  |

| Table 2.6:  | Metrics of circuits implemented for the FIND_FREQ problem                                  | 20  |

| Table 2.7:  | Metrics of circuits implemented with different $r_{opt}$                                   | 20  |

| Table 2.8:  | Description of notations used in our work                                                  | 30  |

| Table 2.9:  | Candidate moves in our optimization                                                        | 39  |

| Table 2.10: | Description of corners                                                                     | 4   |

| Table 2.11: | Summary of testcases                                                                       | 4   |

| Table 2.12: | Experimental results                                                                       | 42  |

| Table 2.13: | Notations used in our work                                                                 | 50  |

| Table 2.14: | Benchmark information                                                                      | 59  |

| Table 2.15: | Scan ordering results                                                                      | 59  |

| Table 2.16: | Gating insertion results                                                                   | 60  |

|             |                                                                                            |     |

| Table 3.1:  | Description of notations used in our discussion                                            | 64  |

| Table 3.2:  | Testcase parameters                                                                        | 7   |

| Table 3.3:  | Experimental results. (Power unit: $mW$ . Current unit: $mA$ . $\eta$ values are           |     |

|             | estimated based on [19].)                                                                  | 79  |

| Table 3.4:  | Results with different current balancing constraints. Designs: <i>TC1</i> and <i>TC2</i> . |     |

|             | $\Delta I$ , $P_{core}$ and $T$ are normalized to those of the conventional design         | 82  |

| Table 3.5:  | Description of notations used in our formulation                                           | 92  |

| Table 3.6:  | Testcase parameters                                                                        | 10  |

| Table 3.7:  | Normalized flop tray area and power, and layout AR                                         | 10  |

| Table 3.8:  | Experimental results                                                                       | 103 |

| Table 3.9:  | Testcases from OpenSPARC T1                                                                | 128 |

| Table 3.10: | Penalties of error-tolerant flip-flops                                                     | 128 |

| Table 3.11: | Impact of SkewOpt                                                                          | 13  |

| Table 3.12: | Pessimism of slow-corner optimization                                                      | 133 |

| Table 3.13: | Comparison among error-tolerant flip-flops                                                 | 134 |

|             |                                                                                            |     |

| Table 4.1:  | Notations used in our work                                                                 | 142 |

| Table 4.2:  | User-defined parameters                                                                    | 153 |

| Table 4.3:  | Benchmarks                                                                                 | 158 |

| Table 4.4:  | Parameters and results of implemented designs                                              | 163 |

| Table 4.5:  | Benchmark designs                                                                          | 174 |

| Table 4.6:  | Experimental setups for timing analysis                                                    | 174 |

| Table 4.7:  | Design metrics of routed design from different flows                                       | 17  |

| Table 4.8:  | Experiment design for reliability-driven stacking optimization                             | 194 |

| Table 4.9:  | Impact of number of dies on QoR of the ILP-based method                                    | 190 |

| Table 4.10: | QoR of output stacks from different methods                                                | 19  |

| Table 4.11: | Description of notations used in our work                                                  | 200 |

| Table 4.12: | Testcases used in the experiments                                        | 214 |

|-------------|--------------------------------------------------------------------------|-----|

| Table 4.13: | Validation of our partitioning methodology on GT2012 and Shrunk2D flows. | 216 |

#### **ACKNOWLEDGMENTS**

Foremost, I would like to thank my advisor Professor Andrew B. Kahng for his continuous support and generous advice throughout my Ph.D. study. I have truly learned a lot from his immense knowledge, serious and responsible work attitude, and passion for research.

I would like to thank my father Biao Li, my mother Yanhua Jiang, and my girlfriend Yun Sheng for their selfless support and encouragement. This journey would not have been possible without their sacrifice.

I would like to thank my fellow labmates in the UCSD VLSI CAD Laboratory (Wei-Ting (Jonas) Chan, Hyein Lee, Kwangsoo Han, Lutong Wang, Bangqi Xu, Ahmed Youssef, Tushar Shah, Sriram Venkatesh) and former lab members (Professor Seokhyeong Kang, Dr. Tuck-Boon Chan, Dr. Siddhartha Nath, Ilgweon Kang, Mulong Luo, Yaping Sun) for their assistance and enthusiastic discussions. I will remember the hard-working time and sleepless nights with them. Special thanks to Professor Seokhyeong Kang, Dr. Tuck-Boon Chan and Dr. Siddhartha Nath for their guidance at the beginning of my Ph.D. studies.

My sincere thanks also go to my thesis committee members Professor Chung-Kuan Cheng, Professor Rajesh Gupta, Professor Patrick Mercier, Professor Tajana Rosing and Professor Steven Swanson for their time, encouragement and insightful comments.

Last, but not least, I would like to thank my industrial collaborators (especially Dr. Bongil Park, Professor José Pineda de Gyvez, Dr. Hamed Fatemi, Jongpil Lee, Sorin Dobre, Nancy MacDonald, Dr. Kun Young Chung, Ajay Kapoor and Kristof Blutman) for their invaluable guidance and feedback in many of my research projects.

The material in this thesis is based on the following publications.

Chapter 2 contains reprints of Kun Young Chung, Andrew B. Kahng and Jiajia Li, "Comprehensive Optimization of Scan Chain Timing During Late-Stage IC Implementation", *Proc. ACM/IEEE Design Automation Conference*, 2016; Tuck-Boon Chan, Andrew B. Kahng, Jiajia Li, Siddhartha Nath and Bongil Park, "Optimization of Overdrive Signoff in High-Performance and Low-Power ICs", *IEEE Transactions on Very Large Scale Integration Systems* 23(8), 2015; Kwangsoo Han, Andrew B. Kahng, Jongpil Lee, Jiajia Li and Siddhartha Nath, "A Global-Local Optimization Framework for Simultaneous Multi-Mode Multi-Corner Skew Variation Reduction", *Proc. ACM/IEEE Design Automation Conference*, 2015; and Tuck-Boon Chan, Andrew B. Kahng, Jiajia Li and Siddhartha Nath, "Optimization of Overdrive Signoff", *Proc. Asia and South Pacific Design Automation Conference*, 2013. The dissertation author is the primary author of the papers.

Chapter 3 contains reprints of Kristof Blutman, Hamed Fatemi, Andrew B. Kahng, Ajay Kapoor, Jiajia Li, and José Pineda de Gyvez, "Floorplan and Placement Methodology for Improved Energy Reduction in Stacked Power-Domain Design", *Proc. Asia and South Pacific Design Automation Conference*, 2017; Andrew B. Kahng, Jiajia Li and Lutong Wang, "Improved Flop Tray-Based Design Implementation for Power Reduction", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2016; Andrew B. Kahng, Seokhyeong Kang, Jiajia Li and José Pineda de Gyvez, "An Improved Methodology for Resilient Design Implementation", *ACM Transactions on Design Automation of Electronic Systems* 20(4), 2015; and Andrew B. Kahng, Seokhyeong Kang and Jiajia Li, "A New Methodology for Reduced Cost of Resilience", *Proc. Great Lakes Symposium on Very Large Scale Integration*, 2014. Chapter 3 also contains the draft submitted to *IEEE Transactions on Very Large Scale Integration Systems*, Kristof Blutman, Hamed Fatemi, Andrew B. Kahng, Ajay Kapoor, Jiajia Li and Jose Pineda de Gyvez, "Logic Design Partitioning for Stacked Power Domains", 2017. The dissertation author is the primary author of the papers and the submitted draft.

Chapter 4 contains reprints of Kwangsoo Han, Andrew B. Kahng and Jiajia Li, "Improved Performance of 3DIC Implementations Through Inherent Awareness of Mix-and-Match Die Stacking", *Proc. Design, Automation and Test in Europe*, 2016; Sorin Dobre, Andrew B. Kahng and Jiajia Li, "Mixed Cell-Height Implementation for Improved Design Quality in Advanced Nodes", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2015; Tuck-Boon Chan, Andrew B. Kahng and Jiajia Li, "NOLO: A No-Loop, Predictive Useful Skew Methodology for Improved Timing in IC Implementation", *Proc. International Symposium on Quality Electronic Design*, 2014; and Tuck-Boon Chan, Andrew B. Kahng and Jiajia Li, "Reliability-Constrained Die Stacking Order in 3DICs under Manufacturing Variability", *Proc. International Symposium on Quality Electronic Design*, 2013. Chapter 4 also contains the draft submitted to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Sorin Dobre, Andrew B. Kahng and Jiajia Li, "Design Implementation with Non-Integer Multiple-Height Cells for Improved Design Quality in Advanced Nodes". The dissertation author is the primary author of the papers and the submitted draft.

My coauthors (Kristof Blutman, Dr. Tuck-Boon Chan, Dr. Kun Young Chung, Sorin Dobre, Dr. Hamed Fatemi, Professor José Pineda de Gyvez, Kwangsoo Han, Professor Andrew B. Kahng, Professor Seokhyeong Kang, Ajay Kapoor, Jongpil Lee, Dr. Siddhartha Nath, Dr. Bongil Park and Lutong Wang listed in alphabetical order) have all kindly approved the inclusion of the aforementioned publications in my thesis.

#### **VITA**

| 1989 | Born, Taiyuan, Shanxi, China                                                                   |

|------|------------------------------------------------------------------------------------------------|

| 2011 | B.Sc., Software Engineering,<br>Shenzhen University, Shenzhen, Guangdong, China                |

| 2013 | M.Sc., Electrical Engineering (Computer Engineering),<br>University of California, San Diego   |

| 2015 | C.Phil., Electrical Engineering (Computer Engineering),<br>University of California, San Diego |

| 2017 | Ph.D., Electrical Engineering (Computer Engineering),<br>University of California, San Diego   |

All papers co-authored with my advisor Prof. Andrew B. Kahng have authors listed in alphabetical order.

- Wei-Ting J. Chan, Andrew B. Kahng and **Jiajia Li**, "Revisiting 3DIC Benefit with Multiple Tiers", *Integration, the VLSI Journal*, 2017, to appear.

- Armin Alaghi, Wei-Ting J. Chan, John P. Hayes, Andrew B. Kahng and Jiajia Li, "Trading Accuracy for Energy in Stochastic Circuit Design", ACM Journal on Emerging Technologies in Computing Systems, 2017, to appear.

- Kristof Blutman, Hamed Fatemi, Andrew B. Kahng, Ajay Kapoor, Jiajia Li, and José

Pineda de Gyvez, "Floorplan and Placement Methodology for Improved Energy Reduction

in Stacked Power-Domain Design", *Proc. Asia and South Pacific Design Automation*Conference, 2017, pp. 444-449.

- Andrew B. Kahng, Hyein Lee and Jiajia Li, "Measuring Progress and Value of IC Implementation Technology", Proc. IEEE/ACM International Conference on Computer-Aided Design, 2016, pp. 27:1-27:8.

- Andrew B. Kahng, Jiajia Li and Lutong Wang, "Improved Flop Tray-Based Design Implementation for Power Reduction", Proc. IEEE/ACM International Conference on Computer-Aided Design, 2016, pp. 20:1-20:8.

- Kun Young Chung, Andrew B. Kahng and Jiajia Li, "Comprehensive Optimization of Scan Chain Timing During Late-Stage IC Implementation", *Proc. ACM/IEEE Design* Automation Conference, 2016, pp. 61:1-61:6.

- Wei-Ting Jonas Chan, Andrew B. Kahng and Jiajia Li, "Revisiting 3DIC Benefit with Multiple Tiers", Proc. ACM International Workshop on System-Level Interconnect Prediction, 2016, pp. 6:1-6:8.

- Kwangsoo Han, Andrew B. Kahng and Jiajia Li, "Improved Performance of 3DIC Implementations Through Inherent Awareness of Mix-and-Match Die Stacking", *Proc. Design, Automation and Test in Europe*, 2016, pp. 61-66.

- Armin Alaghi, Wei-Ting J. Chan, John P. Hayes, Andrew B. Kahng and Jiajia Li, "Optimizing Stochastic Circuits for Accuracy-Energy Tradeoffs", Proc. IEEE/ACM International Conference on Computer-Aided Design, 2015, pp. 178-185.

- Sorin Dobre, Andrew B. Kahng and Jiajia Li, "Mixed Cell-Height Implementation for Improved Design Quality in Advanced Nodes", Proc. IEEE/ACM International Conference on Computer-Aided Design, 2015, pp. 854-860.

- Myung-Chul Kim, Jin Hu, Jiajia Li and Natarajan Viswanathan, "ICCAD-2015 CAD

Contest in Incremental Timing-driven Placement and Benchmark Suite", *Proc. IEEE/ACM* International Conference on Computer-Aided Design, 2015, pp. 921-926.

- Andrew B. Kahng, Seokhyeong Kang, Jiajia Li and José Pineda de Gyvez, "An Improved Methodology for Resilient Design Implementation", ACM Transactions on Design Automation of Electronic Systems 20(4) (2015), pp. 66:1-66:26.

- Tuck-Boon Chan, Andrew B. Kahng, Jiajia Li, Siddhartha Nath and Bongil Park, "Optimization of Overdrive Signoff in High-Performance and Low-Power ICs", *IEEE Transactions on Very Large Scale Integration Systems* 23(8) (2015), pp. 1552-1556.

- Kwangsoo Han, Andrew B. Kahng, Jongpil Lee, Jiajia Li and Siddhartha Nath, "A Global-Local Optimization Framework for Simultaneous Multi-Mode Multi-Corner Skew Variation Reduction", *Proc. ACM/IEEE Design Automation Conference*, 2015, pp. 26:1-26:6.

- Andrew B. Kahng, Hyein Lee and Jiajia Li, "Horizontal Benchmark Extension for Improved Assessment of Physical CAD Research", Proc. Great Lakes Symposium on Very Large Scale Integration, 2014, pp. 27-32.

- Andrew B. Kahng, Seokhyeong Kang and Jiajia Li, "A New Methodology for Reduced Cost of Resilience", Proc. Great Lakes Symposium on Very Large Scale Integration, 2014, pp. 157-162.

- Tuck-Boon Chan, Andrew B. Kahng and Jiajia Li, "NOLO: A No-Loop, Predictive Useful Skew Methodology for Improved Timing in IC Implementation", *Proc. International Symposium on Quality Electronic Design*, 2014, pp. 504-509.

- Tuck-Boon Chan, Andrew B. Kahng and **Jiajia Li**, "Toward Quantifying the IC Design Value of Interconnect Technology Improvements", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2013, pp. 1-6.

- Tuck-Boon Chan, Andrew B. Kahng and **Jiajia Li**, "Reliability-Constrained Die Stacking Order in 3DICs under Manufacturing Variability", *Proc. International Symposium on Quality Electronic Design*, 2013, pp. 16-23.

- Tuck-Boon Chan, Andrew B. Kahng, Jiajia Li and Siddhartha Nath, "Optimization of Overdrive Signoff", Proc. Asia and South Pacific Design Automation Conference, 2013, pp. 344-349.

#### ABSTRACT OF THE DISSERTATION

## Improved Physical Design and Signoff Methodologies for Better Integrated Circuit Design Quality

by

#### Jiajia Li

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California, San Diego, 2017

Professor Andrew B. Kahng, Chair

In the late CMOS era, integrated-circuit physical design and signoff face three major challenges – (i) complex operating conditions, (ii) low-power demand, and (iii) growing design margin. Future scaling of designs and the continuation of Moore's Law itself require better physical design optimization and signoff methodologies. Toward this end, this thesis presents novel optimization techniques and signoff methodologies to respectively address these challenges in three main thrusts.

In modern SoC implementations, multi-mode design is commonly used to achieve better circuit performance and power across voltage scaling, "turbo" and other operating modes. Furthermore, PVT variations result in a large number of corners for circuit design and signoff. To mitigate the impact of complex operating conditions and corner explosion, in the *multi-mode multi-corner optimization* thrust, this thesis presents approaches to optimize signoff corner se-

lection, reduce skew variation in clock network, and perform scan timing optimization without causing any QoR degradation in functional mode.

Energy and battery lifetime constraints induce new and critical challenges to IC designs, especially for mobile and "Internet of Things" (IoT) applications. To achieve power autonomy in the era of a slowing Moore's law, low-power techniques must be exploited. To minimize design power and energy, in the *low-power optimization* thrust, this thesis presents a stacked power domain scheme to align SoC power domain voltages with battery voltages for power delivery efficiency and battery lifetime improvements, a novel flop tray generation technique for clock power reduction, and a low-cost resilient design flow to enable better than worst-case design for energy savings.