# **UC Riverside**

# **UC Riverside Electronic Theses and Dissertations**

## **Title**

Study of Nanocrystal Structures and Their Memory Applications

## **Permalink**

https://escholarship.org/uc/item/58t4w8xd

## **Author**

Olmedo, Mario Jesus

# **Publication Date**

2012

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Study of Nanocrystal Structures and Their Memory Applications

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Mario Jesus Olmedo

June 2012

Dissertation Committee: Dr. Jianlin Liu, Chairperson

Dr. Roger Lake Dr. Cengiz Ozkan

| ne Dissertation of | of Mario Jesus Olmedo is approved: |       |

|--------------------|------------------------------------|-------|

|                    |                                    |       |

|                    |                                    | _     |

|                    |                                    |       |

|                    |                                    | _     |

|                    |                                    |       |

|                    |                                    | _     |

|                    | Committee Chairp                   | erson |

University of California, Riverside

#### ACKNOWLEDGEMENTS

My first and foremost acknowledgement is to my advisor Dr. Jianlin Liu. Without his help, patience and support I would not have been able to have such a wonderful opportunity. During my stay in his lab I was able to learn and grow as a student and as a researcher. It goes without saying that even though we might have had troubled times between each other in research discussions; his goal was always in my best interest.

I would also like to thank my committee members, Dr. Roger Lake, and Dr. Gengiz Ozkan for being supporters of my work and for giving me their time to have very candid discussions on my possible career decisions; they help put in me perspective.

Of all the wonderful people that I have met throughout my graduate studies I would really like to acknowledge my lab mates and colleagues that helped me the most. I would like to thank Jieying Kong, Jing Qi, Faxian Xiu, Zheng Yan, Bei Li, Sheng Chu, Lin Li, Jingjian Ren, Ning Zhang, Zheng Zou, Huimei Zhou, Jian Huang and Monzur Morshed. Without the pleasant working environment you guys created I would not have had such a great time.

Finally I would like to thank my parents, my brother and the rest of my family for their support and understanding that a doctorate takes time and sacrifice. Their support was invaluable and this would not have happened without them.

This thesis is dedicated to my Mom and Dad.

#### ABSTRACT OF THE DISSERTATION

Study of Nanocrystal Structures and Their Memory Applications

by

#### Mario Jesus Olmedo

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, June 2012 Dr. Jianlin Liu, Chairperson

In the field of floating gate memory, also known as flash memory, silicon (Si) nanocrystals (NC) are one of the leading alternatives to traditional poly-Si floating gate memory because of their improved scalability, speed and simpler fabrication. In our research, Si NCs are grown on top of oxide covered carbon nanotubes (CNTs) by gas source molecular beam epitaxy for the purpose of making floating gate memory with the CNT as the field effect transistor (FET) channel. At certain conditions the NCs align on the apexes of the CNTs. These alignment properties are studied with relation to different growth conditions and sample parameters. Also FET and memory device characteristics are studied for devices based on this structure as well as the frequency response of devices that exhibit ambipolar properties. Another memory technology that has been attractive to replace flash due to its low power consumption and its stacking properties is resistive memory. Here ZnO NCs are used as the resistive switching material. The memory characteristics are studied with a conductive atomic force microscope contacting

a single NC. Both of these technologies will be shown to have favorable properties compared to the current floating gate technology.

# Index

| 1 | Chapter 1: Intr | oduction                                    | 1              |

|---|-----------------|---------------------------------------------|----------------|

|   | 1.1 Introducti  | on to flash memory                          | 1              |

|   | 1.2 Introducti  | on to NC floating gate memory               | 5              |

|   | 1.3 Reference   | es                                          | 6              |

| 2 | Chapter 2: Meth | nodology                                    | 10             |

|   | 2.1 NC growt    | h                                           | 10             |

|   | 2.1.1           | Si NC growth                                | 10             |

|   | 2.1.2           | ZnO NC growth                               | 12             |

|   | 2.2 NC chara    | cterization                                 | 12             |

|   | 2.2.1           | AFM characterization.                       | 12             |

|   | 2.2.2           | SEM characterization.                       | 15             |

|   | 2.2.3           | TEM characterization.                       | 17             |

|   | 2.2.4           | AES characterization.                       | 18             |

|   | 2.3 NC devic    | e fabrication                               | 19             |

|   | 2.3.1           | ALD deposition.                             | 19             |

|   | 2.3.2           | Photolithography                            | 20             |

|   | 2.3.3           | E-beam evaporation                          | 22             |

| 3 | Chapter 3: Peri | odic Alignment of Si Quantum Dots on Hafniu | m Oxide Coated |

|   | Single Wall Car | rbon Nanotubes                              | 24             |

|   | 3.1 Introducti  | on                                          | 24             |

|   | 3.2 Experime    | nt                                          | 25             |

|   | 3.3 Results     |                                             | 25             |

|   | 3.3.1           | Structure description                       | 25             |

|   | 3.3.2          | Reference sample.                                                 | 27    |

|---|----------------|-------------------------------------------------------------------|-------|

|   | 3.3.3          | Flow rate dependence.                                             | 27    |

|   | 3.3.4          | Growth time dependence                                            | 28    |

|   | 3.3.5          | Growth temperature dependence                                     | 29    |

|   | 3.3.6          | Oxide thickness dependence                                        | 31    |

|   | 3.4 Conclusio  | n                                                                 | 32    |

|   | 3.5 Reference  | S                                                                 | 33    |

| 4 |                | rbon Nanotube Memory by the Self-Assembly of Charge Storage Nodes |       |

|   | ·              | on                                                                |       |

|   | 4.2 Experime   | nt                                                                | 36    |

|   | 4.2.1          | CNT transfer                                                      | 36    |

|   | 4.2.2          | CNT-based Si NC memory device structure growth                    | 37    |

|   | 4.3 Results    |                                                                   | 38    |

|   | 4.3.1          | Growth characteristics                                            | 38    |

|   | 4.3.2          | Characterization of Si NC alignment                               | 40    |

|   | 4.3.3          | EFM results                                                       | 41    |

|   | 4.3.4          | Device characteristics.                                           | 44    |

|   | 4.3.5          | Tunneling characteristics.                                        | 45    |

|   | 4.3.6          | Transient characteristics                                         | 47    |

|   | 4.3.7          | Retention characteristics                                         | 48    |

|   | 4.3.8          | Retention reference.                                              | 51    |

|   | 4.4 Conclusio  | on                                                                | 51    |

|   | 4.5 Reference  | S                                                                 | 52    |

| 5 | Chapter 5: Am  | bipolar CNT Memory with Multi-mode Signal Respon                  | ıse57 |

|   | 5.1 Introducti | on                                                                | 57    |

|   | 5.2 Experime     | nt                                                      | 58          |

|---|------------------|---------------------------------------------------------|-------------|

|   | 5.2.1            | CNT Pt NC memory device structure growth                | 58          |

|   | 5.3 Results      |                                                         | 59          |

|   | 5.3.1            | Device structure.                                       | 59          |

|   | 5.3.2            | FET characteristics.                                    | 60          |

|   | 5.3.3            | Signal response.                                        | 62          |

|   | 5.3.4            | Binary signal response                                  | 63          |

|   | 5.4 Conclusio    | on                                                      | 65          |

|   | 5.5 Reference    | es                                                      | 65          |

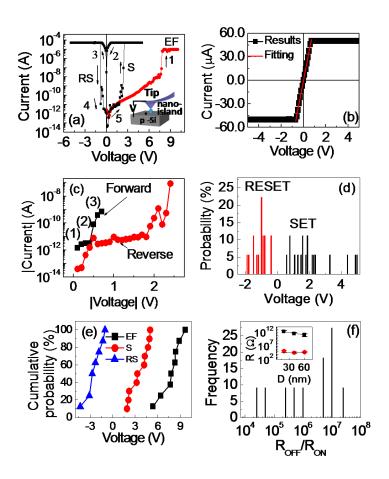

| 5 | Chapter 6: Resis | stive Switching in Single Epitaxial ZnO Nano-Island     | 67          |

|   | 6.1 Introducti   | on                                                      | 67          |

|   | 6.2 Experime     | nt                                                      | 68          |

|   | 6.2.1            | ZnO growth conditions                                   | 69          |

|   | 6.2.2            | I-V characterization and C-AFM measurement system setup | <b>5</b> 70 |

|   | 6.3 Results      |                                                         | 71          |

|   | 6.3.1            | Growth characteristics.                                 | 71          |

|   | 6.3.2            | Morphology of ZnO single-crystal nano-islands           | 73          |

|   | 6.3.3            | I-V characteristics for ZnO single-crystal nano-islands | 74          |

|   | 6.3.4            | Electrical characteristics.                             | 76          |

|   | 6.3.5            | Retention and endurance                                 | 81          |

|   | 6.3.6            | CAFM measurements                                       | 82          |

|   | 6.3.7            | Analysis of CAM tips                                    | 85          |

|   | 6.3.8            | Mechanism.                                              | 89          |

|   | 6.4 Conclusio    | on                                                      | 93          |

|   | 6.5 Reference    | es                                                      | 93          |

| 7 | Chapter 7: Cond  | olucion                                                 | 101         |

# List of figures

| Figure 1-1. Schematic cross section of a floating gate transistor and energy band diagra          | m   |

|---------------------------------------------------------------------------------------------------|-----|

| for the (a) initial state and (b) programmed state                                                | .3  |

| Figure 1-2. I-V curves of a floating gate device when there is no charge stored ( $I_{ON}$ ) at   | nd  |

| when there is negative charge stored ( $I_{OFF}$ )                                                | .3  |

| Figure 1-3. Schematic representation of a leakage site in (a) a countinous floating ga            | ıte |

| and (b) NC floating gate transistor memory.                                                       | .4  |

| Figure 2-1. Effusion cell schematic.                                                              | 11  |

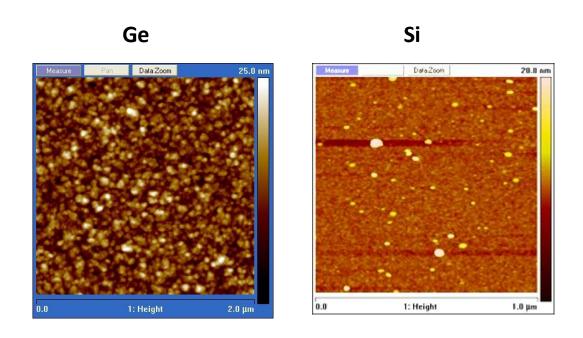

| Figure 2-2. Examples of Ge and Si growths; Images were taken by AFM                               | 12  |

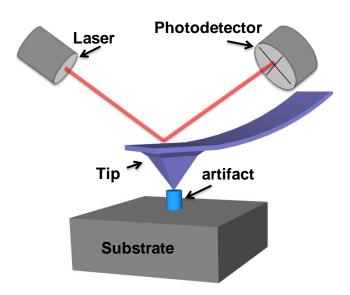

| Figure 2-3. AFM mechanism schematic in contact mode.                                              | 13  |

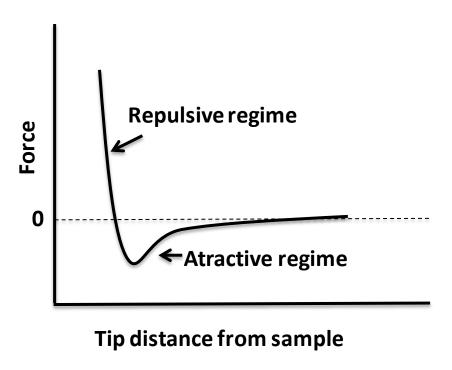

| Figure 2-4. Force curve as a measure of distance. As the tip gets closer to the sample, the       | he  |

| tip will have an attractive force towards the sample. Until the sample and tip touch each         | ch  |

| other then the tip and the sample would have a repulsive force upon them                          | 15  |

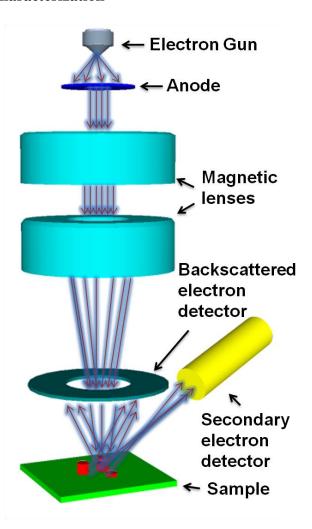

| Figure 2-5. Schematic drawing of the SEM electron optics.                                         | 16  |

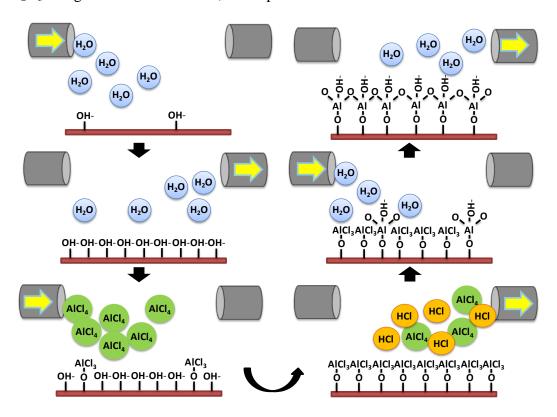

| Figure 2-6. ALD deposition process. First water is pulsed from the source to the grow             | th  |

| chamber, then a set time is waited until the substrate surface is fully covered. After the        | at  |

| time has passed, the remaining water is pumped out and the AlCl <sub>4</sub> sourced is pulsed in | n.  |

| The second precursor reacts with the water to create HCl. After the next water pulse the          | he  |

| first layer of Al <sub>2</sub> O <sub>3</sub> is formed.                                          | 20  |

| Figure 2-7. Schematic of the photolithography process.                                            | 22  |

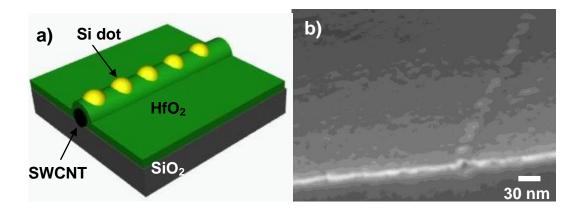

| Figure 3-1. Quantum dots on a hafnium oxide covered carbon nanotube. (a) Schematic of                           |

|-----------------------------------------------------------------------------------------------------------------|

| a cross sectional view of the structure. (b) SEM image cross-sectional shows aligned QDs                        |

| on a HfO <sub>2</sub> covered CNT                                                                               |

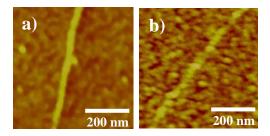

| Figure 3-2. AFM images of HfO <sub>2</sub> covered CNT after in-situ annealing, (a) before and (b)              |

| after the introduction of disilane                                                                              |

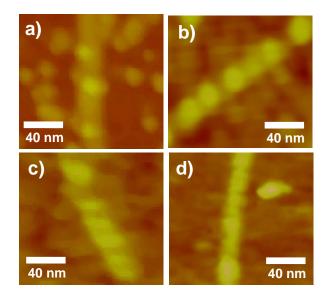

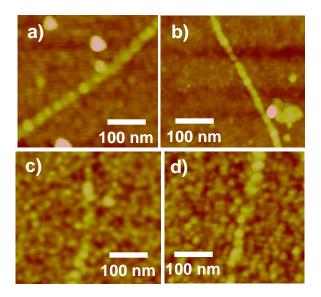

| Figure 3-3. AFM image of four samples that were grown at different Si <sub>2</sub> H <sub>6</sub> flow rate: a) |

| 1.1sccm, b) 1.6sccm, c) 1.8sccm, d) 2.1sccm                                                                     |

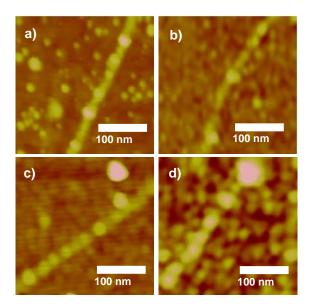

| Figure 3-4. AFM images of four samples that have different growth times: a) 3 min, b) 5                         |

| min, c) 7 min, d) 8min                                                                                          |

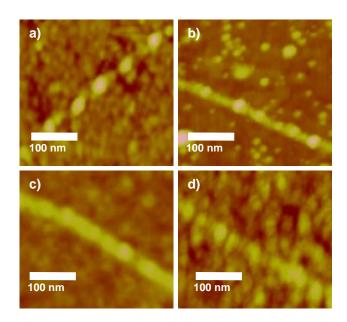

| Figure 3-5. AFM images of four samples that have different growth temperatures: a)                              |

| 640°C, b) 650°C, c) 670°C, d) 680°C                                                                             |

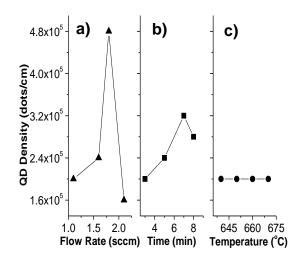

| Figure 3-6. Linear density of QDs on CNTs as a function of a) flow rate, b) growth time,                        |

| and c) growth temperature                                                                                       |

| Figure 3-7. AFM images of four samples that have different hafnium oxide thickness: a)                          |

| 6 nm, b) 7 nm, c) 7.6 nm, d) 8 nm                                                                               |

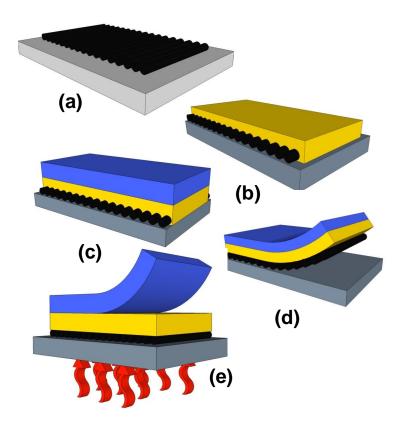

| Figure 4-1. CNT transfer characteristics. (a) CNTs grown on quartz; (b) CNTs covered                            |

| with 100nm Au; (c) thermal tape adhesion and to the quartz substrate and (d) transfer to                        |

| the $SiO_2$ substrate; (e) thermal release of the $Au/CNT$ film on the $SiO_2$ substrate37                      |

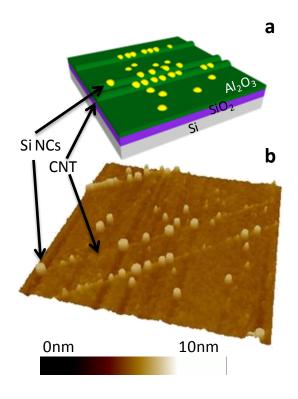

| Figure 4-2. (a) Schematic representation, and (b) AFM image of parallel-aligned CNTs                            |

| after ALD $Al_2O_3$ deposition and Si NC growth. The image size is 2 $\mu m$ with average Si                    |

| NC height of 5nm                                                                                                |

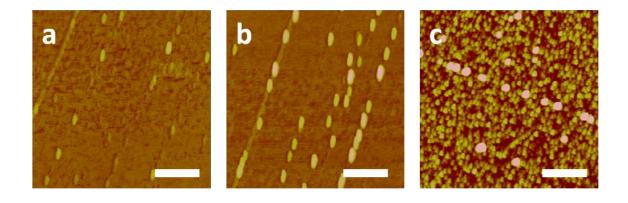

| Figure 4-3. AFM images of Si NCs on Al <sub>2</sub> O <sub>3</sub> covered parallel-aligned CNTs under the |

|------------------------------------------------------------------------------------------------------------|

| growth conditions of (a) 2 sccm $Si_2H_6$ flow rate, 650°C growth temperature, 5 min                       |

| growth time, (b) 4 sccm $Si_2H_6$ flow rate, $650^{\circ}C$ growth temperature, 5 min growth time,         |

| and (c) 4 sccm $Si_2H_6$ flow rate, $650^{\circ}C$ growth temperature, 10 min growth time. The             |

| scale bar represents 500nm. Preferential alignment of Si NCs is evident in all samples                     |

| and the density and size of NCs change as the growth condition changes41                                   |

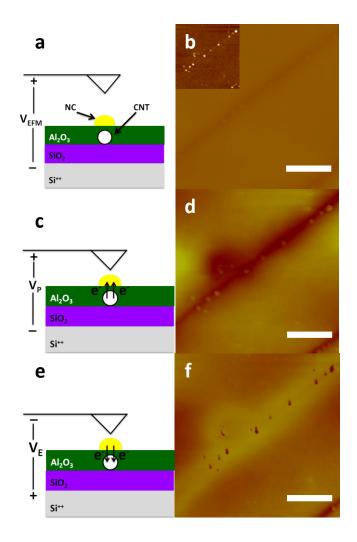

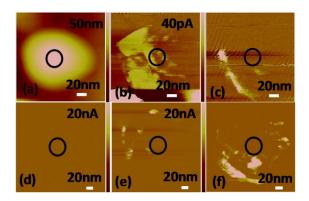

| Figure 4-4. EFM characterization of CNT-based Si NC memory. (a) Schematic                                  |

| representation of $V_{\text{EFM}} = -3V$ applied as reading voltage. (b) EFM image of the initial          |

| state of a CNT with Si NCs and the inset shows the corresponding topography. (c)                           |

| Schematic representation of programming at $V_P = 12V$ and shows (d) the resulting EFM                     |

| image. (e) Schematic representation of erasing at $V_{\text{E}} =$ -12V and shows (f) the resulting        |

| EFM image. The scale bar represents 500nm                                                                  |

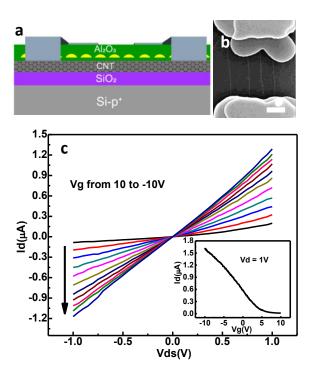

| Figure 4-5. (a) Schematic of the fabricated back gate FET device with a passivation layer                  |

| of 20 nm on top of the Si NCs. (b) SEM image of the CNT-based Si NC memory device                          |

| after passivation; the scale bar indicates $1\mu m.$ (c) Linear Id $-$ Vd characteristics under Vg         |

| = $10$ to $-10V$ with $-2V$ step, indicating that the contacts are Ohmic. The Id $-Vg$ (inset)             |

| characteristic suggests that the device is a p-type semiconducting CNT FET45                               |

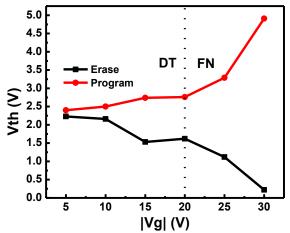

| Figure 4-6. $V_{th}$ change as a function of absolute value of $V_{g}$ . A positive voltage is used        |

| for programming while a negative voltage is used for erasing. During the programming                       |

| and erasing, the pulse width is 1 second while the source/drain are common46                               |

| Figure 4-6. $V_{th}$ change as a function of absolute value of $V_g$ . A positive voltage is used                        |

|--------------------------------------------------------------------------------------------------------------------------|

| for programming while a negative voltage is used for erasing. During the programming                                     |

| and erasing, the pulse width is 1 second while the source/drain are common47                                             |

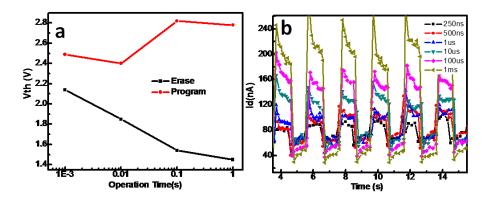

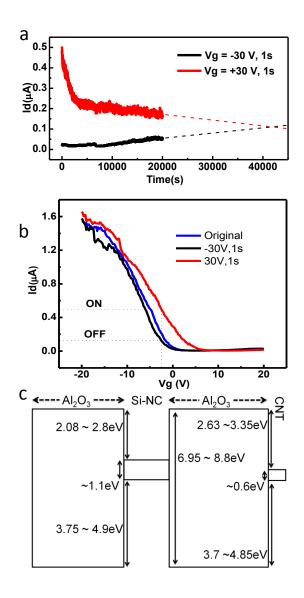

| Figure 4-8. (a) Retention characteristics of the CNT-based Si NC FET memory device.                                      |

| Programming and erasing voltages are $V_g\!=\!$ -30V and $V_g\!=\!$ 30 V, respectively. The linear                       |

| fitting is used to extrapolate the time when all charges are lost to be approximately                                    |

| $4\times10^4 s.$ (b) $I_d\text{-}V_g$ curves for fresh, programmed, and erased states, showing memory                    |

| effect. The reading voltage of $V_{\rm g}$ = -2.5 V was applied constantly throughout the                                |

| retention measurement. (c) Band alignment of the CNT-based Si NC memory with                                             |

| different values for the Al <sub>2</sub> O <sub>3</sub> E <sub>g</sub> , electron barrier height and hole barrier height |

| depending on the crystalline state of the Al <sub>2</sub> O <sub>3</sub>                                                 |

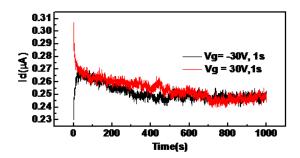

| Figure 4-9. Retention characteristics of CNT memory without NCs                                                          |

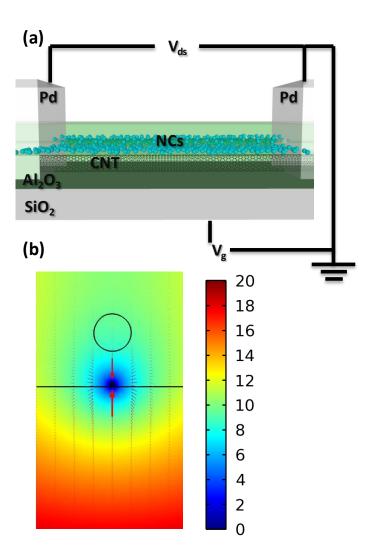

| Figure 5-1. (a) CNT FET with NC floating gate structure. (b) Electrostatic simulation of                                 |

| 20V Vg on the CNT/NC structure 60                                                                                        |

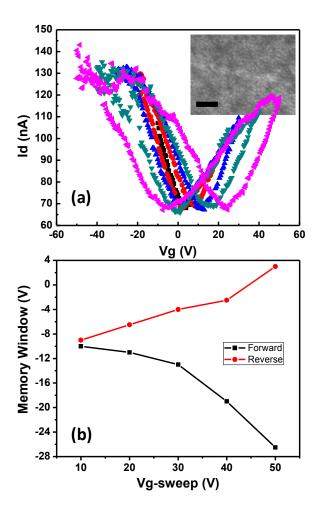

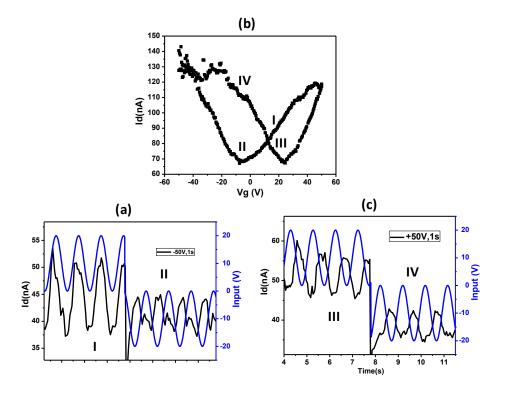

| Figure 5-2. (a)Id-Vg sweep characterization with increasing Vg sweep values. The inset                                   |

| shows the SEM picture of Pt NCs on top of oxide covered CNTs. (b) Memory window                                          |

| voltage characterization taken at Id=100nA with increasing Vg sweep values62                                             |

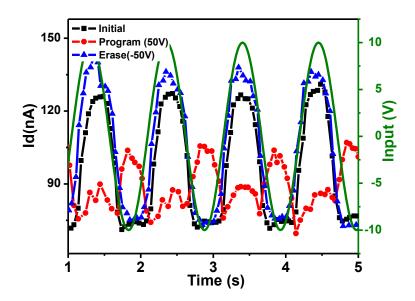

| Figure 5-3. Id change over time with a sinusoidal input at the gate                                                      |

| Figure 5-4. (a) Id response over time to a binary sinusoidal signal after the NCs had been                               |

| erased. (b) Id-Vg sweep showing the points of measurement for the programmed and                                         |

| erased states. (c) Id response over time to a binary sinusoidal signal after the NCs had                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| been programmed                                                                                                                                                                                                                                                                                                                                                                                               |

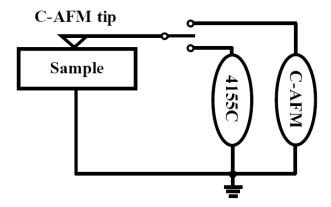

| Figure 6-1. Schematic of measurement system setup including an Agilent 4155C                                                                                                                                                                                                                                                                                                                                  |

| semiconductor parameter analyzer and a C-AFM equipment70                                                                                                                                                                                                                                                                                                                                                      |

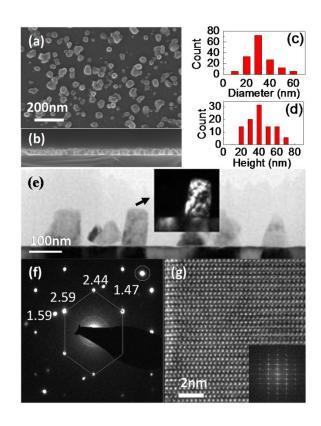

| Figure 6-2. (a) Top-view, (b) cross-sectional SEM images, (c) diameter, and (d) height                                                                                                                                                                                                                                                                                                                        |

| distributions of ZnO nano-islands. (e) Bright-field TEM micrograph of the nano-islands.                                                                                                                                                                                                                                                                                                                       |

| (f) SAED pattern from the area displayed in (e) including diffraction spots from both the                                                                                                                                                                                                                                                                                                                     |

| Si substrate and ZnO nano-islands. (g) A HRTEM image from one ZnO nano-island.                                                                                                                                                                                                                                                                                                                                |

| Inset in (e): A dark-field image recorded with the spot marked in a circle in (f). Inset in                                                                                                                                                                                                                                                                                                                   |

| (g): A fast Fourier transform (FFT) of the image (g)                                                                                                                                                                                                                                                                                                                                                          |

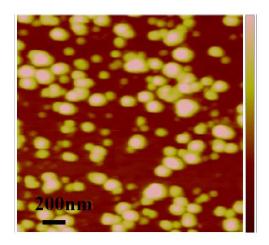

| Figure 6-3. AFM image of ZnO single-crystal nano-islands observed in tapping                                                                                                                                                                                                                                                                                                                                  |

| mode                                                                                                                                                                                                                                                                                                                                                                                                          |

| mode/5                                                                                                                                                                                                                                                                                                                                                                                                        |

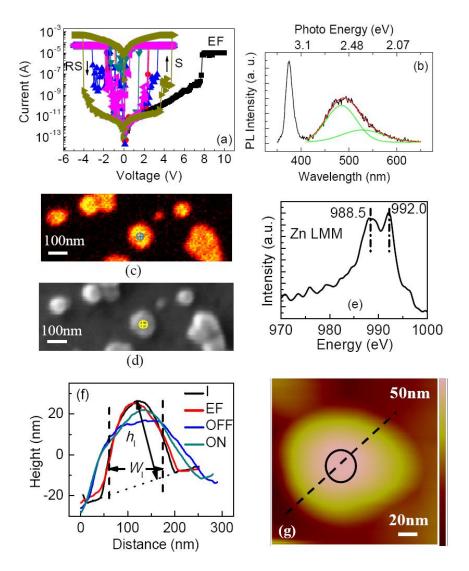

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10μA, CC2=50μA, and                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10 $\mu$ A, CC2=50 $\mu$ A, and                                                                                                                                                                                                                                                                                                                 |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10 $\mu$ A, CC2=50 $\mu$ A, and 500 $\mu$ A. (b) PL measured at room temperature for ZnO nano-islands deposited on Si                                                                                                                                                                                                                           |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10μA, CC2=50μA, and 500μA. (b) PL measured at room temperature for ZnO nano-islands deposited on Si substrate. (c) AES Zn elemental map and (d) SEM image accordingly. (e) AES spectra of                                                                                                                                                       |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10 $\mu$ A, CC2=50 $\mu$ A, and 500 $\mu$ A. (b) PL measured at room temperature for ZnO nano-islands deposited on Si substrate. (c) AES Zn elemental map and (d) SEM image accordingly. (e) AES spectra of Zn LMM for the spot in (c) and (d). (f) Height cross-section profiles corresponding to the                                          |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10μA, CC2=50μA, and 500μA. (b) PL measured at room temperature for ZnO nano-islands deposited on Si substrate. (c) AES Zn elemental map and (d) SEM image accordingly. (e) AES spectra of Zn LMM for the spot in (c) and (d). (f) Height cross-section profiles corresponding to the black dash line in (g) AFM image for four different states |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10μA, CC2=50μA, and 500μA. (b) PL measured at room temperature for ZnO nano-islands deposited on Si substrate. (c) AES Zn elemental map and (d) SEM image accordingly. (e) AES spectra of Zn LMM for the spot in (c) and (d). (f) Height cross-section profiles corresponding to the black dash line in (g) AFM image for four different states |

| Figure 6-4. (a) Bipolar resistive switching behavior with CC1=10μA, CC2=50μA, and 500μA. (b) PL measured at room temperature for ZnO nano-islands deposited on Si substrate. (c) AES Zn elemental map and (d) SEM image accordingly. (e) AES spectra of Zn LMM for the spot in (c) and (d). (f) Height cross-section profiles corresponding to the black dash line in (g) AFM image for four different states |

| electroforming (EF), SET (S), and RESET (RS) voltages for different ZnO nano-island                |

|----------------------------------------------------------------------------------------------------|

| resistive memories. (f) Histogram of $R_{\rm OFF}/R_{\rm ON}$ for different nano-scale resistive   |

| memories. Inset: The relationship between resistance and diameter of the ZnO nano-                 |

| islands for both ON- and OFF-states79                                                              |

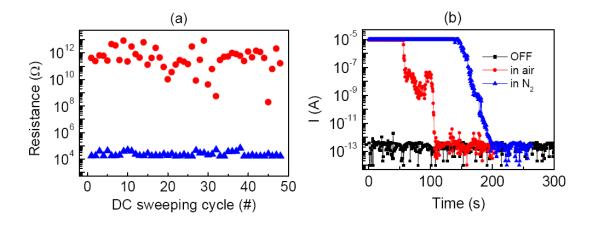

| Figure 6-6. (a) Endurance and (b) retention results of ZnO nano-island82                           |

| Figure 6-7. (a) AFM height image recorded in air on a ZnO nano-island on Si substrate              |

| for initial state. (b) $\sim$ (f) Local current distributions of a nano-scale resistive memory for |

| four different states: (b) initial, (c) electroformed, (d) OFF, and (e)-(f) two ON-states84        |

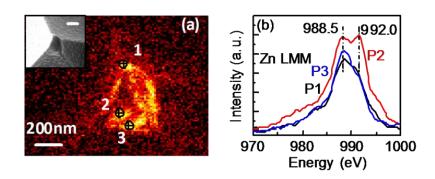

| Figure 6-8. (a) AES Zn map of a C-AFM tip after electrical measurement, inset: top-view            |

| SEM image of this tip. (b) HSR-AES high energy resolution spectra of Zn LMM from the               |

| three spots with diameters of 10nm marked in (a) for this C-AFM tip85                              |

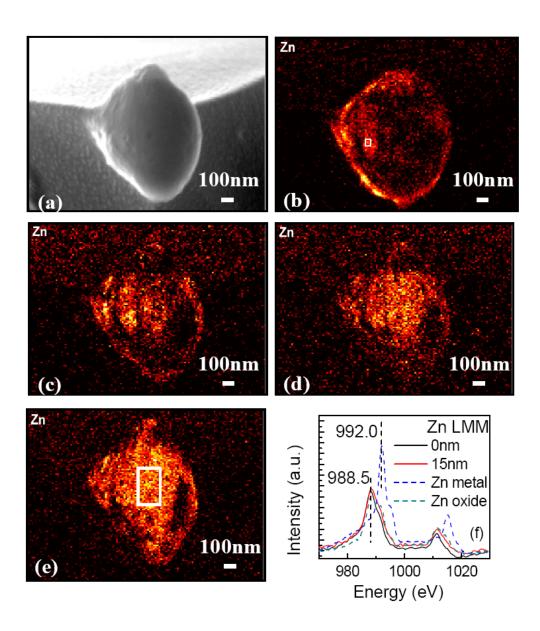

| Figure 6-9. (a) Top-view SEM image of an over-used tip. AES Zn map of the over-used                |

| C-AFM tip: (b) before sputter etching, and after sputter etching of (c) 3nm, (d) 10nm, and         |

| (e) 15nm coated material. (f) XAES spectra of Zn LMM for the square areas in (b) and               |

| (e), XAES spectra for standard Zn-metal and Zn-oxide are also shown for reference86                |

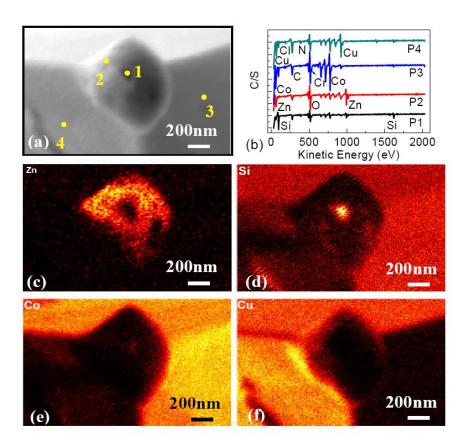

| Fig.6-10 (a) Top-view SEM image of an over-used tip after sputter etching of 40nm                  |

| coated material. (b) AES spectra obtained in location P1, P2, P3, and P4 with diameters            |

| of 10nm, corresponding to the SEM image in (a). (c) Zn, (d) Si, (e) Co, (f) Cu AES map             |

| of the over-used tip after sputter etching of 40nm coated material                                 |

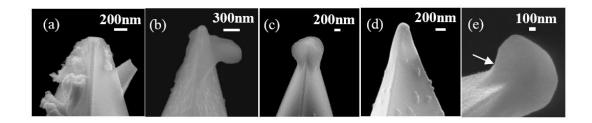

| Figure 6-11. SEM images of three types of used C-AFM tips. C-AFM tip contaminated                  |

| with particulates during AFM and C-AFM mapping (a) before (b) after I-V                            |

| characterization, (c) over-used, and (d) used C-AFM tip. (e) Side-view SEM image of the |

|-----------------------------------------------------------------------------------------|

| over-used tip                                                                           |

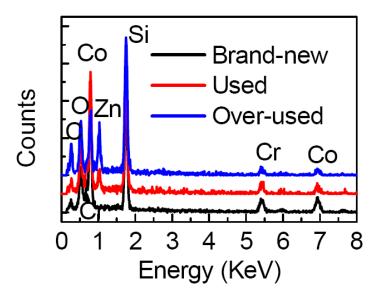

| Figure 6-12. EDX analysis of the new (black), used (red), and over-used (blue)          |

| tips89                                                                                  |

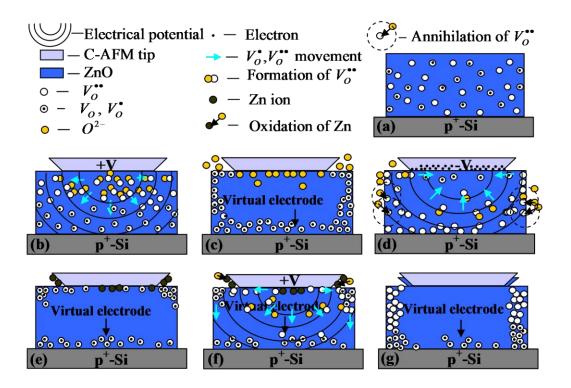

| Figure 6-13. Schematic illustration of the resistive switching mechanism of the ZnO     |

| nano-island resistive memory: (a) homogeneously conductive initial state, (b)           |

| electroforming process for oxygen vacancy generation and filament formation by          |

| movement of oxygen ions or oxygen vacancies, (c) electroformed state, (d) RESET         |

| process for oxygen vacancy annihilation and filament rupture by moving oxygen ions to   |

| V <sub>O</sub> , (e) OFF state, (f) SET process, and (g) ON state93                     |

## **Chapter 1: Introduction**

#### 1.1 Introduction to flash

In the field of electronic storage based on complementary metal oxide semiconductor technology there are two main types of memories. First is volatile memory such as random access memory (RAM) that retains a bit of information for a short amount of time and requires intermittent refreshing to retain that same bit for longer periods. There are several types of volatile memories in use such as static-RAM that has really fast write and erase speeds and it is used as cache in central processing units. Due to the use of six transistors per SRAM cell however this memory is only used in applications where speed and not cost is the main concern. For larger storage, yet volatile performance capabilities, there is dynamic-RAM. This memory is used as temporary storage in computers. It consists of a transistor and a capacitor combination and can be made cheaper than SRAM. Since both memory technologies are volatile, once the power is turned off, all the stored information is lost. For longer, non-volatile electronic storage other technologies are used such as flash memory.

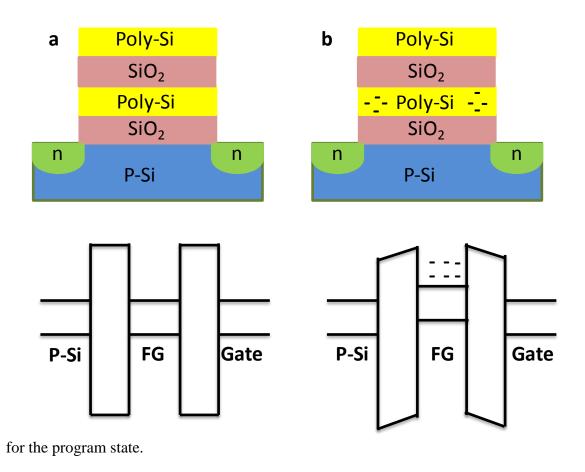

Flash memory, also known as floating gate memory is composed of a single metal oxide semiconductor field effect transistor (MOSFET) that has an extra insulated gate between the control gate and channel. This floating gate has the ability to store charge and change the characteristics of the transistor. Specifically, the stored charge changes the threshold voltage. This means that when device is programmed, when an excess of electrons are present in the floating gate, then the threshold voltage increases in the positive direction. The reason for this is that the field from the floating gate competes

with the electric field of the control gate. To achieve programming and erasing procedures into the floating gate, the electrons are tunneled through the oxide separating the channel and the floating gate. The schematic and respective energy band diagram of the floating gate structures are shown in figure 1-1(a) for the initial state and figure 1-1(b)

Figure 1-1. Schematic cross section of a floating gate transistor and energy band diagram for the (a) initial state and (b) programmed state.

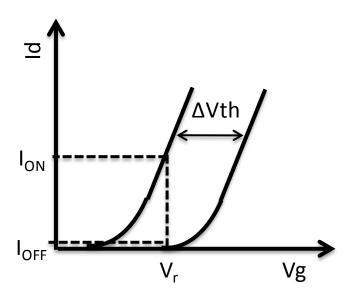

To read the two states in the memory cell, a reading voltage is supplied and the resulting current is measured at the drain. For the programmed state with an n-type transistor the reading current should be near 0 or  $I_{OFF}$ . While after erase there should be a detectable current ( $I_{ON}$ ) as shown in figure 1-2.

Figure 1-2. I-V curves of a floating gate device when there is no charge stored ( $I_{ON}$ ) and when there is negative charge stored ( $I_{OFF}$ ).

It is not a simple task to transfer charge from the channel to the floating gate. There are several methods of tunneling that are used in programming and erasing for different floating gate technologies. The first one is hot electron injection which is generally used in programming and consists of putting a lateral field between the source and drain that heats up the electrons in the channel while also adding a field from the

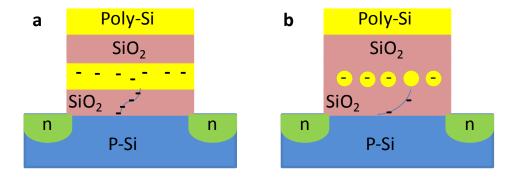

control gate that will attract the electrons into the floating gate. The second method is called Fowler-Nordheim (FN) tunneling. This method consists of putting a high electric field to the control gate while leaving the source and drain either floating or grounded. The high field would lower the oxide barrier width and make it into a triangular shape. This will increase the probability of electron tunneling through the oxide. Since both mechanisms involve electrons passing through the oxide layer, there is no surprise that this layer is the most important and most likely to fail part of the device. A typical oxide failure is the development of leakage sites within the oxide that set a path for electrons that are stored in the floating gate to be released into the channel. A simple solution for this is the use of nanocrystals (NC) as the floating gate instead of a continuous floating gate. The main advantage of NCs is the discretization of charge. So that when a leakage site appears on the tunnel oxide only a small part of the charge is lost and the whole device is not rendered useless. This is depicted in figure 1-3(a) for a continuous floating gate and figure 1-3(b) for a NC floating gate.

Figure 1-3. Schematic representation of a leakage site in (a) a countinous floating gate and (b) NC floating gate transistor memory.

# 1.2 Introduction to NC floating gate memory

To scale flash memory to ever smaller dimensions the thickness of the oxide needs to also be decreased. As the oxide decreases in thickness the durability is compromised. NC floating gate memory has the advantage of having discrete charge distribution that increases the stability and endurance of flash memory. This leads to thinner oxide thicknesses that would not be reliable under a continuous floating gate. In addition, the NCs would be able to affect the channel with as little as one electron per NC. This would also lead to lower power consumption and higher speeds.<sup>3-7</sup> Other ways of implementing NCs have been with MOS capacitor structures, 8-10 as well as with other semiconductors, such as Ge, 9-12 instead of Si, and metals. 13-28 Also, different methods can be used to grow the NCs such as ion implantation, CVD, MBE and sputtering.<sup>8-9,28-30</sup> Since damage to the tunneling oxide is detrimental to memory characteristics, methods such as ion implantation and sputtering that can damage the oxide layer are avoided in favor of CVD and MBE. A major focus for the improvement of NC memory has been density. The higher the density of the NCs, the more charge can be stored and the faster the memory can be switch from one state to another. CVD techniques have been able to reach high densities of 10<sup>11</sup>-10<sup>12</sup> NCs/cm<sup>2</sup> with Si NCs<sup>31-33</sup> and silicide NCs<sup>34-38</sup>. The growth mechanism for CVD grown NCs on oxide starts with introducing a reactive gas, such as silane (SiH<sub>4</sub>), with a heated substrate. On the surface of the substrate the silane breaks into Si adatoms and diffuses until it finds a seed site or trap. Once settled other atoms attach to the seed and the NC forms. Controlling the seed mechanism or the trap sites is a way to increase or decrease density. In the case of CNT alignment, the surface

energy difference between the flat areas and the mesas act as a trap, inducing preferential NC growth.

## 1.3 References

- [1] Pavan, P.; Bez, R.; Olivo, P.; Zanoni, E.; , "Flash memory cells-an overview," Proceedings of the IEEE, vol.85, no.8, pp.1248-1271, Aug 1997

- [2] Bez, R.; Camerlenghi, E.; Modelli, A.; Visconti, A.; , "Introduction to flash memory," Proceedings of the IEEE, vol.91, no.4, pp. 489-502, April 2003

- [3Tiwari, S.; Rana, F.; Chan, K.; Hanafi, H.; Wei Chan; Buchanan, D.; , "Volatile and non-volatile memories in silicon with nano-crystal storage," Electron Devices Meeting, 1995., International, vol., no., pp.521-524, 10-13 Dec 1995 Tech. Dig. 521 (1995).

- [4]A silicon nanocrystals based memory Sandip Tiwari, Farhan Rana, Hussein Hanafi, Allan Hartstein, Emmanuel F. Crabbe, and Kevin Chan, Appl. Phys. Lett. 68, 1377 (1996)

- [5] Hanafi, H.I.; Tiwari, S.; Khan, I.; , "Fast and long retention-time nano-crystal memory," Electron Devices, IEEE Transactions on , vol.43, no.9, pp.1553-1558, (1996)

[6] Single charge and confinement effects in nano-crystal memories Sandip Tiwari,

- Farhan Rana, Kevin Chan, Leathen Shi, and Hussein Hanafi, Appl. Phys. Lett. 69, 1232 (1996)

- [7] De Blauwe, J.; "Nanocrystal nonvolatile memory devices," Nanotechnology, IEEE Transactions on , vol.1, no.1, pp.72-77, Mar 2002

- [8] Nanocrystal metal-oxide-semiconductor memories obtained by chemical vapor deposition of Si nanocrystals, G. Ammendola, M. Vulpio, M. Bileci, N. Nastasi, C. Gerardi, G. Renna, I. Crupi,

- G. Nicotra, and S. Lombardo, J. Vac. Sci. Technol., B 20, 2075 (2002).

- [9] Structural and electrical properties of silicon dioxide layers with embedded germanium nanocrystals grown by molecular beam epitaxy A. Kanjilal, J.L. Hansen, P. Gaiduk, A.N. Larsen, N. Cherkashin, A. Claverie, P. Normand, E. Kapelanakis, D. Skarlatos, and D. Tsoukalas, Appl. Phys. Lett. 82, 1212 (2003).

- [10] Size control and charge storage mechanism of germanium nanocrystals in a metal-insulator-semiconductor structure L. W. Teo, W. K. Choi, W. K. Chim, V. Ho, C. M. Moey, M. S. Tay, C. L. Heng, Y. Lei, D. A. Antoniadis, and E. A. Fitzgerald, Appl. Phys. Lett. 81, 3639

- [11] MOS memory using germanium nanocrystals formed by thermal oxidation of Sil-xGex, Y. C. King, T. J. King, and C. Hu, IEEE IEDM Tech. Dig. 115 (1998).

- [12] Charge storage and photoluminescence characteristics of silicon oxide embedded Ge nanocrystal trilayer structures, K. Das, M. N. Goswami, R. Mahapatra, G. S. Kar, H. N. Acharya, S. Maikap, J. H. Lee, and S. K. Ray, Appl. Phys. Lett. 84, 1386 (2004).

- [13] Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron. Devices 49, 1606 (2002).

- [14] Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron. Devices 49, 1614 (2002).

- [15] C. Lee, A. Gorur-Seetharam, and E. C. Kan, IEEE IEDM Tech. Dig. 557 (2003).

- [16] J. Y. Tseng, C. W. Cheng, S. Y. Wang, T. B. Wu, K. Y. Hsieh, and R. Liu, Appl. Phys. Lett. 85, 2595 (2004).

- [17] M. Takata, S. Kondoh, T. Sakaguchi, H. Choi, J. C. Shim, H. Kurino, and M. Koyanagi, IEEE IEDM Tech. Dig. 553 (2003).

- [18] T. C. Chang, P. T. Liu, S. T. Yan, and S. M. Sze, Electrochem. Solid-State Lett. 8, G71 (2005).

- [19] Y. H. Lin, C. H. Chien, C. T. Lin, C. Y. Chang, and T. F. Lei, IEEE Trans. Electron. Device Lett. 26, 154 (2005).

- [20] S. Choi, S. S. Kim, M. Chang, H. Hwang, S. Jeon, and C. Kim, Appl. Phys. Lett. 86, 123110 (2005).

- [21] Y. Liu, T.P. Chen, P. Zhao, S. Zhang, S. Fung, and Y.Q. Fu, Appl. Phys. Lett. 87, 033112 (2005).

- [22] Z. Tan, S. K. Samanta, W. J. Yoo, and S. Lee, Appl. Phys. Lett. 86, 013107 (2005).

- [23] J. J. Lee, Y. Harada, J. W. Pyun, and D. L. Kwong, Appl. Phys. Lett 86, 103505 (2005).

- [24] J. J. Lee, and D. L. Kwong, IEEE Trans. Electron. Devices 52, 507 (2005).

- [25] P. H. Yeh, C. H. Yu, L. J. Chen, H. H. Wu, P. T. Liu, and T. C. Chang, Appl. Phys. Lett. 87, 193504 (2005).

- [26] J. H. Kim, J. Y. Jin, J. H. Jung, I. Lee, T. W. Kim, S. K. Lim, C. S. Yoon, and Y. -H. Kim, Appl. Phys. Lett. 86, 032904 (2005).

- [27] S. Paul, C. Pearson, A. Molloy, M. A. Cousins, M. Green, S. Kolliopoulou, P. Dimitrakis, P. Normand, D. Tsoukalas, and M. C. Petty, Nano Lett. 3, 533 (2003).

- [28] A. Chandra, and B. M. Clemens, Appl. Phys. Lett. 87, 253113 (2005).

- [29] Silicon nanocrystal based memory devices for NVM and DRAM applications R. A.

- Rao, R. F. Steimle, M. Sadd, C. T. Swift, B. Hradsky, S. Straub, T. Merchant, M. Stoker,

- S. G. H. Anderson, M. Rossow, J. Yater, B. Acred, K. Harber, E. J. Prinz, B. E. White Jr., and R. Muralidhar, Solid-State Electron. 48, 1463 (2004).

- [30] Memory properties of Si+ implanted gate oxides: from MOS capacitors to nvSRAM, J. von Borany, T. Gebel, K.-H. Stegemann, H.-J. Thees, and M. Wittmaack, Solid-State Electron. 46, 1729 (2002).

- [31] F. Mazen, T. Baron, G. Bremond, N. Buffet, N. Rochat, P. Mur, and M. N. Semeria, J Electrochem Soc, 150, G203 (2003).

- [32] S. Madhukar, K. Smith, R. Muralidhar, D. O'Meara, M. Sadd, B. -Y. Nguyen, B. White, and B. Jones, Mater Res Soc Symp Proc, 638, F.5.2.1, (2001).

- [33] T. Baron, A. Fernandes, J. F. Damlencourt, B. De Salvo, F. Martin, F. Mazen, and S. Haukka, Appl Phys Lett., 82, 4151 (2003).

- [34]"High-density NiSi nanocrystals embedded in Al2O3/SiO2 double-barrier for robust retention of nonvolatile memory" Jingjian Ren, Bei Li, Jian-Guo Zheng, and Jianlin Liu Solid-State Electronics 67, 23(2012)

- [35] "Vapor-solid-solid growth of NiSi2 nanocrystals for memory applications" Bei Li, Jianlin Liu, Reuben D. Gann, Jory A. Yarmoff, and Yu Zhu, IEEE Transactions on Nanotechnology 10, 1120(2011)

- [36] "TiSi2 nanocrystal metal oxide semiconductor field effect transistor memory" Huimei Zhou, Bei Li, Zheng Yang, Ning Zhan, Dong Yan, Roger K. Lake, and Jianlin Liu IEEE Transactions on Nanotechnology 10, 499(2011)

- [37] "Synthesis of high-density PtSi nanocrystals for memory applications" Bei Li, Jingjian Ren and Jianlin Liu Appl. Phys. Lett. 96, 172104(2010)

- [38] "CoSi2-coated Si nanocrystal memories" Bei Li, and Jianlin Liu J. Appl. Phys. 105, 084905(2009)

# **Chapter 2: Methodology**

# 2.1 Nanocrystal growth

## 2.1.1 Si nanocrystal growth

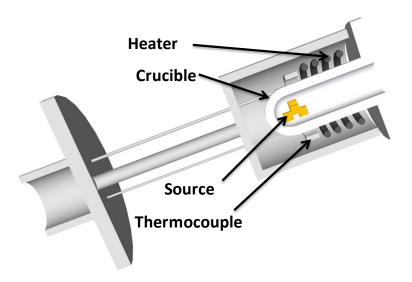

For the growth of silicon NCs on oxide covered CNTs I designed and built a gas source molecular beam epitaxy system (GSMBE). This system consists of two different vacuum chambers separated by a gate valve. The growth chamber is pumped by a turbo molecular pump capable of pumping 170ls<sup>-1</sup> of nitrogen and it is also backed by scroll pump capable of pumping 10m<sup>3</sup>h<sup>-1</sup>. The transfer chamber is only pumped by a scroll pump. The typical vacuum achieved before growth was about  $2\times10^{-8}$ torr. The vacuum is measured first by thermocouple gauges that read pressures starting from atmosphere to 1×10<sup>-3</sup>torr. Then a Bayard-Alpert ionization gauge is used from ~10<sup>-4</sup> to maximum vacuum. The loading procedures for a typical growth begin by introducing the sample to the inside of the transfer chamber in atmosphere and placing it in a holder that attaches to the transfer rod. After the sample is in place, the chamber door is sealed and the chamber is evacuated. Once the set vacuum is reached the gate valve is opened and the sample is transferred to the growth chamber. Inside the growth chamber the sample detaches from the transfer rod while at the same time attaching to the manipulator for growth. The manipulator uses a resistive heater behind the sample to provide heat and raise the sample temperature for growth. In between the heater and the sample lies a C-type thermocouple wire that measures temperature. This wire is calibrated by an outside pyrometer.

For Si/Ge growth the sources used are disilane (Si<sub>2</sub>H<sub>6</sub>) and digermane (Ge<sub>2</sub>H<sub>6</sub>). At high temperatures both gases break into their respective components. The gas lines are

evacuated before every growth to prevent contamination. A mass flow controller controls the gas flow between the low pressure line and the high vacuum chamber. The gas source is introduced to the growth chamber in a direct path to the sample so that even source coverage is reached. Additional features of the GSMBE include a solid source effusion cell; which consists of a tubular resistive heater with a boron nitride crucible in the middle of it that contains the solid source, as shown in figure 2-1. The use of this source is to heat the material inside the crucible to the point of sublimation. The source vapor will then be directed towards the sample because the cell is pointed in a direct path towards it. Also, there is a gas source cracker, which consists of two resistive tubular heaters protected by a boron nitride tube. This addition is used to crack the bonds of a gas passing inside by exposing to large amounts of heat. The gas used in combination with the cracker is acetylene  $(C_2H_2)$  for the growth of graphene. This growth, however, will not be discussed.

Figure 2-1. Effusion cell schematic

Initial growths were performed on SiO<sub>2</sub> surfaces. Growth temperatures were between 500°C and 700°C. It was evident that Ge NCs grew faster than Si NCs on the surface. As seen in figure 2-2. The slower and more controlled Si growth would then be chosen as the material for the use in the alignment experiments.

Figure 2-2. Examples of Ge and Si growths; Images were taken by AFM.

# 2.1.2 ZnO nanocrystal growth

ZnO NCs were grown on a plasma assisted MBE system. The process of growing ZnO NC starts with a clean Si wafer. The reaction consists of a beam of elemental Zn that oxidizes in contact with O that has been previously cracked in the plasma chamber. It will be dicussed in more detail in chapter 6.

# 2.2 Nanocrystal characterization

## 2.2.1 AFM characterization

Atomic force microscopy was developed in the 1980's by Gerd Binning and Calvin Quate and Christoph Gerber. This tool has the ability to detect surface topography at the nanoscale. It uses a mechanical probe sustained by a cantilever. The probe is in contact with the sample and interacts with it through van der walls force. The back of the cantilever is coated with a reflective material so that a laser directed to it can be reflected. On the other side of this reflection, a photodetector is used to track the movements of the laser as shown in figure 2-3. The movement of the laser spot on the photodetector is directly proportional to the movement of the cantilever as it moves across the surface of the sample. This movement is achieved by the deformation of piezoelectric actuators that precisely control the tip movements to less than a nanometer in distance.

Figure 2-3. AFM mechanism schematic in contact mode.

The AFM has three main operation modes: contact mode, non-contact mode and tapping mode. Contact mode is the easiest mode of operation to understand, it was also the first to be developed. Contact mode is also widely used for measurements that require physical contact such as conductive AFM, lateral force AFM and piezoelectric force AFM. Contact mode measures the surface by scanning the tip back and forth on its x-axis then moving its y axis and so forth. The image is created as the laser deflection is detected from tip movement caused by surface corrugations. This however causes the tip to apply different forces to the surface as it moves through it because of the different bend angles of the cantilever with different distances between the tip and surface. A solution is to track the force the tip imposes on the surface by using a constant force mode. For which the tip's height is constantly adjusted to maintain a constant deflection. It is this adjustment that is displayed as height data and composes the images. A feedback circuit is needed to properly make adjustments as the tips moves across the surface. The ability to track the surface in this manner is limited by the feedback circuit speed. If the tip scan mode does not use height adjustment, it will only measure the deflection. This is useful for small area, high-speed scans that can reach atomic resolution. This technique is known as variable-deflection mode. However, because the tip is in direct contact with the surface, the stiffness of the cantilever needs to be less than the effective spring constant holding atoms together, which is on the order of 1 - 10 nN/nm. Most contact mode cantilevers have a spring constant of < 1N/m.

Non-contact mode as it name entail is not in contact with the surface. It belongs to a family of AC modes, which refers to the use of an oscillating cantilever. A stiff

cantilever is oscillated in the attractive force regime (fig. 2-4), meaning that the tip is quite close to the sample, but not touching it, just enough to be affected by Van der Waals forces. The forces between the tip and sample are quite low, on the order of pN (10<sup>-12</sup> N). The detection scheme is based on measuring changes to the resonant frequency or amplitude of the cantilever.

Figure 2-4. Force curve as a measure of distance. As the tip gets closer to the sample, the tip will have an attractive force towards the sample. Until the sample and tip touch each other then the tip and the sample would have a repulsive force upon them.

In tapping mode a stiff cantilever is oscillated closer to the sample than in noncontact mode. Part of the oscillation's amplitude extends into the repulsive regime, so effectively the tip intermittently taps the surface. Very stiff cantilevers are typically used, as tips can get attached in the water contamination layer. The advantage that tapping mode has is that the lateral resolution on soft samples is improved. Lateral forces such as drag, common in contact mode, are virtually eliminated. For poorly adsorbed specimens on a substrate the tapping mode advantage is clearly seen because in contact mode the tip might move that sample. All of the CNT NC sample topographies are measured in tapping mode; while the ZnO NC samples are measured in contact mode.

# 2.2.2 SEM characterization

Figure 2-5. Schematic drawing of the SEM electron optics

The scanning electron microscope (SEM) is a microscope that uses electrons instead of light to form an image. A beam of electrons is produced at the top of the microscope by an electron gun composed commonly by a Ta filament and an anode. The electron beam follows a straight vertical path through the microscope, which has to be held within a vacuum. The beam travels through electromagnetic fields and lenses, as seen in figure 2-5, which focus the beam, like its light counterparts, down toward the sample. Once the beam hits the sample, secondary electrons, X-rays and photons are ejected from the sample. These particles are then detected and processed into an image. The scanning electron microscope has many advantages over traditional microscopes. The SEM has a large depth of field, which allows for specimens with large height contrast to be in focus at one time. The SEM also has much higher resolution, so closely spaced specimens bellow the 200nm limit of light microscopes can still be detected at much higher levels. Because the SEM uses electromagnets rather than lenses, the researcher has much more control in the degree of magnification. All of these advantages, as well as the actual strikingly clear images, make the scanning electron microscope one of the most useful instruments in research today.

#### 2.2.3 TEM characterization

The transmission electron microscope (TEM) uses a higher energy electron beam than an SEM (>100 kV) transmitted through a very thin sample to image and analyze the structure of materials with atomic scale resolution. The electron beam is focused with electromagnetic lenses and the image is observed on a fluorescent screen, or recorded with a digital camera. The electrons are accelerated to several hundred kV, giving them

wavelengths much smaller than that of light: 200kV electrons have a wavelength of 0.025Å. However, whereas the resolution of the optical microscope is limited by the wavelength of light, that of the electron microscope is limited by aberrations inherent in electromagnetic lenses, to about 1-2 Å.

Because it is almost impossible to look trough a single layer of atoms, is it unlikely that TEM images would yield images of individual atoms. Rather for high resolution TEM images that show the crystal lattice of a material it is actually the interference pattern between the transmitted and diffracted beams. This imaging mode allows us to observe planar and line defects, grain boundaries, interfaces, etc. with atomic scale resolution. The TEM has also the capability of having brightfield/darkfield imaging and diffraction pattern modes, which operate at intermediate magnification. They also provide invaluable information about the morphology, crystal phases, and defects in a material.

#### 2.2.4 AES characterization

In an Auger electron spectroscope (AES) which is part and electron microscope which consists of electrons of energy 3-20keV that are incident upon a conducting sample. These electrons cause bound electrons from atoms contained in the material to be ejected resulting in a photoelectron and an atom with a core hole. The atom then relaxes by capturing an electron with a lower binding energy that drops into the core hole. The energy thus released by the electron captured is converted into an X-ray or causes a second electron to be emitted. This electron is called an Auger electron after Pierre Auger who discovered this relaxation process. After the emission of the Auger electron, the

atom is left in a doubly ionised state. The energy of the Auger electron is characteristic of the element that emitted it, and can thus be used to identify the element. The short inelastic mean free path of Auger electrons in solids ensures the surface sensitivity of AES.

AES is a popular technique for determining the composition of the top few layers of a surface. It cannot detect hydrogen or helium, but is sensitive to all other elements, being most sensitive to the low atomic number elements. AES must be carried out in ultra high vacuum (UHV) conditions. A popular method of looking at buried layers with AES is to use the technique in combination with ion millling. This is also common to do when a sample is brought into the UHV environment from air, because it will be coated with carbon compounds and oxygen. These materials have to be removed (usually by sputtering) before a clean surface can be achieved and studied. Sputtering involves directing a beam of plasma ions (usually Ar, Cs or O ions) at between 500eV and 5keV at the sample. This process cleans the surface, but can also be used to erode away the sample to reveal structure beneath the surface. This is obviously a destructive technique.

#### 2.3 Nanocrystal device fabrication

#### 2.3.1 ALD deposition

Atomic layer deposition (ALD) is a self-limiting, sequential surface chemistry technique that deposits conformal thin-films of materials onto substrates of varying compositions. ALD is similar in chemistry to chemical vapor deposition (CVD), except that the ALD reaction breaks the CVD reaction into two half-reactions, keeping the precursor materials separate during the reaction. Due to the characteristics of self-limiting

and surface reactions, ALD film growth makes atomic scale deposition control possible. By keeping the precursors separate throughout the coating process, atomic layer control of film growth can be obtained as fine as ~0.1 Å (10 pm) per cycle. Separation of the precursors is accomplished by pulsing a purge gas (Ar/N<sub>2</sub>) after each precursor pulse to remove excess precursor from the process. Figure 2-6 shows a typical deposition cycle of Al<sub>2</sub>O<sub>3</sub> using both water and AlCl<sub>4</sub> as the precursors.

Figure 2-6. ALD deposition process. First water is pulsed from the source to the growth chamber, then a set time is waited until the substrate surface is fully covered. After that time has passed, the remaining water is pumped out and the  $AlCl_4$  sourced is pulsed in. The second precursor reacts with the water to create HCl. After the next water pulse the first layer of  $Al_2O_3$  is formed.

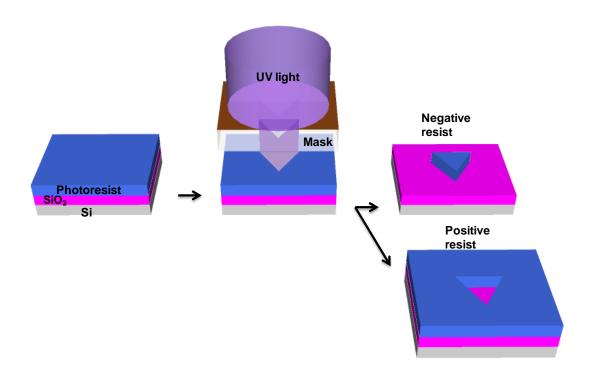

# 2.3.2 Photolithography

Photolithography is the process of transferring geometric shapes on a mask to the surface of a silicon wafer. The steps involved in the photolithographic process are wafer cleaning; barrier layer formation; photoresist application; soft baking; mask alignment; exposure and development; and hard-baking. In the first step, the wafers are chemically cleaned to remove particulate matter on the surface as well as any traces of organic, ionic, and metallic impurities. After cleaning, silicon dioxide, which serves as a barrier layer, is deposited on the surface of the wafer. After the formation of the SiO<sub>2</sub> layer, photoresist is applied to the surface of the wafer. High-speed centrifugal whirling of silicon wafers is the standard method for applying photoresist coatings in IC manufacturing. This technique, known as "spin coating," produces a thin uniform layer of photoresist on the wafer surface. There are two types of photoresist: positive and negative. For positive resists, the resist is exposed with UV light wherever the underlying material is to be removed. In these resists, exposure to the UV light changes the chemical structure of the resist so that it becomes more soluble in the developer. The exposed resist is then washed away by the developer solution, leaving windows of the bare underlying material. The mask, therefore, contains an exact copy of the pattern which is to remain on the wafer.

Negative resists behave in just the opposite manner. Exposure to the UV light causes the negative resist to become polymerized, and more difficult to dissolve. Therefore, the negative resist remains on the surface wherever it is exposed, and the developer solution removes only the unexposed portions. Masks used for negative photoresists, therefore, contain the inverse (or photographic "negative") of the pattern to

be transferred. Figure 2-7 below shows the pattern differences generated from the use of positive and negative resist.

Figure 2-7. Schematic of the photolithography process.

# 2.3.3 E-beam evaporation

In evaporation the substrate is placed inside a vacuum chamber, in which a block of the material to be deposited is also located. The source material is then heated to the point where it starts to boil and evaporate. The vacuum is required to allow the molecules to evaporate freely in the chamber, and they subsequently condense on all surfaces. This principle is the same for all evaporation technologies, only the method used to the heat (evaporate) the source material differs. There are two popular evaporation technologies,

which are e-beam evaporation and resistive evaporation each referring to the heating method. In e-beam evaporation, an electron beam is aimed at the source material causing local heating and evaporation. The material to be evaporated is in the form of single ingots if they are to be melted or in pieces if they are to be sublimated. The electron beams can be generated by thermionic emission, field electron emission or the anodic arc method. The generated electron beam is accelerated to a high kinetic energy and focused towards the ingot. When the accelerating voltage is between 20 kV - 25 kV and the beam current is a few amperes, 85% of the kinetic energy of the electrons is converted into thermal energy as the beam bombards the surface of the ingot. The surface temperature of the ingot increases resulting in the formation of a liquid melt. Although some of incident electron energy is lost in the excitation of X-rays and secondary emission, the liquid ingot material evaporates under vacuum.

# Chapter 3: Periodic Alignment of Si Quantum Dots on Hafnium Oxide Coated Single Wall Carbon Nanotubes

#### 3.1 Introduction

Si QDs are utilized for a wide range of applications including traditional electronics such as memory<sup>1,2</sup>, optoelectronics<sup>3,4</sup>, and biotechnology<sup>5</sup>. Single QD devices have been fabricated to outperform current devices such as field effect transistors<sup>6</sup> for ultra large scale integration. Several options are already available via top-down approaches such as electron beam lithography and nanostamping<sup>7</sup> that can fabricate single QD devices. Another popular method is the growth of QDs via self assembly instead of fabrication. One of the major hurdles in this approach is the alignment of the QDs themselves. Here we demonstrate a solution to Si QD alignment using a hafnium oxide covered SWCNT template.

The template comprises of HfO<sub>2</sub> ridges formed by atomic layer deposition growth of a HfO<sub>2</sub> thin film on SWCNTs on a SiO<sub>2</sub> surface. The major advantage for the use of SWCNTs is in their 1-D shape and nanometer scale diameter, which will enable applications to go beyond the CMOS ultimate limit. The technique of selective area epitaxy<sup>8,9</sup> has reported the alignment of QDs on Si ridges. This technique starts with a top down patterned template, followed by a bottom up growth of QDs. This process requires a smooth surface so that during the QD growth the adatoms can migrate to the lowest energy spots. Traditionally, single crystal surfaces have been used for the alignment of QDs via selective epitaxial growth or QD superlattice growth. The atomic layer

deposition technique can produce HfO<sub>2</sub> thin dielectric films with smooth conformal polycrystalline surfaces, which can be used for QD self assembly<sup>10</sup>. QDs grown on HfO<sub>2</sub> surfaces may have potential applications in nonvolatile nanocrystal memories.

#### 3.2 Experiment

First, SWCNTs were grown on SiO<sub>2</sub>/Si substrates using a chemical vapor deposition technique [11-12]. The nanotube samples were then subjected to an UV cleaning for 5 minutes to make the substrate surface hydrophilic. This time was adjusted to ensure good precursor adhesion as well as keeping the CNTs intact. Following the surface treatment procedure, the samples were introduced to a Cambridge Nanotech Savannah 100 atomic layer deposition chamber. The system ran at a partial pressure of 3x10<sup>-1</sup> torr, and a deposition time of 5 seconds was used for both precursor and source. Substrate temperature for the HfO<sub>2</sub> deposition was kept constant at 250°C. The Si QD deposition was done in a custom built gas source molecular beam epitaxy (GSMBE) system. The disilane  $(Si_2H_6)$  source points directly at the substrate. The base pressure was in the order of 10<sup>-8</sup> torr, while growth pressure was in the range of 10<sup>-5</sup> torr. The samples were heated via a Ta heating coil that coupled with the sample holder. Temperature readings were taken by a thermocouple situated between the sample and the heating coil. The source gas flow was controlled using a mass flow controller (MFC) UFC 1660. AFM characterization was carried out using a Veeco multimode AFM.

#### 3.3 Results

# 3.3.1 Structure description

Figure 3-1(a) shows a schematic of aligned Si QDs on HfO<sub>2</sub> covered CNTs formed by selective epitaxial growth. The QDs are drawn only on the 1-D HfO2 ridge created by the underlying CNTs. Other QDs could be formed on the surrounding flat surface depending on the magnitude of the length of Si adatom migration on HfO2 and the proximity of adjacent CNTs. Figure 3-1(b) shows a cross sectional SEM image of a QD alignment sample. The HfO<sub>2</sub> thickness is 6 nm and the ridge height was measured to be 1nm to 1.2 nm by AFM characterization. QDs are clearly observed to align along the 1-D HfO<sub>2</sub> ridge, while QDs are also seen on the flat surface close to the CNT ridge. The QDs on top of the CNT are larger in size demonstrating that more Si adatoms preferentially migrated to the 1-D ridge. We hypothesized that if the density of CNTs is increased, selective growth of Si dots only on the ridges will be evident. The HfO<sub>2</sub> layer is highly conformal on the SiO2 surface as the shape of the CNT is seen in the SEM image. The CNT surface however is not chemically active 13 so fewer layers are deposited over the ridge than the rest of the film. This characteristic can be advantageous in a circuit setting by utilizing different thicknesses of the oxide film in between CNT channels<sup>14</sup> as the LOCOS equivalent of isolating oxide.

Figure 3-1. Quantum dots on a hafnium oxide covered carbon nanotube. (a) Schematic of a cross sectional view of the structure. (b) SEM image cross-sectional shows aligned QDs on a HfO<sub>2</sub> covered CNT.

# 3.3.2 Reference sample

To ensure that the observed quantum dots on the surface are Si dots rather than HfO<sub>2</sub> grains due to annealing, an experiment comparing the annealed samples before and after disilane flow was introduced. Figure 3-2(a)-(b) shows the AFM images of these samples. Both samples began with the 6 nm HfO<sub>2</sub> covered CNT. The in-situ annealing including ramping from room temperature to 650°C within 2 hours and maintaining at this temperature for 8 minutes was used for both samples. The control sample which was not subjected to disilane growth shows relatively smooth surface, while the sample with disilane flow of 1.6 sccm for 8 minutes shows rough surface with quantum dot alignment.

Figure 3-2. AFM images of HfO<sub>2</sub> covered CNT after in-situ annealing, (a) before and (b) after the introduction of disilane.

### 3.3.3 Flow rate dependence

The growth processes of the selective area epitaxy can be observed clearly through the changes in QD linear density. The QD linear density was obtained via AFM measurement along the CNT ridge. Figures 3-3(a)-(d) show the morphology of the samples grown at different flow rates; a higher rate of disilane flow results in smaller and denser QDs. This is due to the fact that with a higher flow rate there is more source material depositing over the substrate at any given time. More source impingement increases the opportunities for a Si atom to find a high strain point and settle to form a seed, which in turn will form a QD. This behavior has also been observed in QDs grown on HfO<sub>2</sub> patterned surfaces.<sup>10</sup> In contrast, if less Si is deposited then the chances for strain driven alignment are fewer and more QDs start to form over the rest of the substrate as can be seen in Fig. 3-3(a). The size of each image is 200 nm by 200 nm. Due to tip deterioration some of the QDs appear larger in base than the others. Base size is dependent strictly on the size of the ridge created by the CNT since the formation of a

valley at the edges of the CNT is expected to have a greater surface energy. This pattern of size limitation can be seen throughout the different flow rates in the QD growth.

Figure 3-3. AFM image of four samples that were grown at different  $Si_2H_6$  flow rate: a) 1.1sccm, b) 1.6sccm, c) 1.8sccm, d) 2.1sccm.

# 3.3.4 Growth time dependence

Figure 3-4(a)-(d) show the morphology of the samples grown at different growth time. Coincidently the effects of time on the linear density resulted similar to the trend observed with varying flow rate the flow rate. The linear density increases with increasing time at the initial stage. For longer growth time, the QD density starts to decrease. The trend of the increase of linear density continues until the QDs exceed a certain size close to the width of the CNT ridge. The edge of the ridge is the threshold for

the QD growth along the CNT. As the QD size reaches that threshold, the strain created by the CNT is compensated and growth past the edges of the 1-D ridges is accelerated.

Figure 3-4. AFM images of four samples that have different growth times: a) 3 min, b) 5 min, c) 7 min, d)8min.

# 3.3.5 Growth temperature dependence

Figure 3-5(a)-(d) shows the growth temperature effect on the morphology of the dots on CNT. Interestingly different temperatures have a negligible effect on QD density in the window of alignment. Since growth temperature is known to affect adatom diffusion lenght<sup>15,16</sup>, it is reasonable for Si adatoms that are farther from CNT ridges in the initial stages of growth to migrate over to the alignment sites at higher growth temperature. In the examined temperature range, sufficient number of Si adatoms can

migrate to preferential nucleation sites on 1-D HfO<sub>2</sub> ridges on CNTs. Until the strain distribution along the 1-D ridge becomes periodic, this is responsible for periodic aligned QDs. Such "cooperative" regimented growth mode was also observed when Ge dots were grown on 1-D Si ridges<sup>8</sup>. This correlates with our low temperature results (not shown here) that show no alignment due to a low diffusion length. Another reason for a constant density with respect to temperature is that surface desorption of Si adatoms also increases with respect to temperature<sup>10</sup>. All of the linear densities are calculated and summarized in figure 3-6.

Figure 3-5. AFM images of four samples that have different growth temperatures: a) 640°C, b) 650°C, c) 670°C, d) 680°C

Figure 3-6. Linear density of QDs on CNTs as a function of a) flow rate, b) growth time, and c) growth temperature.

# 3.3.6 Oxide thickness dependence

To study different strain conditions created by the underlying CNT, we varied the oxide thickness. The effects created by the increase in oxide thickness can be seen in Fig. 3-7(a)-(d). The thicker the oxide is, the sharper QDs are around the CNT ridge. This is due to the relaxation of the strain that forms along the top of the ridge structure. This in turn will decrease the selectivity of Si adatoms, forming more QDs on flat areas of the substrate. Although atomic layer deposition is conformal to most surfaces, CNTs are known to be non-reactive to the H<sub>2</sub>O precursor<sup>13</sup>. Therefore many more HfO<sub>2</sub> layers are needed to be deposited to fully cover the CNT and have a smooth surface for good Si migration. The window of selectivity starts close to the 6 nm mark and decreases after 1

to 2 nm depending on the size of the ridge, which is dependent on the diameter of the CNT.

Figure 3-7. AFM images of four samples that have different hafnium oxide thickness: a) 6 nm, b) 7 nm, c) 7.6 nm, d) 8 nm.

#### 3.4 Conclusion

In summary, we have successfully aligned Si QDs on strained HfO<sub>2</sub> covered CNTs. We studied the effects of growth temperature, disilane flow rate, and oxide thickness on the density of the QDs on the 1-D HfO<sub>2</sub> ridges created by the underlying CNTs. We found that the size of the ridge created by the CNT dictates the maximum size of the QDs but the effect is diminished with the increase of the oxide thickness. In addition, the changes in disilane flow rate and growth time showed that the density of the QDs on the ridges can be controlled as well as the QD deposition outside of the ridges.

These results show that the alignment of QDs by a bottom up approach to a size beyond CMOS ultimate limit is possible and controllable.

# 3.5 References:

- (1) D.W. Kim, T. Kim, and S.K. Banerjee, IEEE Transactions on Elec. Dev. **50**, 1823 (2003).

- (2) J.J. Lee, X. Wang, W. Bai, N. Lu, and D.L. Kwong, IEEE Transactions on Elec. Dev. **50**, 2067 (2003).

- (3) N.M. Park, T.S. Kim, and S.J. Park, Appl. Phys. Lett. **78**, 2575 (2001).

- (4) Z.T. Kang, B. Arnold, C.J. Summers, and B.K. Wagner, Nanotechnology **17**, 4477 (2006).

- (5) F. Erogbogbo, K.T. Yong, I. Roy, G. Xu, P.N. Prasad, and M.T. Swihart, ACS Nano 2, 873 (2008).

- (6) S.J. Angus, A.J. Ferguson, A.S. Dzurak, and R.G. Clark, Nano Lett. 7, 2051 (2007).

- (7) C. Taylor, E. Marega, E.A. Stach, G. Salamo, L. Hussey, M. Muñoz, and A. Malshe, Nanotechnology 19, 1 (2008).

- (8) G. Jin, J.L. Liu, S.G. Thomas, Y.H. Luo, K.L. Wang, and B.Y. Nguyen, Appl. Phys. Lett. **75**, 2752 (1999).

- (9) G. Jin, J.L. Liu, and K.L. Wang, Appl. Phys. Lett. **76**, 3591 (2000).

- (10) S.S. Coffee, and J.G. Ekerdt, J. Appl. Phys. **102**, 4912 (2007).

- (11) S. Han, X. Liu, and C. Zhou, J. Am. Chem. Soc. 127, 5294 (2005).

- (12) P. Jarillo-Herrero, J.A. Van Dam, and L.P. Kouwenhoven, Nature 439, 953 (2006).

- (13) A. Javey, J. Guo, D.B. Farmer, Q. Wang, E. Yenilmez, R.G. Gordon, M. Lundstrom, and H. Dai, Nano Lett. 4, 1319 (2004).

- (14) S.J. Tans, M.H. Devoret, H. Dai, A. Thess, R.E. Smalley, L.J. Geerligs, and C. Dekker, Nature 386, 474 (1997).

- (15) J. Tershoff, C. Teichert, and M.G. Lagally, Phys. Rev. Lett. 76, 1675 (1996).

- (16) Q. Xie, A. Madhukar, P. Chen, and N.P. Kobayashi, Phys. Rev. Lett. **75**, 2542 (1995).

Chapter 4: Carbon Nanotube Memory by the Self-Assembly of Silicon Nanocrystals as Charge Storage Nodes

#### 4.1 Introduction