# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Comprehensive Reduction of Real and Complex Distribution Feeder Models

#### **Permalink**

https://escholarship.org/uc/item/57m7j89t

#### **Author**

Pecenak, Zachary K.

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# **Comprehensive Reduction of Real and Complex Distribution Feeder Models**

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Engineering Sciences (Mechanical Engineering)

by

Zachary K. Pecenak

### Committee in charge:

Professor Jan Kleissl, Chair Professor Raymond De Callofan Professor Hamed Mohsenian-Rad Professor Tajana Ŝimunic Rosing Professor Paul Yu

Copyright

Zachary K. Pecenak, 2018

All rights reserved.

| The dissertation of Zachary K. Pecenak is approved, and it is |

|---------------------------------------------------------------|

| acceptable in quality and form for publication on microfilm   |

| and electronically:                                           |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

| Chair                                                         |

University of California, San Diego

2018

#### **DEDICATION**

This thesis is dedicated to anyone who is underprivileged, under-educated, or oppressed but knows there is something bigger for them. You can accomplish anything or be anyone if you put in the required time. You are not trapped where you are now. Fight to make the world a place you want to live in. Don't let anyone stop you.

### **EPIGRAPH**

The person who acquires the ability to take full possession of their mind

may take possession of anything else to which they are justly entitled.

—Andrew Carnegie

## TABLE OF CONTENTS

| Signature Pag  | ge     |                | ii |

|----------------|--------|----------------|----|

| Dedication .   |        |                | iv |

| Epigraph       |        |                | V  |

| Table of Cont  | ents . |                | vi |

| List of Figure | s      |                | ix |

| List of Tables |        |                | ii |

| Acknowledge    | ments  | s              | ii |

| Vita           |        |                | V  |

| Abstract of th | e Diss | sertation      | vi |

| Chapter 1      | Intro  | oduction       | 1  |

|                |        |                | _  |

| Chapter 2      |        | 1              | 6  |

|                | 2.1    |                | 6  |

|                | 2.2    | , 11           | 0  |

|                |        | 1              | 0  |

|                |        |                | 1  |

|                |        | V 1            | 3  |

|                |        | V 1            | 3  |

|                | 2.2    |                | 5  |

|                | 2.3    | $oldsymbol{c}$ | 7  |

|                |        |                | 7  |

|                |        |                | 7  |

|                |        | ,              | 8  |

|                |        | ·              | 20 |

|                | 2.4    |                | 22 |

|                | 2.4    |                | 22 |

|                |        |                | .2 |

|                |        | y y            | 27 |

|                | 2.5    | 1              | 29 |

|                | ∠.೨    | Conclusion     | כי |

| Chapter 3 | Inve | rsion Reduction Method for Real and Complex Distribution Systems 31 |

|-----------|------|---------------------------------------------------------------------|

|           | 3.1  | Introduction                                                        |

|           | 3.2  | Review of Reference [1]                                             |

|           |      | 3.2.1 Introduction                                                  |

|           |      | 3.2.2 End Bus Removal                                               |

|           |      | 3.2.3 Middle Bus Removal                                            |

|           |      | 3.2.4 Spatial and Temporal Variation in Load / Generation 36        |

|           | 3.3  | Inversion Method Derivation                                         |

|           |      | 3.3.1 Circuit reduction                                             |

|           |      | 3.3.2 Spatial and Temporal Variation in Load/Generation 39          |

|           |      | 3.3.3 Load / Generation Model Mapping                               |

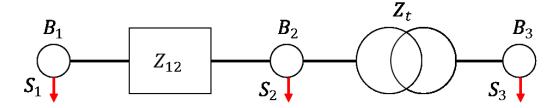

|           | 3.4  | Example reduction of 3 bus system                                   |

|           |      | 3.4.1 Two lines                                                     |

|           |      | 3.4.2 Line and transformer                                          |

|           | 3.5  | Algorithm                                                           |

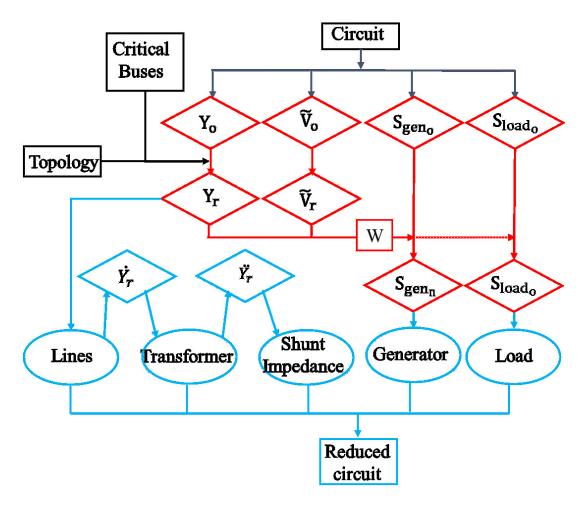

|           |      | 3.5.1 Populate admittance, voltage, and power matrices 45           |

|           |      | 3.5.2 Reduce                                                        |

|           |      | 3.5.3 Rebuild                                                       |

|           | 3.6  | validation                                                          |

|           |      | 3.6.1 Strategy                                                      |

|           |      | 3.6.2 Comparison to reduction in [1] on feeder UCSD A 51            |

|           |      | 3.6.3 Validation on the complete set of feeders                     |

|           | 3.7  | Conclusions                                                         |

| Chapter 4 | Agg  | regation of Voltage Dependant Inverters during Distribution Feeder  |

| 1         |      | uction                                                              |

|           | 4.1  | Introduction                                                        |

|           | 4.2  | Circuit Reduction Overview                                          |

|           | 4.3  | Inverter Aggregation Principles                                     |

|           |      | 4.3.1 Inverter control schemes 63                                   |

|           |      | 4.3.2 Aggregation of Inverters                                      |

|           |      | 4.3.3 Snapshot case study                                           |

|           | 4.4  | Time Series Simulation of Aggregated Network                        |

|           |      | 4.4.1 Framework overview                                            |

|           |      | 4.4.2 voltage estimation                                            |

|           |      | 4.4.3 QSTS case study                                               |

|           | 4.5  | Conclusions                                                         |

| Chapter 5 | Clos | sing remarks                                                        |

| 1         | 5.1  | Recap                                                               |

|           | 5.2  | Future Work                                                         |

| Appendix A   | Voltage Sensitivity Modeling |    |

|--------------|------------------------------|----|

| Bibliography |                              | 89 |

## LIST OF FIGURES

| Figure 2.1: | Depiction of three bus subsection of the feeder in which the middle bus, $B_2$ , is connected upstream to a 3 phase bus $B_1$ and connected downstream to a                                                               |            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 2.2: | 2-phase bus $B_3$ . The red arrows represent current flow out of the nodes A conceptual depiction of the removal of all NCB beyond a CB. The load (triangles) and PV (squares) from the removed NCB are aggregated to the | 12         |

|             | CB. This process is carried out recursively for all CB off the main tree                                                                                                                                                  | 19         |

| Figure 2.3: | Reduced (black) California distribution feeder overlayed on the full distribution feeder (grey). Initially nine buses were user-selected as CB and the                                                                    | 21         |

| Figure 2.4: | algorithm selected the additional buses                                                                                                                                                                                   | 21         |

| 115010 2.1. | to each load are represented in the function (i.e 8,000 simulations $\times \approx 50$ nodes). The inset plot provides a zoomed view of the histogram with x-axis                                                        |            |

|             | limits of $\pm 5 \times 10^{-4}$                                                                                                                                                                                          | 24         |

| Figure 2.5: | Mean error of node voltage plotted as a function of net load on the bus. The mean is taken by binning all net loads in 1 W bins and averaging all errors in                                                               |            |

| E' 2 (.     | the bin.                                                                                                                                                                                                                  | 25         |

| Figure 2.6: | Mean error of node voltage plotted as a function of distance of the node from the substation. The mean is taken by binning all nodes into 100m bins and                                                                   | 26         |

| Figure 2.7: | taking the average of all nodes in that bin across all simulation time steps  Average daily error plotted against the total number of buses removed in                                                                    | 26         |

| 118010 2171 | the simulation. Each point corresponds to error averaged across all time steps and all buses in each simulation, as defined by equation 2.14. 1,000                                                                       |            |

|             | simulations were configured under HS50 with constant impedance loads                                                                                                                                                      | 27         |

| Figure 2.8: | Computation time to reduce the 621 bus feeder to a subset of CB (black) and the QSTS time (red) associated with the reduced feeder for simulating one                                                                     |            |

|             | day at 30 s timesteps. A different simulation set was used to control for time delays due to communication with external storage devices                                                                                  | 29         |

| Figure 3.1: | Line model depicting a single phase 3 bus system connected by two lines. Each bus $B$ injects power $S_B$ . The impedance between a bus and its neighbor                                                                  |            |

|             | is denoted as $Z_{ij}$ , while shunt impedance is noted as $Z_{ii}$                                                                                                                                                       | 41         |

| Figure 3.2: | Line model depicting a single phase 3 bus system connected by one line and one two-winding transformer with impedance $Z_t$                                                                                               | 43         |

| Figure 3.3: | Flowchart of the reduction algorithm. Colors show: (black) breakdown of the original model into its elementary parts; (red) Reduction of parts to                                                                         |            |

|             | equivalents; and (blue) building the reduced model from elementary parts                                                                                                                                                  | 46         |

| Figure 3.4: | IEEE 8500 test feeder (grey) and reduced equivalent (black) for three critical                                                                                                                                            | ء بـ       |

| Eigung 2.5: | buses that were selected to be in areas where voltage extremes are expected.                                                                                                                                              | 52         |

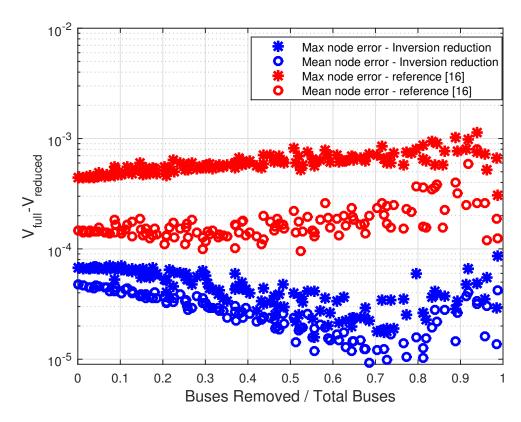

| Figure 3.5: | Comparison of voltage error (maximum and average of all nodes) when reducing the "UCSD A" feeder with the recursive methodology proposed in                                                                               | <b>.</b> . |

|             | reference [1] against the inversion reduction introduced in this work                                                                                                                                                     | 54         |

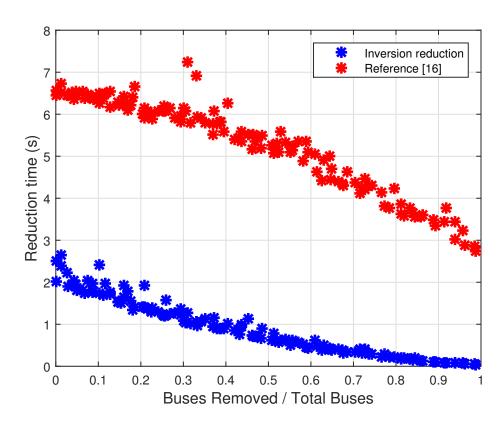

| Figure 3.6:  | Comparison of computational time for reducing the "UCSD A" feeder with the methodology proposed in reference [1] against the inversion reduction. Simulations are run on a desktop with Intel(R) Core(TM) i7-4770 processor with 32 GB RAM.                                     | 55                              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

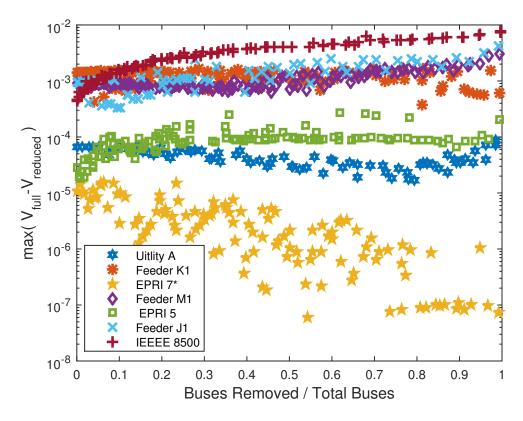

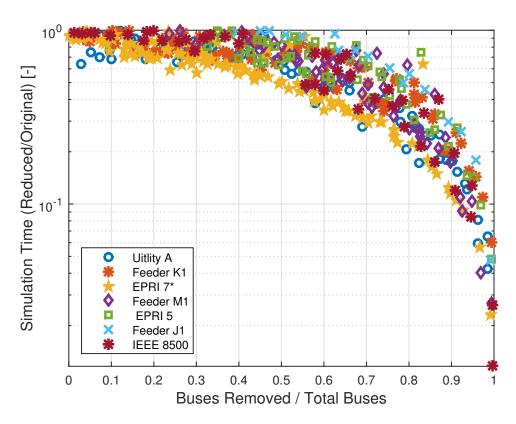

| Figure 3.7:  | Error as a function of the number of buses removed for each of the seven feeders studied. Note the <i>y</i> -axis is logarithmic and represents the maximum                                                                                                                     |                                 |

| Figure 3.8:  | difference between all node voltages between the reduced and the full feeder. The ratio of snapshot simulation time for the reduced circuit to the original circuit as a function of buses removed from the circuit for each feeders studied.                                   | <ul><li>56</li><li>57</li></ul> |

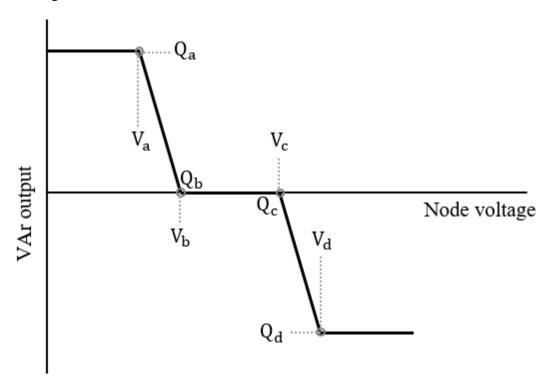

| Figure 4.1:  | Depiction of the category B type volt/VAr curve as defined by the IEEE 1547 standard [2]                                                                                                                                                                                        | 64                              |

| Figure 4.2:  | Depiction of the effect of applying the VDA to the Volt/VAr curve. The original curve is given by the dotted lines and the updated curve is given by the solid lines. The shape of the curve remains the same, however the voltage at which the inverter activates is "shifted" | 66                              |

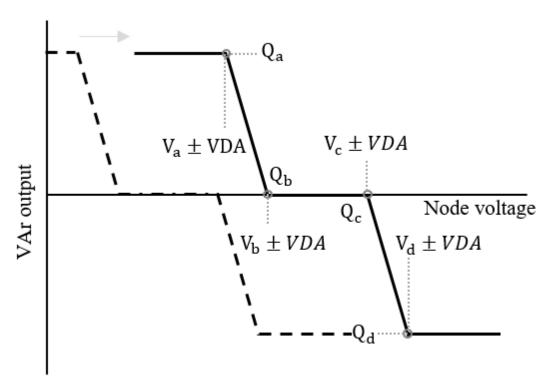

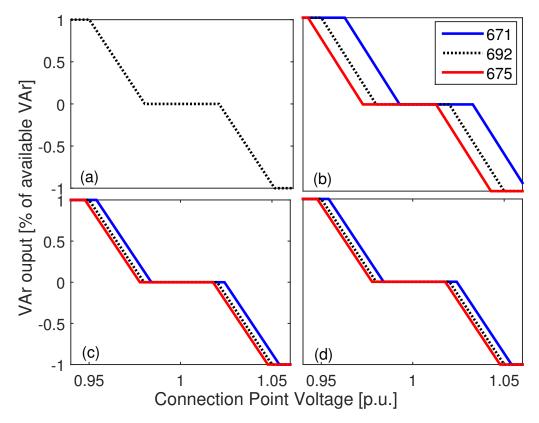

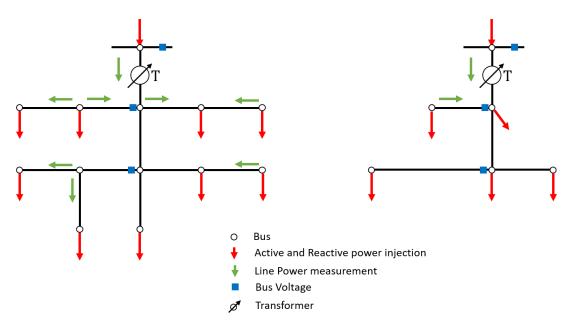

| Figure 4.3:  | Depiction of the IEEE 13 bus system studied. (a) The original circuit was retrofitted with a PV system at bus 692. (b) The reduced circuit with bus 692 removed results in two PV systems on the neighboring buses (buses 671 and 675)                                          | 68                              |

| Figure 4.4:  | The VoltVAr curves for the PV systems. (a) The three phase curve for the original system, used as reference for the modified curves. The VDA modified curve for PV PV <sub>671</sub> and PV <sub>675</sub> for (b) Phase A (c) Phase B (d) Phase C                              | 69                              |

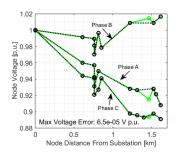

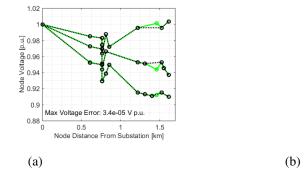

| Figure 4.5:  | Voltage plotted as a function of distance for all nodes of the original circuit (green) and the reduced circuit (dashed black).                                                                                                                                                 | 70                              |

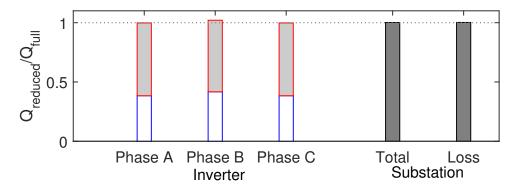

| Figure 4.6:  | Reactive power injection and loSSEs of the reduced circuit normalized by the results of the original circuit                                                                                                                                                                    | 71                              |

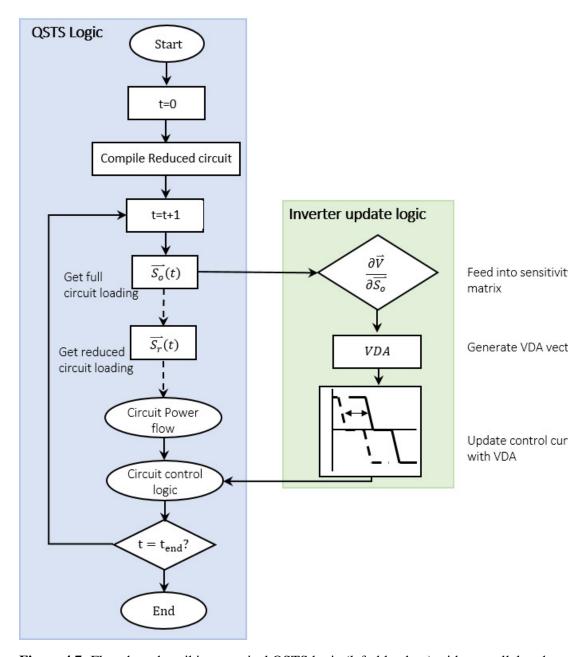

| Figure 4.7:  | Flowchart describing a typical QSTS logic (left, blue box) with a parallel updater which corrects the VDA that is applied to each curve                                                                                                                                         | 72                              |

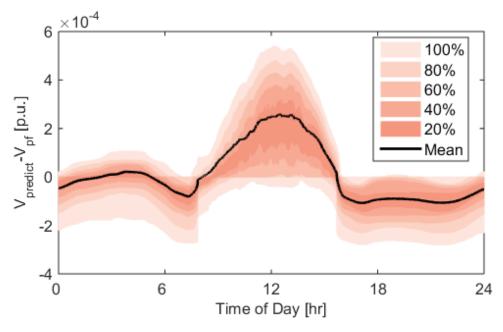

| Figure 4.8:  | Confidence interval (0-100) plot of prediction error over 53 test period. Lighter shading indicate less likelyhood                                                                                                                                                              | 75                              |

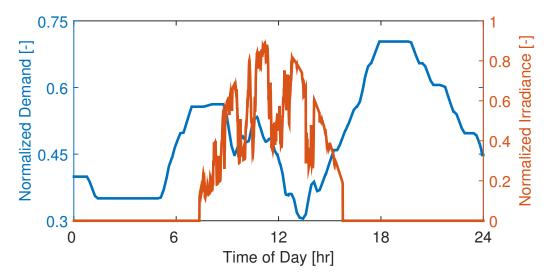

| Figure 4.9:  | Double axis time series plot of the loading for the simulation day. (left, dash-dot blue) Demand shape for all loads in the circuit. (right, solid red) PV profile for a single PV in the circuit.                                                                              | 76                              |

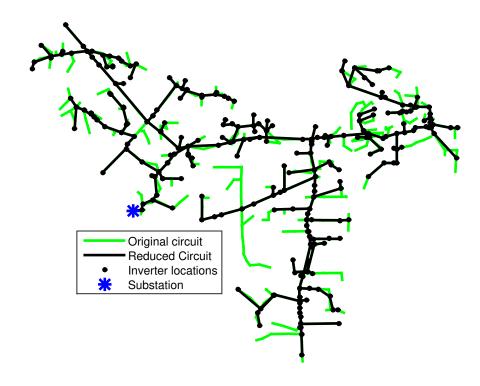

| Figure 4.10: | The original and reduced circuit topology with the location of inverters given for the reduced circuit.                                                                                                                                                                         | 77                              |

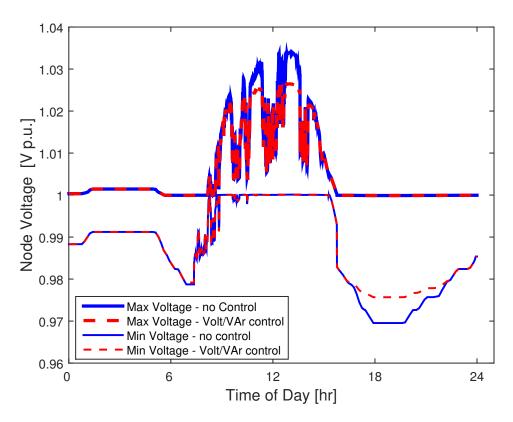

| Figure 4.11: | Voltage time-series for the full feeder for the day studied for the (blue) uncontrolled inverters and the (red) controlled inverters                                                                                                                                            | 78                              |

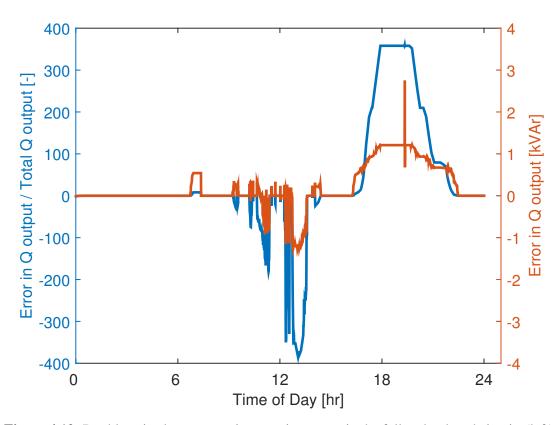

| Figure 4.12: | Double axis plot representign reactive power in the full and reduced circuit. (left) Total reactive power input from inverters timeseries. (right) difference between total inverter reactive power output between the reduced circuit and original circuit.                    | 79                              |

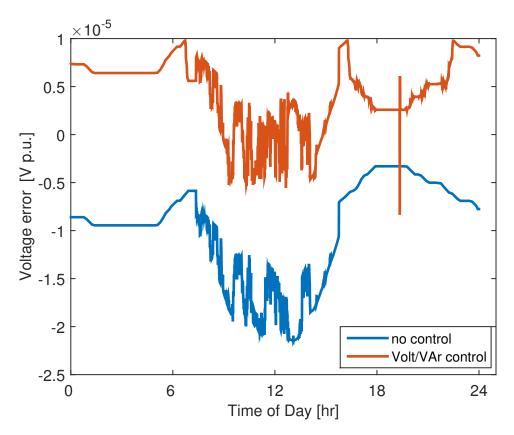

| Figure 4.13: | Maximum nodal voltage error between the reduced and original circuit when (blue) no control is applied and (red) when Volt/VAr control is applied                                                                             | 80 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.1:  | Conceptual depiction of reduction of measurements along a feeder                                                                                                                                                              | 84 |

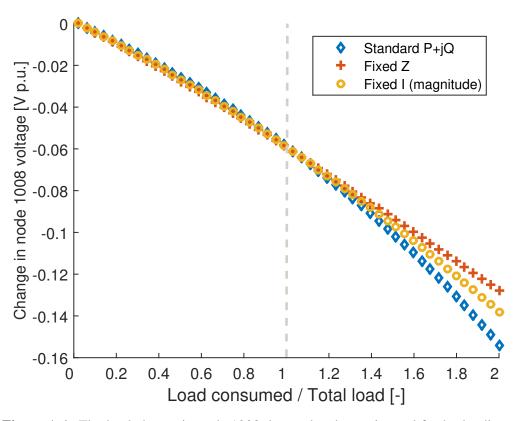

| Figure A.1:  | The load change in node 1008 due to the change in total feeder loading. Three different load models are observed for each load: i) Constant power loads; ii) constant impedance loads; iii) Constant current magnitude loads. | 88 |

## LIST OF TABLES

| Table 2.1: | Computational expense associated with reduction of the original feeder ( $t_{red}$ ) and simulation of the reduced feeder ( $t_{sim}$ ) as presented in Fig. 2.8. The yearly simulation time is extrapolated from the one-day simulation time for 30s time |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | steps                                                                                                                                                                                                                                                      | 28 |

| Table 3.1: | Characteristics of the 7 feeders investigated using the reduction methodology. All feeders studied are publicly available.                                                                                                                                 | 53 |

| Table A.1: | Goodness of fit measures for increasing order of polynomial model fits to the change in voltage of node 1008 with respect to change in feeder loading (Fig A.1)                                                                                            | 88 |

#### **ACKNOWLEDGEMENTS**

In my time at UCSD I was fortunate to work with a world class set of researchers, who I must thank for helping me grow as a researcher, but more importantly as an individual.

First, I would like my advisor, Jan Kleissl. Jan's kind and calm nature is truly rare in this world, but is a model that I would like to see adopted. He was always available when needed and understanding of complexities involved in a grad students life. I am sure having a different advisor would of made my graduate experience a much less enjoyable one.

This work would not be complete without acknowledging my postdoc and freind Vahid R. Disfani. The massive donation of time Vahid gave to my education and research is the sole reason I was able to complete my degree in an unfamiliar field in under four years. I am eternally grateful and look forward to a continued partnership in the future.

Similarly, I would like to acknowledge Hamed Valizedeh Haghi for his contribution to my work. Despite the brevity, our time together has been extremely productive. Simply speaking with him has provided a whole world of education.

San Diego, thank you for providing beautiful nature and year-round mild weather. Thank you also for being so ridiculously expensive that I never got to comfortable on a graduate student salary.

Finally, I need to thank my family and freinds. To my father, mother, brother, stepfather, stepmother, aunts, and grandparents: thanks you for the continued support, you all know how much you mean to me, and I know you are enjoying the fruits of my hard work as much as I am. To my girlfriend Christine, thank you for the day to day sanity measures and giving up your whole life to move out west and allow me to chase my dreams.

The text in Chapter 1 is sampled from i) Multiphase Distribution Feeder Reduction, Pecenak, Z.K., Disfani, V.R., Reno, M., Kelissl, J., *IEEE Transactions on Power Systems*, 2017; ii) Inversion Reduction Method for Real and Complex Distribution Systems, Pecenak, Z.K., Disfani, V.R., Reno, M., Kelissl, J.,; iii) Aggregation of Voltage Dependant Inverters during

Distribution Feeder Reduction, Pecenak, Z.K., Haghi, H.V., Disfani, V.R., Reno, M., Kelissl, J.,.

The dissertation author is the primary investigator and author of all the articles.

The text and data in Chapter 2, in full, is a reprint of the material as it appears in Multiphase Distribution Feeder Reduction, Pecenak, Z.K., Disfani, V.R., Reno, M., Kelissl, J., *IEEE Transactions on Power Systems*, 2017. The dissertation author is the primary investigator and author of this article.

The text and data in Chapter 3, in full, is submitted to *IEEE Transactions on Power Systems* under the title Inversion Reduction Method for Real and Complex Distribution Systems, Pecenak, Z.K., Disfani, V.R., Reno, M., Kelissl, J., The dissertation author is the primary investigator and author of this article.

The text and data in Chapter 4, in full, is in preparation for submition to *IEEE Transactions on Power Systems* under the title Aggregation of Voltage Dependant Inverters during Distribution Feeder Reduction, Pecenak, Z.K., Haghi, H.V., Disfani, V.R., Reno, M., Kelissl, J., The dissertation author is the primary investigator and author of this article.

#### **VITA**

| 2012 | A. S. in Engineering Science <i>cum laude</i> , Mohawk Valley Community College, Utica, NY                                 |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 2014 | Dual B. S. in Mechanical and Aerospace Engineering <i>summa cum laude</i> , Univ. at Buffalo - Honors college, Buffalo, NY |

| 2015 | M. S. in Engineering Sciences (Mechanical Engineering), University of California San Diego, La Jolla, CA                   |

| 2018 | Ph. D. in Engineering Sciences (Mechanical Engineering), University of California San Diego, La Jolla, CA                  |

#### SELECTED PUBLICATIONS

Pecenak, Z.K., Haghi, V.H., Disfani, V.R., Reno, M., Kleissl, J. "Aggregation of Voltage Dependant Inverters During Distribution Network Reduction", *IEEE Trans. on Power Sys.*, *submitting*, 2018.

Pecenak, Z.K., Disfani, V.R., Reno, M., Kleissl, J. "Inversion Reduction Method for Real and Complex Distribution Feeder Models", *IEEE Trans. on Power Sys.*, *submitted*, 2018.

Pecenak, Z.K., Disfani, V.R., Reno, M., Kleissl, J. "Multiphase Distribution Feeder Reduction", *IEEE Trans. on Power Sys.*, 2017.

Pecenak, Z.K., Disfani, V.R., Reno, M., Kleissl, J. "Smart Inverter Impacts on California Distribution Feeders with Increasing PV Penetration: A Case Study", *IEEE PESGM*, 2017.

Pecenak, Z.K., Mejia, F., Kurtz, B., Evans, A., Kleissl, J. "Simulating Irradiance Enhancement Dependence on Cloud Optical Depth and Solar Zenith Angle", *Solar Energy*, 136, 2016.

#### ABSTRACT OF THE DISSERTATION

#### **Comprehensive Reduction of Real and Complex Distribution Feeder Models**

by

#### Zachary K. Pecenak

Doctor of Philosophy in Engineering Sciences (Mechanical Engineering)

University of California, San Diego, 2018

Professor Jan Kleissl, Chair

The US power grid is an engineering marvel. However, it was not designed with the consideration of renewable energy, energy storage, two way electricity transfer from electric vehicles, advanced control devices, or advanced metering systems. In order to properly integrate such devices, power system planning studies in which the proposed device is simulated under yearly operation is performed on a real/existing circuit model are performed. However, the studies are extremely intensive with respect to computational and temporal resources due to: i) the size and complexity of real circuits ii) The daily and seasonal variation in load consumption and available renewable resources iii) The number of operating states of the device.

Model reduction is a common approach in big data applications to reduce the burden.

However, much like the grid itself, traditional methods of circuit reduction are not designed for the growing complexity of distribution side circuits. Specifically, there are no methods in literature that consider circuits with i) unbalance in loading and generation between phases ii) unbalance in distribution line impedances between phases iii) mutual coupling between phases iv) shunt capacitance in distribution lines v) multiple voltage levels. Further, topics like reduction of forecasted generation/consumption time series or aggregation of voltage-controlled devices have not been discussed.

In this thesis, a circuit reduction technique that is specifically formulated for the complexities of real distribution feeders is introduced. The comprehensive methodology is derived from first principles to overcome all of the limitations of circuit reduction techniques listed above. Detailed algorithms of our recommended implementation are given for increase the utility to researchers.

An extensive validation is performed on several real circuit to develop a granular understanding of error sources. It is shown that for even the largest publicly available models, the method is highly accurate, with time savings of up to 99% per simulation, while being flexible enough to handle a range of modeling or control complexities.

# Chapter 1

# Introduction

The aging infrastructure of the US electric grid combined with increasingly severe weather caused by climate change is threatening the reliability of electric delivery. Furthermore, the cost to rebuild and improve the infrastructure is putting pressure on tight state budgets [3]. This and environmental concerns have caused investor owned utilities (IOUs) and policy makers to invest in the next generation of grid deployable devices to improve reliability, voltage and frequency regulation, and advanced metering capabilities. Therefore, emerging technologies of distributed energy resources (DER) such as distributed photovoltaic (PV) systems, other distributed generators (DG), energy storage systems (ESS), and electric vehicle (EV) charging infrastructure will soon enter distribution grids at high penetrations.

In addition to evaluation of economic benefits and costs associated with integration of DER, their technical impacts such as voltage and frequency must be studied in realistic scenarios. Numerical simulations are generally easy to set up and allow investigations of a large number of configurations. However, a typical utility distribution feeder model contains a node for every customer and therefore consists of thousands of buses. While a single power flow completes after a few seconds on a workstation, consideration of multiple distribution feeders, large parametric analyses, or investigation at fine time scales, simulation time can become prohibitive. While

previously it may have been sufficient for a utility to consider a mininimum and maximum load case to optimize voltage regulators to ensure voltage compliance, the emergence of high penetration of PV introduces challenges to this paradigm: (i) weather and seasonal variations of solar generation are typically examined using 8760 hourly times in a year (ii) some PV impacts such as tap operations can only be accurately benchmarked through simulation at time steps commensurate with tap operation control delays and cloud passages (seconds) (iii) worst cases are increasingly hard to define (high load and low solar and high solar variability), motivating a probabilistic framework for allocating future PV installations [4] and for decision-making in general.

So far, these scenarios have primarily materialized in distribution system research [5, 6, 7]. However, in the near future, utilities and their consultants will likely adopt these practices. DG interconnection studies performed by utilities on proposed installations that do not pass the initial screening requirements can then result in delays on the project due to long simulation times [8, 9]. Further, in-depth studies of the dynamic and transient behaviors of several devices in complex systems are not feasible without the aid of super computers.

This predicament closely parallels the issues faced in the study of big data, where observing the full set of data is infeasible. In that field, model or dimensional reduction is a popular approach to overcome this problem [10]. A similar approach has been explored in power systems, where the circuit to be studied is reduced to a smaller equivalent.

In fact, the concept of model reduction can be traced back to the introduction of Kron reduction in 1939 [11]. This simplistic method proposes a methodology to remove parts of the circuit with negligible powerflow through them. The method is mathematically exact, and very accurate, but suffers from lack of general usage.

The field of model reduction was improved with the introduction of the Ward reduction technique a decade later [12]. The technique which uses matrix representations of the system properties finds equivalent current injections for a reduced circuit and solves the powerflow given

that as input. However, the Ward reduction requires an initial solution to the power flow (which increases computational cost) and assumes fixed current loads, which is not representative of common electric loads.

A slew of other methods have been developed in the period between Ward reduction and present day. In reference [13] four of the more popular network reduction techniques are discussed and compared for performance in static power flow simulations: i) Ward reduction [12], ii) Kron Reduction [11], iii) Dimo's Method [14], and iv) Zhukov's reduction [15]. For the two feeders investigated (IEEE 14 bus and IEEE 118 bus), all methods were shown to produce significant error in voltage due to reduction (> 0.01 pu). Surprisingly, the Ward reduction method produced the lowest error overall.

However, all of the methods introduced above are designed for transmission networks which tend to be balanced systems designed with symmetrical components. Applying these methods to distribution feeders is not possible due to the imbalanced nature of phases of distribution systems.

The first attempt at reduction of distribution models was proposed in [16]. The methodology splits and aggregates load consecutively into neighboring buses using an impedance weighting. The accuracy of the method is tested against a 1000-node realistic feeder, where the maximum absolute deviation of voltage magnitudes between the reduced and original feeder is less than 103 V. However, as stated by the authors, the method is only applicable to simplified distribution networks without any unbalanced load or PV, unbalanced wire impedances, mutual coupling, or shunt capacitance and is still based on a constant current assumption. Moreover, in the load and PV aggregation process, the algorithm proposed in [19] does not consider the original positions of loads and PV to simulate of spatial variability. For these reasons, application of the methodology to real feeders results in large errors.

The segmentation method introduced in reference [17] introduces the use of a constant power assumption to the literature on distribution network reduction. The methodology recursively

replaces model segments between two buses of interest with characteristic equations representing a simpler topology. The methodology is tested on Feeder J1 [18] and produces a small max voltage error of  $(\mathcal{O}(10^{-3}))$ . However the authors make no mention of error with changing load conditions or reduction across different voltage levels, and an initial power flow is still needed as a system input.

To the author's knowledge there are no other works focused on circuit reduction for distribution feeders. The work in this thesis addresses the shortcomings in a single methodology that can reduce circuits with

- multiphase connections through out the entire network

- mutual coupling between multiphase unbalanced lines

- unbalanced loads and generation

- spatial variation in load and generation

- shunt capacitance in distribution lines

- multiple voltage levels

- voltage shifting transformers

that accounts for changing demand and generation without requiring an initial powerflow. This is addressed in chapters 2 and 3 of this thesis. For the method developed, novel algorithms for converting between elementary power systems equations and commercial power system solver formats are given.

In Chapter 4, the first attempt at reduction of control devices which are dependent on local voltage measurements is attempted. Building on the advanced circuit reduction algorithm, we integrate a novel voltage estimation technique to replace the required measurements, which produces equivalent control behavior.

In Chapter 5, closing remarks are made about the work, including future work and other uses for the circuit reduction technique developed.

# Chapter 2

# **Multiphase Distribution Feeder Reduction**

# 2.1 Introduction

The aging infrastructure of the US electric grid combined with increasingly severe weather caused by climate change is threatening the reliability of electric delivery. Furthermore, the cost to rebuild and improve the infrastructure is putting pressure on tight state budgets [3]. This and environmental concerns have caused investor owned utilities (IOUs) and policy makers to invest in the next generation of grid deployable devices to improve reliability, voltage and frequency regulation, and advanced metering capabilities. Therefore, emerging technologies of distributed energy resources (DER) such as distributed photovoltaic (PV) systems, other distributed generators (DG), energy storage systems (ESS), and electric vehicle (EV) charging infrastructure will soon enter distribution grids at high penetrations.

In addition to evaluation of economic benefits and costs associated with integration of DER, their technical impacts such as voltage and frequency must be studied in realistic scenarios. Numerical simulations are generally easy to set up and allow investigations of a large number of configurations. However, a typical utility distribution feeder model contains a node for every customer and therefore consists of thousands of buses. While a single power flow completes after

a few seconds on a workstation, consideration of multiple distribution feeders, large parametric analyses, or investigation at fine time scales, simulation time can become prohibitive. While previously it may have been sufficient for a utility to consider a mininimum and maximum load case to optimize voltage regulators to ensure voltage compliance, the emergence of high penetration of PV introduces challenges to this paradigm: (i) weather and seasonal variations of solar generation are typically examined using 8760 hourly times in a year (ii) some PV impacts such as tap operations can only be accurately benchmarked through simulation at time steps commensurate with tap operation control delays and cloud passages (seconds) (iii) worst cases are increasingly hard to define (high load and low solar and high solar variability), motivating a probabilistic framework for allocating future PV installations [4] and for decision-making in general.

So far, these scenarios have primarily materialized in distribution system research [5, 6, 7]. However, in the near future, utilities and their consultants will likely adopt these practices. DG interconnection studies performed by utilities on proposed installations that do not pass the initial screening requirements can then result in delays on the project due to long simulation times [8, 9]. Further, in-depth studies of the dynamic and transient behaviors of several devices in complex systems are not feasible without the aid of super computers.

This dilemma has driven research to develop analytical methods to reduce the computational time required for large systems simulations while maintaining the accuracy of the solutions. A classical method for reducing system size is through the use of Kron reduction techniques, where buses with either no current or voltage are removed from the circuit [11]. While Krons reduction is valid and useful, the amount of reduction that is achievable in most systems is limited. Several authors have proposed reductions of the bulk electric transmission system through the use of equivalent collector systems, power injection matrix reduction, and bus aggregation [19, 20]. However, these methods fail to address the special characteristics of distribution systems such as multiphase connections, unbalanced loads, and mutual impedance.

Several other approaches in the literature propose analytical methods to entirely remove the need for a power flow solver. In [21], a method using base case circuit information is developed to find the optimal two-bus equivalent system of a transmission system for voltage stability analyses. Despite the high speed and accuracy of the method, the resulting circuit offers little flexibility to carry out investigations on other aspects of the power grid beyond transmission voltage stability. Another two-bus equivalent circuit formulation is proposed in [22] which is composed of a slack bus, equivalent impedance, and a single aggregated PV and load bus. The two-bus system allows quick and accurate investigation of voltage extrema in the circuit due to high variability of PV power output. However, the major drawback of this method is the fact that it is only able to simulate a single bus at a time and does not offer the flexibilitiy for comprehensive studies considering the coordinated behavior of several devices.

In addition to speeding up QSTS simulations, circuit reduction has been a research interest for several other applications. Specifically, methods have been proposed to reduce the circuit models for real-time control or hardware-in-the-loop (HIL) testing environments [23] that cannot handle the complexity and number of buses in a full distribution system model. Detailed dynamic analysis of large distribution systems is also often impractical in electromagnetic transient programs without network reduction [24]. With more DER being installed, there has also been a focus to expand the circuit reduction methods developed for equivalencing large wind farms for transmission dynamic [25], voltage ride-through [26], and harmonic studies [27]. These types of co-simulations with both transmission and distribution often reduce the complexity of the distribution system model by aggregating distributed generation into an equivalent dynamic model [28]

A novel methodology to reduce a balanced distribution feeder to any desired set of buses is presented in [16]. The methodology splits and aggregates load consecutively into neighboring buses using an impedance weighting. The accuracy of the method is tested against a 1000-node realistic feeder, where the maximum absolute deviation of voltage magnitudes between

the reduced and original feeder is less than  $10^{-3}$  V. However, as stated by the authors, the method is only applicable to simplified distribution networks without any unbalanced load or PV, unbalanced wire impedances, mutual coupling, or shunt capacitance. Moreover, in the load and PV aggregation process, the algorithm proposed in [16] does not consider the original positions of loads and PV to simulate of spatial variability. For these reasons, application of the methodology to real feeders results in large errors.

This paper builds upon [16] and resolves most of its limitations. An analytical method is proposed to reduce complex multiphase distribution feeders to a subset of buses (the critical buses (CB)) of interest. That is, the algorithm is applicable to *p*-phase distribution feeders with unbalanced loads and PV, unbalanced wire impedance, and mutual coupling between phases. The work is further extended through preserving the spatial diversity of solar and load on the circuit in the reduction process. The accuracy of the reduction is investigated on a real California feeder in reference to the complete simulation. Also, the sensitivity of voltage errors to location of the CB, types of loads, solar irradiance, PV penetration level, and bus distance from substation is investigated. Finally, the computational cost savings are quantified.

Thus, the contributions of this paper to the literature on network reductions are as follows:

- 1. Development of the first methodology to reduce real and complex distribution feeders which are unbalanced in nature. Such feeders can include:

- (a) multiphase connections through out the entire network

- (b) mutual coupling between multiphase unbalanced lines

- (c) unbalanced loads and generation

- (d) spatial variation in load and generation

- 2. The mathematical derivation and algorithm to implement the methodology are provided.

- 3. A novel methodology for aggregating temporal and spatial variation of load and generation

across the network.

- 4. Development of a topology detection algorithm, which serves as a platform for manipulating values between buses.

- 5. Quantification of reduction errors for multiple load types, load conditions, and topology.

The rest of the paper is organized as follows. Section 2.2 explains the mathematical formulation of the reduction method. Section 3.5 proposes the algorithms to reduce the feeder to the desired CB. The simulation results and validation of the accuracy of the reduction method are provided in Section 3.6, along with a discussion on the computational advantages of the reduction. Section ?? concludes the paper.

# 2.2 Analytical Approach

## 2.2.1 Assumptions

We assume a radial network in a p-phase configuration with n buses and m nodes where a node refers to the individual phases of connections on a bus, such that  $m \le p * n$ . For the purpose of clarity, the derivation and analysis is performed for a 3 phase system with multiphase connections (p=3).

Consistent with [16, 12, 29, 30], the power injections and absorption on load and PV buses are assumed to be fixed current for the purpose of mathematical derivation (eq. 2-10). This assumption causes errors for constant PQ and constant impedance loads as well as for the PV systems which are typically modeled as constant PQ. The fixed current assumption is supported by research on conservation voltage reduction (CVR) [18], which showed that every 1% reduction in voltage leads on average to a 0.8% reduction in real power (CVR=0.8), while fixed current loads would cause CVR=1%. In spite of the error, methods using this assumption have shown to

provide higher accuracy than other leading methods [31, 13, 32]. Further, the results provided in [33] demonstrate that the load type selected has minor effects on the simulation results.

However, it should be noted that the load types used in the feeder are kept during the aggregation process, as opposed to being changed to constant current. This is carried out by aggregating loads into groups of like load types in the final reduced feeder. The impacts of using different load types on the voltage error between the original and reduced feeder are investigated in Section 3.6.

In our work it is assumed that neutral connections could be provided by local grounding at any bus. Thus, the line models in this work do not include the neutral wire. In our algorithm, all loads are transformed to the equivalent Y-connected loads to derive the individual loads connected between each phase and ground. These loads define the equivalent single-phase loads on the reduced feeder. Further, the secondary side of the substation transformers are grounded and it remains the same in the reduced feeder since there is no reduction on transformers. Further, perfect grounding is assumed at each bus, thus neglecting the return current in the system, which can lead to inaccuracies under highly imbalanced conditions in models with imperfect grounding.

Finally, line capacitance is not treated in this model and assumed to be zero, thus rendering the method inaccurate for models with non-zero values. Reduction of shunt capacitance is a focus of future work.

#### 2.2.2 Reduction Method

A bus is composed of several nodes  $N_i$ , representing the phases of connection. In a real multiphase distribution feeder, the number of phases between adjacent buses is often different, especially away from the main branch. Furthermore, PV and load on a bus are not necessarily evenly distributed between phases. The reduced feeder is required to maintain the original distribution of PV, load, and impedance by phase, thus it is necessary to aggregate the feeder at the phase level. Our comprehensive feeder reduction algorithm addresses all these special

characteristics of distribution feeders.

The method proposed in this paper, which is based on defining the line impedance by Z matrices, is a highly generalized reduction technique applicable to distribution feeders with multiphase connections through out the entire network, mutual coupling between multiphase unbalanced lines, unbalanced loads and generation, spatial variation in load and generation It employs a recursive bus reduction technique which gradually removes non-critical buses (NCB) until only the set of selected CB remain (see section 2.3.2). At every step, one NCB is removed and its load and PV systems are allocated between the adjacent CB, while total PV and load is preserved.

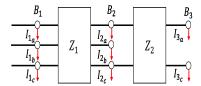

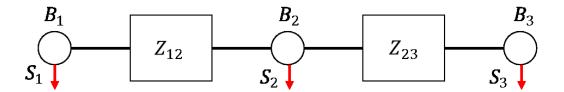

Fig. 2.1 shows the feeder structure at one of the intermediate feeder reduction steps in order to conceptualize the different types of reduction, which are described in Section 3.5 in detail. The objective in this feeder reduction is to remove the NCB while maintaining the voltage on the CB.

**Figure 2.1**: Depiction of three bus subsection of the feeder in which the middle bus,  $B_2$ , is connected upstream to a 3 phase bus  $B_1$  and connected downstream to a 2-phase bus  $B_3$ . The red arrows represent current flow out of the nodes.

$Z_1$  and  $Z_2$  are multi-phase line impedance matrices, e.g.

$$Z_{1} = \begin{bmatrix} Z_{1,aa} & Z_{1,ab} & Z_{1,ac} \\ Z_{1,ba} & Z_{1,bb} & Z_{1,bc} \\ Z_{1,ca} & Z_{1,cb} & Z_{1,cc} \end{bmatrix}$$

(2.1)

where the diagonal elements denote the self-impedances of all phases a, b, c and the off-diagonal elements are associated with the mutual impedance between different phases, which are not

necessarily identical. The procedure is demonstrated through two scenarios;

## 2.2.3 Type 1: End bus Reduction

First, assume that buses  $B_2$  in Fig. 2.1 is CB and the objective is to remove the bus  $B_3$  which is NCB. If  $I_i$  and  $V_i$  respectively denote the 3-phase net current injection vectors and 3-phase voltage vectors on bus  $B_i$ , we have:

$$\begin{bmatrix} V_{3,a} \\ 0 \\ V_{3,c} \end{bmatrix} = \begin{bmatrix} V_{2,a} \\ 0 \\ V_{2,c} \end{bmatrix} - \begin{bmatrix} Z_{2,aa} & 0 & Z_{2,ac} \\ 0 & 0 & 0 \\ Z_{2,ca} & 0 & Z_{2,cc} \end{bmatrix} \times \begin{bmatrix} I_{3,a} \\ 0 \\ I_{3,c} \end{bmatrix}$$

$$\begin{bmatrix} V_{2,a} \\ V_{2,b} \\ V_{2,c} \end{bmatrix} = \begin{bmatrix} V_{1,a} \\ V_{1,b} \\ V_{1,c} \end{bmatrix} - \begin{bmatrix} Z_{1,aa} & Z_{1,ab} & Z_{1,ac} \\ Z_{1,ba} & Z_{1,bb} & Z_{1,bc} \\ Z_{1,ca} & Z_{1,cb} & Z_{1,cc} \end{bmatrix} \times \begin{bmatrix} I_{2,a} + I_{3,a} \\ I_{2,b} \\ I_{2,c} + I_{3,c} \end{bmatrix}.$$

$$(2.2)$$

From (2.2) and (2.3) the voltage vectors  $V_1$  and  $V_2$  can be written as functions  $I_2$  and  $I_3$  which exclude  $V_3$ . Therefore, the bus  $B_3$  can be removed from the feeder by just transferring its current injections to  $B_2$ .

# 2.2.4 Type 2: Middle Bus Reduction

In this type of reduction,  $B_1$ ,  $B_2$ , and  $B_3$  are three consecutive buses in one of the intermediate reduction steps where  $B_2$  is the NCB to be removed,  $B_3$  is CB, and  $B_1$  can be a CB or NCB. Without loss of generality, let us assume a special case where the line between  $B_2$  and

$B_3$  is also three-phase, *i.e.*  $Z_2 \in \mathbb{C}^{3 \times 3}$ . Thus, we have:

$$V_3 = V_2 - Z_2 \times I_3 \tag{2.4}$$

$$V_2 = V_1 - Z_1 \times (I_2 + I_3). \tag{2.5}$$

Replacing voltage parameters corresponding to  $B_2$  by the parameters of the neighboring buses, the voltage vector  $V_3$  is represented as below

$$V_3 = V_1 - Z_1 \times (I_2 + I_3) - Z_2 \times I_3 =$$

$$V_1 - (Z_1 + Z_2) \times (I_3 + (Z_1 + Z_2)^{-1} \times Z_1 \times I_2),$$

(2.6)

which implies a single three-phase line between  $B_1$  and  $B_3$  with an impedance matrix equal to  $Z_{eq}=Z_1+Z_2$ , while the new load at  $B_3$  includes a portion of load from the removed bus in addition to its original load. Due to the symmetry of the example network, the load on bus  $B_1$  must be updated to  $I_1+(Z_1+Z_2)^{-1}\times Z_2\times I_2$ . Therefore, total feeder loads remain the same.

In general, if any of the lines between the original buses lack some phases, the process is slightly different. In such conditions, the equivalent line includes only the common phases between  $Z_1$  and  $Z_2$ . All loads on the phases which are just connected to one of adjacent buses must be transferred to the same phase of that bus.

As a general case, it is assumed here that the number of phases of the lines  $Z_1$  and  $Z_2$  are not the same, e.g.  $Z_1 \in \mathbb{C}^{3\times 3}$  and  $Z_2 \in \mathbb{C}^{2\times 2}$ . These lines connect three buses with phase nodes  $\phi(B_1) = \{a,b,c\}$ ,  $\phi(B_2) = \{a,b,c\}$ , and  $\phi(B_3) = \{a,c\}$  as depicted in Fig. 2.1. For a NCB with multiphase connections, such as the given example, it is necessary to identify the phases common and not common to both lines.

To avoid zero determinants in the inversion of  $Z_{eq}$ , a reduced verion of the matrices is introduced. Assuming that  $Z_1^r$  and  $Z_2^r$  are the reduced format of  $Z_1$  and  $Z_2$  which only includes the elements corresponding to phases  $\{a,c\}=\phi(B_1)\cap\phi(B_2)\cap\phi(B_3)$ , the equivalent impedance is

equal to  $Z_1^r + Z_2^r$ , as defined in (2.7).

$$Z_{eq} = \begin{bmatrix} Z_{1,aa} & Z_{1,ac} \\ Z_{1,ca} & Z_{1,cc} \end{bmatrix} + \begin{bmatrix} Z_{2,aa} & Z_{2,ac} \\ Z_{2,ca} & Z_{2,cc} \end{bmatrix}$$

(2.7)

Since there is no connection between  $B_1$  and  $B_3$  through the uncommon phase, any elements corresponding to this phase in the equivalent impedance disappear.

For uncommon phases, all load and PV connected to the middle bus are transferred to the bus which includes the uncommon phase. For example, all load and PV on phase b of bus  $B_2$  are transferred to phase b of bus  $B_1$  (Fig. 2.1). However, the load and PV on common phases of the middle bus are allocated between the other two buses according to the impedance matrices of  $Z_1^r$ and  $Z_2^r$ .

$$\begin{bmatrix} I_{3,a} \\ I_{3,c} \end{bmatrix}^{\text{new}} = \begin{bmatrix} I_{3,a} \\ I_{3,c} \end{bmatrix} + Z_{eq}^{-1} \times \begin{bmatrix} Z_{1,aa} & Z_{1,ac} \\ Z_{1,ca} & Z_{1,cc} \end{bmatrix} \times \begin{bmatrix} I_{2,a} \\ I_{2,c} \end{bmatrix}$$

$$\begin{bmatrix} I_{1,a} \\ I_{1,c} \end{bmatrix}^{\text{new}} = \begin{bmatrix} I_{1,a} \\ I_{1,c} \end{bmatrix} + Z_{eq}^{-1} \times \begin{bmatrix} Z_{2,aa} & Z_{2,ac} \\ Z_{2,ca} & Z_{2,cc} \end{bmatrix} \times \begin{bmatrix} I_{2,a} \\ I_{2,c} \end{bmatrix}$$

$$(2.8)$$

$$\begin{bmatrix} I_{1,a} \\ I_{1,c} \end{bmatrix}^{\text{new}} = \begin{bmatrix} I_{1,a} \\ I_{1,c} \end{bmatrix} + Z_{eq}^{-1} \times \begin{bmatrix} Z_{2,aa} & Z_{2,ac} \\ Z_{2,ca} & Z_{2,cc} \end{bmatrix} \times \begin{bmatrix} I_{2,a} \\ I_{2,c} \end{bmatrix}$$

(2.9)

$$I_{1,b}^{\text{new}} = I_{1,b} + I_{2,b} \tag{2.10}$$

#### PV and load allocation

To aggregate time-series load shapes a complex matrix  $W \in C^{(3n \times 3n)}$  maps the PV or load from nodes of NCB to the CB nodes which it is transferred to. The elements  $W_{ij}$  are initialized as 1 if there is a PV/load on that node, and it is 0 otherwise. In each step of feeder reduction W is updated to represent the contribution of PV/load from the removed NCB onto the phases of the CB and rows corresponding to NCB are removed.

For middle bus reduction we define the ratio matrices  $R_1 \in \mathbb{C}^{3\times 3}$  and  $R_2 \in \mathbb{C}^{3\times 3}$ . Matrix elements corresponding to the common phases between the three buses are equal to elements of the reduced matrices,  $R_1^r = Z_{eq}^{-1}Z_2^r$  and  $R_2^r = Z_{eq}^{-1}Z_1^r$ . For the elements of  $R_1$  and  $R_2$  corresponding to the uncommon phases off-diagonal elements are all zero, except elements corresponding to common phases with only bus, in which the element is one. For the example shown in Fig. 2.1 the ratio matrices  $R_1$  and  $R_2$  are:

$$R_{1} = \begin{bmatrix} r_{1,aa}^{r} & 0 & r_{1,ac}^{r} \\ 0 & 1 & 0 \\ r_{1,ca}^{r} & 0 & r_{1,cc}^{r} \end{bmatrix}, R_{2} = \begin{bmatrix} r_{2,aa}^{r} & 0 & r_{2,ac}^{r} \\ 0 & 0 & 0 \\ r_{2,ca}^{r} & 0 & r_{2,cc}^{r} \end{bmatrix}$$

(2.11)

The ratio matrices  $R_1$  and  $R_2$  express how load and PV on the middle bus are allocated between the other buses:

$$w_{B_1} = w_{B_1} + R_1 \cdot w_{B_2}, w_{B_3} = w_{B_3} + R_2 \cdot w_{B_2} \tag{2.12}$$

The weight submatrices  $w \in \mathbb{C}^{3\times 3}$ , corresponding to the elements of W representing the two CBs are updated to reflect the phase-wise addition of PV/load from the NCB  $(B_2)$  whose rows are removed.

For end bus reduction where  $B_3$  is to be removed,  $w_{B_2}$  will be updated to  $w_{B_2} + w_{B_3}$  and the rows corresponding to  $B_3$  are removed.

Following the reduction to the final set of nodes, W can be used to map the original PV/load time series profiles to the reduced set.

# 2.3 Feeder Reduction Algorithm

#### 2.3.1 Introduction

The steps of the feeder reduction of a large and complex distribution feeder are broken out next. The procedure of bus selection by the user and the algorithm is discussed (section 2.3.2). The steps of recursively removing NCB from the branches of the feeder following the analytical approach of section 2.2.3 is given in section 2.3.3. A novel approach to handling the reduction between multiphase connections with mutual coupling is discussed in section 2.3.4 based on the methodology of section 2.2.4. The weighting system to maintain solar and load variability proposed in 2.2.5 is implemented in section 2.3.5.

#### 2.3.2 Critical Bus Selection and Identification

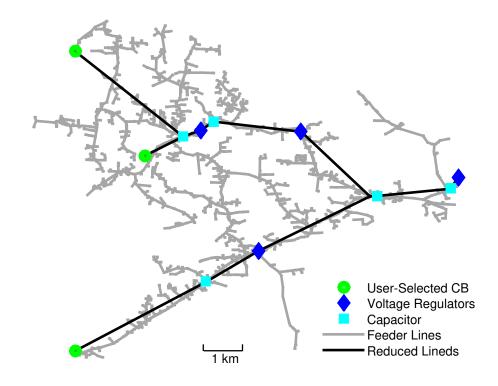

CB are defined as the buses that are to remain in the final reduced feeder configuration. While the number of CB can range from one bus to all of the buses, generally CB are a small subset of the total buses of the feeder. There are three types of CB; i) user-selected CB, ii) CB that host special equipment, and iii) topology CB.

User-selected CB are those of interest to the particular study being performed, such as the location where a large PV system is to be interconnected. CB that host special equipment are buses with shunt capacitors, voltage regulators, and distribution transformers, which are automatically classified as CB.

Based on this initial set of CB, the algorithm must select additional CB which are required to preserve the topology of the feeder. Topology CB are buses on the junctions between branches with CB. The algorithm identifies the topology of the feeder to determine where the user-selected CB or CB with special equipment are located, selects the topology CB, and determines which buses must be removed. A modified version of the recursive topology detection algorithm proposed in [34] has been adopted in this paper.

In the method, adjacent buses to any bus i, as identified through connected phases in the line data or the admittance matrix, form the full set of neighbor buses  $N_i$ . Among the neighbors of bus i, the closest one towards the substation is called the parent of bus i ( $P_i$ ). The remaining buses of  $N_i$  form its children set  $C_i$ . The offspring set of bus i, denoted by  $\Omega_i$ , is recursively defined as the union of the children of bus i ( $C_i$ ) and their offspring set i.e.  $\Omega_i = C_i \cup (\bigcup_{k \in C_i} \Omega_k)$ . The ancestor set of bus i, which is denoted by  $\Lambda_i$ , also has a recursive definition of the bus i's parent and its parent's ancestors, i.e.  $\Lambda_i = P_i \cup \Lambda_{P_i}$ .

The full algorithm is presented in **Algorithm 1**. The algorithm starts from the substation (i = 1), finds its children and updates the sets of global variables  $\Lambda$  and  $\Omega$ . The algorithm is then repeated for each child until the entire network is processed.

#### **Algorithm 1** Topology Detection

```

Initialize \Lambda_i = \emptyset and \Omega_i = \emptyset

identify any bus connected to bus i to form the neighbor set M_i.

Define the children set C_i = \{k : k \notin \{i\} \cup \Lambda_k\}

for any bus l in C_i do

let P_l = i and \Lambda_l = \{i\} \cup \Lambda_i

let i = l and run Algorithm 1

\Omega_{P_i} = \Omega_{P_i} \cup \{i\} \cup \Omega_i

end for

Return the sets \Lambda_i and \Omega_i

```

After the feeder topology is detected, among the common ancestors of each pair of critical buses, the one with higher distance from the substation is considered as the junction of those two critical buses and is added to the list of critical buses. It is notable that the substation bus must be always a critical buse.

## 2.3.3 Branch Reduction, End Bus

Following the concept of graph theory the feeder is considered as a tree where the buses and distribution lines are equivalent to vertices and edges, and the part of the feeder that interconnects the CB is the main tree which just includes the ancestors of all critical buses. The

first objective in the feeder reduction algorithm is to remove all NCB off the main tree. The loads and PV on these NCB are aggregated on the closest CB belonging to the main tree.

**Algorithm 2** elaborates how the buses off the main tree are reduced, where  $w_i \in \mathbb{R}^{(3 \times n)}$  consists of three rows of the matrix of W corresponding to the different phases of bus i.

```

Algorithm 2 Reduction Off Main Tree

```

```

Identify the feeder topology (obtain the sets \Lambda_i and \Omega_i for all buses i)

Form the set of CB

Form the set of all buses on the main tree, T = \bigcup_{i \in CB} \Lambda_i

Initialize the set of NCB: R = \emptyset

for any CB i \in T do

for any l \in C_i if \Omega_l excludes any critical bus do

let R = R \cup \{l\}, w_i = w_i + w_l, and w_l = 0

for any bus k downstream of bus i (k \in \Omega_l) do

let R = R \cup \{k\}, w_i = w_i + w_k, and w_k = 0

end for

end for

Remove the buses belonging to R from the feeder

Remove the row vectors w_r from matrix W for any r \in R

```

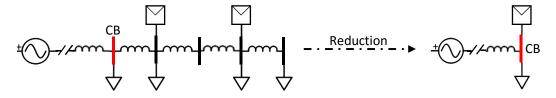

Fig. 2.2 also illustrates a case where the buses off the main tree are reduced on the CB. After this step, the remaining feeder includes all CB and some NCB which reside on the main tree.

**Figure 2.2**: A conceptual depiction of the removal of all NCB beyond a CB. The load (triangles) and PV (squares) from the removed NCB are aggregated to the CB. This process is carried out recursively for all CB off the main tree.

## 2.3.4 Main Tree Reduction, Middle Bus

The impedance that connects the remaining buses composes the characteristic impedance of the reduced circuit and thus must be aggregated as opposed to removed. The methodology as described in 2.2.4 is shown for a simple three bus system, but for larger feeders the process is carried out in the reduction by successively removing NCB parents of CB until the NCB are completely removed from the circuit. **Algorithm 3** summarizes the reduction of the NCB on the main tree.

## Algorithm 3 Reduction On Main Tree

```

Identify the new feeder topology reduced by Algorithm 2

Form the set of CB

Initialize the set of NCB: R = \emptyset

for any i \in CB do

Sort \Lambda_i based upon distance from substation ascendingly

for any k \in \Lambda_i (in order) do

if ((\{k\} \bigcup \Omega_j) - (\{i\} \bigcup \Omega_i)) which excludes any CB then

let w_i = w_i + R_2 \cdot w_k and w_{P_k} = w_{P_k} + R_1 \cdot w_k

let w_k = 0 and R = R \bigcup \{k\}

end if

end for

Remove the NCB belonging to R from the feeder

Remove the row vectors w_r from matrix W for any r \in R

```

#### 2.3.5 The Final Reduced Feeder

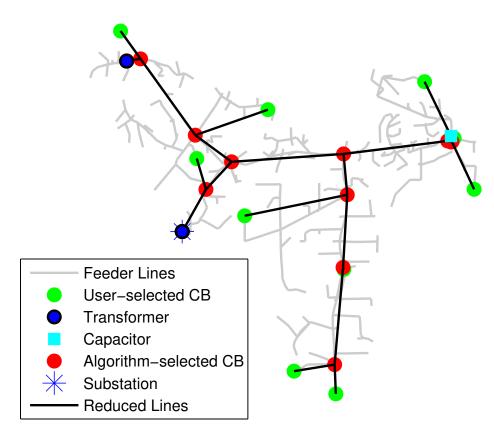

The final configuration contains only CB which are connected through a set of equivalent distribution lines. Fig. 2.3 displays the CB identified by the algorithm following the user-selection of nine CB. The algorithm chose on additional CB due to the presence of a capacitor and 9 topological CB.

The CB are composed of nodes with various weighting vectors. The final matrix W is used both to calculate the equivalent PV and load sizes and to compute the aggregate generation

and demand profiles on the final set of CB. Normalizing the generation and demand profiles based on the equivalent sizes of PV and load generates the temporal PV and load loadshapes. The reduced system contains less PV generators with larger individual capacities than the original system.

An executable to run the feeder reduction code has been uploaded to [35]. Details of the operations and limitations are given there.

**Figure 2.3**: Reduced (black) California distribution feeder overlayed on the full distribution feeder (grey). Initially nine buses were user-selected as CB and the algorithm selected the additional buses.

## 2.4 Validation

## 2.4.1 Distribution Feeder

To evaluate the accuracy of the proposed circuit reduction algorithm, a stochastic sensitivity analysis was performed on a real medium voltage (MV) California distribution feeder with 621 multi-phase buses, two distribution transformers, one large capacitor bank (1350 KVAr), 364 distributed rooftop PV systems, and 471 loads. Each load operates under the same time-series shape scaled by its peak load, while each PV time-series is uniquely determined using a sky imager according to the method introduced in [6]. The feeder lines are modeled with zero shunt capacitance, and all neutral connections are assumed to be grounded perfectly. Feeder reduction simulations are run in OpenDSS [36] for one day with a time resolution of 30s.

A one-year QSTS with 1-minute resolution for each solar deployment is the standard simulation setting that DOE considers for solar planning studies to capture effects of PV fluctuations [9]. Therefore, one-year QSTS simulations with 30-sec resolution in this paper is commensurate with the minimum requirements set by DOE. Given that these standards will guide academia and industries in future solar planning for both research and implementation projects; the authors conclude that these settings are relevant to show the reduction of the computation expenses through the proposed algorithm.

## 2.4.2 Sensitivity Analysis

#### **Error metrics**

Given the importance of voltage in QSTS simulations, errors are defined as the difference in voltage of each CB from the identical node in the full feeder configuration:  $E_j(t) = V_{\text{full}_j}(t) - V_{\text{reduced}_j}(t)$ , where j indicates a node, and t indicates a time step. Mean  $(\overline{E_j}, \overline{\overline{E}})$  absolute error metrics are used to elucidate the voltage difference as a function of the different circuit

configurations:

$$\overline{E}_j = \frac{1}{T} \Sigma_{t=1}^T |E_j(t)| \tag{2.13}$$

$$\overline{\overline{E}} = \frac{1}{J} \sum_{j=1}^{J} |\overline{E}_{j}| = \frac{1}{J} \frac{1}{T} \sum_{j=1}^{J} \sum_{t=1}^{T} |E_{j}(t)|$$

(2.14)

#### **Simulation scenarios**

The sensitivity to the following feeder conditions was analyzed: (i) Two days with the highest (01/18/2015) and lowest (12/26/2014) aggregate load; (ii) PV generation profiles from a mostly clear day (12/19/2014) and a day with overcast clouds in the morning and partly cloudy conditions in the afternoon (12/12/2014); (iii) PV penetrations of 50% and 100% where PV penetration is defined as the ratio between the installed rated PV capacity and the peak rated load on the feeder and is increased/decreased by scaling each PV system up or down by the same factor; (iv) Three different load types (constant-power, constant-impedance, and fixed-current magnitude) to observe the effect of deviating from the fixed current load used in which the algorithm. It is worth mentioning that the fixed-current magnitude load type used in OpenDSS differs from the assumption of fixed complex current which is used in the derivation.

The combination of these conditions results in  $(2 \times 2) \times 2 \times 3 = 24$  feeder configurations. For each of these 24 baseline configurations, 1,000 reduction simulations are run. For each reduction simulation, the number of user-selected CB is randomly selected between 2 and 50. The CB locations are also randomly selected. Topology CB are then selected by the algorithm as described in section 3.5. The three buses with distribution transformers or capacitor banks are always CB.

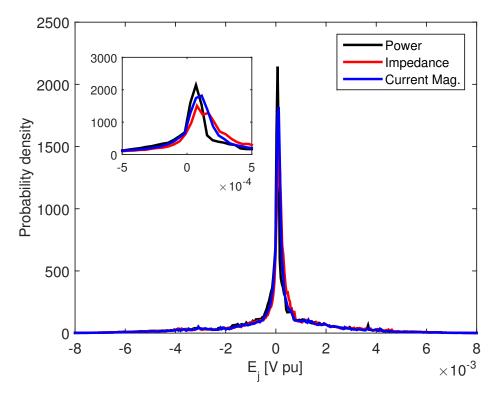

Over all j and all configurations (24,000 simulations and on average 28 CB per simulation) the root-mean square deviation (RMSD) is  $2.11 \times 10^{-4}$  p.u., mean bias error (MBE) is  $3.46 \times 10^{-4}$  p.u., and the maximum observed error is 0.0113 p.u. (or 1.13%).

## Sensitivity load type

Fig. 2.4 gives the histogram of errors for all simulations of each load type. Each load exhibits a strong peak around 0 error and errors greater than  $\pm 1 \times 10^{-3}$  p.u. occurs for less than 0.5% of all nodes. Overall the difference in error imposed by using different load types is small. Contrary to the expected behavior, the largest peak at zero error occurs for the constant power load types, followed by constant current load types and then constant impedance load types. The increase in error for constant current load types is due to the fact that the derivation assumes the current is constant in both magnitude and angle, where the OpenDSS models fixed current magnitude only.

**Figure 2.4**: PDF of error for each load type. All nodes in each simulations corresponding to each load are represented in the function (i.e 8,000 simulations  $\times \approx 50$  nodes). The inset plot provides a zoomed view of the histogram with x-axis limits of  $\pm 5 \times 10^{-4}$

## Sensitivity to loading

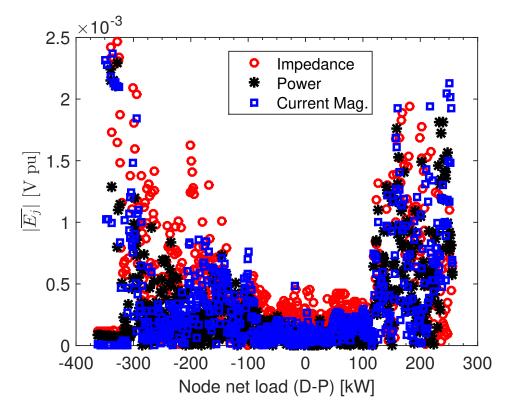

When comparing error as a function of the node net load (Fig. 2.5) we again see little change in error as a function of load type used. For all load types, the lowest error is seen for buses with near zero net load. As the net load deviates from zero, the error increase with some symmetry in both directions. The increase for large positive and negative net load is indicative of the constant current assumption used being a significant source of error, which is more noticeable for large amounts of generation/consumption.

**Figure 2.5**: Mean error of node voltage plotted as a function of net load on the bus. The mean is taken by binning all net loads in 1 W bins and averaging all errors in the bin.

#### Sensitivity to distance

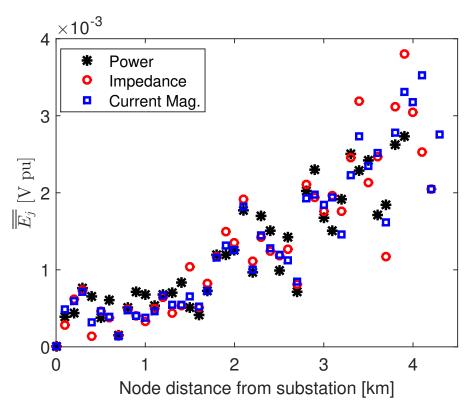

Finally, mean error as a function of distance from the substation (Fig. 2.6), supports the conclusion that the load type has little effect on the error. However, we do see a strong correlation

with increasing distance away from the substation. This behavior is consistent with intuition since the voltage at the substation is a set value dependent on the upstream conditions, whereas buses at the end of the feeder are subject to an accumulation of reduction error.

**Figure 2.6**: Mean error of node voltage plotted as a function of distance of the node from the substation. The mean is taken by binning all nodes into 100m bins and taking the average of all nodes in that bin across all simulation time steps.

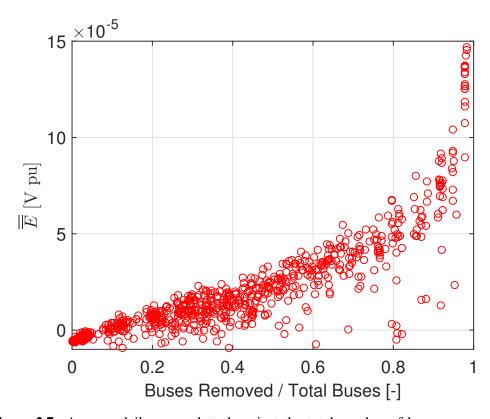

#### Sensitivity to number of critical buses

1,000 additional simulations were performed by randomly selecting number and location of CBs with the number ranging from 1 to the full set of 621. Given the small sensitivity to the parameters considered in the previous section, the analysis is carried out with constant impedance loads (highest error) on 12/26/2014. Figure 2.7 shows that, as expected, the error in voltage decreases as less buses are removed from the circuit. Non-zero error is noticed for the case of zero buses removed (i.e. the circuit is re-written with no modification), as a result of the stopping

criteria of the solver.

**Figure 2.7**: Average daily error plotted against the total number of buses removed in the simulation. Each point corresponds to error averaged across all time steps and all buses in each simulation, as defined by equation 2.14. 1,000 simulations were configured under HS50 with constant impedance loads.

# **2.4.3** Computational Expense

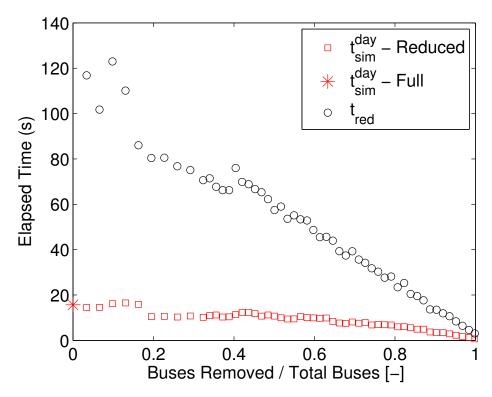

Since the ultimate objective of feeder reduction is increased computational speed, the computational cost associated with reducing and simulating different sized feeders was investigated. Simulations were run on a desktop with an Intel(R) Core(TM) i7-4770 processor and 32 GB RAM. Fig. 2.8 plots the computational time required to reduce the 621 bus feeder as well as the computational time to simulate a full day of QSTS at 30 s resolution for the resulting feeder. Both lines show an increase in time with an increase in the number of buses remaining in the system with slopes 0.18 and 0.021 seconds/bus for reduction and simulation, respectively.

Fig. 2.8 indicates that the time to reduce the feeder is about 9 times that of a short QSTS simulation run. However, the reduction time is a one-time cost which quickly pays back when long-term or parametric studies are conducted. For year long simulations at 30 s resolution (Table 3.1) simulation time decreases by 31% for only a 20% reduction of buses. Savings greater than 90% are observed for system that reduce 96% of buses. At 621 buses the present feeder was relatively small; larger relative computing time savings are expected for larger feeders. It is noted,  $t_red$  increases as fewer buses are reduced. The increase in time is a result of the structure of the algorithm which loops through each bus CB during each step of the reduction. More CB leads to more loops in topology detection, end bus reduction, critical bus reduction, as well as the conversion of the circuit back to a form which can be interpreted by a power flow solver. While the latter part is specific to the OpenDSS solver, it is expected to scale similarly for other solvers.

**Table 2.1**: Computational expense associated with reduction of the original feeder ( $t_{red}$ ) and simulation of the reduced feeder ( $t_{sim}$ ) as presented in Fig. 2.8. The yearly simulation time is extrapolated from the one-day simulation time for 30s time steps.

| User selected buses | % red. | $t_{\text{red}}$ (s) | $t_{\rm sim}^{\rm day}$ (s) | $t_{\rm sim}^{\rm year}$ (min) | $1 - \frac{t_{\text{sim}}^{\text{year}_i}}{t_{\text{sim}}^{\text{year}_1}}$ |

|---------------------|--------|----------------------|-----------------------------|--------------------------------|-----------------------------------------------------------------------------|

| 621 (Full)          | -      | -                    | 15.68                       | 95.4                           | -                                                                           |

| 500                 | 20%    | 86.0                 | 10.5                        | 65.0                           | 31%                                                                         |

| 400                 | 36%    | 66.2                 | 10.3                        | 63.6                           | 33%                                                                         |

| 300                 | 52%    | 53.6                 | 9.5                         | 58.4                           | 39%                                                                         |

| 200                 | 67%    | 37.4                 | 7.5                         | 46.0                           | 52%                                                                         |

| 100                 | 84%    | 13.7                 | 5.6                         | 34.2                           | 64%                                                                         |

| 50                  | 92%    | 10.9                 | 3.4                         | 20.7                           | 78%                                                                         |

| 20                  | 96%    | 6.8                  | 1.9                         | 9.4                            | 90%                                                                         |

| 10                  | 98%    | 4.6                  | 1.2                         | 7.6                            | 92%                                                                         |

| 1                   | 99.8%  | 3.1                  | 0.6                         | 3.7                            | 96%                                                                         |

**Figure 2.8**: Computation time to reduce the 621 bus feeder to a subset of CB (black) and the QSTS time (red) associated with the reduced feeder for simulating one day at 30 s timesteps. A different simulation set was used to control for time delays due to communication with external storage devices.

## 2.5 Conclusion

A comprehensive method to reduce large realistic distribution feeders is proposed. The algorithm is sophisticated enough to handle complex configurations such as

- 1. multiphase connections through out the entire network

- 2. mutual coupling between multiphase unbalanced lines

- 3. unbalanced loads and generation

- 4. spatial variation in load and generation

through manipulation of the full impedance matrix. The method is also unique through the

retention of geographic variance in both PV generation and load consumption by a phase and impedance-weighted impact.