# UCLA UCLA Electronic Theses and Dissertations

### Title

Resource and Data Management in Accelerator-Rich Architectures

Permalink https://escholarship.org/uc/item/56h233jw

**Author** Huang, Muhuan

Publication Date 2016

Peer reviewed|Thesis/dissertation

UNIVERSITY OF CALIFORNIA

Los Angeles

Resource and Data Management in Accelerator-Rich Architectures

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Muhuan Huang

2016

© Copyright by Muhuan Huang 2016

#### Abstract of the Dissertation

#### Resource and Data Management in Accelerator-Rich Architectures

by

Muhuan Huang Doctor of Philosophy in Computer Science University of California, Los Angeles, 2016 Professor Jingsheng Jason Cong, Chair

In many domains, accelerators—such as graphic processing units (GPUs) and field programmable gate arrays (FPGAs)—provide a significantly higher performance than general-purpose processors and at a much lower power. Accelerator-rich architectures are thus much more energy-efficient and are becoming mainstream.

This dissertation investigates two important keys to the performance and power efficiency of accelerator-rich architectures—resource and data management. Three broad classes of accelerator-rich architectures are considered: chip-level accelerator-rich architectures such as systems-on-chips(SoC), node-level accelerator-rich architectures, and cluster-level accelerator-rich architectures.

We first study SoC resource management for a broader class of streaming applications. On accelerator-rich SoCs, where multiple computation kernels space-share a single chip, we target the exploration of tradeoffs of on-chip resources and system performance, and find the best combination of accelerator implementations and data communication channel implementations to realize the application functionality.

We continue our study of node-level accelerator-rich architectures where we consider orchestrating two kinds of computation resources, CPU and accelerator, in the PCIeintegrated CPU-accelerator platform and explore the CPU-FPGA collaboration approach to improve application performance.

Then we study the resource allocation problem on accelerator-rich clusters, where accelerators are time-shared among multiple tenants. Unlike traditional cluster resource management, we propose to consider accelerators as the first-class citizen in the cluster resource pool, and develop an accelerator-centric resource scheduling policy to enable fine-grained accelerator sharing among multiple tenants.

Finally, we investigate data shuffling on accelerator-rich clusters and evaluate the possibility of using accelerators during data shuffling. We find that although data shuffling involves a large amount of computation, using accelerators does not necessarily improve system performance due to the data serialization and deserialization overhead introduced by accelerators.

The dissertation of Muhuan Huang is approved.

Wotao Yin

Wei Wang

Tyson Condie

Jingsheng Jason Cong, Committee Chair

University of California, Los Angeles 2016

To my parents

## TABLE OF CONTENTS

| 1        | Intr           | oduction                                                         | 1 |

|----------|----------------|------------------------------------------------------------------|---|

|          | 1.1            | Chip-Level Resource and Data Management Challenges               | 4 |

|          | 1.2            | Node-Level Resource Management Challenges                        | 7 |

|          | 1.3            | Cluster-Level Resource and Data Management Challenges            | 7 |

|          | 1.4            | Dissertation Statement                                           | 8 |

|          | 1.5            | Organization                                                     | 9 |

| <b>2</b> | Bac            | ground                                                           | 0 |

|          | 2.1            | Chip-Level Programming Model                                     | 0 |

|          |                | 2.1.1 Synchronous Data Flow Graph                                | 0 |

|          |                | 2.1.2 Homogeneous Synchronous Data Flow Graph                    | 1 |

|          |                | 2.1.3 Throughput Definition                                      | 2 |

|          | 2.2            | Chip-Level Design Space Exploration with High Level Synthesis 13 | 3 |

|          |                | 2.2.1 Design Space Exploration                                   | 3 |

|          |                | 2.2.2 High Level Synthesis                                       | 5 |

|          | 2.3            | Node-Level CPU-Accelerator Orchestration                         | 5 |

|          |                | 2.3.1 Dataflow/Streaming Execution Model                         | 5 |

|          |                | 2.3.2 CPU and GPU Coordination 15                                | 5 |

|          | 2.4            | Cluster-Level Programming Model and Resource Management 16       | 6 |

|          |                | 2.4.1 Cluster-Level Programming Model                            | 6 |

|          |                | 2.4.2 Cluster-Level Resource Management                          | 7 |

|          | 2.5            | Cluster-Level Data Sort and Shuffle                              | 9 |

| 3        | $\mathbf{Chi}$ | p-Level Resource and Data Management                             | 1 |

|          | 3.1            | Introduction                                                     | 1 |

|          | 3.2            | A Motivation Example                                             | 2 |

|   | 3.3 | Syster | n Mapping                                             | 23 |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | 3.3.1  | Implementation Library Constraints                    | 25 |

|   |     | 3.3.2  | Scheduling Constraints From Computation Modules       | 27 |

|   |     | 3.3.3  | Scheduling Constraints From Communication Channels    | 28 |

|   |     | 3.3.4  | Problem Statement                                     | 30 |

|   | 3.4 | Propo  | sed Approach: ST-Syn                                  | 31 |

|   |     | 3.4.1  | Schedulability Checking                               | 32 |

|   |     | 3.4.2  | Iterative Improvement                                 | 33 |

|   |     | 3.4.3  | Update Scheduling Graph                               | 35 |

|   |     | 3.4.4  | Complexity of ST-Syn                                  | 36 |

|   |     | 3.4.5  | Alternative Solution using Integer Linear Programming | 36 |

|   | 3.5 | Exper  | iments                                                | 37 |

|   |     | 3.5.1  | Settings                                              | 37 |

|   |     | 3.5.2  | FIFO-based Merge Sort                                 | 38 |

|   |     | 3.5.3  | MPEG4                                                 | 40 |

|   |     | 3.5.4  | Overall Speedup and Area Overhead                     | 41 |

|   | 3.6 | Conclu | usion                                                 | 41 |

| 4 | Noc | le-Lev | el CPU-Accelerator Orchestration                      | 43 |

|   | 4.1 | Introd | uction                                                | 43 |

|   | 4.2 | CPU-   | FPGA Co-Scheduling                                    | 44 |

|   |     | 4.2.1  | Dataflow Execution Model                              | 44 |

|   |     | 4.2.2  | Proposed Runtime Thread Allocation Strategy           | 45 |

|   | 4.3 | A Cas  | e Study of In-Memory Samtool Sorting                  | 46 |

|   |     | 4.3.1  | Samtool In-Memory Sorting                             | 46 |

|   |     | 4.3.2  | Experiment Setup and Initial Profiling                | 47 |

|   |     | 4.3.3  | Accelerator Design and Performance                    | 48 |

|   |       | 4.3.4          | FPGA Accelerator Integration with CPU                | 49  |

|---|-------|----------------|------------------------------------------------------|-----|

|   |       | 4.3.5          | Performance of Samtool Sorting                       | 54  |

|   |       | 4.3.6          | Parallelizing the Read Stage                         | 55  |

|   |       | 4.3.7          | Dataflow-Samtools                                    | 57  |

|   |       | 4.3.8          | Overall Performance                                  | 60  |

|   | 4.4   | More C         | Case Studies                                         | 63  |

|   |       | 4.4.1          | Changing Input format                                | 63  |

|   |       | 4.4.2          | Changing Storage Type                                | 64  |

|   | 4.5   | Acceler        | rator Designs                                        | 64  |

|   | 4.6   | Conclu         | usions                                               | 65  |

| - | Class |                |                                                      | 0.0 |

| 5 |       |                | evel Resource Management                             |     |

|   | 5.1   | Introdu        | uction                                               | 66  |

|   | 5.2   | System         | n Overview                                           | 67  |

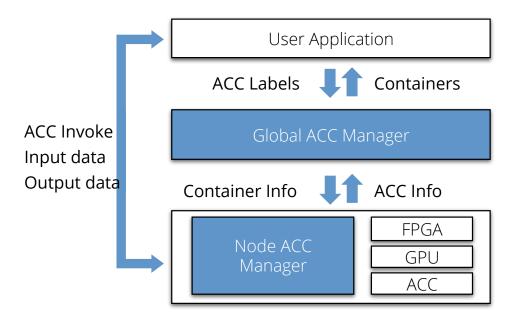

|   | 5.3   | Global         | Accelerator Manager                                  | 69  |

|   | 5.4   | Experi         | iments                                               | 71  |

|   |       | 5.4.1          | Experimental Setup                                   | 71  |

|   |       | 5.4.2          | GAM Analysis                                         | 72  |

|   | 5.5   | Offline        | Scheduling Formulation                               | 74  |

|   |       | 5.5.1          | Problem Formulations                                 | 74  |

|   |       | 5.5.2          | ILP formulations                                     | 77  |

|   |       | 5.5.3          | Complexity Analysis                                  | 78  |

|   |       | 5.5.4          | Discussions                                          | 78  |

|   |       | 5.5.5          | Related Work on Offline Resource and Task Scheduling | 79  |

|   | 5.6   | Conclu         | isions                                               | 80  |

| C |       | , <del>.</del> |                                                      | 0.0 |

| 6 |       |                | evel Data Shuffling                                  | 82  |

|   | 6.1   | Introdu        | uction                                               | 82  |

|    | 6.2   | Exper  | iment Setup and Initial Profiling                                    | 83 |

|----|-------|--------|----------------------------------------------------------------------|----|

|    |       | 6.2.1  | Data Shuffling in Spark                                              | 83 |

|    |       | 6.2.2  | Initial Terasort Profiling                                           | 83 |

|    |       | 6.2.3  | Acceleration Opportunities                                           | 85 |

|    |       | 6.2.4  | Sorting TeraFormat Records in C++ and Java                           | 86 |

|    | 6.3   | Using  | Accelerators in Spark Shuffling                                      | 87 |

|    |       | 6.3.1  | Terasort with Customized Java/Scala Sorting Routines $\ . \ . \ .$ . | 87 |

|    |       | 6.3.2  | Terasort with Customized C++ Sorting Routines $\ldots \ldots \ldots$ | 88 |

|    |       | 6.3.3  | Reducing Memory Footprint                                            | 89 |

|    |       | 6.3.4  | Performance Summary                                                  | 90 |

|    | 6.4   | Conclu | usions                                                               | 91 |

| 7  | Con   | clusio | ns and Future Directions                                             | 92 |

| Re | efere | nces . |                                                                      | 94 |

## LIST OF FIGURES

| 1.1 | Xilinx Zynq-7000 EPP dual-core ARM Cortex-A9 + FPGA                                                                                                                                                                                                                                                                                                                                           | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Intel Xeon + FPGA platform                                                                                                                                                                                                                                                                                                                                                                    | 2  |

| 1.3 | Our local cluster with FPGA cards                                                                                                                                                                                                                                                                                                                                                             | 3  |

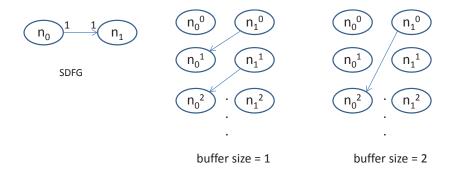

| 2.1 | An example of SDFGs. Producer/consumer rates are labeled at the begin-<br>ning/end of the edges.                                                                                                                                                                                                                                                                                              | 10 |

| 2.2 | The HSDFG converted from SDFG in Fig. 2.1                                                                                                                                                                                                                                                                                                                                                     | 12 |

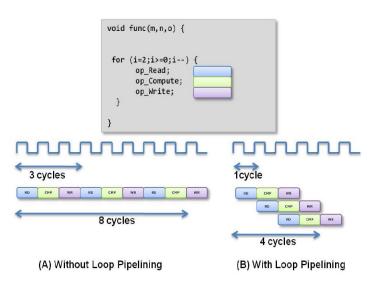

| 2.3 | Module implementation with and without pipelining. This figure is adopted from [viv]                                                                                                                                                                                                                                                                                                          | 13 |

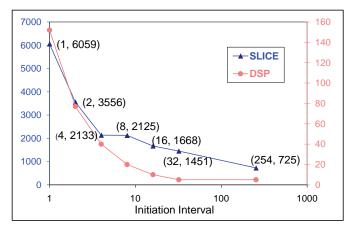

| 2.4 | Tradeoff between performance and area of one module in benchmark "fil-<br>terbank."                                                                                                                                                                                                                                                                                                           | 14 |

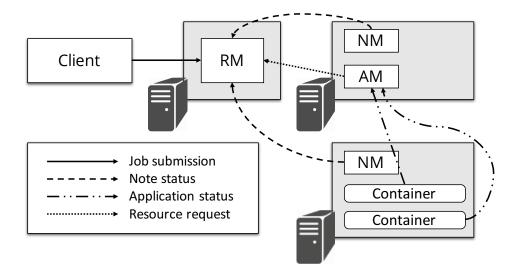

| 2.5 | Example YARN architecture showing a client submitting jobs to the global resource manager.                                                                                                                                                                                                                                                                                                    | 17 |

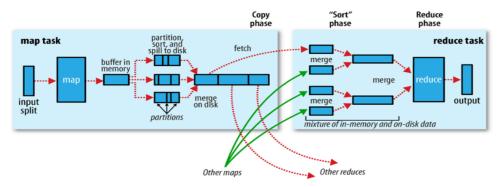

| 2.6 | Data Sorting and Shuffling in MapReduce. This figure is adopted from                                                                                                                                                                                                                                                                                                                          |    |

|     | [Whi12]                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

| 3.1 | The proposed system synthesis framework                                                                                                                                                                                                                                                                                                                                                       | 21 |

| 3.2 | A motivating example. In scenario 1, buffer size is not considered during<br>module selection. The implementation with minimum logic is selected. In<br>scenario 2, buffer size is considered together with module selection. In both<br>cases, these are feasible schedules that can meet the system throughput<br>requirement. However in scenario 2 with the consideration of buffer size, |    |

|     | the selected implementation can reduces BRAM use by 20%                                                                                                                                                                                                                                                                                                                                       | 22 |

| 3.3 | An example of module replication. Module throughput can be further<br>improved by duplicating the modules and adding the corresponding split<br>and join logic                                                                                                                                                                                                                                | 25 |

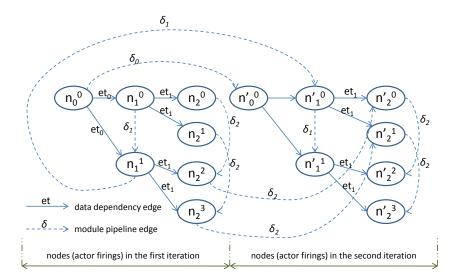

| 3.4 | Scheduling graph for SDFG in Fig. 2.1. It contains all the actor firings in                                                                                                                                                                                                                                                                                                                   | 20 |

|     |                                                                                                                                                                                                                                                                                                                                                                                               |    |

two iterations. Detailed explanations of the edges can be found in Sec. 3.3.2. 27

| 3.5  | An example of buffer-constrained edges. An SDFG is shown on the left.                    |    |

|------|------------------------------------------------------------------------------------------|----|

|      | Buffer-constrained edges are shown in the scheduling graph when buffer                   |    |

|      | size is 1 and 2 respectively. The producer rate and consumer rate is 1. $\ .$            | 29 |

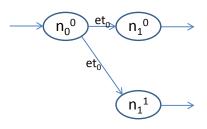

| 3.6  | An example of part of an $\epsilon\text{-critical path.}$ An improved hardware module    |    |

|      | of $n_0$ will contribute to both paths in the graph. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 34 |

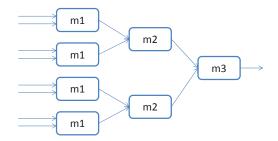

| 3.7  | An example of merge sort to sort 8 values. $m1$ takes one value from each                |    |

|      | of its two input channels, reorders the two values and then sends them out               |    |

|      | to $m2$ . $m2$ takes two values from each of its two input channels, merges              |    |

|      | them into one sorted stream that contains 4 values. $m3$ works in a similar              |    |

|      | fashion and outputs a sorted stream that contains 8 values                               | 38 |

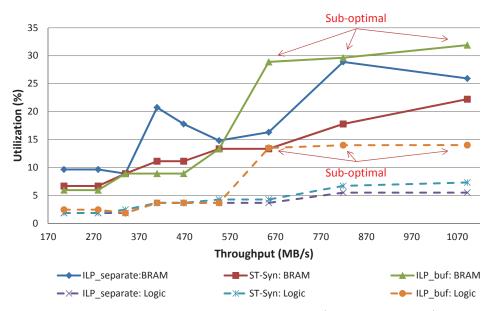

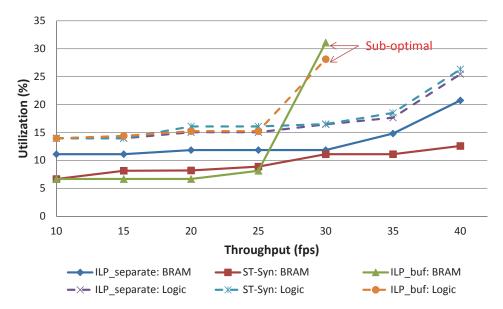

| 3.8  | FIFO-based merge sort: area utilization (logic & BRAM) under different                   |    |

|      | throughput settings. 16384 values are merged. Runtime of ILP_buf is                      |    |

|      | limited to up to 2 hours, and thus ILP_buf only generates sub-optimal                    |    |

|      | results                                                                                  | 39 |

| 3.9  | MPEG4: area utilization under different throughput settings. Runtime of                  |    |

|      | $\rm ILP\_buf$ is limited up to 2 hours. ILP\_buf does not return a feasible integer     |    |

|      | solution at 2 hours when throughput is 35 fps and 40 fps                                 | 40 |

| 3.10 | Overall speedup and area overhead                                                        | 41 |

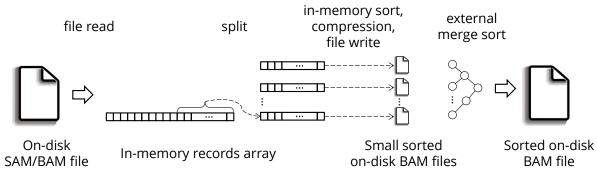

| 4.1  | An overview of the sort routine in Samtools                                              | 47 |

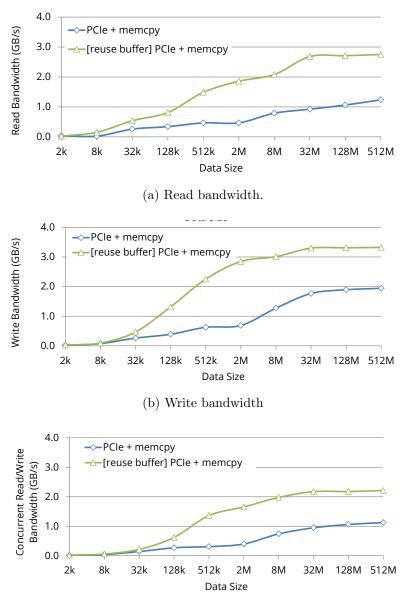

| 4.2  | Effective data transfer bandwidth between CPU and FPGA through PCIe.                     | 51 |

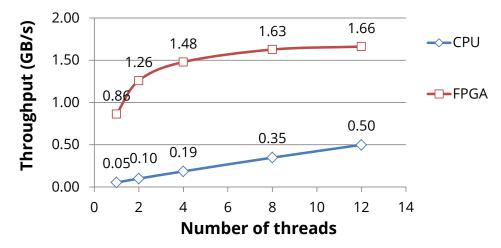

| 4.3  | Compression and CRC task throughput measured from host CPU side.                         |    |

|      | Measured FPGA performance includes data transfer time between the                        |    |

|      | CPU and the FPGA                                                                         | 53 |

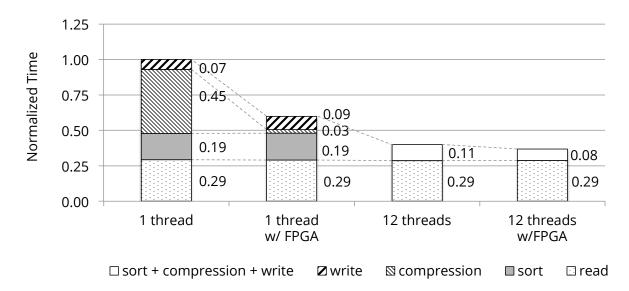

| 4.4  | Normalized time for in-memory Samtool sorting                                            | 54 |

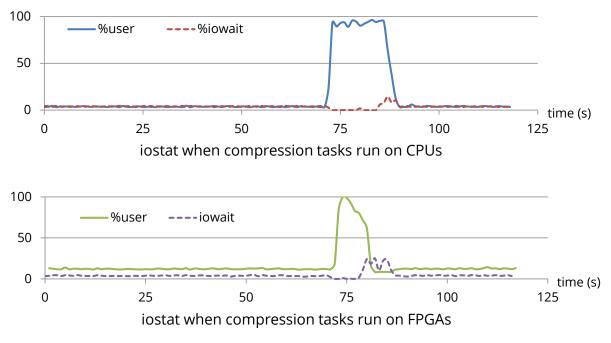

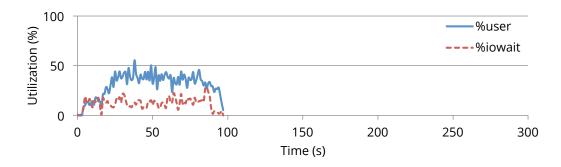

| 4.5  | System iostat during 12-thread in-memory sorting.                                        | 55 |

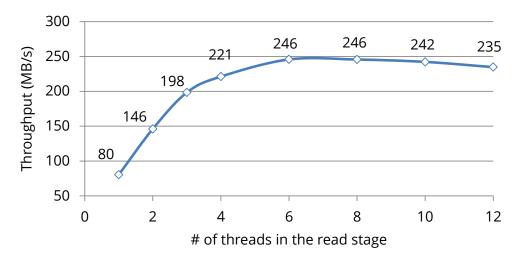

| 4.6  | SAM file read throughput on SSD.                                                         | 56 |

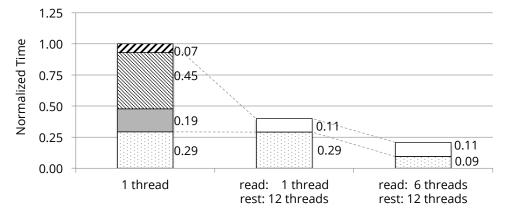

| 4.7  | Normalized execution time for in-memory Samtool sorting using different                  |    |

|      | number of threads.                                                                       | 56 |

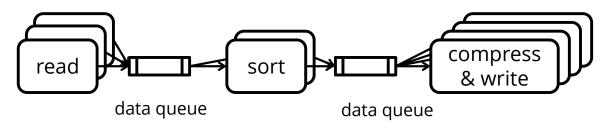

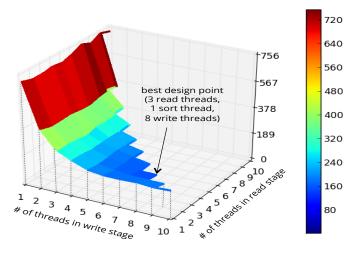

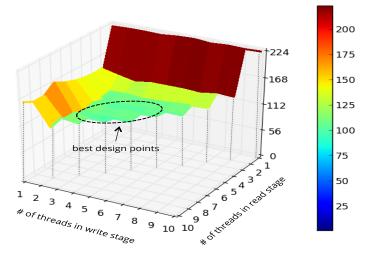

4.8 A dataflow model for in-memory sorting. In this example, 3, 2 and 4 threads are used to execute *read*, *sort* and *write* stages, respectively. Data between stages are organized using multi-input and multi-output queues. 57

| 4.9  | Design space exploration on thread allocation for Dataflow-Samtool sort-                        |       |

|------|-------------------------------------------------------------------------------------------------|-------|

|      | ing. The number of threads in <i>sort</i> stage equals to $(12 - \# of threads in read starts)$ | tage- |

|      | # of threads in write stage). Since we need to maintain at least one                            |       |

|      | thread for each stage, the range of $x$ and $y$ axes are $[1, 10]$ . The $z$ axis               |       |

|      | shows the execution time in seconds using different colors. $\ldots$                            | 58    |

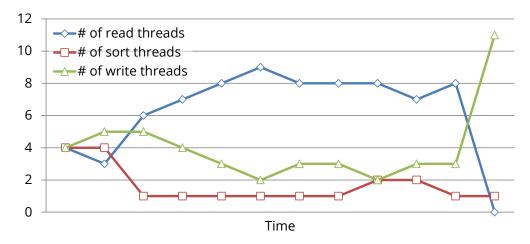

| 4.10 | Runtime adaptive thread distribution on our CPU-FPGA platform                                   | 59    |

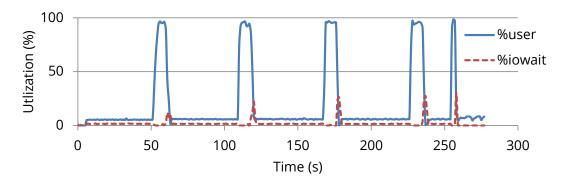

| 4.11 | System iostat during 12-thread in-memory sorting in Samtool, dataflow-                          |       |

|      | Samtool, and dataflow-Samtool-FPGA                                                              | 61    |

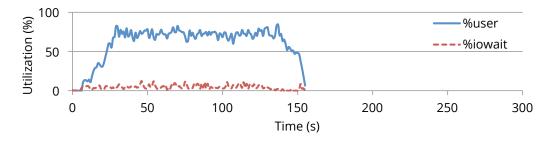

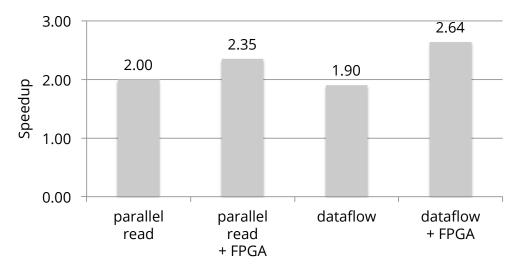

| 4.12 | Overall speedup of different optimizations over original 12-thread Samtool                      |       |

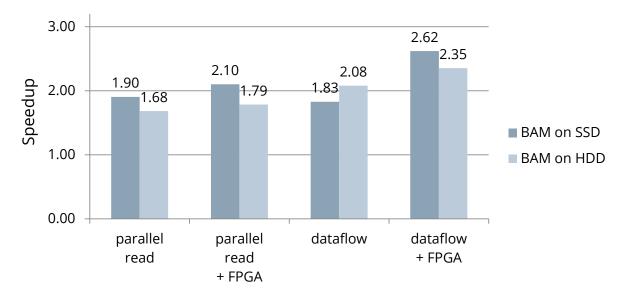

|      | in-memory sorting                                                                               | 62    |

| 4.13 | Overall speedup of different optimizations over original 12-thread Samtool                      |       |

|      | in-memory sorting using different configurations                                                | 64    |

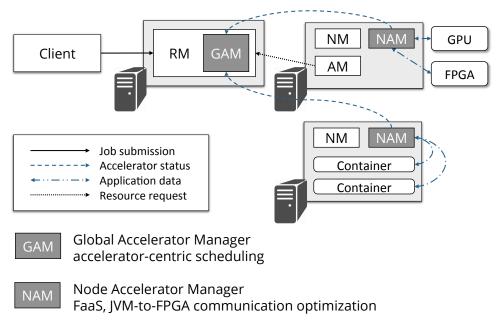

| 5.1  | Overview of Blaze runtime system.                                                               | 68    |

| 5.2  | Blaze execution flow.                                                                           | 69    |

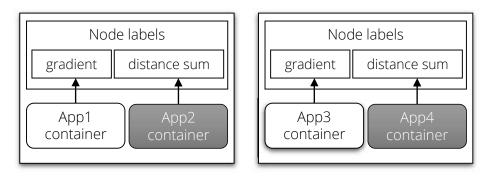

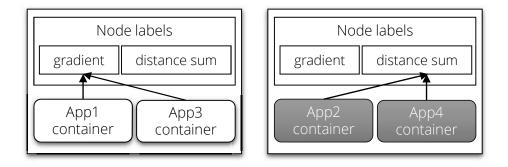

| 5.3  | Different resource allocation policies. In this example, each cluster node                      |       |

|      | has one FPGA platform and two accelerator implementations, "gradient"                           |       |

|      | and "distance sum". Four applications are submitted to the cluster, re-                         |       |

|      | questing different accelerators                                                                 | 70    |

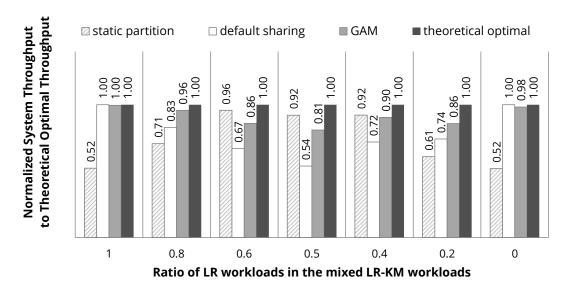

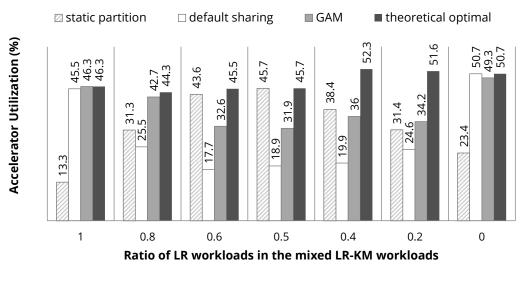

| 5.4  | Normalized system throughput and accelerator utilization of mixed work-                         |       |

|      | loads on a CPU-FPGA cluster.                                                                    | 73    |

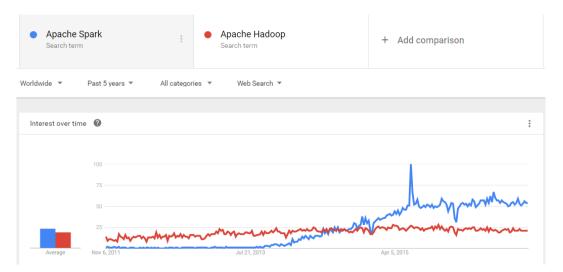

| 6.1  | Google Trend for Apache Spark and Apache Hadoop. Data was collected                             |       |

|      | from www.google.com/trends on November 6, 2016                                                  | 84    |

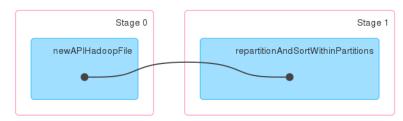

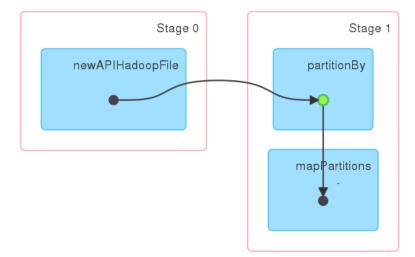

| 6.2  | RDD computation lineage for the code in Listing 1                                               | 84    |

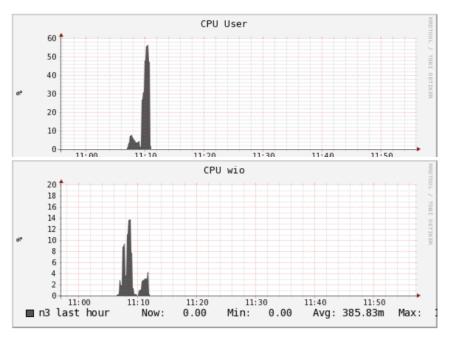

| 6.3  | System metrics of a node when running 64 GB Spark Terasort on 8-node                            |       |

|      | cluster                                                                                         | 84    |

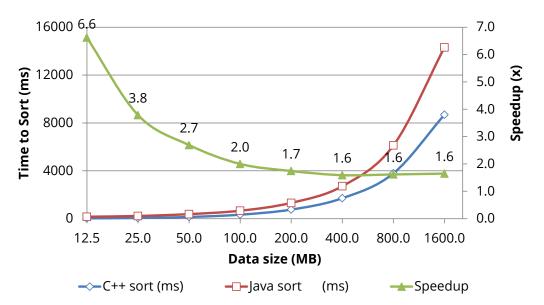

| 6.4 | Performance comparison on sorting routines written in C++ and Java. |    |  |

|-----|---------------------------------------------------------------------|----|--|

|     | Speedup of C++ sorting over Java sorting is also measured. $\hdots$ | 87 |  |

| 6.5 | RDD computation lineage for the code in listing 2                   | 89 |  |

## LIST OF TABLES

| 3.1 | Denotation of variables.                                                 | 24 |

|-----|--------------------------------------------------------------------------|----|

| 4.1 | FPGA resource utilization of compression and cyclic redundancy check     |    |

|     | accelerator.                                                             | 48 |

| 4.2 | FPGA accelerator comparison                                              | 49 |

| 4.3 | Comparisons between static thread allocation and adaptive thread alloca- |    |

|     | tion on application time (seconds).                                      | 60 |

| 4.4 | Application execution time for different datasets (minutes)              | 63 |

| 5.1 | FPGA accelerator performance profile.                                    | 72 |

| 6.1 | Spark configurations in Terasort.                                        | 85 |

| 6.2 | Performance of sorting 100GB TeraFormat records                          | 90 |

### Acknowledgments

First and foremost, I wish to express my deepest gratitude to my advisor, Professor Jason Cong, for his continuous support and guidance throughout my education. I first met Jason during an undergraduate exchange program at UCLA in my junior year. Jason guided me into the area of FPGA acceleration and has sparked my desire to pursue research in the field of customized computing. Throughout my PhD study, Jason has provided many insightful suggestions for my research projects. He also generously provided various amazing opportunities towards conducting better research and producing better industrylevel products. It is my great fortune to have him as my advisor.

I wish to express my appreciation to my doctoral committee members, Professor Tyson Condie, Professor Wei Wang, and Professor Wotao Yin, for their time, interest and advice to improve the quality of this dissertation. I especially wish to thank Tyson for his guidance on the runtime of large-scale distributed data processing system.

I also wish to thank all my collaborators at UCLA, especially Zhenman Fang, Karthik Gururaj, Hui Huang, Matteo Interlandi, Sen Li, Di Wu, Bingjun Xiao, Peng Zhang and Yi Zou. They helped to shape my ideas and research. It has been a true blessing to work with these brilliant people.

In addition, I wish to thank my friends at UCLA VAST lab for supporting me throughout my lengthy graduate school and making the past six years much more enjoyable. I wish to thank the staffs in the computer science department for all their help during my study here. I especially wish to thank Alexandra Luong for taking care of my appointments every month, and Janice Martin-Wheeler for proofreading all my paper submissions.

Beyond UCLA, I wish to thank the fellow researchers at HP Labs for the most rewarding internship experience they have given me. I have been privileged to work with many amazing people there, which has certainly brought out the best in me. I especially wish to thank Kevin Lim who helped mentor me during my times at HPL.

Last but certainly not least, I wish to express my deep appreciation for my parents, Yan and Feng. They have supported me all throughout my life, allowing me to seek my own path, providing me security and guiding me in the moments of confusion. I would not be where I am today without them.

This work is partially supported by the Center for Domain Specic Computing under the NSF InTrans Award CCF1436827, funding from CDSC industrial partners including Baidu, Fujitsu Labs, Google, Huawei, Intel, IBM Research Almaden, and Mentor Graphics; C-FAR, one of the six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; grants NSF IIS-1302698 and CNS-1351047; and U54EB020404 awarded by NIH Big Data to Knowledge (BD2K).

### Vita

| 2010        | B.S. Electronics & Information Engineering,    |

|-------------|------------------------------------------------|

|             | Xi'an Jiaotong University, China               |

| 2010 - 2016 | Ph.D. Student, Department of Computer Science, |

|             | University of California, Los Angeles          |

### PUBLICATIONS

Muhuan Huang, Di Wu, Cody Hao Yu, Zhenman Fang, Matteo Interlandi, Tyson Condie, and Jason Cong, "Programming and Runtime Support to Blaze FPGA Accelerator Deployment at Datacenter Scale", *Symposium on Cloud Computing (SOCC)*, 2016.

Jason Cong, Muhuan Huang, Peichen Pan, Di Wu, and Peng Zhang, "Software Infrastructure for Enabling FPGA-Based Accelerator in Data Centers: Invited Paper", *International Symposium on Low Power Electronics and Design (ISLPED)*, 2016.

Jason Cong, Muhuan Huang, Di Wu, and Cody Hao Yu, "Invited-Heterogeneous Datacenters: Options and Opportunities", *Design Automation Conference (DAC)*, 2016.

Peng Zhang, Muhuan Huang, Bingjun Xiao, Hui Huang, and Jason Cong, "CMOST: a System-Level FPGA Compilation Framework", *Design Automation Conference (DAC)*, 2015.

Muhuan Huang, Kevin Lim, and Jason Cong, "A Scalable High-Performance Customized Priority Queue", International Conference on Field Programmable Logic and Applications (FPL), 2014. Jason Cong, Muhuan Huang, and Peng Zhang, "Combining Computation and Communication Optimizations in System Synthesis for Streaming Applications", International Symposium on Field Programmable Gate Arrays (FPGA), 2014.

Yu-Ting Chen, Jason Cong, Mohammad Ali Ghodrat, Muhuan Huang, Chunyue Liu, Bingjun Xiao, and Yi Zou, "Accelerator-Rich CMPs: From Concept to Real Hardware", International Conference on Computer Design (ICCD), 2013.

Jason Cong, Milos Ercegovac, Muhuan Huang, Sen Li, and Bingjun Xiao, "Energy-Efficient Computing using Adaptive Table Lookup based on Nonvolatile memories", *International Symposium on Low Power Electronics and Design (ISLPED)*, 2013.

Jason Cong, Muhuan Huang, Bin Liu, Peng Zhang, and Yi Zou, "Combining Module Selection and Replication for Throughput-Driven Streaming Programs", *Conference on Design, Automation and Test in Europe (DATE)*, 2012.

Jason Cong, Karthik Gururaj, Muhuan Huang, Sen Li, Bingjun Xiao, and Yi Zou, "Domain-Specific Processor with 3D Integration for Medical Image Processing", *International Conference on Application-specific Systems, Architectures and Processors (ASAP)*, 2011.

Jason Cong, Muhuan Huang, and Yi Zou, "Accelerating Fluid Registration Algorithm on Multi-FPGA Platforms", *International Conference on Field Programmable Logic and Applications (FPL)*, 2011.

Jason Cong, Muhuan Huang, and Yi Zou, "3D Recursive Gaussian IIR on GPU and FPGAs — A Case for Accelerating Bandwidth-bounded Applications", *Symposium on Application Specific Processors (SASP)*, 2011.

### CHAPTER 1

### Introduction

The last decade has witnessed tremendous changes in processor and platform designs, shifting from higher frequency processors to multi-core processors, and more recently shifting in favor of accelerator-rich architectures. As pointed out in [CSR11, CGG12], there often exists a significantly large performance gap between an entirely customized solution and a general-purpose one. The difference in the case study of the 128-bit key AES encryption algorithm implies a performance/energy efficiency gap of roughly 3 million. In their study, an investigation of the energy breakdown of the CPU pipeline components reveals that the majority of the energy consumption (i.e., 64%) is attributable to supporting the flexible instruction-oriented model of the general-purpose core, and not for performing actual computations.

Accelerator-rich architectures have two major advantages over traditional generalpurpose processing architectures. On one hand, accelerators such as GPUs and FPGAs are massively parallel architectures and thus can provide significant higher processing functionality than CPUs; they can help to meet and even exceed our ever-increasing processing needs. On the other hand, since energy consumption is becoming one of the major limiting factors for scaling up the processing capability of computation platforms (e.g., power-constrained or battery-operated systems-on-chips) and data centers, designers are looking beyond general-purpose processors to leverage accelerators that increase the performance per-watt metric of the applications and reduce the energy consumption of the system.

As a result, accelerators have found their home in many computing architectures.

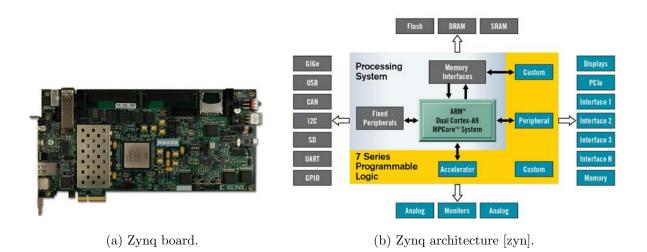

Single-Chip Level Designs: For example, system-on-chip (SoC) FPGAs and SoC GPUs are widely available on the market. Major FPGA vendors, such as Xilinx [xil] and Altera [alt], provide SoC FPGAs which integrate an ARM-based processing system

Figure 1.1: Xilinx Zynq-7000 EPP dual-core ARM Cortex-A9 + FPGA.

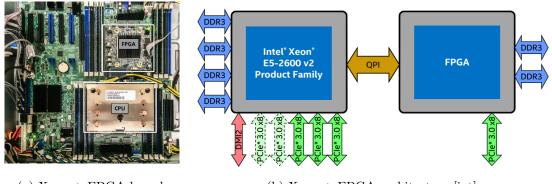

(a) Xeon + FPGA board.

(b) Xeon + FPGA architecture [int].

Figure 1.2: Intel Xeon + FPGA platform.

and the on-chip programmable logics on a same chip. Figure 1.1 shows an example of the Xilinx SoC that contains a dual-core ARM Coretx-A9 and an FPGA [zyn].

Server Node Level Platforms: Server vendors have been looking beyond generalpurpose servers and aim to provide an easy-to-customize server node to boost the performace and power efficiency. For example, since early 2013, HP has been building a line of high-efficiency servers called Moonshot. The servers can be customized to embed GPUs, DSPs or FPGAs, and thus can provide the most resourceful systems with a minimum of space. More recently, Intel has built an Xeon + FPGA platform that links CPU and FPGA together through Quick Path Interconnect (QPI) so that they can share memory. Figure 1.2 demonstrates the Xeon + FPGA platform. A quantitative comparison between the QPI-based CPU-FPGA system and PCIe-based CPU-FPGA system can be

Figure 1.3: Our local cluster with FPGA cards.

found in [CCF16].

Datacenter Level Solutions: Cloud computing vendors (e.g., Amazon Web Service) have incorporated GPUs in their platforms. FPGAs are also becoming popular in the cloud environment. Recently the Bing search engine from Microsoft [PCC14] demonstrated 2X better system throughput when its 1632-node servers are equipped with FP-GAs. At UCLA, we also built a local cluster with FPGA boards as shown in Figure 1.3. The cluster has 20 CPU nodes and 8 of them have PCIe integrated FPGA boards. Considering that there is one FPGA board per server, it is not a trivial task to manage all the FPGAs in the system.

Such accelerator-rich architectures, with their recent increased system heterogeneity, bring new challenges in accelerator and data management. These challenges are detailed in the following sections.

### 1.1 Chip-Level Resource and Data Management Challenges

A large percentage of real-world applications can be classified as streaming applications, where the applications are centered around the notion of *streams* of data. Streaming applications are becoming increasingly important and widespread. Due to the prevalence of streaming applications, there are extensive studies on system modeling and design techniques. Actor-based streaming modeling is developed to capture the intrinsic features of these applications, such as synchronous data flow models [LM87a]. Each actor in such a modeling refers to the computation that is to be performed on the incoming streams of data. Recent studies also provide language support for streaming applications, such as StreamIt [TKA02], Brook [BFH04] and Cg [MGA03]. In this modeling an application is specified as a set of actors connected by communication channels. The parallelism of an application is implicitly specified within the graph model, and can be derived from the data dependencies between the actors, *i.e.*, actors that do not have data dependencies among them can work in parallel. Throughput is an important criterion for evaluating performance of streaming applications. We can implement efficient FIFO-based dedicated and low-cost communication channels on FPGAs to support pipelining and thus improve the system throughput. In addition, we can also design customized computation datapaths for the actors.

How to best utilize the parallelism and regularity of streaming application at design time has recently been a hot research topic. The first common approach to increase the system performance is replicating the actors to exploit the data parallelism. A stateless actor, whose output is fully determined by its input, offers opportunities for data parallelism — replicas of a stateless actor can be executed in parallel. This strategy has been well studied on the multi-core platforms [GTA06, GTK02, KM08, HCK09, LDW06, UGT09, ZBS13]. The general idea is to first perform actor fission and fusion and then allocate the replicas to different processor cores. In the context of FPGA, replication optimization is more complex, because actors have different resource utilizations in terms of look-up tables (LUT) and registers, and they have to share the available on-chip resource. In [HWB09], a heuristic method is proposed which performs maximal replication of all the stateless actors and then iteratively fuses the actors that do not affect the throughput. In general, the replication technique is an easy way to increase throughput. However by simply replicating the actors, not only are the critical computation datapaths replicated, all the non-critical datapaths and control paths are also replicated, which does not necessarily contribute to improving the system performance. To better utilize the FPGA on-chip resources, one should explore different customized actor implementations with the same functionality, rather than rely on the replication technique only. This is a typical module selection problem, as discussed below.

The second approach to increase the system performance focuses on module selection [ID91, ADC95, ILP98, SWN07, CCX05]. Given different implementations of each actor, one selects the proper implementations to integrate into the system and schedule the actors to meet the system requirement. A more recent work [JHI10] explores different configurations of application specific instruction set processors (ASIPs) under throughput and latency constraints and proposes an ILP-based solution. However, most of the studies mainly focus on module selection while the design space of module replication, which is essentially useful in the case of FPGAs, is not explored.

On the other hand, communication between computation actors is also important for streaming applications in terms of system performance and resource utilization. FIFO is the common communication mechanism used to enable pipelining between actors. FIFO size is one of the key design parameters that needs to be optimized in the system synthesis. It affects the on-chip block RAM (BRAM) utilizations. More importantly, it affects the concurrency of the actor scheduling and thus has a direct impact on system performance. The buffer optimization problem is known to be NP-complete [BML12]. [SGB06] formulates the buffer size constraints directly on the SDF graph. The buffer size requirement on communication channels is imposed on the SDF graph by adding additional backward channels. The number of initial tokens corresponds to the FIFO size. Thus the original application model that does not the consider the FIFO size is transformed into a new model which contains the scheduling constraints imposed by the given FIFO size.

Several approaches have been proposed to optimize the buffer utilization under certain design metrics [GGD02, NG93]. Integer linear programming is used to obtain the minimal buffer size for synchronous data flow(SDF) [GGD02] and homogeneous synchronous data flow (HSDF) [NG93] respectively. But these methods are limited to the maximal throughput scheduling which is not efficient in exploring the different performance and area trade-off options. Some researchers [GBS05,LGX09] use a model checking technique to efficiently explore the state-space of the SDF graph. But the complexity of these methods is relatively high, especially for the graphs with large amount of state transitions. In addition, they minimize buffer size just for a deadlock-free scheduling without considering actual performance. [SGB06] proposed an efficient way to explore the Pareto-curve of the buffer size and throughput by pruning the design space without losing the Pareto points, where throughput is calculated by an eager simulation of the periodic execution, and buffer size distribution is incrementally explored according to the storage dependencies. A recent work [CZ12] modeled the buffer size directly in the analytic model and proposed an efficient heuristic based on it. But it works only on acyclic SDFs and does not prove optimal or near-optimal in large graphs. In all of this set of work, actor optimizations like module selection and replication are assumed to be a separate preprocessing or postprocessing stage. This may lose the optimality in finding the scheduling for both actor and buffer optimization.

Other related work includes [KDV97] where a simulator is adopted to evaluate different dataflow architectures for streaming applications. Our problem is a subset of their's since in our architecture we only consider FIFO interfaces. With our simplified architecture, we are able to quickly decide the selected modules without resorting to a simulator. Outside of streaming context, a computation and communication co-optimization framework is studied in [LCM09]. It combines data-reuse optimization using a scratchpad and loop-level parallelism optimization into a singe framework and formulate it into an integer geometric programming problem. This is a module-level optimization and does not apply to our problem directly.

Learning from the existing work, we observe that system design for streaming applications is still facing two major challenges: (1) System design results are determined by a complicated combination of different design aspects (module selection, module replication, buffer size optimization, scheduling and allocation), but current automation frameworks always take single or limited aspects into considerations. (2) Considering all these comprehensive design objectives and constraints makes the existing algorithms either non-scalable for large and complex designs, or difficult to achieve comparable quality of results with the optimal solutions.

We will investigate this problem in Chapter 3.

### 1.2 Node-Level Resource Management Challenges

Accelerators such as FPGAs and GPUs often serve as slave processors on a host CPU node. Typical CPU-acceleration integration methods include a PCIe-based approach and a QPI-based approach. To make use of these slave processors, current solutions require an explicit user program that handles data communication between the host and accelerators, and monitors computation tasks that are offloaded to the accelerators through APIs that are either driver-level APIs or higher-level APIs, such as OpenCL. This is also true in the virtualized environment (such as the virtual machine (VM) or the container environment); the operating system or the hypervisor relies on the user to decide which tasks should be offloaded to the accelerator.

Therefore, it is important to manage both computation resources at runtime to get the best possible performance. When computation tasks are offloaded to the accelerators, the CPU should not be idled, waiting for other tasks to finish. Other computation tasks should be executed on the CPU at the same time in the ideal case. A straightforward integration of CPU and accelerators that simply offloads tasks to accelerators and leaves the CPU idle may achieve only marginal performance gains, despite the high speedup achieved from the accelerator.

### **1.3** Cluster-Level Resource and Data Management Challenges

At the cluster-level, the current trend in equipping accelerators such as GPUs and FPGAs in commodity data centers also requires new resource and data management strategies.

Accelerators usually only accelerate part of the application's execution, and nonaccelerable tasks have to be converted back to the host. Thus, unlike other cluster resources, accelerators are usually underutilized from a tenant's perspective; accelerators should no longer be bundled to a single tenant at a time. Other unique properties of accelerators include: (1) Accelerators are often treated as I/O devices. (2) CPUs can be treated as a backup resource for accelerators; if accelerators are not available, tasks can be converted back to the host CPU and can take advantage of CPU computation power. (3) Accelerators have predictable performance since they are clean slaves that do not run OS; this feature enables more sophisticated accelerator management based on runtime accelerator status. However, most current cluster resource management—such as YARN [VMD13], Mesos [HKZ11] and Omega [SKA13]—are accelerator-oblivious. They only consider allocating CPU and memory resources. We believe that accelerators should be the first-class citizen in the resource pool, and this requires dedicated management techniques.

Traditional cluster resource management support for CPU and memory-sharing mainly relies on operating system (OS) features. CPU core-sharing is realized by launching multiple computation processes on a core, and it relies on the context switch by OS. Similarly, memory-sharing among multiple processes is managed by OS—when the used memory exceeds the total available memory on the core, memory is swapped out to disks. As current OS does not manage accelerators directly, it is hard to apply these resource management techniques to accelerators.

Concurrently, accelerator-rich architectures offer new opportunities in cluster data management. Data shuffling, which moves the data across all the machines, is the heart of almost all the cluster-scale data processing frameworks, including MapReduce and Spark. "Sorting," which is the major computation-intensive kernel during data shuffling, ought to achieve improved performance and energy-efficiency when being offloaded to accelerators. How to seamlessly incorporate accelerators in the data shuffling stage is yet an open question.

### **1.4** Dissertation Statement

This dissertation examines and addresses several resource and data management challenges in accelerator-rich architectures.

• At chip-level, we explore the design space of mapping streaming applications onto accelerators. Specifically, we consider FPGAs as the targeted accelerators. A computation and communication co-optimization algorithm is proposed to minimize the

occupied resources while meeting system performance requirements.

- At node-level, we study the runtime to orchestrate task execution on CPU and task execution on accelerators. A dataflow execution model and its corresponding runtime thread allocation policy are proposed.

- At cluster-level, we develop a cluster accelerator manager which is deployed on top of a commodity cluster resource manager. The proposed on-line accelerator allocation allows fine-grained time-sharing of accelerators between multiple tenants and improves cluster throughput.

- Finally, we present our analysis on accelerating data shuffling on accelerator-rich clusters. We demonstrate that although data shuffling is computation-intensive, integrating accelerators into the system does not provide performance gain due to data serialization and deserialization overhead.

### 1.5 Organization

This dissertation will examine the above-mentioned challenges. The remainder of the dissertation is organized as follows. Chapter 3 presents resource and data management on accelerator-rich systems-on-chips. Chapter 4 presents resource management on accelerator-rich nodes. Chapter 5 presents our resource management in accelerator-rich clusters. Chapter 6 presents our analysis on accelerating data shuffling on accelerator-rich clusters. We conclude and discusses future research opportunities in Chapter 7.

### CHAPTER 2

### Background

This chapter presents the background for several key topics, including chip-level programming model, cluster-level programming model, node-level execution model, nodelevel CPU and GPU orchestration, cluster-level resource manager and cluster-level data shuffling.

### 2.1 Chip-Level Programming Model

In this section we present synchronous data flow graphs and homogeneous synchronous data flow graphs which are commonly used to model streaming applications, and we define system throughput from the graphs.

#### 2.1.1 Synchronous Data Flow Graph

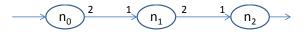

Synchronous data flow graphs (SDFGs) [LM87a] have been traditionally used to model streaming applications. In an SDFG G(V, E), each node  $v \in V$  (also called an actor) represents a computation kernel. Each edge  $u \to v$  represents a data communication channel from node u to v. The amount of data tokens consumed and produced by a computation kernel is determined at design time, and is usually referred to as the producer rate and the consumer rate. For example, in Fig. 2.1, the producer rate and consumer rate for actor  $n_1$  is 2 and 1 respectively. When an actor starts its firing/execution, it removes the number of tokens that equals the consumer rate from its input channels. At

Figure 2.1: An example of SDFGs. Producer/consumer rates are labeled at the beginning/end of the edges.

the end of a firing/execution, the actor produces the number of tokens that equals the producer rate to its output channels. We model the data consumption and production process as an atomic process where the number of tokens on a channel will only be changed at the beginning or at the end of an actor firing. Such a fixed producer rate and consumer rate make it easier to analyze and predict the timing behavior of complex streaming applications, and this is the main reason that SDFGs are used.

The execution of an SDFG is defined in terms of actor firings:

**Definition 1** A periodic execution schedule or iteration of an SDFG is a set of actor firings such that after all these firings, the SDFG returns to the same state, i.e., the number of tokens on each channel remains the same before or after an iteration.

The number of actor firings in one periodic execution schedule is called the repetition factor vector q [LM87b]. In Fig. 2.1, actors  $n_1$ ,  $n_2$  and  $n_3$  fire 1, 2 and 4 times respectively to maintain a data balance between producer and consumer actors. Therefore, the corresponding repetition factor vector q is [1;2;4]. Note that it is possible that the execution of SDFGs results in deadlock or an infinite number of accumulated tokens on the channels. In this case, there does not exist a periodic execution schedule. More detailed analysis on whether there exists a periodic execution schedule given an SDF can be found in [LM87a]. Such a system is called an inconsistent system, and it is beyond the scope of this work.

The *periodic execution schedule* is very important in analyzing system throughput for streaming applications. Streaming applications usually perform computation on a very long data sequence (which is typically assumed to be infinite). It is costly to adopt an irregular scheduling for each of the repeated actor firings. Since SDFG has a periodic behavior in actor firings, it's reasonable to have a periodic scheduling.

Note that in the context of SDF, communication channels are often referred to as buffers. In the context of FPGA implementations, communication channels are often referred to as FIFOs. In this chapter we do not distinguish between these two.

#### 2.1.2 Homogeneous Synchronous Data Flow Graph

An SDFG can be transformed into an equivalent single-rate data flow graph, which is called a homogeneous synchronous data flow graph (HSDFG) [LM87a]. In HSDFG, all

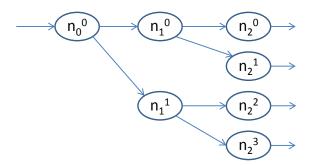

Figure 2.2: The HSDFG converted from SDFG in Fig. 2.1.

the actor firings in one iteration are explicitly enumerated. Fig. 2.2 shows the HSDFG converted from the SDFG in Fig. 2.1. There are two firings of actor  $n_1$   $(n_1^0 \text{ and } n_1^1)$  and four firings of actor  $n_2$   $(n_2^i, 0 \le i < 4)$ . Edges in HSDFG represent data dependency between producers and consumers. For example,  $n_1^0$  and  $n_1^1$  can start to work only after  $n_0^0$  finishes and produces one data to each of them, so there are data dependency edges between them.

We find it easier to start from the HSDFG (instead of the SDFG) when modeling scheduling constraints since all the actor firings have been enumerated in the graph. Thus, given an application that is modeled in an SDFG, we will first transform it into an HSDFG by using the conversion algorithm in [SB00].

### 2.1.3 Throughput Definition

In this work throughput is viewed as a constraint for streaming applications. Denote  $n_i^j$  as the *j*th firing of actor  $n_i$  in the first iteration. We associate each actor firing  $n_i^j$  in the scheduling graph with a start firing time  $t_i^j$ , which denotes when the firing can start. We also refer to  $t_i^j$  as scheduling variables.

Throughput is defined as how often the actor firing  $n_i^j$  can start a firing again. Particularly in the scheduling graph, throughput is defined as follows:

$$Throughput = \frac{1}{t_i^{\prime j} - t_i^j},\tag{2.1}$$

where  $t'_i^j$  denotes the start firing time of the *j*th firing of actor  $t_i$  in the following iteration.

Figure 2.3: Module implementation with and without pipelining. This figure is adopted from [viv].

# 2.2 Chip-Level Design Space Exploration with High Level Synthesis

### 2.2.1 Design Space Exploration

The modules in the streaming application typically work on a very large sequence of data. Therefore it is nature to adopt the module replication strategy, where multiple modules of the same functionality work on multiple data in parallel. System designers need to decide the number of replicas of each module.

Besides, system designers may also need to consider the best module implementation. In general, module replication is not an area-efficient design technique for increasing throughput because control logics, which do not directly contribute to throughput, are also duplicated. Moreover, some computing logics might be wasteful after replication. For example, consider a module that contains two add and one multiply operation, while the slowest implementation would use one adder and one multiplier to do the computation. When we duplicate such an implementation, two adders and two multipliers are generated, and one multiplier is wasted.

When mapping a module in streaming programs onto FPGAs, by setting different design goals and deploying different optimization configurations we can generate "func-

Figure 2.4: Tradeoff between performance and area of one module in benchmark "filterbank."

tionally equivalent" implementations that differ in area and performance. Therefore, we could generate a library of implementations for each module so that design space is enlarged. For example, *initiation interval* (II) is a well-known parameter that trades off between area and throughput. In streaming applications, the initiation interval specifies the number of cycles between the consecutive firing of a module and indicates to what extent the module is pipelined. A pipelined module offers high throughput, but usually at a large area cost because resource sharing opportunities are reduced. Figure 2.3 shows an example of module implementations with and without pipelining.

Figure 2.4 plots the initiation interval and area cost of our FPGA-based implementations for one module in the StreamIt benchmark "filterbank" [Str]. The initiation interval of these design points are 1, 2, 4, 8, 16 and 254, respectively. We can see from the figure that decreasing the initiation interval results in more DSP logics and slices. To achieve a throughput of one firing per cycle, we could either replicate the slowest implementation (with II = 254) into 254 copies, or use the implementation with II = 1 directly. Obviously the latter option is more area efficient.

It's worthwhile to mention that pipelining does not guarantee that the throughput target can be satisfied, and replication is still needed in cases where a fully pipelined design cannot satisfy the high throughput target. There are also situations when hardware designers choose to use the predefined IP cores to avoid high development cost, and they do not have many choices for different implementations.

#### 2.2.2 High Level Synthesis

Thanks to recent advantages in high-level synthesis (HLS) tools [ZFJ08, CLN11], we are able to design FPGAs using a C/C++ based programming flow. HLS allows user to specify the module optimizations. For example, to enable loop pipelining (Figure 2.3), user only need to insert "pragma HLS pipeline" into the code. HLS greatly reduces programming efforts, allowing us to quickly design and evaluate the performance and area consumption of different modules.

### 2.3 Node-Level CPU-Accelerator Orchestration

Now we present background for node-level CPU execution model and related works on CPU-GPU execution model. Commonly used execution models to exploit data-level parallelism and task-level pipeline parallelism are data-parallel execution model and streaming execution models. In data-parallel execution model, multiple threads are launched in parallel to process the same task but with different data. While in streaming execution model, multiple threads may be launched to process different computation tasks.

### 2.3.1 Dataflow/Streaming Execution Model

Relevant work includes compilation of new streaming languages such as StreamIt [TKA02] and Brook to multicore architectures [KM08, HCK09, GTA06]. However, these studies do not consider the scenario of offloading computation to accelerators where CPUs may become idle, waiting for the accelerator to finish. Our runtime can make good use of these idled CPU cycles by launching other tasks onto the CPU cores.

### 2.3.2 CPU and GPU Coordination

Prior works studied the CPU-GPU collaboration for data parallel kernels [KDT12,KKL11, LSP13, LHK09]. These studies present frameworks that can partition the workloads/threads across multiple devices such as CPUs and GPUs. StarPU [KDT12] presents new APIs to offload kernel computations to OpenCL-based GPUs. The work in [KKL11] presents an OpenCL framework/runtime that works on multiple GPUs using a single compute device image. The work in [LSP13] deals with a single kernel multiple devices system. Scheduling optimizations based on prior profiling information or prediction models are studied as well in [LSP13,LHK09]. However, these studies only explore data-level parallelism and do not consider pipeline parallelism between different tasks.

In this thesis, we will investigate the execution models that consider both datalevel parallelism and task-level pipeline parallelism on the heterogeneous CPU-accelerator node.

# 2.4 Cluster-Level Programming Model and Resource Management

Further expanding the scope of accelerator-rich architectures, we look into resource and data management at cluster-level accelerator-rich architectures. In this section we will review the conventional cluster-level application programming model and discuss how to management cluster resources for cluster tenants.

#### 2.4.1 Cluster-Level Programming Model

MapReduce, originally proposed from Google [DG08], is a programming model and an associated implementation for processing and generating datasets. It inspires much of the initial big data analytics work and serves as a template for open source systems like Apache Hadoop.

In the MapReduce programming model, users specify the computation in terms of a *map* and a *reduce* function. In the map function, each input record is processed to generate a key-value pair. In the reduce function, values associated with the same key are grouped together, and an operation is applied to them to obtain the final results.

map:  $(k1, v1) \rightarrow list(k2, v2)$ reduce:  $(k2, list(v2)) \rightarrow list(v2)$

Figure 2.5: Example YARN architecture showing a client submitting jobs to the global resource manager.

### 2.4.2 Cluster-Level Resource Management

YARN (Yet Another Resource Negotiator) is a widely used cluster resource management layer in the Hadoop system that allocates resources, such as CPU and memory, to multiple big data applications (or jobs). Figure 2.5 shows a high-level view of the YARN architecture. A typical YARN setup would include a single resource manager (RM) and several node manager (NM) installations. Each NM typically manages the resources of a single machine, and periodically reports to the RM, which collects all NM reports and formulates a global view of the cluster resources. The periodic NM reports also provide a basis for monitoring the overall cluster health at the RM, which notifies relevant applications when failures occur.

A YARN job is represented by an application master (AM), which is responsible for orchestrating the job's work on allocated *containers*, i.e., a slice of machine resources (some amount of CPU, RAM, disk, etc.). A client submits an AM package—that includes a shell command and any files (i.e., binary executable configurations) needed to execute the command—to the RM, which then selects a single NM to host the AM. The chosen NM creates a shell environment that includes the file resources, and then executes the given shell command. The NM monitors the containers for resource usage and exit status, which the NM includes in its periodic reports to the RM. At runtime, the AM uses an RPC interface to request containers from the RM, and to ask the NMs that host its containers to launch a desired program. Returning to Figure 2.5, we see the AM instance running with allocated containers executing a job-specific task.

To manage heterogeneous computing resources in the datacenter and provide placement control, YARN recently introduced a mechanism called *label-based scheduling* [yar]. Administrators can specify labels for each server node and expose the label information to applications. The YARN resource manager then schedules the resource to an application only if the node label matches with the application-specified label. Examples of node labels can be an FPGA or GPU, which indicate that the nodes are equipped with a special hardware platform.

Different from the centralized resource scheduling frameworks (*e.g.*, YARN), Mesos [HKZ11], which originated at Berkeley, is a two-level resource scheduling framework. Its centralized resource manager makes resource offers to its underlying applications, offering one piece of resource to one application at a time. Applications make the decision as whether to accept the resource offer or not. Since Mesos distributes the resource offers without knowing the resource needs of the applications, applications achieve data locality of the resource by rejecting the offers without data locality.

In both YARN and Mesos, applications only see the resources that have been allocated or offered. Omega [SKA13] adopts a completely different strategy by introducing a new share-state resource allocation mechanism and allowing each application to access a view of the overall cluster resource. A lock-free concurrency control is subsequently implemented in their resource manager.

Although structurally different, these cluster resource managers share many common design principles:

- Data Locality. Moving computation is cheaper than moving data. This is particularly true when the data size is large. Resource managers should respect applications' data locality and allocate resources close to where the data is located.

- Multi-Tenancy and High Utilization. The traditional approach which allocates a physical node to only one tenant at a time results in low cluster utilization. Resource managers should support fine-grained resource sharing among multiple tenants.

Figure 2.6: Data Sorting and Shuffling in MapReduce. This figure is adopted from [Whi12].

• Scalability. Resource allocation should be fast and scalable to increasing cluster sizes. For example, current capacity scheduler in YARN can fill up a decent- sized cluster in less than 100ms. That being said, resource managers should avoid high-complexity resource scheduling algorithms.

# 2.5 Cluster-Level Data Sort and Shuffle

Data sorting and shuffling is, in many ways, the heart of large-scale distributed computing frameworks, such as MapReduce/Hadoop and Spark. For simplicity, here we use shuffle to refer to this data sorting and data shuffling stage. In MapReduce, shuffle performs the data sorting and data transmission from the mappers to the reducers, guaranteeing that the input to every reducer is sorted by key. It is an area of the codebase where refinement and improvements are continually being made, and is where the "magic" happens [Whi12]. Spark, whose operators are a strict superset of MapReduce, also supports sorting-based data shuffle between consecutive computation stages. In fact, at an earlier stage of Spark development, it adopts a hashing-based shuffle which turns out to be one of the limiting factors of scaling out Spark. Sorting-based shuffle is thus then introduced to Spark. Overall, the data shuffle is an expensive but indispensable operation of many distributed computing frameworks.

Figure. 2.6 provides an illustration of the shuffle stage in MapReduce. At the mapper side, an in-memory buffer collects the output from each map task. When the buffer is almost full (80% by default), a new thread starts to sort the data (using quicksort by

default) and spills the content to the disk. When map tasks finish, a thread performs a merge-sort to merge multiple sorted data on the disk to a single sorted sequence of data. The reducers fetch the data from the mappers and perform a final round of data merging that merges data from the mappers on different nodes. Multiple rounds of merge-sort are performed if the number of mappers is large.

# CHAPTER 3

# **Chip-Level Resource and Data Management**

# 3.1 Introduction

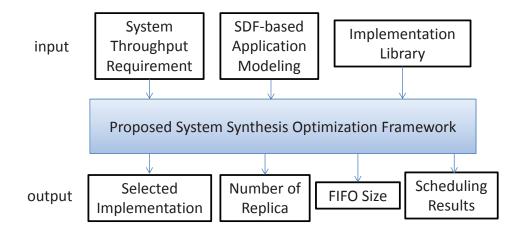

In this chapter we propose a novel system synthesis approach to tackling the resource and data management issues. We formulate the module selection, module replication, buffer size optimization and scheduling simultaneously into one single optimization framework, considering the trade-offs among system throughput, logic and on-chip memory utilization. The proposed framework is shown in Fig. 3.1. It takes the system throughput requirement, application model, and an implementation library as inputs and outputs the module selection/replication results, FIFO size and a feasible schedule. Within the framework, an efficient solving algorithm is presented which achieves both high-quality design (*i.e.* low logic/BRAM costs within the throughput constraints) and scalability.

The remainder of this chapter is organized as follows. Section 3.2 gives a motivation example which shows the benefit of combining computation and communication optimizations in system synthesis. Section 3.3 provides a detailed analytic formulation of the scheduling constraints and objectives for module selection, module replication and

Figure 3.1: The proposed system synthesis framework.

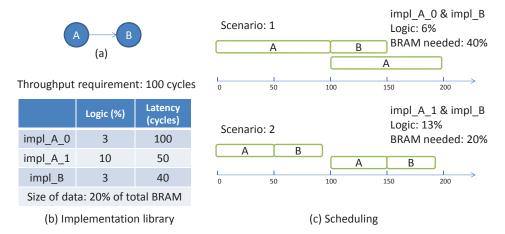

Figure 3.2: A motivating example. In scenario 1, buffer size is not considered during module selection. The implementation with minimum logic is selected. In scenario 2, buffer size is considered together with module selection. In both cases, these are feasible schedules that can meet the system throughput requirement. However in scenario 2 with the consideration of buffer size, the selected implementation can reduces BRAM use by 20%.

buffer size optimizations. Section 3.4 proposes an efficient iterative algorithm to find the solution to the combined optimization problem. Experimental results are shown in Section 3.5, where both design quality and run-time complexity are measured with streaming benchmarks.

# **3.2** A Motivation Example

Fig. 3.2 gives a motivational example. We show a very simple case in streaming applications in Fig. 3.2(a), where A is the producer actor and B is the consumer actor. A and B are executed repeatedly.

The implementation options are listed in Fig. 3.2(b). Actor A has two implementations, impl\_A\_0 and impl\_A\_1, which show the trade-offs between the logic cost and execution latency. Actor B has only one fixed implementation. Each of actor A's executions produce a fixed size of data to the communication channel. We assume the size is 20% of the FPGA on-chip memory. Each of actor B's executions consume the same amount of data from the communication channel. The system throughput target is set to one execution of A and B in every 100 cycles. In Fig. 3.2(c) scenario 1, we decouple the computation and communication optimizations by first considering module selection without considering buffer size. The solution with minimal logic utilization is considered to be the optimal one. Then the scheduling that has the minimum buffer size requirement is calculated afterwards. Therefore, in the optimal solution, impl\_A\_0 and impl\_B are selected. Then in this case, we need to double the data buffer size which takes 40% BRAM resource, since a second execution of A has to be overlapped with the first execution of B in order to meet the throughput constraint. And the second execution of A has already started before the first execution of B finishes. In Fig. 3.2(c) scenario 2, we consider buffer size optimization together with module selection. In this case, a slightly large implementation of A is selected which can significantly improve the performance of actor A (at the cost of 7% logic increase compared to scenario 1). Then we do not have to execute A and B in parallel. When the second execution of A starts, the first execution of B has finished and the communication channel is empty. Thus, the needed buffer size is only 20% of total BRAM.

From the example we see that we cannot take computation optimizations (module selction/replication) and communication (buffer size) optimizations as two separate steps. Thus, in this work we propose to combine computation and communication optimizations together during system synthesis.

# 3.3 System Mapping

With the modeling of application behavior in the HSDF graph, our system mapping problem can be defined as the following:

Given application modeling in an HSDF graph consisting of actor firings  $n_i^j$  as nodes and data dependencies between actor firings as edges, the target throughput requirement  $Thr_{tar}$ , and implementation options  $P_n^s$  for each actor with the logic cost  $A(P_n^s)$ , execution latency  $et(P_n^s)$ , and pipeline initial interval  $\delta(P_n^s)$ , we find the optimized module selection results  $P_n^{sel}$  and replication factors  $rep_n$  for each actor, the total FIFO size, and the periodic scheduling  $t_i^j$  for each actor firing. The BRAM and logic utilization on FPGA is minimized under the given system throughput constraint.

A list of the denotations used in the following sections of the chapter can be found in

| parameters      | meaning                                             |

|-----------------|-----------------------------------------------------|

| $n_i^j$         | $j$ th firing of actor $n_i$                        |

| $n'^j_i$        | $j$ th firing of actor $n_i$ in 2nd iteration       |

| $Lib_n$         | implementation library for actor $n$                |

| $P_n^s$         | implementation in library $Lib_n$                   |

| $A(P_n^s)$      | area cost of $P_n^s$                                |

| $et(P_n^s)$     | execution time of $P_n^s$                           |

| $\delta(P_n^s)$ | initiation interval of $P_n^s$                      |

| $Thr_{tar}$     | throughput target                                   |

| variables       |                                                     |

| (unknown)       | meaning                                             |

| $t_i^j$         | start firing time of $n_i^j$ , scheduling variables |

| $t'^j_i$        | start firing time of $n_i^j$ in 2nd iteration,      |

|                 | scheduling variables                                |

| $b_n^s$         | if implementation $P_n^s$ is selected               |

| $rep_n$         | number of replicas for each module                  |

Table 3.1: Denotation of variables.

Table. 3.1.

In this section we discuss the problem of mapping HSDFGs onto FPGAs. First, we generate an FPGA implementation library for each actor which realizes the functionality of streaming application kernels. Second, given the selected modules, we formulate all the scheduling constraints and delineate them as new edges on the HSDFG. We refer to the HSDFG with scheduling constraints as the scheduling graph. Last, we formally state the whole system synthesis framework, which contains module selection/replication, buffer size optimization and scheduling. An ILP formulation is presented throughout this section to capture the optimal solution. We present a scalable and efficient near-optimal algorithm in Sec. 3.4.

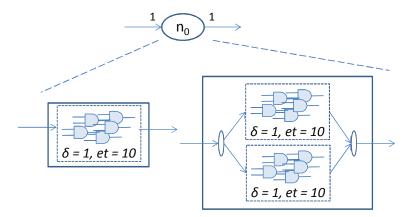

Figure 3.3: An example of module replication. Module throughput can be further improved by duplicating the modules and adding the corresponding split and join logic.

#### 3.3.1 Implementation Library Constraints

In realizing streaming applications onto FPGAs, by setting different optimization configurations we can generate a set of "functionally equivalent" implementations that differ in area and performance. Usually a significant area saving can be achieved by using slower implementations. In terms of performance, hardware implementations can differ in initiation interval ( $\delta$ ) and latency (*et*). Initiation interval specifies to what extent the hardware module can be pipelined. Latency specifies execution time of the hardware module. It is the time interval between the time point when an actor starts firing and the time point when the actor finishes its firing and produces data tokens to its output channels.

In streaming applications, initiation interval means the number of cycles that the two consecutive firings, which are mapped to the same module, need to be separated by. An initiation interval  $\delta = 1$  indicates a fully pipelined module with a new firing initiated every clock cycle. Hardware modules with a smaller  $\delta$ , and thus with a higher throughput, are usually achieved at a larger area cost because a smaller  $\delta$  reduces many resource-sharing opportunities. For the same reason, hardware modules with a smaller *et* require more logic for parallel computing since the logic can not be shared if they are used in parallel.

Module replication techniques can further improve the module throughput even when  $\delta$  has decreased to 1. Fig. 3.3 shows an example of module replication. The actor consumes one data token and produces one data token on each firing. Assume we already have a module that achieves  $\delta = 1$  and et = 10 and we replicate it into two copies. Then

from a system point of view, such an implementation consumes and produces two data tokens on each firing in every clock cycle. Note that additional split and join logic is needed here to distribute the data to different modules in a round-robin fashion.

Several commercial C-to-FPGA high-level synthesis tools now provide the ability to synthesize hardware modules with a specified pipeline level and parallelism level. For example, the initiation interval and loop unrolling factor can both be specified for a loop. FPGA synthesis tools can also provide an estimation of area usage, initiation interval and latency of the current synthesized hardware modules. Thus, given a C program for streaming applications, we can quickly generate different hardware implementations by altering the design configurations, and build up a library of implementations. In addition, to save development cost, we can also adopt IPs (*e.g.* FFT) cores provided by FPGA vendors into our implementation library. In this work, granularity of a module is defined by users — it can be a few instructions for the smallest module or multiple loops for a large module.