# **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

### **Title**

Graphene for Future ESD Protection Circuits and Ultrasound Transducer Applications

### **Permalink**

https://escholarship.org/uc/item/5610m61c

### **Author**

Chen, Qi

## **Publication Date**

2017

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

Graphene for Future ESD Protection Circuits and Ultrasound Transducer Applications

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Qi Chen

December 2017

Dissertation Committee:

Dr. Albert Wang, Chairperson

Dr. Ming Liu

Dr. Sheldon Tan

| The Dis | ssertation of Qi Chen is approved: |                       |

|---------|------------------------------------|-----------------------|

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    | Committee Chairperson |

University of California, Riverside

### Acknowledgements

I would like to express my gratitude to my research advisor, Dr. Albert Wang, wholeheartedly, for his academic mentorship and constant supports during my Ph.D. studies. His visions in electrical engineering and research advices have guided me throughout my Ph.D. research activities. It's been a great pleasure and fortune for me to have him as my advisor.

I would like to thank the Department of Electrical and Computer Engineering at University of California, Riverside, especially the members of my dissertation committee, Dr. Ming Liu and Dr. Sheldon Tan, for their supports on my dissertation research. I would thank all my laboratory mates with whom I have conducted researches together, Fei Lu, Rui Ma, Chenkun Wang, Feilong Zhang and Cheng Li. I would also like to thank my research collaborators at University of California, Los Angeles, Dr. Wei Zhang, Jimmy Ng and Prof. Ya-Hong Xie, for the joint efforts. During our collaboration, I have learned valuable lessons from their experiences in the graphene material synthesis and device fabrication. I want to acknowledge the National Science Foundation for its support for my PhD research. I would like to express my deepest gratitude to my family. Thanks for their generous and endless love to me. They are always with me when I went through tough situations and provided encouragement and supports to me.

My research outcomes were published in IEEE Transactions of Electron Devices (TED), IEEE Electron Device Letters (EDL), Micro & Nano Letters, and several technical conferences including IEEE International Reliability Physics Symposium (IRPS) and IEEE International Conference on Nano/Micro Engineered and Molecular Systems (NEMS).

To my family for all the supports.

#### ABSTRACT OF THE DISSERTATION

Graphene for Future ESD Protection Circuits and Ultrasound Transducer Applications

by

### Qi Chen

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, December 2017 Dr. Albert Wang, Chairperson

Electrostatic discharge (ESD) can easily damage integrated circuits (IC) and electronics systems [1-6]. It is hence imperative to investigate the ESD fundamentals and develop robust ESD protection solutions for semiconductors and ICs. Conventional on-chip ESD protection structures for ICs rely on in-Si PN-junction-based devices, which have many inherent disadvantages, making them unsuitable for future ICs at nano nodes.

Both novel ESD device structures and robust ESD interconnects are critical to onchip ESD protection designs. In this dissertation, I report research outcomes of transient and systematic characterization of graphene ribbon (GR) used as interconnects for on-chip ESD protection circuits for future ICs. A large set of GR wires with varying and practical dimensions were fabricated using chemical vapor deposition (CVD) method and characterized by transmission line pulsing (TLP) and very fast TLP (VFTLP) measurements. This research indicates that, with its unique properties, e.g., high thermal conductivity and high current handling capability, graphene ribbons may be used as interconnects for on-chip ESD protection circuits, replacing existing aluminum and copper metal interconnects. I also report a novel above-IC graphene-based nanoelectromechanical system (gNEMS) transient switch ESD protection mechanism and structure. TLP testing confirms the new gNEMS ESD protection concept, showing dualpolarity transient ESD switching effect with a response time down to 200ps. This novel gNEMS switch is a potential ESD protection solution to realize above-Si ESD protection designs through 3D heterogeneous integration in the back end of line (BEOL) of ICs.

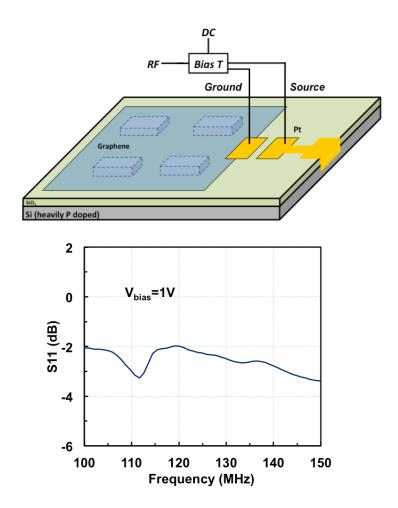

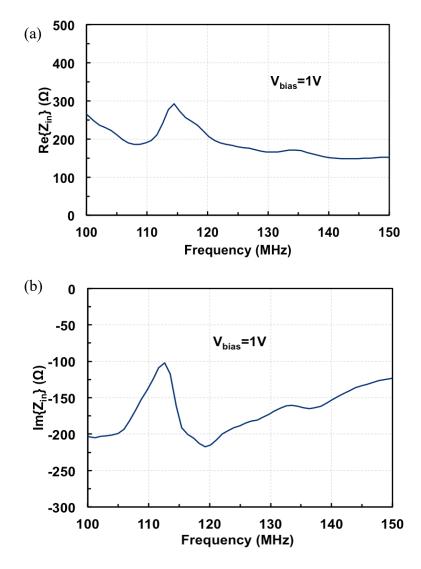

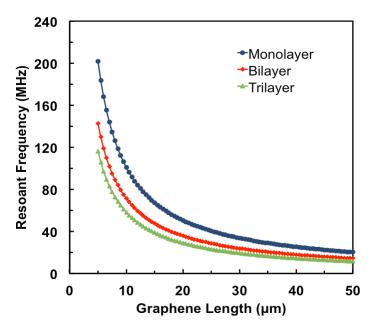

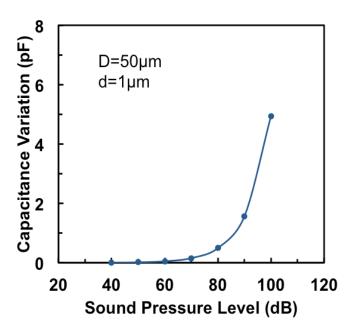

The third part of my PhD research was to explore using graphene to make novel ultrasound transducers. Ultrasound imaging utilizes ultrasonic acoustic waves to monitor organs and tissues, which has been widely used in biomedical diagnosis, such as in obstetrics and gynecology, cardiology, urology and cancer detection areas. Capacitive micro-machined ultrasound transducers (CMUT) are recently used for ultrasound imaging systems. CMUTs have advantages over piezoelectric micro-machined ultrasound transducers (PMUTs). CMUT can be fabricated by standard IC fabrication processes, making it possible to make high-performance, lost-cost and compact ultrasounic system-on-s-chip (SoC) for hand-held ultrasound imaging systems for various biological and medical applications. One key disadvantage of existing CMUT structures is the relatively low frequency, well below 100MHz as reported, hence, poor imaging resolution. I report the first concept of a graphene CMUT structure with a resonant frequency around/beyond 110MHz, making it possible to develop ultra-high resolution hand-held ultrasound imaging products for healthcare applications.

## **Contents**

| Chapter 1 Introduction to Graphene                                 | 1  |

|--------------------------------------------------------------------|----|

| 1.1 Graphene Material                                              | 1  |

| 1.2 Graphene Synthesis                                             | 3  |

| 1.3 Graphene Properties                                            | 4  |

| 1.4 Graphene Applications                                          | 6  |

| 1.5 Graphene for ESD Protection Circuits                           | 7  |

| Chapter 2 Introduction to Electrostatic Discharge (ESD) Protection | 9  |

| 2.1 ESD Protection for ICs                                         | 9  |

| 2.2 ESD Protection Designs                                         | 11 |

| 2.3 ESD Testing Models and Equipment                               | 13 |

| 2.4 Motivation for Above IC ESD Protection Structure               | 14 |

| Chapter 3 Graphene ESD Interconnects                               | 16 |

| 3.1 Motivation                                                     | 16 |

| 3.2 Graphene ESD Interconnects                                     | 18 |

| 3.2.1 Structure and Operation Mechanisms                           | 18 |

| 3.2.2 Fabrication.                                                 | 19 |

| 3.3 Characterization & Discussions                                 | 20 |

| 3.3.1 Design Splits & Testing Conditions                           | 20 |

| 3.3.2 Graphene Resistance                                          | 22 |

| 3.3.3 Transient ESD Testing                                        | 23 |

| 3.3.4 ESD Characteristics versus GR Dimensions                     | 25 |

| 3.3.5 ESD Characteristics versus Pulse Rise Time and Duration      | 32 |

| 3.3.6 ESD Characteristics versus Temperature                       | 37 |

| 3.3.7 ESD Characteristics versus Zapping Methods                   | 43 |

| 3.4 Failure Analysis                                               | 45 |

| 3.5 Conclusion                                                     | 47 |

| 3.6 Single Crystalline Graphene ESD Interconnects                  | 48 |

| Chapter 4 Graphene NEMS ESD Switch                                 | 59 |

| 4.1 Graphene NEMS ESD Switch                                       | 59 |

| 4.1.1 Concept & Structure                                          | 59 |

| 4.1.2 Properties                         | 61  |

|------------------------------------------|-----|

| 4.1.3 Fabrication                        | 63  |

| 4.2 Characterization & Discussions       | 67  |

| 4.2.1 Design Splits & Testing Conditions | 67  |

| 4.2.2 DC Testing                         | 68  |

| 4.2.3 Transient TLP Testing              | 69  |

| 4.2.4 Device Dimension Effects           | 72  |

| 4.2.5 ESD Pulse Shape Effects            | 82  |

| 4.2.6 Temperature Test                   | 88  |

| 4.2.7 Reliability Test                   | 89  |

| 4.3 Failure Analysis                     | 92  |

| 4.4 Conclusion                           | 93  |

| Chapter 5 Graphene Ultrasound Transducer | 94  |

| 5.1 Introduction and Motivation          | 94  |

| 5.1.1 Ultrasound Imaging System          | 94  |

| 5.1.2 Ultrasound Transducers             | 99  |

| 5.1.3 Motivation                         | 106 |

| 5.2 Graphene CMUT                        | 112 |

| 5.2.1 Structure & Operation Mechanism    | 114 |

| 5.2.2 Properties                         | 115 |

| 5.2.3 Fabrication                        | 117 |

| 5.3 Characterization & Discussions       | 120 |

| 5.3.1 C-V Measurement                    | 120 |

| 5.3.2 S-Parameter Measurement            | 122 |

| 5.3.3 Z-Parameter                        | 123 |

| 5.4 Modeling & Simulation                | 125 |

| 5.5 Conclusion                           | 129 |

| Chapter 6 Conclusion                     | 130 |

| Rihlingranhy                             | 132 |

# **List of Figures**

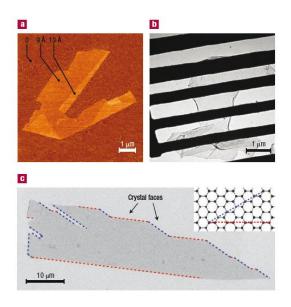

| Figure 1. 1 Graphene materials under optical microscopy [7]                                              |

|----------------------------------------------------------------------------------------------------------|

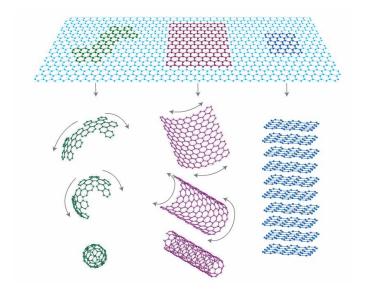

| Figure 1. 2 Graphene lattice structures. It is the building blocks for other carbon                      |

| allotropes. 2D graphene can be wrapped up into 0D fullerences, rolled into 1D nanotubes                  |

| and stacked into 3D graphite [7]                                                                         |

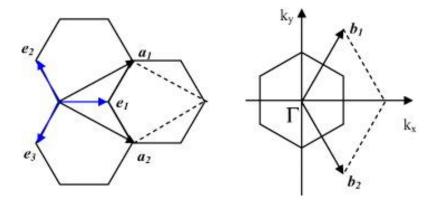

| Figure 1. 3 Graphene lattice structures and primitive vectors in real space and reciprocal               |

|                                                                                                          |

| lattice [7]                                                                                              |

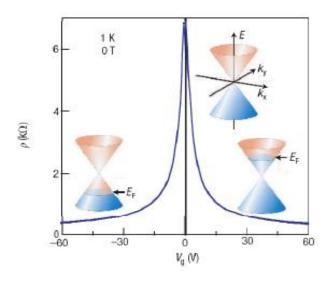

| Figure 1. 4 Ambipolar transportation in graphene [8]                                                     |

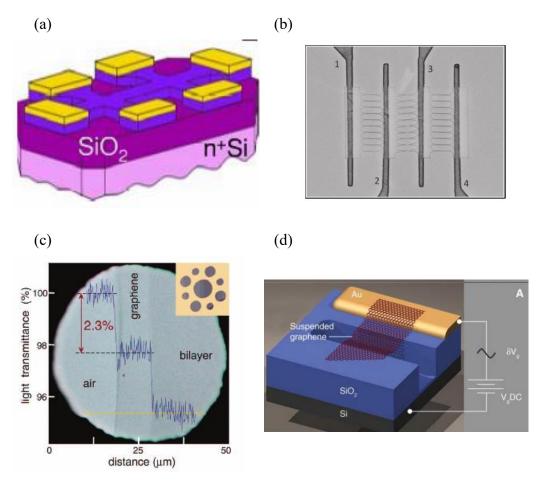

| Figure 1. 5 Graphene applications for (a) transistors [9], (b) interconnects [11], (c)                   |

| electrodes [8] and (d) resonators [41]6                                                                  |

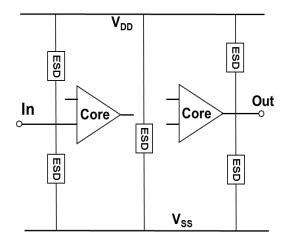

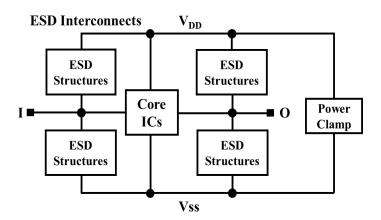

| Figure 2. 1 Complete full-chip ESD protections including ESD structures and ESD                          |

| interconnect at each pin against all possible ESD stressing modes                                        |

|                                                                                                          |

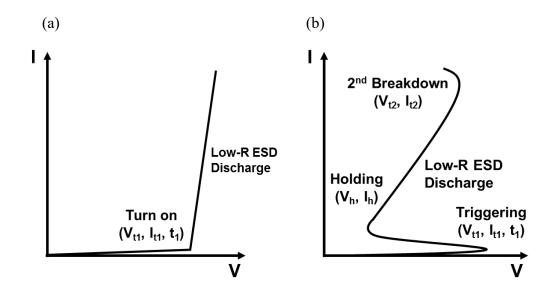

| Figure 2. 2 Typical non-snapback (a) and snapback I-V (b) characteristic for an ESD                      |

| protection structure where ESD-critical parameters are defined for triggering threshold                  |

| $(V_{t1}, I_{t1}, t_1)$ , holding point $(V_h, I_h)$ , discharging impedance (Ron) and thermal breakdown |

| $(V_{12}, I_{12})$                                                                                       |

| Figure 2. 3 TLP and VFTLP test equipment in this study                                                   |

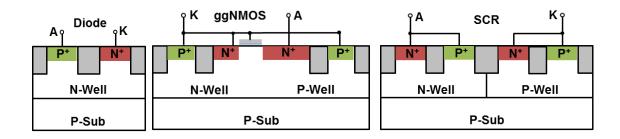

| Figure 2. 4 Typical ESD protection structures including diode, ggNMOS and SCR 15                         |

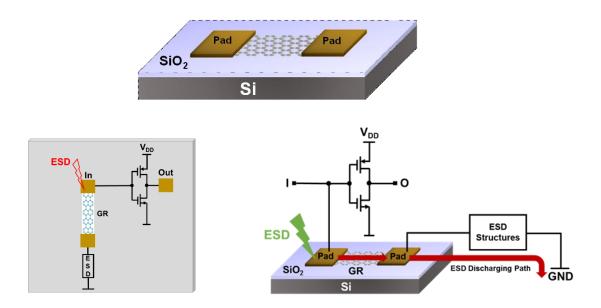

| Figure 3. 1 A conceptual on-chip ESD protection scenario using GR interconnects. GR                      |

| wires connect ESD structures with pads. During ESD events, large ESD transients will                     |

| 1 0 , 0                                                                                                  |

| discharge through GR interconnects and ESD devices. Hence, the GR interconnects must                     |

| survive the ESD surges                                                                                   |

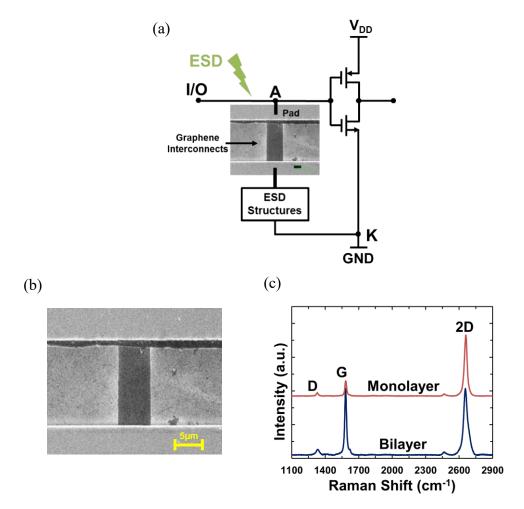

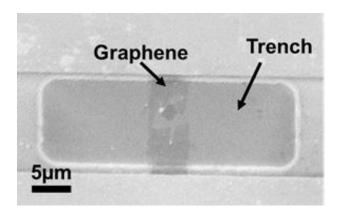

| Figure 3. 2 (a) Graphene ESD interconnects protection mechanisms. (b) SEM image of a                     |

| bilayer GR wire (vertical dark stripe) of L=12μm and W=5μm. (c) Raman spectrums for                      |

| monolayer and bilayer GR samples where G peak reveals number of graphene layers [28,                     |

| 29]                                                                                                      |

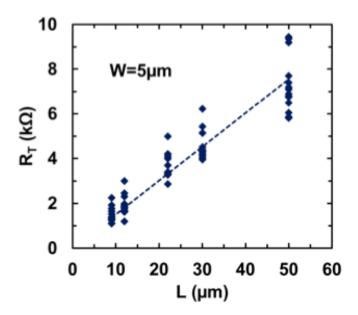

| Figure 3. 3 Statistics analysis for $R_T$ for GR wires of varying L (W=5 $\mu$ m) by measured            |

| by DC stressing results in $R_C \sim 188\Omega$ and GR sheet-R $\sim 650\Omega/\square$                  |

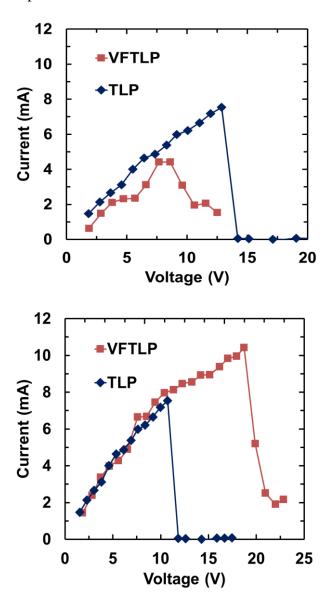

| Figure 3. 4 Two typical transient I-V characteristics by TLP and VFTLP for a bilayer GR                  |

| sample (L=12μm, W=5μm) at room temperature reveals ESD failure threshold (I <sub>C</sub> )               |

| corresponding to an abrupt current drop                                                                  |

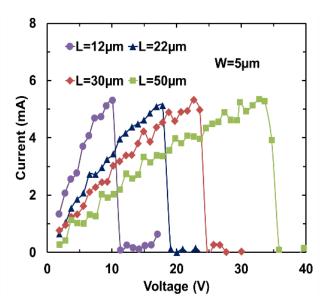

| Figure 3. 5 Transient I-V curves for GR wires with varying L (fixed W=5µm) by TLP                        |

| testing shows that $V_C$ increases substantially with L                                                  |

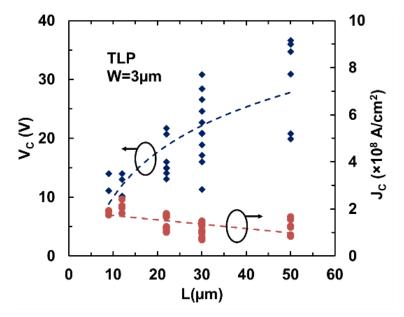

| Figure 3. 6 Statistics for TLP testing results of GR samples with varying L (fixed W=3                   |

| $\mu$ m) confirm that $V_C$ increases significantly with L. However, $J_C$ only shows little             |

| ·                                                                                                        |

| $\mathcal{E}$                                                                                            |

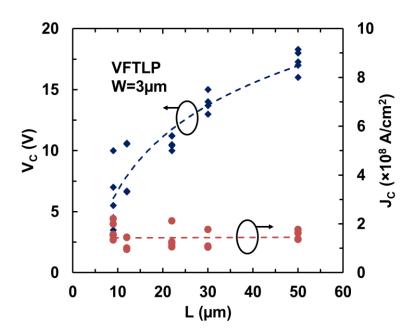

| Figure 3. 7 Statistics for VFTLP results of GR wires of the same size show that V <sub>C</sub>           |

| increases significantly with L, while J <sub>C</sub> is almost independent of L                          |

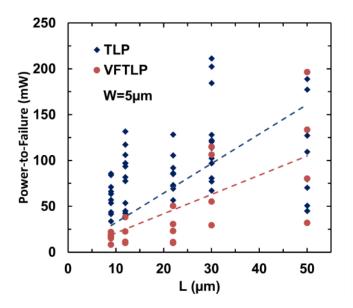

| Figure 3. 8 Statistics, by TLP and VFTLP measurements, of power-to-failure of GR                         |

| samples with a fixed W=5µm and varying L shows that PC increases with L                                  |

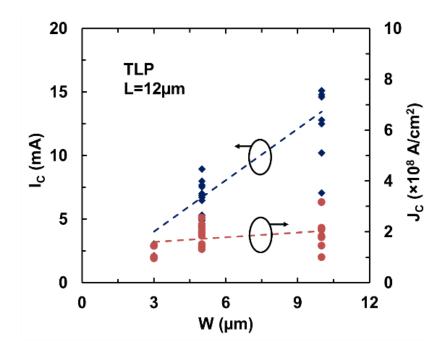

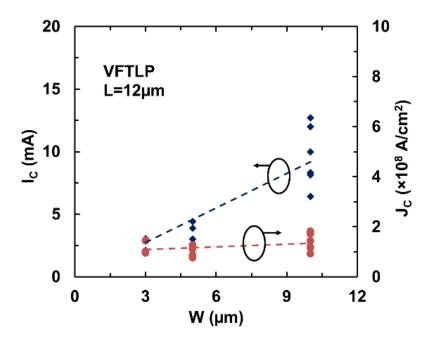

| Figure 3. 9 Statistics for I <sub>C</sub> and J <sub>C</sub> for GR samples of a fixed L=12µm and varying W                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| obtained by TLP (t <sub>d</sub> =100ns, t <sub>r</sub> =10ns) shows a clear dependence of I <sub>C</sub> on W, however, J <sub>C</sub>      |

| $(\sim 1.8 \times 10^8 \text{ A/cm}^2)$ seems to be insensitive to W                                                                        |

| Figure 3. 10 Statistics for I <sub>C</sub> and J <sub>C</sub> versus W for GR samples of a fixed L=12µm and                                 |

| varying W obtained by VFTLP (t <sub>d</sub> =5ns, t <sub>r</sub> =0.2ns) shows clear dependence of I <sub>C</sub> on W,                     |

| however, J <sub>C</sub> (~1.6×10 <sup>8</sup> A/cm <sup>2</sup> ) is almost independent of W                                                |

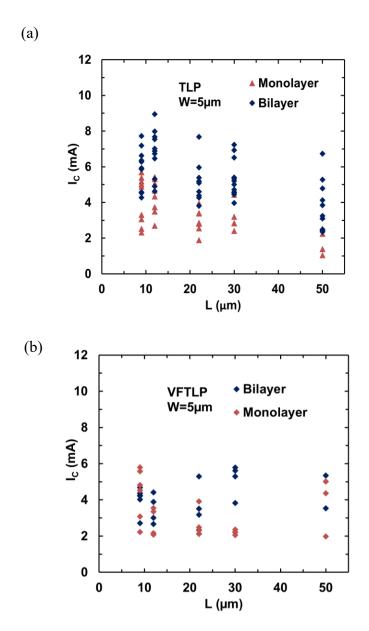

| Figure 3. 11 Statistics on I <sub>C</sub> behaviors for GR samples of W=5 μm, varying L and                                                 |

| number of graphene layers (monolayer and bilayer) obtained by (a) TLP & (b) VFTLP                                                           |

| testing show the layer number impact on ESD robustness: bilayer GR wires are stronger                                                       |

| than monolayer GR wires as expected                                                                                                         |

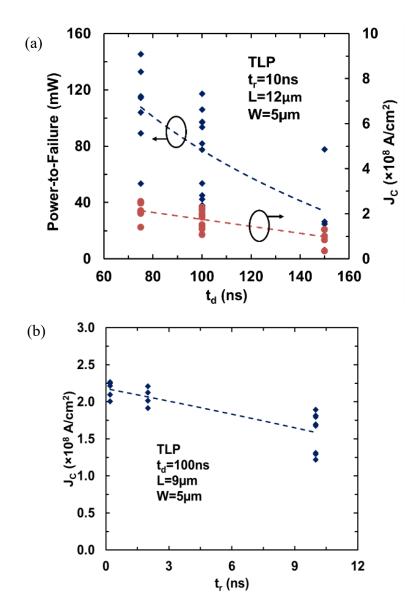

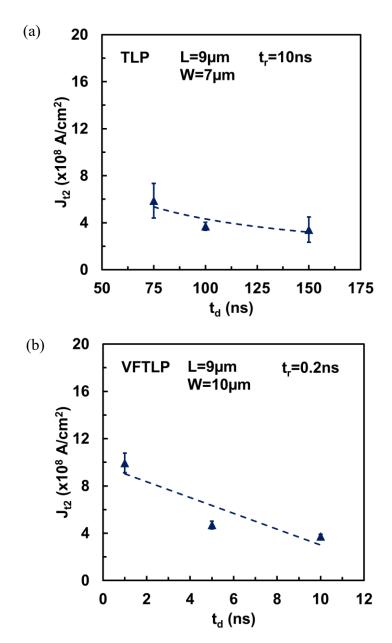

| Figure 3. 12 (a) Statistics of $J_C \sim t_d$ characteristics by TLP ( $t_d = 75/100/150$ ns & $t_r = 10$ ns)                               |

| for GR samples (L=12 $\mu$ m, W=5 $\mu$ m) shows strong impact of t <sub>d</sub> : J <sub>C</sub> decreases (from                           |

| $2.4\times10^8$ A/cm <sup>2</sup> to $1.5\times10^8$ A/cm <sup>2</sup> ) as t <sub>d</sub> increases. Similar phenomenon was also observed  |

| for the measured $P_C$ . (b) Statistics of $J_C \sim t_r$ characteristics by TLP ( $t_r = 0.2/2/10$ ns &                                    |

| $t_d$ =100ns) for GR samples (L=9 $\mu$ m, W=5 $\mu$ m) shows a strong impact of $t_r$ on $J_C$                                             |

| (decreasing from $2.2 \times 10^8$ A/cm <sup>2</sup> to $1.5 \times 10^8$ A/cm <sup>2</sup> )                                               |

| Figure 3. 13 (a) Statistics of $J_C \sim t_d$ characteristics by VFTLP ( $t_d = 1/5/10$ ns & $t_r = 0.2$ ns)                                |

| for GR samples (L=12μm, W=5μm) shows s strong impact of t <sub>d</sub> : J <sub>C</sub> decreases (from                                     |

| $1.5 \times 10^8 \text{ A/cm}^2 \text{ to } 0.2 \times 10^8 \text{ A/cm}^2)$ as $t_d$ increases. Similarly, $P_C$ also decreases for longer |

| VFTLP pulses. (b) Statistics of $J_C \sim t_r$ characteristics by VFTLP with varying $t_r$                                                  |

| $(0.1/0.2/0.4 \text{ns \& } t_d=5 \text{ns})$ for GR samples (L=9 $\mu$ m, W=5 $\mu$ m) shows strong dependence of                          |

| $J_{\rm C}$ on $t_{\rm r}$ .                                                                                                                |

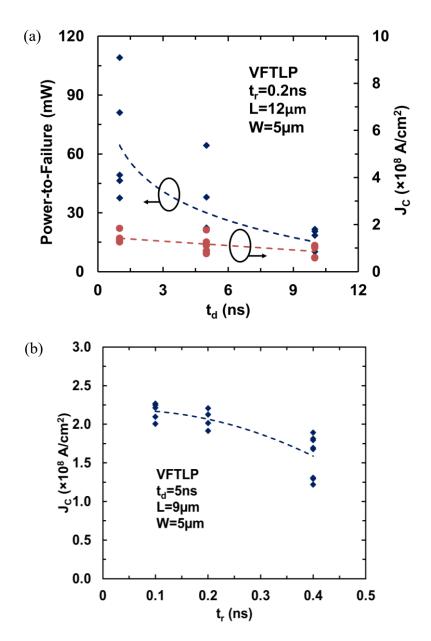

| Figure 3. 14 A 3D statistics map for measured J <sub>C</sub> distribution against varying t <sub>d</sub>                                    |

| $(75/100/150 \text{ns}) \& t_r (0.2/2/10 \text{ns}) \text{ by (a) TLP testing and varying } t_d (1/5/10 \text{ns}) \& t_r$                  |

| (100/200/400ps) by (b) VFTLP testing for GR sample (L=12µm, W=5µm) clearly show                                                             |

| degradation of J <sub>C</sub> with longer t <sub>d</sub> and t <sub>r</sub>                                                                 |

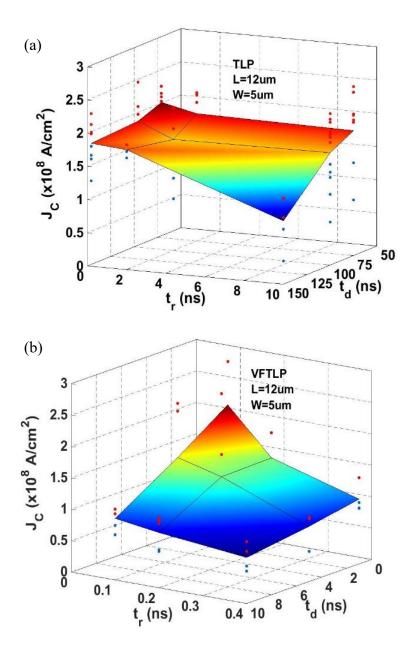

| Figure 3. 15 (a) Measured transient I-V curve for a bilayer GR sample (L=12μm, W=5                                                          |

| $\mu$ m) by TLP at T= -40°C shows exceptional J <sub>t2</sub> ~2.46x10 <sup>8</sup> A/cm <sup>2</sup> . (b) Measured I-V curve              |

| for a bilayer GR sample (L=12 $\mu$ m, W=5 $\mu$ m) by TLP at T= +140 °C shows exceptional                                                  |

| $J_{t2}\sim 2.17 \times 10^8 A/cm^2$                                                                                                        |

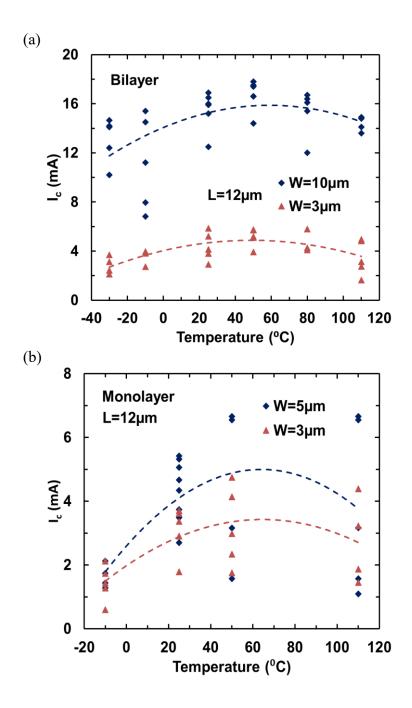

| Figure 3. 16 Statistics for measured I <sub>C</sub> ~T behavior (-30°C to +110°C) for (a) bilayer & (b)                                     |

| monolayer GR wires by TLP testing suggests that optimal temperature treatment                                                               |

| (T~50°C) may exist to improve ESD robustness. 40                                                                                            |

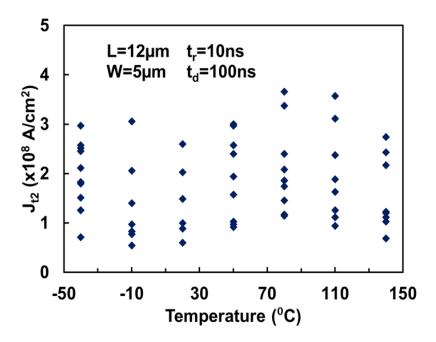

| Figure 3. 17 Statistics for TLP-measured J <sub>12</sub> data against temperature variation (-40°C to                                       |

| 140°C) for bilayer GR samples suggests that possibly optimal temperature treatment may                                                      |

| exist to improve ESD robustness of GR interconnects (T~80°C)                                                                                |

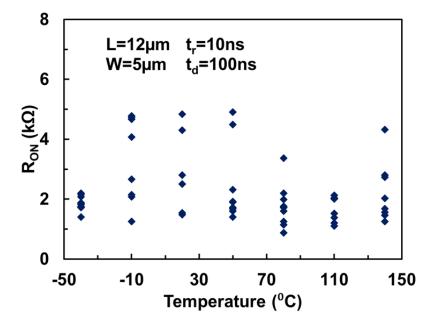

| Figure 3. 18 Statistics for TLP-measured ESD discharging R <sub>ON</sub> for varying temperature (-                                         |

| 40°C to 140°C) shows slight improvement at lower temperature at -40°C and degradation                                                       |

| at higher temperature of +140°C                                                                                                             |

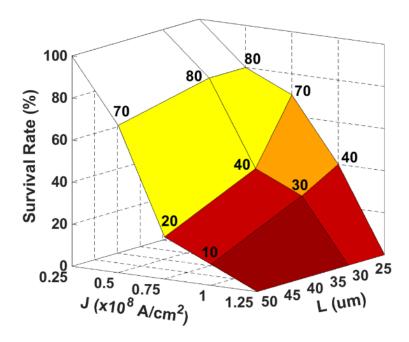

| Figure 3. 19 A 3D statistical map for GR survival rate with respect to GR wire length and                                                   |

| zapping current level for GR samples of varying L (fixed W=5µm) obtained by Abrupt                                                          |

| TLP zapping method                                                                                                                          |

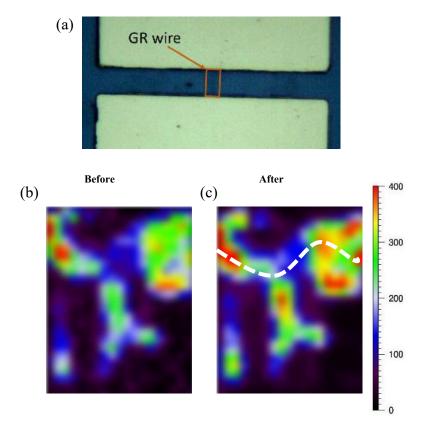

| Figure 3. 20 D-peak intensity in Raman spectrum for a GR sample (L=12μm, W=5μm)                                                             |

| before and after TLP zapping breakdown illustrates defect development, leading to ESD                                                       |

| failure: (a) optical microscopy for GR wire; (b) D-peak intensity before breakdown; (c) D-peak intensity after breakdown                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

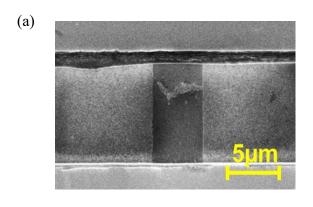

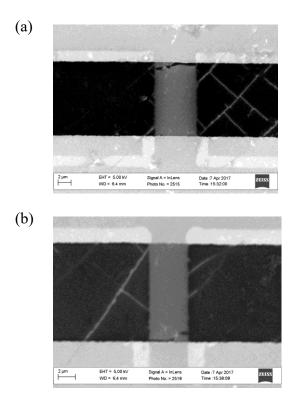

| Figure 3. 21 SEM images show the failure signature that is a fault line across the GR wire after ESD zapping breakdown: (a) GR wires (L=9μm, W=5μm) by TLP zapping (t <sub>d</sub> =100ns, t <sub>r</sub> =10ns); (b) GR wires (L=12μm, W=5μm) by VFTLP stressing (t <sub>d</sub> =5ns, t <sub>r</sub> =0.2ns)                                                    |

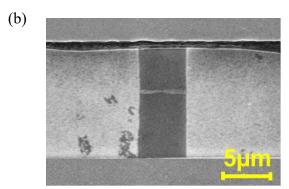

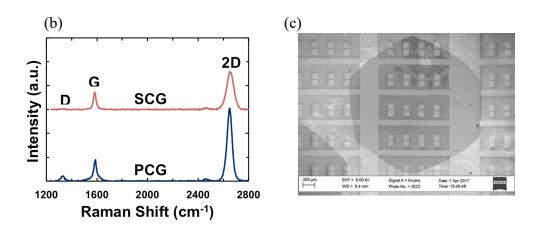

| Figure 3. 22 (a) Single-crystalline graphene (SCG) on coppor films. (b) Raman Analysis of the PCG and SCG graphene films. (c) SEM images of metal pads covered by SCG film                                                                                                                                                                                        |

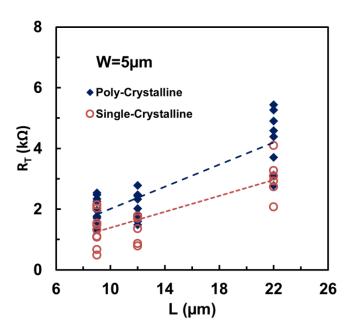

| Figure 3. 23 Statistics analysis for graphene wire total resistance for varying L (W=5 $\mu$ m) by DC testing. Graphene sheet resistances are extracted to be 650 $\Omega$ / $\square$ (SCG) and 910 $\Omega$ / $\square$ (PCG)                                                                                                                                   |

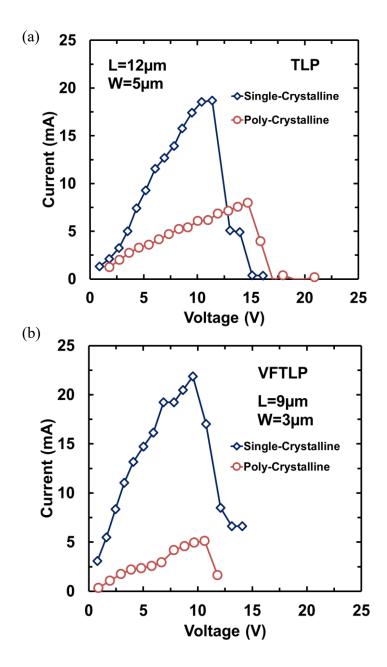

| Figure 3. 24 (a) Comparison of TLP transient I-V characteristics for SCG and PCG interconnects samples (L=12 $\mu$ m, W=5 $\mu$ m) shows improved ESD capability for SCG. (b) VFTLP I-V curves for SCG and PCG samples (L=9 $\mu$ m, W=3 $\mu$ m) shows It2 of SCG interconnects is much improved over PCG wires                                                  |

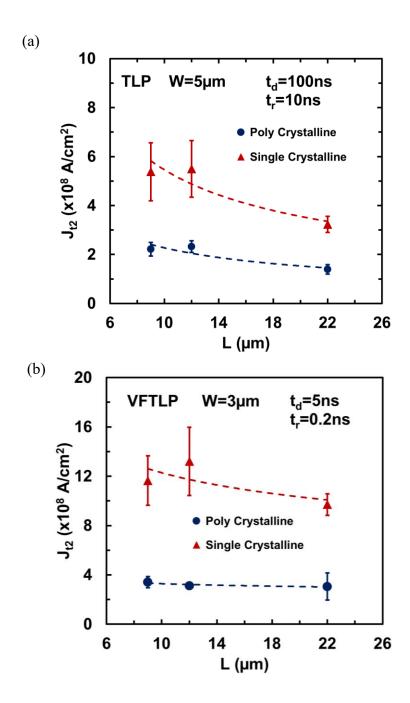

| increases                                                                                                                                                                                                                                                                                                                                                         |

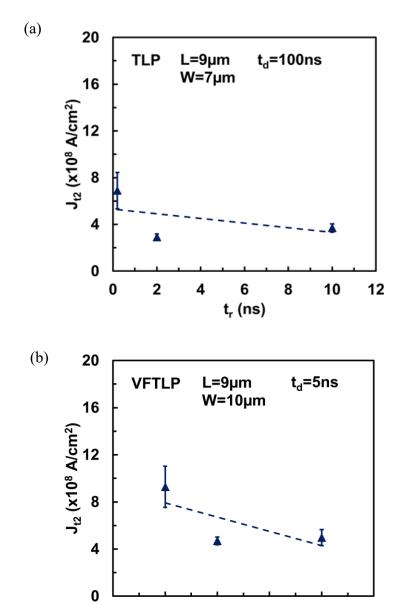

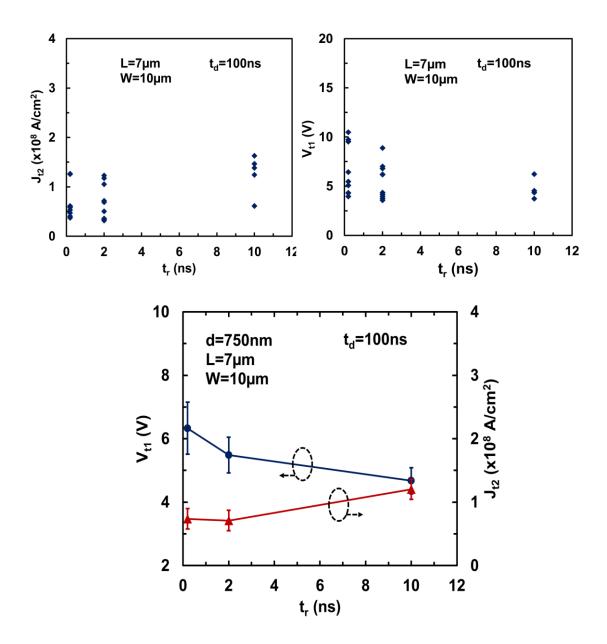

| Figure 3. 27 (a) Statistics of $J_{t2} \sim t_r$ characteristics by TLP testing ( $t_r = 0.2/2/10$ ns for fixed $t_d$ =100ns) for SCG wires. (b) Statistics of $J_{t2} \sim t_r$ characteristics by VFTLP testing with varying $t_r$ (0.1/0.2/0.4ns at fixed $t_d$ =5ns) for SCG samples (L=9 $\mu$ m, W=10 $\mu$ m). Dependence of $J_{t2}$ on $t_r$ is observed |

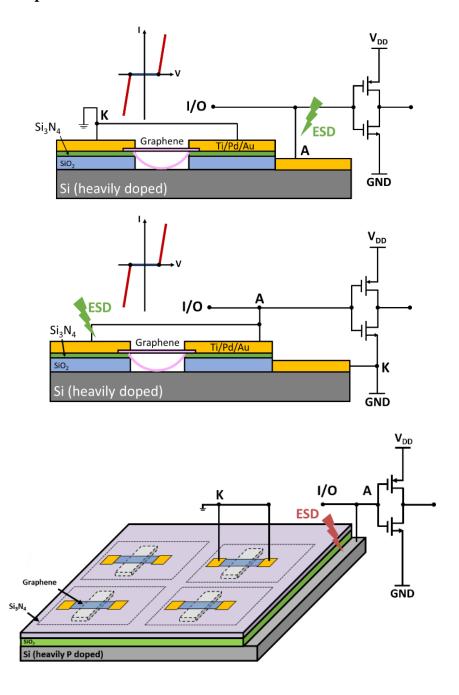

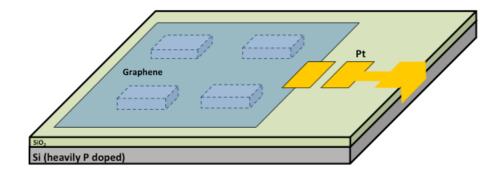

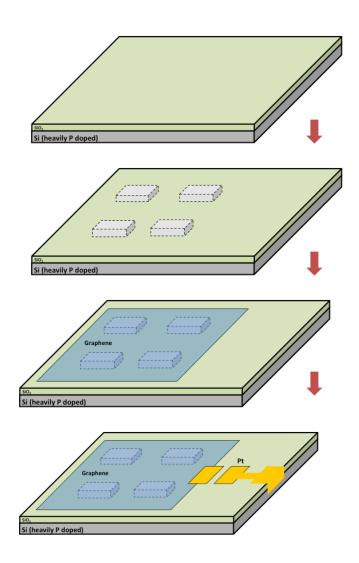

| Figure 4. 1 Cross-section and 3D view with circuit scenario for the new gNEMS switch ESD protection structure. The normal-OFF switch can be turned on by pulling down the graphene membrane by ESD pulses. The inset illustrates an ideal ON-OFF I-V behavior for the gNEMS ESD switch.                                                                           |

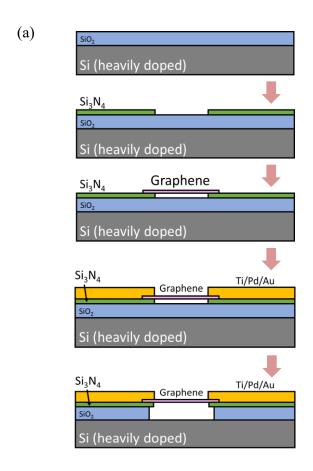

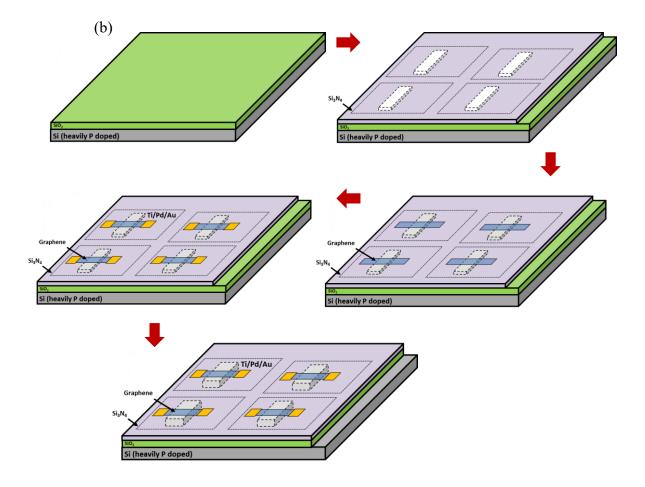

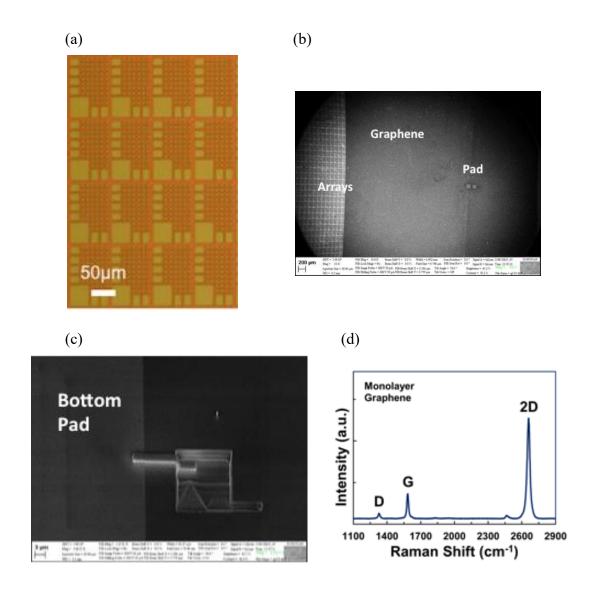

| Figure 4. 2 A new CMOS-compatible fabrication flow for making gNEMS ESD switch devices                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                   |

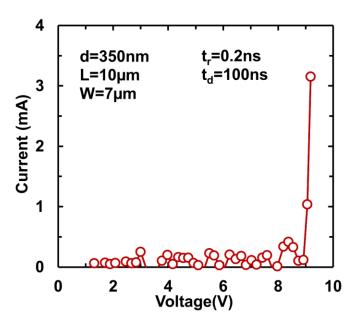

| Figure 4. 5 Measured I-V curve by TLP pulsing for a prototype gNEMS device shows                                                 |

|----------------------------------------------------------------------------------------------------------------------------------|

| transient ESD switching with a fast response time down to 200ps                                                                  |

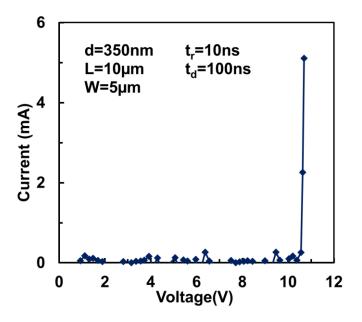

| Figure 4. 6 Measured transient ESD I-V curve for a sample gNEMS switch by TLP                                                    |

| stressing                                                                                                                        |

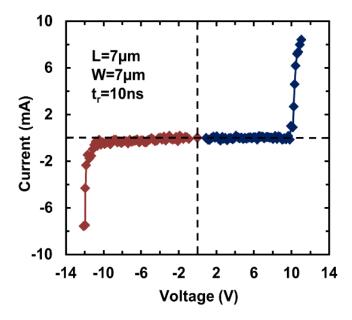

| Figure 4. 7 Measured I-V curve by TLP for a prototype gNEMS device shows near                                                    |

| symmetric I-V switching behaviors desired for ICs. The slight asymmetry is attributed to                                         |

| the asymmetric prototype device structure used                                                                                   |

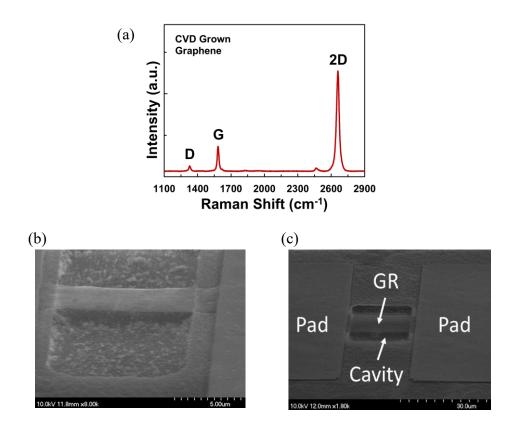

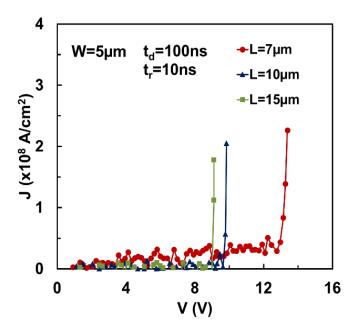

| Figure 4. 8 Measured transient J~V characteristics of gNEMS switches with different                                              |

| graphene length (L= $7/10/15\mu m$ , W= $5\mu m$ ) by TLP testing show that $V_{t1}$ increases as L                              |

| decreases                                                                                                                        |

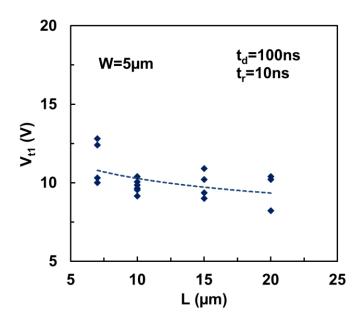

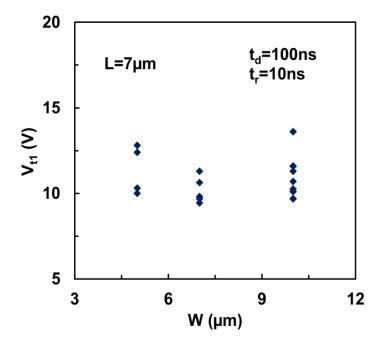

| Figure 4. 9 Statistical $V_{t1} \sim L$ (W=5 $\mu$ m) for gNEMS devices from TLP measurement                                     |

| shows a monotonic relationship                                                                                                   |

| Figure 4. 10 Statistical $J_{t2} \sim L$ characteristics of gNEMS switches (W=5 $\mu$ m) by TLP                                  |

| testing shows that J <sub>12</sub> slightly degraded for longer graphene ribbons                                                 |

| Figure 4. 11 Statistical $J_{t2} \sim L$ characteristics of gNEMS switches (W=5 $\mu$ m) by TLP                                  |

| testing shows that J <sub>t2</sub> slightly degraded for longer graphene ribbons                                                 |

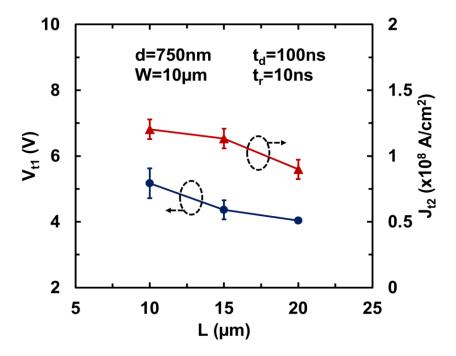

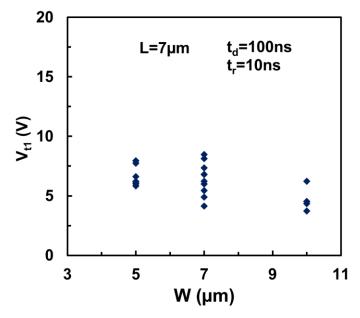

| Figure 4. 12 Statistical Vt1 ~ W characteristics (L=7μm) for gNEMS devices (d=350nm)                                             |

| by TLP testing suggests that Vt1 seems to be insensitive to W                                                                    |

| Figure 4. 13 Statistical $I_{t2} \sim W$ characteristics (L=7 $\mu$ m) for gNEMS devices (d=350nm)                               |

| by TLP testing shows dependence of ESD I <sub>t2</sub> on W                                                                      |

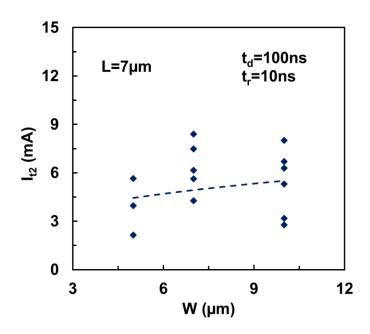

| Figure 4. 14 Statistical $I_{t2} \sim W$ characteristics (L=7 $\mu$ m) for gNEMS devices (d=750nm)                               |

| by TLP testing shows dependence of ESD I <sub>t2</sub> on W                                                                      |

| Figure 4. 15 Statistical $I_{t2} \sim W$ characteristics (L=7 $\mu$ m) for gNEMS devices (d=750nm)                               |

| by TLP testing shows dependence of ESD I <sub>t2</sub> on W                                                                      |

| Figure 4. 16 Statistical $I_{t2} \sim W$ characteristics (L=7 $\mu$ m) for gNEMS devices by TLP                                  |

| testing shows dependence of ESD I <sub>t2</sub> on W                                                                             |

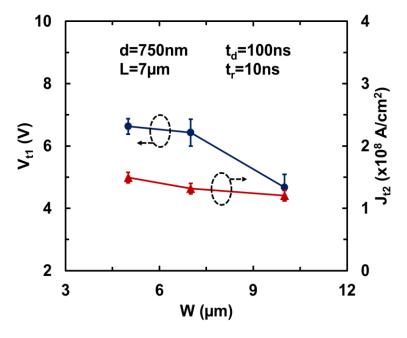

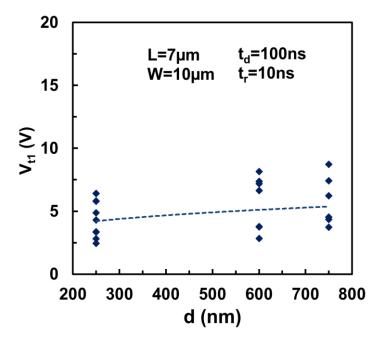

| Figure 4. 17 Statistics for V <sub>t1</sub> versus trench depth (d=250/600/750nm) for gNEMS switch                               |

| samples of a fixed L= $7\mu m$ and W= $10\mu m$ obtained by TLP testing (t <sub>d</sub> = $100ns$ , t <sub>r</sub> = $10ns$ ) 79 |

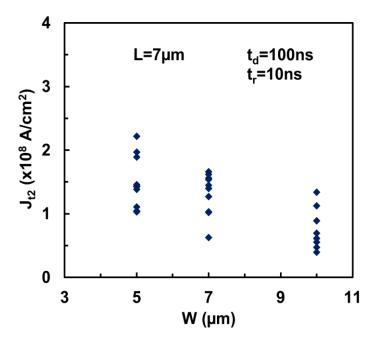

| Figure 4. 18 Statistics for J <sub>t2</sub> of gNEMS samples with varying trench depth                                           |

| $(d=250/600/750nm)$ of a fixed L=7 $\mu$ m, W=10 $\mu$ m obtained by TLP (t <sub>d</sub> =100ns, t <sub>r</sub> =10ns).80        |

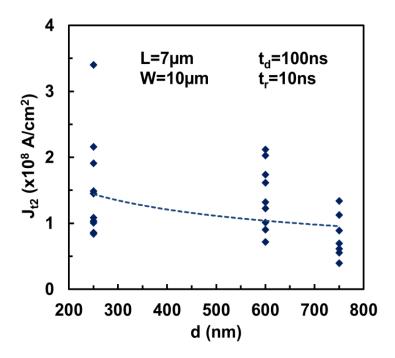

| Figure 4. 19 Measured ESD discharging R <sub>ON</sub> distribution for sample gNEMS devices                                      |

| shows dependence of the device dimensions                                                                                        |

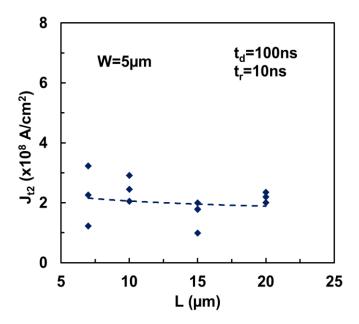

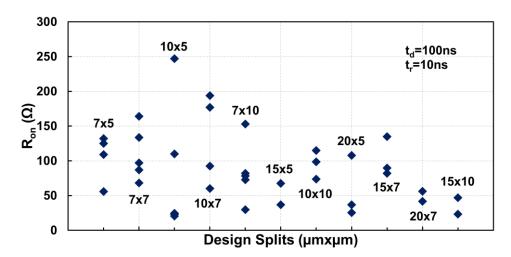

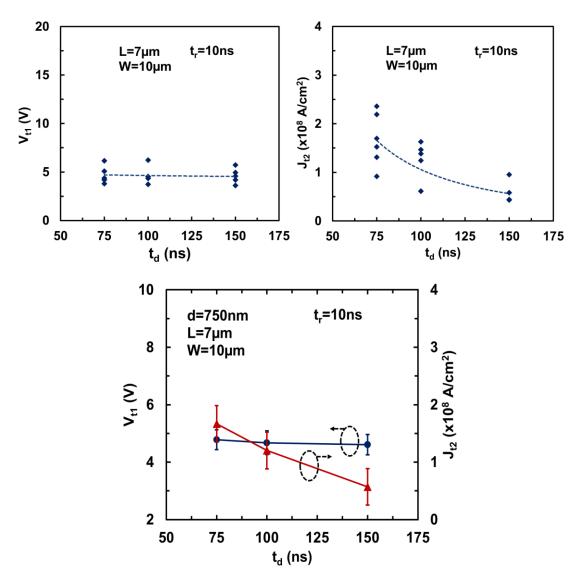

| Figure 4. 20 Statistics of $V_{t1} \sim t_d$ characteristics by TLP testing ( $t_d = 75/100/150$ ns at                           |

| t <sub>r</sub> =10ns) for gNEMS switch samples (L=10μm, W=15μm) shows influence of t <sub>d</sub> on                             |

| transient ESD triggering voltage                                                                                                 |

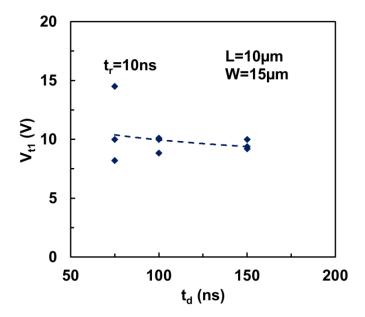

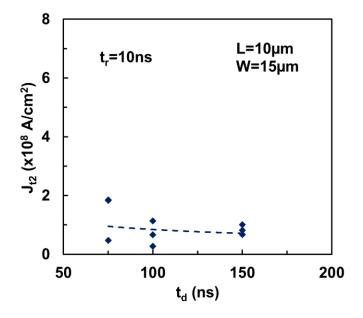

| Figure 4. 21 Statistics of $J_{t2} \sim t_d$ characteristics by TLP testing ( $t_d = 75/100/150$ ns at                           |

| $t_r$ =10ns) for gNEMS switch samples (L=10 $\mu$ m, W=15 $\mu$ m) shows influence of $t_d$ on ESD                               |

| discharging capacity J <sub>t2</sub> 83                                                                                          |

| Figure 4. 22 Statistics of $J_{t2} \sim t_d$ characteristics by TLP testing ( $t_d = 75/100/150$ ns at                           |

| $t_r\!\!=\!\!10 ns)$ for gNEMS switch samples (L=10 $\mu m$ , W=15 $\mu m$ ) shows influence of $t_d$ on ESD                     |

| discharging capacity J <sub>t2</sub> 84                                                                                          |

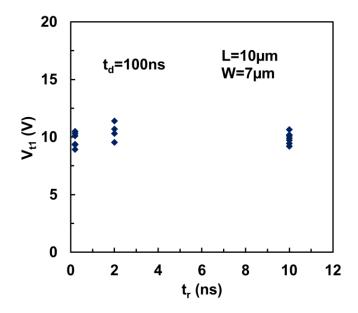

| Figure 4. 23 Statistics of $V_{t1} \sim t_r$ characteristics by TLP testing ( $t_r = 0.2/2/10$ ns at                             |

| $t_d=100$ ns) for gNEMS switch samples ( $I=10$ um, $W=7$ um).                                                                   |

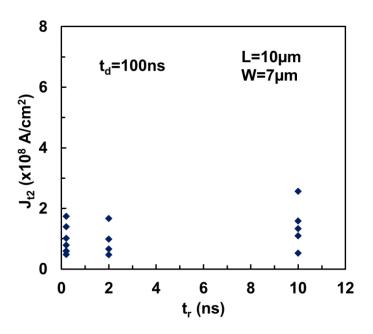

| Figure 4. 24 Statistics of $J_{t2} \sim t_r$ characteristics by TLP testing ( $t_r = 0.2/2/10$ ns at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>d</sub> =100ns) for gNEMS switch samples (L=10μm, W=7μm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 4. 25 Statistics of $V_{t1} \sim t_r$ characteristics by TLP testing ( $t_r = 0.2/2/10$ ns at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| t <sub>d</sub> =100ns) for gNEMS switch samples (L=10μm, W=7μm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

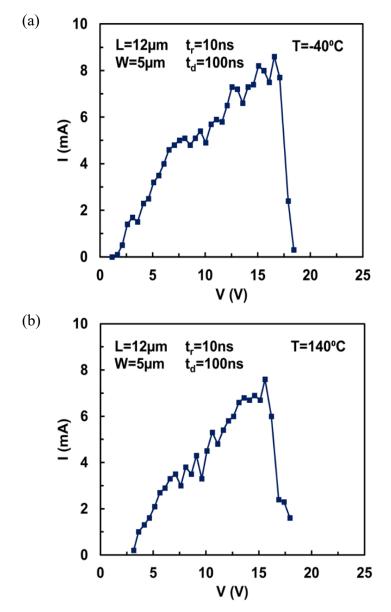

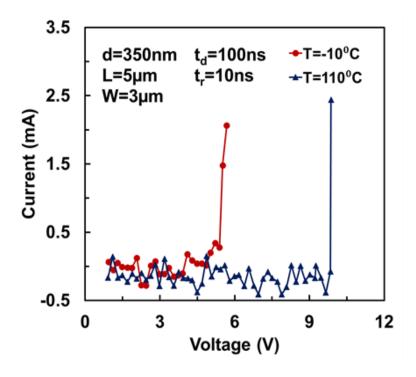

| Figure 4. 26 Graphene NEMS switch tested in extremely high and low temperatures 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

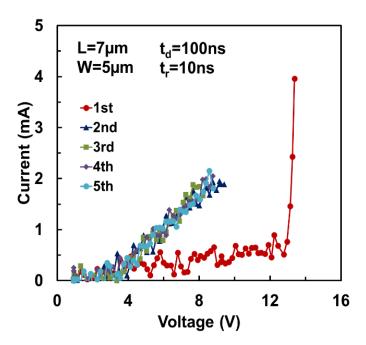

| Figure 4. 27 TLP characteristic of graphene ESD switch (L=7μm, W=5μm) for 5 times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>t1</sub> degrades after the second test. The R <sub>ON</sub> increases due to the leakage from dielectrics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

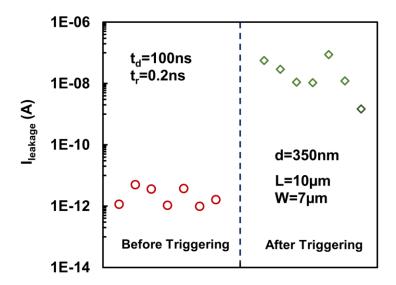

| Figure 4. 28 DC leakage current testing of graphene ESD switch (d=350nm, L=10µm,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| W=7µm) before and after triggering. The leakage current ramps up after the device turns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| on91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4. 29 SEM image of graphene ESD switch (d=350nm, L=10μm, W=5μm) after                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TLP stressing. Graphene ribbon shows an explicit discontinuous vacancy by the transient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| pulses, indicating the graphene switch breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| pulses, moreums are graphene strategical s |

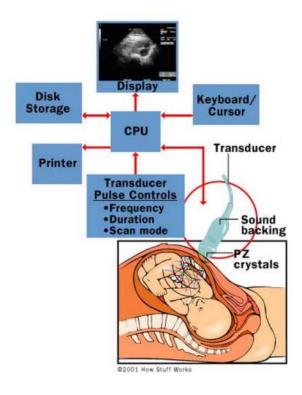

| Figure 5. 1 Ultrasound imaging system [57]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

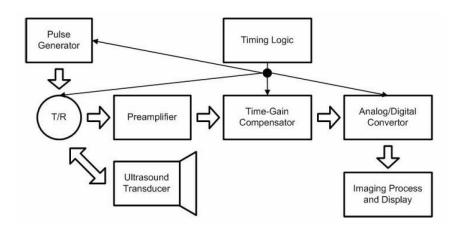

| Figure 5. 2 Ultrasound imaging system with pulse generators and IC components 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

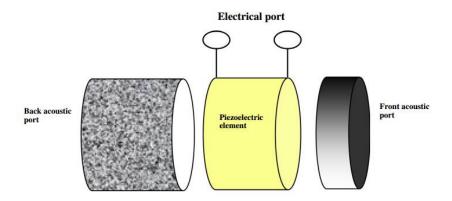

| Figure 5. 3 Structure of bulk piezoelectric ultrasound transducer [68]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

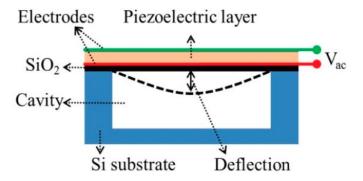

| Figure 5. 4 Structure of a typical PMUT design where a piezoelectric membrane is onto a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| cavity [69]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

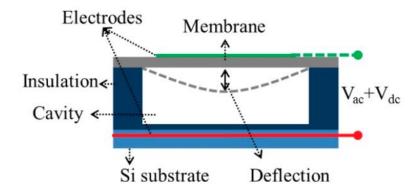

| Figure 5. 5 Structure of a typical CMUT design [83]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

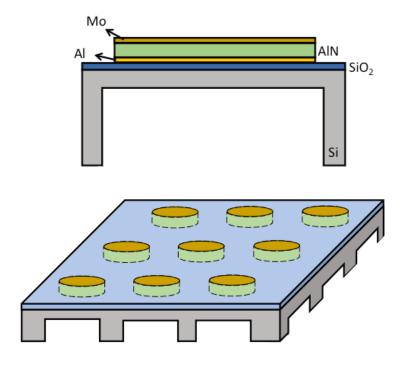

| Figure 5. 6 Proposed AIN PMUT with single element and array design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

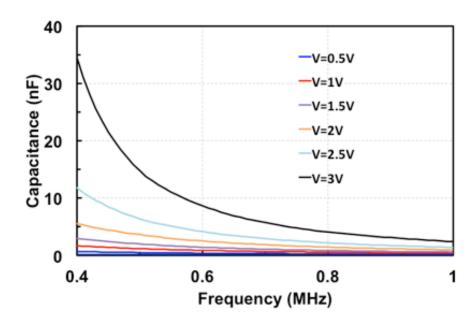

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |