## **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Nanopillar Emitters: Photonic Crystals, Heterostructures, and Waveguides

### **Permalink**

https://escholarship.org/uc/item/52n3j50z

#### **Author**

Scofield, Adam Christopher

## **Publication Date**

2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

## Los Angeles

Nanopillar Emitters: Photonic Crystals, Heterostructures, and Waveguides

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

By

Adam Christopher Scofield

©Copyright by

Adam Christopher Scofield

2015

#### ABSTRACT OF THE DISSERTATION

Nanopillar Emitters: Photonic Crystals, Heterostructures, and Waveguides

by

#### Adam Christopher Scofield

Doctor of Philosophy in Electrical Engineering

University of California, Los Angeles, 2015

Professor Diana L. Huffaker, Chair

Compound semiconductors, which consist mostly of column III and column V elements, are widely used in opto-electronic devices such as light-emitting diodes, lasers, and solar cells. Thin-film, one-dimensional III-V devices are a mature technology used in industrial and commercial applications. Because of this, there is little left to explore in one-dimensional structures to improve device performance significantly, with advances usually attributed to improvements in fabrication and production volume.

In order to further explore the possibilities of compound semiconductors, research has to led to the development of nanowires and nanopillars. These nanostructures, with diameters ranging from 10 - 100 nm and lengths of several micrometers, are synthesized in a bottom-up approach, rather than being etched with standard nanofabrication techniques. This approach allows researchers to develop unique three-dimensional structures with differing III-V

ii

compositions in order to make transformational, rather than incremental improvements in device performance. The ability to control III-V synthesis in three-dimensions has led to numerous demonstrations of opto-electronic devices with broad applications in solid-state lighting, medical sensing, spectroscopy, and telecommunications.

In this dissertation, nanopillar-based emitters, particularly in the near-infrared, are explored. The fundamental motivation behind this work is the ability to directly grow GaAs and InGaAs nanopillars on Si (111) substrates without dislocation defects, making them promising for applications such as low-power lasers for optical interconnects. We begin with an analysis for the needs of a laser design to reach power levels necessary for chip-scale optical interconnects. This sets the direction for research on nanopillar-based emitters. First, the photonics of nanopillar arrays are explored, which led to the demonstration of photonic crystal cavities and photonic crystal lasers. Then, the fabrication of electrically-driven nanopillar emitters is demonstrated and used to develop advanced heterostructures for current injection and carrier confinement. Finally, we show the monolithic waveguide integration of nanopillar devices and effective coupling between a single-mode optical fiber and nanopillar device, paving the way for future development of nanopillar lasers for optical interconnects.

The dissertation of Adam Christopher Scofield is approved.

Robert N. Candler

Robert F. Hicks

Dwight C. Streit

Diana L. Huffaker, Committee Chair

University of California, Los Angeles

2015

This thesis is dedicated to my friends and family.

## TABLE OF CONTENTS:

| Ab | ostract of the dissertation                             | ii   |

|----|---------------------------------------------------------|------|

| Ac | cknowlegdements                                         | viii |

| Vi | ta                                                      | ix   |

| 1. | Introduction                                            | 1    |

|    | 1.1. Overview                                           | 1    |

|    | 1.2. System Analysis of Optical Interconnects           | 2    |

|    | 1.3. General Design Requirements of the Laser           | 5    |

|    | 1.4. Micro-Ring and Photonic Crystal Resonators         | 12   |

|    | 1.5. Conclusions                                        | 12   |

|    | 1.6. References                                         | 14   |

| 2. | Nanopillar Crystal Growth                               | 16   |

|    | 2.1. Selective-Area Growth of III-V Nanopillars         | 16   |

|    | 2.2. In-situ Passivation of Nanopillars                 | 18   |

|    | 2.3. References                                         | 22   |

| 3. | Nanopillar Photonic Crystals                            | 24   |

|    | 3.1. Optical Resonators for Nanowires                   | 24   |

|    | 3.2. Bottom-up Photonic Crystals                        | 25   |

|    | 3.3. Optical Characterization of Nanopillar PhCs        | 28   |

|    | 3.4. Conclusions                                        | 33   |

|    | 3.5. References                                         | 33   |

| 4. | Low-Threshold Photonic Crystal Lasers                   | 36   |

|    | 4.1. Background and Challenges of Nanowire Lasers       | 36   |

|    | 4.2. Nanopillar PhC Laser Structure                     | 37   |

|    | 4.3. FDTD Simulation and Cavity Optimization            | 39   |

|    | 4.4. Nanopillar PhC Laser Characterization              | 41   |

|    | 4.5. Conclusions.                                       | 43   |

|    | 4.6. References                                         | 43   |

| 5. | Light-Emitting Diodes                                   | 46   |

|    | 5.1. Background of Nanowire-Based Light-Emitting Diodes | 46   |

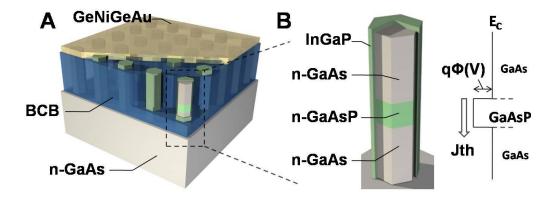

|    | 5.2. Nanopillar LED Device Design and Structure                           | 47  |  |  |

|----|---------------------------------------------------------------------------|-----|--|--|

|    | 5.3. Nanopillar LED Optical and Electrical Characterization               | 49  |  |  |

|    | 5.4. Conclusions                                                          | 52  |  |  |

|    | 5.5. References                                                           | .52 |  |  |

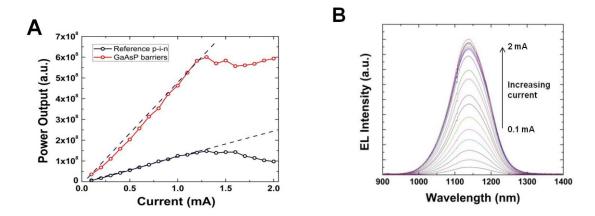

| 6. | Advanced Heterostructures in LEDs                                         | 55  |  |  |

|    | 6.1. Nanowire-Based LED Heterostructures                                  | 55  |  |  |

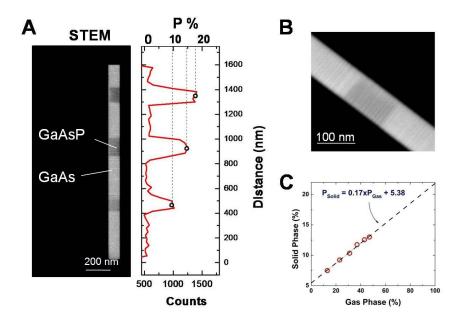

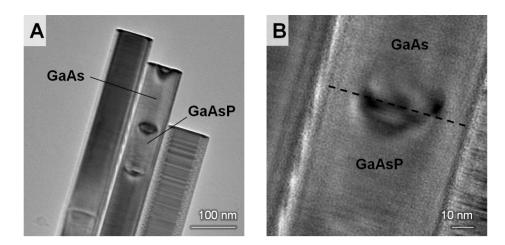

|    | 6.2. Forming Axial Diffusion Barriers with GaAsP Inserts                  | 56  |  |  |

|    | 6.3. TEM and EDS Analysis of GaAsP Inserts                                | 57  |  |  |

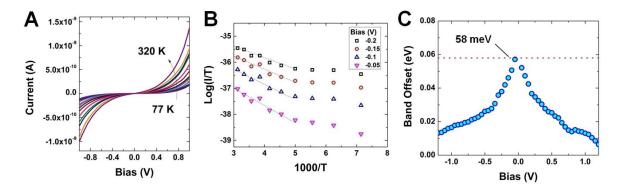

|    | 6.4. Single GaAsP Insert Devices and Band-Offset Measurements             | 59  |  |  |

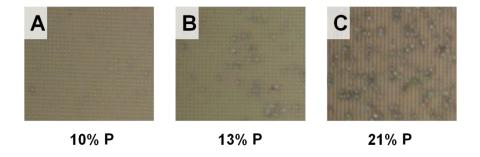

|    | 6.5. Implementing GaAsP Barriers in Nanopillar LEDs                       | 61  |  |  |

|    | 6.6. Conclusions                                                          | 63  |  |  |

|    | 6.7. References                                                           | .64 |  |  |

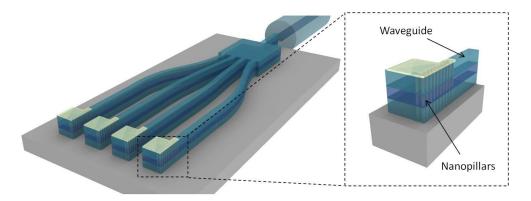

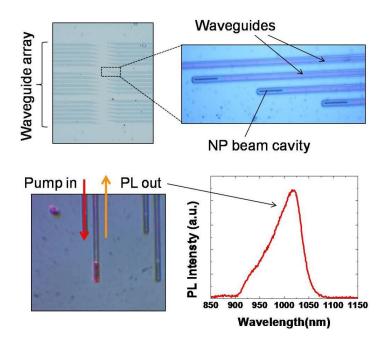

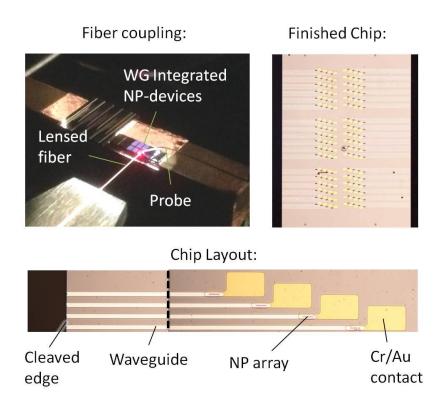

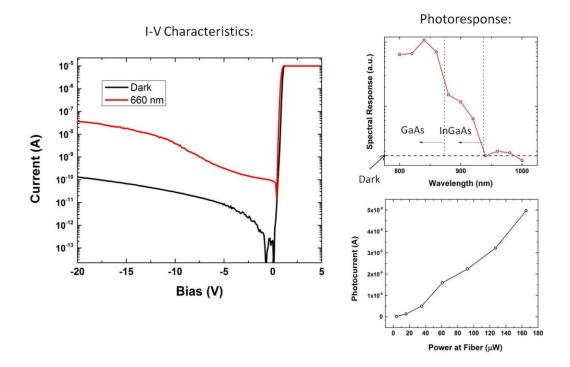

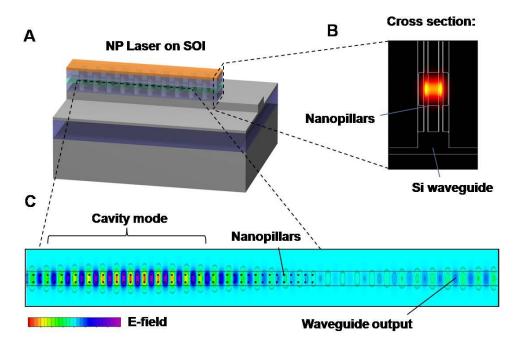

| 7. | Waveguide Integration                                                     | 66  |  |  |

|    | 7.1. Integration of Nanopillars with Passive Optical Waveguides           | 66  |  |  |

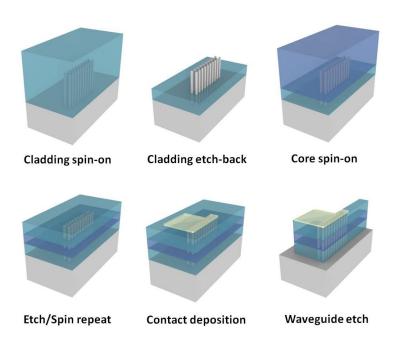

|    | 7.2. Process Development and Testing of Waveguide Coupling to Nanopillars | 68  |  |  |

|    | 7.3. Photonic Crystal Cavities in Waveguides                              | 71  |  |  |

|    | 7.4. Fiber-Coupled Nanopillar Photodetectors                              | 75  |  |  |

|    | 7.5. Conclusions                                                          | 78  |  |  |

|    | 7.6. References                                                           | .78 |  |  |

| 8. | Summary and Outlook                                                       | 81  |  |  |

| Ap | Appendix A83                                                              |     |  |  |

| Ap | pendix B                                                                  | 84  |  |  |

| Ap | Appendix C86                                                              |     |  |  |

#### **ACKNOWLEDGEMENTS**

The work that contributed to this thesis was challenging, painstaking, and required years of long hours and late nights in the lab. It couldn't have been done without the support of my friends and family making sure I didn't get lost in the work. Special thanks also go to my advisor, Diana Huffaker, who spends nearly every day in the lab working with her students and challenging them to do more.

The majority of the work in this thesis was supported by Dr. Gernot Pomrenke of the Air Force Office of Scientific Research. A major part of the electromagnetic simulation was done in collaboration with Dr. Se-Heon Kim while a post-doctoral researcher at Caltech. Important aspects of the material growth were based on earlier work by Joshua Shapiro. All transmission electron microscopy was performed by Andrew Lin. Dr. Baolai Liang constructed the first version of the photoluminescence setup which formed the basis of future setups used for nearly all of the optical measurements.

#### **VITA**

University of California, Los Angeles Los Angeles, CA

M.S. in Electrical Engineering 2011

Rensselaer Polytechnic Institute Troy, NY

B.S. in Electrical Engineering 2009

Rensselaer Polytechnic Institute Troy, NY

B.S. in Physics 2009

#### **Journal Publications**

- **A.C. Scofield**, S-H Kim, J.N. Shapiro, A. Lin, B. Liang, A. Scherer, D.L. Huffaker, "Bottom-up photonic crystal lasers", *Nano Letters*, 11 (12), 5387-5390

- A.C. Scofield, A. Lin, J.N. Shapiro, P.N. Senanayake, G. Mariani, M. Haddad, D.L.

Huffaker, "Composite axial/core-shell nanopillar light-emitting diodes at 1.3 μm", *Applied Physics Letters*, 101 (5) 05311

- A.C. Scofield, J.N. Shapiro, A. Lin, A.D. Williams, P.S. Wong, B. Liang, D.L. Huffaker

"Bottom-up photonic crystal cavities formed by patterned III-V nanopillars", *Nano Letters*,

11(6), 2242-2246

- **A.C. Scofield**, A. Lin, M. Haddad, D.L. Huffaker, "Axial diffusion barriers in near-infrared nanopillar LEDs", *Nano Letters*, in press

#### **Conference Presentations**

- A.C. Scofield, D.L. Huffaker, "Monolithic waveguide integration of nanopillar photonic devices", Semiconductor and Integrated Optoelectronics, 2014 (Invited)

- A.C. Scofield, D.L. Huffaker, "Integrated nanopillar devices: 3D engineering of

- optoelectronics from the bottom up", SPIE Photonics West, 2014

- A.C. Scofield, C. Tu, J.N. Shapiro, A. Lin, B.L. Liang, D.L. Huffaker, "Emission enhancement of axial Ga(In)As nanopillar heterostructures with GaAs(P) diffusion barriers",

International Symposium on Compound Semiconductors, 2012 (Invited), Best Student

Paper Award

- **A.C. Scofield**, S-H Kim, J.N. Shapiro, A. Lin, B. Liang, A. Scherer, D.L. Huffaker, "Room-temperature continuous-wave lasing in nanopillar photonic crystal cavities", *Conference for Lasers and Electro-Optics*, 2012

- **A.C. Scofield**, J.N. Shapiro, A. Lin, A.D. Williams, P.S. Wong, B. Liang, D.L. Huffaker, "Bottom-up photonic crystal cavities formed by III-V nanopillar arrays", *Conference for Lasers and Electro-Optics*, 2011

### **Patents and Intellectual Property**

- A.C. Scofield, D.L. Huffaker, "Nanopillar photonic crystal lasers", U.S. Patent Application

No. 14/071,283

- A.C. Scofield, D.L. Huffaker, "Nanopillar photonic devices coupled to dielectric waveguides", U.S. Provision Patent No. 61/823,720

- A.C. Scofield, D.L. Huffaker, "Axial GaAs/GaAsP nanopillar heterostructures grown by selective-area MOCVD", U.S. Provision Patent No. 62/019,231

- A.C. Scofield, A. Lin, D.L. Huffaker, "Hybrid Si/III-V nanopillar optoelectronic devices",

U.S. Provision Patent No. 62/019,234

## Chapter 1

#### 1.1 OVERVIEW

For more than a decade, researchers across the field of photonics have strived to achieve optical interconnects within and between silicon chips<sup>1</sup>. While forming an effective detector based on epitaxial Germanium was developed early on<sup>2–5</sup>, there is still a strong need for a light-emitting device on Silicon. The advent of high-efficiency vertical cavity surface emitting lasers (VCSELs) and flip-chip bonded InGaAsP lasers on silicon-on-insulator (SOI) substrates<sup>6,7</sup> has enabled high-speed active optical cables to increase bandwidth and reduce power consumption in computer clusters. However, as scaling in electronics increases, the demand for higher bandwidth between processors and lower power consumption per bit is also increasing<sup>8,9</sup>. To address this problem, many companies and researchers have been working towards pushing optoelectronic transceivers on chip.

While the power requirements in terms of femto-joules-per-bit have been well established for optical interconnects for intra- and inter-chip communications<sup>9</sup>, there is a void in literature as to the actual requirements these numbers place on the design of lasers that can operate at this extremely low power level. For optical interconnects to be viable for inter- and intra-chip communications, it is well known that the system power dissipation needs to be on the order of 10 fJ/bit or less. Even though a large body of research exists for micro/nano lasers aimed at this application, an analysis of the actual laser device requirements that are necessary to make these systems practical is absent from literature. In this chapter, we analyze a basic optical interconnect based on the state-of-the-art reported values for the various components, and determine the laser design requirements in terms of cavity Q, active area, carrier lifetime, and thermal dissipation.

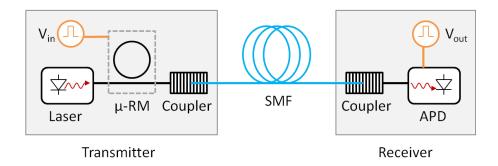

**Fig. 1**. Schematic of the optical system for a single channel. Whether the complete system uses multiple fibers or wavelength division multiplexing, each laser will have to power the photodetectors through these same basic components.

#### 1.2 SYSTEM ANALYSIS OF OPTICAL INTERCONNECTS

In order to make a realistic set of input and output power requirements for the next generation lasers, a basic system analysis of the optical interconnect is necessary. While the driver electronics for the lasers are quite complicated, the actual optical system is relatively simple. Figure 1 shows a schematic diagram of the system for a single transmission channel. The systems consists of five components: (i) laser, (ii) modulator, (iii) waveguide-to-fiber couplers, (iv) optical fiber, and (v) photodetector. The input power of the laser is the target energy per bit minus the energy per bit consumed by the modulator. The output power of the laser is set by the photodetector sensitivity plus the optical loss of each of the components between the laser and detector.

#### A. SILICON MICRO-RING MODULATORS

The most compact and lowest energy consumption modulators on the silicon platform are microring modulators<sup>10–12</sup>. The fundamental operating principle of these devices is plasma dispersion due to excess carriers in silicon. The silicon microring is incorporated with a lateral p-i-n junction. Injection of carriers into the ring causes a change in the refractive index of silicon, and shifts the resonant frequency of the microring. This

shift in resonant frequency changes the coupling of light from the adjacent bus waveguide into the ring. This results in modulation of the light passing through the bus waveguide. The fundamental limitations on this design have been explored in detail to achieve the highest level of performance. The end result is a modulation rate of 25 Gb/s at a cost of 7 fJ/bit. Additionally, the inherent waveguide coupling results in an insertion loss of 2 dB.

#### **B. WAVEGUIDE-TO-FIBER COUPLERS**

A critical function and challenge in optical interconnects is coupling of light from on-chip waveguides to optical fibers. Two approaches are taken in the design of fiber couplers: vertical couplers and edge couplers <sup>13,14</sup>. The vertical couplers shown have the advantage of easier alignment. Large holes can be etched into the silicon substrate which serves as a plug for a multi-fiber connector <sup>15</sup>. The drawback to this approach is that multimode fibers are necessary for low loss coupling. Alternatively, edge couplers using a gradient index waveguide or inverse tapered waveguide can couple to single mode fibers at the cost of precision alignment. In either case, over a 50 nm wavelength range necessary for wavelength division multiplexing, approximately 1 dB of low can be expected.

#### C. OPTICAL FIBERS

The loss mechanisms in optical fibers are well established. As the total loss is dependent on the length of the fiber between the two chips, the fiber length must be set to some reasonable value. Both for high performance computer clusters and data centers, it can be expected that 1 km of fiber will fit most applications. Whether the 1310 nm or 1550 nm center wavelength is used is yet to be determined since at both of these wavelengths, the

optical loss is less than 1 dB/km. The worst case scenario using a 1310 nm center wavelength will have a loss of 0.5 dB/km.

#### D. GE-ON-SI AVALANCHE PHOTODETECTORS

Currently, the standard detectors used in silicon optoelectronic transceivers are Ge pii-n photodetectors grown on silicon waveguides 16. The material quality has been dramatically improved in order to achieve responsivities greater than 0.9 A/W. However, since there is no gain in the detector, a substantial optical power is necessary for a reasonable bit-error-rate. Ge-on-Si avalanche photodetectors have recently been demonstrated with a gain-bandwidth product of 340 GHz<sup>4</sup>. The end result is that a bit-error-rate of 10<sup>-9</sup> gives a receiver sensitivity of -29 dBm. This value sets the absolute minimum power to 1.3 µW average incident on the detector.

#### E. INPUT AND OUTPUT POWER REQUIREMENTS FOR LASERS

With a brief analysis of the optical system from laser to photodetector, a reasonable estimate of the output power of the laser can be made. This is done using the following equation,

$$P_o = 2\alpha_{coupler} + \alpha_{modulator} + \alpha_{fiber} + P_{receiver}$$

(1)

where  $P_o$  is the output power of the laser in units of dBm. From the previously established values for optical losses and receiver sensitivity, the resulting output power of the laser is then -24.5 dBm or 3.6  $\mu$ W continuous power in the waveguide. A reasonable buffer to ensure low bit-error-rate is at least 2 dB, so that the target power should be closer to 6  $\mu$ W.

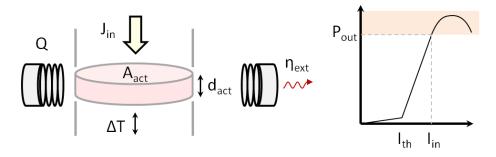

**Fig. 2.** The general design or "black box" laser. The important parameters are only the active area, cavity Q, confinement factor, and waveguide coupling efficiency. Relationships between these values are found by assuming a maximum input power and minimum output power.

The input power can be determined entirely by the target energy consumption of the system and the fraction required by the modulator. The continuous input power can be determined by using the following equation,

$$P_{in} = \left(E_{target} - E_{modulator}\right) \times B_{modulator} \tag{2}$$

where Emodulator and Bmodulator are the energy consumption (fJ/bit) and bit rate (Gb/s) of the modulator. Using the values for the state-of-the-art silicon microring modulators described above, the input power of the laser is 75  $\mu$ W.

#### 1.3 GENERAL DESIGN REQUIREMENTS OF THE LASER

With the input and output power requirements established, it is important to then find the required properties of a laser of arbitrary geometry in order to evaluate the different candidate designs. Most generally, the output power can be related to the input power by a number of measures: (i) current area  $A_{act}$ , (ii) cavity Q, (iii) confinement factor  $\Gamma$ , and (iv) waveguide coupling efficiency  $\eta$ . These parameters for a "black box" laser are shown in Figure 2.

#### A. INPUT CURRENT AND WAVEGUIDE COUPLING

The first task is to find the maximum input current Iin from the input power. This is most simply done by using the Shockley equation for a diode to find the current for a given input power,

$$P_{in} = I_{in} \frac{nkT}{q} ln \left( \frac{I_{in}}{A_{act} I_0} + 1 \right) \tag{3}$$

where n is the ideality factor and  $I_0$  is the saturation current. While the range of materials used in near-infrared extends from GaAs to InP, an ideality factor of n = 1.5 and saturation current of  $J_0 = 2.2 \times 10^{-9}$  A/cm2 can be expected. The resulting maximum input current is then ~60  $\mu$ A.

With the maximum input current clearly defined, the threshold current and external coupling efficiency of the laser can be related by assuming the laser will operate well above threshold. In this case, the output power of the laser is given by

$$P_o = \eta_{ext} (I_{in} - I_{th}) \frac{hv}{a} \tag{4}$$

where  $\eta_{ext}$  and  $I_{th}$  are the external coupling efficiency and threshold current. The coupling efficiency  $\eta_{ext}$  is the product of internal quantum efficiency  $\eta_{int}$  and waveguide coupling efficiency  $\eta_{wg}$ , denoted as

$$\eta_{ext} = \eta_{int} \times \eta_{WG} \tag{5}$$

The waveguide coupling efficiency affects the total cavity Q by

$$Q_{tot} = \left(\frac{\eta_{WG}}{1 + \eta_{WG}}\right) Q_{WG} \tag{6}$$

where  $Q_{wg}$  is the fraction of the cavity Q coupled to the waveguide. The actual values of  $Q_{wg}$  and  $\eta_{wg}$  will need to be determined for each candidate design.

#### B. CAVITY Q, ACTIVE AREA, AND MODAL CONFINEMENT FACTOR

The cavity Q, active area Aact, and confinement factor  $\Gamma$  will be the three most important parameters in the laser design, as they are related to the threshold gain by

$$g_{th} = \frac{2\pi n_{g,a}}{\lambda} \cdot \frac{1}{Q \cdot \Gamma} \tag{7}$$

where ng,a is the group refractive index of the gain material and  $\lambda$  is the lasing wavelength<sup>17</sup>. The current density can also be related to the gain in the active material by

$$g = g_0 \ln \left( \frac{N + N_s}{N_{tr} + N_s} \right) \tag{8}$$

where  $N_s$  and  $N_{tr}$  are the saturation current density and transparency current density. For InGaAs compounds emitting in the wavelength range of interest,  $N_s = 5 \times 10^{18}$  cm<sup>-3</sup> and  $N_{tr} = 1.1 \times 10^{18}$  cm<sup>-3</sup>, while  $g_0 = 3000$  cm<sup>-1</sup>. Combining these equations then leads to an expression for the threshold current

$$I_{th} = A_{act} \frac{d_{act}}{\tau_{eff}} \left[ (N_{tr} + N_s) exp \left( \frac{2\pi n_{g,a}}{\lambda} \cdot \frac{1}{g_0 \cdot Q \cdot \Gamma} \right) - N_s \right]$$

(9)

This equation can then be combined with the power output of the laser in order to show the relationship between Q,  $\Gamma$ , and Aact to achieve the desired output power given a maximum input current. This expression is given by

$$A_{act} = \frac{I_{in} - \frac{q}{hv} \cdot \frac{P_O}{\eta_{ext}}}{(N_{tr} + N_s)exp(\frac{2\pi ng_A a}{\lambda} \cdot \frac{1}{g_0 \cdot Q \cdot \Gamma}) - N_s}$$

(10)

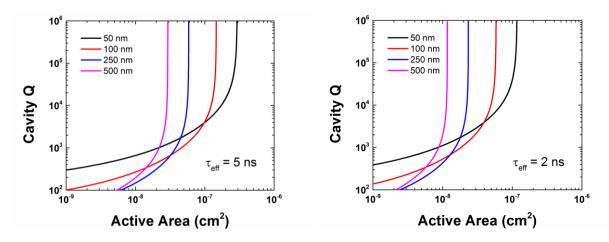

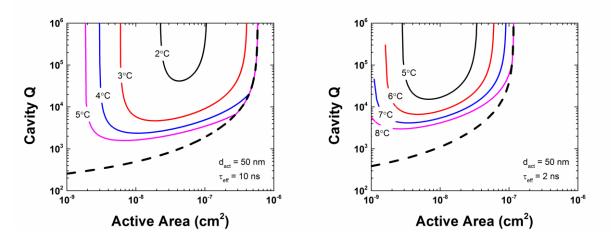

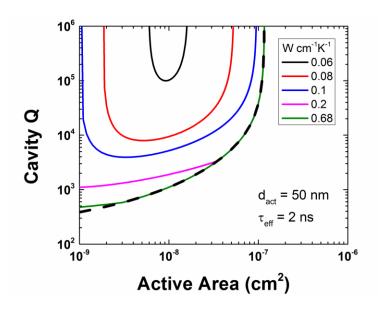

**Fig. 3.** Plot of active area vs. cavity Q for several confinement factors. Reducing the active area for the fixed input current value produces a higher gain coefficient and results in a lower Q value necessary for the required threshold. Thermal issues will arise at smaller active areas due to the extremely high current density.

From this equation we can find the necessary Q value for a given active area  $A_{act}$  and confinement factor  $\Gamma$ .

Figure 3 shows a plot of multiple  $Q(A_{act})$  curves for different values of  $d_{act}$ . This shows a distinct relationship between the cavity Q and active area to reach 6  $\mu W$  output with only 60  $\mu A$  input. For smaller active areas, a lower Q value is necessary to reduce the threshold current while for larger areas a higher Q is necessary due to the low material gain. Without any other considerations, this would indicate that an extremely small active area device can still function even with a very low Q value. However, the current density through such a small active area would be unreasonably high, likely causing the device to fail. In order to place a lower limit on the active area, the thermal impedance of the device must be considered.

#### C. THERMAL IMPEDANCE AND EFFICIENCY RESTRICTIONS

The low Q value as a result of the previous calculation seems unreasonable at first. However, when dealing with a small current aperture such as this, the overall wall plug

efficiency must be taken into consideration. The curve in Figure 3 represents the minimum Q and  $A_{act}$  to get 6  $\mu W$  output for 75  $\mu W$  input. This means the ~69  $\mu W$  of the input power is dissipated as heat. If the active area is represented as a disk, the radius would be 0.9  $\mu M$  with a power density of 2.7  $k M/cm^2$ . To estimate the temperature change due to power dissipation, we can use the equation

$$\Delta T = P_D Z_T \tag{11}$$

where  $P_D$  is the dissipated power and  $Z_T$  is the thermal impedance. The expression for thermal impedance of a disk source on a large substrate is given by

$$Z_T = \frac{1}{2\varepsilon r} \tag{12}$$

where  $\varepsilon$  is the thermal conductivity of the substrate and r is the radius of the disk. For the thermal conductivity of the substrate, we must use the value for SiO2 of 0.014 Wcm<sup>-1</sup>K<sup>-1</sup>, since the laser will be on a silicon-on-insulator substrate. The resulting increase in temperature for this example is then  $\Delta T = 13^{\circ}C$ . While seemingly small, this rise in temperature will greatly reduce the output power much below the required output. For consistent performance, the laser should have a temperature rise of less than 1°C due to dissipated power.

Setting a constant temperature difference places further restriction on the relationship between input and output power. For the case of the disk source on a large substrate, he expression for thermally dissipated power as a function of active area is

$$P_D = P_{in} - P_o = 4\varepsilon\Delta T \sqrt{\frac{A_{act}}{\pi}}$$

(13)

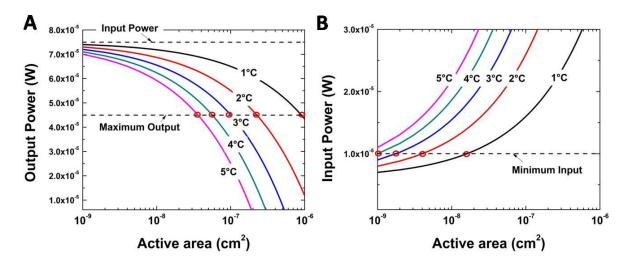

The consequence of this expression can be viewed in two ways: either the input power has to be significantly reduced but still achieve the same output, or the output power has to be significantly increased for the given input. Figure 4 shows a comparison of restricting the input and the output power for different allowed temperature differences. In Figure 4(a), the input power is held constant. As the active area decreases, the laser output must be increased in order to maintain the same temperature difference. In Figure 4(b), the output power is held constant, and as the active area is decreased the input power must also be decreased in order to maintain the same temperature difference.

The result of this is that the active area can only be made smaller if the efficiency of the laser is improved. Depending on the temperature restriction, the necessary cavity Q to reduce threshold will increase asymptotically as either the input power approaches the theoretical minimum or the output power approaches the theoretical maximum. A revised

**Fig. 4.** Comparison of thermal limitations on the laser design. (A) The case where the input power is constant and the laser efficiency is improved to reduce temperature increase. The theoretical maximum output power is shown for the laser, where the intersections (red circles) show the minimum area that can be used. (B) The case where the output power is constant while the efficiency is increased to reduce the necessary input power. The theoretical minimum input power is shown where the allowed area is significantly smaller than in (A).

**Fig. 5.** Plot of cavity Q vs. active area with the thermal budget taken into consideration. In order to maintain a certain temperature, the cavity Q rises asymptotically below a particular active area to compensate with increased efficiency. For a given temperature value, there is a minimum active area where even a threshold-less laser does not have the required efficiency.

plot of Q vs. A<sub>act</sub> for various temperatures is shown in Figure 5 to illustrate this behavior. Realistically, the target temperature increase should be in the 1-2°C range. For any given thermal budget, a minimum cavity Q can be found as a function of area. As high-Q cavities are difficult to fabricate repeatedly in many designs, this value for A<sub>act</sub> should be used.

Several additional facts must be considered in a more thorough analysis than what is presented here. The optical system analysis used to determine the minimum output power in the previous section will need to be extended for specifics of the actual optoelectronic transceiver such as waveguide losses on chip and additional components (optical isolators, multiplexors, demultiplexors, etc.). Raising the minimum output of the laser will shift the optimal active area to larger values accordingly. Finally, this analysis assumes a waveguide coupling efficiency of 90%. This means that the minimum Q value for the laser design must be the total Q with at least 90% coupling efficiency. In other words, the uncoupled cavity Q must be at least  $10 \times \text{larger}$ .

#### 1.4 MICRO-RING AND PHOTONIC CRYSTAL RESONATORS

Currently, the best performing lasers on silicon are microdisk <sup>18</sup> and microring <sup>19</sup> resonators. This laser design is used for many of the reasons established above: high-Q, small footprint, and high waveguide coupling efficiency. However, the circular design is limited by bend losses in the ring waveguide, and as a result the maximum Q value of the resonator is scaled down with the active area. Even at the lower limit for waveguide width of 0.5 µm, the microring cavity does not have a sufficient Q value to operate. Overcoming the thermal limitation to the device design could push microring lasers closer to the target region. This has motivated development in silicon-on-diamond wafers, but this work is still in the early stages and may prove too costly for manufacture.

#### 1.5 CONCLUSIONS

With a relatively simple analysis, general requirements for lasers to be used in next generation optical interconnects have been established in terms of basic laser cavity properties. It is found that in order to reach the famed 10 fJ/bit mark, the power dissipation is the key limitation in lasers on this size scale. Therefore, lasers meeting these design requirements must have a sufficiently small area and high cavity Q. The current state-of-the-art microring lasers do not appear to meet these requirements due to fundamental limitation on cavity Q vs. active area for microrings. Since the requirements are so stringent for lasers operating at these power levels, it is evident that a new type of photodetector will be needed to continue scaling past the 10 fJ/bit mark. In any case, it is likely that in 20 years, optical interconnects will face a crisis similar to the scaling of silicon CMOS transistors in that lasers will not be able to be made smaller and still function.

An additional aspect that should be considered is illustrated in Figure 6. For the silicon photonics platform, much of the restriction on the laser design is due to the thermally insulating buried oxide layer. In this case, we can take the same parameters used in Figure 5(a) and change the thermal conductivity of the substrate while considering a junction temperature rise of 1°C. The most important outcome of this calculation is that for a substrate thermal conductivity of 0.68 Wcm<sup>-1</sup>K<sup>-1</sup>(equivalent to bulk InP), the necessary cavity Q is nearly identical to the case of Figure 3, where power dissipation was neglected. This can be interpreted in two ways: either fJ/bit transceivers should be made on InP rather than SOI, or a highly effective metal heat sink process must be developed for silicon photonics so that the power can be directed to the silicon substrate underneath the buried oxide layer.

**Fig. 6.** Comparison of different substrate thermal conductivities shows that the  $SiO_2$  layer in the SOI substrate is the main limitation of the laser design. Improved thermal conductivity greatly reduces the necessary cavity Q to reach the required output power. In the case of an InP substrate, the cavity Q is nearly equivalent to the model with no thermal restrictions.

#### **REFERENCES:**

- 1. Ibm, Y. V. Silicon photonics for next generation computing systems. (2008).

- 2. Okyay, A. K. *et al.* Silicon Germanium CMOS Optoelectronic Switching Device : Bringing Light to Latch. **54**, 3252–3259 (2007).

- 3. Vivien, L. *et al.* High speed and high responsivity germanium photodetector integrated in a Silicon-On-Insulator microwaveguide. *Opt. Express* **15**, 9843–8 (2007).

- 4. Kang, Y. *et al.* Monolithic germanium / silicon avalanche photodiodes with 340 GHz gain bandwidth product. **3,** 59–63 (2009).

- 5. Assefa, S., Xia, F. & Vlasov, Y. a. Reinventing germanium avalanche photodetector for nanophotonic on-chip optical interconnects. *Nature* **464**, 80–4 (2010).

- 6. Fang, A. W. *et al.* Electrically pumped hybrid AlGaInAs-silicon evanescent laser. *Opt. Express* **14**, 9203–10 (2006).

- 7. Fang, A. W., Lively, E., Kuo, Y.-H., Liang, D. & Bowers, J. E. A distributed feedback silicon evanescent laser. *Opt. Express* **16**, 4413–9 (2008).

- 8. Miller, D. a B. Optical interconnects to electronic chips. *Appl. Opt.* **49**, F59–70 (2010).

- 9. Miller, D. Device Requirements for Optical Interconnects to Silicon Chips. *Proc. IEEE* **97,** 1166–1185 (2009).

- 10. Chen, L., Preston, K., Manipatruni, S. & Lipson, M. Integrated GHz silicon photonic interconnect with micrometer-scale modulators and detectors. *Opt. Express* **17**, 15248–56 (2009).

- 11. Manipatruni, S., Xu, Q., Schmidt, B., Shakya, J. & Lipson, M. High Speed Carrier Injection 18 Gb/s Silicon Micro-ring Electro-optic Modulator. *LEOS* 2007 *IEEE Lasers Electro-Optics Soc. Annu. Meet. Conf. Proc.* 537–538 (2007). doi:10.1109/LEOS.2007.4382517

- 12. Li, G. *et al.* 25Gb/s 1V-driving CMOS ring modulator with integrated thermal tuning. *Opt. Express* **19**, 20435–43 (2011).

- 13. Gunn, C. CMOS P HOTONICS FOR H IGH -S PEED I NTERCONNECTS BETWEEN SILICON DIE ARE POSSIBLE AT A PRICE PERFORMANCE POINT. 58–66 (2006).

- 14. Wang, Q., Loh, T.-H., Ng, D. K. T. & Ho, S.-T. Design and Analysis of Optical Coupling Between Silicon Nanophotonic Waveguide and Standard Single-Mode Fiber Using an

- Integrated Asymmetric Super-GRIN Lens. *IEEE J. Sel. Top. Quantum Electron.* **17,** 581–589 (2011).

- 15. Benner, a. F., Ignatowski, M., Kash, J. a., Kuchta, D. M. & Ritter, M. B. Exploitation of optical interconnects in future server architectures. *IBM J. Res. Dev.* **49**, 755–775 (2005).

- 16. Michel, J., Liu, J. & Kimerling, L. C. High-performance Ge-on-Si photodetectors. *Nat. Photonics* **4**, 527–534 (2010).

- 17. Kim, S.-H., Huang, J. & Scherer, A. From vertical-cavities to hybrid metal/photonic-crystal nanocavities: towards high-efficiency nanolasers. *J. Opt. Soc. Am. B* **29**, 577 (2012).

- 18. Van Campenhout, J. *et al.* Electrically pumped InP-based microdisk lasers integrated with a nanophotonic silicon-on-insulator waveguide circuit. *Opt. Express* **15**, 6744–9 (2007).

- 19. Liang, D. *et al.* Electrically-pumped compact hybrid silicon microring lasers for optical interconnects. *Opt. Express* **17**, 20355–64 (2009).

## Chapter 2

#### 2.1 SELECTIVE-AREA GROWTH OF III-V NANOPILLARS

The selective-area growth of III-V nanopillars has been studied by several groups around the world over the last decade<sup>1,2</sup>. It is notably different than other forms of III-V nanowire synthesis in that there is no metal catalyst to assist in the growth. Instead, the growth is confined to nanoscale openings patterned in a dielectric mask which prevents growth elsewhere on the substrate surface. This approach has unique advantages and challenges: (1) The nanopillars are grown without a catalyst, and therefore cannot suffer from metal contamination, (2) The nanopillar position and diameter is well defined by the lithography used to pattern the nanoholes, (3) Control over axial and radial crystal growth can be accomplished, but only for certain materials and specific growth conditions.

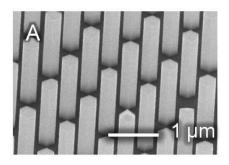

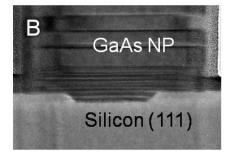

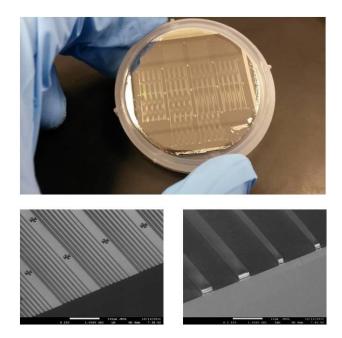

The fact that the nanopillar position and diameter can be accurately controlled by the lithography process is the key enabler of much of the work in this thesis. The impact of the nanopillars' periodic structure on optical properties will be explored in later chapters. However, the most important aspect of the selective-area growth is the greatly relaxed lattice matching requirements of different materials used to form heterostructures <sup>3,4</sup>. The use of selective-area growth at nanoscale dimensions (<100 nm) avoids defect formation due to lattice mismatch by allowing strain relief in the lateral direction. By this method, highly uniform arrays of III-V nanopillars can be successfully grown on Si (111) substrates <sup>5-8</sup>. An example of this growth is shown in Figure 1.

Initially, development of III-V NPs grown on Si focused on the nanoscale lithographic patterning of nanohole arrays to serve as a growth template. For this purpose, LPCVD silicon nitride films 20 nm in thickness were used as the growth mask in order to

**Figure 1.** (a) Tilted SEM of GaAs NP array grown on Si. (b) Cross-section TEM of the GaAs/Si interface showing dislocation-free growth.

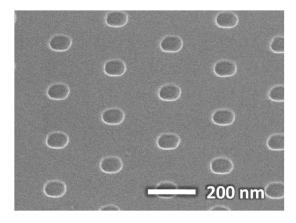

provide a high etch selectivity over silicon dioxide during the native oxide removal prior to growth. The nanohole arrays were patterned by electron-beam lithography and reactive-ion etching as shown in Figure 2.

The growth of GaAs was demonstrated by using a two-temperature growth process. The initial GaAs layer was grown at a low temperature of 400°C in order to form a stable GaAs (111)B surface. This low temperature growth was chosen both to prevent anti-phase domain formation at the interface, but also in order to facilitate development of nanopillar growth and devices by creating an identical growth surface to GaAs (111)B substrates. Following the formation of the low temperature GaAs seeding layer, the nanopillar growth

**Figure 2.** Nanohole array etched into the silicon nitride growth mask on Si(111).

is carried out at 700°C, identical to the growth conditions on GaAs substrates. This resulted in the growth of highly uniform GaAs nanopillar arrays on Si (111) substrates.

The ability to grow nanopillar arrays under nearly identical conditions on both Si(111) and GaAs (111)B substrates is the primary motivation for the development of nanopillar based emitters as the nanopillar growth could be studied more rapidly by growth on GaAs substrates, followed by porting of the growth conditions to the Si substrates.

#### 2.2 In-Situ Passivation of Nanopillars

While nanopillars are a promising route to achieving high-efficiency emitters on Si, the current limitation of all nanopillar opto-electronic devices is the quality, or effectiveness, of the surface passivation. Previous studies of surface passivation of III-V materials are almost entirely limited to chemical passivation by Ammonium Sulfide or similar Sulfur containing compounds<sup>9,10</sup>. The majority of the work in this thesis is based on InGaP shells lattice matched to GaAs for *in-situ* surface passivation<sup>11–13</sup>. However, small changes in interrupt time between switching of As and P precursors produced considerable variation in device performance. This observation indicates that the primary limitation of the InGaP passivation is the interface between Ga(In)As and InGaP, as luminescence intensity and diode characteristics are nearly independent of the InGaP shell thickness.

A possible reason for the interface sensitivity to the As and P precursor switching is the fact that InGaAsP compounds formed between GaAs and InGaP can potentially lead to non-radiative recombination. This effect has been documented widely in studies of crystal growth related to Heterojunction Bipolar Transistors (HBTs) based on InGaP/GaAs. Since the necessary thickness of the passivation shell is on the order of 5 - 10 nm, the lattice

matching of the shell material to the core is not highly restricted as it is for planar devices. Therefore, the InGaP shell can be replaced with a GaP shell that is only slightly tensile strained. The advantage of the GaP shell compared to the InGaP shell is that all compositions of GaAsP have a higher band-gap than GaAs, potentially reducing the sensitivity to the As and P precursor switching.

Initial studies of GaP shells have shown that an optimized growth condition of GaP is able to produce a 15x improvement in PL intentsity relative to the best known InGaP passivation. Even with this marked improvement in luminescence intensity, the GaP passivated NPs still show signs of interface limitation. Most notable, is the degradation of luminescence intensity over several hours of excitation at medium pump powers, and rapid degradation at high pump powers.

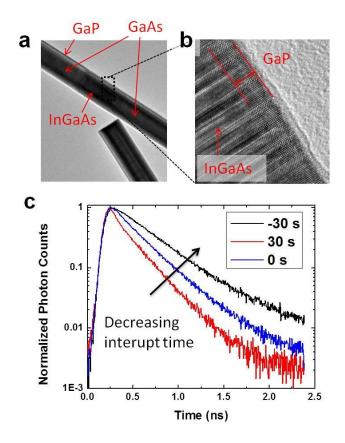

In order to better understand these limitations, knowledge of the carrier lifetime is necessary. To accomplish this, a customized time-resolved micro-photoluminescence setup was constructed based on time-correlated single photon counting (TCSPC) module with a Si avalanche photodiode (APD) and photomultiplier tube (PMT) for sub-nanosecond time resolution from 350 - 1700 nm. Initial TRPL measurements of InGaP and GaP passivated NPs fell below the system resolution of ~100 ps. Changes in interrupt time shown in Figure 3 showed that intermixing between As and P at the interface between GaAs and GaP could dramatically improve the lifetime up to ~0.5 ns.

**Figure 3.** (a) TEM image showing the Ga(In)As NPs with GaP shells. (b) Magnified TEM image of the InGaAs/GaP interface. (c) TRPL measurements of the carrier lifetime with varying interrupt times between As and P precursor flows.

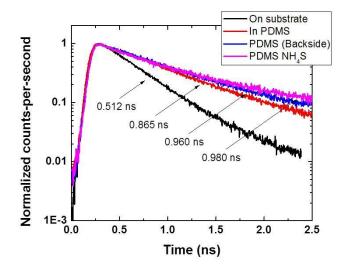

While the changes in interrupt time yielded a substantial improvement in lifetime, the measured lifetimes are still below values typical of planar films by up to an order of magnitude. Therefore, a study of the possible mechanisms of the non-radiative recombination limiting the lifetime has revealed that one of the major limitations of the carrier lifetime is the substrate, as shown in Figure 4. Here, TRPL measurements compared the carrier lifetime under different conditions: on-substrate, in PDMS, in PDMS under back illumination, and in PDMS under back illumination and with Ammonium Sulfide passivation of the exposed GaAs surface from the PDMS peel-off process. The fact that the lifetime is highest in the case of the PDMS back-side illumination with sulfide passivation indicates that the substrate quality is one of the major limitations in carrier lifetime.

**Figure 4.** TRPL measurements of GaP passivated GaAs NPs under different conditions: onsubstrate, in PDMS, in PDMS under back illumination, and in PDMS under back illumination and with Ammonium Sulfide passivation of the exposed GaAs surface from the PDMS peel-off process.

However, even under these ideal conditions, the carrier lifetime is still substantially lower than bulk GaAs and InGaAs.

As an alternative to III-P passivation, purely III-As passivation was explored to

**Figure 5.** TRPL measurements of the optimized GaP passivation in comparison to the optimized AlGaAs passivation.

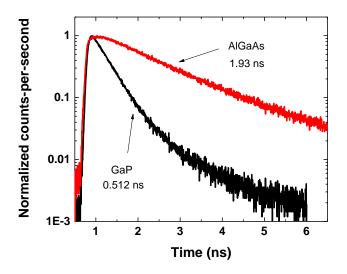

potentially reduce interfacial recombination. For this purpose, alloys of AlGaAs are ideal, as they have a significantly wider bandgap than GaAs and are lattice matched for any Al composition. Similar to the development of InGaP and GaP passivation, the AlGaAs passivation was studied initially by PL intensity measurements in order to establish the optimum growth temperature and Al/Ga ratio. This concluded with the ideal growth temperature being between 580 - 600°C and an Al/Ga ratio of 1:1.

A comparison between the optimized GaP passivation and AlGaAs passivation is shown in Figure 5. While the longest carrier lifetime of the GaP passivation was only ~0.5 ns, the optimum AlGaAs passivation has a lifetime of ~2 ns. With a lifetime of ~2 ns, the NPs can be considered a suitable material for lasers in the fJ/bit regime as shown in Chapter 1.

#### **REFERENCES:**

- 1. Goto, H. *et al.* Growth of Core—Shell InP Nanowires for Photovoltaic Application by Selective-Area Metal Organic Vapor Phase Epitaxy. *Appl. Phys. Express* **2**, 035004 (2009).

- 2. Noborisaka, J., Motohisa, J. & Fukui, T. Catalyst-free growth of GaAs nanowires by selective-area metalorganic vapor-phase epitaxy. *Appl. Phys. Lett.* **86**, 213102 (2005).

- 3. Glas, F. Critical dimensions for the plastic relaxation of strained axial heterostructures in free-standing nanowires. *Phys. Rev. B* **74**, 121302 (2006).

- 4. Ye, H. *et al.* Critical thickness and radius for axial heterostructure nanowires using finite-element method. *Nano Lett.* **9,** 1921–5 (2009).

- 5. Tomioka, K., Motohisa, J., Hara, S. & Fukui, T. Control of InAs nanowire growth directions on Si. *Nano Lett.* **8,** 3475–80 (2008).

- 6. Tanaka, T. *et al.* Vertical Surrounding Gate Transistors Using Single InAs Nanowires Grown on Si Substrates. *Appl. Phys. Express* **3**, 025003 (2010).

- 7. Tomioka, K., Tanaka, T., Hara, S., Hiruma, K. & Fukui, T. III–V Nanowires on Si Substrate: Selective-Area Growth and Device Applications. *IEEE J. Sel. Top. Quantum Electron.* **17**, 1112–1129 (2011).

- 8. Tomioka, K., Motohisa, J., Hara, S., Hiruma, K. & Fukui, T. GaAs/AlGaAs core multishell nanowire-based light-emitting diodes on Si. *Nano Lett.* **10**, 1639–44 (2010).

- 9. Senanayake, P. *et al.* Photoconductive gain in patterned nanopillar photodetector arrays. *Appl. Phys. Lett.* **97,** 203108 (2010).

- 10. Shapiro, J. N. *et al.* InGaAs heterostructure formation in catalyst-free GaAs nanopillars by selective-area metal-organic vapor phase epitaxy. *Appl. Phys. Lett.* **97**, 243102 (2010).

- 11. Lin, A. *et al.* Extracting transport parameters in GaAs nanopillars grown by selective-area epitaxy. *Nanotechnology* **23**, 105701 (2012).

- 12. Senanayake, P. *et al.* Thin 3D multiplication regions in plasmonically enhanced nanopillar avalanche detectors. *Nano Lett.* **12**, 6448–52 (2012).

- 13. Senanayake, P. *et al.* 3D nanopillar optical antenna photodetectors. *Opt. Express* **20**, 25489–96 (2012).

# Chapter 3

#### 3.1 OPTICAL RESONATORS FOR NANOWIRES

NW based lasers pose a unique challenge over other optoelectronic components because they require a carefully designed and fabricated resonant optical cavity. Several different approaches have been taken to form cavities for NW lasers, including plasmonic waveguides<sup>1</sup>, Fabry-Perot resonators<sup>2</sup>, microring racetrack resonators<sup>3</sup>, and top-down etched photonic crystal cavities<sup>4,5</sup>. However, these devices were fabricated by mechanical removal of the NWs from the growth substrate and random placement on a host substrate<sup>5,6</sup>. Alignment of subsequent process steps was done to each NW individually. Currently there is no feasible manufacturing method to place the NWs on the host substrate with the necessary precision to fabricate these devices at the wafer scale.

An alternative approach to integration of NWs and NPs with PICs is lithographic control of the growth position and diameter. This allows for photonic crystal (PC) waveguides, resonant cavities, and active gain regions to be formed entirely by NPs grown simultaneously. These PC devices correspond to the dielectric rods in air structure, which differs from the more conventional air holes in a dielectric slab structure in that the photonic band gap occurs for TM polarization rather than TE polarization. PC waveguides of this type with no active gain have been reported previously using vapor-liquid-solid (VLS) grown NWs patterned by nanoimprint lithography<sup>7</sup>. However, this method suffers from limited variability in the NW diameter due to the Au catalyst particle size, the tapered profile of the NWs, and defect growth between the NWs that will result in optical losses. These problems can be avoided by growth of NPs via catalyst-free selective-area epitaxy (SAE). Furthermore, the SAE patterns include optical alignment marks for device integration.

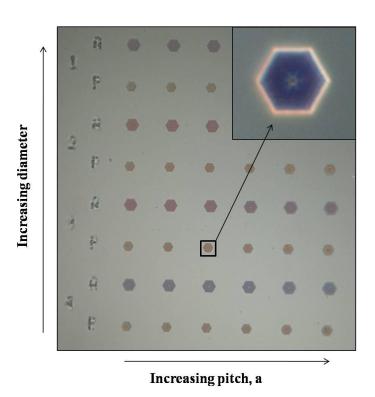

## 3.2 BOTTOM-UP PHOTONIC CRYSTALS

In this work, we exploit the ability to design device parameters with SAE to enable 2-D photonic crystal devices. Control of both NP pitch and diameter allow for the photonic band-gap (PBG) region and defect cavity active region to be comprised entirely of III-V NPs grown simultaneously. The SAE grown NPs offer a unique advantage due to their hexagonal cross-sections with side-wall facets consisting of the {1-10} family of crystal planes<sup>8</sup>. These side-walls are completely vertical and have atomic scale roughness<sup>9-11</sup>, avoiding two of the largest contributors to cavity losses in top-down fabricated photonic crystals<sup>12,13</sup>. The growth of pure axial GaAs/InGaAs/GaAs heterostructures allows for the appropriate placement of gain material within the cavities at the anti-nodes of the electric field<sup>14,15</sup>. Furthermore, the ability to grow lattice matched InGaP shells over the NPs provides effective *in-situ* surface passivation to prevent non-radiative recombination and surface pinning that is detrimental to device performance<sup>16,17</sup>.

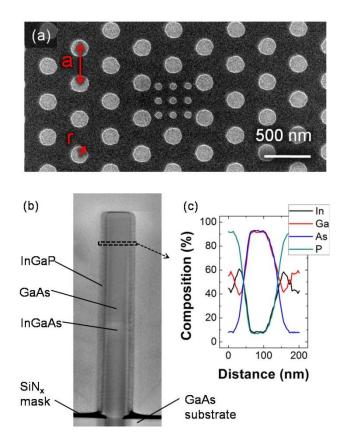

These PC cavities consist of a PBG region and an active gain region. Figure 1(a) shows a scanning electron microscope (SEM) image of the etched growth mask for a single defect cavity to illustrate the NP arrangement. The growth mask consists of a 20 nm thick  $SiN_x$  film formed by plasma-enhanced chemical vapor deposition that is subsequently patterned by electron-beam lithography (EBL) and reactive ion etching (RIE). Line edge roughness typical of EBL and RIE patterns is visible in the SEM, however, this roughness does not translate into the NP sidewall. For the PBG region, the NPs are arranged in a triangular lattice with a constant radius to pitch ratio (r/a) of 0.2. This ratio is chosen to ensure a wide TM like band-gap exhibited by the dielectric rods in air structure. For all of the active regions, NPs with a 65 nm diameter and 175 nm pitch are arranged in a square lattice fill the defect cavities. This particular arrangement of

**Figure 1.** (a) Top-down SEM of the etched growth mask of an L1 cavity. (b) Cross-section HRTEM of a NP showing the GaAs/InGaAs axial core structure and InGaP shell. (c) Radial EDS scan with composition of In, Ga, As, and P.

NPs in the active regions is chosen due to its high concentration factor for TM polarization at the peak emission wavelength. The resulting fill factor (FF) of this configuration is 0.433, while that of the PBG region is 0.145.

To study the effects of the PBG on the emission spectrum, an array of devices is formed with varying pitch ranging from 264 - 534 nm in increments of 12 nm for a total of 20 columns. The first row in each column is a device with no defect cavity for reference. The second and third rows of each column are devices with single (L1) or triple defect (L3) cavities in the center. Each device is referred as x-y, where x is the column number in order of smallest to largest pitch and y is the row number. Based on the standard 2-D model of infinitely tall dielectric rods in a triangular lattice, the PBGs of the devices should range from 0.8 to 1.6  $\mu$ m. To reduce the

perturbation to the 2-D approximation used to estimate the band-gap wavelength ranges, the pillars were grown at least 800 nm tall to be sufficiently greater than the half-wavelength of the emission peak.

The NPs used to form the PC cavities are grown with axial InGaAs heterostructures followed by *in-situ* passivation with InGaP shells to prevent non-radiative surface recombination. Figure 1(b) shows a high-resolution transmission electron microscopy (HRTEM) image of the NP cross-section where the contrast between the GaAs, InGaAs, and InGaP portions can be seen. These NPs are grown by low-pressure vertical flow metal-organic chemical vapor deposition on patterned GaAs (111)B substrates. The NP growth is separated into two steps. First, the axial GaAs/InGaAs/GaAs double heterostructure is grown at a temperature of 735°C under an ambient hydrogen pressure of 60 Torr using trimethyl-gallium (TMGa), trimethyl-indium (TMIn), and tertiary-butyl-arsine (TBA) as precursors. The InGaAs section is grown at approximately the mid-length of the NP with a calculated gas phase concentration of 30% Indium. A more detailed description of the growth and masking is reported elsewhere<sup>12</sup>. The resulting Indium concentration in the solid is calculated to be 14.5% from the peak emission wavelength of 970 nm. Once the axial core structure is grown, the temperature is reduced to 575°C under an arsenic overpressure. Following a hydrogen purge and tertiary-butyl-phosphorous (TBP) preflow optimized to reduce As/P intermixing, an ~8-10 nm thick InGaP shell lattice matched to GaAs is grown. Figure 1(c) shows an energy dispersive x-ray spectroscopy (EDS) scan in the radial direction of the NP used to verify the composition of the GaAs core and InGaP shell.

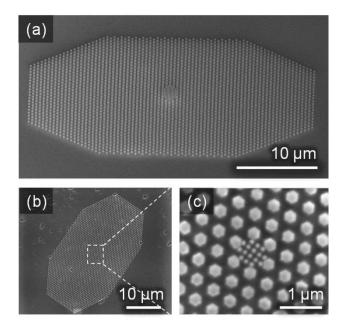

Figure 2(a) shows an SEM image of a full device after growth demonstrating the high uniformity of the NP arrays. While these PC cavities provide in-plane optical confinement, the lower effective index of refraction in the active region ( $n_{eff} \sim 2.0$ ) results in optical loss into the

**Figure 2.** (a) 45° tilted SEM of a NP photonic crystal cavity. (b) Low vacuum SEM of NP PC cavity embedded in PDMS. (c) High magnification image of the single-defect cavity from the device in (b).

substrate ( $n_{GaAs} = 3.3$ ). Due to the reduced pitch and diameter, the NPs within the cavity are as much as 20% taller than those forming the PBG. To form cavities with out-of-plane optical confinement, the NP PCs are encapsulated in polydimethylsiloxane (PDMS) and removed from the patterned substrate mechanically by shearing at the NP/substrate interface. Figure 2(b) shows a top-down image of a PC embedded in PDMS after lift-off taken by a low-vacuum SEM. In Figure 2(c), a high-magnification SEM shows the L1 defect cavity region of the device in 2(b). By performing a lift-off of the NPs in PDMS, the refractive index above the cavity is then n = 1.0 for air and n = 1.47 below the cavity for PDMS.

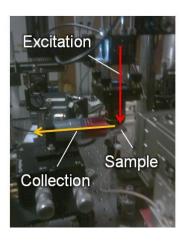

### 3.3 OPTICAL CHARACTERIZATION OF NANOPILLAR PHCS

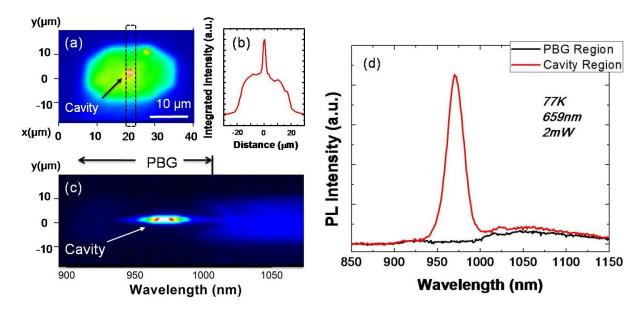

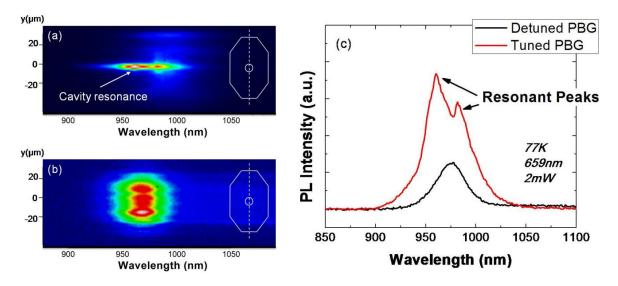

Prior to the PDMS lift-off, the PC cavities are characterized on the substrate. The samples are characterized at both 300K (data not shown) and 77K using a liquid-nitrogen cooled InGaAs focal plane array with a 50x objective lens oriented normal to the substrate. A 659 nm continuous wave diode laser operating at 2 mW output power is used as the excitation source

**Figure 3.** (a) Spectrally integrated image of a PC where the PBG exists in the emission range of the device. (b) Line scan of integrated intensity along the center axis of the device shown in (a). (c) Spectrally resolved image of the PC in (a) taken along the center axis of the device as illustrated by the outlined box in (a). (d) Comparison of PL spectra taken on the cavity region and on the PBG region of the device.

with a 75° angle of incidence to the substrate normal and a spot size of ~100  $\mu$ m in diameter. At 300K, the full-width half-maximum (FWHM) of the cavity emission is greater than 50 nm and not well separated from the emission outside the PBG. Figure 3(a) shows a spectrally integrated image of device 17-3 at 77K, which exhibits a PBG from 800 to 1000 nm spanning the range of emission. In Figure 3(b) a line-scan of the integrated image shows that the PL intensity of the cavity region located in the center of the device is increased by a factor of 2 relative to the PBG region. Figure 3(c) shows the spectrally resolved PL taken along the center axis of the device. At the edge of the device (y = 10  $\mu$ m), the cut-off wavelength of the PBG appears to be at 1  $\mu$ m, where only the "tail" of the InGaAs emission can be observed. Closer to the center of the device (y = 0  $\mu$ m), the PBG cut-off shifts to 1025 nm due to the increase in NP height. Only at the center of the device, where the cavity is located, can the InGaAs emission peak ( $\lambda$ ~970 nm) be observed. To exemplify this, Figure 3(d) shows a comparison of the spectra taken on the cavity

**Figure 4.** (a) Spectrally resolved image along the center axis of a PC where the PBG in not in the emission range. The inset diagram shows the orientation of the device with the dotted line showing the axis along which the emission is resolved. (b) PL spectra of the PC in (a) comparing the cavity and PBG regions of the device.

region and at the midpoint between the cavity and the edge of the device. The spectrum taken at the midpoint does not exhibit the emission peak at 970 nm above the noise floor of the detector. This provides clear evidence of a PBG inhibiting the InGaAs band-edge transition in agreement with previous optical characterization of top-down PC cavities<sup>18</sup>.

To further demonstrate that the suppression of the 970 nm emission is due to a PBG and not the NP growth itself, a device on the same sample with identical configuration but different lattice constant in the PBG region is characterized for comparison. Figure 4(a) shows the spectrally resolved PL along the center axis of device 5-3. In this case, the 970 nm emission peak

is observable across the entire device. This is exemplified in Figure 4(b), where spectra taken on the cavity region and at the midpoint between the cavity and edge are compared. Only an increase in intensity is observed from the cavity region relative to the PBG region. Since this is observed in both devices, it is most likely due to the increased FF of the NPs in the cavity region compared to the PBG region. This results in a larger volume of InGaAs per unit area within the cavity.

Although the PC cavities characterized on the substrate are expected to have a significant optical loss in the out-of-plane direction, the effect of the optical confinement due to the PBG is readily observable. In devices where the PBG does not overlap the range of emission, the FWHM is measured to be 33 nm. In the devices where the PBG spans the range of emission, the FWHM is measured to be 23 nm. This reduction in line-width corresponds to a cavity quality factor Q of 42. In addition to the optical power loss into the substrate, the precise arrangement of NPs forming the cavity will also have a strong effect on the Q factor. For top-down PC cavities, it has been shown through simulation and experiment that displacement of the etched holes adjacent to the cavity can result in greater than an order of magnitude difference in Q factor  $^{19,20}$ . These displacements modify the k-space distribution of the electric field to reduce the out-of-plane optical loss. Since this technique has not yet been applied to the devices presented in this paper, it is expected that a similar performance increase can be attained by more detailed modeling of the cavity design.

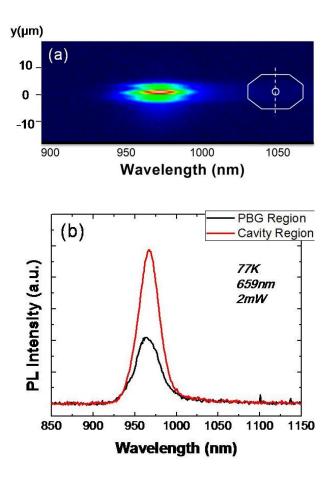

To form a PC cavity with out-of-plane optical confinement, the index of refraction both above and below the cavity must be less than the effective index of the cavity. Using the same characterization method as described above, the samples are cooled to 77K and the PL spectrum is measured along the center axis of the devices. Figure 5(a) shows device 16-3 with a PBG

**Figure 5.** (a) Spectrum of a PC embedded in PDMS with a PBG in the emission range. (b) Spectrum of device where no PBG is present in the emission range. (c) PL spectra comparing the two devices in (a) and (b) taken on the cavity region.

overlapping the emission range while Figure 5(b) shows device 5-3 with a PBG outside the emission range. Similar to the devices on the growth substrate, a clear suppression of the InGaAs band-edge emission is observed where the emission is within the range of the PBG. More importantly, though, is the observation of resonant peaks in the PL spectrum of the cavity in 5(a). As a comparison, Figure 5(c) shows the spectra of the two devices taken on the cavity region. For the device with the PBG covering the emission range, two resonant peaks are observed at 960 nm and 980 nm. The FWHM of each of the resonant peak is estimated to be 10 nm, corresponding to a cavity Q of ~96. While an improvement over the Q factor measured for the devices on the substrate, this value is still considerably low.

Examination of the devices in PDMS by low-vacuum SEM did not reveal any damage or defects surrounding the cavity. Because of this, the low cavity Q indicates that the specific arrangement of NPs in the cavity is most likely to be the limiting factor. This arrangement not only influences the spatial distribution of the cavity mode but also variation in NP height due to

the difference in pitch and diameter, both of which will affect the cavity Q. More specifically, the reduced diameter and pitch in the cavity region results in taller NPs. Future improvements will require finite-difference time-domain (FDTD) simulations to determine the optimum placement of NPs within and adjacent to the cavity. The primary goal will be to minimize the variation in pitch and diameter while simultaneously maximizing the cavity Q.

#### 3.4 CONCLUSIONS

In summary, we report the ability to form bottom-up PC cavities with SAE of III-V NPs. By exploiting the flexibility provided by the SAE growth technique, both PBG structures and active gain regions are formed simultaneously during growth. Careful control of the V-III ratio and growth rates results in highly uniform PC devices with L1 and L3 defect cavities. An axial GaAs/InGaAs heterostructure with an InGaP shell shows strong emission at a peak wavelength of 970 nm. Inhibition of the band-edge transition in devices where the PBG overlaps the emission range is observed. Out-of-plane optical confinement is achieved by embedding the PC devices in PDMS followed by mechanical separation from the original substrate. The PC cavities in PDMS exhibit cavity resonances at 960 nm and 980 nm. Future work will include FDTD simulations to optimize the cavity design to achieve higher *Q* factors. Applications to optofluidics and reuse of patterns after PDMS lift-off will also be explored.

#### **REFERENCES:**

- 1. Oulton, R. F. *et al.* Plasmon lasers at deep subwavelength scale. *Nature* **461**, 629–32 (2009).

- 2. Fast, C. G. Single-nanowire electrically driven lasers. **421**, 241–245 (2003).

- 3. Barrelet, C. J. *et al.* Hybrid Single-Nanowire Photonic Crystal and Microresonator Structures. (2006).

- 4. Park, H. *et al.* A wavelength-selective photonic-crystal waveguide coupled to a nanowire light source. **1,** (2008).

- 5. Heo, J., Guo, W. & Bhattacharya, P. Monolithic single GaN nanowire laser with photonic crystal microcavity on silicon. *Appl. Phys. Lett.* **98**, 021110 (2011).

- 6. Park, H.-G., Qian, F., Barrelet, C. J. & Li, Y. Microstadium single-nanowire laser. *Appl. Phys. Lett.* **91**, 251115 (2007).

- 7. Wu, P. M., Anttu, N., Xu, H. Q., Samuelson, L. & Pistol, M.-E. Colorful InAs nanowire arrays: from strong to weak absorption with geometrical tuning. *Nano Lett.* **12**, 1990–5 (2012).

- 8. Noborisaka, J., Motohisa, J. & Fukui, T. Catalyst-free growth of GaAs nanowires by selective-area metalorganic vapor-phase epitaxy. *Appl. Phys. Lett.* **86**, 213102 (2005).

- 9. Goto, H. *et al.* Growth of Core–Shell InP Nanowires for Photovoltaic Application by Selective-Area Metal Organic Vapor Phase Epitaxy. *Appl. Phys. Express* **2**, 035004 (2009).

- 10. Tomioka, K., Motohisa, J., Hara, S. & Fukui, T. Control of InAs nanowire growth directions on Si. *Nano Lett.* **8,** 3475–80 (2008).

- 11. Tomioka, K., Motohisa, J., Hara, S., Hiruma, K. & Fukui, T. GaAs/AlGaAs core multishell nanowire-based light-emitting diodes on Si. *Nano Lett.* **10**, 1639–44 (2010).

- 12. Kim, S.-H., Huang, J. & Scherer, A. From vertical-cavities to hybrid metal/photonic-crystal nanocavities: towards high-efficiency nanolasers. *J. Opt. Soc. Am. B* **29**, 577 (2012).

- 13. Lončar, M., Yoshie, T., Scherer, A., Gogna, P. & Qiu, Y. Low-threshold photonic crystal laser. *Appl. Phys. Lett.* **81**, 2680 (2002).

- 14. Shapiro, J. N. *et al.* InGaAs heterostructure formation in catalyst-free GaAs nanopillars by selective-area metal-organic vapor phase epitaxy. *Appl. Phys. Lett.* **97**, 243102 (2010).

- 15. Shapiro, J., Lin, a., Huffaker, D. & Ratsch, C. Potential energy surface of In and Ga adatoms above the (111)A and (110) surfaces of a GaAs nanopillar. *Phys. Rev. B* **84**, 1–5 (2011).

- 16. Lin, A. *et al.* Extracting transport parameters in GaAs nanopillars grown by selective-area epitaxy. *Nanotechnology* **23**, 105701 (2012).

- 17. Lin, a., Shapiro, J. N., Scofield, a. C., Liang, B. L. & Huffaker, D. L. Enhanced InAs nanopillar electrical transport by in-situ passivation. *Appl. Phys. Lett.* **102**, 053115 (2013).

- 18. Painter, O. Two-Dimensional Photonic Band-Gap Defect Mode Laser. *Science* (80-. ). **284**, 1819–1821 (1999).

- 19. Akahane, Y., Asano, T., Song, B. & Noda, S. High-Q photonic nanocavity in a two-dimensional photonic crystal. *Nature* **425**, 4–7 (2003).

- 20. Song, B.-S., Noda, S., Asano, T. & Akahane, Y. Ultra-high-Q photonic double-heterostructure nanocavity. *Nat. Mater.* **4**, 207–210 (2005).

# Chapter 4

# 4.1 BACKGROUND AND CHALLENGES OF NANOWIRE LASERS

In the past decade, intense research has been performed in the area of nanowires (NWs) and nanopillars (NPs). These semiconductor nanostructures can be synthesized with specific material compositions<sup>1</sup>, axial and radial heterostructures<sup>2,3</sup>, and on large lattice mismatched substrates including silicon<sup>4,5</sup>. Such attributes, combined with their small cross sections, promise new device architectures and pathways to on-chip photonic integration<sup>6</sup>. An essential component for a viable photonic circuit is a high-performance NW-based laser. Researchers have sought to make efficient NW-based lasers by a number of methods, including top-down photonic crystal (PhC) cavities<sup>7</sup>, micro-stadium resonators<sup>8</sup>, plasmonic waveguides<sup>9</sup>, and NWs that support whispering gallery modes 10,11. So far, these demonstrations have largely been limited to single NWs due to lack of control over position and diameter, thus inhibiting low-loss optical cavity design with sufficient material gain<sup>12,13</sup>, while avoiding highly detrimental surface recombination<sup>14</sup>. In some cases, the resonant cavity and the NW active region require separate lithography and processing steps<sup>7,8</sup>. In other cases the cavity is simply limited by optical losses at the facets<sup>9-11</sup>. As a result, NW-laser demonstrations to date have large threshold power densities and awkward external coupling schemes making them impractical for large-scale integration. Typical reported values of threshold power density range from ~100 kW/cm<sup>2</sup> to >1 MW/cm<sup>2</sup> and require femto-second pulses. Furthermore, most reported NW-based lasers are multimode, which can limit their utility for communications and multiplexing applications.

In order to overcome these problems and realize a practical NW-based laser solution, a high-Q cavity with effective surface passivation is necessary. Of the different possible candidates for high-Q optical cavities, PhC nano-cavity resonators<sup>15</sup> are an attractive choice due to small

mode volume<sup>16</sup>, high spontaneous emission coupling factor<sup>16,17</sup>, and low threshold power. In this work, we implement a "bottom-up" technique where the PhC cavity is formed entirely by III-V NPs using catalyst-free selective-area metal-organic chemical vapor deposition<sup>18</sup>. The resulting device is fundamentally different in that it uses a NP ensemble rather than a single NW to form both active region and cavity. This approach is enabled by accurate control of position and diameter of the NPs, whereby the photonic band-gap and active gain region are grown simultaneously from a masked substrate. By carefully engineering the geometry and heterostructures of the NPs forming the cavity, we achieve low-threshold single mode lasing at room-temperature.

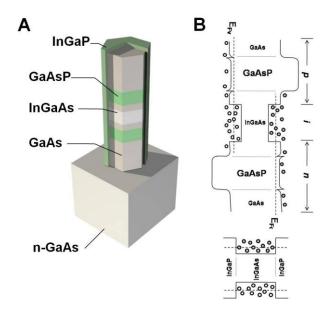

## 4.2 NANOPILLAR PHC LASER STRUCTURE

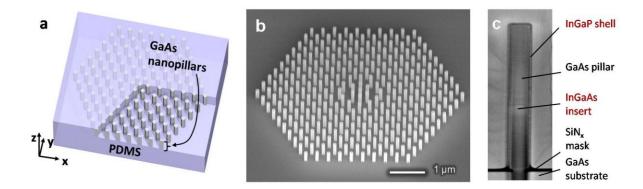

The NPs forming the PhC lasers implement a GaAs/InGaAs/GaAs axial heterostructure for accurate placement of gain within the cavity<sup>19</sup>, while radial growth of InGaP shells provides in-situ passivation. The selective-area grown NPs take the equilibrium shape determined by environmental growth conditions with the resulting side-wall facets consisting of the {1-10} family of crystal planes<sup>20</sup>. The resulting pillar side-walls are perfectly vertical and have atomic scale roughness<sup>21,22</sup>, which inherently avoids two major contributions to loss in top-down PhC cavities<sup>23,24</sup>. Both pillar placement and diameter, which fix cavity resonance wavelength and Q, are determined lithographically. Thus, the cavity resonant wavelength can be designed arbitrarily. Furthermore, the same patterns used to define the position and diameter of the NPs also include optical alignment marks for device integration.

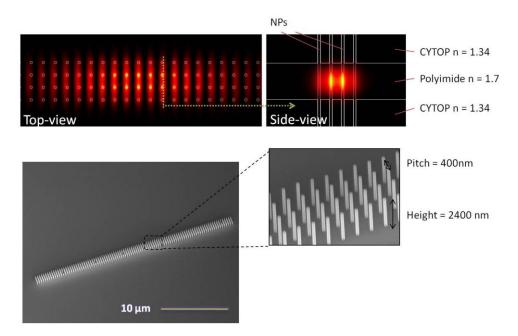

**Figure 1.** (a) Schematic diagram of the NP PhC lasers in PDMS. (b) 45° tilted SEM of a NP PhC as grown on the substrate. (c) Cross-section STEM of a NP showing the InGaAs insert located at the center of the pillar and InGaP shell.

The bottom-up PhC lasers consist of NPs embedded in polydimethylsiloxane (PDMS) as shown in Figure 1(a). The NPs are first grown on a SiN<sub>x</sub> masked GaAs (111)B substrate. Following growth, PDMS is drop cast to a thickness of ~1 mm and cured in atmosphere. The PDMS film is then removed mechanically from the growth substrate. During the PDMS lift-off, the NPs are broken at the base making the patterned substrate reusable for additional growths. The resulting structure forms the complete laser cavity, where the NPs are surrounded by PDMS on all but the top side where they are exposed to air.

Figure 1(b) shows an SEM image of a typical NP PhC laser as grown on the substrate. Each device is a 5  $\mu$ m  $\times$  5  $\mu$ m array of hexagonally-packed pillars which comprise the resonant cavity, surrounding seven central pillars which form the laser active region. The cavity Q and resonant wavelength are lithographically-defined by NP diameter and pitch, respectively. A 4  $\times$  6 matrix of cavity arrays is patterned across the growth substrate for controlled variation in both pillar diameter (100 - 130 nm) and inter-pillar pitch (324 - 342 nm). A microscope image of the device array matrix embedded in PDMS is shown in Appendix A.

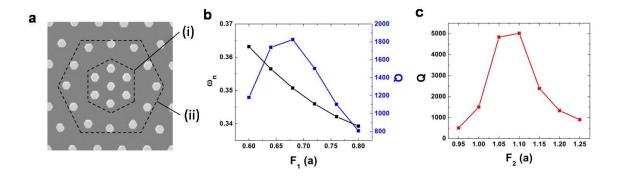

**Figure 2.** (a) Top-down SEM image of the NPs forming the high-Q cavity. The two hexagonal contours labeled (i) and (ii) show the regions where the NP positions were optimized. (b) The Q and frequency dependence on the NP spacing in region (i). (c) The Q dependence on the NP spacing in region (ii).

A cross-section scanning transmission electron microscope (STEM) image of a single representative NP from one of the cavities is shown in Figure 1(c). The pillars are ~730 nm tall and 120 nm in diameter with about 5-10% height variation from center to edge of a cavity and are comprised of both an axial and a radial heterostructure. The axial double-heterostructure is formed by a well-placed 130 nm In<sub>x</sub>Ga<sub>1-x</sub>As insert, where x is measured to be ~15% from both the spontaneous emission peak wavelength and energy dispersive x-ray spectroscopy scan. The lateral heterostructure is formed by a 5 nm lattice-matched InGaP shell to reduce surface recombination. The details of the patterning process and growth conditions are described in more detail in Chapter 3.

### 4.3 FDTD SIMULATION AND CAVITY OPTIMIZATION

3-D finite-difference time-domain (FDTD) simulations are employed to optimize structural parameters such as the height, radius, and the locations of the NPs. The cavity is formed by modifying the original lattice points of the triangular photonic-crystal as shown in Figure 2(a). The cavity consists of two separate sub-regions defined by the two hexagonal contours labeled (i) and (ii). For the inner region (i), the six pillars are rotated by 90° with respect

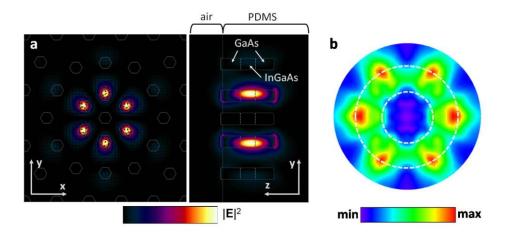

**Figure 3.** (a) Top-down view of the vector field pattern of the magnetic-field  $(H_x, H_y)$  overlaid upon the electric-field intensity  $(|\mathbf{E}|^2)$  distribution within the cavity showing the hexapole mode overlapping six center NPs and cross-section view of  $|\mathbf{E}|^2$  within the cavity showing the overlap with the InGaAs inserts. (b) Far-field radiation pattern of the cavity hexapole mode. The far-field data over the upper hemispherical points  $(\theta, \phi)$  is represented in (x,y) by the mapping defined by  $x = \theta \cos \phi$  and  $y = \theta \sin \phi$ .

to the center pillar position. The distance is then scaled down from the center by a factor of  $F_1$ . Figure 2(b) shows the change in cavity Q and normalized resonant frequency  $\omega_n$  as a function of  $F_1$ . It should be noted that Q and the frequency of the mode are critically dependent on  $F_1$ , since the majority of the mode energy is concentrated within these six pillars. For the outer region (ii), the twelve pillar positions are arranged in a circle and fine tuned by the scaling factor  $F_2$  to optimize Q as shown in Figure 2(c).

A top-down and cross-sectional view of the electric-field intensity distribution ( $|\mathbf{E}|^2$ ) in the cavity is shown in Figure 3(a). The final arrangement of the NPs in the center of the cavity forms a non-degenerate hexapole mode<sup>25</sup>. The positions of the neighboring pillars are modified to maximize the cavity Q while keeping the resonant frequency close to the center of the PBG in order to maintain a large spontaneous emission factor  $\beta$ . The final result of this design optimization yields a simulated cavity Q of 4,600 with an effective mode volume  $V_{eff}$  of 0.137  $(\lambda/n)^3$ . In the cross-sectional view of Figure 3(a), the location of the InGaAs inserts is highlighted

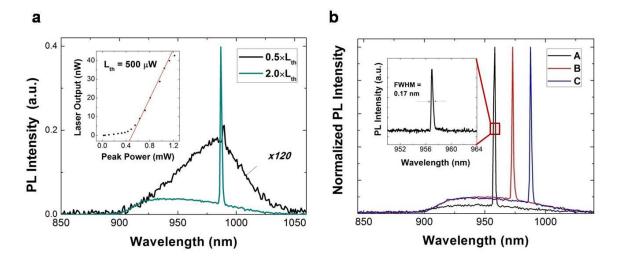

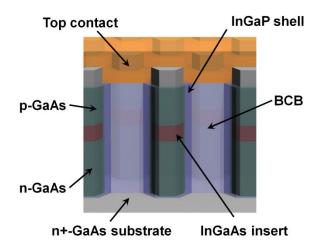

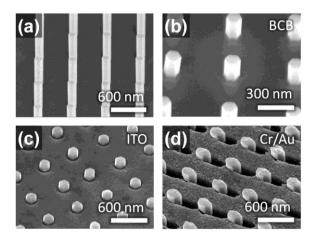

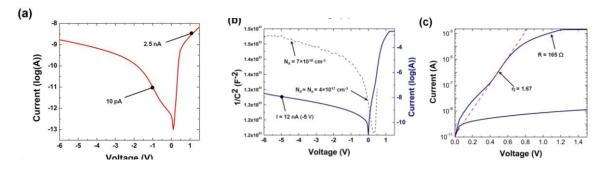

**Figure 4.** (a) Emission spectra of a NP-PC laser emitting at 989 nm both at  $0.5 \times L_{th}$  and  $2 \times L_{th}$ . Inset shows L-L curve of the same device with a threshold of 500  $\mu$ W peak pulse power. (b) Comparison of devices A, B, and C with different pitch and diameter NPs that emit at wavelengths between 960 and 990 nm. Inset shows high-resolution laser spectrum of device A with a FWHM of 0.17 nm.

to show the confinement of carriers to the field anti-node. Based on the insert length as a fraction of the total pillar, the energy confinement factor  $\Gamma$  and threshold gain  $g_{th}$  are calculated with group index and material dispersion of bulk InGaAs<sup>26</sup>. With an insert length that is 18% of the total height as measured by STEM, this method yields  $\Gamma = 0.185$  and  $g_{th} = 197$  cm<sup>-1</sup>.

## 4.4 NANOPILLAR PHC LASER CHARACTERIZATION

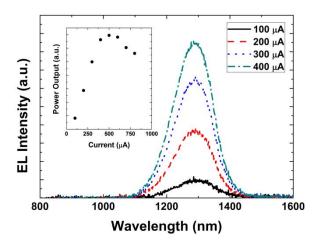

The devices are optically pumped using a pulsed semiconductor laser with a 660 nm peak wavelength, 10  $\mu$ m diameter spot size, and 16 ns excitation pulse at a 1 MHz repetition rate. A 50× microscope objective oriented at 45° to the surface normal is used to both excite the NPs and collect emission. Simulated far-field radiation patterns<sup>27,28</sup> of the cavity resonant mode (Fig. 2B) show that the laser emission should be directed 50° - 70° from normal. Figure 4(a) shows emission spectra from one array both below and above threshold at pump powers of  $0.5 \times L_{th}$  and  $2 \times L_{th}$ . Below threshold, the spectrum is the integrated emission from all NPs within the array including cavity and active region. The spontaneous spectrum is peaked near 975 nm with

FWHM of 65 nm. Even at this very low pump power, the resonant cavity mode can be detected. The characteristics of the sub-threshold cavity emission has not yet been analyzed as stimulated or spontaneous. The FWHM of the modal peak is approximated to be 0.45 nm, which corresponds to an experimental cavity Q of ~2000. At  $2 \times L_{th}$ , the spectrum is dominated by a single peak at 989 nm. The corresponding L-L curve for this device, shown as the inset, indicates a lasing threshold of 500  $\mu$ W peak pulse power or 625 W/cm<sup>2</sup> peak power density. The output power increases linearly until above  $2 \times L_{th}$  where the device emission begins to saturate, reaching an estimated peak output power of 42.5 nW at the InGaAs detector.

The model used to predict the ideal Q required threshold gain gives  $g_{th} = 197 \text{ cm}^{-1}$ . However, with the measured cavity Q of ~2000, an actual threshold gain of  $g_{th} \sim 500 \text{ cm}^{-1}$  is predicted. Since InGaAs bulk gain can be expected to reach >1000 cm<sup>-1</sup> at room temperature with moderate carrier densities, the measured L-L curve and consequent lasing threshold appear to be in reasonable agreement with the predictions of the model. This combined with the measured data provide strong evidence that the devices achieve single mode lasing at low threshold power density. Additionally, the fact that these estimates are based on gain in bulk InGaAs indicates the effectiveness of the InGaP shells used for surface passivation since the threshold for unpassivated InGaAs with the given surface to volume ratio would not be achievable at room temperature.