## UC San Diego

UC San Diego Electronic Theses and Dissertations

Title

Hardware-Algorithm Co-design for Efficient and Privacy-Preserved Edge Computing

Permalink https://escholarship.org/uc/item/4rz7q6zx

Author

Khaleghi, Behnam

Publication Date 2022

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA SAN DIEGO

### Hardware-Algorithm Co-design for Efficient and Privacy-Preserved Edge Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Behnam Khaleghi

Committee in charge:

Professor Tajana Simunic Rosing, Chair Professor Chung-Kuan Cheng Professor Ryan Kastner Professor Farinaz Koushanfar Professor Jishen Zhao

2022

Copyright Behnam Khaleghi, 2022 All rights reserved. The dissertation of Behnam Khaleghi is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2022

### DEDICATION

To my wife, Fatemeh, for her unconditional love, care, and support.

### TABLE OF CONTENTS

| Dissertation A | Approv                                 | val Page                                                                                                       |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 | •••                           |                                           | •••                                   | •••                          |                           | •••                | • •                                                | . iii                                                                        | i          |

|----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------|-------------------------------------------|---------------------------------------|------------------------------|---------------------------|--------------------|----------------------------------------------------|------------------------------------------------------------------------------|------------|

| Dedication .   |                                        |                                                                                                                |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           | •••                |                                                    | . iv                                                                         | 7          |

| Table of Cont  | tents                                  |                                                                                                                |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | ••                           |                           | •                  |                                                    | . v                                                                          | 7          |

| List of Figure | es                                     |                                                                                                                |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           |                    |                                                    | . viii                                                                       | Ĺ          |

| List of Tables | 5                                      |                                                                                                                |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           | ••                 |                                                    | . x                                                                          |            |

| Acknowledge    | ements                                 | 5                                                                                                              |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           | ••                 |                                                    | . xi                                                                         | ĺ          |

| Vita           |                                        |                                                                                                                |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           | ••                 |                                                    | . xiii                                                                       | ĺ          |

| Abstract of th | e Diss                                 | sertation                                                                                                      |                                                                                             |                                                                                     |                                                              |                                    |                                   |                                                                                                                                              |                                                 |                               |                                           | •••                                   | •••                          |                           | ••                 |                                                    | . xvi                                                                        | ĺ          |

| Chapter 1      | Intro<br>1.1<br>1.2                    | Efficie<br>Efficie<br>1.2.1<br>1.2.2<br>1.2.3                                                                  | ncy by<br>ncy by<br>Exact<br>ence<br>High                                                   | Aggr                                                                                | essive<br>w Lea<br>Appro                                     | e Ene<br>arnin<br>oxima<br><br>ASI | ergy<br>g Al<br>ate F<br><br>C De | Red<br>gorit<br>PGA<br><br>esigi                                                                                                             | uction<br>thm<br>MIM<br>MIM<br>MIM              | on c<br>for<br>pler<br><br>HD | of FI<br>Edg<br>nent<br><br>C L           | PGA<br>e Aj<br>atio:<br>              | -ba<br>pplion<br>n of<br>ing | sed<br>catio<br>HD<br>and | Des<br>ons<br>C Ii | igns<br>nfer                                       | s 5<br>. 6<br>. 6<br>. 6<br>nce 7                                            | 55         |

| Chapter 2      | FPG<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | A Energ<br>Introdu<br>Backg<br>2.2.1<br>2.2.2<br>Propos<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>Experi<br>Conch | action<br>round a<br>FPGA<br>Relat<br>sed Me<br>Prelin<br>Propo<br>Propo<br>Timin<br>mental | and Re<br>A Arch<br>ed Wo<br>thod<br>minary<br>osed T<br>osed T<br>ng-Spe<br>I Resu | initect<br>nitect<br>ork in<br>herm<br>herm<br>herm<br>culat | l Wor<br>ure .<br>                 | ware<br>ware                      | · · ·<br>· · · | · · ·<br>· · ·<br>· · ·<br>tage<br>ergy<br>Over | Sca                           | · · ·<br>· · ·<br>· · ·<br>aling<br>timit | · · · · · · · · · · · · · · · · · · · | <br><br><br><br><br><br>     |                           |                    | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | . 12<br>. 14<br>. 14<br>. 15<br>. 17<br>. 17<br>. 20<br>. 28<br>. 30<br>. 32 | 2445770802 |

| Chapter 3      |                                        | cient FP<br>imation<br>Introdu<br>Backg<br>3.2.1                                                               | uction                                                                                      | · · · ·                                                                             | <br><br>otiva                                                | <br><br>tion                       | · · ·                             | • •<br>• •                                                                                                                                   | · ·<br>· ·                                      | · ·                           | · ·                                       | •••                                   | •••                          | ••••                      |                    | · ·<br>· ·                                         | . 37<br>. 38<br>. 41                                                         | 8          |

|           |            | 3.2.2 Motivation                                                                          |

|-----------|------------|-------------------------------------------------------------------------------------------|

|           | 3.3        | Proposed Method: SHEARer                                                                  |

|           |            | 3.3.1 Approximate Encoding                                                                |

|           |            | 3.3.2 SHEAR <i>er</i> Architecture                                                        |

|           |            | 3.3.3 Software Layer                                                                      |

|           | 3.4        | Experimental Results                                                                      |

|           | 3.5        | Conclusion                                                                                |

| Chapter 4 | Effic      | cient Learning Engine on Edge using Hyperdimensional Computing . 59                       |

|           | 4.1        | Introduction                                                                              |

|           | 4.2        | Hyperdimensional Computing Background                                                     |

|           |            | 4.2.1 Encoding                                                                            |

|           |            | 4.2.2 HDC Clustering                                                                      |

|           | 4.3        | Proposed HDC Encoding                                                                     |

|           |            | 4.3.1 GENERIC Encoding                                                                    |

|           |            | 4.3.2 Accuracy Comparison                                                                 |

|           |            | 4.3.3 Efficiency on Conventional Hardware                                                 |

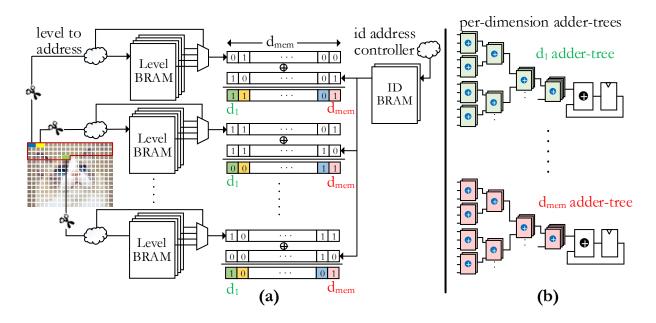

|           | 4.4        | GENERIC Architecture                                                                      |

|           |            | 4.4.1 Overview                                                                            |

|           |            | 4.4.2 Classification and Clustering                                                       |

|           |            | 4.4.3 Energy Reduction                                                                    |

|           | 4.5        | Results                                                                                   |

|           | 1.5        | 4.5.1 Setup                                                                               |

|           |            | 4.5.2 Classification Evaluation                                                           |

|           |            | 4.5.2       Clustering Evaluation       76                                                |

|           | 4.6        | Conclusion         78                                                                     |

| Chapter 5 | Priv       | ate Learning and Inference with Hyperdimensional Computing 79                             |

| Chapter 5 | 5.1        | Introduction                                                                              |

|           | 5.2        | Related Work   82                                                                         |

|           | 5.3        | Reversibility of HDC                                                                      |

|           | 5.5        | 5.3.1 Encoding and Decoding                                                               |

|           |            | 5.3.1         Encoding and Decoding         5.3.2         Parameter Extraction         85 |

|           | 5.4        | Privacy-Preserved HDC Inference                                                           |

|           | 5.4<br>5.5 | •                                                                                         |

|           | 5.5        | 5                                                                                         |

|           |            | 5.5.1 Differential Privacy (DP)                                                           |

|           |            | 5.5.2 Private One-pass Training                                                           |

|           |            | 5.5.3 Private Iterative Training                                                          |

|           | <b>F</b> ( | 5.5.4 Privé-HDnn: Private Image Classification                                            |

|           | 5.6        | Results                                                                                   |

|           |            | 5.6.1 Encoding                                                                            |

|           |            | 5.6.2 Decoding                                                                            |

|           |            | 5.6.3 Inference Privacy                                                                   |

|              |     | 5.6.4   | One-pa    | ss Trai  | ning I | Priva | icy |     |       | <br> |   |       |     |     | 105 |

|--------------|-----|---------|-----------|----------|--------|-------|-----|-----|-------|------|---|-------|-----|-----|-----|

|              |     | 5.6.5   | Iterative | e Train  | ing Pi | rivac | су. |     |       | <br> |   | <br>• |     |     | 106 |

|              |     | 5.6.6   | Image (   | Classifi | catio  | ı.    |     |     |       | <br> | • | <br>• |     |     | 107 |

|              |     | 5.6.7   | Overhe    | ad       |        |       |     |     |       | <br> | • | <br>• |     |     | 109 |

|              | 5.7 | Conclu  | usion .   |          |        |       |     |     | <br>• | <br> |   | <br>• |     |     | 109 |

|              |     |         |           |          |        |       |     |     |       |      |   |       |     |     |     |

| Chapter 6    | Sum | mary an | nd Future | Work     |        |       |     |     |       | <br> |   | <br>• |     | • • | 111 |

|              | 6.1 | Disser  | tation Su | mmary    | ·      |       |     |     |       | <br> |   | <br>• |     |     | 112 |

|              | 6.2 | Future  | Directio  | ns.      |        |       |     |     |       | <br> | • | <br>• |     |     | 115 |

|              |     |         |           |          |        |       |     |     |       |      |   |       |     |     |     |

| Bibliography |     |         |           |          |        | • •   |     | • • |       | <br> |   | <br>• | • • | ••• | 117 |

### LIST OF FIGURES

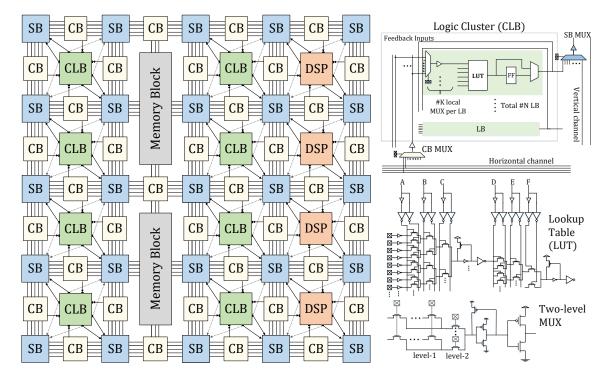

| Figure 2.1: | Tile-based FPGA architecture (left), and building blocks (right) [1].                     | 15 |

|-------------|-------------------------------------------------------------------------------------------|----|

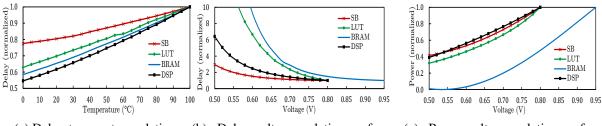

| Figure 2.2: | Different behavior of different FPGA resources under varying temperature and voltages.    | 21 |

| Figure 2.3: | Activity of benchmarks nodes for different activities of primary inputs                   |    |

| -           | (left/blue), and DSP power at different activities of its inputs (right/red)              | 25 |

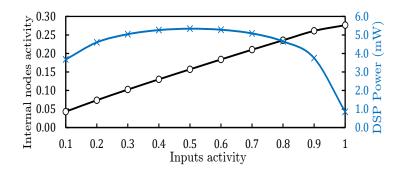

| Figure 2.4: | Outputs of Algorithm 1 for mkDelayWorker benchmark under different                        | 20 |

| Figure 2.5: | ambient temperatures                                                                      | 26 |

| Figure 2.5. | speculative voltage scaling                                                               | 32 |

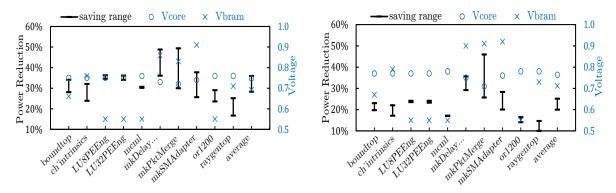

| Figure 2.6: | Power reduction and voltages for 40°C and 65°C board temperatures.                        | 32 |

| Figure 2.7: | Range of energy savings at 65°C (left axis), and corresponding optimal                    | 52 |

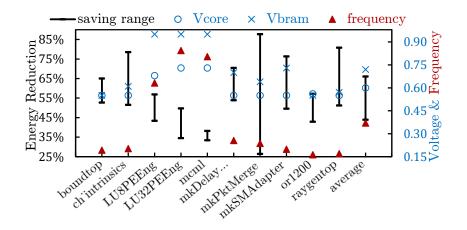

|             | voltage values and frequency ratio (right axis).                                          | 33 |

| Figure 2.8: | Power reduction (left axis) and error increase (right axis) under voltage                 |    |

| C           | over-scaling. X-axis shows violation of critical path delay. $T_{amb}$ is 40°C            | 34 |

| Figure 3.1: | Encoding and training in HD.                                                              | 39 |

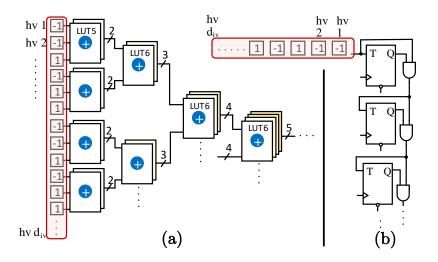

| Figure 3.2: | (a) Adder-tree and (b) counter-based implementation of popcount. (+) denotes              |    |

| -           | add operation.                                                                            | 43 |

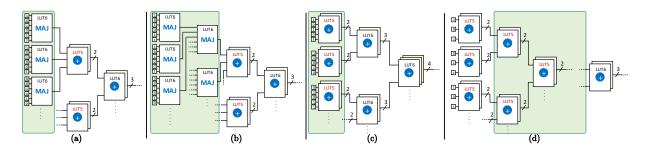

| Figure 3.3: | Our proposed approximate encoding techniques. MAJ and $\oplus$ denote majority            |    |

|             | and addition, respectively.                                                               | 46 |

| Figure 3.4: | SHEARer datapath overview.                                                                | 49 |

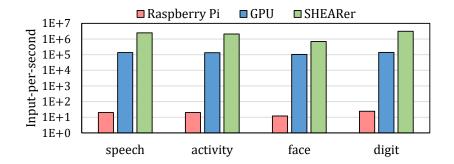

| Figure 3.5: | Throughput of SHEARer versus Raspberry Pi 3 and Nvidia GTX 1080 Ti.                       |    |

| -           | Y-axis is logarithmic scale.                                                              | 55 |

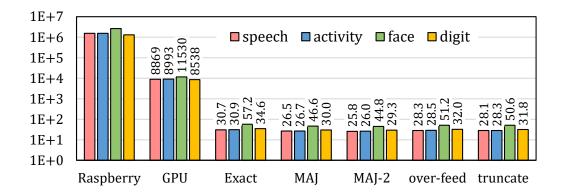

| Figure 3.6: | Energy (Joule) consumption of SHEARer, Raspberry Pi and GPU for 10                        |    |

|             | million inference. Y-axis is logarithmic.                                                 | 56 |

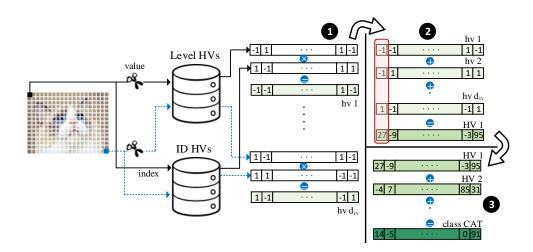

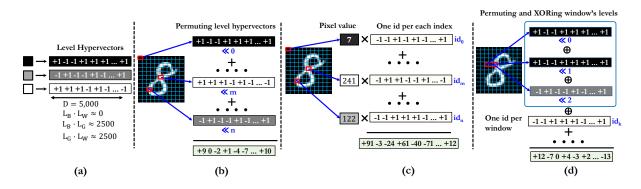

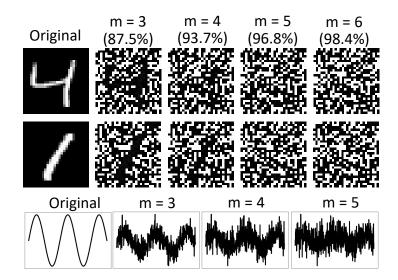

| Figure 4.1: | (a) Level hypervectors, (b) permutation encoding, (c) random projection                   |    |

|             | encoding, (d) proposed GENERIC encoding.                                                  | 62 |

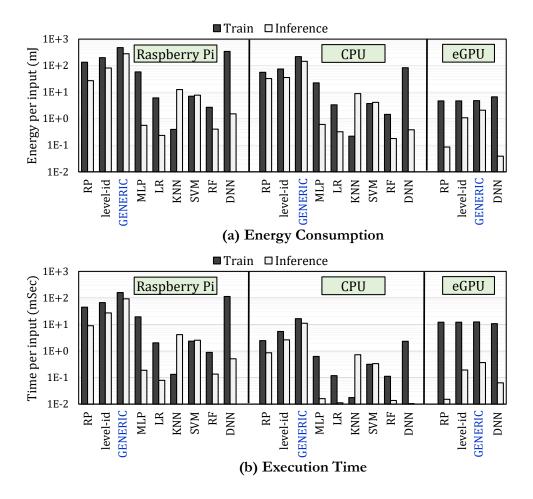

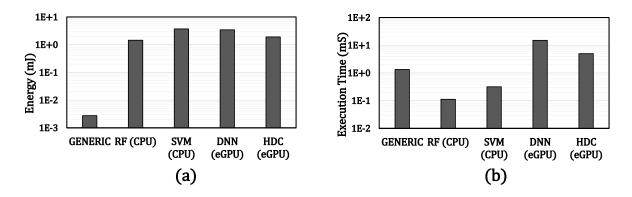

| Figure 4.2: | (a) Energy consumption and (b) execution time of HDC and ML algorithms                    |    |

|             | on different devices.                                                                     | 67 |

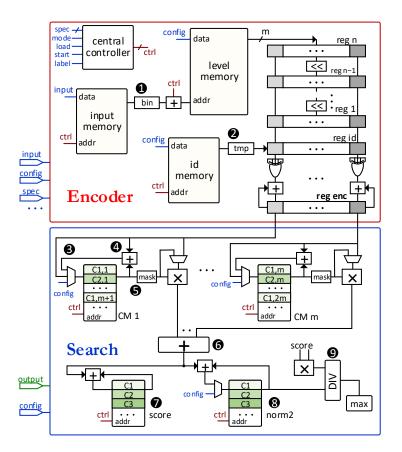

| Figure 4.3: | Overview of GENERIC architecture.                                                         | 69 |

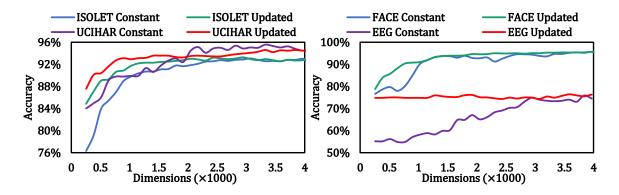

| Figure 4.4: | Accuracy with constant and updated L2 norm                                                | 73 |

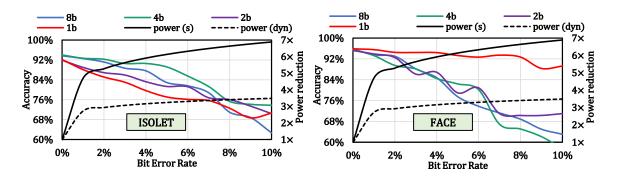

| Figure 4.5: | Accuracy and power reduction with respect to memory error                                 | 73 |

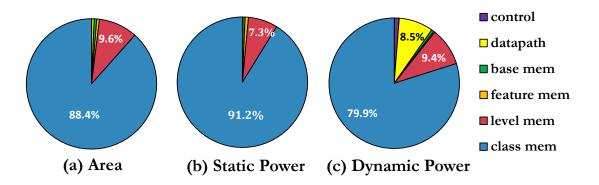

| Figure 4.6: | Area and power breakdown of GENERIC components                                            | 75 |

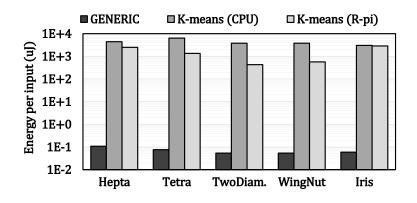

| Figure 4.7: | (a) Training energy and (b) execution time                                                | 76 |

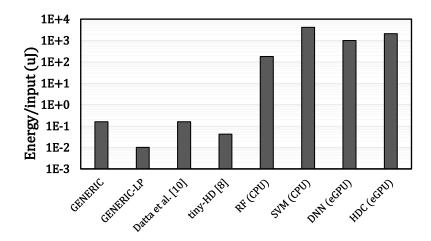

| Figure 4.8: | Inference energy of GENERIC vs baselines                                                  | 77 |

| Figure 4.9: | GENERIC and K-means energy comparison.                                                    | 77 |

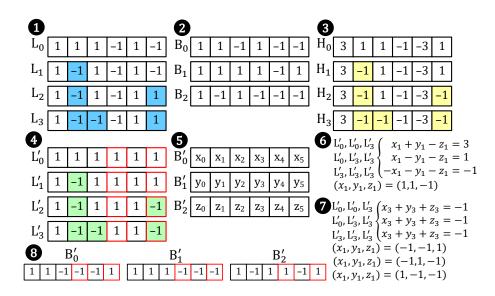

| Figure 5.1: | An example of inferring an unknown level vector $\vec{\mathcal{L}}_x$ by setting all four |    |

|             | features $v_k$ to $\vec{\mathcal{L}}(v_k) = \vec{\mathcal{L}}_x$ .                        | 87 |

| Figure 5.2: | An example of extracting the level and base vectors.                                      | 88 |

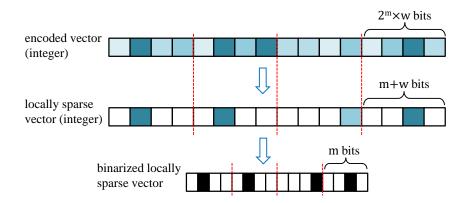

| Figure 5.3:  | Local sparsification. Darker colors indicate larger values                                   | 89   |

|--------------|----------------------------------------------------------------------------------------------|------|

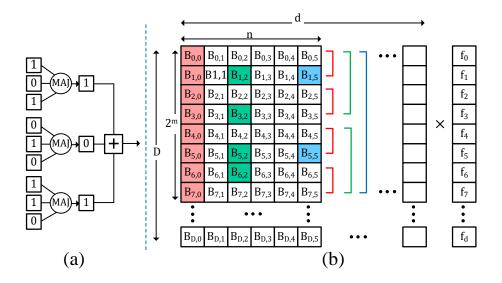

| Figure 5.4:  | (a) Approximate element-wise addition, suitable for sparse base-level and                    |      |

|              | permutation encodings [2], (b) approximate local sparse encoding random                      |      |

|              | projection.                                                                                  | 91   |

| Figure 5.5:  | Privé-HDnn for private training on images. A shallow CNN extracts the                        |      |

|              | features (only once) as raw inputs for HDC, which performs private training                  |      |

|              | according to Algorithm 4                                                                     | 96   |

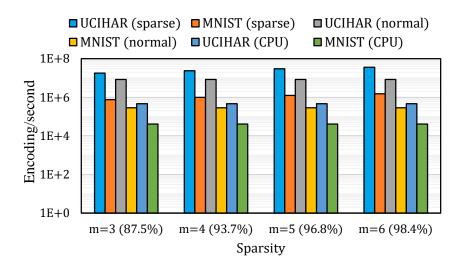

| Figure 5.6:  | Comparing the encoding performance of the approximate locally sparse                         |      |

|              | encoding (FPGA) versus normal encoding on FPGA and CPU                                       | 99   |

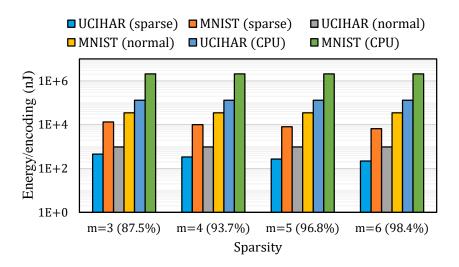

| Figure 5.7:  | Comparing the energy consumption of the approximate locally sparse encod-                    |      |

| C            | ing (FPGA) versus normal encoding on FPGA and CPU.                                           | 100  |

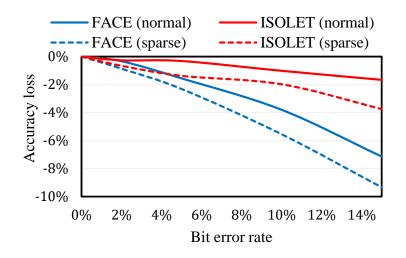

| Figure 5.8:  | Impact of bit error on the accuracy of conventional and sparse encoding.                     |      |

|              | D = 4000 for both datasets.                                                                  | 102  |

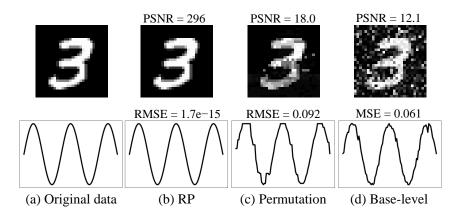

| Figure 5.9:  | Examples of decoded data from handwritten digit and a sinusoidal wave for                    |      |

| C            | different encodings.                                                                         | 102  |

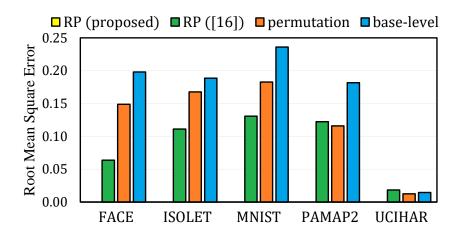

| Figure 5.10: | RMSE between the original and the decoded data for different encodings (RP,                  |      |

|              | base-level, permutation) along with comparison with analytical RP decoding                   |      |

|              | of [3]                                                                                       | 103  |

| Figure 5.11: | Decoding the sparse vectors of RP encoding.                                                  | 105  |

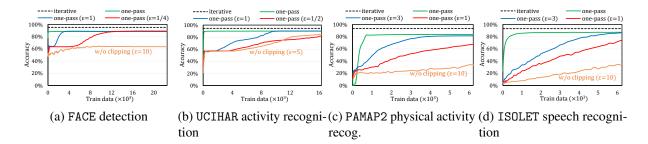

| -            | Accuracy of differentially private one-pass HDC training ( $\delta = 10^{-5}$ , $D = 4000$ ) | .106 |

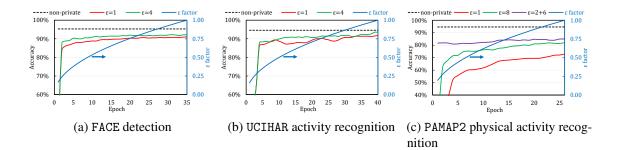

|              | Accuracy of differentially private iterative HDC training ( $\delta = 10^{-5}, D = 4,000$ )  |      |

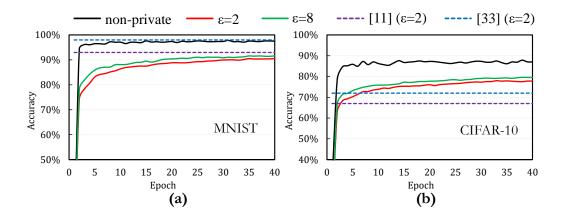

|              | Private training on images with Privé-HDnn.                                                  | 108  |

### LIST OF TABLES

| Table 2.1: | FPGA architecture parameters used in COFFE                                      | 19  |

|------------|---------------------------------------------------------------------------------|-----|

| Table 2.2: | Specifications of the benchmarks.                                               | 20  |

| Table 2.3: | Iterations of Algorithm 1 on mkDelayWorker at $T_{amb} = 60^{\circ} \text{ C.}$ | 28  |

| Table 3.1: | Baseline implementation results.                                                | 54  |

| Table 3.2: | LUT count for a 512-input adder-tree.                                           | 54  |

| Table 3.3: | Relative accuracies SHEARer approximate encodings.                              | 55  |

| Table 4.1: | Accuracy of HDC and ML algorithms.                                              | 66  |

| Table 4.2: | Mutual information score of K-means and HDC                                     | 78  |

| Table 5.1: | Communication bit reduction.                                                    | 100 |

| Table 5.2: | Execution time (ms) for decoding                                                | 103 |

| Table 5.3: | Accuracy and decoding RMSE for sparse encoding.                                 | 104 |

| Table 5.4: | Training time (minutes) of Privé-HDnn versus previous studies                   | 109 |

#### ACKNOWLEDGEMENTS

I would like to first express my gratitude to my advisor, Prof. Tajana Rosing, for her support, guidance, and appreciation during my Ph.D. She went above and beyond her responsibilities as an academic advisor and was understanding of all aspects of my life. Her kind and considerate attitude always impacted me throughout my Ph.D. I would like to also thank my committee members, Prof. CK Cheng, Prof. Ryan Kastner, Prof. Farinaz Koushanfar, and Prof. Jishen Zhao for their feedback and discussions related to this Ph.D. work. I would like to thank all my friends and colleagues in SEELab for their active collaboration. A very special thanks to Mohsen Imani and Amin Kalantar for their continued help and all the good memories. I would like to extend my thanks to all our collaborators from academia and industry who helped us during the last few years, especially Prof. Niema Moshiri, Ramesh Chauhan my supervisor when I was an intern at Qualcomm and his later supports, and Carlos Diaz and his team from TSMC.

My research was made possible by funding from the National Science Foundation (NSF) grants 1730158, 1911095, 2028040, 2003279, 2100237, CRISP, one of six centers in JUMP, an SRC program sponsored by DARPA, SRC Global Research Collaboration (GRC), DARPA HyDREA project, and Taiwan Semiconductor Manufacturing Company (TSMC).

Above all, I owe so much to my wife and my family. My wife, Fatemeh, has been unconditionally supportive and caring and really made countless sacrifices to help me get to this point. I wouldn't be able to pass overcome the difficulties without of her kindness, support, and patience.

The material in this dissertation is, in part, based on the following published or under review papers. The Abstract and Introduction constrain material from all works listed below. Chapter 2, in part, is a reprint of the material as it appears in "FPGA Energy Efficiency by Leveraging Thermal Margin" by Behnam Khaleghi, Sahand Salamat, Mohsen Imani, and Tajana Rosing, which appears in IEEE International Conference on Computer Design (ICCD), 2019. The dissertation author was the primary investigator and author of this paper.

xi

Chapter 3, in part, is a reprint of the material as it appears in "SHEARer: Highly-Efficient Hyperdimensional Computing by Software-Hardware Enabled Multifold Approximation" by Behnam Khaleghi, Sahand Salamat, Anthony Thomas, Fatemeh Asgarinejad, Yeseong Kim, and Tajana Rosing which appears in Proceedings of ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED), 2020. The dissertation author was the primary investigator and author of this paper.

Chapter 4, in part, is a reprint of the material as it appears in "GENERIC: Highly Efficient Learning Engine on Edge using Hyperdimensional Computing" by Behnam Khaleghi, Jaeyoung Kang, Hanyang Xu, Justin Morris, and Tajana Rosing, which appears in Proceedings of the 59th ACM/IEEE Design Automation Conference (DAC), 2022. The dissertation author was the primary investigator and author of this paper.

Chapter 5, in full, is currently being prepared for submission for publication of the material "Private Learning and Inference with Hyperdimensional Computing" by Behnam Khaleghi, Jaeyoung Kang, Xiaofan Yu, and Tajana Rosing, to be submitted to IEEE Internet of Things Journal. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2013 | B. S. in Computer Engineering, Sharif University of Technology, Tehran, Iran                         |

|------|------------------------------------------------------------------------------------------------------|

| 2016 | M. S. in Computer Engineering (Computer Architecture), Sharif University of Technology, Tehran, Iran |

| 2022 | Ph. D. in Computer Science (Computer Engineering), University of California San Diego, US            |

#### PUBLICATIONS

B. Khaleghi, J. Kang, X. Yu, T. Rosing, "Private Learning and Inference with Hyperdimensional Computing", *IEEE Internet of Things Journal (IOTJ)*, 2022 (under submission).

B. Khaleghi, T. Zhang, C. Martino, G. Armstrong, A. Akel, K. Curewitz, J. Eno, S. Eilert, R. Knight, N. Moshiri, T. Rosing, "SALIENT: Ultra-Fast FPGA-based Short Read Alignment", *IEEE International Conference on Field-Programmable Technology (ICFPT)*, 2022.

A. Thomas, B. Khaleghi, G. K. Jha, N. Himayat, R. Iyer, N. Jain, T. Rosing, "Streaming Encoding Algorithms for Scalable Hyperdimensional Computing", *arXiv preprint*, 2022.

U. Mallappa, P. Gangwar, B. Khaleghi, H. Yang, T. Rosing, "TermiNETor: Early Convolution Termination for Efficient Deep Neural Networks", *IEEE International Conference on Computer Design (ICCD)*, 2022.

B. Khaleghi, T. Zhang, N. Shao, A. Akel, K. Curewitz, J. Eno, S. Eilert, N. Moshiri, T. Rosing, "FAST: FPGA-based Acceleration of Genomic Sequence Trimming", *IEEE Biomedical Circuits and Systems (BIOCAS)*, 2022.

J. Kang, B. Khaleghi, Y. Kim, T. Rosing, "OpenHD: A GPU-Powered Framework for Hyperdimensional Computing", *IEEE Transactions on Computers (TC)*, 2022.

J. Morris, Y. Hao, S. Gupta, B. Khaleghi, B. Aksanli, T. Rosing. "Stochastic-HD: Leveraging Stochastic Computing on the Hyper-Dimensional Computing Pipeline", *Frontiers in Neuroscience*, 2022.

A. Dutta, S. Gupta, B. Khaleghi, R. Chandrasekaran, W. Xu, T. Rosing. "HDnn-PIM: Efficient in Memory Design of Hyperdimensional Computing with Feature Extraction", *Proceedings of the Great Lakes Symposium on VLSI (GLSVLSI)*, 2022.

J. Morris, K. Ergun, B. Khaleghi, M. Imani, B. Aksanli, T. Rosing. "HyDREA: Utilizing Hyperdimensional Computing for a More Robust and Efficient Machine Learning System", *ACM Transactions on Embedded Computing Systems (TETC)*, 2022.

G. Armstrong, C. Martino, J. Morris, B. Khaleghi, et al. "Swapping Metagenomics Preprocessing Pipeline Components Offers Speed and Sensitivity Increases", *mSystems*, 2022.

B. Khaleghi<sup>\*</sup>, U. Mallappa<sup>\*</sup>, D. Yaldiz, H. Yang, M. Shah, J. Kang, T. Rosing "PatterNet: Explore and Exploit Filter Patterns for Efficient Deep Neural Networks", *59th ACM/IEEE Design Automation Conference (DAC)*, 2022.

B. Khaleghi, J. Kang, H. Xu, J. Morris, T. Rosing "GENERIC: Highly Efficient Learning Engine on Edge using Hyperdimensional Computing", *59th ACM/IEEE Design Automation Conference* (*DAC*), 2022.

S. Gupta, B. Khaleghi, S. Salamat, J. Morris, R. Ramkumar, J. Yu, A. Tiwari, J. Kang, M. Imani, B. Aksanli, T. Rosing "Store-n-Learn: Classification and Clustering with Hyperdimensional Computing across Flash Hierarchy", *ACM Transactions on Embedded Computing Systems (TETC)*, 2022.

J. Morris, H. Lui, K. Stewart, B. Khaleghi, A. Thomas, T. Marback, B. Aksanli, E. Neftci, T. Rosing, "HyperSpike: HyperDimensional Computing for More Efficient and Robust Spiking Neural Networks", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2022.

J. Kang, B. Khaleghi, Y. Kim, T. Rosing, "XCelHD: An Efficient GPU-Powered Hyperdimensional Computing with Parallelized Training", *27th Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2022.

R. Fielding-Miller, S. Karthikeyan, T. Gaines, et al., "Wastewater and surface monitoring to detect COVID-19 in elementary school settings: The Safer at School Early Alert project", *Medrxiv*, 2021.

A. Paul, G. Hota, B. Khaleghi, Y. Xu, T. Rosing, G. Cauwenberghs, "Attention State Classification with In-Ear EEG", *IEEE Biomedical Circuits and Systems (BIOCAS)*, 2021.

Y. Hao, S. Gupta, J. Morris, B. Khaleghi, B. Aksanli, T. Rosing, "Stochastic-HD: Leveraging Stochastic Computing on Hyper-Dimensional Computing", *IEEE International Conference on Computer Design (ICCD)*, 2021.

S. Salamat, A. H. Aboutalebi, B. Khaleghi, J. H. Lee, Y. S. Ki, T. Rosing, "NASCENT: Near-Storage Acceleration of Database Sort on SmartSSD", *ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)*, 2021.

B. Khaleghi, H. Xu, J. Morris, T. Rosing, "tiny-HD: Ultra-Efficient Hyperdimensional Computing Engine for IoT Applications", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2021.

J. Morris, K. Ergun, B. Khaleghi, M. Imani, B. Aksanli, T. Rosing, "HyDREA: Towards More Robust and Efficient Machine Learning Systems with Hyperdimensional Computing", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2021. R. Garcia, F. Asgarinejad, B. Khaleghi, T. Rosing, M. Imani, "TruLook: A Framework for Configurable GPU Approximation", *Design, Automation & Test in Europe Conference & Exhibition* (*DATE*), 2021.

S. Salamat, S. Shubhi, B. Khaleghi, T. Rosing, "Residue-Net: Multiplication-free Neural Network by In-situ, No-loss Migration to Residue Number Systems", *27th Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2021.

B. Khaleghi, S. Salamat, T. Rosing, "Revisiting FPGA Routing under Varying Operating Conditions", *International Conference on Field-Programmable Technology (ICFPT)*, 2020.

B. Khaleghi, S. Salamat, A. Thomas, F. Asgarinejad, Y. Kim, T. Rosing, "SHEARer: Highly-Efficient Hyperdimensional Computing by Software-Hardware Enabled Multifold AppRoximation", *ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED)*, 2020.

B. Khaleghi, M. Imani, T. Rosing, "Prive-HD: Privacy-Preserved Hyperdimensional Computing", *ACM/IEEE Design Automation Conference (DAC)*, 2020.

B. Khaleghi, S. Salamat, M. Imani, T. Rosing, "FPGA Energy Efficiency by Leveraging Thermal Margin", *International Conference on Computer Design (ICCD)*, 2019.

S. Salamat, B. Khaleghi, M. Imani, T. Rosing, "Workload-Aware Opportunistic Energy Efficiency in Multi-FPGA Platforms", *IEEE/ACM International Conference on Computer-Aided Design* (*ICCAD*), 2019.

S. Gupta, M. Imani, B. Khaleghi, V. Kumar, T. Rosing, "RAPID: A ReRAM Processing in Memory Architecture for DNA Sequence Alignment", *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, 2019.

M. Imani, S. Salamat, B. Khaleghi, M. Samragh, F. Koushanfar, T. Rosing, "SparseHD: Algorithm-Hardware Co-Optimization for Efficient High-Dimensional Computing", *IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 2019.

J. Sim, M. Kim, Y. Kim, S. Gupta, B. Khaleghi, T. Rosing, "MAPIM: Mat Parallelism for High Performance Processing in Non-volatile Memory Architecture", *International Symposium on Quality Electronic Design (ISQED)*, 2019.

S. Salamat, M. Imani, B. Khaleghi, T. Rosing, "F5-HD: Fast Flexible FPGA-based Framework for Refreshing Hyperdimensional Computing", *ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)*, 2019.

B. Khaleghi, T. Rosing, "Thermal-Aware Design and Flow for FPGA Performance Improvement", *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2019.

#### ABSTRACT OF THE DISSERTATION

#### Hardware-Algorithm Co-design for Efficient and Privacy-Preserved Edge Computing

by

Behnam Khaleghi

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2022

Professor Tajana Simunic Rosing, Chair

The rapidly growing number of edge devices continuously generating data with real-time response constraints coupled with the bandwidth, latency, and reliability issues of centralized cloud computing have made computing near the edge indispensable. As a result, using Field-Programmable Gate Arrays (FPGAs) at the edge, due to their unique capabilities that meet the requirements of both high-performance applications and the Internet of Things (IoT) domain, is becoming prevalent. However, designs deployed on these devices suffer from efficiency gap versus custom implementations mainly due to the overhead associated with the FPGAs reconfigurability. This problem is more pronounced in the edge domain, where most devices are battery-powered. In the first part of this dissertation, we identify and overcome the challenges

behind the power reduction of FPGA-based applications and propose techniques to lower their energy consumption. Our approach exploits the pessimistic timing margin of the designs to tune the voltage and improves the energy consumption by 66%.

An increasing number of edge applications rely on machine learning (ML) algorithms to generate useful insights from data. While modern machine learning techniques – in particular deep neural networks (DNNs) – can produce state-of-the-art results, they often entail substantial memory and compute requirements that may exceed the power and resources available on lightweight error-prone edge devices. Hyperdimensional Computing (HDC) is an emerging lightweight and robust learning paradigm suited for the edge domain that copes with the memory and compute overhead of conventional ML algorithms. The next part of the dissertation proposes efficient FPGA-based and custom hardware implementations of HDC to enable intelligence on devices with limited resources, strict energy constraints, and in noisy environments. The proposed HDC algorithms and accelerators reduce the energy consumption by more than three orders of magnitude compared to other ML solutions, with a comparable or better accuracy.

The last part of the dissertation seeks to resolve the privacy concerns of HDC that stem from its reversible algorithm and pose challenges for HDC-based learning and inference. We propose hardware- and communication-efficient techniques that improve the 'inference' privacy of HDC by reducing the information of the transferred data while consuming less energy than the non-private baseline. We then show that HDC 'learning' can meet tight privacy budgets with negligible accuracy degradation. We also propose a hybrid CNN and HDC model for differentially-private training over image data, which achieves comparable or better accuracy than the state-of-the-art CNN-only methods with more than three orders of magnitude faster training.

# Chapter 1

# Introduction

The growing number of computing devices and systems in the information age creates an exploding amount of data every moment. There are already over 13 billion connected devices of different sizes and computation power, from sensory edge devices to many-core servers, producing or consuming around 3000 terabyte of data every second [4, 5]. Processing such an unprecedented volume of data has exacerbated the energy and performance issues of current processing systems caused by the failure of Dennard scaling [6] and the slowdown of Moore's law [7]. Notably, the growth of the edge devices, ranging from resource and energy-constrained lightweight remote sensors carrying out simple data filtering to battery-powered self-driving cars performing complex machine learning (ML) algorithms, have aggravated the bandwidth, latency, and reliability challenges of offloading data to the cloud and made more efficient and robust computing at the edge indispensable [8, 9].

A promising approach to address the energy and performance crisis is architectural specialization [10], i.e., designing a custom accelerator tailored for particular application(s). While an effective solution for ML and AI market, developing customized hardware is costly, time-consuming, and hence not plausible for applications with limited use cases or continually

evolving/updating ones. Accordingly, using Field-Programmable Gate Arrays (FPGAs), which offer programmability while being more energy efficient than CPUs and GPUs [11, 12] is getting more popular not only on cloud [13, 14, 15] but also at the edge [16, 17, 18]. However, the reconfigurability of FPGAs causes non-negligible performance and energy gaps with the custom ASIC counterparts [19, 20]. In addition, nowadays, more and more edge applications rely on ML algorithms to generate useful insights from data [21, 22, 23]. While modern ML techniques – in particular deep neural networks (DNNs) – can produce state-of-the-art results, they often entail substantial memory and compute requirements that exceed edge devices' resource and energy limitations even if implemented on custom architectures [24, 25, 26, 27].

That being said, there is a pressing need to unfold more aggressive energy reduction techniques on both the hardware and algorithm side while considering the reliability and privacy concerns. In this dissertation, we seek orthogonal hardware and algorithm strategies to achieve this goal. Given the FPGAs gaining traction in both data center and edge applications, in the first part of this dissertation, we identify and overcome the challenges behind the power reduction of FPGA-based applications and propose techniques to lower their energy consumption. The second part of the dissertation focuses on alternative computing paradigms to address the resource and energy demands of nowadays ubiquitous algorithms, i.e., machine learning. To this end, we introduce hyperdimensional computing (HDC) as a lightweight and robust learning alternative and propose efficient FPGA-based and custom ASIC implementations of HDC to enable intelligence on devices with limited resources, strict energy constraints, and in noisy environments. We also investigate and address the privacy challenges of HD computing.

**Field-Programmable Gate Arrays (FPGAs):** The key characteristics of FPGAs, such as customizability based on the applications features, programmability to adopt new attributes, and low latency by creating deep processing pipeline, have paved the way for these devices to be deployed on data centers to either provide software as a service such as low-latency DNN accelerator [14] and search engine [13] or used internally such as offloading host networking to

hardware [15]. That being said, FPGAs are even more attractive at the edge. Compared to the other commercial off-the-shelf alternatives such as microcontrollers, FPGAs offer versatile interfaces to connect peripherals such as cameras and other types of sensors. The connectivity of FPGAs also allows them to act as a support processing unit for sensory devices in the edge gateway [18]. The unrivaled computing power offered by FPGAs, together with their reconfigurability that allows in-field upgrade, make them more advantageous for a manifold of edge applications including but not limited to image and signal processing, communication within the Internet of things (IoT) stack, smart energy controller system, and real-time heavyweight video analysis [18]. Therefore, more and more applications in the IoT era can be implemented on FPGAs, with the need for utmost energy efficiency [16, 17, 18]. However, the reconfigurability of FPGAs, while appealing, imposes energy overhead. This, together with slowed shrinking of supply voltage [28], have pushed the high-end family of these devices to a point they consume power comparable to processors [29]. All in all, more aggressive power reduction approaches for FPGAs have become indispensable.

**Hyperdimensional Computing (HDC):** Hyperdimensional Computing (HDC) is a novel brain-inspired learning paradigm based on the observation that brains perform cognitive tasks by mapping sensory inputs to high-dimensional neural representation [30, 31, 32, 33, 34, 35]. It enables the brain to carry out simple, low-power, error-resilient, and parallelizable operations, all in hyperspace. Such characteristics of HDC make it appealing for a wide variety of applications, particularly the edge domain, with devices with tight resource and energy constraints working in noisy environments. HDC uses a deterministic encoding to map the raw input data to points in hyperspace, represented by vectors with thousands of dimensions. For random vectors  $\vec{H}_1$  and  $\vec{H}_2$ , the sum vector  $\vec{S} = \vec{H}_1 + \vec{H}_2$  is more similar to  $\vec{H}_1$  and  $\vec{H}_2$  than any other random vector. This concept is leveraged to represent sets in hyperspace. Vectors of the same category are bundled by vector addition to create a class vector. To classify a query, the input is encoded in the same fashion and compared with the class vectors to find the most similar label.

Despite the simplicity of the HDC algorithm, its bit-level massively parallel operations do not accord well with general-purpose processors such as CPUs and GPUs due to, e.g., memory latency and data movement of large vectors and the fact that these devices are over-provisioned for majorly binary operations of HDC. FPGA-based implementation can provide a great extent of flexibility, high degree of parallelism, and bit-level granularity of operations that significantly improves the effective allocation of resources and hence the performance. Nevertheless, while appealing for a large body of edge use cases, FPGAs suffer from large form-factor and leakage power, as well as power overhead associated with its reconfiguration capability. These drawbacks hinder the deployment of FPGAs in extremely energy/area-constrained use cases such as wearable devices and ultra-low-power sensory devices and call for custom HDC circuits. However, previous attempts on custom HDC accelerators support a limited number of applications, achieve low accuracy, and mainly do not support training [36, 37, 38, 39, 40].

Additionally, the simple encoding techniques that HDC benefits from are reversible to the original data. That is, the original data can be reconstructed from the encoding vectors with a good estimate. It poses serious privacy concerns to data. First, in certain applications of HDC, such as federated learning or cloud-hosted inference [41, 42], offloading the encoded data jeopardizes privacy since an untrustworthy server or communication link can reconstruct the original data. Second, as the HDC model is a superposition of vectors, small changes in the training data can reveal the statistics of particular encoded vectors from which the raw data can be retrieved. It is more problematic than DNNs, wherein the model is realized by backpropagation and non-linear operations that somewhat obfuscate the training details [43].

In the rest of the introduction, we give an overview of the contributions of this dissertation to tackle the aforementioned challenges.

# 1.1 Efficiency by Aggressive Energy Reduction of FPGA-based Designs

FPGA devices are continuously evolving to meet the high computation and performance demand for emerging applications. As a result, cutting-edge FPGAs are not as energy efficient as conventionally presumed, and therefore, aggressive power-saving techniques have become imperative. The clock rate of an FPGA-mapped design is set based on worst-case conditions to ensure reliable operation under all circumstances. This usually leaves a considerable timing margin that can be exploited to reduce power consumption by scaling voltage without lowering clock frequency. There are hurdles for such opportunistic voltage scaling in FPGAs because (a) critical paths change with designs, making timing evaluation difficult as voltage changes, (b) each FPGA resource has a particular power-delay trade-off with voltage, (c) data corruption of configuration cells and memory blocks further hampers voltage scaling.

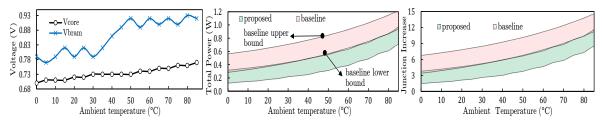

Chapter 2 details the proposed techniques to reduce the power and energy consumption of FPGA-based designs. To this end, we propose incorporating thermal-aware voltage scaling in the FPGA design flow. We first obtain the temperature-delay-voltage correlation of FPGA resources within the supported temperature range. Then, we statically (i.e., offline) estimate the thermal distribution of applications to obtain the available timing headroom, for which voltages of different power rails can be efficiently determined based on the characterized library. For further effectiveness, we also propose online (i.e., dynamic) voltage adaptation based on the response of thermal sensors. The proposed methods consider the voltage-temperature feedback loop and the separate power rails of specific resource types to yield maximum power efficiency. Thereafter, we leverage the aforementioned proposed flow to explore the *energy* consumption, whereby we trade-off the performance and power consumption to achieve the minimum energy point. This is desirable for a majority of edge and IoT applications for which total energy consumption is of the utmost concern. Experimental results over a set of industrial benchmarks indicate up to 36% power reduction with the same performance and 66% total energy saving when energy is the optimization target.

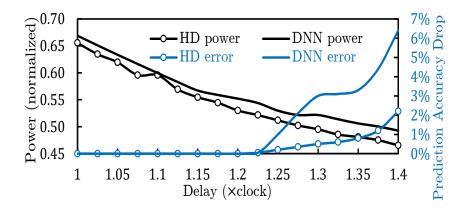

Our approaches mentioned above are deterministic, as they guarantee timing closure. Nonetheless, many use cases, such as image processing and machine learning applications, can tolerate a certain level of computation errors, which allows voltage *over-scaling*. However, it needs an examination of applications under these non-ideal conditions to get a glimpse of produced error in the output. Accordingly, we propose a primary FPGA simulation framework to be able to evaluate an FPGA-mapped design under voltage-scaling, i.e., when the delay of resources varies. Using the proposed framework, we map demonstrative machine learning applications into FPGA fabric and examine the impact of voltage *over-scaling* on extra power gain versus accuracy drop. This yields an additional ~15% power reduction compared to our original (non-invasive) voltage scaling.

# **1.2 Efficiency by a New Learning Algorithm for Edge Applications**

### **1.2.1** Exact and Approximate FPGA Implementation of HDC Inference

The primary appeal of HD computing lies in its amenability to implementation in modern hardware accelerators. Because the HD representations are simply long Boolean vectors, they can be processed extremely efficiently in highly parallel platforms. Particularly, FPGA-based implementations can provide a high degree of parallelism and bit-level customization of operations that significantly improves the effective resource utilization and hence the performance. The principal challenge of HD computing – and the focus of this chapter – lies in designing good encoding schemes that (1) represent the data in a format suitable for learning and (2) are efficient to implement in hardware. In general, the encoding phase is the most expensive stage in the HD

learning pipeline. Existing encoding methods require generating vectors in full integer-precision and then *ex-post* quantizing to  $\{\pm 1\}$ . While this accelerates the associative search phase, it does not address encoding, which is the primary source of inefficiency.

In Chapter 3, we propose novel techniques to compute the encodings in an approximate manner that saves a substantial amount of resources with an insignificant impact on accuracy. Of independent interest is our novel FPGA implementation that achieves striking performance through massive parallelism with low power consumption. Approximate encodings entail models to be trained in a similar approximate fashion. Thus we also develop a software emulation to enable users to train desired HD models. Our software framework enables users to explore the trade-off between the degree of approximation, accuracy, and resource utilization (hence power consumption) by generating a pre-compiled library that correlates approximation schemes and FPGA resource utilization and power consumption. We show that our procedure leads to performance improvement of  $15.7 \times$  and energy savings of up to  $301 \times$  compared to state-of-the-art encoding methods implemented on GPU.

### **1.2.2** Highly-Efficient ASIC Design of HDC Learning and Inference

Unleashing the potential of HDC is contingent on the underlying hardware. Conventional processing platforms such as CPUs and GPUs are incapable of taking full advantage of the highly-parallel bit-level operations of HDC. FPGA platforms, while appealing for HDC, cannot be utilized in the domains that require small form-factor and extremely low power and energy consumption such as tiny wearable devices. While this makes custom HDC engines crucial, existing HDC encoding techniques do not cover a broad range of applications to make a custom HDC design capable of running varied applications without the need for expensive FPGA-like reconfigurability plausible.

In Chapter 4, we propose GENERIC (highly efficient learning engine on edge using hyperdimensional computing) for highly efficient and accurate trainable classification and cluster-

ing. Our primary goal is to make GENERIC compact and low-power to meet year-long batterypowered operation, yet fast enough during training and burst inference, e.g., when it serves as an IoT gateway. To this end, we first propose a novel HDC encoding that yields high accuracy in various benchmarks. Such a generic encoding is fundamental to developing a custom yet flexible circuit and avoiding otherwise expensive configurable (FPGA-like) platforms. Then we perform a detailed comparison of HDC and various ML techniques on conventional devices and point out the failure of these devices in unleashing HDC advantages. To our knowledge, it is the first detailed comparison of the accuracy and efficiency of different HDC and ML techniques. Using the proposed encoding, we develop the GENERIC flexible architecture that implements accurate HDC-based trainable classification and clustering. GENERIC benefits from extreme energy reduction techniques such as application-opportunistic power gating, on-demand dimension reduction, and error-resilient voltage over-scaling.

We implemented GENERIC using 14 nm technology. The design occupies only  $0.30 \text{ mm}^2$  area and consumes  $90 \,\mu\text{W}$  static and  $3.94 \,\mu\text{W/MHz}$  dynamic power. Comparison of GENERIC with the state-of-the-art HDC implementations reveals GENERIC improves the classification accuracy by at least 3.5% over existing HDC techniques and 6.5% over conventional ML techniques (e.g., support-vector machines, random forest, and multilayer perceptron). Compared to the most efficient baseline ML algorithm (random forest), GENERIC improves the inference energy consumption by  $530\times$ , and training energy by  $1590\times$  with 8.2% higher accuracy. Such a tiny form-factor and power draw of our design enables uninterrupted use of HDC in a very wide-range of IoT applications including wearables and remote sensors that otherwise would require network access (and associated peripherals) and battery replacement.

### **1.2.3** Preserving the Privacy of HDC-based Learning and Inference

One of the unique advantages that HDC offers is facilitating federated learning, where distributed edge devices can simply offload the encoded vectors and a central aggregator creates

the unified model by just adding up the vectors and returning the aggregate model. Federated learning by HDC significantly reduces the transmission costs, requires less computation power, and can cope with unreliable network due to the error tolerance of HDC [41]. In addition, in certain cases that the memory of a very tiny sensory device might not fit the HDC model, vectors can be offloaded to an adjacent device, gateway or cloud for inference. Since HDC uses simple encoding techniques, as we shown in Chapter 5, these encoded vectors can be decoded to the original data with a good estimate, which raises privacy concerns to data since an untrustworthy server or communication link can reconstruct the original data. Second, as the HDC model (classes) is a superposition of vectors, small changes in the training data can reveal the statistics of particular encoded vectors from which the raw data can be retrieved. It is more problematic than DNNs, wherein the model is realized by backpropagation and non-linear operations that can obfuscate the training details.

In Chapter 5, we investigate the inference and training privacy of HDC. We show that although HDC operations are reversible, we can leverage its noise resiliency for private training and inference. Specifically, we make the following novel contributions. First, for different HDC encoding techniques, we show that *encoding parameters* can be extracted by using adversary inputs and observing the encoded vector. Then, using these extracted (or already known) parameters, we introduce techniques to decode the *original data* from the encoded vectors for various encodings. The decoded data have relatively low mean squared error (MSE) versus the original data. To tackle this reversibility challenge, we propose hardware- and communication-efficient techniques to enhance the inference privacy of HDC by reducing the information of the transferred data. To this end, we use hardware-friendly (regular) local sparsification of the encoded vectors that eliminates all but the maximum value of consecutive vector embeddings. Our approach, implemented on FPGA, reduces both encoding and communication energy (by transferring the index of the maximum element only). Thereafter, the chapter targets privacy-preserved training of HDC based on the concept of differential privacy. We propose private one-pass (suited for online

and federated learning) as well as iterative learning of HDC. We show that privacy-preserved HDC training, in particular one-pass learning, can meet tight privacy budgets with a similar accuracy to the non-private models. Finally, we propose privacy-preserved HDC models for image classification, namely Privé-HDnn (HD + neural network), which combines a pre-trained CNN feature extractor and a trainable HDC classifier for private training on the target dataset. By using a constant CNN trained on public dataset and private training of HDC only, we get around the sensitivity of CNNs to noise injection while extracting complex features for HDC to tackle its challenge on image data. Experimental results show Privé-HDnn can achieve a similar or better (by up to 5.8%) accuracy compared to CNN-only approaches, with  $9.2-1231 \times$  faster training, while offering other advantages such as few-shot learning due to the capability of HDC in learning from fewer data.

# Chapter 2

# FPGA Energy Efficiency by Leveraging Thermal Margin

In the previous chapter, we explained that the programmability and performance balance of FPGAs have paved the way for these devices to a variety of heavy data center applications such as search engines, machine learning, and networking [13, 14, 15] to name a few. Other key characteristics of FPGAs, such as easy interfacing with peripherals and integration with soft and hard processors, have also made the lower-end families of devices popular in less heavy edge workloads [16, 17, 18]. Unfortunately, the resource overhead associated with the programmability of devices has caused an energy efficiency gap between the designs implemented on FPGAs versus the ASIC counterparts. In this chapter, we dig into some roots of this inefficiency and mitigation challenges and elaborate on our approach to reduce the energy consumption of FPGA devices, both data center class and lower-end devices. We propose a systematical approach to leverage the available thermal headroom of FPGA-mapped designs for power and energy improvement by tuning the voltage level. By comprehensively analyzing the timing and power consumption of FPGA building blocks under varying temperatures and voltages, we propose a thermal-aware voltage scaling flow that effectively utilizes the thermal margin to reduce power consumption without degrading performance. We show that the proposed flow can be especially employed for energy optimization as well, whereby power consumption and delay are compromised to accomplish the tasks with minimum energy.

### 2.1 Introduction

The prevalence of computation-intensive workloads with high-performance requirements such as machine learning (ML) and data center applications [13, 14, 15, 44] accompanied with the advance of technology node have persuaded the FPGA vendors to integrate more resources with boosted clock rate in state-of-the-art FPGAs [45]. This, together with slowed shrinking of FPGAs supply voltage [28], have pushed these devices to a point they consume power comparable to CPUs [29]. Beside data center applications, there are prevailing energy-constrained applications at the edge, implemented in more low-end FPGAs, with the need for extreme energy efficiency [16, 17].

As FPGAs already employ a manifold of device-level optimization to throttle power consumption [46], more *aggressive* power reduction techniques are gaining traction. These techniques generally build upon the conservative timing margin  $(d_g)$  that is considered to compensate reliability threats in deep-nano technologies; while an FPGA-mapped design is able to deliver an *actual* clock period of  $d_{V_{nom}}$  at nominal voltage  $V_{nom}$ , in practice, STA (static timing analysis) tools report an operating clock delay of  $d_{V_{nom}} + d_g$  to make up for uncertainties such as voltage fluctuations, degradation, temperature, etc. [29]. The aforementioned aggressive techniques exploit this available timing headroom to reduce supply voltage of FPGAs down to  $V_{low}$  for which the *actual* clock period  $d_{V_{low}}$  becomes equal or close to  $d_{V_{nom}} + d_g$  (leaving no margin for guardbands). Thus, the device still delivers the original performance at a lower voltage. Note that *aggressive* voltage scaling techniques are different from conventional DVFS (dynamic voltage and frequency).

scaling) that concurrently tunes the frequency and voltage based on per-task performance demand of applications.

Although lowering the supply voltage of processors and ASIC devices has been known to be an effective power saving technique [47, 48, 49], there are limited studies presenting voltage scaling in FPGAs. Voltage scaling (in particular, aggressive and performance-aware one) in FPGAs is challenging mainly because: (a) Critical Path (CP) in an FPGA is designdependent, which makes timing probing difficult under voltage scaling, especially considering the impact of temperature. Therefore, in contrast to ASIC designs, a set of precalibrated stand-alone sensory circuits, e.g., ring oscillators and CP monitors [48] cannot accurately correlate the sensor frequency with all varying CPs. (b) FPGA architectures are heterogeneous, comprising soft-fabric (i.e., programmable logic and routing resources), DSP cores, memory blocks (BRAM), etc. These building blocks are tightly coupled, and each has a particular power/delay relation with supply voltage. Considering the separate voltage rails provided for certain components, i.e., V<sub>bram</sub>, V<sub>core</sub>, and  $V_{io}$  that can be regulated separately, finding efficient voltage points becomes design-dependent and challenging. In other words, in multi-supply devices, multiple voltage combinations can lead to the target  $d_{V_{nom}} + d_g$  boundary, while only one tuple yields minimum power. This makes speculative voltage decrement no more efficient. (c) Scaling the voltage of FPGAs is also constrained by the data corruption of configuration and memory SRAM cells. In addition, as we will discuss in this chapter, reducing the voltage of configuration cells unexpectedly increases FPGA power consumption in certain cases, calling for cautious analysis.

We leverage the pessimistic thermal-induced timing slack to scale down FPGA operating voltage for power saving while tackling the aforementioned challenges as follows.

(1) We propose to incorporate thermal-aware voltage scaling in the FPGA design flow. We first obtain the temperature-delay-voltage correlation of FPGA resources within the supported temperature range. Then, we statically estimate the thermal distribution of applications to obtain the available timing headroom, for which voltages of different power rails can be efficiently

determined based on the characterized library. For further effectiveness, we also suggest online (i.e., dynamic) voltage adaptation based on the response of thermal sensors. The proposed methods consider the voltage-temperature feedback loop and the separate power rails of specific resource types to yield maximum power efficiency.

(2) We leverage the proposed flow of (1) to explore the *energy* consumption, whereby we trade-off the performance and power consumption to achieve the minimum energy point. This is desirable for a majority of edge and IoT applications for which total energy consumption is the utmost concern.

(3) Our approaches mentioned in (1) and (2) are deterministic, as they guarantee timing closure. Nonetheless, many use-cases such as image processing and machine learning applications can tolerate a certain level of computation errors, which gives an opportunity for voltage *over-scaling*. However, it needs an examination of applications under these non-ideal conditions to get a glimpse of produced error in the output. We propose a primary FPGA simulation framework to be able to evaluate an FPGA-mapped design under voltage-scaling, i.e., when the delay of resources vary. Using the proposed framework, we map demonstrative machine learning applications into FPGA fabric and examine the impact of voltage *over-scaling* on extra power gain versus accuracy drop.

### 2.2 Background and Related Work

### 2.2.1 FPGA Architecture

Figure 2.1 illustrates the architecture of conventional tile-based FPGAs. The architecture comprises tiles of logic clusters (a.k.a CLBs or slices) that bind together using the configurable switch boxes (SBs) and connection blocks (CBs) to implement larger functions. Each logic CLB consists of N (e.g., N = 10) K-input look-up tables (LUTs) each of which is capable to implement Boolean expressions up to K variables. SB multiplexers are located in the intersection of horizontal and vertical channels (wire tracks) to enable connectivity and bending of nets.

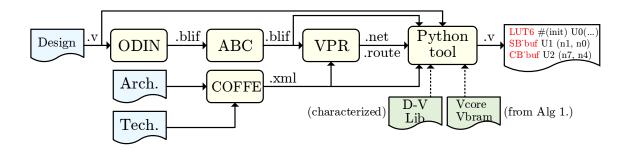

Figure 2.1: Tile-based FPGA architecture (left), and building blocks (right) [1].

These multiplexers are also responsible for connecting outputs of logic resources (LUTs, FFs, carry chain, etc.) to global routing, i.e., to horizontal and vertical channels. Analogously, CB multiplexers pass the selected global wires into the logic clusters. Specific FPGA columns are repetitively dedicated to Block RAMs and DSP cores. The majority of logic and routing resources have a multiplexer-like structure, mainly implemented as two-stage multiplexers that have been shown to provide optimal area-delay efficiency [50]. These resources often drive large loads, especially the global routing resources that have a high number of long fanout wires, so are augmented with large output buffers to improve performance.

### 2.2.2 Related Work

While many previous studies have attempted to reduce FPGA power dissipation by power-gating, conventional DVFS, configurable dual supply voltage, control of signal levels, architectural innovations, etc. [51], there are limited number of works that leverage the available

timing margin to reduce voltage without scarifying performance. Authors of [52] explore the timing headroom of FPGA-mapped designs by gradually reducing the voltage (keeping the frequency fixed) until observing the error. They detect the error by inserting a shadow register per each CP with a phase-shifted clock to detect the data mismatch caused by voltage reduction. As there are a huge number of CP and near-CP paths in a large synthesis-flattened design, the area and power overhead of this technique can be excessive. Also, measuring the slack in this technique depends on capturing the signal traversing the CP, while the CP may not be controllable at the runtime. Furthermore, the introduced capture registers cannot be used for paths that head to hard blocks such as BRAM. The study in [53] addresses the latter issue by replicating such paths and inserting an end-point proxy register (instead of the hard block) where an error-detector circuitry checks timing violations. However, the error-detector itself imposes delay, so a timing error raised in the original CP might propagate into the memory before being detected.

In [54], the authors propose a two-step self-calibrating voltage scaling scheme by exploiting the available timing slack of thermal margin. CPs of a design are extracted by using the STA tool and are then implemented on the FPGA fabric. Afterward, for different values of temperature and core voltage (T and  $V_{core}$ ), the maximum frequency is obtained by gradually increasing it until error is observed by the implemented error-detection circuit. This approach does not consider the thermal distribution within the chip [55] where a CP may experience varied temperature in reality. This either results in timing violation by ignoring the parts of CP that resides in hot (hence, slower) tiles, or gives non-optimal results if a related thermal margin is considered. In addition, the STA tool reports the CPs according to worst-case condition while CPs might change at lower temperatures. Thus a larger number of near-CP paths need to evaluate which makes the entire process further cumbersome. BRAM and soft-logic voltage rails also are not separately considered, so the minimum employed voltage will be limited by the one that violates the timing first.

Finally, recent work in [56] examines the voltage scaling of FPGA BRAMs. The authors

showed that up to 39% of BRAM voltage can be reduced without observing any error. Though it is promising in reducing the power of BRAMs by one order of magnitude, a trial-and-error based approach does not guarantee correct functionality as it is infeasible to examine all the inputs. Moreover, the overall efficiency is limited to power of BRAMs.

Aforementioned techniques are all speculative as they decrease the voltage until observing error. This overlooks errors that emerge gradually due to violating the guardbands (e.g., timing error as a result of degradation [57]) or may arise abruptly due to voltage transients [29]. Recently, work in [29] showed a margin over 36% is needed for voltage transients as a result of load transients, and this margin is already considered in STA tools. Nevertheless, as voltage transients occur infrequently, the speculative voltage scaling methods do not take them into consideration, which will lead to timing violation at certain conditions. Our voltage scaling approach is different from previous studies as we incorporate it in the FPGA design flow by characterizing the resources during FPGA architecting. This eliminates the arduous task of voltage-timing speculation and guarantees timing. Our method precisely considers the correlation of temperature, delay, voltage, and power of resources and separate power rails of soft-fabric and memories, so it yields maximum efficiency by setting the optimal core and BRAM voltages as well as accurately estimating the timing according to the thermal distribution of the blocks. Finally, *over-scaling* of voltages needs timing simulation to observe the impact of timing violations. We enable it by our novel FPGA simulation flow.

### 2.3 Proposed Method

### 2.3.1 Preliminary

FPGA flow is different from conventional standard-cell based design of ASICs, thus we first elaborate the setup of experiments used in the rest of the chapter before detailing the proposed method.

• Power and Delay. We use circuit-level simulations to obtain the delay and power of FPGA resources. For this end, we use the latest version of COFFE [58] that generates and characterizes an accurate netlist of FPGA resources according to the given architectural description using comprehensive circuit-level HSPICE simulations. Besides the description of the target FPGA architecture, COFFE also requires technology process of transistors, for which we use 22nm predictive technology model (PTM) [59]. COFFE also generates and evaluates the memory blocks of FPGA and has been shown to have a suitable delay and exact area match with commercial FPGAs [60]. Similar to configuration SRAM cells, the core of the memory blocks (i.e., eight-transistor dual-port SRAM cells) is implemented by 22nm high-threshold low-power transistors [61], which throttles their leakage power by two orders of magnitude. As we will show in the rest of this chapter, our simulations show a similar power trend to commercial FPGAs.

COFFE does not model DSP blocks. We thus develop the DSP HDL code based on the Stratix IV description [62] and characterize it using Synopsys Design Compiler with NanGate 45nm open cell library [63]. Then we scale the results to 22nm based on measuring scaling factors of a selected set of cells at 45nm and 22nm technologies. Based on PrimeTime report, the developed DSP consumes 4.6mW at 250MHz, which is comparable to a 28nm DSP that dissipates 5.6mW at the same frequency [64]. To characterize the delay and power of programmable resources at different temperature and voltages, we sweep the parameters of COFFE-generated netlists in HSPICE simulations. For DSP, we create a set of standard-cell libraries using NanGate netlists by the means of Synopsys SiliconSmart so we could characterize the DSP at different operating conditions.

• **FPGA Flow.** We use VTR 7.0 (Verilog-to-Routing) [65] toolchain that enables defining a customized FPGA architecture and place and route the benchmarks. We use FPGA architecture parameters similar to Intel Stratix devices [66, 1] in COFFE and VPR<sup>1</sup> placement and routing, which is summarized in Table 2.1. COFFE uses these parameters to generate SPICE netlist and

<sup>&</sup>lt;sup>1</sup>VPR (Versatile Place and Route) is the P&R tool in VTR toolchain.

| Parameter             | Value | Parameter                       | Value                |

|-----------------------|-------|---------------------------------|----------------------|

| К                     | 6     | $SB_{mux}$ size                 | 12                   |

| Ν                     | 10    | $CB_{mux}$ size                 | 64                   |

| Channel tracks        | 240   | <i>local<sub>mux</sub></i> size | 25                   |

| Wire segment length   | 4     | $V_{core}, V_{bram}$            | 0.8V, 0.95V          |