## **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

## **Title**

Whole-Chip ESD CAD Tools and Scalable ESD Device Modeling Methodology

### **Permalink**

https://escholarship.org/uc/item/4r60g2gx

### **Author**

Wang, LI

## **Publication Date**

2015

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Whole-Chip ESD CAD Tools and Scalable ESD Device Modeling Methodology

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Li Wang

June 2015

Dissertation Committee:

Dr. Albert Wang, Chairperson

Dr. Jianlin Liu

Dr. Sheldon Tan

| The Dis | ssertation of Li Wang is approved: |                       |

|---------|------------------------------------|-----------------------|

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    |                       |

|         |                                    | Committee Chairperson |

University of California, Riverside

## Acknowledgements

First of all, I want to extend my sincerest gratitude to my advisor, Dr. Albert Wang, who have given me the support, guidance and encouragement during my Ph.D. studies. His profound knowledge, unique perspective and rigorous attitude in research have inspired and guided me to complete my PhD research. Without his advice and patience, this work would not have been possible.

I would like to thank my dissertation committee members: Prof. Jianlin Liu, Prof. Sheldon Tan and Prof. Albert Wang, for their enthusiastic guidance on my dissertation research. I would like to thank all my graduate friends, especially the group members at LICS lab at UC Riverside, Xin Wang, Hui Zhao, Zitao Shi, Jian Liu, Qiang Fan, Zongyu Dong, Chen Zhang, Rui Ma, and Fei Lu. I learnt a lot from them and enjoyed the time with them together.

I wish to express my deepest gratitude to my beloved families: my parents, my husband and my baby, for their endless love to me. Their love and encourage have been with me throughout my PhD study period.

Lastly, I offer my best regards to all of those who supported me in any aspect during my Ph.D. studies.

To my family for all the supports.

#### ABSTRACT OF THE DISSERTATION

Whole-Chip ESD CAD Tools and Scalable ESD Device Modeling Methodology

by

#### Li Wang

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, June 2015 Dr. Albert Wang, Chairperson

Electrostatic discharge (ESD) failure is a major reliability problem to integrated circuits (IC). On-chip ESD protection is mandatory for all IC chips to protect against any possible ESD damages. Therefore, Whole-chip ESD protection circuit simulation is essential to chip-level ESD protection design synthesis, optimization, verification and prediction. Today, trial-and-error approaches still dominate in practical ESD circuit designs due to lack of full-chip ESD simulation tools and accurate ESD device modeling technique.

This thesis reports a new chip-level ESD CAD tool, which can accurately extract ESD devices from layout files, generate an ESD netlist, simulate ESD discharge function at chip level and conduct full-chip ESD zapping test simulation. This CAD tool is designed with several unique algorithms and a smart ESD parametric checking mechanism, which takes full consideration of ESD protection operation principles. Therefore, this new CAD tool is different from existing simple ESD spacing and bus resistance checking approaches, and can achieve whole-chip ESD protection verification and prediction. The CAD tool consists of three modules: an ESD device extraction

module, an ESD design inspection module and an ESD zapping test module. The ESD extraction module can accurately extract arbitrary ESD protection structures at full chip level. Decomposed-based subgraph isomorphism algorithm is used for ESD device extraction to improve time efficiency. The ESD design inspection module serves to remove non-critical ESD devices extracted based upon a novel smart parametric checking mechanism. The ESD zapping test module is developed to perform complex ESD protection zapping test simulation using Dijkstra's algorithm to resolve the problem of finding the critical ESD discharging path at chip level. The new ESD CAD tool was verified at full chip level using ESD protection designs implemented in 0.35 µm BiCMOS technology.

ESD device models were reported for traditional diode and MOSFET type ESD structures. However, due to complex ESD behaviors, particularly the electro-thermal-process-device-circuit-layout coupling effects, the existing ESD models have limited accuracy in describing complex ESD physics and coupling effects, such as thermal boundary condition and snapback I-V behavior.

This thesis presents a new scalable ESD behavioral modeling technique, which uses Verilog-A to develop accurate ESD behavior models for various ESD protection structures, such as novel nano crossbar ESD protection structures, novel 3D field-programmable ESD protection structures using SONOS and NCD ESD devices, silicon controlled rectifier (SCR) based ESD protection structures, HV diode and SCR ESD protection structures, 28nm CMOS gated diode and DTSCR ESD protection structures. The new scalable ESD behavior modeling technique was fully verified by SPICE circuit

simulation and transmission line pulse (TLP) ESD testing, which will enable whole-chip ESD circuit design optimization and verification.

Flip chip technique using ball grid array (BGA) pad-ring arrays is a popular technology for small footprint chips used in size-sensitive electronics. However, ESD protection design for ICs using large BGA pad-ring array is an emerging challenge since where to place an ESD structure becomes a real layout design problem.

This thesis reports design of a BGA pad-ring array with different ESD metal routing for a visible light communication (VLC) transceiver implemented in 180nm BCD technology at whole-chip level. The ESD structures and their ESD-critical parameters, and the ESD metal bus resistance were extracted by our ESD Extractor CAD tool. The new ESD behavior modeling technique was used to model the ESD structures. The extraction and modeling was validated by SPICE simulation and TLP testing for different ESD metal routing.

## **Contents**

| Chapte | r 1 Intro | oduction                                               | 1  |

|--------|-----------|--------------------------------------------------------|----|

| 1.1    | Backgro   | ound                                                   | 1  |

| 1.2    | Whole-    | chip ESD Protection Design Principle                   | 4  |

| 1.3    | ESD Pr    | otection Structure                                     | 8  |

|        | 1.3.1 D   | Piode                                                  | 9  |

|        | 1.3.2 D   | Piode String                                           | 11 |

|        | 1.3.3 G   | GMOS                                                   | 12 |

|        | 1.3.4 S   | CR                                                     | 13 |

| 1.4    | Design    | Overview of Whole-chip ESD Protection CAD and Modeling | 16 |

| 1.5    | Thesis (  | Organization                                           | 23 |

| Chapte | r 2 Who   | le-chip ESD CAD Tool                                   | 25 |

| 2.1    | Introduc  | ction                                                  | 25 |

| 2.2    | ESD Ex    | stractor                                               | 25 |

|        | 2.2.1     | Design Overview of ESD Extractor                       | 26 |

|        | 2.2.2     | Layout Processor                                       | 27 |

|        | 2.2.3     | Device Model Processor                                 | 29 |

|        | 2.2.4     | Device Recognition Algorithm                           | 31 |

| 2.3    | ESD Ins   | spector                                                | 38 |

|        | 2.3.1 D   | Design Overview of ESD Inspector                       | 38 |

|        | 2.3.2 S   | mart Parametric Checking Mechanism                     | 39 |

| 2.4    | ESD Za    | pper                                                   | 40 |

|        | 2.4.1 D   | Design Overview of ESD Zapper                          | 41 |

|        | 2.4.2 C   | ritical Discharging Path Algorithm                     | 42 |

| 2.5    | ESD CA    | AD Tool Application Example                            | 46 |

| Chapte | r 3 Scala | able ESD Protection Structure Behavior Modeling        | 52 |

| 3.1    | New Sc    | alable ESD Behavior Modeling                           | 52 |

| 3.2     | Novel 1   | Nano Crossbar ESD Device Model Method and Verification | 54         |

|---------|-----------|--------------------------------------------------------|------------|

|         | 3.2.1     | Novel Nano Crossbar ESD Protection                     | 54         |

|         | 3.2.2     | Nano Crossbar ESD Device Model Method                  | 57         |

|         | 3.2.3     | ESD Device Model Verification for Nano Crossbar        | 59         |

| 3.3     | SONO      | S ESD Protection Model Method and Verification         | 62         |

|         | 3.3.1 S   | SONOS ESD Protection                                   | 63         |

|         | 3.3.2 S   | SONOS ESD Device Model Method                          | 65         |

|         | 3.3.3 S   | SONOS ESD Device Model Verification                    | 67         |

| 3.4     | NCD E     | SD Protection Model Method and Verification            | 69         |

|         | 3.4.1 N   | NCD ESD Protection                                     | 69         |

|         | 3.4.2 N   | NCD ESD Device Model Method                            | 70         |

|         | 3.4.3 N   | NCD ESD Device Model Verification                      | 72         |

| 3.5     | SCR ba    | ased ESD Protection Model Method and Verification      | 74         |

|         | 3.5.1 I   | LVSCR ESD Protection Structure                         | <b>7</b> 4 |

|         | 3.5.2 I   | LVSCR ESD Device Model Method                          | 79         |

|         | 3.5.3 L   | LVSCR ESD Device Model Verification                    | 80         |

| 3.6     | HV ES     | D Protection Model Method and Verification             | 86         |

|         | 3.6.1 H   | HV ESD Protection Structure                            | 86         |

|         | 3.6.2 H   | IV ESD Device Model Method                             | 88         |

|         | 3.6.3 H   | HV ESD Device Model Verification                       | 89         |

| 3.7     | 28nm (    | CMOS ESD Protection Model Method and Verification      | 91         |

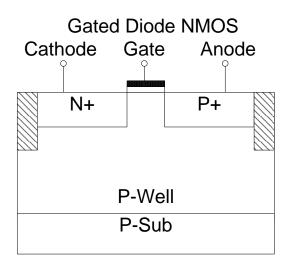

|         | 3.7.1 2   | 28nm CMOS ESD Protection Structure                     | 91         |

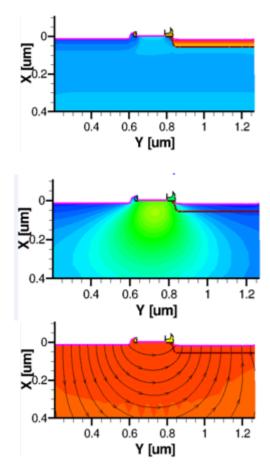

|         | 3.7.2 2   | 8nm CMOS ESD Device Model Method                       | 94         |

|         | 3.7.3 2   | 8nm CMOS ESD Device Model Verification                 | 95         |

| Chapte  | er 4 Desi | gn BGA Pad-Ring Array ESD Design Verification          | 98         |

| 4.1     | Introdu   | ction                                                  | 98         |

| 4.2     | ESD D     | esign Split and ESD Netlist Extraction                 | 100        |

| 4.3     | Full-Ch   | nip ESD Circuit Verification                           | 102        |

| Chapte  | er 5 Con  | clusions                                               | 109        |

| Referei | nce       |                                                        | 114        |

# **List of Figures**

| Figure 1.1 ESD damage to IC chips                                                                     | 1    |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 1.2 ESD induced damages: thermal breakdown and gate breakdown                                  | 3    |

| Figure 1.3 IC Technology Roadmap (from internet)                                                      | 4    |

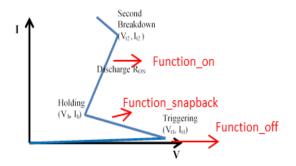

| Figure 1.4 Typical discharging I-V curves for ESD protection structures (a) simply to on (b) snapback |      |

| Figure 1.5 ESD Protection Design Window                                                               | 6    |

| Figure 1.6 Full-chip ESD protection scheme                                                            | 8    |

| Figure 1.7 STI Diode N+PW cross-section                                                               | 9    |

| Figure 1.8 Gated Diode N+PW cross-section                                                             | . 10 |

| Figure 1.9 ESD discharge path for N+/Pwell STI (L) and poly-gated (R) diode                           | . 10 |

| Figure 1.10 Diode string (N=2) cross-section                                                          | . 11 |

| Figure 1.11 GGNMOS cross-section                                                                      | . 12 |

| Figure 1.12 SCR cross-section                                                                         | . 14 |

| Figure 1.13 LVSCR cross-section                                                                       | . 15 |

| Figure 1.14 DTSCR cross-section with 3 trigger diodes.                                                | . 16 |

| Figure 1.15 Illustration of the Whole-chip ESD CAD Tool                                               | . 18 |

| Figure 1.16 HBM current waveform                                                                      | . 19 |

| Figure 1.17 A flow chart of ESD behavior modeling.                                                    | . 21 |

| Figure 2.1 Flow chart for ESD Extractor                                                               | . 25 |

| Figure 2.2 Layout processing example                                                                  | . 26 |

| Figure 2.3 TG for the layout design example in Figure 2.2                                             | 27   |

| Figure 2.4 GGNMOS (a) cross-section (b) layout (c) MG definition                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.5 SCR (a) cross-section (b) MG definition                                                                                                |

| Figure 2.6 (a) LVSCR cross-section, (b) GGNMOS cross-section                                                                                      |

| Figure 2.7 Flow char of Decomposition procedure                                                                                                   |

| Figure 2.8 Model Decomposition Procedure for GGNMOS and LVSCR                                                                                     |

| Figure 2.9 Flow chart of Device Recognition procedure                                                                                             |

| Figure 2.10 Flow chart for ESD Extractor and ESD Inspector                                                                                        |

| Figure 2.11 whole chip ESD stress scenario                                                                                                        |

| Figure 2.12 Flow chart for ESD zapper                                                                                                             |

| Figure 2.13 Example for (a) ESD protection circuit (b) transformed weighted graph 42                                                              |

| Figure 2.14 Flow chart of Dijkstra's algorithm                                                                                                    |

| Figure 2.15 Model Graph Definition for LVSCR                                                                                                      |

| Figure 2.16 layout of an ESD protection circuit example                                                                                           |

| Figure 2.17 Extraction results in the graphical format                                                                                            |

| Figure 2.18 Extraction results in the text format                                                                                                 |

| Figure 2.19 (a) Intermedia netlist (b) Final netlist                                                                                              |

| Figure 2.20 two possible discharge path from VDD to GND                                                                                           |

| Figure 2.21 Critical discharge path between VDD and GND (a) graphical output(b) tex output                                                        |

| Figure 3.1 Flow chart for developing behavior models by Verilog-A                                                                                 |

| Figure 3.2 Partition TLP curve into sections per ESD discharging functions                                                                        |

| Figure 3.3 The circuit level ESD simulation schematic used to verify the new nESD behavior models                                                 |

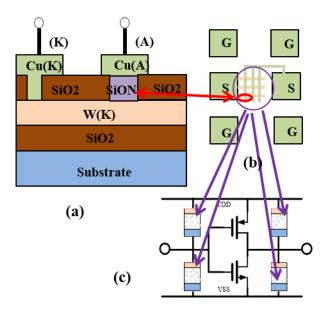

| Figure 3.4 New nano crossbar ESD protection structure and circuit scheme: (a) Cross-section, (b) 3X3 ESD array, (c) on-chip ESD protection scheme |

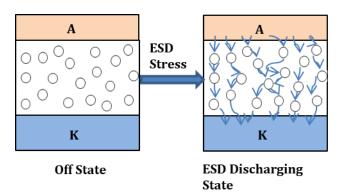

| Figure 3.5 New nano crossbar ESD dispersed local tunneling model                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

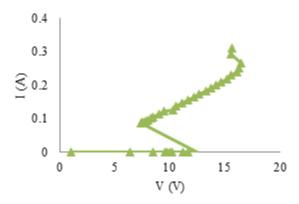

| Figure 3.6 Measured snapback I-V curve for a nano crossbar single-node ESD device with node area of $5\mu m X 5\mu m$ by TLP testing                                                         |

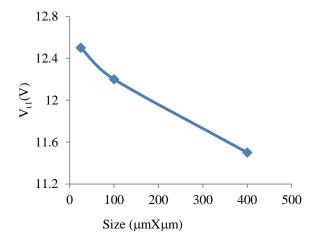

| Figure 3.7 Measured Vt1 v.s. device size for nano crossbar ESD structures                                                                                                                    |

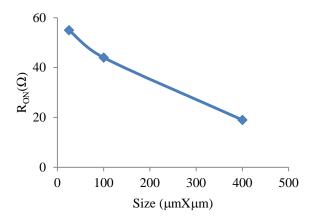

| Figure 3.8 Measured ESD RON v.s. size for nano ESD devices                                                                                                                                   |

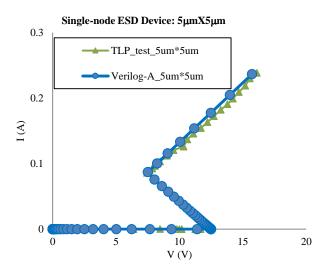

| Figure 3.9 SPICE simulation for a single-node nano crossbar ESD device (area size $5\mu mX5\mu m$ ) using the new ESD bahavior model matches the TLP testing result well 58                  |

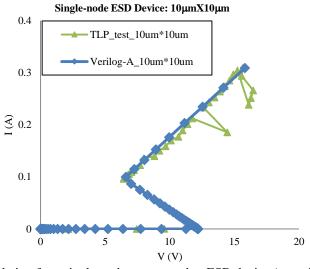

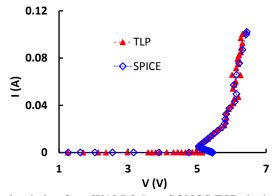

| Figure 3.10 SPICE simulation for a single-node nano crossbar ESD device (area size $10\mu mX10\mu m$ ) using the new ESD bahavior model matches the TLP testing result well 59               |

| Figure 3.11 SPICE simulation for a single-node nano crossbar ESD device (area size $20\mu mX20\mu m$ ) using the new ESD bahavior model matches the TLP testing result well 59               |

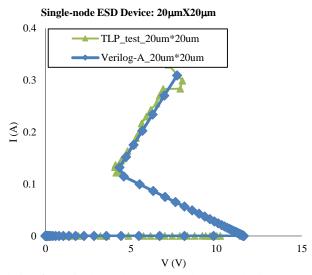

| Figure 3.12 SPICE simulation for an nano crossbar array ESD protection circuit (node area: 10µmX10µm, array size: 3X3) using the new ESD bahavior model matches the TLP testing result well. |

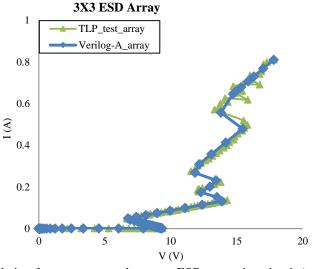

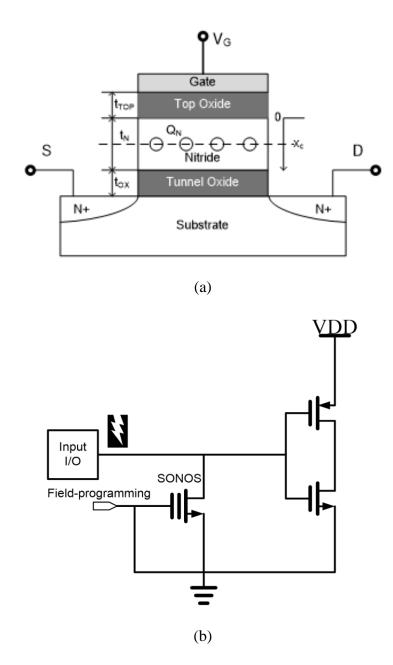

| Figure 3.13 SONOS (a) field-programmable ESD protection structure concepts, and ESD protection circuit scheme (b)                                                                            |

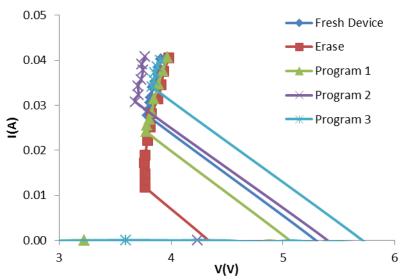

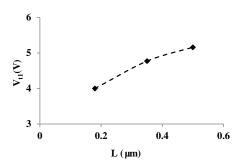

| Figure 3.14 Measured ESD I-V curves by TLP for SONOS                                                                                                                                         |

| Figure 3.15 Measured Vt1 versus device size for sample SONOS ESD structures 63                                                                                                               |

| Figure 3.16 TLP curve partition for a W10/L0.5µm SONOS ESD device                                                                                                                            |

| Figure 3.17 SPICE circuit simulation for a W10/L0.18µm SONOS ESD device using ESD behavior model matches TLP testing curve well                                                              |

| Figure 3.18 SPICE circuit simulation for a W10/L0.5µm SONOS ESD device using ESD behavior model matches TLP testing curve well                                                               |

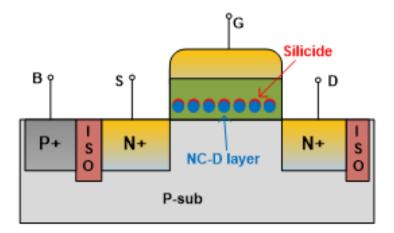

| Figure 3.19 NCD field-programmable ESD protection structure concepts                                                                                                                         |

| Figure 3.20 Measured ESD I-V curves by TLP for NCD                                                                                                                                           |

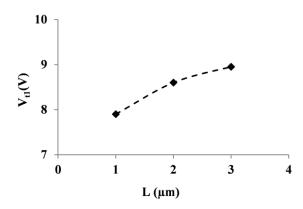

| Figure 3.21 Measured Vt1 versus device size for sample NCD ESD structures 68                                                                                                                 |

| Figure 3.22 TLP curve partition for a W100/L1µm NCD ESD device                                                                                                                               |

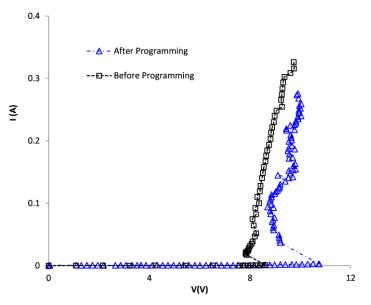

| Figure 3.23 SPICE circuit simulation for a W100/L1µm NCD ESD device using ESD behavior model matches TLP testing curve well (Fresh)                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.24 SPICE circuit simulation for a W100/L2µm NCD ESD device using ESD behavior model matches TLP testing curve well (before programming)                                                                             |

| Figure 3.25 SPICE simulation for a W100/L2µm NCD ESD device (Fig. 3.24) using behavior model matches TLP testing curve well (after programming)                                                                              |

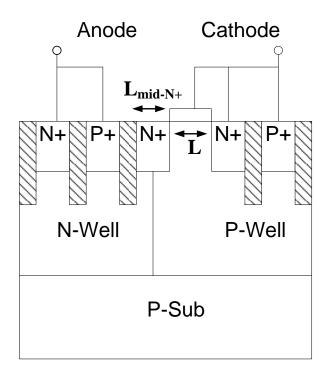

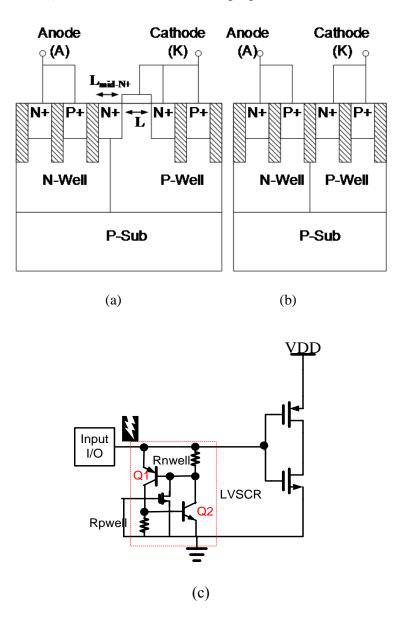

| Figure 3.26 LVSCR (a) versus SCR (b) ESD structure(L is NMOS channel length and Lmid-N+ is length for N+ across Pwell/Nwell), and equivalent circuit model and on-chip ESD protection circuit scheme for LVSCR structure (c) |

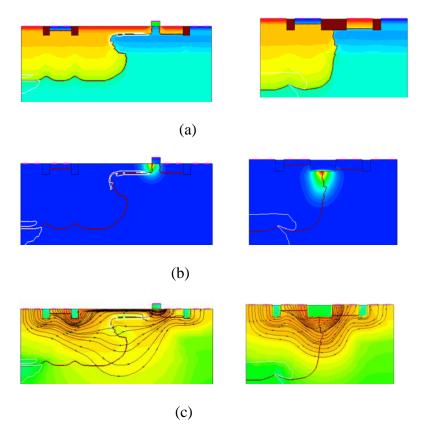

| Figure 3.27 Simulated (a) cross-section, (b) temperature contours and heating effect, and (c) ESD discharging current flows for NMOS-LVSCR (Left) and SCR (Right) ESD protection structures under the same ESD stressing     |

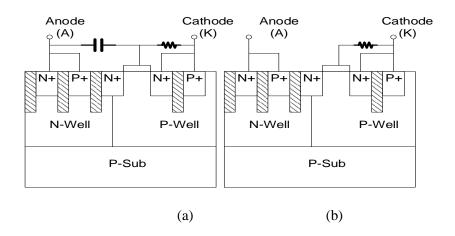

| Figure 3.28 (a) Schematic for RC-coupled LVSCR, (b) schematic of gate-resistor LVSCR                                                                                                                                         |

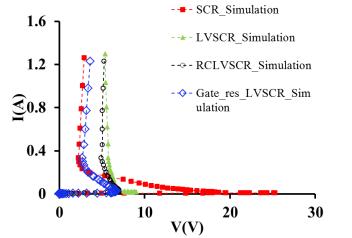

| Figure 3.29 Simulated transient ESD discharging I-V curves for SCR, NMOS-LVSCR(L0.35 $\mu$ m/Lmid-N+3 $\mu$ m), RC-coupled LVSCR(L0.35 $\mu$ m/Lmid-N+3 $\mu$ m) and gate-resistor LVSCR(L0.35 $\mu$ m/Lmid-N+1 $\mu$ m)     |

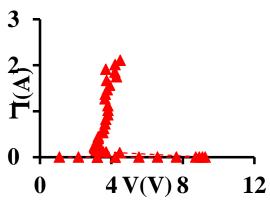

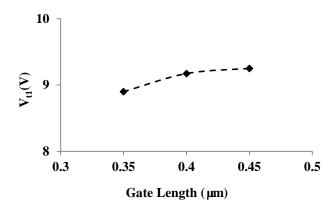

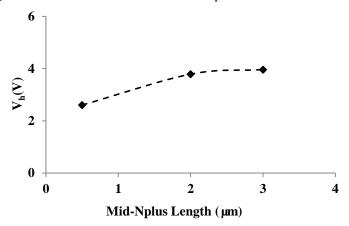

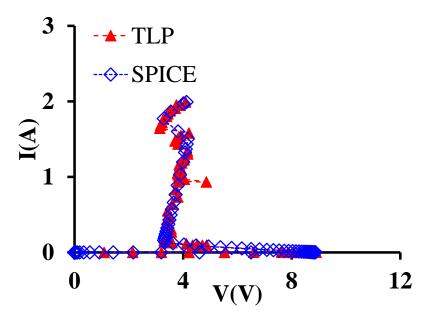

| Figure 3.30 Measured snapback I-V curve for a sample NMOS-LVSCR ESD device featuring W/L/Lmid-N+=30/0.45/1µm by TLP testing                                                                                                  |

| Figure 3.31 Measured Vt1 versus L for sample LVSCR ESD structures                                                                                                                                                            |

| Figure 3.32 Measured Vh versus mid-N+ length for sample LVSCR ESD devices 76                                                                                                                                                 |

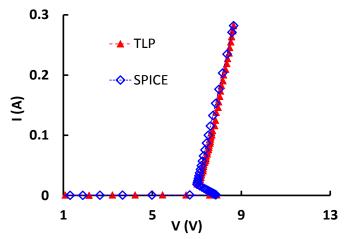

| Figure 3.33 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= $30/0.35/1\mu m$                                                                      |

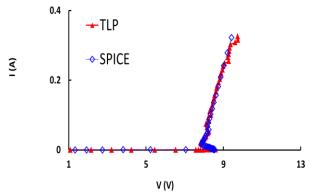

| Figure 3.34 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= $30/0.4/1\mu m$                                                                       |

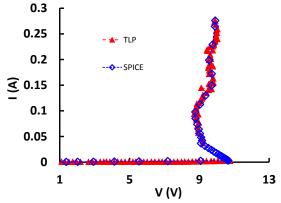

| Figure 3.35 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= $30/0.45/1\mu m$                                                                      |

| Figure 3.36 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= $30/0.35/0.5\mu m$                                                                    |

| Figure 3.37 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= 30/0.35/2µm79                                                                         |

| Figure 3.38 SPICE circuit simulation using behavior model matches TLP testing well for a sample LVSCR structure featuring W/L/Lmid-N+= $30/0.35/3\mu m$                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.39 SPICE circuit simulation using behavior model matches TLP testing well for a sample RC-coupled LVSCR structure featuring W/L/Lmid-N+=90/0.35/3 $\mu$ m, C=1pF and R=10K $\Omega$ . |

| Figure 3.40 SPICE circuit simulation using behavior model matches TLP testing well for a sample gate-R LVSCR structure featuring W/L/Lmid-N+=30/0.35/1 $\mu$ m and R=100K $\Omega$             |

| Figure 3.41 The whole-chip HV ESD protection scheme in this design consists of HV ESD diodes at I/O and stacked bi-directional SCR ESD power clamp                                             |

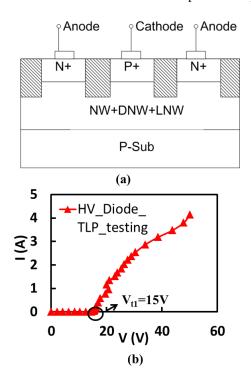

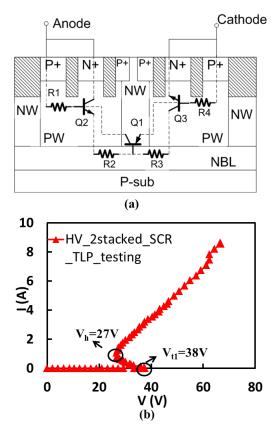

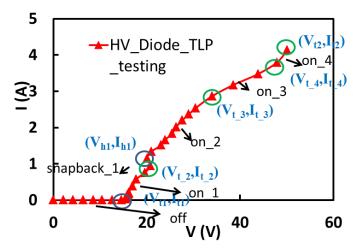

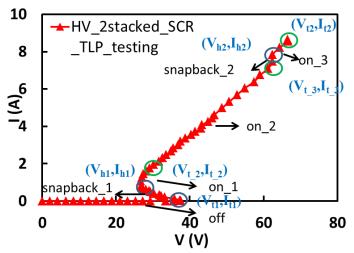

| Figure 3.42 A cross-section (a) and measured ESD I-V curve by transmission line pulse (TLP) testing (b) for the HV ESD diode                                                                   |

| Figure 3.43 A cross-section (a) and measured ESD I-V curve by TLP testing (b) for the 2-stacked SCR HV power clamp                                                                             |

| Figure 3.44 The measured, by TLP testing, ESD I-V curve for the HV I/O ESD diode is partitioned for ESD behavior modeling                                                                      |

| Figure 3.45 The measured, by TLP testing, ESD I-V curve for the 2-stacked SCR HV power clamp is partitioned for ESD behavior modeling                                                          |

| Figure 3.46 SPICE circuit simulation for a sample HV diode ESD device matches the TLP testing curve well                                                                                       |

| Figure 3.47 SPICE circuit simulation for a sample HV 2-stacked SCR ESD device matches the TLP testing curve well                                                                               |

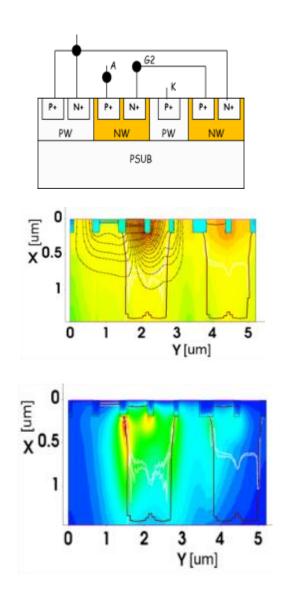

| Figure 3.48 Gated diode cross-section                                                                                                                                                          |

| Figure 3.49 Simulation reveals ESD behaviors for gated diode ESD structures: X-section (upper), temperature contours and heating effect (middle), and ESD discharging current flows (lower)    |

| Figure 3.50 X-section of a sample DTSCR ESD structure (upper) and its simulated ESD discharging current flow (middle) and temperature contours (lower)                                         |

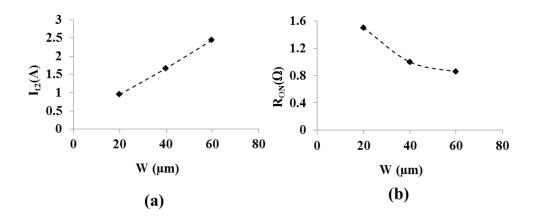

| Figure 3.51 Measured It2 (a) and RON (b) for sample N+PW gated diodes ESD devices of varying sizes (W) by TLP testing                                                                          |

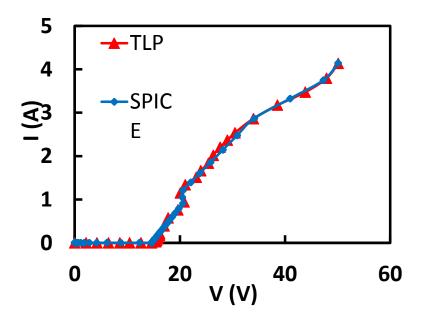

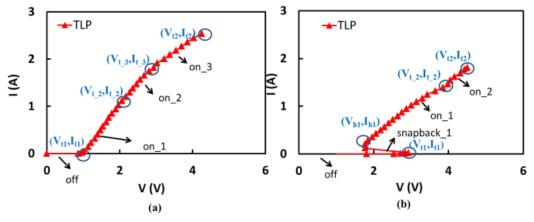

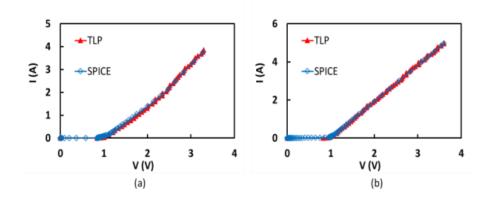

| Figure 3.52 Partitioning transient ESD I-V curves from TLP testing for ESD behavior modeling for sample (a) N+PW gated diode and (b) DTSCR                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

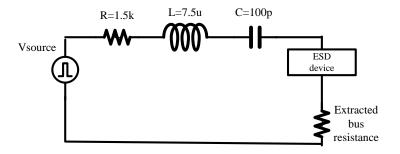

| Figure 3.53 A HBM ESD test equivalent circuit for ESD circuit simulation                                                                                                                                                               |

| Figure 3.54 SPICE ESD circuit simulation using the extracted ESD behavioral models matches ESD TLP testing curves well for sample N+PW gated diode: (a) W/L=100 $\mu$ m/0.54 $\mu$ m (HBM 3KV), and (b) 120 $\mu$ m/0.54 $\mu$ m (4KV) |

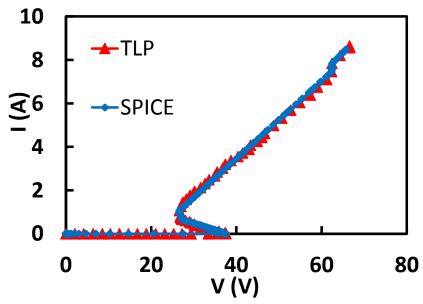

| Figure 3.55 SPICE ESD circuit simulation using the extracted ESD behavioral models matches ESD TLP testing curve well for a sample DTSCR (W=50 $\mu$ m, 2KV)93                                                                         |

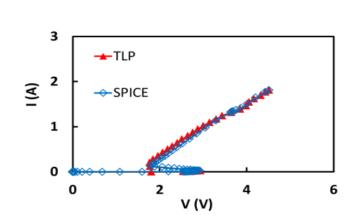

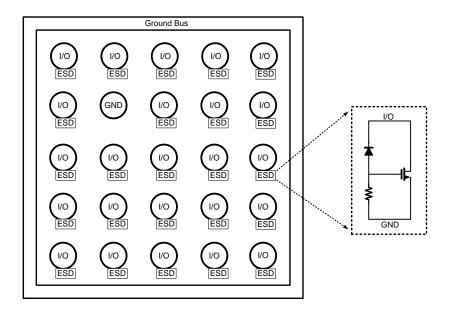

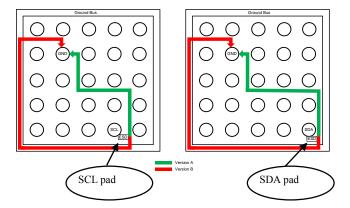

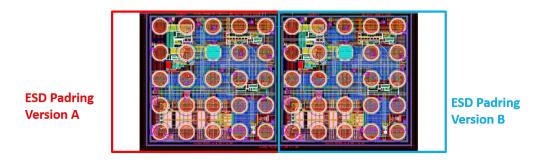

| Figure 4.1 Illustration of BGA pad-ring array (Upper) used for flip-chip based VLC transceiver (Lower) in this design                                                                                                                  |

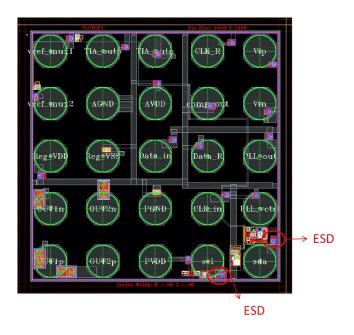

| Figure 4.2 Two ESD metal route splits were designed between a given IO pad and a fixed GND pad in the flip-chip VLC IC showing two possible ESD current discharging paths for ESD route A and B in this design                         |

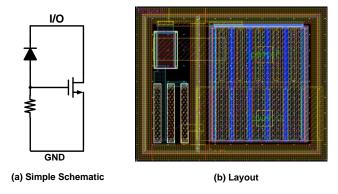

| Figure 4.3 Schematic and layout for a gcNMOS ESD protection structure used for the digital and analog domain in this design                                                                                                            |

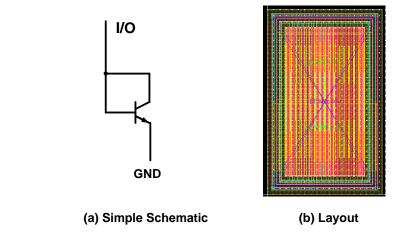

| Figure 4.4 Schematic and layout for ESD protection in power domains used in this design98                                                                                                                                              |

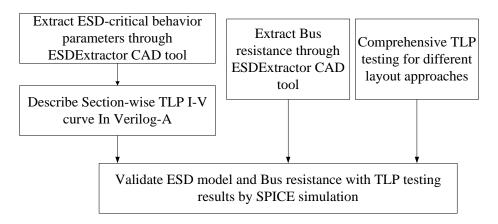

| Figure 4.5 A flow chart for ESD behavior model and ESD bus resistance extraction and validation                                                                                                                                        |

| Figure 4.6 The VLC die diagram shows the ESD metal path splits (i.e., path A and path B) in the BGA pad-ring array                                                                                                                     |

| Figure 4.7 Layout floorplan for one VLC IC split where each PI pad has its own ESD device integrated                                                                                                                                   |

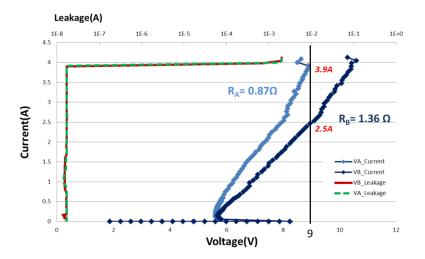

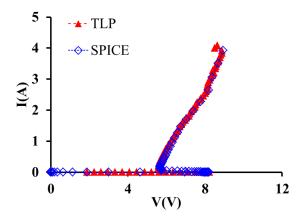

| Figure 4.8 SCL ESD TLP testing results with version A (VA) and version B (VB) 101                                                                                                                                                      |

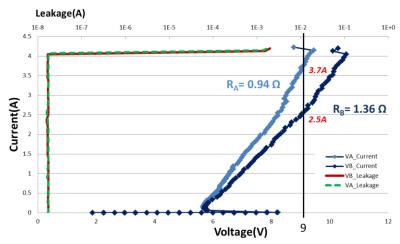

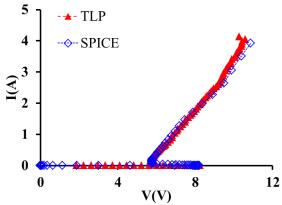

| Figure 4.9 SDA ESD TLP testing results with version A (VA) and version B (VB) 101                                                                                                                                                      |

| Figure 4.10 Schematic for HBM ESD circuit simulation for ESD protection circuit including ESD device and ESD metal path resistance                                                                                                     |

| Figure 4.11 SPICE ESD circuit simulation matches TLP testing well for the design split of SCL-GND with ESD metal route Version A                                                                                                       |

| Figure 4.12 SPICE ESD circuit simulation matches TLP testing well for the design split of SCL-GND with ESD metal route Version B                                                                                                       |

| Figure 4.13 SPICE ESD circuit simulation matches TLP testing well for | the design split |

|-----------------------------------------------------------------------|------------------|

| of SDA-GND with ESD metal route Version A                             | 103              |

|                                                                       |                  |

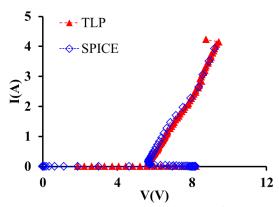

| Figure 4.14 SPICE ESD circuit simulation matches TLP testing well for | the design split |

| of SDA-GND with ESD metal route Version B                             | 104              |

## **List of Tables**

| Table 3.1 TLP Results for Different Nano Esd Devices                                         | . 55 |

|----------------------------------------------------------------------------------------------|------|

| Table 3.2 Measured ΔVt1 for sample SONOS ESD devices                                         | . 62 |

| Table 3.3 Measured ΔVt1 for sample NCD ESD device                                            | . 67 |

| Table 4.1 Extracted ESD-critical parameters and ESD bus resistance for ESD metal round and B |      |

## **Chapter 1 Introduction**

## 1.1 Background

ESD (electrostatic discharge) phenomenon originates from transfer of static electric charges between two objects with different electrostatic potentials as they are brought into contact [1]. Figure 1.1 shows one of the most-widely ESD scenario, where the human body discharging current to IC parts. This process usually lasts several hundred nanoseconds and the peak current could reach to several amperes. The heat produced by the human body discharging current will cause thermal breakdown damage in the IC parts if there're no proper on-chip ESD protection structures [48].

Figure 1.1 ESD damage to IC chips

In the past few years, up to billions of dollars loss is caused by ESD damage in IC (integrated circuit) industry every year, since the ESD resulting large voltage and current surges may cause severe damages to IC parts. Therefore, ESD failure is becoming a major reliability problem to IC chips, which have gained wide research interests from both academic and industry.

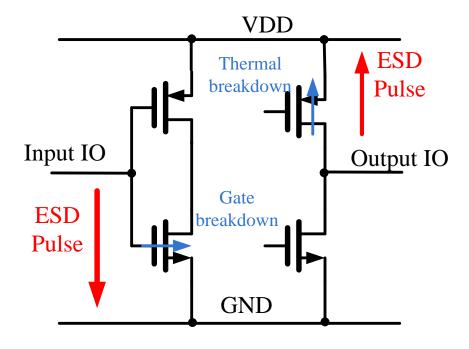

There're two types of ESD induced damages: thermal breakdown due to high current, and MOSFET gate dielectric rupture due to excess electric field, both of which are the catastrophic failures. Figure 1.2 shows two kinds of ESD induced damages, including thermal breakdown which often happens on the output IO, and gate breakdown which often happens at the input IO since the gate is directly faced to the ESD pulse. Hence, on-chip ESD protection is mandatory for all IC chips to protect against any possible ESD damages [2]. In principle, on-chip ESD protection is implemented in the way that an ESD protection unit is connected between a pair of IC pins such as I/O to ground (GND). The ESD protection structure remains off in normal IC operation. When an ESD transient appears at the I/O pin, it will trigger the ESD protection circuit and form a low-impedance shunting path to discharge the high ESD current efficiently. ESD protection is provided since not too much heat is generated and I/O voltage is clamped to a sufficiently low level to avoid any dielectric rupture.

Figure 1.2 ESD induced damages: thermal breakdown and gate breakdown

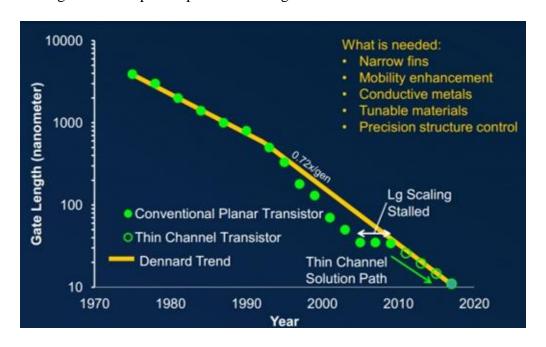

As IC technologies continue advance into very-deep-sub-micron (VDSM) domain as shown in Figure 1.3, on-chip ESD protection circuit design becomes increasingly more challenging particularly for parasitic sensitive analog, mixed-signal (AMS) and multi-GHz RF ICs [3, 4]. There are many challenges remain to be addressed in ESD protection designs, including CAD based ESD protection design methodology for design prediction and optimization, ESD-RFIC co-design, accurate high current ESD device modeling, low-parasitic ESD protection for RF/AMS ICs, accurate RF ESD design characterization, and ESD protection for nano systems, and so on [52]. However, whole-chip ESD protection design verification CAD tools and accurate high-current ESD device modeling are in urgent demand because the experience-based trial-and-error ESD protection design approaches, which are both time-consuming and exceedingly expensive, are becoming intolerable to today's design of complex chips with large number of I/O

pins and strong influences between ESD protection and the core IC protected [3]. A working stand-alone ESD protection unit does not warrant chip level ESD operation because parasitic devices inside the core circuit has the potential of becoming an unexpected shunting path, which will cause ESD failure. It usually takes average two or three times for an experienced circuit designer to complete a successful ESD protection design. The demand for 1st–Si success to meet the critical time-to-market requirement in industrial designs will not be possible without CAD-based whole-chip ESD protection design verification and accurate high-current ESD device modeling. In all, novel whole-chip ESD verification CAD tool and accurate high-current ESD device modeling are the biggest challenges in on-chip ESD protection designs.

Figure 1.3 IC Technology Roadmap (from internet)

### 1.2 Whole-chip ESD Protection Design Principle

The principle of ESD protection is two ways: one is to discharge high ESD current through a low impedance path, and the other is to clamp voltage to a low level.

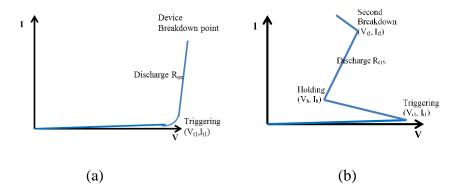

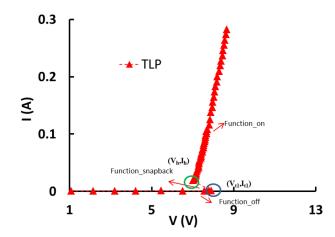

The typical discharging I-V curves of ESD protection structures are shown in Figure 1.4 (a) simply turn-on type (b) snapback type.

Figure 1.4 Typical discharging I-V curves for ESD protection structures (a) simply turn-on (b) snapback

The simply turn-on type ESD protection structure will be triggered to discharge ESD current after the device voltage reaches its turn-on voltage ( $V_{t1}$ ) as depicted in Figure 1.4 (a). "On-resistance" ( $R_{on}$ ) indicates the discharging resistance of the I-V curve. The ESD protection structure could provide lower clamping voltage when the  $R_{on}$  is lower. The ESD protection structure will breakdown, when the ESD current exceeds its ESD current protection ability.

The second solution is based on the snapback I-V curve shown in shown in Figure 1.4 (b). When the ESD voltage stress on this type of ESD protection structure reaches its triggering voltage ( $V_{t1}$ ), it will firstly go into a state of negative resistance, which is called snapback, until the device voltage reduces to the holding voltage ( $V_h$ ). The holding voltage  $V_h$  will clamp the ESD voltage on device to a sufficiently low level and hence protect the inner circuits from dielectric breakdown. The ESD protection structure begins

to discharge ESD current in a low- $R_{on}$  state until it reaches the second breakdown ( $V_{t2}$ ,  $I_{t2}$ ) after the holding voltage.

The triggering voltage, current and time  $(V_{t1}, I_{t1} \text{ and } t_1)$ , holding voltage and current  $(V_h \text{ and } I_h)$ , discharging on-resistance  $(R_{on})$ , second breakdown voltage and current  $(V_{t2}, I_{t2})$ , are all critical parameters for ESD protection structures. Proper ESD protection requires comprehensive design consideration for these ESD critical parameters in practices.

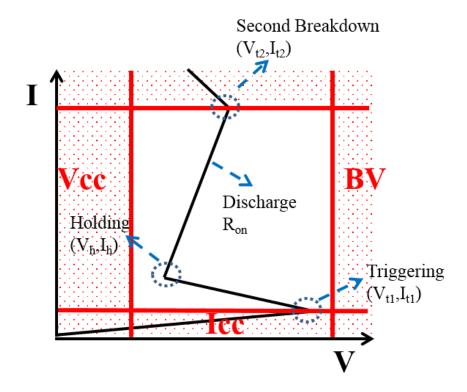

Figure 1.5 ESD Protection Design Window

The region between inner circuit breakdown voltage (BV) and power supply voltage ( $V_{CC}$ ), with current bounded by the total on-chip supply current ( $I_{CC}$ ), is called ESD Design Window as shown in Figure 1.5. Firstly, the  $V_{t1}$  of ESD protection structure

must be lower than the breakdown voltage of the protection node by a safety margin (at least 10%).  $V_{t1}$  also needs to be higher than  $V_{CC}$  since the ESD protection structure should be kept off during inner circuit normal operation. Secondly,  $V_h$  should be higher than the supply voltage ( $V_{CC}$ ) by a safety margin and  $I_h$  should be higher than the supply current ( $I_{CC}$ ) to avoid possible latch-up effect. The emerging challenge is that, this ESD design window becomes narrower when using traditional ESD protection structures as IC technologies continue to advance into sub-100nm domains [39]. Therefore, it is imperative to develop novel non-traditional ESD protection structures and triggering-assisting circuitry to satisfy the narrower ESD design window, which makes today's ESD protection design more complicated [43, 47]. As a result, whole-chip ESD protection design verification CAD tools and accurate high-current ESD device modeling are strongly needed to simulate the complicated ESD protection design and modeling the novel ESD protection structure.

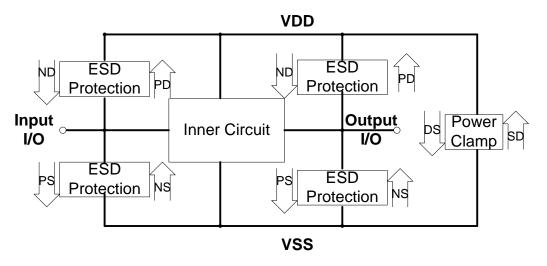

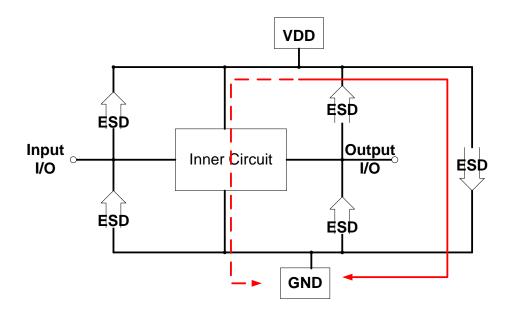

Moreover, ESD protection design is a whole-chip design task as opposed to designing stand-alone ESD protection devices. Ideally, a complete full-direction ESD protection solution is necessary for the whole IC chip as illustrated in Figure 1.6 for a mixed-signal chip, which consists of I/O ESD protection for each I/O pad, as well as a power clamp. The ESD protection in the circuit should provide ESD protections in the directions as follows to protect against all possible ESD pulse modes: positive ESD from I/O to VSS (PS), negative ESD from I/O to VSS (NS), positive ESD from I/O to VDD (PD), negative ESD from I/O to VDD (ND), positive ESD from VDD to VSS (DS) and positive ESD from VSS to VDD (SD). As a result, there is a low-impedance conducting

path from each pad to any other pads on the chip. However, full-chip complete ESD protection scheme may resulted in significant ESD-induced parasitic effects and large layout area used if traditional one-directional ESD protection devices are used. Hence, novel multi-directional ESD protection structures are desired [3] and so accurate high-current ESD device modeling are necessary for the novel multi-directional ESD protection structure.

Figure 1.6 Full-chip ESD protection scheme

#### 1.3 ESD Protection Structure

Various ESD protection structures have been developed and applied in different circuits and designs of IC technology. Commonly used ESD protection structures includes the simply turn-on type ESD protection structure in section 1.2, including STI diode, gated diode, and diode string, and snapback type ESD protection structure, including GGMOS (ground-gated MOS), SCR (silicon controlled rectifier), LVSCR (low voltage triggered SCR), DTSCR (diode triggered SCR) and so on.

### **1.3.1 Diode**

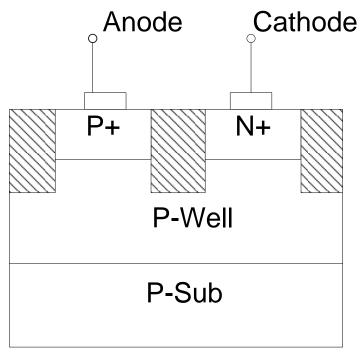

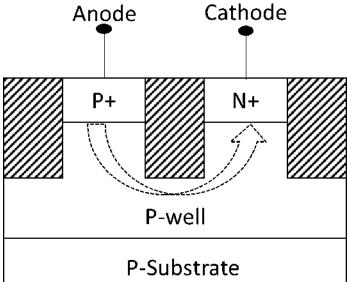

There're two types of diode: STI diode and gated diode. As shown in Figure 1.7, STI diode contains a PN junction, which is formed by N+/P-Well in CMOS IC process. The forward PN junction has low on resistance and so very high current handle ability. And its triggering voltage  $V_{t1}$  is as low as ~0.7V.

Figure 1.7 STI Diode N+PW cross-section

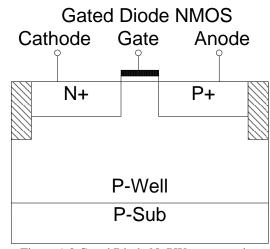

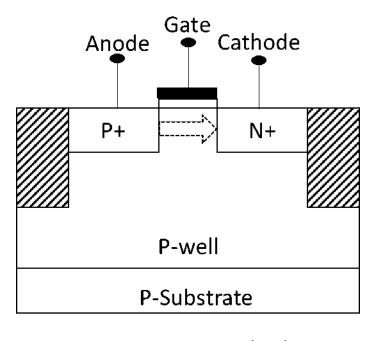

Figure 1.8 indicates the gated N+PW diode x-section. Gated diode also contains a PN junction, which is formed by N+/P-Well in CMOS IC process as STI diode. But gated diode has larger ESD current conduction ability since the current can go straightly through the channel between the N+ and P+ without any sharp turning and current crowding as seen in Figure 1.9.

Figure 1.8 Gated Diode N+PW cross-section

Figure 1.9 ESD discharge path for N+/P-well STI (upper) and poly-gated (lower) diode

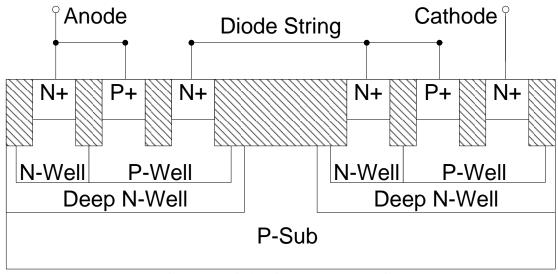

## 1.3.2 Diode String

Figure 1.10 shows a diode string ESD protection structure, which has N (N=2) diodes isolated by deep N-well connected in series. The trigger voltage  $V_{t1}$  will be N multiplying single diode triggering voltage, and the diode string total parasitic

capacitance will be 1/N of the single diode. However, the total ESD discharging Ron of the diode string will be N multiplying the single diode Ron. In ESD protection circuit schematic, diode string could be placed at I/O ports to provide low parasitic ESD protection, and it could also be used as a power clamp, whose number of diodes should be decided by the power supply voltage.

Figure 1.10 Diode string (N=2) cross-section

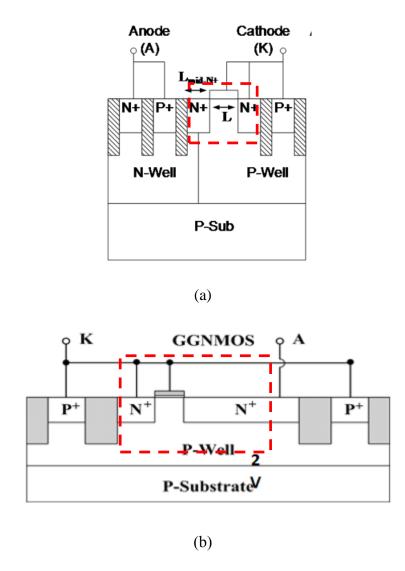

#### **1.3.3 GGMOS**

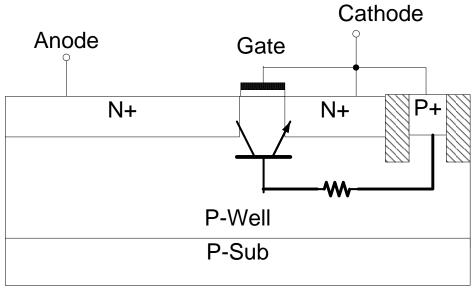

Gate-grounded NMOS transistor (GGNMOS) could be used as an ESD protection device. Figure 1.11 shows the cross-section and equivalent circuit of a GGNMOS. The drain is connected to anode, and the gate, source and bulk nodes are connected together to cathode.

The principle of a GGNMOS in ESD protection operation is as below. When a positive ESD transient pulse appears at the anode with respect to the cathode, the drain-bulk junction is reverse-biased all the way to its breakdown. Avalanche breakdown takes place and generates lots of electron-hole pairs. The hole current flows into the cathode

via the bulk-region and build up a potential, across the lateral parasitic resistance R. As the potential increases, the bulk-source junction turns on, eventually triggers the parasitic lateral NPN transistor. The parasitic bipolar is triggered into snapback region and the following active region, to shunt ESD current and clamp voltage at anode.

Figure 1.11 GGNMOS cross-section

PMOS could also be connected as GGPMOS for ESD protection. However, the parasitic PNP bipolar will be the discharging device in the GGPMOS. Another difference is the GGPMOS cathode will be tied to the power supply when it is placed in the circuits.

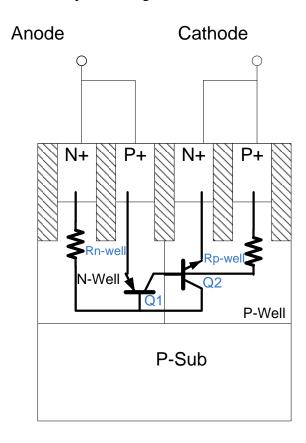

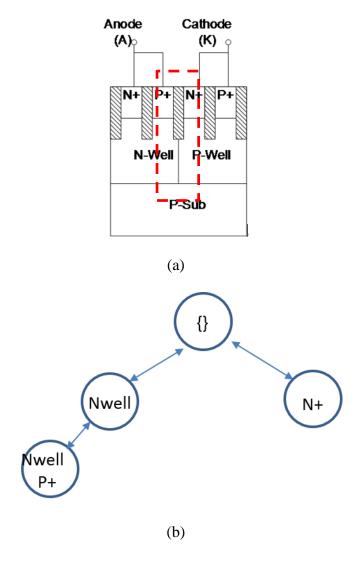

#### 1.3.4 SCR

The silicon-controlled rectifier (SCR) ESD structure is attractive because it has high ESD protection efficiency. Figure 1.12 shown the cross-section and equivalent circuit of a SCR. The N+ and P+ in N-Well are connected to anode, and the N+ and P+ in P-Well are connected to cathode. There're two parasitic bipolar, Q1 and Q2, and two parasitic well resistors, R<sub>N-Well</sub> and R<sub>P-Well</sub> for the equivalent circuit of SCR. Q1 is a PNP

bipolar, which is formed by the P+ in N-Well, N-Well and P-Well, and Q2 is an NPN bipolar, which is composed of N-Well, P-Well and the N+ in P-Well.

When a positive ESD transient pulse appears from anode to cathode, the current from the N-Well/P-Well junction avalanche breakdown will generate a voltage drop on  $R_{N\text{-Well}}$ . With the increasing of the avalanche current, the voltage drop will be high enough to turn on Q1. The current from the collector of Q1 will go to the base of the Q2, and finally will turn on the Q2. Then, both of the bipolar will feed current from their own collector for the other one's base, thus the voltage on the anode will drop rapidly to the holding voltage  $V_h$ . The two bipolar will be in active region and start to discharge ESD current in a low-Resistance and clamp the voltage at the anode.

Figure 1.12 SCR cross-section

The drawback of SCR is that it has a high  $V_{t1}$  than those of other devices introduced above, due to the high avalanche breakdown voltage between N-Well and P-Well. Thus it will not meet the ESD design window. However,  $V_{t1}$  of SCR ESD structures may be reduced by different low-triggering mechanism.

The LVSCR ESD structure is a type of improvement for the low-triggering mechanism. Figure 1.13 depicts the LVSCR cross-section. The LVSCR structure is a normal SCR device with embedded short-channel NMOS to enhance ESD triggering. Since the NMOS drain breakdown voltage occurs first at a much lower voltage level than the normal N-well/P-well breakdown in a regular SCR structure, a LVSCR can be triggered at a much lower ESD  $V_{t1}$ . ESD triggering for a LVSCR can be reduced to  $V_{t1}$ =6~10V, suitable for advanced ICs.

Figure 1.13 LVSCR cross-section

Diode triggered silicon controlled rectifiers (DTSCR) is another type of improvement for the low-triggering mechanism. It has become an attractive ESD protection device in advanced CMOS technologies due to their low capacitive loading and high failure current compared to diode based or NMOS based devices [31]. The DTSCR's tunable trigger/holding voltages offer design flexibility for a range of different I/O voltage requirements.

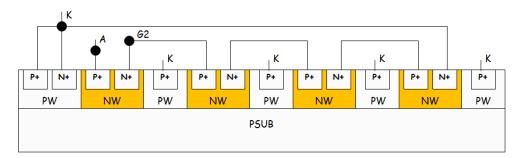

The DTSCR employs an external trigger diode chain to latch the device during ESD stress conditions as soon as the diode string injects enough current into the SCR gates G2, as shown in Figure 1.14. The triggering voltage  $V_{t1}$  of the DTSCR depends on the number of trigger diodes.

Figure 1.14 DTSCR cross-section with 3 trigger diodes.

## 1.4 Design Overview of Whole-chip ESD Protection CAD and Modeling

On-chip ESD protection solution development has drawn more and more attentions both in academic and industry, especially in developing ESD CAD tools and accurate ESD device models for practical ESD protection design verification.

Recent R&D efforts in ESD CAD may be classified in two types: Technology Computer-Aid Design (TCAD)-based [5-7] and ECAD-centric [8-10]. Physics-based numerical TCAD simulation has proven to be very useful in practical ESD protection

design at I/O cell scale. However, TCAD-based ESD protection design requires comprehensive and in-depth knowledge in device physics and process technology since TCAD simulator is a device-level simulation tool, which is often beyond the capabilities of IC designers. In addition, TCAD-based ESD protection design is very time consuming, computing expensive and not quite suitable for large-scale chip level simulation. On the other hand, ECAD-based ESD protection design verification has been limited to checking of ESD layout spacing, bus resistance checking, and so on, which cannot address ESD protection operation details quantitatively that is essential to achieving full-chip level ESD protection design verification and prediction as desired for RF/AMS IC designs.

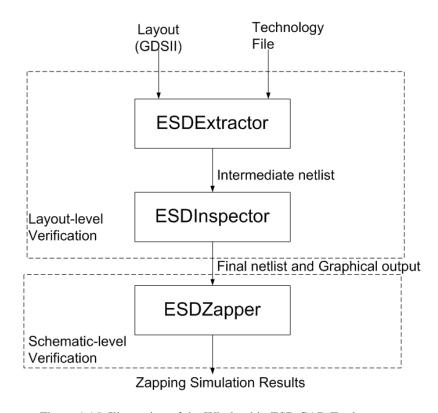

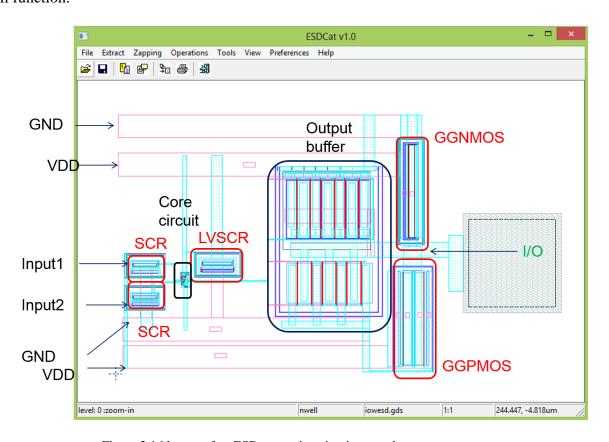

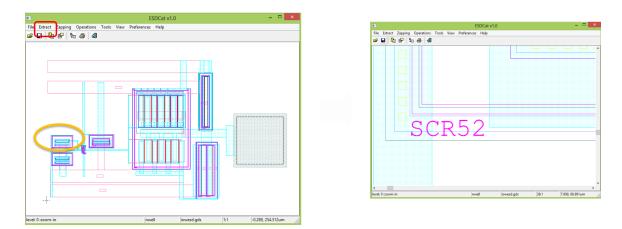

Regarding to all these issues, we proposed the whole-chip ESD CAD tool as illustrated in Figure 1.15. This CAD tool is designed with several unique algorithms and a smart ESD parametric checking mechanism, which takes full consideration of ESD protection operation principles. It consists of three modules: ESD Extractor, ESD Inspector and ESD Zapper. ESD Extractor is a new function to extract arbitrary ESD structures at full chip level. Decomposed-based subgraph isomorphism algorithm is invented for ESD devices extraction to improve time efficiency. ESD Inspector is to remove non-critical ESD devices extracted based upon a novel smart parametric checking mechanism. In addition, ESD Zapper is developed to perform ESD protection zapping test simulation by implementing Dijkstra's algorithm to resolve the problem of finding the critical ESD discharging path.

Figure 1.15 Illustration of the Whole-chip ESD CAD Tool

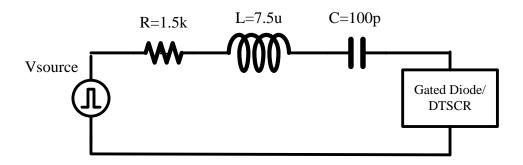

From the circuit design perspective, ESD Extractor and ESD Inspector realize layout-level verification, which provide IC designers a quick feedback after the physical layout design is completed and also provide the netlist for the schematic-level verification. ESD Zapper provides circuit designers complete simulation of the behavior of the whole chip circuit under ESD zapping of human body model (HBM).

HBM is one of the most-widely adopted ESD stress models in both academic and industry. HBM represents the process that the electrostatic charges storing in human body discharge to ground through IC parts when human body make a contact with the pins of the IC parts. This human body discharging process usually lasts several hundred nanoseconds and the peak current could reach to several amperes. The heat produced by

the human body discharging current will cause thermal breakdown damage in the IC parts if proper on-chip ESD protection structures are not available.

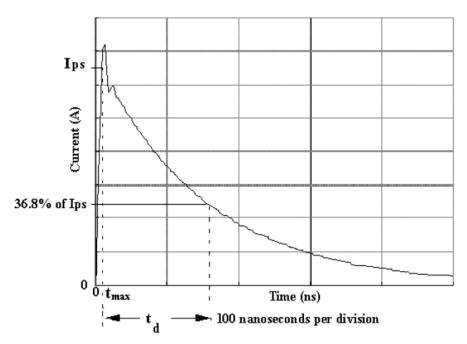

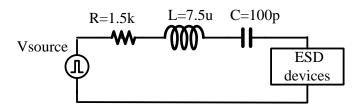

Typical HBM discharging current waveform has the main features as below: pulse rise time ( $t_r$ ) is about 2 ~ 10nS; pulse duration time ( $t_d$ ) is around 150nS, as shown in Figure 1.16 as defined in ESDA/JEDEC HBM standard [32]. Commercial HBM ESD testers must follow these rules of waveform, and waveform verification has to be done before the HBM test begins every day.

Figure 1.16 HBM current waveform

On the other hand, several ESD device modeling methods were reported for normal diode and MOSFET type of ESD protection devices based on the high current physical mechanisms [11-13]. However, due to the complexity of ESD discharging behaviors, i.e., the electro-thermal-process-device-circuit-layout coupling effects, existing ESD modeling approaches have limited accuracy in modeling complicated ESD

physical behaviors, such as thermal boundary conditions and snapback I-V behavior [1-3]. It is particularly challenging to develop physics-based ESD models for emerging nano ESD protection structures where the ESD protection mechanisms are still being investigated [14-17].

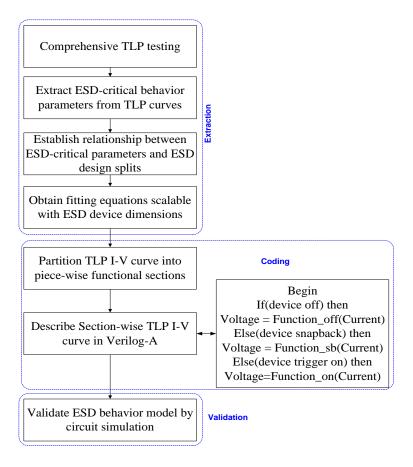

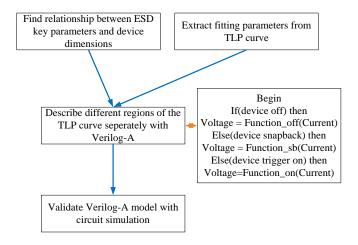

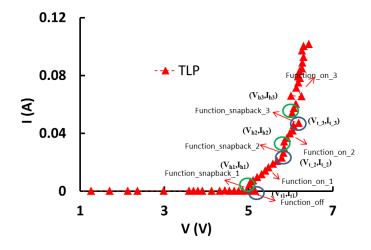

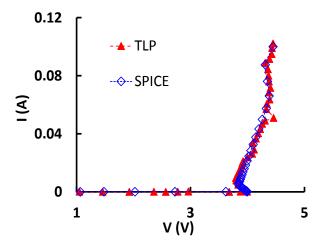

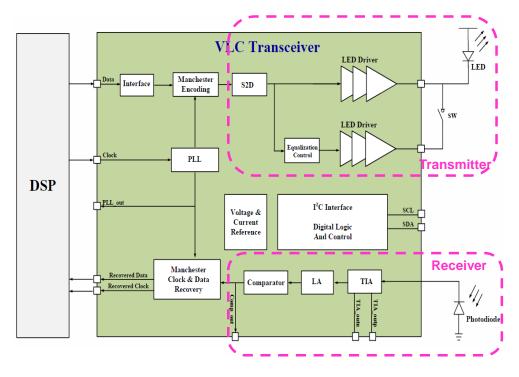

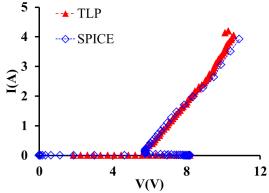

Regarding to all these modeling challenges, we proposed a new scalable ESD behavioral modeling technique as illustrated in Figure 1.17. The new ESD behavior modeling technique utilizes Verilog-A to describe complicated ESD discharging behavior, which enables accurate description of ESD device behaviors without being limited by the complex, and often unknown, ESD device physics. Firstly, the relationship between ESD-critical parameters and design splits must be established. After extracting ESD-critical parameters from TLP testing results and analysis, a scalability model per device dimensions can be set up. Next, the TLP curves are divided into several section-wise segments. Each segment of the TLP testing curve can be modeled by a formula to describe the corresponding ESD function in Verilog-A and the fitting parameters can be extracted from the TLP curve directly correlated with device dimensions. An accurate scalable ESD behavior model is then obtained, which must be verified by comparing SPICE circuit simulation with TLP testing.

Figure 1.17 A flow chart of ESD behavior modeling.

From the device modeling perspective, behavioral ESD device modeling enables accurate description of ESD device behaviors without being limited by the complex, and often unknown, ESD device physics. It overcomes the difficulties to extract complicated parameters based on high current and thermal physics. It is relatively easy to achieve a semi-physical model to describe high current ESD device behaviors using behavior language Verilog-A. It is empirical since scalability with device dimensions for key ESD-critical parameters (Vt1, Vh) can be established by matching TLP testing with design splits. In addition, behavioral ESD modeling also contribute to ease the convergence problem often caused by avalanche breakdown.

Besides, flip chip technique using ball grid array (BGA) pad-ring arrays is a popular technology for small footprint chips used in size-sensitive electronics. However, ESD protection design for ICs using large BGA pad-ring array is an emerging challenge due to several reasons. First, unlike chips using wire bonding, ICs using BGA pad-ring arrays have constraints in on-chip ESD protection design where I/O pads, supply and ground (GND) pads are fixed in a given BGA pad-ring array determined by the chip performance. Hence, where to place an ESD structure becomes a real layout design headache. Second, with no layout flexibility for placing ESD structures in a BGA padring array, ESD metal routing is very challenging that will seriously affect ESD protection performance at chip level. Between any given IO pad with an ESD protection structure underneath and a supply/GND pad with a fixed location, there will be many possible ESD metal routes. For a large chip using BGA pad-ring array, different ESD metal routing may significantly take effect on-chip ESD protection design due to the substantially different bus resistance associated with ESD metal routes even using the same ESD device for a given pad.

Regarding to all these BGA pad-ring array ESD protection challenges, we proposed a full-chip level verification using the new ESD Extractor CAD tool and new scalable ESD behavioral modeling technique. A BGA pad-ring array with different ESD metal routing for a VLC transceiver implemented in 180nm BCD technology was verified at whole-chip level. Two types of ESD were designed, one for the digital & analog domain (up to 5V) and the other for the power domain (up to 30V). The ESD structures and their ESD-critical parameters from full-chip layout design (GDSII data

file), were extracted by our ESD Extractor CAD tool. For accurate chip-level ESD protection circuit simulation, the ESD metal bus resistance was extracted by ESD Extractor tool. The geometrical dimension width and length of ESD metal interconnects are extracted from the layout file and the bus resistance can be calculated according to related metal sheet resistivity and layout data. The new ESD behavior modeling technique was used to model the GCNMOS ESD structures fabricated in this work to enable whole-chip ESD circuit design simulation and verification. It utilizes Verilog-A language to describe ESD-critical parameters extracted from ESD Extractor CAD tool. The extraction and modeling was validated by SPICE simulation and TLP testing for different ESD metal routing.

## 1.5 Thesis Organization

This thesis consists of 5 chapters.

Chapter 2 will treat the implementation of whole-chip ESD CAD tool. First, challenges for ESD device extraction will be studied. Then novel algorithms and the implementation methods for ESD Extractor are presented. The necessity of developing ESD Inspector is discussed and then a novel concept of smart parametric checking is proposed along with a set of reduction criteria. ESD zapper is designed according to ESD protection design critical task of simulating the complex, time-consuming ESD zapping test at whole-chip level. The algorithm and implementation for ESD zapper is also provided. To the end, full chip ESD protection application example was designed and verified the CAD tool implemented in 0.35 µm BiCMOS technology.

Chapter 3 focuses on new accurate and scalable behavioral modeling method. The modeling method is explored on novel ESD protection structures, such as nano crossbar, novel 3D field-programmable ESD protection structures including SONOS and NCD ESD devices firstly. Then it's applied to traditional ESD protection structures, for example SCR, HV diode, gated diode and DTSCR. For each kind of ESD protection structure, the ESD behavior models were developed from ESD testing results and verified in SPICE circuit simulation.

Chapter 4 will be dedicated to a BGA pad-ring array with different ESD metal routing for a VLC transceiver implemented in 180nm BCD technology full-chip verification. The ESD structures and their ESD-critical parameters, and the ESD metal bus resistance were extracted by our new ESD Extractor CAD tool. The new ESD behavior modeling technique was used to model the ESD structures. The extraction and modeling was validated by SPICE simulation and TLP testing for different ESD metal routing.

Chapter 5 will conclude with the main contributions and achievements of the presented work, and some suggestions for future research.

# **Chapter 2 Whole-chip ESD CAD Tool**

#### 2.1 Introduction

In this chapter, we proposed the whole-chip ESD CAD tool as illustrated in Figure 1.15. This CAD tool is designed with several unique algorithms and a smart ESD parametric checking mechanism, which takes full consideration of ESD protection operation principles. It consists of three modules: ESD Extractor, ESD Inspector and ESD Zapper. ESD Extractor is a new function to extract arbitrary ESD structures at full chip level. Decomposed-based subgraph isomorphism algorithm is invented for ESD devices extraction to improve time efficiency. ESD Inspector is to remove non-critical ESD devices extracted based upon a novel smart parametric checking mechanism. In addition, ESD Zapper is developed to perform ESD protection zapping test simulation by implementing Dijkstra's algorithm to resolve the problem of finding the critical ESD discharging path.

#### 2.2 ESD Extractor

To enable ESD-function-based whole-chip ESD protection design verification at layout level, ESD Extractor CAD module is critical since it's the very first step in any design verification. Several challenges exist for ESD protection device extraction tool as follow [51]. Firstly, extraction of ESD protection device is different from that regular IC devices since ESD protection circuits often use unconventional devices. Conventional IC devices, such as MOSFET and BJT, can be extracted using basic Boolean operation of layout features, while ESD protection devices usually have very complicated and

failure problem, good ESD device extraction method must be able to extract all possible parasitic ESD-like devices within the whole chip, since ESD transient current often causes the turn-on of parasitic ESD-like devices before the desired intentional ESD devices may be triggered and results in pre-mature ESD failure at chip level. The ESD netlist generated by the ESD Extractor should contain all ESD-type devices possibly being turned on under an ESD pulse, whether it is an intentionally designed ESD protection device or a parasitic ESD-like device. Therefore, the ESD Extractor is designed to have the capability of extracting any possible ESD-type structures and their ESD-critical parameters from full-chip layout design.

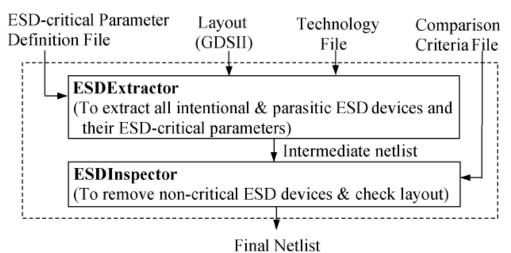

## 2.2.1 Design Overview of ESD Extractor

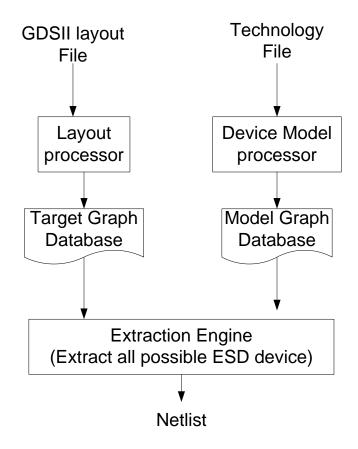

Figure 2.1 shows the flow chart for ESD Extractor, a new CAD tool that is capable of extracting arbitrary ESD-like devices of any structure and takes full consideration of both intentional and parasitic ESD-type device, which consists of three execution steps: (1) to read the device definition in the technology file and save it in the model database; (2) to save the layout data into the layout database after necessary prepossessing; (3) to identify all possible ESD-type devices with their ESD-critical parameters, intentional or parasitic, in the extraction engine. The output data is sent to the next module, ESD Inspector, to remove non-critical ESD devices extracted.

Figure 2.1 Flow chart for ESD Extractor

## 2.2.2 Layout Processor

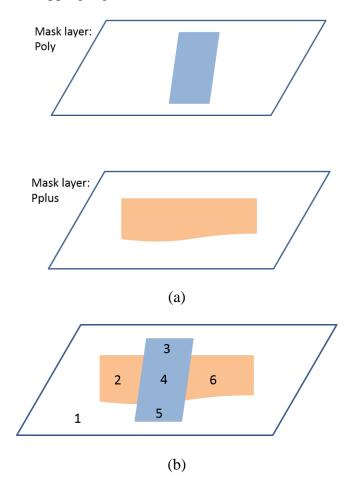

IC layout is a geometrical description of masks in GDSII format, so it's necessary to have a layout processor to transform the input GDSII layout file into graph data structures and save them in the target graph (TG) database as shown in Figure 2.1.

GDSII layout file contains a set of graphical geometries situated on separate mask layers as illustrated in Figure 2.2 (a), which includes two partly overlapping polygons situated in two separate mask layer Poly and P-plus. To avoid using more computationally expensive geometrical operations (such as include, intersect, surround, divide), all the input geometries in all mask layers are first merged together and then

partitioned into non-overlapping regions, as shown in Figure 2.2 (b) the layout is partitioned into 6 non-overlapping regions [49].

Figure 2.2 Layout processing example

In our design, each region is a simple polygon consisting of a set of stacked mask layers, where the presence and absence of mask layers are described in the program as mask values, which use a bit mask code word, with "1" representing the presence of that layer and "0" indicating the absence of the mask layer. Therefore, a mask value code of all "0's" represents the bare wafer substrate without any other IC physical layers.

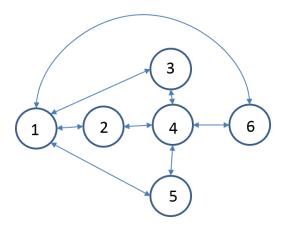

For the inner geometrical presentation, the target layout graph (TG) data structure are used to indicate the GDSII layout file. A TG consists of a finite set of vertices, where

each vertex corresponds to a non-overlapping region and a set of edges joining the vertices with each edge representing an adjacency relationship existing between a pair of the vertices. The TG for the layout design in Figure 2.2 is shown in Figure 2.3, where each circle represents a vertex for TG and the solid lines represent the edges for TG.

Figure 2.3 TG for the layout design example in Figure 2.2

### 2.2.3 Device Model Processor

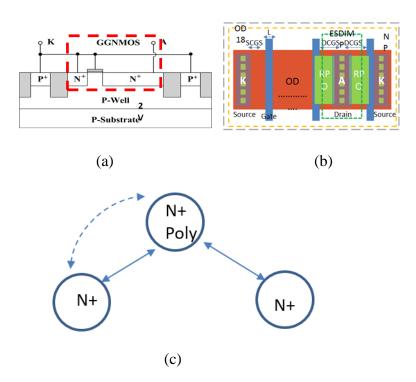

There're many ESD device types including the classic GGNMOS, GCNMOS, BJT, diode and SCR, as well as any novel ESD protection structures. Hence, each device type is described by a unique device model graph (MG). An adjacent list graph structure is adopted for device model graph definition. The structure of a MG is defined as MG (V, E). The attribute V is a set of vertices with each vertex corresponding to a non-overlapping region with a specific mask value. The attribute E is a set of relationships between two different vertices of the device model, which includes geometrical adjacency relationship and electrical connectivity relationship for ESD protection. Hence, a complete set of vertices form a device model, MG. The part in dashed box shown in Figure 2.4(a) is the cross-section for GGNMOS without guard-ring and pick-ups, with its

layout indicated in Figure 2.4(b). A MG for it is shown in Figure 2.4(c), where each circle represents a vertex of the MG, the solid lines represent geometrical adjacency relationship R1 and the dashed lines represent electrical connectivity R2.

Figure 2.4 GGNMOS (a) cross-section (b) layout (c) MG definition

Figure 2.5 illustrates an SCR ESD device with pick-ups. So the part in dashed box without pickups is selected as MG for SCR ESD device. This SCR MG definition ensures that each parasitic ESD-type SCR device will be extracted.

Figure 2.5 SCR (a) cross-section (b) MG definition

## 2.2.4 Device Recognition Algorithm

Since the whole IC layout data is presented as a target graph and each device type is described by a unique device model graph, a device is identified by matching one section of the target graph with one of the model graphs. So we propose a decomposition-based subgraph isomorphism technique to recognize arbitrary ESD protection structures.

We want to find all subgraph isomorphism from any of the models to the input graph. Under a naive strategy, some reported device extractors [26, 27] use a top-down

approach, which would match the input graph sequentially to each model using. The main disadvantage of this approach is that it is linearly dependent on the number of model graphs [25].

However, an ESD protection device extractor has its own special requirement. Firstly, there're many ESD device types including the classic GGNMOS, BJT, diode and SCR, as well as any novel ESD protection structures, e.g., a dual-direction SCR ESD protection device [21]. Besides, another unique feature of ESD protection devices is that different ESD protection structures may share common layer elements. For example, LVSCR and GGNMOS share common elements shown in Figure 2.6.

Figure 2.6 (a) LVSCR cross-section, (b) GGNMOS cross-section

According to the unique features of ESD protection devices, we propose a new device recognition algorithm based on a decomposition approach to improve ESD device recognition efficiency. Unlike the top-down approach [26, 27] that handles each MG individually, our algorithm first explores the relationship between the device MGs by a decomposition procedure. The main advantage of this scheme is that the common part of any two or more MGs will only be matched for once, which makes the device recognition

procedure not heavily dependent upon the number of device MGs as does the top-down approach. Meanwhile, in our new approach, model containment relationship can be explicitly expressed. Hence, any redundant device, i.e., the small device like GGNMOS contained in a larger device LVSCR, can be easily removed from the final result, thus eliminates the necessity of developing an individual redundant device processor and improves the computing time efficiency in ESD protection device recognition.

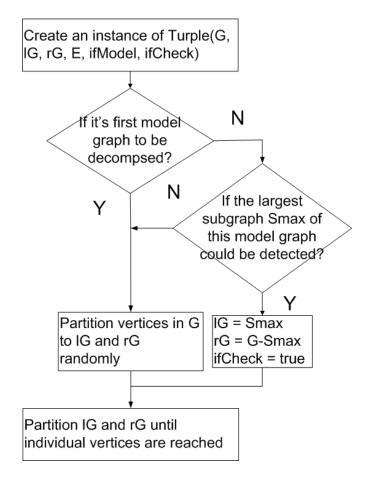

The device recognition algorithm consists of two steps: model decomposition and device recognition. Firstly, different device MGs are recursively decomposed and the decomposition results, D (M), are saved by a special inner data structure. Secondly, the TG is matched with D (M).

The decomposition result of MG, D(M), is a set of tuple data structure as T(G, IG, rG, E, ifModel, ifCheck), where G, IG, rG are graphs; IG is left subgraph of G; rG is right subgraph of G; E is a set of edges between IG and rG to construct G. ifModel is a Boolean variable. If ifModel = true, G is corresponding to a device model. IfCheck is a Boolean variable. If ifCheck = true, G may contain another MG, directly or indirectly. Decomposition procedure is shown in Figure 2.7.

Figure 2.7 Flow chart of decomposition procedure

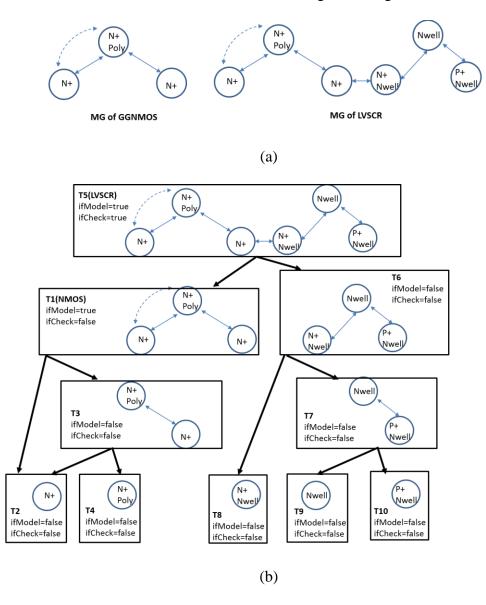

Figure 2.8 illustrates the MGs for a GGNMOS and LVSCR ESD protection device. Let MG1 = GGNMOS and MG2 = LVSCR, the decomposition result, T1~T10 in D (M), is shown in Figure 2.8 (b). From the decomposition procedure, the GGNMOS is first decomposed into two parts, with the left subgraph, IG, being T2 and the right subgraph, rG, being T3. Because the IG contains only one vertex, it will not be decomposed any more. The rG will be further decomposed into two parts. The decomposition results of the GGNMOS are saved in D (M) as T1~T4. Now the LVSCR is decomposed. Firstly, the largest subgraph in D (M), Smax, is first searched in D (M) whose contents are now T1~T4, and the result is T1 (GGNMOS). Then the LVSCR will

be decomposed into two parts, with IG to be T1 (GGNMOS) and the leftover parts as rG to be T6. Next, the algorithm further decomposes the right subgraph of LVSCR as T6, with results of T7~T10. The common subgraph of GGNMOS and LVSCR, GGNMOS as T1, is saved only once in D (M). In addition, for the LVSCR (T5), if Check = true makes sure that redundant device is removed in the device recognition stage.

Figure 2.8 Model Decomposition Procedure for GGNMOS and LVSCR

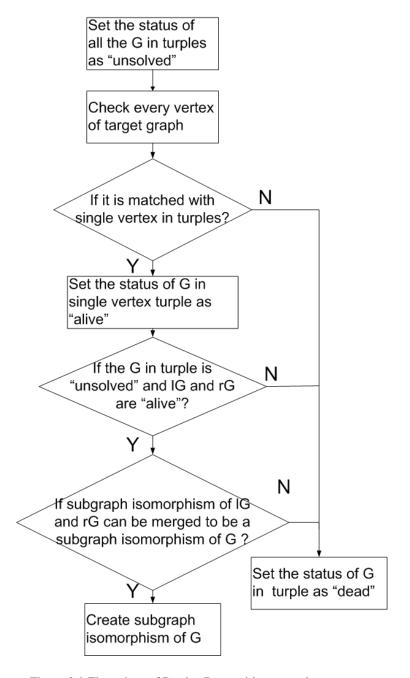

Instead of matching each MG individually to a TG, the device recognition procedure is shown in Figure 2.9. Firstly, it finds all individual vertices of the D (M) within the TG and then gradually combine them into larger subgraph isomorphism. In order to keep track of the components that have been matched already with the TG, each member in D (M) can be marked with one of three different tags. In the beginning, all members in D (M) are marked unsolved. As soon as a member has been tested for subgraph isomorphism with the TG, it is either marked alive or dead. If the search for subgraph isomorphism was successful, then the member is marked alive and all detected subgraph isomorphism are associated with it using hash map. Otherwise, the subgraph is marked dead and no subgraph isomorphism are associated with it. This process continues until either all members in D (M) have been tested or no member can be found for which both subgraphs are marked alive.

Figure 2.9 Flow chart of Device Recognition procedure

For the time complexity, the top-down approach is O (NIM), in which N is the number of the model graphs, I is the number of vertices in the target graph, and M is the total number of vertices of model graphs. Compared to that, if all model graphs are

identical for the extremely situation, the decomposition-based subgraph isomorphism approach has the time complexity of O(IM), which heavily improves the time efficiency by N times than the top-down approach.

## 2.3 ESD Inspector

The ESD extractor extracts all intentional and parasitic ESD devices from a layout file, however, the number of the ESD devices are so large that it will take effect to the time efficiency for the schematic level simulation. Therefore, it is critical to identify those life-threatening ESD-type parasitic devices that designers should really concern. Therefore, a new CAD tool module of ESD Inspector is developed to remove non-critical ESD devices extracted based upon a novel smart parametric checking mechanism.

#### 2.3.1 Design Overview of ESD Inspector

The goal of ESD Inspector is to remove non-critical ESD devices extracted and to generate an input deck for schematic-level simulation. Different from other ESD physical design checking tools reported, ESD Inspector use a new smart ESD parametric checking mechanism [28]. It is observed that the behavior of all kinds of ESD devices, including intentional or parasitic can be described by some important quantitative parameters. Such ESD-critical parameters include triggering ( $V_{t1}$ ,  $I_{t1}$ ), holding ( $V_{h}$ ,  $I_{h}$ ), discharging ( $R_{ON}$ ) and thermal breakdown ( $V_{t2}$ ,  $I_{t2}$ ), etc., which is introduced in Section 1.2. Figure 2.10 illustrates the combined functional flow chart for the ESD Extractor and ESD Inspector.

Figure 2.10 Flow chart for ESD Extractor and ESD Inspector.

## 2.3.2 Smart Parametric Checking Mechanism

Considering all possibilities in the ESD protection combination, the new smart parametric checking mechanism defines a group of ESD-critical parameter checking criteria [33].

Assuming a case of two ESD devices, A and B, in series. Then the total series triggering voltage,  $V_{t1}$ , will be estimated first, by  $V_{t1}A+V_{t1}B$ .

Assuming a case of two ESD devices, A and B, in parallel. Several criteria is described as below. (1) Triggering criteria: If ESD devices A and B are in parallel and  $V_{t1}$  of A is much higher than  $V_{t1}$  of B, then device A is a non-critical ESD device and could be removed. (2) Holding criteria: If ESD devices A and B are connected in parallel and A has a higher  $V_h$  than B does, then A is a non-critical ESD device and will be removed. (3)  $R_{ON}$  criteria: If ESD devices A and B are in parallel and have comparable  $V_{t1}$ , but  $R_{ON}$  of A is much larger than that of B, then device-A may not discharge the ESD current and could be removed.

As more about the ESD protection behavior is understood and any novel ESD protection mechanisms are discovered, more ESD-critical parameter based smart parametric checking criteria can be added in practical ESD layout design verification. However, the fundamental smart parametric checking mechanism remains the same as we discussed as above.

The smart parametric checking mechanism is used to remove non-critical ESD devices and to generate critical ESD devices netlist using ESD Inspector after extraction of ESD devices and ESD-critical parameters, which take effect to the time efficiency for the schematic level simulation.

## 2.4 ESD Zapper

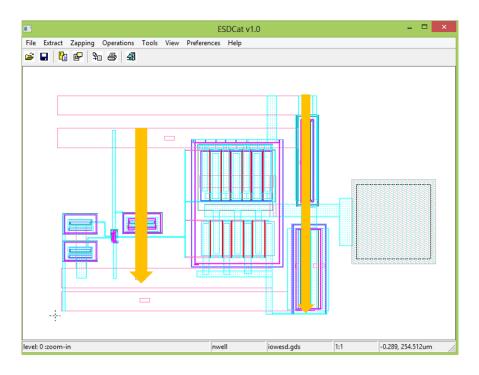

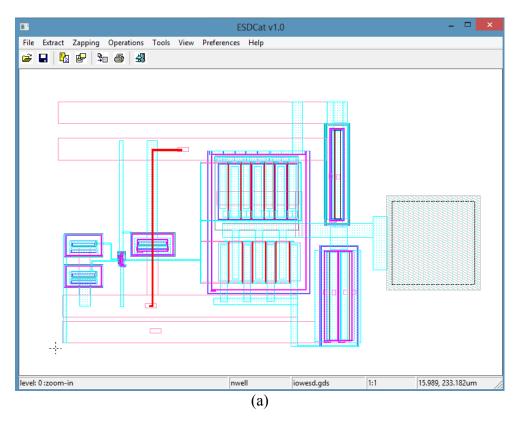

Successful on-chip ESD protection design must use the whole-chip ESD protection design approach because of complex ESD circuit has interaction effects with core circuit, compared to traditional design practices that often treat ESD protection design as stand-alone ESD protection structure. Figure 2.11 shows an example for a whole chip ESD stress scenario. While an ESD discharging path between the PADs is designed (solid line), parasitic conducting paths may conduct the current (dash line) and result in early ESD failure.

Figure 2.11 whole chip ESD stress scenario

Therefore, one important problem to resolve for whole-chip ESD protection circuit design verification is to identify the critical ESD discharging paths on a chip, which considers all possible ESD-type devices including designed ESD structures and parasitic ESD type devices. Hence, ESD zapper is designed to achieve whole-chip ESD protection design verification and prediction, since this module is developed to perform whole-chip checking to identify critical ESD discharging paths.

### 2.4.1 Design Overview of ESD Zapper

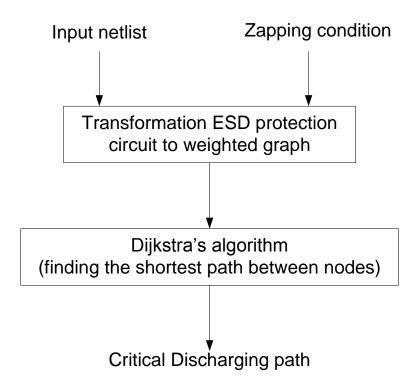

Figure 2.12 shows the flow chart of ESD Zapper. As described in section 2.2 and 2.3, after complete ESD extraction operation by ESD extractor and device reduction by ESD Inspector, the output ESD netlist is the input to the ESD Zapper. Also zapping condition including the pad combination is the input for the ESD Zapper. The ESD netlist is transformed to a novel weighted graph, where the ESD protection circuit is described as a weighted graph with each electrical node corresponding to a vertex and each ESD

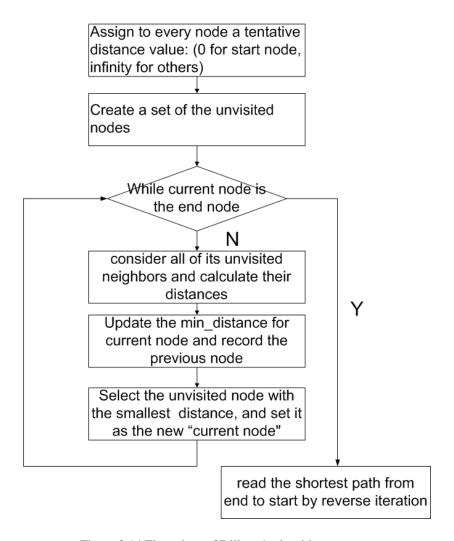

device being an edge of the graph. Then critical ESD discharging paths between pads are found using Dijkstra's algorithm, which finds the shortest paths between nodes in a graph [50].

Figure 2.12 Flow chart for ESD zapper

### 2.4.2 Critical Discharging Path Algorithm

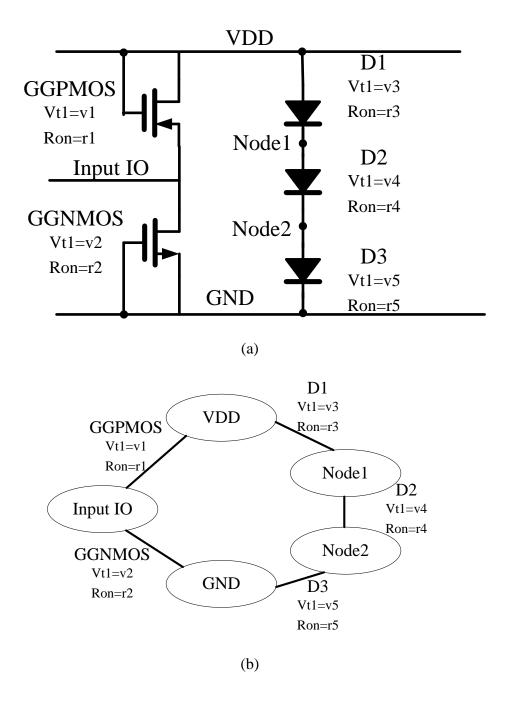

The ESD protection circuit is described as a weighted graph with each electrical node corresponding to a vertex and each ESD device being an edge of the graph. The ESD-critical parameters of each device are assigned to the corresponding edge as its weight. Figure 2.13 illustrates an example circuit with ESD protection (a), consisting of GGNMOS and GGPMOS as the input IO ESD protection, and diode string as power clamp, and its corresponding weighted graph (b). Then the critical discharging path can

be found by finding the path with the smallest weight between two given vertices, for example VDD and GND.

Figure 2.13 Example for (a) ESD protection circuit (b) transformed weighted graph

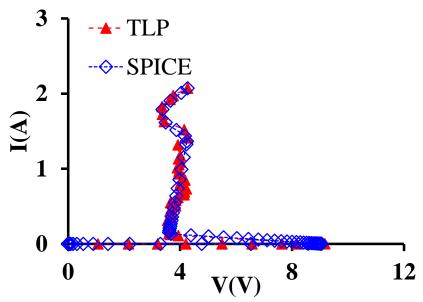

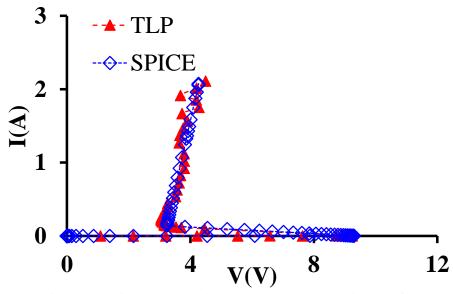

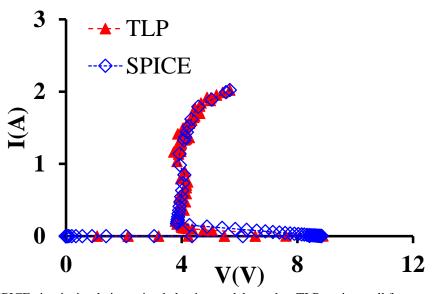

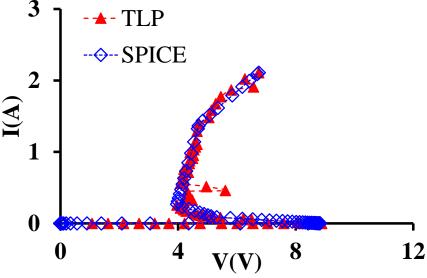

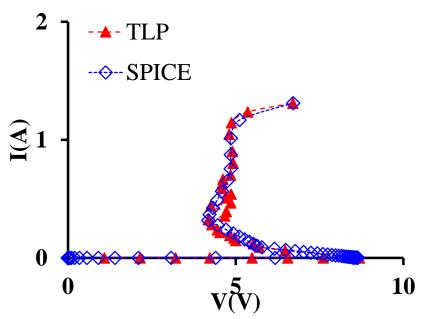

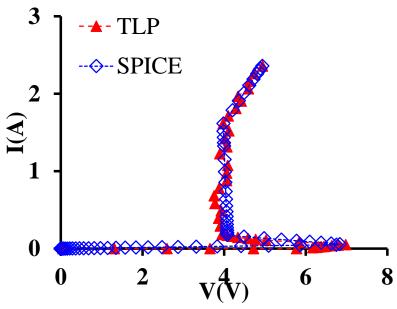

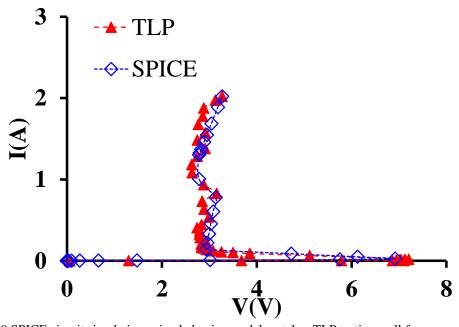

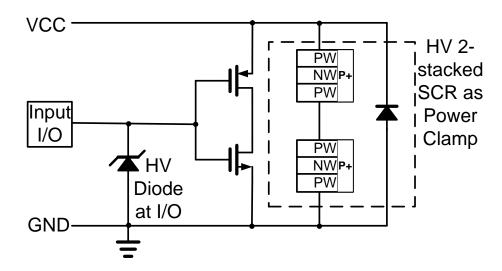

There are many developed algorithms we can choose to find the shortest path in the graph, such as Dijkstra's algorithm, the Bellman–Ford algorithm, and Prim's algorithm. Considering the feature of weighted graph in this problem, which does not include negative edge weights and is concerned with only two nodes, Dijkstra's algorithm is selected to find the shortest path.