# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Ultra-Low Noise Current Measurement Front-Ends for Biological Applications

#### **Permalink**

https://escholarship.org/uc/item/4r0185pn

#### **Author**

Hsu, Chung-Lun

### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### **Ultra-Low Noise Current Measurement Front-Ends for Biological Applications**

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Chung-Lun Hsu

### Committee in charge:

Professor Drew A. Hall, Chair Professor Gert Cauwenberghs Professor Yu-Hwa Lo Professor Patrick Mercier Professor Daniel Sievenpiper

Copyright

Chung-Lun Hsu, 2018

All rights reserved.

| The Dissert | atio  | n of Chu   | ng-Lı  | ın Hsu | is ap | proved, an  | d it is   |

|-------------|-------|------------|--------|--------|-------|-------------|-----------|

| acceptable  | in    | quality    | and    | form   | for   | publication | n on      |

| microfilm a | ınd e | electronic | cally: |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       |             |           |

|             |       |            |        |        |       | (           | <br>Chair |

University of California, San Diego

2018

# DEDICATION

To my family.

### TABLE OF CONTENTS

| Signatu   | re Page                                                | iii  |

|-----------|--------------------------------------------------------|------|

| Dedicat   | tion                                                   | iv   |

| Table of  | of Contents                                            | v    |

| List of I | Figures                                                | x    |

| List of 7 | Tables                                                 | xiv  |

| Acknow    | wledgments                                             | XV   |

| Vita      |                                                        | xvii |

| Abstrac   | et of the Dissertation                                 | xix  |

| Chapter   | r 1                                                    | 1    |

| Intro     | duction                                                | 1    |

| 1.1       | Research Motivation                                    | 1    |

| 1.2       | Biosensors and Electronic Readout                      | 2    |

| 1.3       | Current-based Biosensors                               | 4    |

| 1.4       | Challenges                                             | 5    |

| 1.5       | Scope of Dissertation                                  | 6    |

| Chapter   | r 2                                                    | 7    |

| Curre     | ent Measurement Front-Ends for Biosensing Applications | 7    |

| 2.1 B     | Background                                             | 7    |

| 2.2 C     | Current Conveyor                                       | 10   |

|   | 2.3 Transimpedance Amplifier                                           | 12 |

|---|------------------------------------------------------------------------|----|

|   | 2.3.1 Resistive Feedback TIA                                           | 13 |

|   | 2.3.2 Capacitive Feedback TIA                                          | 14 |

|   | 2.3.3 Log TIA                                                          | 15 |

|   | 2.3.4 Wideband TIA                                                     | 16 |

|   | 2.4 Current-Input ADC                                                  | 17 |

|   | 2.4.1 Delta-Sigma Modulator                                            | 17 |

|   | 2.4.2 Oscillator-based ADC                                             | 18 |

|   | 2.5 Summary and Comparison                                             | 20 |

| C | Chapter 3                                                              | 21 |

|   | A Hybrid Semi-Digital Transimpedance Amplifier with Noise Cancellation |    |

|   | Technique for Nanopore-Based DNA Sequencing                            | 21 |

|   | 3.1 Introduction                                                       | 22 |

|   | 3.2 The Architecture of the HSD-TIA                                    | 28 |

|   | 3.3 Semi-Digital Feedback Loop                                         | 31 |

|   | 3.3.1 Digital Filter                                                   | 31 |

|   | 3.3.2 DC Compensation Current                                          | 34 |

|   | 3.4 Noise Cancellation Technique and Noise Analysis                    | 36 |

|   | 3.4.1 Noise Cancellation Technique                                     | 36 |

|   | 3.4.2 Noise Analysis                                                   | 37 |

|   | 3.5 Implementation                                                     | 39 |

|   | 3.6 Circuit Performance                                                | 43 |

|   | 3.6.1 Frequency Response                                               | 43 |

| 3.6.2 Noise Performance                                         | 44 |

|-----------------------------------------------------------------|----|

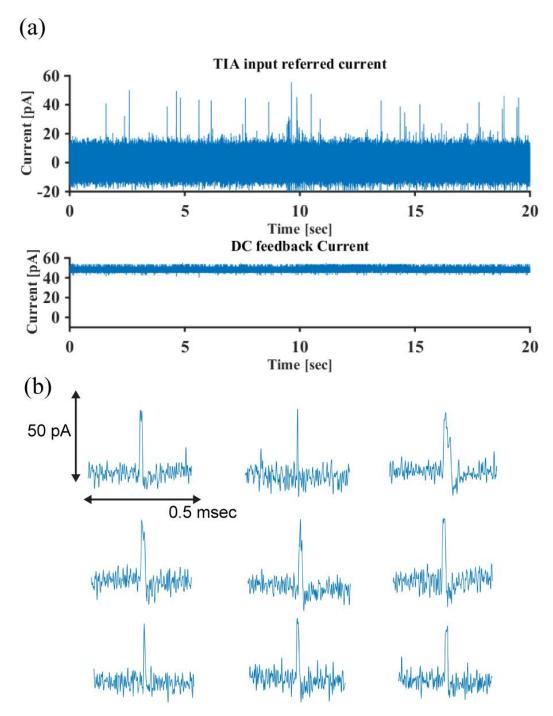

| 3.7 Biological Measurement Results                              | 46 |

| 3.7.1 Creating Lipid Bilayer                                    | 46 |

| 3.7.2 Measurement of Nanopore Insertion                         | 48 |

| 3.7.3 Measurement of DNA Translocation                          | 49 |

| 3.8 Conclusion                                                  | 51 |

| Chapter 4                                                       | 53 |

| An Hourglass ADC with 162 dB DR Using First-Order Noise-Shaping | 53 |

| 4.1 Introduction                                                | 53 |

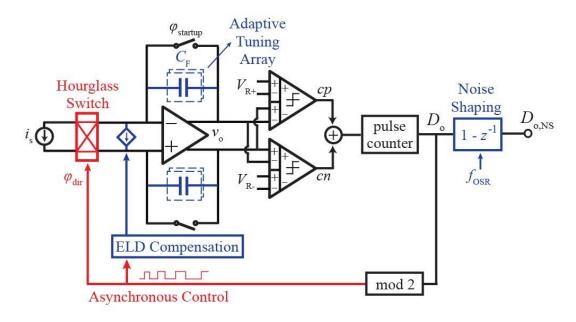

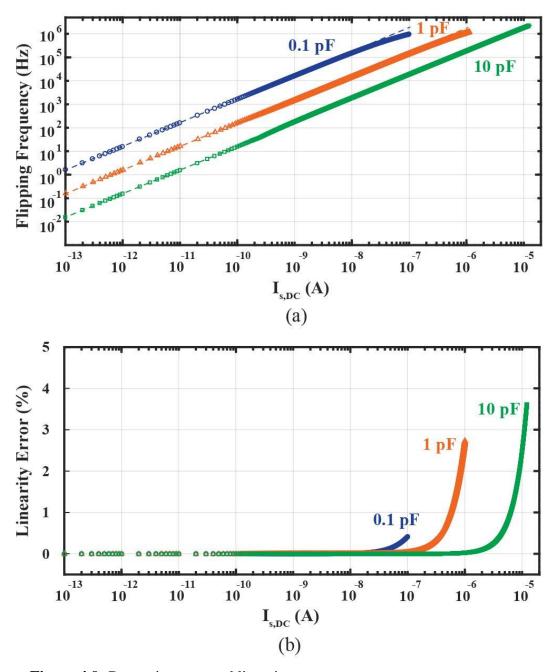

| 4.2 Hourglass ADC Architecture                                  | 54 |

| 4.2.1 <i>I</i> -to- <i>F</i> conversion                         | 55 |

| 4.2.2 Analog-to-Digital Conversion                              | 57 |

| 4.2.3 First-Order Noise-Shaping Behavior                        | 59 |

| 4.2.4 ELD Compensation                                          | 60 |

| 4.2.5 Adaptive Feedback Capacitor Array                         | 61 |

| 4.3 Asynchronous Sigma-Delta Modulator                          | 61 |

| 4.3.1 Asynchronous SDM                                          | 62 |

| 4.3.2 CCO-Based ADC                                             | 63 |

| 4.4 Integrated Circuit Implementation                           | 63 |

| 4.4.1 System                                                    | 63 |

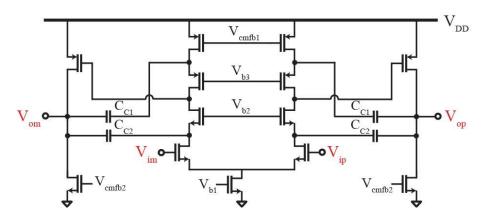

| 4.4.2 Amplifier                                                 | 64 |

| 4.4.3 Switch                                                    | 65 |

| 4.4.4 Continuous-Time Comparator                                | 66 |

| 4.4.4 Digital Blocks                                     | 66 |

|----------------------------------------------------------|----|

| 4.5 Measurement Results                                  | 66 |

| 4.6 Summary                                              | 72 |

| Chapter 5                                                | 73 |

| An Hourglass ADC with 160 dB Dynamic Range and 7 ppm INL | 73 |

| 5.1 Introduction                                         | 73 |

| 5.2 Architecture Overview                                | 75 |

| 5.3 System Analysis                                      | 78 |

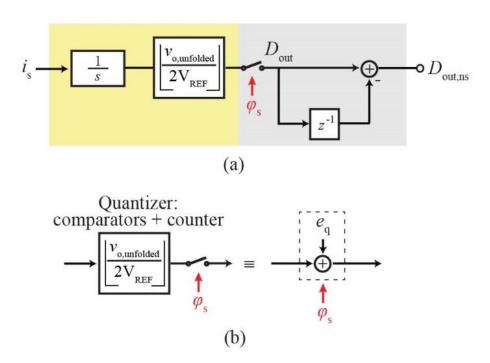

| 5.3.1 Open-Loop Delta-Sigma Modulation                   | 78 |

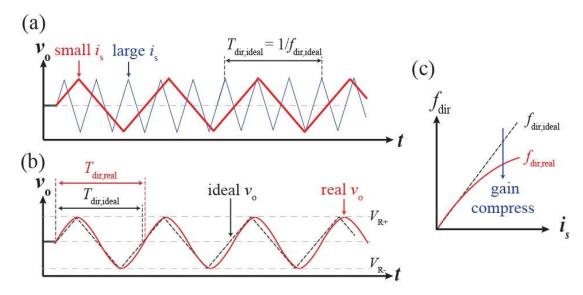

| 5.3.2 <i>I</i> -to- <i>F</i> Conversion Linearity        | 79 |

| 5.3.3 Predictive DAC                                     | 82 |

| 5.4 Noise Analysis                                       | 84 |

| 5.4.1 Noise in Hourglass ADC                             | 85 |

| 5.4.2 Noise in I-DAC                                     | 87 |

| 5.5 Implementation                                       | 87 |

| 5.5.1 System                                             | 87 |

| 5.5.2 Power Optimization                                 | 88 |

| 5.5.3 <i>I</i> -to- <i>F</i> Linearity Calibration       | 89 |

| 5.5.4 Amplifier                                          | 89 |

| 5.5.5 I-DAC                                              | 90 |

| 5.5.6 Digital Blocks                                     | 91 |

| 5.5 Measurement Results                                  | 92 |

| 5.6 Conclusion                                           | ne |

| Chapter 6                   | 100 |

|-----------------------------|-----|

| Summary                     | 100 |

| 6.1 Summary of Dissertation | 100 |

| 6.2 Areas for Future Work   | 102 |

| References                  | 104 |

# LIST OF FIGURES

| Figure 1.1: | Elements of a typical biosensor [1]                                        |

|-------------|----------------------------------------------------------------------------|

| Figure 1.2: | Sensitivity requirements for biological applications                       |

| Figure 1.3: | (a) Examples of current-input electrochemical biosensors where (b) and (c) |

| show 1      | representative waveforms4                                                  |

| Figure 2.1: | Simplified model for a current-based biosensor                             |

| Figure 2.2: | Schematic of a current conveyor                                            |

| Figure 2.3: | Schematic of (a) a transimpedance amplifier, and (b) equivalent circuit    |

| with n      | oise sources. 12                                                           |

| Figure 2.4: | Schematic of an R-TIA                                                      |

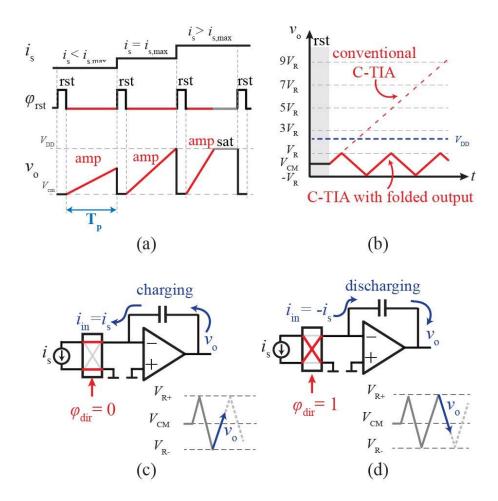

| Figure 2.5: | (a) Schematic and (b) waveform of a C-TIA14                                |

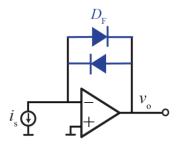

| Figure 2.6: | Schematic of a bidirectional Log-TIA                                       |

| Figure 2.7: | Schematic of a wideband TIA                                                |

| Figure 2.8: | Schematic of a DSM                                                         |

| Figure 2.9: | Schematic of a VCO-based ADC                                               |

| Figure 3.1: | (a) Illustration of a nanopore-based DNA sequencing platform. (b) The      |

| baselir     | ne current shift that occurs when a ssDNA translocates23                   |

| Figure 3.2: | (a) Conventional resistive feedback TIA with voltage and current noise     |

| model       | . (b) The corresponding power spectrum density (PSD) of the input-         |

| referre     | ed current noise. The high frequency noise of the TIA is dominated by the  |

| input o     | capacitor $C_{\rm in}$ and the voltage noise $e_{\rm n}$                   |

| Figure 3.3: (a) Architecture of the HSD-TIA with noise cancellation technique. (b)        |

|-------------------------------------------------------------------------------------------|

| The frequency response of HSD-TIA with low cutoff frequency $f_L$ introduced by           |

| the semi-digital feedback loop and high cutoff frequency $f_{\rm H}$ . (c) Equivalent     |

| nanopore circuit model. $R_p$ and $C_P$ are the nanopore resistance and capacitance,      |

| and $R_{\rm E}$ and $C_{\rm E}$ are from the Ag/AgCl electrodes                           |

| Figure 3.4: (a) Concept of the semi-digital feedback loop. (b) Frequency response of      |

| integrator and LPF. (c) Frequency response of the loop gain with the tuning factor        |

| $1/k$ . The tuning factor $1/k$ is implemented to tune the low cutoff frequency $f_L$ and |

| the stability of the feedback loop                                                        |

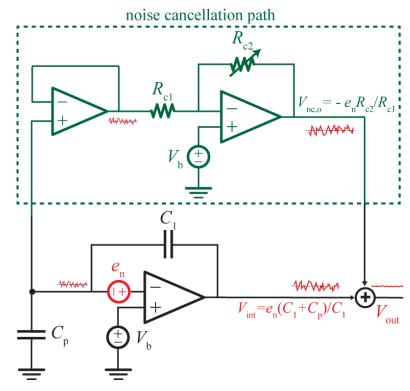

| Figure 3.5: Schematic of feedforward noise cancellation circuit. The integrator voltage   |

| noise is sensed and amplified by the noise cancellation path                              |

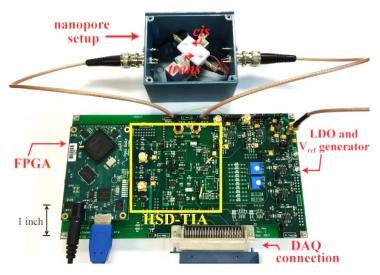

| Figure 3.6: Photograph of nanopore and TIA                                                |

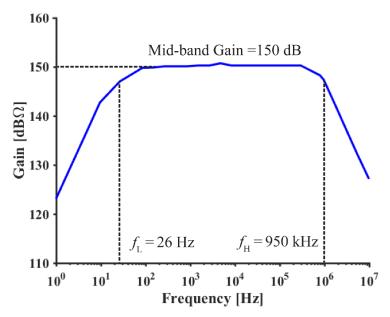

| Figure 3.7: Frequency response of reported HSD-TIA                                        |

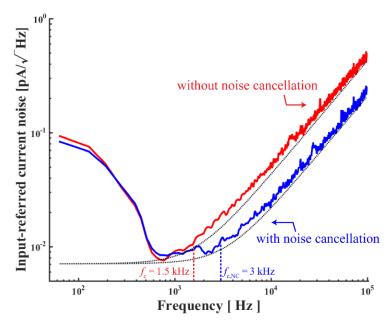

| Figure 3.8: Photograph of nanopore and TIA. Measured input-referred noise spectrum        |

| density of reported HSD-TIA with and without noise cancellation circuit. The              |

| dotted lines are theoretical noise spectrum density with and without noise                |

| cancellation path calculated from (14) and (11), respectively45                           |

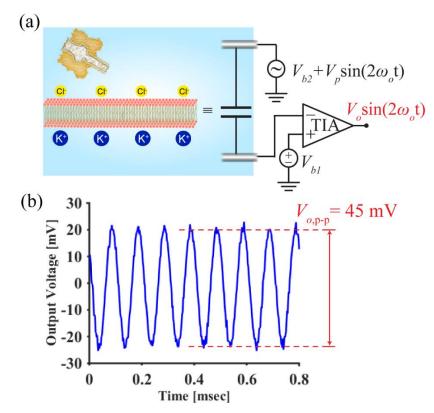

| Figure 3.9: (a) Equivalent test circuit with the HSD-TIA for verifying the existence of   |

| a lipid bilayer. (b) Measured output waveform of the HSD-TIA with a single-               |

| tone sine-wave input                                                                      |

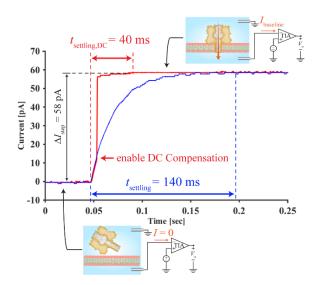

| Figure 3.10: Comparison of the step responses of the reported TIA with and without |

|------------------------------------------------------------------------------------|

| the DC compensation current when a protein nanopore is inserted in the lipid       |

| bilayer49                                                                          |

| Figure 3.11: Comparison of the step responses of the reported TIA with and without |

| the DC compensation current when a protein nanopore is inserted in the lipid       |

| bilayer50                                                                          |

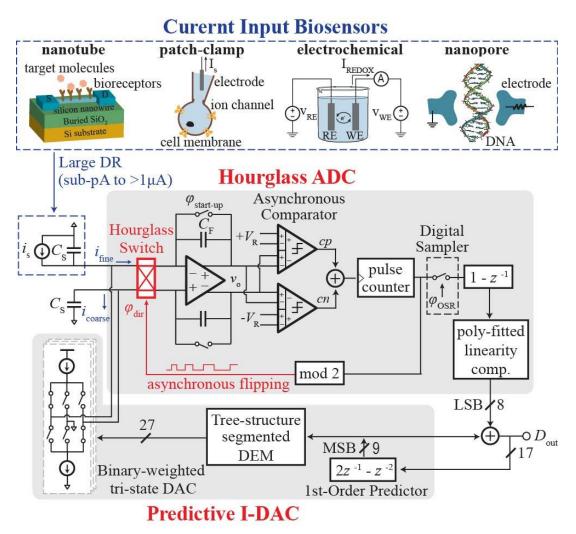

| Figure 4.1: Architecture of the current measurement front-end                      |

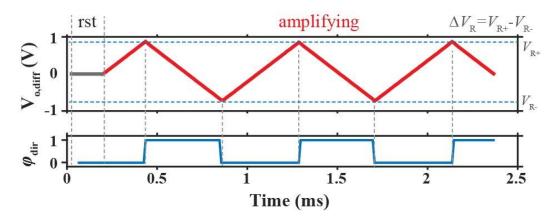

| Figure 4.2: Waveform of (a) a conventional C-TIA with period reset, the C-TIA with |

| folded output. The C-TIA with the Hourglass switch folds the output by charging    |

| and discharging $C_f$ alternatively in (c) and (d) respectively56                  |

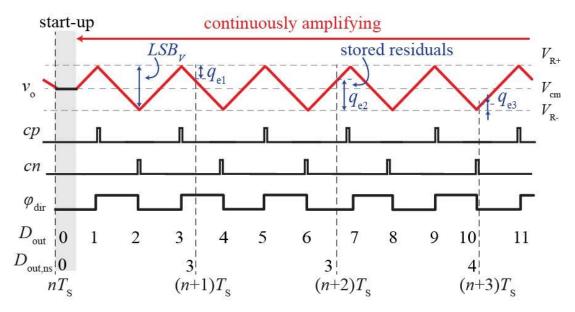

| Figure 4.3: Illustration of LSB and quantization error in the Hourglass ADC. The   |

| ADC providing the first-order noise shaping behavior when the C-TIA stores         |

| residuals at each sampling phase59                                                 |

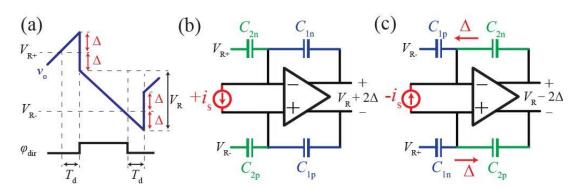

| Figure 4.4: The waveform of ELD compensation in (a) by switching the integrating   |

| capacitor to compensate the overshoot before and after the polarity of the input   |

| flips in (b) and (c) respectively60                                                |

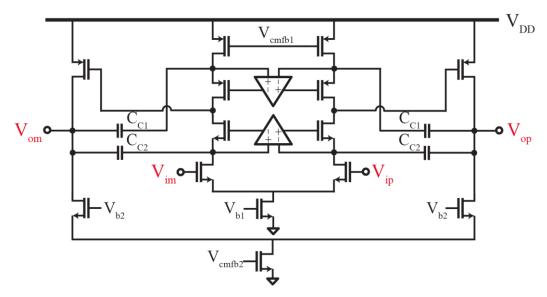

| Figure 4.5: Schematic of dual cascode compensation gain-boosted amplifier65        |

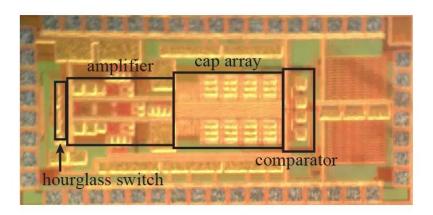

| Figure 4.6: Photograph of the chip.                                                |

| Figure 4.7: Photograph of the chip.                                                |

| Figure 4.8: Photograph of the chip.                                                |

| Figure 4.9: Dynamic range and linearity error 70                                   |

| Figure 5.1: Illustration of the closed-loop Hourglass ADC with a corresponding                       |

|------------------------------------------------------------------------------------------------------|

| equivalent circuit model for current input biosensors74                                              |

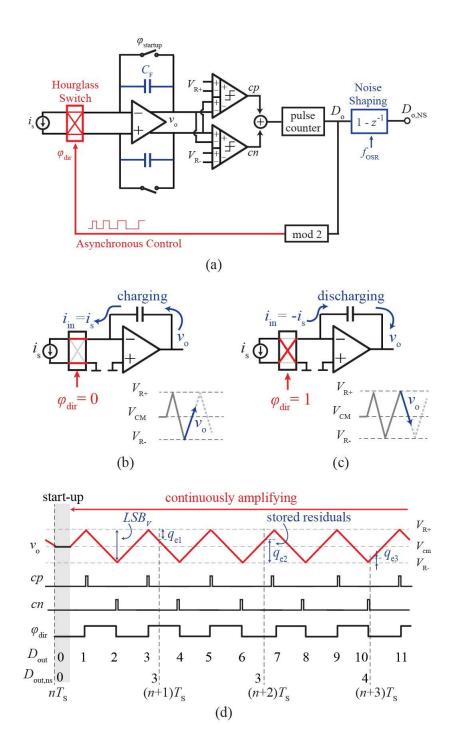

| Figure 5.2: (a) Schematic of Hourglass ADC with an asynchronous control loop. The                    |

| C-TIA and the Hourglass switch fold the output by charging and discharging $C_F$                     |

| alternatively, as shown in (b) and (c), respectively. (d) Complete waveforms                         |

| illustrating operation                                                                               |

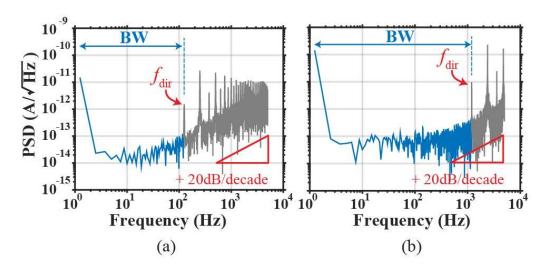

| Figure 5.3: (a) Block diagram of Hourglass ADC and (b) the quantizer78                               |

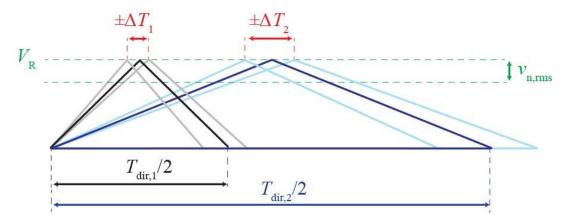

| Figure 5.4: (a) Waveform showing the <i>I</i> -to- <i>F</i> conversion. (b) Distortion caused by the |

| finite-bandwidth of the amplifier and (c) resulting <i>I</i> -to- <i>F</i> compression81             |

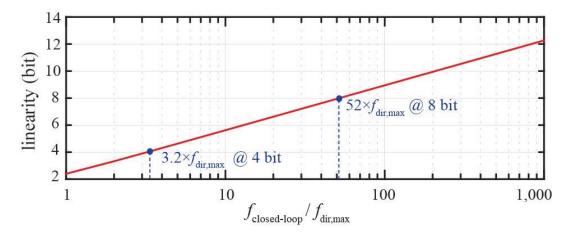

| Figure 5.5: Relationship between <i>I</i> -to- <i>F</i> linearity and the normalized amplifier       |

| bandwidth82                                                                                          |

| Figure 5.6: The output-referred voltage noise at the output of C-TIA causes the jitter               |

| of the triangle wave86                                                                               |

| Figure 5.7: Schematic of dual cascode compensation amplifier90                                       |

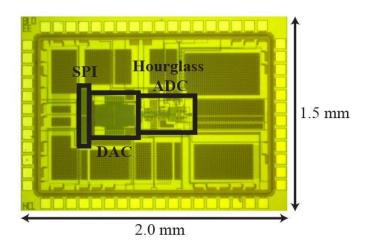

| Figure 5.8: Die micrograph                                                                           |

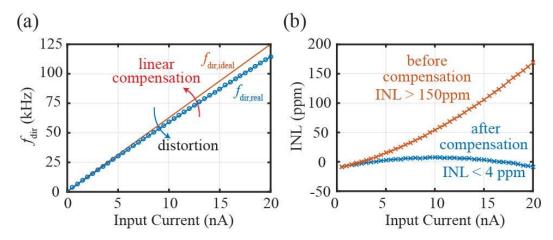

| Figure 5.9: <i>I</i> -to- <i>F</i> conversion of the Hourglass ADC: (a) transfer function and (b)    |

| linearity error94                                                                                    |

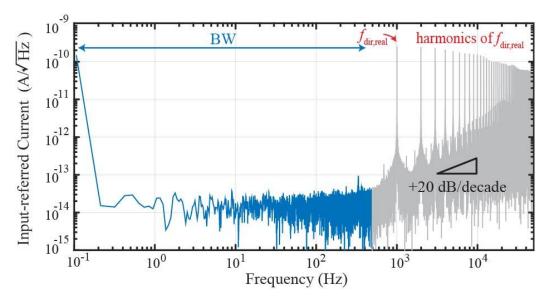

| Figure 5.10: PSD of Hourglass ADC with a DC input94                                                  |

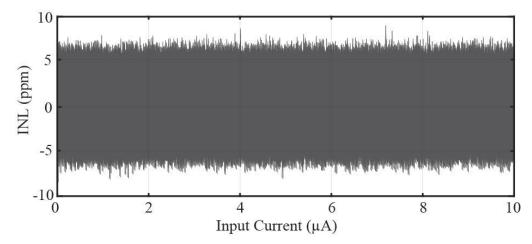

| Figure 5.11: Linearity error of the AFE96                                                            |

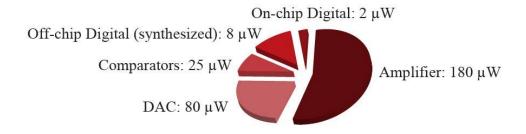

| Figure 5.12: Power breakdown of the AFE96                                                            |

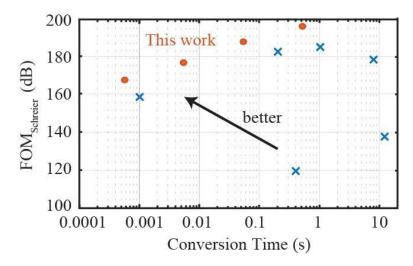

| Figure 5.13: FOM of this work and state-of-the-arts                                                  |

### LIST OF TABLES

| Table 2.1: | Comparison of conventional current-sensing front-ends | 20 |

|------------|-------------------------------------------------------|----|

| Table 3.1: | List of Discrete Components and Values                | 42 |

| Table 3.2: | Performance Comparison.                               | 46 |

| Table 4.1: | Performance Comparison.                               | 71 |

| Table 5.1: | Performance Comparison.                               | 97 |

#### **ACKNOWLEDGMENTS**

First, I would like to acknowledge my advisor Professor Drew Hall for his guidance, support, and encouragement. This work could not possibly be accomplished without his tremendous input. I would also like to thank my other committee members, Professor Daniel Sievenpiper, Professor Gert Cauwenberghs, Professor Patrick Mercier, and Professor Yu-Hwa Lo for their guidance.

I appreciate the help from my colleagues at UCSD, Alexander Sun, Somok Mondal, Haowei Jiang, Xiahan Zhou, Da Ying, and Corentin Pochet, for their discussions and suggestions on my projects. I also wish to thank all the other Biosensors and Bioelectronics group members, Venkatash Govindaraj, Rajesh Seenivasan, and Chih-Cheng Huang, for their valuable assistance. I would like to thank my family and friends for their continuous support and encouragement.

Portions of Chapter 3 is a reprint of the material as it appears in IEEE TBioCAS 2015. Chung-Lun Hsu, Haowei Jiang, A. Venkatesh, and Drew A. Hall. A Hybrid Semi-Digital Transimpedance Amplifier with Noise Cancellation Technique for Nanopore-Based DNA Sequencing. IEEE Transactions on Biomedical Circuits and Systems (TBioCAS), vol. 9, no. 5, pp. 652-661, 2015. The thesis author was the first author of this paper.

Portions of Chapter 4 and Chapter 5, contain both a reprint and material currently being prepared for submission for publication as it appears in IEEE ISSCC 2018. A Current Measurement Front-end with 160dB Dynamic Range and 7 ppm INL.

IEEE International Solid-State Circuits Conference (ISSCC). The thesis author was the first author of this paper.

Chung-Lun Hsu

La Jolla, CA

March 2018

#### VITA

#### **EDUCATION**

| 2007 | Bachelor of Science in Electrical Engineering, National Cheng<br>Kung University, Taiwan                                   |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 2009 | Master of Science in Electrical Engineering, National Cheng<br>Kung University, Taiwan                                     |

| 2018 | Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems), University of California, San Diego, USA |

#### **PUBLICATIONS**

Chung-Lun Hsu, Alexander Sun, Yunting Zhao, Eliah Aronoff-Spencer, and Drew A. Hall. A 16×20 Electrochemical CMOS Biosensor Array with In-Pixel Averaging Using Polar Modulation. *IEEE Custom Integrated Circuits Conference (CICC)*, San Diego, CA, USA, Apr. 8-11, 2018.

Chung-Lun Hsu and Drew A. Hall. A Current Measurement Front-end with 160dB Dynamic Range and 7 ppm INL. *IEEE International Solid-State Circuit Conference (ISSCC)*. San Francisco, CA, USA, Feb. 12-14, 2018.

Somok Mondal, **Chung-Lun Hsu**, Roozbeh Jafari, and Drew Hall. A Dynamically Reconfigurable ECG Analog Front-End with a 2.5× Data-Dependent Power Reduction. *IEEE Custom Integrated Circuits Conference (CICC)*, Austin, TX, USA, May 1-3, 2017.

Chung-Lun Hsu, Tiantian Zhang, Yu-Hwa Lo, Drew A. Hall. A Low-Noise Gain-Enhanced Readout Amplifier for Induced Molecular Electronic Signals. *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, Atlanta, GA, USA, Oct. 22-24 2015.

**Chung-Lun Hsu**, Haowei Jiang, A. G. Venkatesh, and Drew A. Hall. A Hybrid Semi-Digital Transimpedance Amplifier with Noise Cancellation Technique for Nanopore-Based DNA Sequencing. *IEEE Transactions on Biomedical Circuits and Systems (TBioCAS)*, vol. 9, no. 5, pp. 652–661, 2015. (Invited paper)

Chung-Lun Hsu, A. G. Venkatesh, Haowei Jiang, and Drew A. Hall. Hybrid Semi-Digital Transimpedance Amplifier for Nanopore-Based DNA Sequencing. *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, Lausanne, Switzerland, October 22-24, 2014.

#### **PATENTS**

**Chung-Lun Hsu**, Alexander Sun, Yunting Zhao, Eliah Aranoff-Spencer, Drew A. Hall. Electrochemical Biosensor Array Devices, Systems, and Methods for Point-of-Care Detection. US Provisional Patent

**Chung-Lun Hsu**, Drew A. Hall. Wide Dynamic Range Current Measurement Front-End. US Provisional Patent

#### Abstract of the Dissertation

#### **Ultra-Low Noise Current Measurement Front-Ends for Biological Applications**

by

#### Chung-Lun Hsu

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2018

#### Professor Drew A. Hall, Chair

Current measurement front-ends are widely used to provide a high precision, real-time signal acquisition for biological applications where charge perturbations occur during biological interactions. The requirement of the high dynamic range in front-ends has become imperative for high sensitivity biosensors; however, designing front-ends with high dynamic range is challenging in advanced CMOS process nodes with reduced supply voltages where the minimum and maximum detectable signals are determined by circuit noise and power supply voltage, respectively.

In this dissertation, I present several ultra-low noise current measurement front-ends for biosensing applications that aim to address this issue. The first work was designed for nanopore-based DNA sequencing. A hybrid semi-digital transimpedance amplifier senses the minute current signatures introduced by single-stranded DNA (ss-DNA) translocating through a nanopore, while discharging the baseline current using a semi-digital feedback loop. The amplifier achieves fast settling by adaptively tuning a DC compensation current when a step input is detected. A noise cancellation technique reduces the total input-referred current noise caused by the parasitic input capacitance. The amplifier has 31.6 M $\Omega$  mid-band gain, 950 kHz bandwidth, and 8.5 fA/ $\sqrt{}$ Hz input-referred current noise, a 2× noise reduction due to the noise cancellation technique. This system is demonstrated by capturing ssDNA translocation events.

The second front-end is a new current-input analog-to-digital converter (ADC) architecture, an asynchronous Hourglass structure that provides both low-noise amplification while decoupling the maximum detectable signal from the supply voltage, and first-order quantization noise-shaping. By eliminating the need for the reset switch in a capacitive transimpedance amplifier (C-TIA) and the feedback digital-to-analog converter in a delta-sigma modulator and compensating the excess loop delay, this Hourglass ADC achieves over 160 dB dynamic range (sub-pA to >10  $\mu$ A), sub-pA<sub>rms</sub> input-referred noise, and a conversion time of 400 ms – 2.5× faster than the state-of-the-art.

The linearity and power efficiency of the Hourglass ADC is further improved when implementing the ADC in a closed loop structure where a predictive I-DAC provides a coarse estimate of the current and the Hourglass ADC processes only the residue. A calibration technique is proposed to optimize the power consumption in the C-TIA and improve the current-to-frequency (*I*-to-*F*) linearity. This closed-loop Hourglass ADC achieved Shreier FOM of 197 dB with a 7 ppm linearity error over a 160 dB dynamic range from 100 fA to 10 μA.

# Chapter 1

# Introduction

### 1.1 Research Motivation

Over the past three decades, biosensors have been promising tools to provide better stability and sensitivity compared to traditional methods in many fields, namely medical and biological applications. The recent trend in biosensing technology has taken this equipment from simple and cheap components to the integration of several sensor systems into a single unit capable of detecting multiple analytes, making these systems smaller and tailored for particular applications. For example, biosensors can be integrated into mobile phone systems, making them user-friendly and accessible to a large number of users. To further reduce the cost and size, novel signal measurement front-ends with an ultra-low noise and high input dynamic range are needed to make these innovations possible.

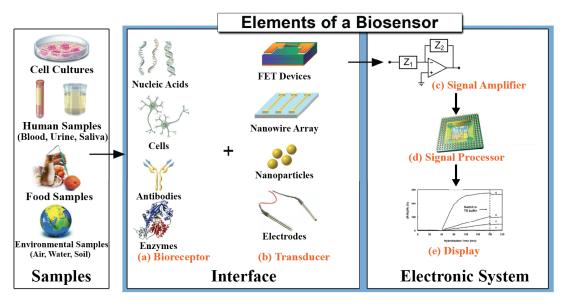

**Figure 1.1:** Elements of a typical biosensor [1].

### 1.2 Biosensors and Electronic Readout

A biosensor is an analytical device that converts a biological interaction (e.g., a binding event, DNA passing through an orifice, etc.) into a quantifiable and processable electric signal [2]. Figure 1.1 shows the various elements of a typical biosensor [1] where a transducer is coated with bioreceptor molecules that provide specificity to the analyte of interest. The sensor response is converted to an electric signal and amplified by an electronic front-end. A signal processor and a graphical user interface analyze and quantify binding events. Biosensors can be applied to a large variety of analytes including small molecules (e.g., antibodies, proteins, nucleic acids), food samples, and even environmental samples.

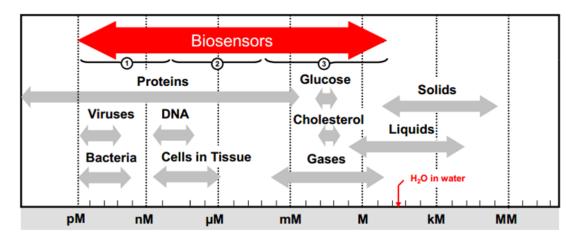

**Figure 1.2:** Sensitivity requirements for biological applications.

Compared to conventional instruments such as optical microscopy, electronic biosensors have the advantages of lower cost and smaller size. One of the biggest challenges today is dealing with the wide dynamic range of analytes present in biological samples. For example, some analytes exist in concentrations as low as a few fM (10<sup>-15</sup> M) in the early stages of disease (e.g., cardiac troponins [3]) while other analytes (e.g., glucose [4-6]) are over 12 orders of magnitude higher. Several biosensors have demonstrated detection of analytes at concentrations less than pM (10<sup>-12</sup> M) [7] as shown in Fig. 1.2, but none have enough dynamic range to cover the vast range of analytes. As such, researchers are working on designing biosensors and frontend circuitry with higher dynamic range while maintaining the high sensitivity. While it would not cover the entire dynamic range, the ability to detect pM concentrations to more than µM concentrations (>120 dB) would significantly advance the state-of-the-art and is the focus of this work.

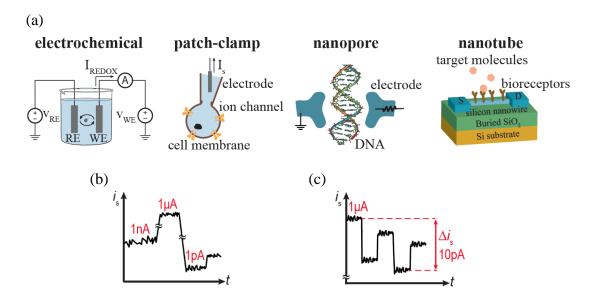

**Figure 1.3:** (a) Examples of current-input electrochemical biosensors where (b) and (c) show representative waveforms.

### 1.3 Current-based Biosensors

In current-based biosensors, a signal in the form of a change in charge is generated when biological events perturb the charge distribution of the electrode/electrolyte interface. Figure 1.3 shows some examples of current-based biosensors. In electrochemical cells, a charge transfer current,  $I_{\rm redox}$ , occurs when the target molecule reduces (gains an electron) or oxidizes (loses an electron) on the surface of the working electrode (WE) with an applied analyte specific potential ( $V_{\rm WE}$  -  $V_{\rm RE}$ ) between the working and reference electrodes (RE), respectively [8, 9]. Intracellular dynamics can be studied using a patch-clamp system [10] and DNA can be sequenced as it passes through a nanopore where it modulates the conductance across or through the pore [11, 12]. Finally, binding events on a nanoFET (e.g., a

nanotube or a nanowire) coated with bioreceptors are detected by the modulation in surface charge acting as the gate of the device [13].

The amplitude of the current in these sensors can vary by over 6 orders of magnitude. For example, the detection of neurotransmitters using an electrochemical biosensor requires more than 120 dB of dynamic range (DR), where the concentration of Dopamine can vary from 1 nM to >1 mM due to spontaneously spike activity or pharmacological stimulus [7]. The current in a patch-clamp setup covers several orders of magnitude depending on the number and the types of ion channels on the cell membrane. The high DR requirement has become even more critical with single molecule biosensors, e.g., nanopores and nanotubes, where the signal is a sub-pA current superimposed on a slowly varying nA to μA background current from the ion channel. These biosensing applications require a current readout front-end with a DR higher than 140 dB and an input-referred current noise less than 1 pA<sub>rms</sub> [14, 15].

## 1.4 Challenges

Conventional current measurement front-ends have been extensively reported and analyzed in the literature [14, 15]. The dynamic range of these circuits is fundamentally determined by the circuit noise and supply voltage, which limits the minimum and maximum input currents, respectively. The decreasing supply voltage in advanced CMOS process nodes further limits the DR of conventional current-sensing front-ends [16, 17]. Furthermore, an output with a digital format is often desirable for further signal processing in the digital domain, so the front-end should

function both as a low-noise signal amplifier and an analog-to-digital converter (ADC). The design and optimization of such a front-end that achieves high linearity and reduces power consumption is a very attractive research topic, especially for high DR biosensing applications.

### 1.5 Scope of Dissertation

This dissertation presents the development of ultra-low noise current measurement front-ends for high dynamic range biosensing applications. In Chapter 2, performance and design trade-offs of conventional front-ends are discussed and analyzed. Chapter 3 presents a wide-band low-noise hybrid transimpedance amplifier for nanopore-based DNA sequencing. Chapter 4 presents a high dynamic range asynchronous Hourglass ADC with first-order noise shaping. Chapter 5 expands on this architecture showing a closed-loop Hourglass ADC achieving 160 dB dynamic range and 7 ppm linearity error. Lastly, concluding remarks and future research directions are presented in Chapter 6.

# Chapter 2

# **Current Measurement Front-Ends for**

# **Biosensing Applications**

In this chapter, current measurement front-ends for biosensing applications are introduced and the design and properties of different architectures is analyzed. Due to the various design trade-offs, comparisons of these architectures are discussed.

## 2.1 Background

Many biosensors provide a current signal during the detection of target molecules or proteins, and this current signal is captured by a signal amplifier for further signal processing. The most critical current signals in biosensing applications typically range from sub-pA to more than a few  $\mu A$  within a  $\sim kHz$  bandwidth. Thus, the amplifier requires a dynamic range of greater than six orders, i.e., more than 120

dB, and very low input-referred noise (tens to hundreds of  $fA_{RMS}$  in the kHz bandwidth). In addition, the input impedance of the signal amplifier should be low compared to the sensor's output impedance to avoid attenuation.

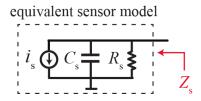

To design an amplifier and analyze the effect of the noise, a current input biosensor can be modeled as a current source  $i_s$  with a shunt capacitance  $C_s$  and a shunt resistance  $R_s$ , as shown in Fig. 2.1., where the shunt capacitance is formed by the ionic double layer in an electrochemical cell, the gate oxide in a nanotube or an ion-sensitive field-effect transistor (ISFET), or the lipid bilayer membrane in a nanopore. The capacitance is on the order of a few pF when the sensor is tightly integrated with a CMOS readout circuit [14, 15] and can be more than nF for off-chip biosensors [9, 18]. Meanwhile, the shunt resistance is a charge transfer resistance of 1 - 100 M $\Omega$  in an electrochemical cell or the leakage in a nanotube/nanopore and often >1 G $\Omega$ . This simplified model with an output impedance  $Z_s$  provides a first-order circuit for the analysis of the amplifier's performance while more accurate models of each type of biosensor can be found in the literature, if needed [14].

**Figure 2.1:** Simplified model for a current-based biosensor.

The amplifier can be categorized into either: 1) a current-to-current amplifier or 2) a current-to-voltage amplifier. The conventional implementations of these are a current conveyor (CC) and a transimpedance amplifier (TIA), respectively. The signals after amplification can be filtered and then quantized into a discrete-time digital signal by an ADC for further analysis. Although the amplifier and the ADC can be designed separately, a current-input ADC provides a lower noise, higher linearity, and lower power consumption when the ADC is designed to amplify and quantize the input signal at the same time. For example, a current-input  $\Delta\Sigma$  modulator (DSM) uses global feedback to improve the linearity as well as reduce power consumption. An oscillator-based ADC is another example that provides signal amplification from current to time domain and quantizes this time information efficiently in a mostly digital way.

Most commercial instrumentations are based on different TIA architectures, such as the Axon Axopatch 200B [19, 20] and Stanford Research Systems SR570 [21]. However, being more general-purpose instrumentation, these are quite large and power-hungry devices. CMOS integrated circuit miniaturization shrink complex current-sensing architectures into silicon chips and offer a unique opportunity to cointegrate biosensors directly with the readout circuit. The integration of the sensor and amplifier provides a lower noise due to a reduction in interconnection capacitances. This enables biosensing and point-of-care applications and arranges high, density compact arrays for high throughput applications. The implementation and

performance details of a CC, TIA, and current-input ADC are discussed in the following section.

# 2.2 Current Conveyor

A current conveyor amplifies low currents while providing a clamping voltage bias for the biosensor. The CC is essentially a buffer decoupling the input and output impedances while providing amplification so the noise and performance requirement of the following stages are relaxed. Fig. 2.2 shows a schematic of a CC. The CC takes an input current from node *X* and provides an amplified output current at a high output impedance node *Z*. Node *Y* can be connected to a well-defined voltage to clamp the voltage at node *X* for the necessary bias voltage of the sensor.

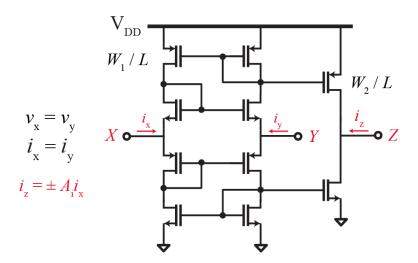

Figure 2.2: Schematic of a current conveyor.

The sensor current flowing into node X is copied to node Z with a high impedance output. The gain of the CC is determined by the ratio of the current mirror between branch X and Z, which can be simplified as  $A_i = W_2/W_1$  when all the transistors have the same channel length, L. This current is also mirrored to node Y, so the voltage at the node X is a virtual short to an external voltage applied at node Y by the feedback loop.

The input-referred current noise of the CC can be calculated by adding the current noise from the all the transistors together directly when both the input and output are currents

$$S_{i,CC} = 8\left(4kT\gamma g_{m1} + \frac{K_f}{C_{ox}W_1Lf}\right) + \frac{2}{A_i}\left(4kT\gamma g_{m2} + \frac{K_f}{C_{ox}W_2Lf}\right),$$

(2-1)

where k is Boltzmann's constant, T is the absolute temperature,  $C_{ox}$  is the gate oxide capacitance per unit area,  $\gamma$  and  $K_f$  are the process dependent thermal and flicker noise coefficients, respectively, f is the frequency, and  $g_m$  is the transconductance of each stage, which is determined by both the input signal and the bias current of the CC. The overall noise resulting from the sum of the sensor current plus the conveyor bias current. The current noise of a CC can be reduced by biasing the current mirror in deep saturation region, i.e., larger  $V_{gs}$ - $V_t$  with a smaller  $g_m/I_d$ . When the input current increases, the  $|V_{gs}|$  of the current mirror increases and moves the operation of the cascode transistors into the triode region. This causes a feedback error and sets the maximum allowable input current of a CC. A CC usually achieves a noise power spectrum density higher than 1 pA/ $\sqrt{Hz}$  and a dynamic range of 60 dB [14, 22].

## 2.3 Transimpedance Amplifier

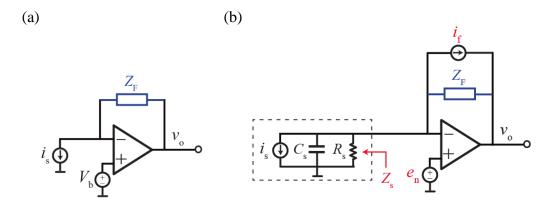

A TIA converts a current input to a voltage output. The basic TIA structure is implemented based on an amplifier with a feedback element  $Z_f$ , either a resistor, a capacitor, or a diode, which determines the gain of the TIA, as shown in Fig. 2.3. The virtual ground at the input of the amplifier provides: 1) a DC voltage  $V_b$  to bias a sensor in the wanted operation region and 2) a near-zero input impedance for current measurement.

The input-referred noise of a TIA can be analyzed when the two noises source are uncorrelated. The amplifier noise can be modeled as an input-referred voltage source  $e_n$  at the non-inverting input node of the amplifier, so the output-referred noise is  $(1+Z_F/Z_s)e_n$  where  $Z_s$  is the output impedance of the sensor. Thus, the total input-referred current noise can be obtained from this quantity divided by the closed loop gain.  $V_b$ ,  $e_n$  and  $Z_s$  are not drawn in the later figures for simplicity but included for analysis.

**Figure 2.3:** Schematic of (a) a transimpedance amplifier, and (b) equivalent circuit with noise sources.

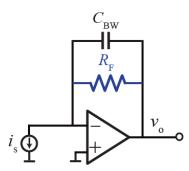

### 2.3.1 Resistive Feedback TIA

Figure 2.4 shows a schematic of a resistive feedback TIA (R-TIA). The gain of the R-TIA is determined by the feedback resistor,  $R_f$ , where the output voltage  $v_o = i_s \times R_F$ . The noise from the feedback component is  $i_f^2 = 4kT/R_f$ , so the total input-referred current noise power density is

$$S_{i,R-TIA} = \frac{4kT}{R_f} + \left(\frac{1}{(R_s//R_f)^2} + s^2 C_s^2\right) e_n^2.$$

(2-2)

The feedback resistor generates noise in addition to the noise from the amplifier, so the noise from  $R_f$  should be minimized. For example,  $R_f$  should be larger than 165 M $\Omega$  to obtain a current noise density less than 10 fA/ $\sqrt{Hz}$ . An additional shunt capacitor  $C_{BW}$  can be used to reduce the total noise by controlling both the bandwidth of the R-TIA and the wideband white noise. This  $C_{BW}$  can also stabilize the amplifier when the parasitic capacitances from  $R_f$  and the inverting input node of the amplifier affects the stability of a R-TIA. Therefore, the minimum detectable signal of R-TIA can be determined and is usually limited by the extra noise from the feedback resistor in a well-designed low noise amplifier.

Figure 2.4: Schematic of an R-TIA.

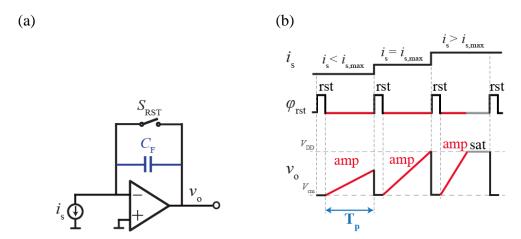

### 2.3.2 Capacitive Feedback TIA

A capacitive feedback TIA (C-TIA) as shown in Fig. 2.5(a) is an amplifier with a capacitor,  $C_F$ , in feedback. The C-TIA provides a gain of  $1/sC_F$ , which decreases by 20 dB/decade. The total input-referred current noise density can be derived as

$$S_{i,C-TIA} = \left(\frac{1}{R_s^2} + s^2(C_s + C_F)^2\right)e_n^2.$$

(2-3)

As such, a smaller  $C_F$  increases the gain and reduces the input-referred noise but must be reset more often for large currents. The noise in a C-TIA is less than that of an R-TIA because of the lack of noise from the feedback element.

Due to the infinite gain at DC, a periodic reset switch is required to prevent the saturation of  $C_F$ , so the DC gain equals to  $T_p/C_f$ , with an amplifying period of  $T_p$ . This periodic reset limits the maximum input current to be less than  $i_{s,max} = C_f V_{DD}/T_p$  so the C-TIA does not saturate before the next reset phase, as shown in Fig. 2.5. To improve the DR of a C-TIA, a smaller  $T_p$  or larger  $C_f$  can be chosen, but this results in a tradeoff with a decreased DC gain and increased noise.

Figure 2.5: (a) Schematic and (b) waveform of a C-TIA.

## **2.3.3 Log TIA**

A logarithmic TIA (Log-TIA) with a diode in feedback provides a wide input dynamic range by converting the input current in linear scale to an output voltage in log scale, as shown in Fig. 2.6 [23]. The gain of a Log-TIA is obtained by the current-voltage relationship of the feedback diode:  $v_0 = V_{\text{th}} \ln(i_s/I_{\text{S}})$ , where  $V_{\text{th}}$  is the thermal voltage (i.e., kT/q) and  $I_{\text{S}}$  is the reverse bias saturation current.

The total input-referred current noise density can be derived as

$$S_{i,\text{Log-TIA}} = 2qi_s + \left(\frac{1}{(R_s||r_D)^2} + s^2C_s^2\right)e_n^2,$$

(4)

where  $r_D$  is the small-signal resistance of the diode (i.e.,  $V_{th}/i_s$ ). Both the noise and feedback impedance from the diode are signal dependent, where the noise of a Log-TIA is dominated by the second term in (4) due to the squaring relationship between the noise power and input current  $i_s$ . Therefore, this noise only limits the maximum SNR rather than the DR.

The design challenges in a Log-TIA are the temperature stability and linearity. Due to the temperature dependence of the current-voltage relationship, a Log-TIA requires an additional compensation circuit which contributes extra noise [24]. Also,

Figure 2.6: Schematic of a bidirectional Log-TIA.

the higher-order non-linearity of this current-voltage relationship introduces distortion in a Log-TIA of more than 1% (in linear scale) over a 100 dB DR, such as Analog Device ADL5304 [25] or Texas Instruments LOG112 [26].

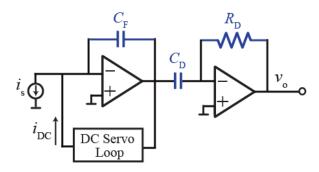

#### 2.3.4 Wideband TIA

In Fig. 2.7, a wide, flat-gain bandwidth and low noise TIA is obtained using an integrator-differentiator structure where the C-TIA serves as a low-noise amplifier and the pole of the C-TIA is cancelled by the zero in the differentiator [16, 17, 27, 28]. The gain is constant as  $R_dC_d/C_f$  up to over 1 MHz, which is limited by the bandwidth of the amplifiers or the parasitic capacitance from  $R_d$ . The DC servo loop discharges the slowly varying background signal, i.e., near DC components, so that the C-TIA only amplifies the AC signal of interest. Therefore, the transfer function of TIA is a bandpass filter with a low cutoff frequency, and the overall DR of is improved by 2 to 3 orders depending on the maximum available current from the DC servo loop.

**Figure 2.7:** Schematic of a wideband TIA.

The total input-referred current noise density can be derived as

$$S_{i,\text{WB-TIA}} = i_{\text{FB}}^2 + \left(\frac{1}{R_{\text{S}}^2} + s^2(C_{\text{S}} + C_{\text{F}})^2\right) e_{\text{n1}}^2 + \left(\frac{C_{\text{F}}}{C_{\text{D}}}\right)^2 \left(\frac{1}{R_{\text{D}}^2} + s^2C_{\text{D}}^2\right) e_{\text{n2}}^2, \tag{2-4}$$

where  $i_{FB}$  is the total current noise contributed by the DC servo loop, and  $e_{n1}$  and  $e_{n2}$  are the input-referred voltage noises from the first and the second amplifier, respectively.

## 2.4 Current-Input ADC

In this section, two types of current-input ADCs are discussed.

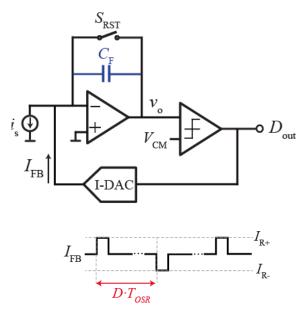

#### 2.4.1 Delta-Sigma Modulator

Figure 2.8 shows a current-input  $\Delta\Sigma$  modulator providing high resolution by oversampling and placing the C-TIA in a global feedback loop where the C-TIA provides the necessary high transimpedance gain and low input-referred noise. With a fixed feedback current, this DSM can quantize small input current by reducing the duty cycle, D, of the feedback current. This is because the equivalent feedback current is scaled down by the same ratio, e.g., 1-bit I-DAC equals to multi-bit I-DAC by tuning the duty cycle. By programming the duty cycle over 5 orders, this DSM can achieve 160 dB dynamic range with the oversampling technique while the DSM with a fixed D provides 60 dB dynamic range.

Figure 2.8: Schematic of a DSM.

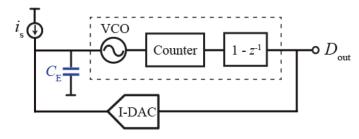

#### 2.4.2 Oscillator-based ADC

An input signal can also be used to control the frequency of an oscillator, where the signal is subsequently quantized in either the frequency or phase domain [29, 30]. An oscillator-based ADC is essentially an open-loop DSM, so the linearity is very sensitive to any circuit non-idealities. This can be overcome when such an ADC is implemented as a closed-loop current input DSM, as shown in Fig. 2.9, where a passive current-to-voltage integrator, i.e., a capacitor  $C_E$ , is used as the first stage and a voltage-controlled oscillator (VCO) is used as a first-order, noise-shaping quantizer. The input current is amplified and converted to a voltage when the charge integrates on  $C_E$ , and this voltage is quantized by the VCO-based ADC. The feedback loop with an I-DAC minimizes the voltage swing on  $C_E$ , so the non-linearity of the VCO-based ADC is suppressed. The passive integrator  $C_E$  can be implemented using an explicit

designed on-chip capacitor [29] or the intrinsic capacitance from the sensor [30]. The structure should be very carefully design when the capacitance is either voltage dependent or introducing larger input-referred current noise when  $C_E$  increasing the equivalent sensor impedance  $C_S$  in (2).

Figure 2.9: Schematic of a VCO-based ADC.

## 2.5 Summary and Comparison

The performance of each type of current amplifier and current-input ADC was analyzed, and Table 2.1 summarizes the design trade-offs of these front-ends. Because the requirements of low noise in biological applications, a C-TIA based architecture is preferable, such as a wideband TIA or a current-mode DSM. However, the DR and power efficiency of these architectures should be further improved to detect widerange signals from biosensors.

**Table 2.1:** Comparison of conventional current-sensing front-ends.

|                         | Bandwidth | Gain | Noise | Dynamic<br>Range | Operation     | Quantizer | Linearity |

|-------------------------|-----------|------|-------|------------------|---------------|-----------|-----------|

| <b>Current Conveyer</b> | ++        | -    |       |                  | Continuous    | No        | -         |

| R-TIA                   |           | +    |       | -                | Continuous    | No        | +         |

| C-TIA                   | -         | ++   | +     | +                | Discrete      | No        | +         |

| Log-TIA                 | +         | +    | -     | ++               | Continuous    | No        | -         |

| Wideband TIA            | ++        | ++   | +     | -                | Continuous No |           | +         |

| <b>Current-Mode DSM</b> |           | ++   | +     | ++               | Discrete      | YES       | +         |

| Signal-based ADC        | +         | ++   | +     | +                | Continuous    | YES       | +         |

# Chapter 3

## A Hybrid Semi-Digital Transimpedance

## **Amplifier with Noise Cancellation Technique**

## for Nanopore-Based DNA Sequencing

In this chapter, I present a hybrid semi-digital transimpedance amplifier (HSD-TIA) to sense the minute current signatures introduced by single-stranded DNA (ss-DNA) translocating through a nanopore, while discharging the baseline current using a semi-digital feedback loop. The amplifier achieves fast settling by adaptively tuning a DC compensation current when a step input is detected. A noise cancellation technique reduces the total input-referred current noise caused by the parasitic input capacitance. Measurement results show the performance of the amplifier with 31.6 M $\Omega$  mid-band gain, 950 kHz bandwidth, and 8.5 fA/ $\sqrt{\text{Hz}}$  input-referred current noise,

a 2× noise reduction due to the noise cancellation technique. The settling response is demonstrated by observing the insertion of a protein nanopore in a lipid bilayer, and ssDNA translocation events were measured by the HSD-TIA.

#### 3.1 Introduction

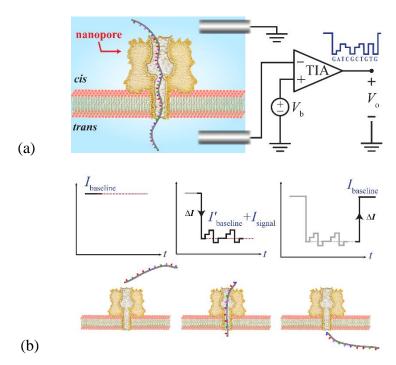

Nanopore-based DNA sequencing has been under active development since 1995 [11, 12, 31-38]. It is a biophysical technique to sequence DNA based on the physical properties of the four types of nucleotides - guanine (G), adenine (A), thymine (T), and cytosine (C) - the building blocks of DNA. A nanopore is a small orifice, usually only a few nanometers in diameter, sandwiched between two fluidic chambers, the cis and trans, as shown in Fig. 3.1(a). When the nanopore is immersed in an ionic buffer with a bias voltage  $V_b$  applied between the two chambers, a baseline current I<sub>baseline</sub> is generated from the ions that drift through the nanopore. As DNA, being negatively charged, translocates through the pore, a current blockade occurs due to the different size and charge distribution of the nucleotides inside of the nanopore. One can, in theory, reconstruct the nucleotide sequence of single-stranded DNA (ssDNA) by observing the characteristic amplitude changes. Compared to conventional sequencing methods [31], nanopore-based methods are more efficient using only electrical and physical features of DNA without the need for complicated optical detection steps or custom nucleotides.

**Figure 3.1:** (a) Illustration of a nanopore-based DNA sequencing platform. (b) The baseline current shift that occurs when a ssDNA translocates.

Two main techniques are used to create nanopores: solid-state fabrication [11, 33, 34] and biological proteins (porin) [35-38]. Solid-state nanopores utilizes semiconductor manufacturing techniques, whereas a porin is a natural protein in the shape of a tube inserted in a lipid bilayer. Controlling the spatial and temporal resolution of nanopores is an active area of research where researchers are investigating methods to control the translocation speed and engineering thin, narrow pores to reduce the interrogation region [34]. Both types of pores require instrumentation to measure the small current differences between nucleotides, often less than 10 pA, in the presence of the baseline ionic current, which can be more than 1,000× larger [34]. Uncontrolled, the speed of ssDNA translocating through a

nanopore can be faster than one nucleotide per microsecond. Thus, the requirements of the current-sensing circuits for nanopores are quite demanding: high gain (>10  $M\Omega$ ), high bandwidth (>10 kHz), low noise (<10 pA<sub>RMS</sub>), and wide dynamic range.

Another more application specific challenge in nanopore-based DNA sequencing is the abrupt change in baseline current that occurs when a protein nanopore inserts or leaves a lipid bilayer [28]. Considering the protein nanopore lifetime, the time period when a pore is inserted into a lipid bilayer, can be as short as several seconds at room temperature [39], it is essential to minimize the settling time of the amplifier. This requirement for low settling time also applies when ssDNA enters or leaves the pore impeding the flow of ions, reducing the baseline current by 30-90% [34], as shown in Fig. 3.1(b). This change in *I*<sub>baseline</sub> is inversely proportional to the size of the pore. In our setup, using a protein nanopore with a diameter of 1.4 nm, the baseline current is reduced by 83-95% by the presence of ssDNA. Therefore, the step response of the current-sensing circuit must be minimized to prevent missing any current signatures during the settling of the circuit [28].

A TIA functions as a current-sensing circuit to convert the current input into a voltage output for further processing and analysis [14, 15]. Resistive and capacitive TIAs are widely used in many commercial instruments, such as the Axopatch 200B [20]. However, these topologies have notable drawbacks in this application. Namely, they either have large input-referred noise and low bandwidth, as is the case for a resistive feedback TIA [14, 15], or must be constantly reset since  $I_{\text{baseline}}$  can saturate the amplifier in a capacitive feedback TIA [40, 41]. This large  $I_{\text{baseline}}$  also increases

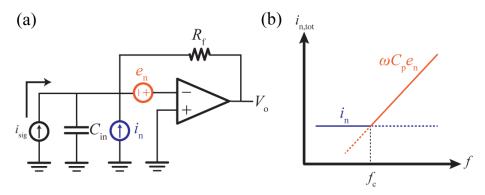

**Figure 3.2:** (a) Conventional resistive feedback TIA with voltage and current noise model. (b) The corresponding power spectrum density (PSD) of the input-referred current noise. The high frequency noise of the TIA is dominated by the input capacitor  $C_{\rm in}$  and the voltage noise  $e_{\rm n}$ .

the dynamic range requirement of the TIA [33]. A TIA with a DC feedback loop is one method to achieve low noise and high bandwidth [17, 27] without the need for a reset network; however, the limited bandwidth of the feedback loop requires long settling time for a step-input current, such as when a pore is inserted into the lipid bilayer [28].

As the bandwidth is increased, the sensitivity of a TIA is limited by the quadratic growth of total integrated input-referred current noise [14, 15]. The TIA in Fig. 3.2 has two noise sources: a current noise in and a voltage noise  $e_n$  from the OPAMP, neglecting noise from the feedback resistor. The input-referred current noise density is:

$$\overline{\iota_{n,tot}^{2}(\omega)} = \overline{\iota_{n}^{2}} + \overline{e_{n}^{2}}\omega^{2}C_{in}^{2}, \tag{3-1}$$

where  $C_{in}$  is the total capacitance at the input node of the TIA. At low frequencies, the input-referred current noise density is approximately equal to the current noise in and the noise from  $e_n$  can typically be ignored. However, the second term in (1) produced

by the  $e_n$  and  $C_{in}$  dominates when the bandwidth increases beyond the noise corner frequency  $f_c$ , which is often only several kilohertz because  $C_{in}$  is predominantly caused by the capacitance of the nanopore [33]. Depending on how the pore is realized, it may not be possible to reduce this capacitance. Hence, the input-referred current noise must be reduced by either using circuit techniques or actively cooling the system [14] when the bandwidth is greater than 10 kHz.

In this paper, we describe a hybrid semi-digital TIA (HSD-TIA) with high flat-gain bandwidth and very low noise. The HSD-TIA continuously measures the input current without a reset switch by discharging the baseline current through a semi-digital feedback loop. In addition to servoing out the DC and low frequency baseline currents, this loop also adaptively provides a DC compensation current for fast step response. A noise cancellation technique is shown to reduce the input-referred current by partially cancelling the second term of (3-1).

The architecture of the proposed HSD-TIA with noise cancellation technique is introduced in Section 3.2. In Section 3.3, the semi-digital feedback loop with fast step response is explained. The noise cancellation technique and noise performance of the TIA are analyzed in Section 3.4. Section 3.5 focuses on the implementation of the proposed TIA, and the measurement results are presented in Section 3.6. Using the designed TIA, the biological measurements are shown in Section 3.7. Finally, conclusions are in Section 3.8.

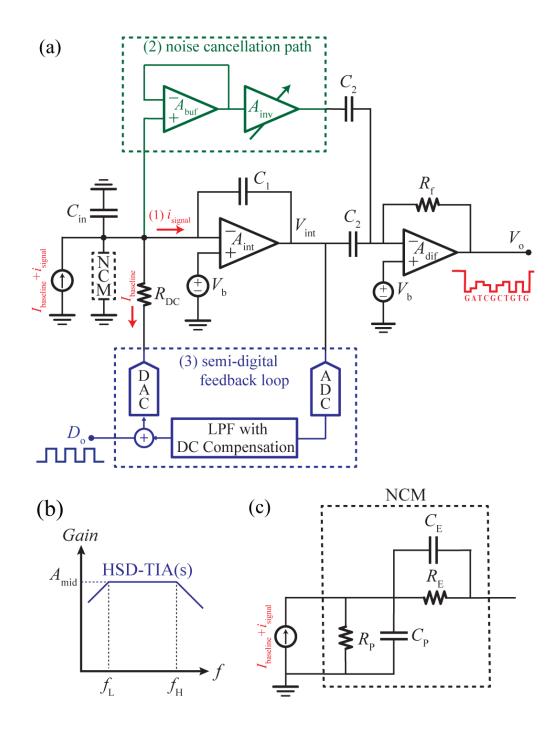

**Figure 3.3:** (a) Architecture of the HSD-TIA with noise cancellation technique. (b) The frequency response of HSD-TIA with low cutoff frequency  $f_L$  introduced by the semi-digital feedback loop and high cutoff frequency  $f_H$ . (c) Equivalent nanopore circuit model.  $R_P$  and  $C_P$  are the nanopore resistance and capacitance, and  $R_E$  and  $C_E$  are from the Ag/AgCl electrodes.

#### 3.2 The Architecture of the HSD-TIA

We describe a HSD-TIA with a noise cancellation technique to obtain low noise, fast settling time, and continuous operation for nanopore-based DNA sequencing as shown in Fig. 3.3. The HSD-TIA contains three paths: (1) the signal path to amplify the input current at mid-band, (2) the feedback path to discharge the low-frequency components, including the baseline current and flicker noise (1/f), and (3) the feed-forward noise cancellation path to remove the voltage noise from the integrator. The signal path of the TIA consists of a capacitive feedback integrator that is cascaded with a differentiator to obtain high flat-gain bandwidth. The high cutoff bandwidth,  $f_H$ , is obtained by cancelling a DC pole from the integrator with a DC zero from the differentiator. The mid-band gain is:

$$A_{\text{mid}} = R_{\text{f}} \times C_2/C_1 \tag{3-2}$$

where  $C_1$  is the feedback capacitor in the integrator, and  $C_2$  and  $R_f$  form the differentiator. The transfer function of the HSD-TIA is shown in Fig. 3.3(b).

The semi-digital feedback path is wrapped around the integrator to discharge the low frequency components, particularly the baseline current and 1/f noise. The feedback loop introduces poles and zeros to shape the low-frequency response [17, 27]. The lower cutoff frequency  $f_L$  needs to be as low as a few tens of Hz to prevent loss of signal for nanopores with low DNA translocation speed, such as engineered MspA [36, 37] and motor controlled pores [38]. The frequency of these poles and zeros must be carefully designed to avoid attenuating the signal at mid-band and to maintain stability of the amplifier. Here, the poles and zeros are implemented by a

digital low-pass filter (LPF) in the feedback path. Compared to the variation of an analog implementation using discrete components with large resistances and capacitances [17, 27], the frequency of the poles and zeros can be precisely controlled in the digital domain.

Another advantage of this approach is the direct accessibility of the digitized low-frequency component, which is filtered out in an analog implementation that contains relevant biological information, such as the size of the nanopore and the number of nanopores inserted in a lipid bilayer. Compared to an analog feedback loop, an additional ADC, DAC, and FPGA are needed to implement the filter. However, the feedback signal may be digitized anyway, so we are merely pushing the ADC inside the feedback loop. The low-frequency nature of this loop does not necessitate high performance data converters.

The settling behavior of the HSD-TIA is determined by the bandwidth of the feedback loop, i.e., the low cutoff frequency,  $f_L$ . When a step-input current occurs, the baseline current accumulates on the integrator capacitor during the settling of the feedback loop. This step-input current can be as large as 95% of  $I_{baseline}$  [34], which can easily saturate the output of the integrator since the feedback loop discharges the accumulated current slower than the integrator saturation rate, resulting in loss of the input signal during settling. We utilize an adaptive DC compensation current in the feedback loop to improve the settling behavior. A digital logic circuit in the FPGA detects the occurrence and magnitude of the input step by tracking the integrator output and checking if it exceeds a predefined window. The feedback loop then

adaptively produces a DC compensation current by adding a digital code  $D_0$  with the opposite sign of the step to the output of the filter. This compensation current reduces the difference between the feedback current and baseline current without having to wait for the LPF to settle and prevents saturation of the integrator resulting in a significant reduction of the settling time.

The noise of a high bandwidth TIA is dominated by  $C_{\rm in}$  and  $\bar{e}_{\rm n}^2$  at high frequencies (3-2) where  $C_{\rm in}$  is the capacitance of nanopore including the fluidic interface [33, 42], the input capacitance of the OPAMP, and cable parasitic capacitances.  $C_{\rm in}$  is often 10 pF, even when co-integrating the nanopore and TIA [33]. Thus, there is a fundamental limit to how much  $C_{\rm in}$  can be reduced necessitating alternative methods to reduce the noise. Here, we propose a noise cancellation technique to reduce the input-referred current noise by sensing and subtracting the voltage noise  $e_{\rm n}$ . This feed-forward noise cancellation path contains a voltage-sensing amplifier and an inverting amplifier with matched gain, such that the noise from the signal and noise cancellation paths add destructively when the output of the two stages are combined. As shown in Fig. 3.3, the condition to cancel this voltage noise is:

$$e_{\rm n} \times (C_{\rm i} + C_{\rm p})/C_{\rm i} = e_{\rm n} \times |A_{\rm inv}| \tag{3-3}$$

Thus, the voltage noise  $e_n$  from the integrator is cancelled by summing the inversely duplicated version of the same voltage noise from the noise cancellation path. Note that no input signal is amplified by the noise cancellation path [43, 44] because the input voltage of the HSD-TIA is clamped by the virtual ground. The equivalent nanopore circuit model (NCM) [14, 15, 45], shown in Fig. 3.3(c), is considered when

analyzing the stability and noise performance of the TIA.

In summary, the semi-digital feedback loop performs several functions: 1) it discharges the baseline current preventing saturation of the integrator and allowing continuous operation without the need for the reset network that is common in a capacitive TIA [40, 41], 2) it provides precise control of the low-frequency response and 3) it improves the settling response through an adaptive current. The TIA noise performance is improved by feed-forward cancellation of the integrator voltage noise and the removal of the 1/f noise in the feedback loop. Collectively, these relax the requirements of the integrator, particularly the voltage noise and input capacitance.

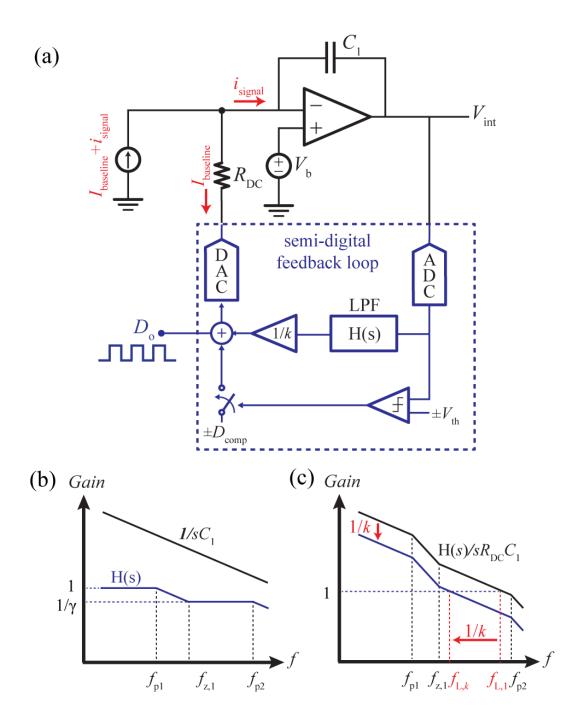

## 3.3 Semi-Digital Feedback Loop

The semi-digital feedback loop consists of two main components: a low pass filter and a DC compensation block, as shown in Fig. 3.4(a). The circuits are implemented digitally to guarantee the stability of the feedback loop without attenuating the desired signal. The frequency response of the feedback path, shown in Fig. 3.4(b) and (c), can be controlled efficiently, precisely, and adaptively in the digital domain.

### 3.3.1 Digital Filter

The semi-digital feedback path is composed of an ADC, a LPF, and a DAC. The LPF removes the high frequency signals from the output of the integrator and feeds the resulting signal back to the input of HSD-TIA. Thus, the baseline current is

**Figure 3.4:** (a) Concept of the semi-digital feedback loop. (b) Frequency response of integrator and LPF. (c) Frequency response of the loop gain with the tuning factor 1/k. The tuning factor 1/k is implemented to tune the low cutoff frequency  $f_L$  and the stability of the feedback loop.

discharged through a resistor RDC by the feedback loop. The ideal loop gain of this feedback path (Fig. 3.4) can be derived as,

$$G(s) = -\frac{H(s)}{sR_{\rm DC}C_1},\tag{3-4}$$

where H(s) is the transfer function of the digital LPF. Without loss of generality, H(s) is assumed to have a pole  $f_{p1}$ , one or more high frequency poles  $f_{p2}$ , a zero  $f_{z1}$ , passband gain of unity, and an attenuation ratio of  $\gamma$  in the stopband. The low cutoff frequency  $f_L$  of the HSD-TIA can be derived from unity gain frequency of this loop, i.e.,  $|G(2\pi f_L)|=1$ :

$$f_L = \frac{1}{2\pi\gamma R_{\rm DC}C_1}. (3-5)$$

Considering the stability of a feedback loop, the additional poles introduced by the digital filter reduce the closed loop phase margin [17, 27]. A positive tuning factor k added in the digital domain to control the frequency response of the feedback loop and set the low cutoff frequency  $f_L$ . Changing the value of k shifts the magnitude response and the unity gain frequency  $f_L$  while keeping the phase response unchanged, thus allowing one to tune the frequency of  $f_L$  dynamically while guaranteeing the phase margin of the feedback loop. We define  $f_{L,k}$  as the unity gain frequency with a tuning factor of 1/k. When 1/k is less than 1, the magnitude response shifts down, and  $f_{Lk}$  decreases by k with respect to  $f_{L,1}$ ; that is:

$$f_{\mathrm{L},k} = \frac{1}{2\pi\gamma k R_{\mathrm{DC}} C_1}.\tag{3-6}$$

By carefully choosing k and the -3dB frequency of the LPF, it is possible to maintain a phase margin of the low-frequency feedback loop greater than 45°. Hence, the

stability of the feedback loop is obtained by tuning k even with variation of  $R_{DC}$  and  $C_1$ . A DC gain larger than unity in H(s) could also be implemented to improve the stability; however, a higher order filter is required resulting in longer settling time.

The LPF is implemented in the digital domain with a sampling frequency of  $f_s$ . With a fixed  $f_s$  and  $f_L$ , one can save power and area in the LPF using a lower order LPF with a large  $f_{p1}$  and small 1/k. However, the static gain error at the output of the integrator depends on the feedback factor at low frequency. That is:

$$\Delta V_{\rm int} = \Delta I_{\rm baseline} R_{\rm DC}/k, \tag{3-7}$$

where  $\Delta V_{\rm int}$  is the static gain error. The static gain error shifts the output common-mode voltage and limits the output swing of the integrator, so the value of k must be chosen carefully. For example, an input-step current of 100 pA with  $R_{\rm DC}$  of 1 G $\Omega$  and 1/k of 0.1 causes a static gain error of 1 V. This large static gain error can saturate the integrator especially with a low power supply voltage. The DC compensation current described later mitigates this problem and allows one to reduce the area and power of this digital LPF by using a lower order filter.

#### 3.3.2 DC Compensation Current

A DC compensation current is added to reduce the settling time and prevent the integrator from saturating when a step-input current occurs. In order to implement this, a digital comparator monitors the digitized integrator output. Once the integrator output exceeds a predefined voltage range, a DC compensation code  $D_{\text{comp}}$  is added to the output of the LPF. The output voltage of the integrator with the DC compensation current can be written as:

$$D_{\text{o.norm}}(t) = D_{\text{comp.norm}} + (1 - D_{\text{comp.norm}})(1 - e^{-t/\tau}), \tag{3-8}$$

where  $D_{0,norm}$  and  $D_{comp,norm}$  are the digital codes of the feedback loop and DC compensation normalized to the amplitude of the step-input current,  $\tau$  is the closed-loop time constant, and V(D) is the corresponding analog voltage of the digital code D. The feedback loop estimates the size of the step-input current by measuring the static gain error of the feedback loop from (3-7), and a digital code  $D_{comp}$  is calibrated based on this static gain error. The gain error is readily obtained in the digital domain because this gain error shows up at the output of the integrator and is digitized by the ADC. The algorithm is as follows: initially,  $D_{comp}$  is set to zero; once a step current is detected, the current of this step-input is measured. Then, a new digital code  $D_{comp}$  is updated and used for all later measurements since the size of the step-input current is roughly constant throughout the experiment. Using this technique, the settling time is reduced from  $5\tau$  to  $2\tau$ , a 60% reduction in settling time with a settling error of 0.7% when  $D_{comp}$  is 95% of the step.

The other benefit of the DC compensation current is the reduction in the static gain error due to the tuning factor in (3-7). When the  $D_{\rm comp}$  is used, most of the discharging current is provided by  $D_{\rm comp}$  rather than the feedback loop. The loop gain error can be reduced to:

$$\Delta V_{\rm int} = |\Delta I_{\rm baseline} R_{\rm DC} - V(D_{\rm comp})|, \tag{3-9}$$

Hence, the DC compensation current can both decrease the static gain error of the integrator and reduce the settling.

**Figure 3.5:** Schematic of feedforward noise cancellation circuit. The integrator voltage noise is sensed and amplified by the noise cancellation path.

## 3.4 Noise Cancellation Technique and Noise Analysis

### 3.4.1 Noise Cancellation Technique

The proposed noise cancellation technique requires a low-noise voltage buffer to sense the voltage noise from integrator, and an amplifier to provide the matched gain between the noise cancellation path and the integrator [43, 44], as shown in Fig. 3.5. Due to the virtual ground at the input of the integrator, the voltage noise of the integrator can be sensed by a unity gain buffer. This sensed voltage noise is then amplified by a tunable inverting amplifier. From (3-3), the value of  $R_{c1}$  and  $R_{c2}$  are tuned to obtain the optimized noise cancellation effect with respect to the input

capacitance from nanopore and cable connections.

#### 3.4.2 Noise Analysis

To analyze the total-referred input current noise density of the HSD-TIA in the signal band, we first neglect the noise cancellation path. The equivalent input noise is given by

$$\overline{\iota_{n,\text{tot}}^{2}}(\omega) = \overline{\iota_{n1}^{2}} + \overline{e_{n1}^{2}} \omega^{2} \left(C_{1} + C_{p}\right)^{2} + \frac{\overline{e_{n1}^{2}}}{R_{DC}^{2}} + \frac{4kT}{R_{DC}} + \frac{\overline{e_{Q}^{2}}}{k^{2} \gamma^{2} R_{DC}^{2}} + \left(\frac{C_{1}}{C_{2}}\right)^{2} \left(\overline{\iota_{n1}^{2}} + \overline{e_{n1}^{2}} \omega^{2} C_{2}^{2} + \frac{\overline{e_{n2}^{2}}}{R_{f}^{2}} + \frac{4kT}{R_{f}}\right),$$

(3-10)

where  $\overline{\iota_{n1}^2}$ ,  $\overline{e_{n1}^2}$ ,  $\overline{\iota_{n2}^2}$ , and  $\overline{e_{n2}^2}$  are the current and voltage noises of the OPAMPs in the integrator and differentiator, respectively;  $C_{in}$  is the total capacitance at the input of the HSD-TIA, including the input node of integrator, the connection between the TIA, and the capacitance of the lipid bilayer; and  $\overline{e_Q^2}$  is the noise from the digital circuits, including the quantization error of the ADC and digital LPF. For simplicity, the integrated digital noise  $\overline{e_{Q,rms}^2}$  is taken to be only the ADC quantization noise,  $V_{LSB}^2/12$  over the bandwidth of the feedback loop which is attenuated by the tuning factor k. The ratio of  $C_2/C_1$ , which forms part of the gain of the TIA, is much greater than unity by design, so the input-referred noise of the TIA is approximately

$$\overline{\iota_{\rm n,tot}^2}(\omega) \cong \overline{\iota_{\rm n1}^2} + \overline{e_{\rm n1}^2} \omega^2 (C_1 + C_{\rm in})^2 + \frac{4kT}{R_{\rm DC}} + \frac{\overline{e_{\rm Q}^2}}{k^2 \gamma^2 R_{\rm DC}^2} + \left(\frac{C_1}{C_2}\right)^2 \frac{4kT}{R_{\rm f}}.$$

(3-11)

Note that the input-referred current noise of the TIA, like the resistive feedback TIA, is dominated by the second term in (11) at frequencies higher than  $f_c$ .

Next, we analyze the input-referred current noise with the noise cancellation

technique using similar steps

$$\overline{\iota_{n,\text{tot}}^{2}}(\omega) \cong \left(\overline{\iota_{n1}^{2}} + \overline{\iota_{nc1}^{2}}\right) + \alpha^{2} \overline{e_{n1}^{2}} \omega^{2} (C_{1} + C_{\text{in}}')^{2}

+ \left(\overline{\iota_{nc2}^{2}} \cdot R_{c1}^{2} || R_{c2}^{2} + 4kT R_{c1} \frac{R_{c2}^{2}}{R_{c1}^{2}} + 4kT R_{c2}\right) \omega^{2} C_{1}^{2}

+ \overline{e_{nc1}^{2}} \omega^{2} (C_{1} + C_{\text{in}}')^{2} + \frac{4kT}{R_{DC}} + \frac{\overline{e_{0}^{2}}}{k^{2} \gamma^{2} R_{DC}^{2}} + \left(\frac{C_{1}}{C_{2}}\right)^{2} \frac{4kT}{R_{f}},$$

(3-12)

where  $\overline{\iota_{\rm nc1}^2}$ ,  $\overline{e_{\rm nc1}^2}$ ,  $\overline{\iota_{\rm nc2}^2}$ , and  $\overline{e_{\rm nc2}^2}$  are the current and voltage noises of the OPAMPs in the voltage buffer and the inverting amplifier and  $C_{\rm in}'$  is the total input capacitance at the input of the HSD-TIA after adding the noise cancellation path. We define a  $\alpha$  as the residual noise factor after noise cancellation where

$$\alpha = \left| 1 - \frac{R_{c2}/R_{c1}}{(c_i + c'_{in})/c_i} \right|. \tag{3-13}$$

The noise at frequencies higher than fc is reduced significantly, by a factor of  $\alpha$ , with the trade-off of slightly increased noise at low frequencies due to the additional term  $\overline{\iota_{\rm nc1}^2}$ . The noise from the inverting amplifier can be neglected because  $R_{\rm c1}$ ,  $R_{\rm c2}$ , and  $\overline{e_{\rm nc2}^2}$  can be designed with smaller values compared to  $\overline{e_{\rm n1}^2}$ , since no signal is processed in the noise cancellation path. Thus, the TIA input-referred current noise can be approximated as

$$\overline{\iota_{\text{n,tot}}^{2}}(\omega) \cong \left(\overline{\iota_{\text{n1}}^{2}} + \overline{\iota_{\text{nc1}}^{2}}\right) + \alpha^{2} \overline{e_{\text{n1}}^{2}} \omega^{2} (C_{1} + C_{\text{in}}')^{2} + \overline{e_{\text{Q}}^{2}} + \left(\frac{c_{1}}{c_{2}}\right)^{2} \frac{4kT}{R_{\text{f}}},$$

(3-14)

From (3-14), the performance of the noise cancellation is limited: by (1) the residual noise factor  $\alpha$  and (2) the voltage noise  $\overline{e_{\rm nc1}^2}$  from the buffer. The residual noise factor is optimized by tuning the gain of the inverting amplifier to match the

signal path. The unity gain buffer can be designed/chosen with lower voltage noise  $\overline{e_{\rm nc1}^2}$  than  $\overline{e_{\rm n1}^2}$  because the requirement of this buffer is relaxed with a feedback factor of unity, which is much larger than the integrator. Hence, the total integrated noise of the HSD-TIA with the noise cancellation in (3-14) is reduced compared to (3-11).

## 3.5 Implementation

We verified the proposed HSD-TIA with noise cancellation technique using discrete components on a PCB (Fig. 3.6). This design has a mid-band gain of 31.6 M $\Omega$  and a flat-gain bandwidth of 950 kHz. The component values for the design are listed in Table 3.1. A 6th order Bessel LPF with a gain of 10 dB is cascaded with the HSD-TIA as an anti-aliasing filter. The gain of the HSD-TIA was designed based on (3-2). The differentiator is implemented as a band-pass filter to set the high cutoff frequency  $f_{\rm H}$  and improve the stability of the TIA.  $f_{\rm H}$  is readily changed for different types of nanopores by simply tuning the feedback capacitor in the band-pass filter without increasing the input-referred noise or decreasing the gain. Currently,  $f_{\rm H}$  is limited by the parasitic capacitance on the PCB in the feedback path of the differentiator rather than the OPAMPs when the bandwidth is increased.

To obtain low noise and low leakage current, the considerations of the integrator OPAMP were a voltage noise less than  $10 \text{ nV/}\sqrt{\text{Hz}}$ , a current noise less than  $10 \text{ fA/}\sqrt{\text{Hz}}$ , and an input capacitance of only a few pF. A MOS-input OPAMP with low input bias current is used for the integrator. The total input bias current of the HSD-TIA is designed to be less than 10 pA to minimize signal leakage. The requirements of low voltage noise and low input capacitance are relaxed because of

the noise cancellation path from (3-14). The noise requirement of the differentiator OPAMP is reduced because of the gain from the integrator.

The semi-digital feedback loop was realized with a 12-bit ADC, FPGA, 12-bit DAC, and a resistor RDC. The FPGA implemented the LPF, DC compensation logic, and all control logic. The LPF was designed based on the values of  $f_L$  and k in (3-6), (3-8) and (3-9). The LPF is implemented as an equal-ripple finite impulse response (FIR) filter with a -3dB frequency of 100 Hz and a gain factor 1/k of 0.1 which results in an  $f_L$  of 26 Hz. The -3dB frequency could be lower with a larger value of k, but the area/power overhead is increased due to a higher order FIR LPF.  $R_{DC}$  was chosen according to the discharging current capability and the current noise  $4kT/R_{DC}$ . Furthermore,  $R_{DC}$  should be on the same order of magnitude as the resistance of nanopore channel, so the baseline current caused by the bias voltage  $V_b$  can be discharged by  $R_{DC}$ . Here, an  $R_{DC}$  of 1 G $\Omega$  provides a maximum baseline discharging capability of 2 nA with  $V_{0,peak}$  of 2 V and low input-referred noise based on (3-14).