## **UC Riverside**

## **UC Riverside Electronic Theses and Dissertations**

### **Title**

System-Level Thermal Modeling and Management for Multi-Core and 3D Microprocessors

### **Permalink**

https://escholarship.org/uc/item/4n69v486

### **Author**

Liu, Zao

### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA RIVERSIDE

System-Level Thermal Modeling and Management for Multi-Core and 3D  $$\operatorname{Microprocessors}$$

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering

by

Zao Liu

June 2014

Dissertation Committee:

Professor Sheldon X.-D. Tan, Chairperson Professor Yingbo Hua Professor Kambiz Vafai

University of California, Riverside

### Acknowledgments

I owe deep gratitute to my adviser Dr. Sheldon X.-D. Tan for his guidance, understanding and most importantly his invaluable advices that help and encourage me to move forward in the right directions in my dissertation research. His mentorship provides me invaluable experience that helps me to set my long-term career goals. I sincerely appreciate his kindness to me as the most important research mentor in my life. I would also like to thank all the committee members Prof. Yingbo Hua and Prof. Kambiz Vafai for their beneficial direction, discussion and advices for improving my research.

Also, I would like to extend my special thanks to all my lab members, Duo Li, Ruijing Shen, Hai Wang, Xuexin Liu, Sahana Swarup, Eric Mullinar, Santiago, Rodriguez, Adair Palm, Xin Huang, Kai He for all kinds of supports and help, which not necessarily limits to research projects. A good team environment is indispensible to overcome challenges and make good progress in research.

Last but not least, I would like to thank my parents, my related family branches across US and China, my friends all over the world, for their constant support and encouragement, which always inspires me to move forward. Also, I would like to express my special thanks to my loved one, Ying Zheng, for her deep understanding of my academic and career pursuit. Closely bonded relationship with them is an invaluable resource for my every success.

#### ABSTRACT OF THE DISSERTATION

System-Level Thermal Modeling and Management for Multi-Core and 3D Microprocessors

by

#### Zao Liu

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, June 2014 Professor Sheldon X.-D. Tan, Chairperson

The continuously scaling down of CMOS technology inevitably increases the power density for high performance microprocessors, which makes thermal effects and related problems urgent and challenging. Unpredicted thermal behavior and on-chip thermal hot spots could lead to performance degradation of microprocessor chips, incurring reliability issues. Hence, it is becoming increasingly important to develop thermal modeling methods to predict the thermal behavior of microprocessor chips, and thermal management techniques to control the on-chip thermal hot spots and thermal related reliability issues.

This research focuses on system level thermal behavior modeling and management methods to enable the thermal aware design of high performance microprocessor chips and packages, which also considers the thermal related reliability issues. First, at chip level, a new compact lateral thermal resistance model is proposed to model the lateral thermal behavior of through silicon vias (TSVs), which was largely ignored previously. The proposed lateral thermal model is fully compatible with the existing thermal modeling method of TSVs, and could be integrated into finite difference (FD) simulation to improve the

accuracy. Second, targeting at the package level modeling of thermal behavior for microprocessor chip package, the top-down approach building the thermal behavioral models from the given accurate temperature and power information by means of the subspace identification method (SID) is systematically explored in this dissertation research. Power map based approach and piecewise linear modeling method are developed to improve the accuracy of the identified model in presence of thermal nonlinearity and correlated power traces. Third, a more effective architecture level distributed thermal management method is developed to balance the on-chip temperature distribution in this dissertation research. A new temperature metric called *effective initial temperature* that incorporates both initial temperature and other transient thermal effects is proposed to make optimized task migration decisions in the new distributed thermal management method, leading to more effective reduction of thermal hot spots. The last but not least, since temperature imposes exponential influence on the reliability of the chip, this research also proposes a new system level reliability model derived from fundamental physics principles, in which reliability is modeled as life time resources that are to be consumed as the chip works. Based on this model, a dynamic management method is proposed to effectively balance and compensate the life time resources across all the cores in a multi-core processor system, preventing the chance of early failure of heavily loaded cores.

## Contents

| Li       | List of Tables x                                                      |                                                                                                                                   |    |  |

|----------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----|--|

| Li       |                                                                       |                                                                                                                                   |    |  |

| 1        | Intr                                                                  | roduction                                                                                                                         | 1  |  |

|          | 1.1                                                                   | Thermal Related Issues for High Performance Microprocessors                                                                       | 1  |  |

|          | 1.2<br>1.3                                                            | Finite Difference Thermal Modeling Method for 3D IC Chips System Identification based Top-down Thermal Modeling Method for Micro- |    |  |

|          |                                                                       | processor Packages                                                                                                                | 6  |  |

|          | 1.4                                                                   | Architectural Level Thermal Management Techniques                                                                                 | (  |  |

|          | 1.5                                                                   | System Level Reliability Modeling and Management Techniques                                                                       | 12 |  |

|          | 1.6                                                                   | High Lights and Contributions                                                                                                     | 15 |  |

|          | 1.7                                                                   | Organization                                                                                                                      | 19 |  |

| <b>2</b> | Fundamentals of Thermal Modeling and Management Methods               |                                                                                                                                   |    |  |

|          | 2.1                                                                   | General Thermal Modeling Concepts and Approaches                                                                                  | 20 |  |

|          |                                                                       | 2.1.1 Deriving Thermal Behavior Model from its Physical Principle                                                                 | 21 |  |

|          |                                                                       | 2.1.2 Equivalent Thermal Circuit Modeling Approach                                                                                | 24 |  |

|          |                                                                       | 2.1.3 State Space Thermal Modeling Approach                                                                                       | 25 |  |

|          | 2.2                                                                   | Review of Subspace Identification Method                                                                                          | 26 |  |

|          |                                                                       | 2.2.1 Introduction to N4SID Method                                                                                                | 27 |  |

|          |                                                                       | 2.2.2 Input signal requirements                                                                                                   | 29 |  |

|          |                                                                       | 2.2.3 A special case - baseline model for system identification                                                                   | 30 |  |

|          | 2.3                                                                   | Architectural Level Thermal Management Methods                                                                                    | 31 |  |

|          |                                                                       | 2.3.1 Introduction to Dynamic Voltage and Frequency Scaling Methods .                                                             | 32 |  |

|          |                                                                       | 2.3.2 Introduction to Task migration Methods                                                                                      | 33 |  |

|          | 2.4                                                                   | Summary                                                                                                                           | 34 |  |

| 3        | Compact Lateral Thermal Resistance Model of TSVs for Fast Finite Dif- |                                                                                                                                   |    |  |

|          | fere                                                                  | nce Thermal Analysis of 3D Stacked Chips                                                                                          | 35 |  |

|          | 3.1                                                                   | Problem Formulation                                                                                                               | 36 |  |

|          | 3.2                                                                   | Analytical expression for lateral thermal resistance of TSVs                                                                      | 39 |  |

|   |     | *                                                                             | 39         |

|---|-----|-------------------------------------------------------------------------------|------------|

|   | 0.0 | v v                                                                           | 43         |

|   | 3.3 | •                                                                             | 46         |

|   | 3.4 |                                                                               | 51         |

|   |     | *                                                                             | 52         |

|   |     |                                                                               | 59         |

|   |     | •                                                                             | 64         |

|   | 3.5 | Summary                                                                       | 71         |

| 4 |     | ospace-based Compact Nonlinear Thermal Modeling of Packaged Inte-             |            |

|   | _   | ·                                                                             | <b>7</b> 3 |

|   | 4.1 |                                                                               | 74         |

|   | 4.2 |                                                                               | 80         |

|   |     |                                                                               | 80         |

|   |     |                                                                               | 82         |

|   |     |                                                                               | 83         |

|   | 4.3 | 9 **                                                                          | 85         |

|   |     | •                                                                             | 85         |

|   |     |                                                                               | 88         |

|   | 4.4 |                                                                               | 91         |

|   |     | 4.4.1 Multi-configuration model identification and validation for the package |            |

|   |     | 9                                                                             | 98         |

|   | 4.5 | Summary                                                                       | 12         |

| 5 |     | k Migration based Distributed Thermal Management Considering Tran-            |            |

|   |     | at Effects for Many-Core Microprocessors                                      |            |

|   | 5.1 |                                                                               | 14         |

|   | 5.2 |                                                                               | 16         |

|   |     | 1                                                                             | 16         |

|   |     | 1                                                                             | 21         |

|   |     | • •                                                                           | 24         |

|   |     | 9                                                                             | 27         |

|   | 5.3 |                                                                               | 29         |

|   |     |                                                                               | 29         |

|   |     | 1                                                                             | 31         |

|   |     |                                                                               | 34         |

|   | 5.4 | Summary                                                                       | 38         |

| 6 | -   | namic Reliability Management Considering Resource-Based EM Mod-               |            |

|   |     | ag for Multi-Core Microprocessors                                             |            |

|   | 6.1 | v C                                                                           | 43         |

|   | 6.2 |                                                                               | 44         |

|   |     |                                                                               | 45         |

|   |     | 1 9                                                                           | 47         |

|   |     | 6.2.3 System level EM-reliability resource consumption model 1                | 48         |

| $\mathbf{Bi}$ | Bibliography 10 |        |                                                                | 167 |

|---------------|-----------------|--------|----------------------------------------------------------------|-----|

| 7             | Con             | clusio | n                                                              | 163 |

|               | 6.5             | Summ   | nary                                                           | 161 |

|               |                 |        | Evaluation of the proposed methods                             |     |

|               |                 | 6.4.1  | A walk-through example for the proposed reliability estimation | 156 |

|               | 6.4             | Nume   | rical results and discussions                                  | 155 |

|               |                 | 6.3.2  | EM-reliability resource based low power control                | 152 |

|               |                 | 6.3.1  | EM-reliability resource based task migration                   | 150 |

|               | 6.3             | EM-re  | eliability management method                                   | 150 |

# List of Figures

| 2.1  | A node of the equivalent thermal circuits, which represents a temperature         |    |

|------|-----------------------------------------------------------------------------------|----|

|      | point connecting to all its adjacent nodes through thermal conductance.    .      | 26 |

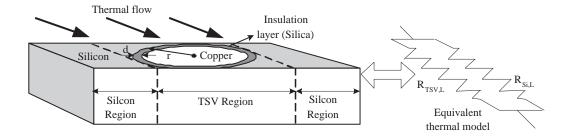

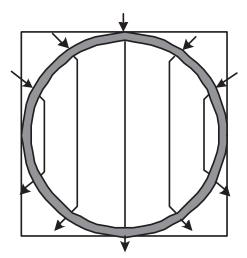

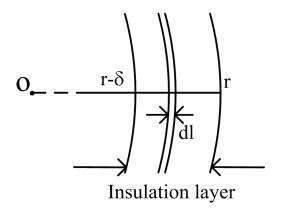

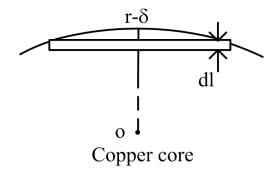

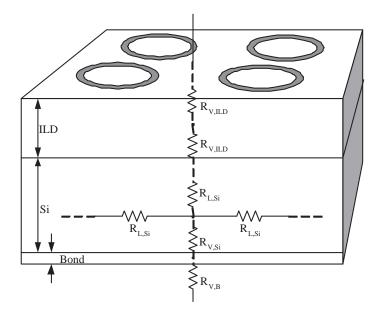

| 3.1  | A structure view of TSV cell with copper core and insulation layer                | 38 |

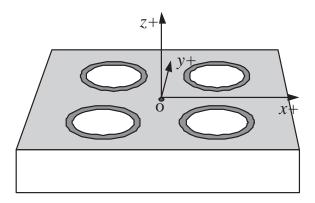

| 3.2  | Top view of TSV array built using individual TSV cells                            | 38 |

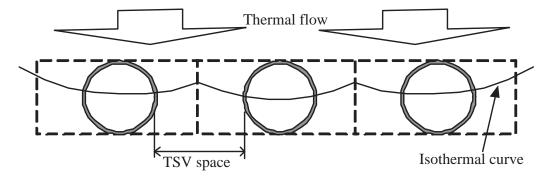

| 3.3  | Direction of lateral thermal flow (arrows) across the TSV region                  | 40 |

| 3.4  | Thermal resistance calculation across the insulation layer                        | 41 |

| 3.5  | Thermal resistance calculation across the TSV core                                | 42 |

| 3.6  | Silicon structure containing TSV array and its compact thermal model con-         |    |

|      | sidering thermal resistance of TSVs in 3D Cartesian coordinate                    | 50 |

| 3.7  | Extending the proposed lateral model into more complicated TSV structures         | 52 |

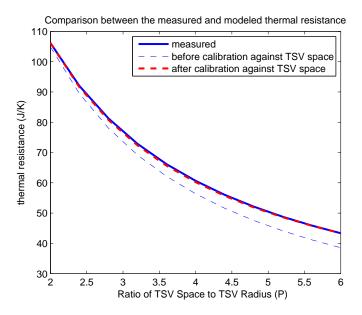

| 3.8  | Isothermal curve of the TSV cell under test                                       | 54 |

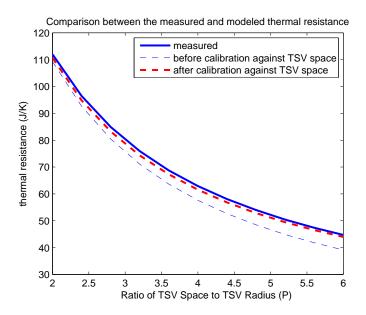

| 3.9  | The measured data used for calibration (the TSV with the insulation linear        |    |

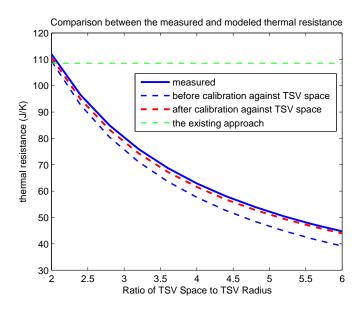

|      | to be $1.5um$ vs the proposed model before and after calibration                  | 55 |

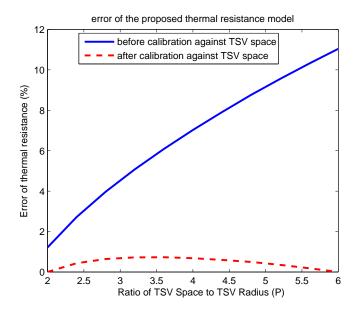

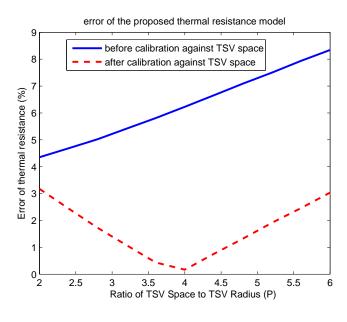

| 3.10 | Error of the proposed model (before calibration and after calibration) for the    |    |

|      | TSV with the insulation linear thickness to be $1.5um$                            | 56 |

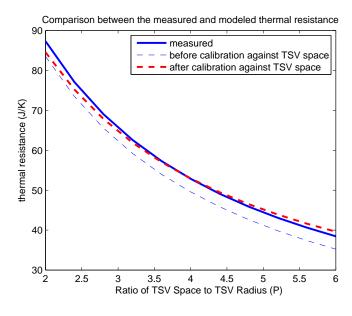

| 3.11 | Comparison of the proposed model and the measured data in different insu-         |    |

|      | lation thickness                                                                  | 57 |

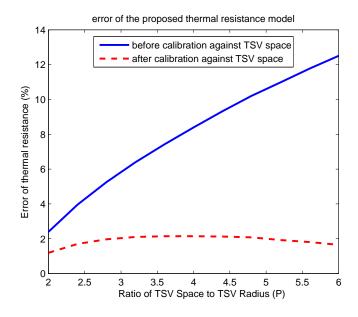

| 3.12 | Error of the proposed model (before calibration and after calibration)            | 58 |

| 3.13 | Comparison of the proposed modeling method with the existing lumped mod-          |    |

|      | eling method                                                                      | 60 |

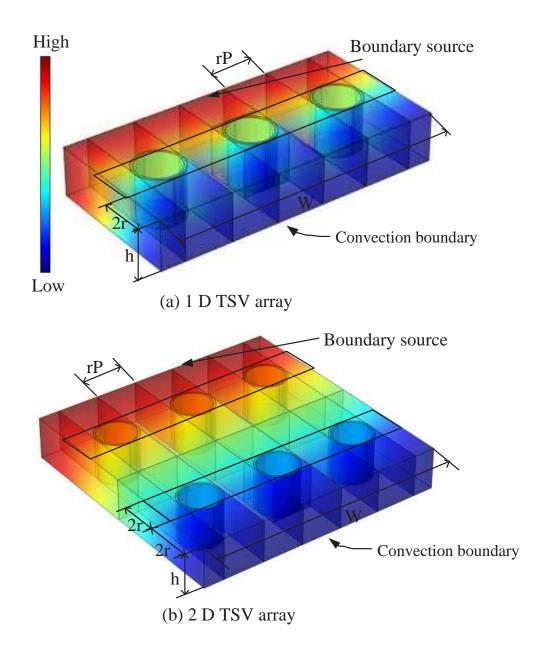

|      | TSV array structures used for lateral thermal resistance validation               | 61 |

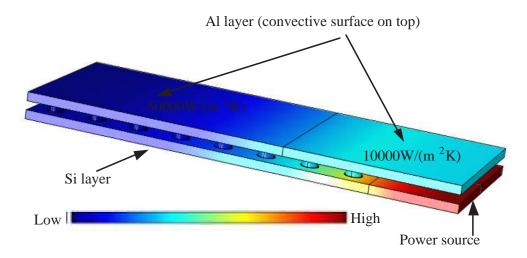

| 3.15 | Two layer chip structure with $4\times8$ TSV array and the temperature distribu-  |    |

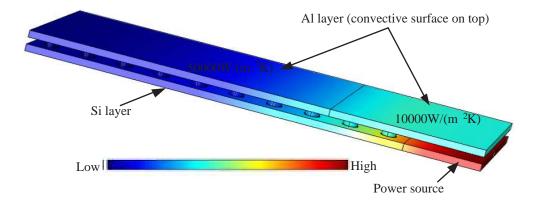

|      | tion simulated by COMSOL                                                          | 65 |

|      | 2D bottom View of the $2 \times 5$ meshed chip and its power source configuration | 66 |

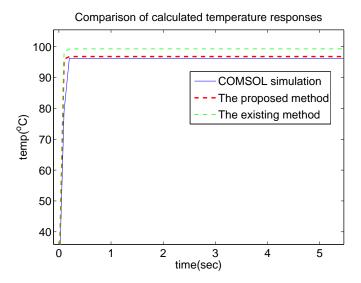

| 3.17 | Transient temperature responses of the two layer structure with $4\times8$ TSV    |    |

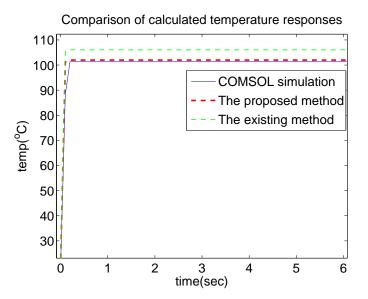

|      | array                                                                             | 67 |

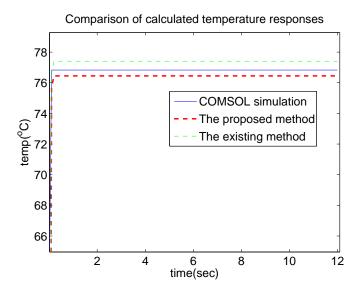

| 3.18 | Transient temperature responses of TSV grid in the two layer structure with       |    |

|      | 4×8 TSV array under reconfigured power sources                                    | 68 |

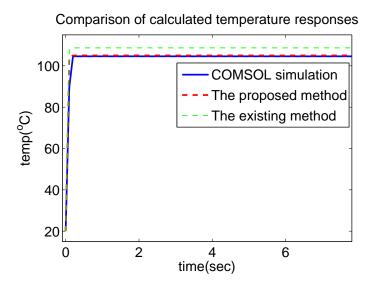

| 3.19 | 1 1                                                                               |    |

|      | array representing wide I/O memory                                                | 69 |

| 3.20       | Two layer chip structure with $4\times10$ TSV array and the temperature distribution simulated by COMSOL                                           | 70       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.21       |                                                                                                                                                    | 11       |

| 0.21       | array representing wide I/O memory                                                                                                                 | 7        |

|            | witey representing wide 1/0 memory                                                                                                                 | •        |

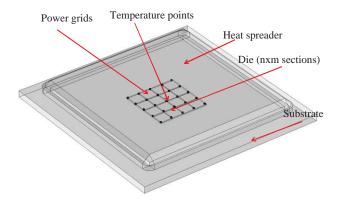

| 4.1        | Meshed chip and package                                                                                                                            | 75       |

| 4.2        | The abstracted model system and correlated power inputs                                                                                            | 76       |

| 4.3        | Transient temperature response of the system identified with one highly cor-                                                                       |          |

|            | related power inputs                                                                                                                               | 77       |

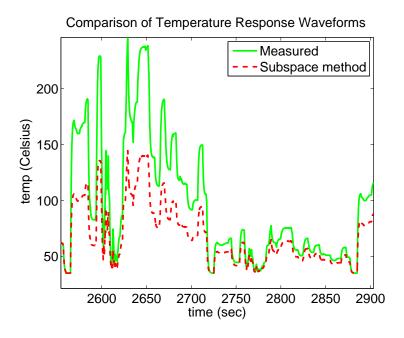

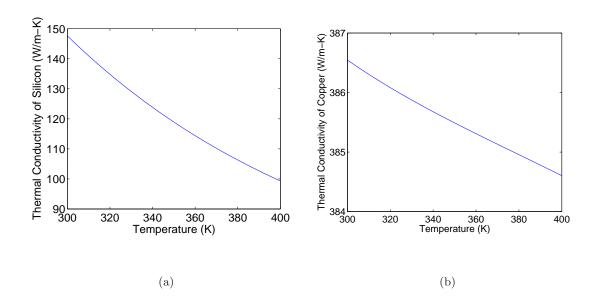

| 4.4        | Temperature dependence of the thermal conductance (a) Silicon (b) Copper                                                                           | 78       |

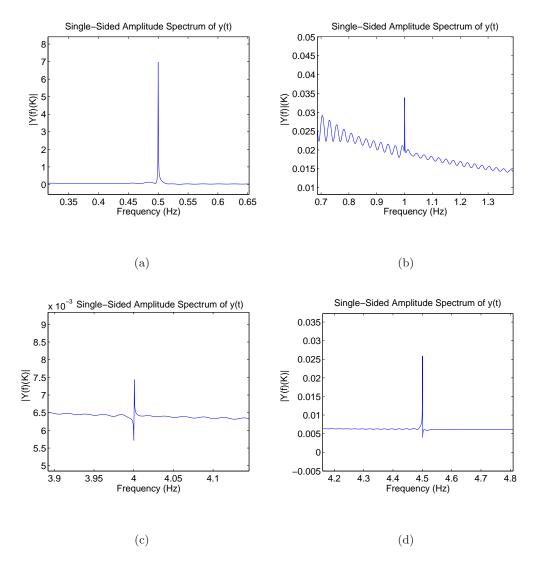

| 4.5        | Frequency domain response of the thermal system under sinusoid input with frequency of 0.5HZ (a) baseband spectral (b) 1st order harmonics (c) 2nd |          |

|            | order harmonics (d) 3rd order harmonics                                                                                                            | 79       |

| 4.6        | Accuracy loss of the temperature response of the identified 4-th order linear                                                                      | 0.0      |

| 4 7        | model                                                                                                                                              | 80       |

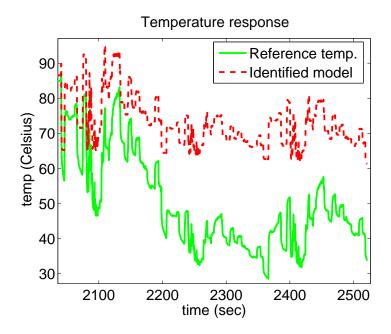

| 4.7        | The new ThermSubCP algorithm                                                                                                                       | 84       |

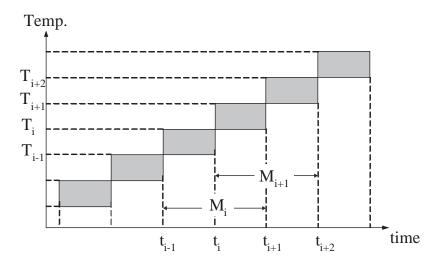

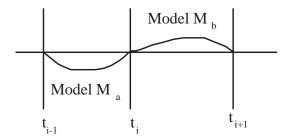

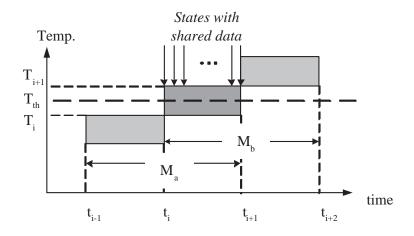

| 4.8<br>4.9 | Identification of linear subsystems for different temperature ranges Abrupt model transition at known time instance                                | 87<br>89 |

| 4.10       | Model transition from $M_a$ to $M_b$                                                                                                               | 89       |

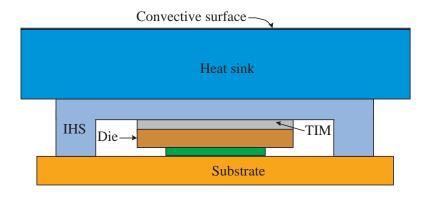

|            | Microprocessor chip package                                                                                                                        | 92       |

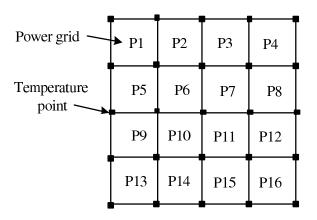

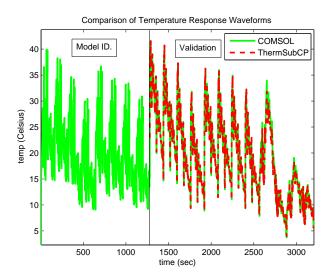

|            | Top view of partitioned die area with power grids and temperature points                                                                           | 02       |

| 1.12       | (heat sink removed)                                                                                                                                | 92       |

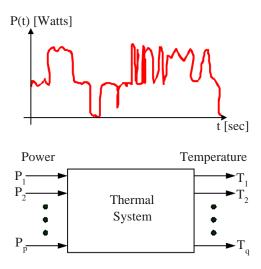

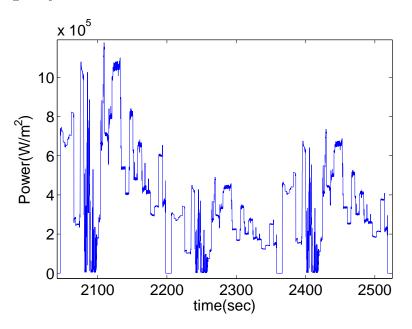

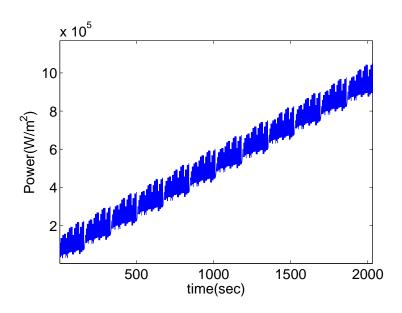

| 4.13       | Transient on-chip power waveform from industry                                                                                                     | 93       |

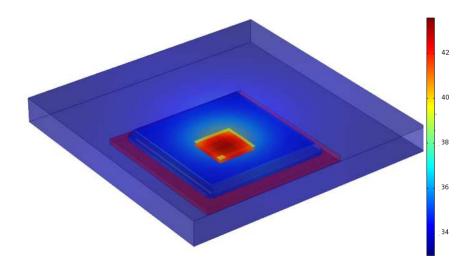

|            | Steady state temperature distribution simulated by COMSOL 4.1                                                                                      | 94       |

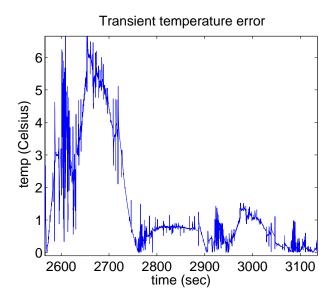

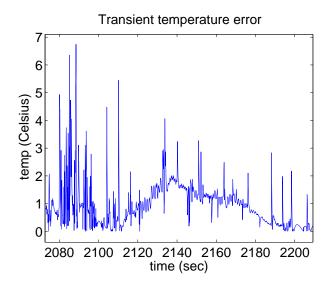

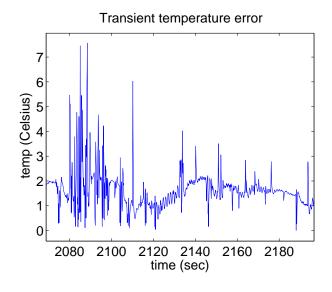

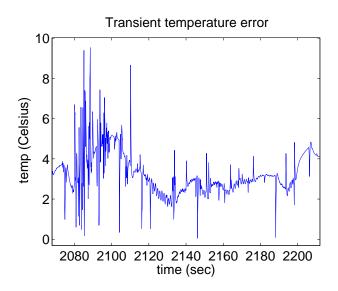

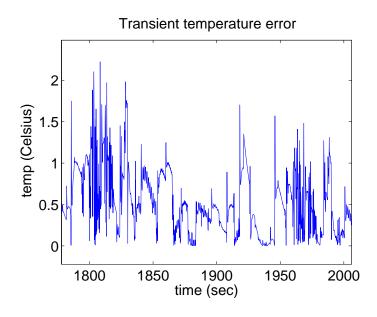

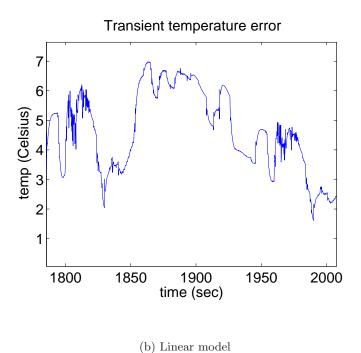

| 4.15       | Transient temperature responses and the temperature errors of the identified                                                                       |          |

|            | model (order:15)                                                                                                                                   | 96       |

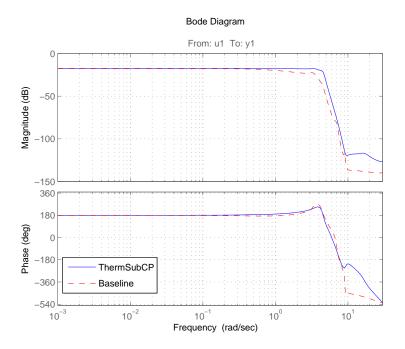

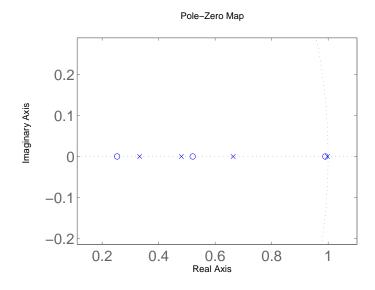

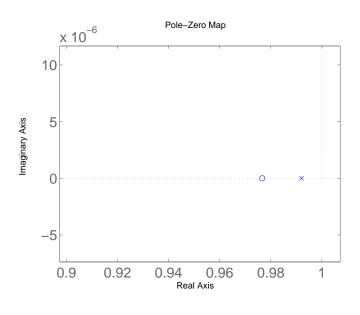

|            | Bode diagram of the transfer function from input $u_1$ to output $y_1 \ldots \ldots$                                                               | 97       |

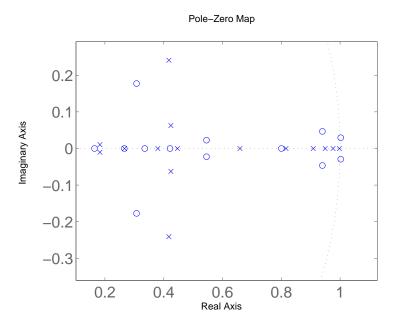

|            | Poles and zeros distribution of the 15th-order model                                                                                               | 97       |

|            | The stair-like PRBS input signal in model identification phase                                                                                     | 96       |

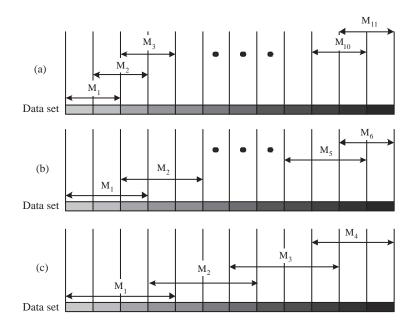

| 4.19       | Data partition schemes for model identification (a) scheme-1(11 local models)                                                                      |          |

| 4.00       | (b) scheme-2(6 local models) (c) scheme-3 (4 local models)                                                                                         | 100      |

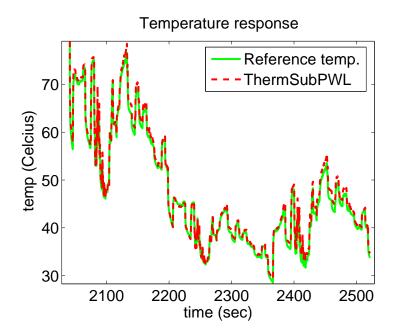

| 4.20       | Transient view of the on-chip temperature response (at the 1st temperature                                                                         | 101      |

| 4.01       | point) of the piecewise linear models (PLM) built with 11 local models                                                                             | 101      |

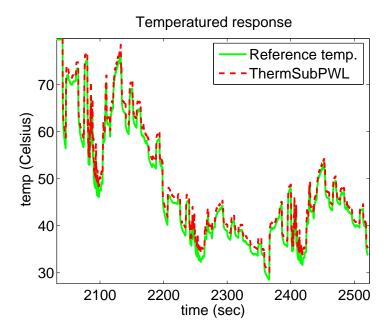

| 4.21       | Transient view of the on-chip temperature response (at the 1st temperature                                                                         | 109      |

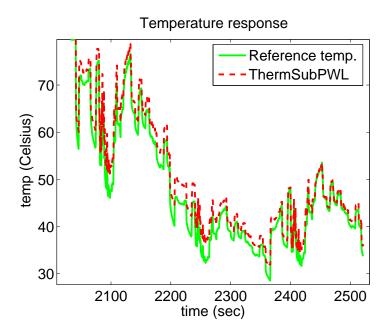

| 4 22       | point) of the piecewise linear models (PLM) built with 6 local models Transient view of the en chip temperature response (at the 1st temperature   | 102      |

| 4.22       | Transient view of the on-chip temperature response (at the 1st temperature point) of the piecewise linear models (PLM) built with 4 local models   | 103      |

| 1 23       | Absolute errors of the on-chip temperature response (at the 1st temperature                                                                        | 100      |

| 4.20       | point) of the piecewise linear models (PLM) built with 11 local models                                                                             | 104      |

| 4.24       | Absolute errors of the on-chip temperature response (at the 1st temperature                                                                        | 10       |

|            | point) of the piecewise linear models (PLM) built with 6 local models                                                                              | 104      |

| 4.25       | Absolute errors of the on-chip temperature response (at the 1st temperature                                                                        |          |

|            | point) of the piecewise linear models (PLM) built with 4 local models                                                                              | 105      |

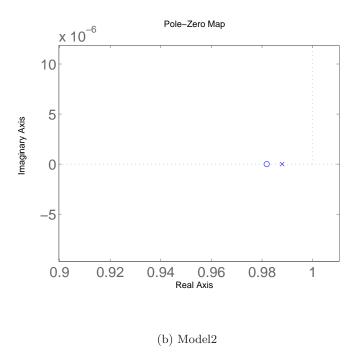

| 4.26       | Pole-zero configuration of a transfer functions in an identified local model .                                                                     | 105      |

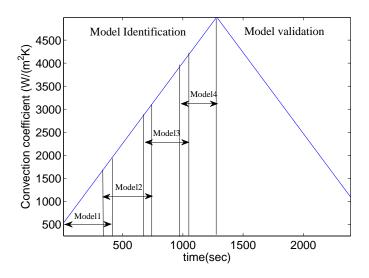

| 4 27       | Different convection rates of the heat sink                                                                                                        | 107      |

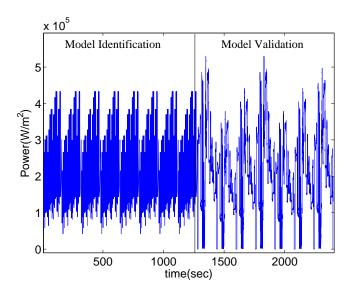

| 4.28       | Power traces used to build and validate the piecewise linear model for different convection rate                                                    | 1( |

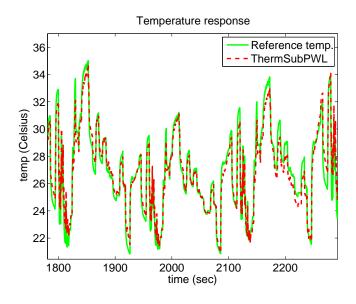

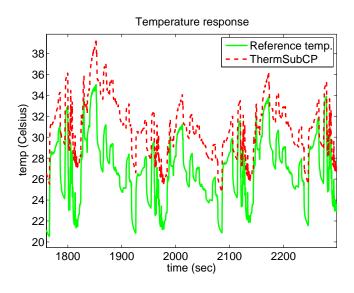

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.29       | Comparison of the on-chip temperature response (at the 1st temperature point) predicted by the piecewise linear models (PLM) with the one predicted | 1( |

|            | by a linear model under variant convection rate                                                                                                     | 1( |

| 4.30       | Absolute error of one on-chip temperature response at the 1st temperature                                                                           |    |

| 4.31       | point                                                                                                                                               | 11 |

| <b>-</b> 1 |                                                                                                                                                     |    |

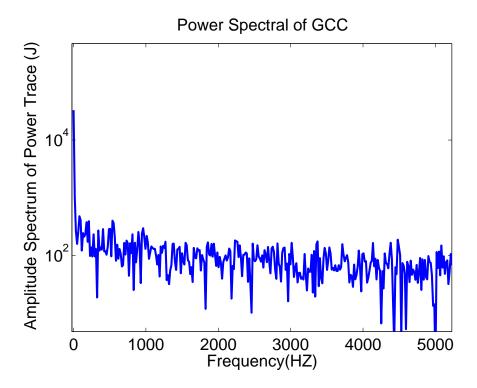

| 5.1        | Discrete Fourier transform of the power trace for running GCC benchmark                                                                             | 11 |

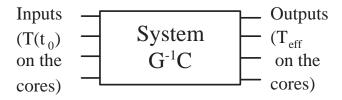

| 5.2        | The transient thermal system and input and output                                                                                                   | 12 |

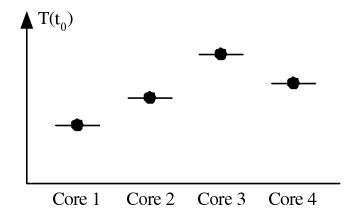

| 5.3<br>5.4 | The initial temperature distribution at time $T(t_0)$                                                                                               | 12 |

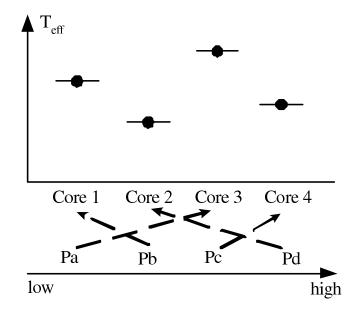

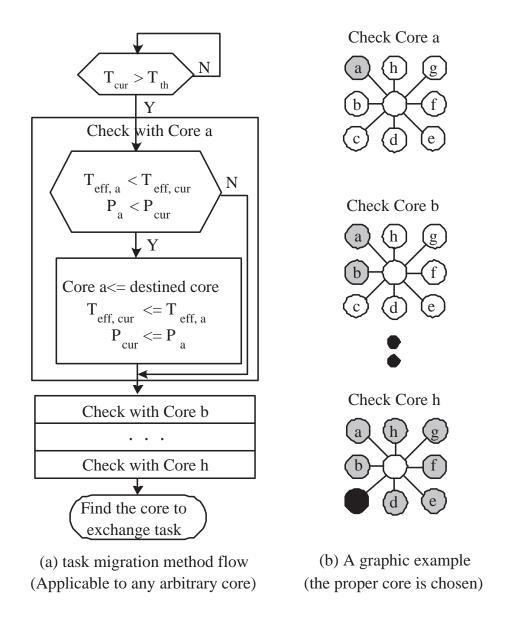

| 5.5        | task migration scheme                                                                                                                               | 12 |

|            | adjacent cores                                                                                                                                      | 12 |

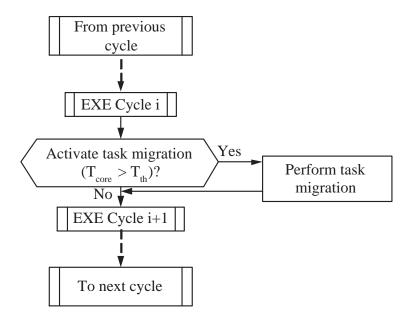

| 5.6        | The proposed distributed task migration method                                                                                                      | 1: |

| 5.7        | The run-time thermal management framework                                                                                                           | 1: |

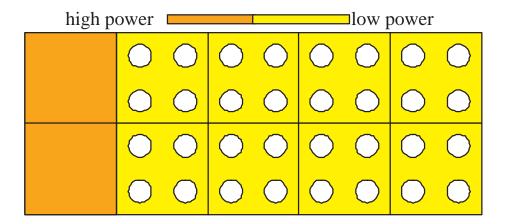

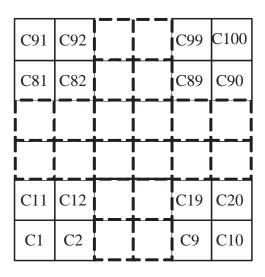

| 5.8        | The configuration of the 100-core microprocessor die                                                                                                | 1  |

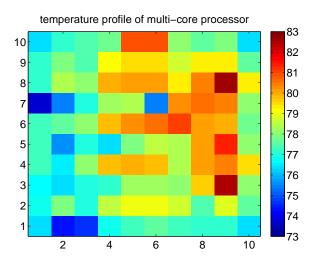

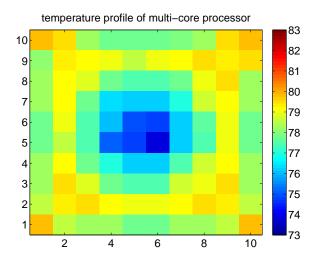

| 5.9        | On-chip temperature distribution across processor cores at the end of 20th task execution cycle                                                     | 1  |

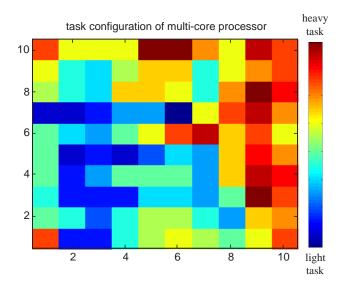

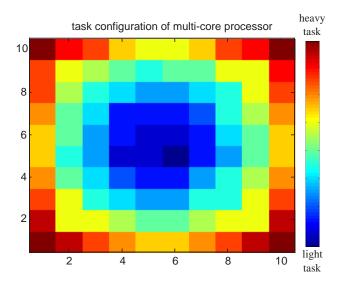

| 5.10       | On-chip task configurations at the beginning of the 20th task execution cycle under centralized task scheduling methods                             | 1  |

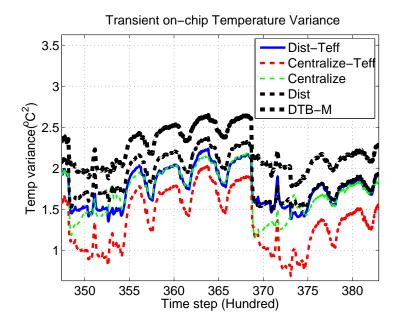

| 5.11       | Comparison of the transient temperature variance under different thermal management policy                                                          |    |

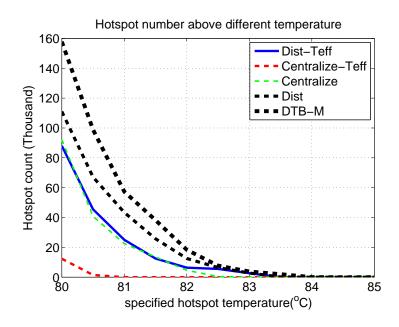

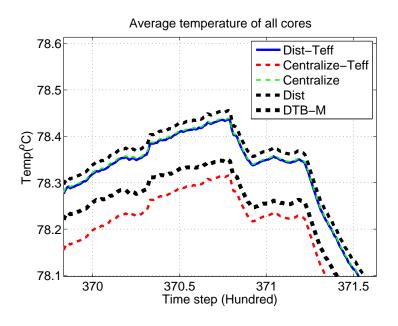

| 5.12       | The occurrence of thermal hot spots above different temperature levels during                                                                       | 1  |

| 5.13       | task execution                                                                                                                                      | 1  |

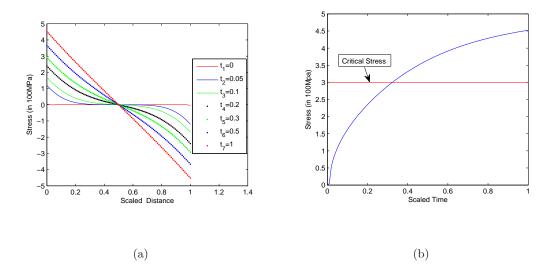

| 6.1        | (a) EM-stress distribution change over time in a simple metal wire. (b) EM-                                                                         |    |

|            | stress evaluation versus time                                                                                                                       | 1  |

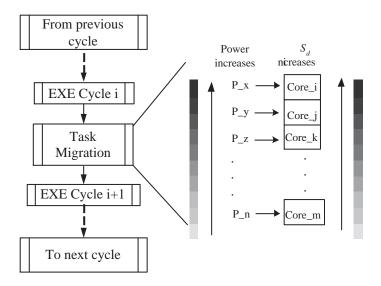

| 6.2        | The proposed reliability resource based task migration scheme                                                                                       | 1  |

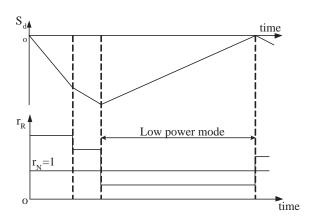

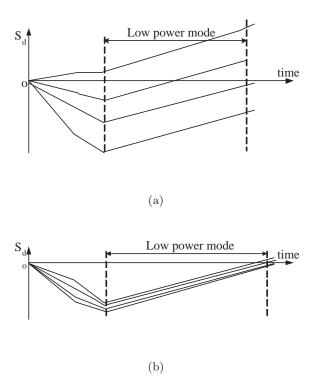

| 6.3        | Low power mode compensation scheme (one core)                                                                                                       | 1  |

| 6.4        | Low power mode compensation scheme for a 4-core system with (a) imbalanced MTTF consumption (b) balanced MTTF consumption                           | 1  |

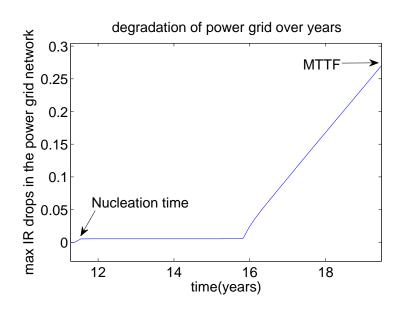

| 6.5        | The increase of IR drop in power grid over years                                                                                                    | 1  |

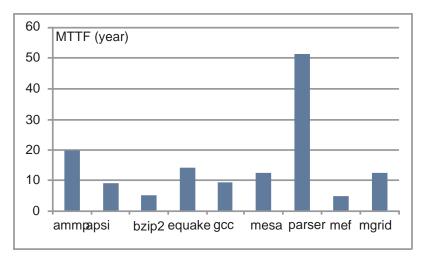

| 6.6        | The different MTTF values under different task loads                                                                                                | 1  |

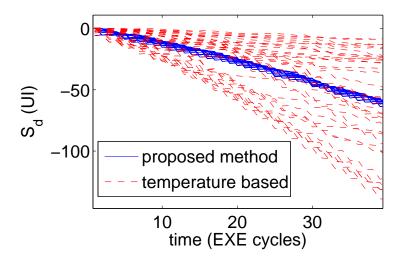

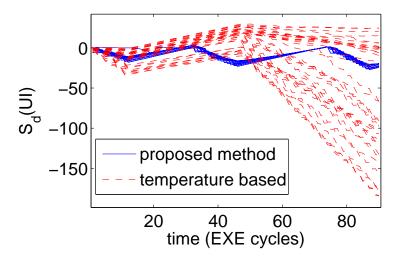

| 6.7        | MTTF resource slack (represented by $S_d$ ) under different task migration                                                                          |    |

| 6.8        | schemes                                                                                                                                             | 1  |

| 0.0        | mode under different task migration schemes                                                                                                         | 1  |

## List of Tables

| 3.1 | Comparison of modeled and measured lateral thermal resistance of 1D TSV      |      |

|-----|------------------------------------------------------------------------------|------|

|     | array                                                                        | 62   |

| 3.2 | Comparison of modeled and measured lateral thermal resistance of the 2D      |      |

|     | TSV array                                                                    | 62   |

| 3.3 | Comparison of modeled and measured lateral thermal resistance of the mod-    |      |

|     | ified 2D TSV array                                                           | 63   |

| 4.1 | Material and geometry of the microprocessor package                          | 91   |

| 4.2 | Additional input power map configurations for validation                     | 95   |

| 4.3 | Model identification CPU times and model errors                              | 98   |

| 4.4 | Model accuracy comparison with different identified models (order: 4)        | 103  |

| 4.5 | Comparison of model accuracy and CPU times                                   | 104  |

| 5.1 | The package structure and thermal properties of the many-core microprocessor | .130 |

| 5.2 | temperature variance and maximum temperature difference                      | 133  |

## Chapter 1

## Introduction

This chapter gives an overview of thermal related modeling and management in today's multi-core microprocessor chip. The thermal and its related issues are discussed to explain the motivation of the researches in this field. Also, the existing works in these fields are reviewed, and the potential challenges are identified. The object and the organization of the dissertation are also given in this chapter.

# 1.1 Thermal Related Issues for High Performance Microprocessors

The continuously technology scaling down offers benefits of large scale integration and high clock rate for processor designs. Billions of transistors are integrated in a single processor chip using 14 nm silicon fabrication technologies. Due to the complexity of today's sophisticated chip, huge amount of design efforts are put to guarantee that the processor

chip achieves varieties of specifications in different aspects. Various of design tools are used in the design flow to help engineers to analyze and understand the intricacies of the systems.

The design tools for digital design aims at simulation and optimization of logical design. Various of digital design tools are specialized for different design stage to evaluate and optimize the logic design. Successful examples that are extensively used by semiconductor industry are VCS simulator, Synopsis design compiler, PrimeTime, et. al. Also, the design tools for analog design focus on analyzing electrical behavior of the circuits based on physical circuit models or empirical data from lab characterization. Different tools are developed to model and simulate the analog system in different abstract levels (system level, transistor level, physical level). However, the design tools used for thermal behavior analysis are largely under-developed. Nevertheless, the increased power density has caused the on-chip temperature to become a major concern for high performance microprocessor design and package as more devices are integrated on the processor chips that aim at working clock frequency of Gigahertz range. Exacerbated temperature would result in slow transistors, increased interconnect delays, and potentially increases power consumptions due to leakage current, degrading the performance of the chip and incurring reliability issues [1, 2].

Hence, thermal management and related design problems continue to be identified by the Semiconductor Industries Association Roadmap [3] as one of the five key challenges during the next decade for achieving the projected performance goals of the industry. Accurate and efficient system level thermal modeling and analysis is vital for the thermal-aware chip and package design to improve performance, reliability, power reduction, and online temperature regulation techniques [4–6]. As the thermal effect becomes top constraint for the performance of high speed processor chip, more efficient thermal modeling and analysis technology at different levels (chip level, package level, and board level) need to be developed for thermal-aware chip and package design, and more efficient architecture level thermal management techniques are also required to effectively control the on-chip temperature, and thermal related reliability issues that are becoming increasingly challenge also needs to be addressed. Thus, to effectively enable thermal-aware chip and package design and alleviate thermal and related issues of the processor chip, this dissertation focuses on:

- chip level thermal modeling methodology using FDM (Finite Difference Method) that considers TSV thermal behavior for 3D stacked IC chips.

- package level top down thermal modeling methodology using subspace identification to extract thermal behavior model of a processor package.

- architecture level thermal management techniques that efficiently control and regulate the on-chip temperature to alleviate thermal issues for multi-core processors.

- system level reliability modeling and management method that effectively control the life time resources of different cores in multi-core processors to prevent the chance of early failure of the cores.

# 1.2 Finite Difference Thermal Modeling Method for 3D IC Chips

Thermal issues tend to be more exacerbated in three dimensional (3D) stacked integrated circuits (ICs), which necessitates the chip level thermal behavior model to predict

thermal hot spots. The major factors driving the thermal issues in 3D ICs are increased thermal resistance along the primary heat transfer path and high power density in 3D integration. Through silicon vias (TSVs) or thermal TSVs (TTSVs) are introduced to facilitate the heat removal inside 3D chips. Essentially, TSVs are vertical vias in 3D ICs, which can effectively convey heat from multiple layers to the heat sink. TSVs have shown promise in alleviating the thermal problem seen in 3D stacked ICs [7, 8]. For thermal modeling of 3D chip structures, it is important to incorporate TSVs into the thermal model because it can significantly change the thermal profile of the 3D chip and TSV models are important for many thermal-aware physical optimizations [9–14].

Traditional approaches treat TSVs as a vertical lumped thermal resistor in each physical plane and its resistance value is proportional to the length and inversely proportional to the diameter of the TTSV [15,16]. The TSV as a one dimensional (1D) network implies heat flows only in the vertical direction towards the heat sink of the system. This method is shown to be insufficient in capturing the thermal behavior of the TSVs since the lateral heat transfer through these structures is neglected. Recent study shows that the lateral thermal effects due to TSVs or TSV array or farms can have a significant impact on the thermal profile of the 3D chips [17]. Alternately, accurate numerical approaches such as finite difference (FD) and finite element methods (FEM) can be applied to build the thermal model of the chip package. However, to capture the small feature size of TSVs such as the diameter of TSV and thickness of the insulation layer of TSVs, very fine mesh grids are required, which significantly increase the model complexity and thus the cost of simulation.

For finite difference based analysis especially in system level or full chip levels, large grid sizes may be used in order to reduce the computation cost of thermal analysis of 3D stacked chips with TSVs. In this case, we may have one or more TSVs in one grid and it becomes important to drive the equivalent lumped models (in both vertical and lateral directions) for such TSV-bearing grids. In addition to fast finite difference analysis, a very compact and accurate TSV model which offers insight about the thermal properties of TSV structures and links the heat transfer process with the physical parameters will be very useful for architecture level TSV planning and inter-layer level thermal design for 3D ICs.

Recently, a compact thermal TSV model for 3D stacked ICs was proposed in [18], in which the lateral thermal resistance is considered. It is an initial effort to address this important thermal modeling problem. This method, however, mainly studied the stacked thermal TSVs across many active layers. It only considered the lateral thermal resistance caused by the insulation liners. Furthermore, their thermal model works only for a single TSV, not for an array of TSVs. As we can see that the array of TSVs cannot be simply constructed by this individual TSV models. To mitigate the model accuracy issues, a larger model (called distributed model) is used in [18]. This in turn will impact the analysis efficiency.

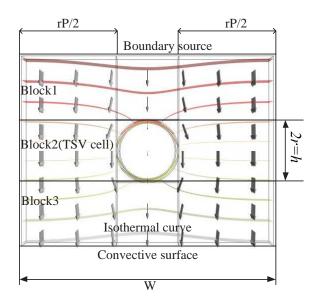

Chapter 3 of this dissertation explores a new compact physics-based lateral thermal resistance model for both a single TSV and a TSV array. It first focuses on developing a physics-based analytical expression for the lateral thermal resistance of TSVs and TSV arrays in terms of physical and material parameters. The proposed model targets at estimating the lateral thermal resistance considering TSV arrays, and the model also takes into

the account of lateral resistance changes caused by the bending of isothermal curves due to the interplays of TSVs. Second, the method also integrates this lumped lateral model into finite difference thermal modeling code of 3D microprocessor package, and demonstrates the improved modeling accuracy by comparing the simulated results against the results from COMSOL, and the one from the existing method [18].

# 1.3 System Identification based Top-down Thermal Modeling Method for Microprocessor Packages

The traditional bottom-up approaches including FEM (finite element method), FDM (finite difference method), and computational flow dynamics (CFD) based methods were widely used in thermal modeling and analysis in the past [19–21]. For compact thermal modeling at package level, many existing approaches try to use thermal resistors and capacitors with fixed topology networks subject to different thermal boundary conditions [22–24]. However, the accurate RC values of package elements, especially for complex geometries and boundary conditions of the processor package, are difficult to determine, and the calibration against the numerical field solvers or analytical results [25, 26] and measured data are usually required [27].

For thermal modeling at package levels, many works have been proposed targeting at different applications in the past. An excellent survey on recent works can be found in [28]. In general, existing approaches can be classified into bottom-up white-box approaches, which are based on the thermal dynamic physics and approximation techniques, the top-

down black-box behavioral modeling approaches and the third modeling approaches, which are something in between the two approaches [28].

Existing work on HotSpot [6,29] attempts to solve this problem by generating the compact thermal model in a bottom-up manner based on processor and package structures. However, such white-box models may suffer from accuracy issues for complicated structures and boundary conditions, which are not properly modeled in the starting models. For instance, complicated package design may require exploration of packages with different structures and materials and boundary conditions for their thermal performance in the industry setting.

Recently, top-down black-box behavioral thermal modeling methods have been proposed to extract thermal behavior model from high level abstraction. Many proposed models target at the on-line temperature regulation applications, in which compact thermal models can estimate or predict the thermal behaviors of a real systems and they can be built in a dynamic way based on the online thermal sensor reading and online power estimation techniques [30–32]. For example, a distributed online thermal model was proposed and validated on a realistic many-core system [33–35].

Another important development for the top-down black-box thermal modeling is for building more accurate and even parameterized thermal models for architecture or package level thermal-aware design and optimization. The input power signal and output thermal temperatures for learning or training are assumed to be measured from off-line complicated equipments in the lab. Existing works consist of the matrix pencil method [36] and the subspace identification method [37–39]. The major advantage of such pure behav-

ioral modeling methods is their flexibility and easy to use as no physical restrictions and assumptions are made or required for the models. They are also very accurate as the training is based on measured data. However, stability and other properties of thermal systems need to be enforced explicitly.

Recently, Beneventi et al. [28] proposed a hybrid (or gray-box) identification method, in which a pre-structured compact model under physical constraints is built via an optimization approach. The main advantage of such models is that many physical properties such as stability and passivity can be satisfied automatically. But such models will be less flexible for different architectures and structures as the thermal models or topologies are based on specific architectures. Also, all the existing thermal behavioral modeling methods assume that the thermal systems are linear, which may not be the case for many practical thermal systems as we show in this work, and they have difficulty to deal with varying thermal boundary conditions.

In this dissertation, we still focus on the black-box based thermal modeling scheme based on the subspace identification method. We consider practical measured power maps, which can be obtained from thermal lab based on the test thermal vehicle (testing thermal chips). We first observe that the subspace identification method may suffer from the lack of predictability problems in general [40, 41], especially when the input power is given as series of 2-dimensional power distributions (called *power maps*) in which the input signal is highly spatially correlated. Power map-based thermal characterization is widely used in industry for thermal characterizations of package design as power maps can be easily obtained (measured or computed) practically. However, the spatially correlated power

signals in the power map make the system identification process more difficult. The reason is that it is difficult to distinguish the contribution from specific input when all the inputs have the same or similar transient waveforms. Also, compact behavioral thermal modeling for changing boundary conditions still remain to be a challenging problem.

Chapter 4 of this dissertation presents a new behavioral thermal modeling technique considering more practical power maps and nonlinear effects of thermal systems for package level design space exploration of high-performance microprocessors, using subspace identification method. In the proposed new method, the thermal system model is trained by more practical power maps to improve the predictability. Also, piecewise linear techniques are used to handle the thermal nonlinearity of the processor package to improve the model accuracy without increasing the model order, which leads to a compact and accurate thermal model for package level fast thermal simulation and analysis.

## 1.4 Architectural Level Thermal Management Techniques

Multi-core and upcoming many-core architectures are the trend for current and future microprocessor designs. With the scaling of CMOS devices, the chip multiprocessor is progressing from the *multi-core* era to *many-core* era [42–45] where thousands of cores are predicted to be integrated on a single chip connected by a network-on-chip (NoC) in the near future. However, the increasing chip complexity and power envelope elevate the peak temperature of chips and increase the on-chip thermal gradients. Thermal constraints are the major driving force for wide adoption of multi/many core architectures. As the power density continues to increase, the excessively high temperature spots would

adversely lead to performance degradation, increased cooling costs, reduced reliability and aging issues for those high-performance chip multiprocessors [6,46]. Thermal-induced long-term reliability issues such as electro-migration, thermal stress migration, time-dependent dielectric breakdown (TDDB) and thermal cycling are especially a growing concern for to-day's microprocessors as the mean time to failure (MTTF) depends exponentially on the chip temperature due to Arrhenius relationship [47]. The semiconductor industry faces the challenges of maintaining reliability due to the continued increase in die size and number of transistors as well as the continuous scaling of transistors for increasing performance [48]. For multi/many core reliability systems, the power consumptions and the resulting temperatures of cores highly depend on the tasks or loads. As a result, effectively regulating the on-chip temperatures and optimizing related reliability issues of these chips becomes very important and imperative.

Dynamic thermal management (DTM) techniques have been proposed in the past to keep the temperature to stay below a limit [5,6,49]. These techniques, which typically consist of dynamic voltage and frequency scaling (DVFS), task throttling and clock gating, were first developed for single-core microprocessors. Recently, those techniques have been extended for multi-core architectures and MPSoCs. They include control theory-based frequency-control method [50], the combined DVFS and task migration methods [51,52], the predictive control method [53,54], and task migration based methods [53,55,56].

Among these thermal management methods, task scheduling/migration technique serves as a viable way to control the temperature of the cores [53, 55, 56] while maximally maintaining the performance of the processor system. The general idea of these methods

is to migrate the heavy loaded task away from an overheated core to a cooler core. The traditional approach like [55], typically migrate the heaviest task (with largest power consumption) to the coolest cores to balance the temperature profile of all the cores. However, such an intuitive decision may lead to sub-optimal result, because it does not take into account of the influence from the neighboring cores as well as transient heat removal effect due to heat conduction of the package. To improve the thermal profile, recent work [56] proposed a new thermal management approach that used a temperature incremental factor to count the heat flux from the neighboring cores. But this approach is more of an ad-hoc way than a systematic way to solve this problem.

Also, most existing approaches [30,53,55,56] are centralized control approaches, which requires a Centralized Manager (CM) to monitor the temperature and power of each core in the many-core microprocessor, and globally reallocate the resources and schedule the tasks. The centralized control method, however, will not be scalable in the context of future many core processors with hundreds and even thousands of cores [42,44]. It will suffer high computational costs inside the CM, single point of failure, and large volume of monitoring and communication traffics around CM. To mitigate these problems of the centralized control approach, the distributed control approaches have been proposed [57–59]. In [57], an agent-based distributed power/thermal management method was proposed, using dynamic voltage and frequency scaling technique. The thermal management is done via localized agent negotiations and each agent (or the core it represents) acts independently and is reactive to its neighbors only. But this method only considers the current steady-state temperatures of each core for each agent to make the decision. In [58,59], a distributed

task migration technique, called *DTB-M*, was proposed. DTB-M monitors steady-state temperature and power in each local core, and performs task migration only between two neighboring cores. However, DTB-M aims at reducing average temperature based only on steady-state temperature information, and thus may be sub-optimal in terms of reducing on-chip thermal hot spots and transient temperature variations.

We notice that considering the thermal transient effects can be very straightforward: one can perform the full-blown transient thermal analysis inside the internal loops of those thermal optimization and scheduling algorithms. However, the major issue for such a simple approach is the prohibitive cost. Some existing works for thermal-aware task scheduling for real-time systems still try to avoid the transient analysis in the scheduling method based on the mixed-integer linear programming method [60]. However, it only allows the transient analysis on the relaxed heuristic method. In Chapter 5 of this dissertation, we propose a new task-migration based distributed thermal management scheme to reduce the on-chip temperature variance and the occurrence of hot spots by considering package related transient thermal effects without incurring the high computation costs of transient thermal analysis.

# 1.5 System Level Reliability Modeling and Management Techniques

High on-chip temperature could exacerbate reliability issues, which are becoming a limiting constraint in high-performance microprocessor designs due to the high failure rates in deep submicron and nanoscale devices. The increase in failure rates is caused by high integration levels and higher power densities, which leads to excessive on-chip temperatures. The introduction of new materials, processes and devices, coupled with voltage scaling limitations and increasing power consumption will impose many new reliability challenges. The semiconductor industry faces the challenges to maintaining reliability such as the continued increase in die size and number of transistors and the constant scaling of transistors for performance [48]. Increasing transistor density and thus power density is causing higher temperatures on chip, resulting in failure acceleration. Scaling to smaller transistors increases failure rates by shrinking the thickness of dielectrics. This has led the International Technology Roadmap for Semiconductor (ITRS) to predict the onset of significant reliability problems in the future, and at a pace that has not been seen in the past [61].

Some initial efforts have been carried out for system level reliability analysis for SoCs (system-on-a-chip). RAMP [62] is the first architecture level tool for modeling the long-term processor reliability of microprocessors at the design stage. The follow-up work by the same authors proposed a dynamic reliability management (DRM) concept by dynamic voltage and frequency scaling (DVFS) [63]. It showed that it is not sufficient to just manage the temperature or power from the reliability perspective. Method in [64] shows that the power/performance and reliability are intrinsically conflicting metrics and have strong interactions on SoC designs, and proposes a joint policy optimization method. Another dynamic reliability management method was proposed in [65], in which a simple PID based run-time control was applied to optimize the performance subject to the long-term reliability constraints. Recently, DVFS techniques considering negative bias temperature

instability (NBTI) effects were proposed for microprocessors [66]. A supply voltage scheduling technique was proposed for optimizing energy subject to NBTI constraints [67].

Despite of these early efforts, the research on system or architecture-level reliability analysis and optimization is still in its early stage. For electromigration related reliability effects, all the early efforts at architecture and system level are based on the simple semi-empirical Black's equation shown below to estimate the mean time to failure (MTTF) of interconnect wires and simplified series reliability and constant failure rate models [62, 68].

$$MTTF = Aj^{-n}exp\{E_a/kT\}$$

(1.1)

Here, j is the current density, k is the Boltzmann's constant; T is the absolute temperature;  $E_a$  is the EM activation energy. However, the current density exponent, n, and Activation energy  $E_a$  in (1.1) actually depends on current density and temperature [69,70]. Typically the values of the two parameters were obtained at the stressed (accelerated) conditions. However, value of n actually depends on the current densities and residual stress and  $E_a$  is the function of temperature. As a result, the Black's equation will not be accurate for normal operational conditions of chips. Second, the Black's equation ignores the impacts of existing thermal stress and residual stress caused by the chip manufacture process and chippackage interactions. Third, existing approaches employed high pessimistic series reliability model to compute the reliability of interconnect wires. For practical mesh-structured power grid networks, which are more susceptible to EM reliability issues, there exists high-level redundancy as the failure of some of wire segments will not be necessary to result in the voltage drops below the critical threshold, which really determine the failure of the power grid networks.

Chapter 6 of this dissertation first presents a new life time resource based reliability model derived from fundamental physics principles instead of black equation, and then proposes a dynamic management method for multi/many core processors to effectively balance and compensate the consumption of the life time resources across the cores so that early failure of a particular core could be prevented.

### 1.6 High Lights and Contributions

To enable thermal aware chip and package design and alleviate the on-chip thermal stress and related issues, new thermal modeling and management methods to analyze and control on-chip temperature at different abstraction levels are studied in this dissertation, thermal related reliability problems are also addressed with new prospectives, and the major contributions of this dissertation work are explained and summarized as the following different aspects:

• A compact closed form thermal model of TSV (Through silicon via) is proposed based on physics principles for chip level thermal behavior modeling of 3D ICs. The proposed model considers both insulation and the filling core of TSV because the thermal resistivity of copper is approximately one third that of silicon and cannot be ignored. We show that the space between TSVs has a significant impact on the lateral thermal resistance as TSVs change the isothermal profiles of each other, and the models for TSV array or farms must be TSV space dependent. Model calibration is usually required to take into account this variance. The research shows that the thickness of the insulation layer has limited influence on the accuracy of the proposed

model in many practical cases and does not need to be calibrated. The proposed model is fully compatible with existing TSV modeling approaches, and could be integrated into a finite difference thermal model code to improve the accuracy of package level thermal simulation.

- Top down thermal modeling flow based on subspace identification method is proposed to extract the package level thermal model for microprocessors package thermal analvsis. We observe that the subspace identification method may suffer predictability problem when power maps are given where power inputs are spatially correlated. For instance, the busy ALU will be likely to have frequent memory accesses and many instruction fetching activities. As a result, the corresponding function units will have power increases or decreases at the same or similar times. Such correlated input signals pose difficulty for the subspace identification method and will easily lead to loss of predictability as it is more difficult to distinguish the contributions from specific inputs when all the inputs have the same or similar transient waveforms. In this dissertation, we show that the input power signal needs to meet some independence requirements to ensure model predictability (rank of input power maps or their power signal matrix needs to meet certain requirements). A new algorithm, ThermSubCP, can generate independent power maps to meet the spatial rank requirement and can also automatically select the order of the resulting thermal models for the given error bounds.

- In package level thermal modeling, we also show that thermal package systems are fundamentally nonlinear. One important example is that thermal conductivities of

silicon and package materials are temperature dependent. Another example is the changing thermal boundary conditions due to different fan speeds. To mitigate this problem, in the proposed subspace identification based top-down modeling flow, we apply the piecewise linear (PWL) scheme to characterize the nonlinear thermal behavior under these conditions. Our experiments show that the nonlinear effects in the thermal systems are typically mild and weak but are still significant enough to warrant the PWL modeling. However, nonlinearity due to boundary conditions can be very significant. PWL can deal with both mild and hard nonlinearities. We observe that the PWL method can lead to smaller models and reduced modeling costs compared to high order model approximation. This is important as the costs of identifying and simulating the reduced models will grow at least quadratically, it is critical to reduce the model order to maintain the efficiency gain from the reduced order modeling. The new modeling algorithm, ThermSubPWL, partitions the nonlinear ranges (due to temperature or boundary condition changes) into a number of small ranges and performs the modeling on each range using the previously proposed *ThermSubCP* method. A linear transformation method, which avoids the existing multi-transition requirement, is proposed to transform the identified linear local-models to the common state basis to build the continuous piecewise linear model. To the best knowledge of the authors, the proposed method is the first work addressing the nonlinear thermal modeling problem.

• To achieve more efficient architecture level thermal management, unlike the existing approaches, which use the steady state temperature, we propose a new temperature

metric, called effective initial temperature, to guide the task migration process. The new temperature metric is based on frequency domain moment matching analysis technique. It automatically and systematically considers the impacts of neighbor cores. Furthermore, it also considers the thermal conductivity and thermal capacity effects of each individual core and rest of other cores. We show that by considering the dominant temperature moment component, the resulting algorithm can lead to more reduction of thermal hot spots without full transient thermal simulation. Furthermore, we show how the effective initial temperature of each core can be computed in a localized or distributed way for fully distributed thermal management. With locally computed effective initial temperature of each core as a thermal metric, the proposed distributed task migration algorithm can still perform very effective task scheduling in a distributed way compared to the centralized one but with much better scalability to future many-core systems with hundreds or thousands of cores.

• To effectively quantize and control electro-migration induced reliability (EM-reliability) of the system that is strongly influenced by temperature, the EM induced mean time to failure (MTTF) at the system level is modeled as a resource, which is abstracted from a more physics-based EM model at the chip physical level. Such resource-based EM models allow more flexible dynamic EM-reliability management for multi/many-core systems. With the insight of the new EM model, we propose a new reliability resource based task migration method to explicitly balance the consumption of EM life time resources for all the cores. The new method will lead to the equal chance of failure of these cores, which will maximize the life time of the whole multi/many core

system by eliminating early failures. With balanced life time among all the cores, low power mode control is enabled to compensate the excessively consumed life time of all the cores when the chip is assigned with heavy tasks for a certain period of time. In this way, the MTTF of all the cores could be compensated to satisfy the requirement, giving the multi/many core system more flexibility to handle heavy task assignment when needed.

## 1.7 Organization

The rest of the dissertation is organized as the following: In Chapter 2, the fundamental concepts and methods of thermal modeling and management are introduced. In Chapter 3, a physical lateral thermal model of TSV and TSV arrays is proposed, and incorporated into finite difference method for chip level thermal behavior modeling and simulation of 3D stacked ICs. In Chapter 4, the proposed top-down methodology for package level thermal behavior modeling are presented, and piecewise linear method to improve model accuracy in presence of thermal nonlinearity is discussed. In Chapter 5, an architecture level distributed thermal management method that considers package induced transient thermal effect to make optimized task migration decision is presented. In Chapter 6, a system level EM-reliability model is proposed, which models EM-reliability as life time resources, and a dynamic reliability management method is developed to balance and compensate the life time resources. Chapter 7 concludes this dissertation.

## Chapter 2

## Fundamentals of Thermal

## Modeling and Management

## Methods

This chapter gives an overview of the basic concepts and methods used in thermal modeling and related management methods. It also presents a detailed discussion of the mathematics that will be used in the later chapters of this dissertation.

## 2.1 General Thermal Modeling Concepts and Approaches

This section gives a brief introduction to the basical concepts in thermal modeling and simulation, and outlines fundamental approaches used in this area.

### 2.1.1 Deriving Thermal Behavior Model from its Physical Principle

The fundamental physics principle of heat transfer and dissipation is given by the 3-D parabolic partial differential equation [71]. Using  $T(\vec{r},t)$  to represent the temperature at location  $\vec{r}$  and time point t, the 3-D heat equation could be written as the following:

$$\rho C_p \frac{\partial T(\vec{r}, t)}{\partial t} = \nabla \cdot [\kappa(\vec{r}, T) \cdot \nabla T(\vec{r}, t)] + g(\vec{r}, t), \qquad (2.1)$$

which subjects to Robin's boundary condition

$$\kappa(\vec{r}, T) \frac{\partial T(\vec{r}, t)}{\partial n} = h(T(\vec{r}, t) - T_{amb}). \tag{2.2}$$

In (2.1),  $\rho$  ( $Kg/m^3$ ) denotes the density of the material that conducts the heat flow,  $C_p$  ( $J/Kg\cdot K$ ) represents the thermal capacity of the material,  $\kappa$  ( $W/m\cdot K$ ) represents the thermal conductivity of the material, and g ( $W/m^3$ ) represents energy generation rate inside the material. In the boundary condition in (2.2), n represents a unit vector that is normal to the boundary surface, h ( $W/m^2K$ ) represents the heat-transfer coefficient for the convective surface, and  $T_{amb}$  is the temperature of the ambient environment that surrounds the thermal system.

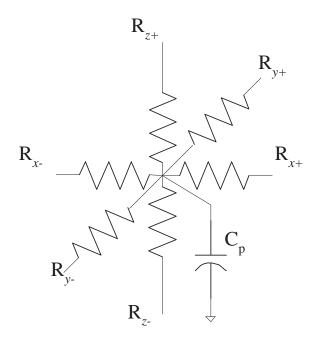

In order to compute the item  $\kappa(\vec{r},T)\cdot\nabla^2T(\vec{r},t)$  in (2.1), denote  $\kappa_x$ ,  $\kappa_y$ , and  $\kappa_z$  as the effective thermal conductivities along the x, y, and z axes, respectively. Let  $\kappa_{x+}$ ,  $\kappa_{x-}$ ,  $\kappa_{y+}$ ,  $\kappa_{y-}$ ,  $\kappa_{z+}$ , and  $\kappa_{z-}$  represent the effective thermal conductivities in the x+, x-, y+, y-, z+, and z- directions to model the inhomogeneous of the heat conduction media, respectively, i.e., we have the following relations

$$\kappa_x = \begin{cases} \kappa_{x+}, & x \to x+, \\ \kappa_{x-}, & x \to x-, \end{cases}$$

$$\kappa_y = \begin{cases}

\kappa_{y+}, & y \to y+, \\

\kappa_{y-}, & y \to y-,

\end{cases}$$

$$\kappa_z = \begin{cases}

\kappa_{z+}, & z \to z+, \\

\kappa_{z-}, & z \to z-.

\end{cases}$$

Using the finite difference method, derivatives at discretized mesh grid (i, j, k) are given by

$$\kappa_{x} \frac{\partial^{2} T}{\partial x^{2}} = \kappa_{x} \frac{T_{i+1,j,k} - 2T_{i,j,k} + T_{i-1,j,k}}{\Delta x^{2}}$$

$$= \frac{\kappa_{x+}}{\Delta x^{2}} (T_{i+1,j,k} - T_{i,j,k}) + \frac{\kappa_{x-}}{\Delta x^{2}} (T_{i-1,j,k} - T_{i,j,k}),$$

$$\kappa_{y} \frac{\partial^{2} T}{\partial y^{2}} = \kappa_{y} \frac{T_{i,j+1,k} - 2T_{i,j,k} + T_{i,j-1,k}}{\Delta y^{2}}$$

$$= \frac{\kappa_{y+}}{\Delta y^{2}} (T_{i,j+1,k} - T_{i,j,k}) + \frac{\kappa_{y-}}{\Delta y^{2}} (T_{i,j-1,k} - T_{i,j,k}),$$

$$\kappa_{z} \frac{\partial^{2} T}{\partial z^{2}} = \kappa_{z} \frac{T_{i,j,k+1} - 2T_{i,j,k} + T_{i,j,k-1}}{\Delta z^{2}}$$

$$= \frac{\kappa_{z+}}{\Delta z^{2}} (T_{i,j,k+1} - T_{i,j,k}) + \frac{\kappa_{z-}}{\Delta z^{2}} (T_{i,j,k-1} - T_{i,j,k}),$$

where  $T_{i,j,k}$  represents the temperature at node (i, j, k);  $\Delta x$ ,  $\Delta y$ , and  $\Delta z$  are the discretized steps along the x, y, z directions, respectively. Thus, the discretized form of (2.1) is

$$\rho C_p \frac{dT}{dt} = -\left(\frac{\kappa_{x+}}{\Delta x^2} + \frac{\kappa_{x-}}{\Delta x^2} + \frac{\kappa_{y+}}{\Delta y^2} + \frac{\kappa_{y-}}{\Delta y^2} + \frac{\kappa_{z+}}{\Delta z^2} + \frac{\kappa_{z-}}{\Delta z^2}\right) T_{i,j,k}

+ \frac{\kappa_{x+}}{\Delta x^2} T_{i+1,j,k} + \frac{\kappa_{x-}}{\Delta x^2} T_{i-1,j,k} + \frac{\kappa_{y+}}{\Delta y^2} T_{i,j+1,k}

+ \frac{\kappa_{y-}}{\Delta y^2} T_{i,j-1,k} + \frac{\kappa_{z+}}{\Delta z^2} T_{i,j,k+1} + \frac{\kappa_{z-}}{\Delta z^2} T_{i,j,k-1} + g_{i,j,k,t},$$

where  $g_{i,j,k,t}$  is the heat generation at node (i,j,k). Furthermore, the above discretized heat equation for the mesh grid (i,j,k) can be rewritten as follows

$$\rho C_p \Delta V \frac{dT}{dt} = -(G_{x+} + G_{x-} + G_{y+} + G_{y-} + G_{z+} + G_{z-})T_{i,j,k} + G_{x+}T_{i+1,j,k} + G_{x-}T_{i-1,j,k} + G_{y+}T_{i,j+1,k} + G_{y-}T_{i,j-1,k} + G_{z+}T_{i,j,k+1} + G_{z-}T_{i,j,k-1} + \Delta V g_{i,j,k,t},$$

(2.3)

where  $\Delta V = \Delta x \Delta y \Delta z$ ,  $G_{x+} = \frac{\kappa_{x+} \Delta y \Delta z}{\Delta x}$ ,  $G_{x-} = \frac{\kappa_{x-} \Delta y \Delta z}{\Delta x}$ ,  $G_{y+} = \frac{\kappa_{y+} \Delta x \Delta z}{\Delta y}$ ,  $G_{y-} = \frac{\kappa_{y-} \Delta x \Delta z}{\Delta y}$ ,  $G_{z+} = \frac{\kappa_{z+} \Delta x \Delta y}{\Delta z}$ , and  $G_{z-} = \frac{\kappa_{z-} \Delta x \Delta y}{\Delta z}$  give the physics definitions of the thermal conductance along x-,x+,y-,y+,z- and z+ directions. Since the method of calculating thermal conductance in z- and z+ directions have been studied [16], this dissertation will be focusing on the way to calculate the lateral thermal conductance in x-,x+,y- and y+ direction, and apply it to finite difference thermal analysis through (2.3).

Note that the thermal conduction inside the material is now modeled by (2.3), however, at the convective surface, the boundary condition (2.2) governs the thermal transfer, which could be discretized along x, y, and z directions as

$$\kappa \frac{T_{x0} - T_{x1}}{\Delta x} = h_x (T_{amb} - T_{x0})$$

$$\kappa \frac{T_{y0} - T_{y1}}{\Delta y} = h_y (T_{amb} - T_{y0})$$

$$\kappa \frac{T_{z0} - T_{z1}}{\Delta z} = h_z (T_{amb} - T_{z0})$$

(2.4)

in which  $T_{x0}$ ,  $T_{y0}$ , and  $T_{z0}$  are the temperature grids at the convective boundary, and  $T_{x1}$ ,  $T_{y1}$ , and  $T_{z1}$  are the temperature the adjacent temperature grids of those at the convective boundary inside the material. Using the thermal conductance  $G_x$  defined in (2.3), the thermal boundary equations could be written as

$$(T_{x0} - T_{x1})G_x = \frac{h_x \Delta x G_x}{\kappa} T_{amb} - \frac{h_x \Delta x G_x}{\kappa} T_{x0}$$

$$(T_{y0} - T_{y1})G_y = \frac{h_y \Delta x G_y}{\kappa} T_{amb} - \frac{h_y \Delta y G_y}{\kappa} T_{y0}$$

$$(T_{z0} - T_{z1})G_z = \frac{h_z \Delta x G_z}{\kappa} T_{amb} - \frac{h_z \Delta z G_z}{\kappa} T_{z0}$$

$$(2.5)$$

Hence, in this way, given the chip and package properties as well as the convective cooling conditions, the thermal model of the chip and package could be built through finite difference method based on the physics principles of heat conduction equation (2.1).

### 2.1.2 Equivalent Thermal Circuit Modeling Approach

The discretized heat equation (2.3) has the same format as that of electrical network. With temperature analogous to voltage, and energy source analogous to current source, the discretized heat equation (2.3) could be represented by an equivalent circuit model, which is called thermal circuit to distinguish it with the conventional electrical circuit. Assuming the model has totally n temperature node, it could be proved that, the discretized heat equation (2.3) could be written as the following matrices format [71]:

$$GT(t) + C\frac{dT(t)}{dt} = BU(t), (2.6)$$

in which  $T(t) \in \mathbb{R}^n$  is the temperature vector with the temperature value T(i,j,k) as its element for each grid (i,j,k),  $G \in \mathbb{R}^{n \times n}$  is the thermal conductance matrix with  $G_x$ ,  $G_y$ , and  $G_z$  in (2.3) as its elements,  $C \in \mathbb{R}^{n \times n}$  is the thermal capacitance matrix with  $\rho C_p$  as its elements in diagnal,  $U(t) \in \mathbb{R}^n$  is the energy source vector with  $\Delta V g(i,j,k,t)$  as its elements for each grid (i,j,k) at time instance t, and B is the position matrix that defines the position of the energy sources. A node of the equivalent thermal circuit is shown in Fig.2.1 to represent the thermal model described by the discretized heat equation (2.3). The temperature node connects to its 6 adjacent nodes through thermal resistors, and is connected to ground by a heat capacitor and a current source that mimic the energy source inside the mesh grid the node represents. In this way, thermal model is abstracted into an

equivalent circuit network with resistors and capacitors, and the circuit analysis techniques could be directly applied to thermal analysis, providing insights for intuitive understanding of thermal behavior of the chip and its package.

### 2.1.3 State Space Thermal Modeling Approach

In general, multiple-input and multiple-output dynamic systems could be modeled by state space equations as the following

$$x(t+1) = Ax(t) + Bu(t)$$

$$y(t) = Cx(t) + Du(t),$$

(2.7)

where  $A \in \mathbb{R}^{l \times l}$  is a state matrix, l is the number of states.  $B \in \mathbb{R}^{l \times p}$ ,  $C \in \mathbb{R}^{q \times l}$ , and  $D \in \mathbb{R}^{q \times p}$ . The input vectors  $u(t) \in \mathbb{R}^{p \times 1}$  are the measured power input traces and output vectors  $y(t) \in \mathbb{R}^{q \times 1}$  are the temperature responses. The thermal system could be perceived as a multiple-input and multiple-output dynamic system with power as inputs  $u(t_i)$  and temperature as outputs  $y(t_i)$ . The benefit of representing the thermal system in this way is that subspace identification method could be directly used to identify the state space matrices A, B, C, and D based on the measured inputs and outputs of the system [41]. Once these matrices are determined, the state space equation could be used to predict the temperature response under any power profiles. Note that given the discrete system matrices, the continuous system matrices can be obtained using methods such as Zero-Order-Hold, Impulse Invariance and Tustin Approximation [72]. Hence, this research uses subspace identification method to find the state matrices for discrete time model.

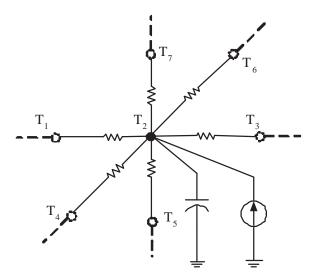

Figure 2.1: A node of the equivalent thermal circuits, which represents a temperature point connecting to all its adjacent nodes through thermal conductance.

### 2.2 Review of Subspace Identification Method

This section reviews an important techniques – subspace identification method that will be using for thermal modeling in this dissertation. That is, given the time domain waveform of input u(t) and output y(t), subspace identification method identifies the state matrices A, B, C, and D of (2.7). The subspace identification basically tries to first identify the system states first (Kalman states), then the state matrices will be obtained by the least square based optimization method [41]. For subspace method, there are several implementations such as the Ho-Kalman' method, the MOSEP method and the N4SID (Numerical algorithms for Subspace System Identification) method [40]. In this research, we apply the widely used N4SID method for the thermal system identification problem.

#### 2.2.1 Introduction to N4SID Method