# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

## **Title**

Off-chip wire distribution and signal analysis

## **Permalink**

https://escholarship.org/uc/item/4mk8x7r2

## **Author**

Shi, Rui

## **Publication Date**

2008

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

Off-Chip Wire Distribution and Signal Analysis

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science

by

Rui Shi

## Committee in charge:

Professor Chung-Kuan Cheng, Chair Professor Peter M. Asbeck

Professor Fan Chung Graham

Professor Ernest Kuh

Professor Tajana Simunic Rosing

Copyright

Rui Shi, 2008

All rights reserved.

| The dissertation of Rui Shi is approved, and it is accept- |

|------------------------------------------------------------|

| able in quality and form for publication on microfilm and  |

| electronically:                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

|                                                            |

| Chair                                                      |

2008

University of California, San Diego

## TABLE OF CONTENTS

| Signature Page                                               | iii  |

|--------------------------------------------------------------|------|

| Table of Contents.                                           | iv   |

| List of Figures.                                             | vii  |

| List of Tables.                                              | ix   |

| Acknowledgements                                             | x    |

| Vita, Publications and Field of Study                        | xii  |

| Abstract of the Dissertation                                 | xiii |

|                                                              |      |

| Chapter 1 Interconnection in High-speed Electronic System    |      |

| 1.1 Overall View of Electronic System                        |      |

| 1.2 Interconnection in Electronic System                     |      |

| 1.3 Escape Routing                                           | 5    |

| 1.3.1 Background                                             | 5    |

| 1.3.2 Problem Description                                    | 7    |

| 1.3.3 Strategies for Improving Escape Routing Performance    | 8    |

| 1.3.3.1 Traditional Method                                   | 8    |

| 1.3.3.2 Special Placement of the Pins/Pads                   | 9    |

| 1.3.3.3 Routing Resource Exploration                         | 10   |

| 1.4 Signaling Analysis                                       | 11   |

| 1.4.1 Background                                             | 11   |

| 1.4.2 Eye Diagram Prediction                                 | 13   |

| 1.4.2.1 Analytical Technique                                 | 13   |

| 1.4.2.2 Analysis Based on Unit Pulse Response                |      |

| 1.4.2.3 Analysis Based on Step Response                      |      |

|                                                              |      |

| Chapter 2 Escape Routing for Square Area Array               |      |

| 2.1 Escape Bottleneck and Escape Sequence Analysis           | 19   |

| 2.1.1 Escape Bottleneck                                      | 20   |

| 2.1.2 Maximum Flow Problem Formulation                       | 20   |

| 2.1.3 Maximum Flow Algorithm for Escape Bottleneck Analysis  | 22   |

| 2.1.4 Escape Bottleneck Analysis                             | 24   |

| 2.2 Escape Sequence and Guidelines for Escape Routing        | 27   |

| 2.3 Escape Routing Strategies with Different Escape Sequence | 28   |

| 2.3.1     | Row-by-row Escape Sequence                               | 28 |

|-----------|----------------------------------------------------------|----|

| 2.3.2     | Parallel Triangular Escape Sequence                      | 29 |

| 2.3.3     | Central Triangular Escape Sequence                       | 30 |

| 2.3.4     | Two-sided Escape Sequence                                | 31 |

| 2.3.5     | Four Escape Sequence Strategies Comparison               | 33 |

| 2.4 Aut   | omatic Escape Routing Algorithm                          | 34 |

| 2.4.1     | The Characteristics of Escape Routing                    | 34 |

| 2.4.2     | Automatic Escape Routing Algorithm                       | 35 |

| 2.5 Exp   | perimental Results                                       | 37 |

| 2.6 Ana   | ılysis Model                                             | 43 |

| 2.6.1     | Extraction Tool Raphael                                  | 43 |

| 2.6.2     | Extraction Demonstration.                                | 44 |

| Chapter 3 | Escape Routing for Hexagonal Area Arrayagonal Area Array |    |

| 3.1.1     | Feature 1: Increasing the Number of I/Os                 |    |

| 3.1.2     | Feature 2: Increasing the Spacing between I/Os           |    |

| 3.2 Esc   | ape Routing Strategies for Hexagonal Area Array          |    |

| 3.2.1     | Column-by-Column Horizontal Escape Routing               |    |

| 3.2.2     | Two-sided Horizontal/Vertical Escape Routing             | 54 |

| 3.2.3     | Multi-direction Hybrid Channel Escape Routing            | 56 |

| 3.2.      | 3.1 Array Partition and Hybrid Channel                   | 56 |

| 3.2.      |                                                          |    |

| 3.2.      | 3.3 Automatic Escape Routing Procedure                   | 59 |

| 3.2.      | 3.4 Escape Routing Example                               | 60 |

| 3.3 Ana   | llysis of Escape Routing for Hexagonal Array             | 61 |

| 3.4 Ana   | ılysis Model                                             | 62 |

|           |                                                          |    |

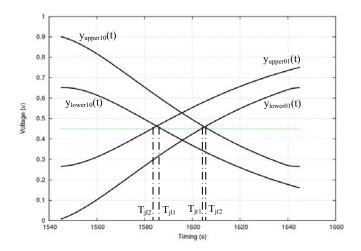

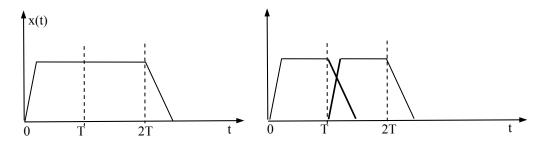

| Chapter 4 | Eye Diagram Prediction for High Speed Signaling          |    |

|           | liminaries                                               |    |

| 4.1.1     | Step Response and Digital Signal Communication           |    |

| 4.1.2     | Eye Diagram                                              |    |

|           | rst-case Eye Diagram Prediction                          |    |

| 4.2.1     | Voltage Bounds for Worst-case Eye Diagram                |    |

| 4.2.2     | Worst-case Eve Opening                                   | 71 |

| 4.2.3      | Worst-case Timing Jitter                                    | 71 |

|------------|-------------------------------------------------------------|----|

| 4.2.4      | Worst-case Input Data Pattern                               | 72 |

| 4.3 Ana    | llysis of Prediction                                        | 73 |

| 4.3.1      | Prediction Complexity                                       | 73 |

| 4.3.2      | Prediction Error                                            | 73 |

| 4.3.3      | Digital Signal with Symmetric and Asymmetric Rise/Fall Time | 74 |

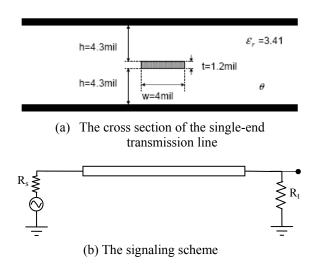

| 4.4 Veri   | fication Experiments                                        | 75 |

| 4.4.1      | Experiment Setup                                            | 75 |

| 4.4.2      | Experimental Results                                        | 77 |

| 4.5 Esca   | aping Wires Analysis                                        | 84 |

| Chapter 5  | Conclusion                                                  | 87 |

| 5.1 Diss   | sertation Contribution                                      | 87 |

| 5.2 Futu   | ıre Work                                                    | 88 |

| 5.2.1      | Escape Routing                                              | 89 |

| 5.2.2      | Eye Diagram Prediction                                      | 90 |

| References |                                                             | 91 |

## LIST OF FIGURES

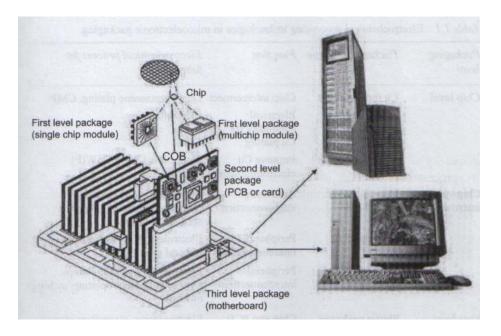

| Figure I. 1 Typical assembly hierarchy of the electronic system.                   | 3   |

|------------------------------------------------------------------------------------|-----|

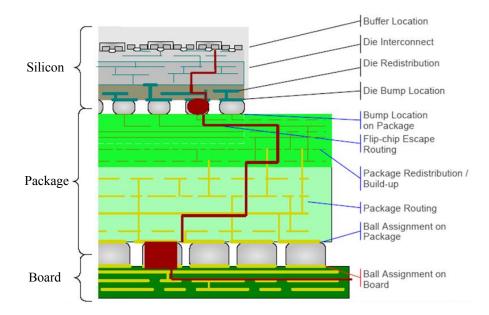

| Figure I. 2 Interconnection in the electronic system.                              |     |

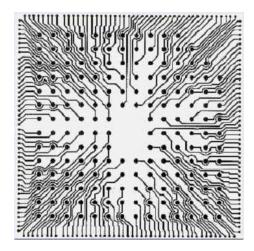

| Figure I. 3 Escape routing connects I/O pins to outside.                           |     |

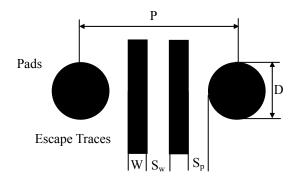

| Figure I. 4 Fundamental parameters of package design.                              |     |

| Figure I. 5 Traditional escape routing.                                            |     |

| Figure I. 6 Formation of groups of pins for three different values of n            |     |

| Figure I. 7 The preferential routing structure.                                    |     |

| Figure I. 8 Eye diagram.                                                           |     |

| Figure I. 9 Circuit model of a transmission-line with resistive termination        |     |

| Figure I. 10 PWL waveform model                                                    |     |

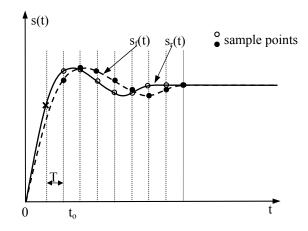

| Figure I. 11 A generic bitonic step response.                                      |     |

| Figure 1. 11 A generic oftonic step response                                       | 1 / |

| Figure II. 1 Routing graph.                                                        | 21  |

| Figure II. 2 Sink vertices and source vertices.                                    |     |

| Figure II. 3 Modified Ford-Fulkerson algorithm                                     |     |

| Figure II. 4 Modified Dijkstra's algorithm.                                        |     |

| Figure II. 5 Escape routing bottleneck.                                            |     |

| Figure II. 6 Row-by-row escape routing.                                            | 29  |

| Figure II. 7 Parallel triangular escape routing.                                   |     |

| Figure II. 8 Central triangular escape routing.                                    |     |

| Figure II. 9 Two-sided escape routing.                                             |     |

| Figure II. 10 The transformation of array outline.                                 |     |

| Figure II. 11 Escape routing algorithm.                                            |     |

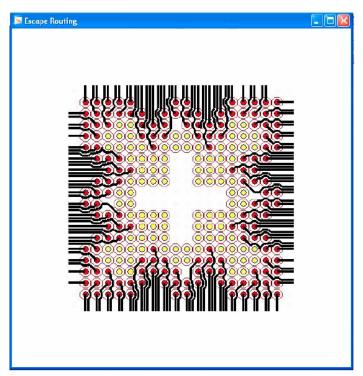

| Figure II. 12 Escape routing results.                                              |     |

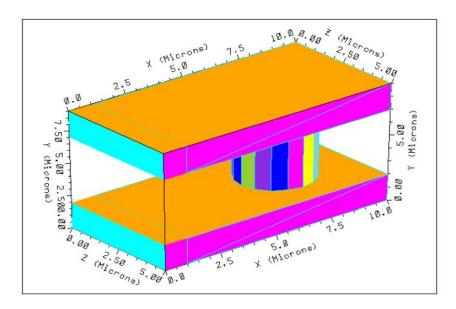

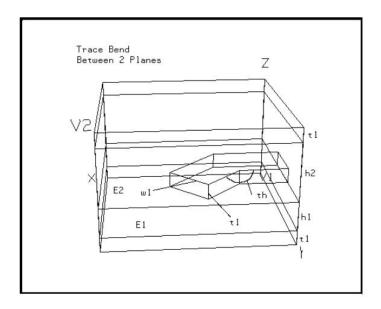

| Figure II. 13 Extraction example, via structure                                    |     |

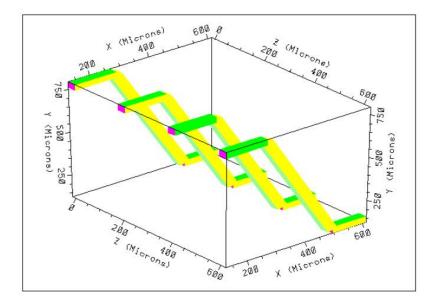

| Figure II. 14 Extraction example, bond leads structure                             |     |

| Figure II. 15 Escaping wire structure                                              |     |

| Figure II. 16 Escaping wire modeling                                               | 43  |

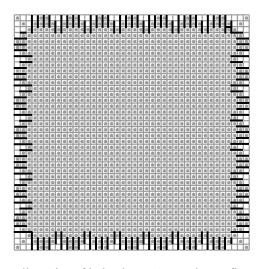

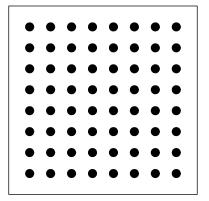

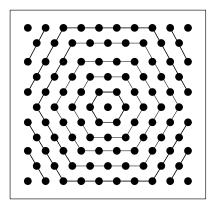

| Figure III. 1 Square grid array.                                                   | 47  |

| Figure III. 2 Hexagonal area array.                                                |     |

| Figure III. 3 Traditional escape routing for square grid array.                    |     |

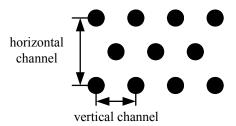

| Figure III. 4 Vertical/horizontal channels.                                        |     |

| Figure III. 5 Zigzag columns in hexagonal array.                                   |     |

| Figure III. 6 Column-by-column horizontal escape routing.                          |     |

| Figure III. 7 Column-by-column horizontal escape routing                           |     |

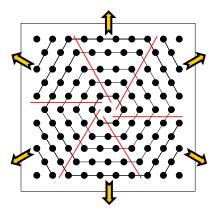

| Figure III. 8 Two-sided horizontal/vertical escape routing.                        |     |

|                                                                                    |     |

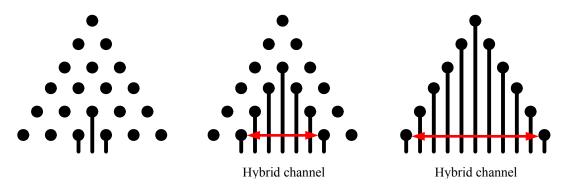

| Figure III. 9 Nested hexagons.                                                     |     |

| Figure III. 10 Hexagonal array partition.                                          |     |

| Figure III. 11 Indented outline and hybrid channel.                                |     |

| Figure III. 12 Indented rows in hexagonal array.                                   |     |

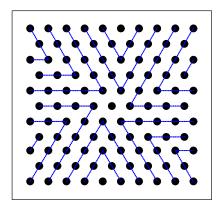

| Figure III. 13 Automatic escape routing.                                           |     |

| Figure III. 14 Multi-direction hybrid channel escape routing.                      | 60  |

| Figure IV. 1 Step response and digital signals                                     | 65  |

| Figure IV. 1 Step response and digital signals.  Figure IV. 2 Eye Diagram          |     |

| Figure IV. 2 Eye Diagram.  Figure IV. 3 Algorithm for '1' edge rising lower bound. |     |

| rigure rv. 3 migoriumi ior ir euge rising lower bound                              | / 0 |

| Figure IV. 4 Step response example.                                          | 70 |

|------------------------------------------------------------------------------|----|

| Figure IV. 5 Timing jitter                                                   | 72 |

| Figure IV. 6 Unit pulse response doesn't work                                | 74 |

| Figure IV. 7 The single-end transmission line structure.                     | 76 |

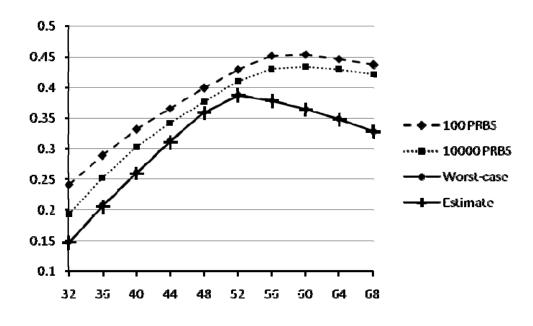

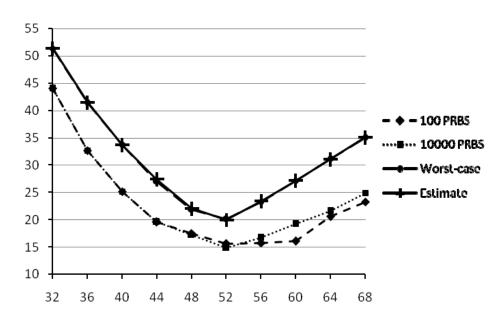

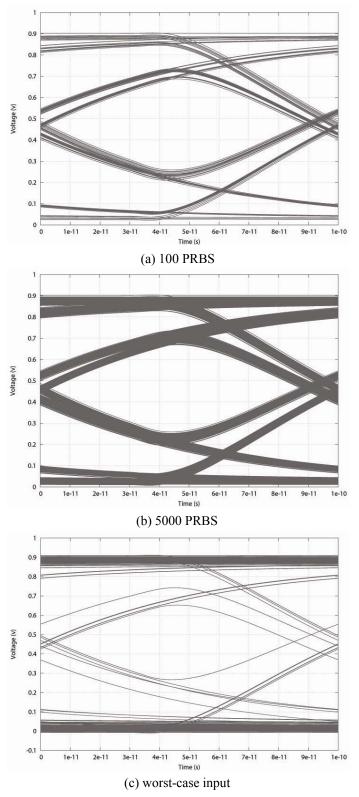

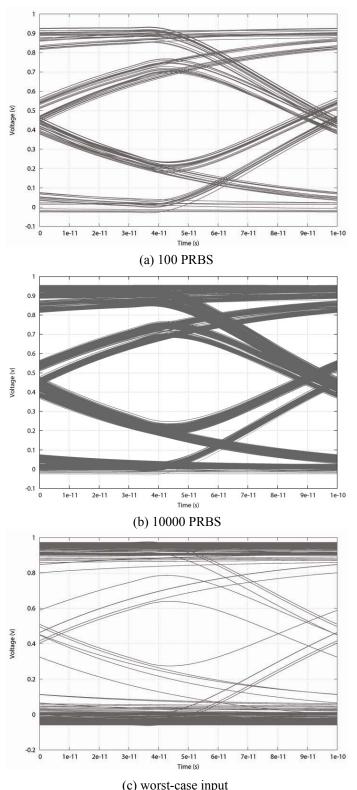

| Figure IV. 8 Results for signal with symmetric rise/fall time                | 80 |

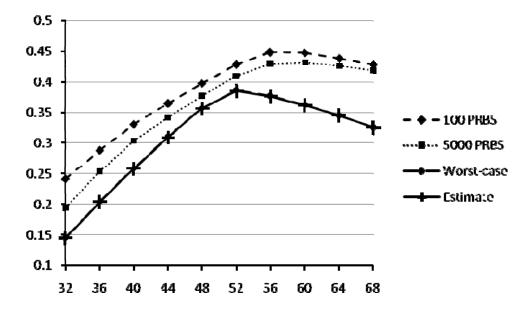

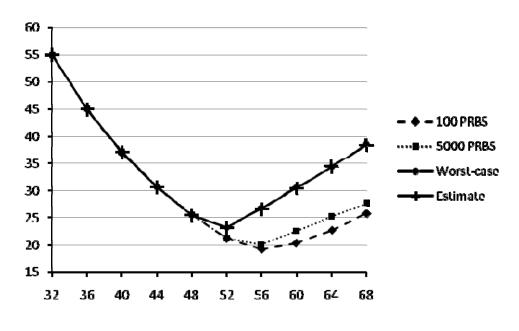

| Figure IV. 9 Results for signal with asymmetric rise/fall time.              | 81 |

| Figure IV. 10 Eye diagram for signal with asymmetric rise/fall time, Rt=52 Ω | 82 |

| Figure IV. 11 Eye diagram for signal with symmetric rise/fall time, Rt=60 Ω  | 83 |

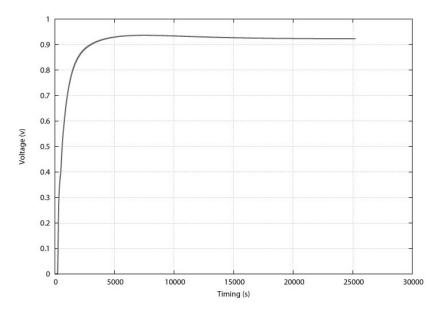

| Figure IV. 12 Step response of escaping wire                                 | 85 |

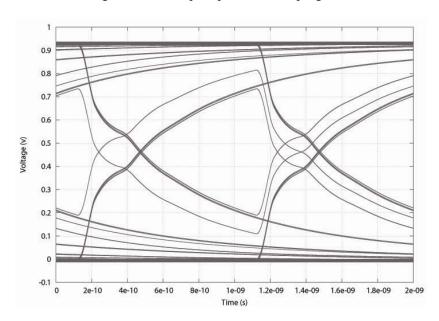

| Figure IV. 13 Eye diagram of escaping wire                                   | 85 |

## LIST OF TABLES

| Table I. 1 Characterization of a generic bitonic response                         | 17 |

|-----------------------------------------------------------------------------------|----|

| Table II. 1 The number of breakout I/Os escaped on each layer for four strategies | 38 |

| Table II. 2 The number of breakout I/Os escaped on each layer for four strategies | 38 |

| Table III. 1 Square grid array vs. Hexagonal array                                | 49 |

| Table III. 2 Square grid array vs. Hexagonal array                                | 50 |

| Table III. 3 Practical parameters for condition, unit: μm.                        | 53 |

| Table III. 4 Practical parameters for condition, unit: μm•                        | 59 |

| Table IV. 1 Voltage bounds equations                                              | 68 |

| Table IV. 2 Example: find minimum value starting from array B.                    | 71 |

| Table IV. 3 Eye opening, symmetric rise/fall time.                                | 78 |

| Table IV. 4 Timing jitter, symmetric rise/fall time.                              | 78 |

| Table IV. 5 Average CPU time, symmetric rise/fall time.                           | 78 |

| Table IV. 6 Eye opening, asymmetric rise/fall time.                               | 79 |

| Table IV. 7 Timing jitter, asymmetric rise/fall time.                             |    |

| Table IV. 8 Average CPU time, asymmetric rise/fall time.                          | 79 |

#### **ACKNOWLEDGEMENTS**

First of all, I would like to express my deep and sincere gratitude to my advisor, Professor Chung-Kuan Cheng for his continuous support. I appreciate all his contributions of time, ideas, and funding to make my Ph.D. experience productive and stimulating. His wide knowledge and his logic way of thinking have been of great value for me. His understanding, encouraging and personal guidance have provided a good basis for the present thesis. I could not have imagined having a better advisor for my PhD, and without his common-sense, knowledge, perceptiveness and cracking-of-the-whip I would never have finished.

I wish to express my sincere thanks to Professor Ernest Kuh of University of California, Berkeley. His supervision and constructive advice on my research work is extremely important to me.

My thanks and appreciation goes to my dissertation committee members, Professor Fan Chung Graham, Professor Peter M. Asbeck and Professor Tajana Simunic Rosing for technical discussions and their advices and reviews of this dissertation.

I am indebted to my many student colleagues for providing a stimulating and fun environment in which to learn and grow. I am especially grateful to Haikun Zhu, Peng He, Yi Zhu, Ling Zhang, Zhengyong Zhu, Hongyu Chen, Bo Yao, Shuo Zhou, Jianhua Liu, Renshen Wang, Wanping Zhang and many others.

I am grateful to Dan Beckman and Dawei Huang of SUN Microsystems. They provided me valuable technical discussions and support in escape routing project.

I wish to thank my entire family for providing a loving environment for me. Especially, I would like to give my special thanks to my husband Dawei Sun, whose patient love enabled me to complete this work, my thanks to my child, Kevin W. Sun for giving me happiness and joy.

Lastly, and most importantly, I wish to thank my parents, Junheng Shi and Jirong Wu.

They raised me, taught me, and loved me. To them I dedicate this thesis.

Chapter 2, in part, is a reprint of the paper "Layer Count Reduction for Area Array Escape Routing" co-authored with Hongyu Chen, Chung-Kuan Cheng, Dan Beckman and Dawei Huang in the proceedings of 2005 International Conference and Exhibition on Device Packaging. The dissertation author was the primary investigator and author of this paper.

Chapter 3, in part, is a reprint of the paper "Efficient Escape Routing for Hexagonal Array with high I/Os density" co-authored with Chung-Kuan Cheng in the proceedings of 43<sup>rd</sup> ACM/IEEE Design Automation Conference 2006. The dissertation author was the primary investigator and author of this paper.

Chapter 4, in part, is a reprint of the paper "Efficient and Accurate Eye Diagram Prediction for High Speed Signaling" co-authored with Wenjian Yu, Yi Zhu, Chung-Kuan Cheng and Ernest S. Kuh in the proceedings of IEEE/ACM International Conference on Computer-Aided Design 2008. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 1999 | B.E. in Electronic Engineering<br>Tsinghua University, Beijing, China          |

|------|--------------------------------------------------------------------------------|

| 2002 | M.S. in Computer Science and Technology<br>Tsinghua University, Beijing, China |

| 2008 | Ph.D. in Computer Science<br>University of California, San Diego               |

#### **PUBLICATIONS**

- R. Shi and C.K. Cheng, Efficient Escape Routing for Hexagonal Array with high I/Os density, DAC 2006, pp1003-1008

- R. Shi, H. Chen, C.K. Cheng, D. Beckman, and D. Huang, Layer Count Reduction for Area Array Escape Routing, International Conference and Exhibition on Device Packaging 2005

- R. Wang, R. Shi, and C.K. Cheng, Layer Minimization of Escape Routing in Area Array Packaging, ICCAD 2006, pp.815-819

- Z. Zhu, R. Shi, and C.K. Cheng, An Unconditional Stable General Operator Splitting Method for Transistor Level Transient Analysis, ASP-DAC 2006, pp.428-433

- H. Zhu, R. Shi, C.K. Cheng, and H. Chen, Approaching Speed-of-light Distortionless Communication for On-Chip Interconnect, ASP-DAC 2007, pp.684-689

- H. Zhu, R. Shi, H. Chen, C.K. Cheng, A. Deutsch, and G. Katopis, Distortion Minimization for Packaging Level Interconnects, EPEP 2006, pp.175-178

- H. Chen, R. Shi, C.K. Cheng, and D.M. Harris, Surfliner: A Distortionless Electrical Signaling Scheme for Speed of Light On-Chip Communications, ICCD 2005, pp.497-502

- W. Zhang, L. Zhang, R. Shi, H. Peng, Z. Zhu, C.E. Lew, M. Rajeev, S. Toshiyuki, I. Noriyuki and C.K. Cheng, Fast Power Network Analysis with Multiple Clock Domains, ICCD 2007, pp.456-463

#### FIELDS OF STUDY

Major Field: Computer Engineering Studies in VLSI CAD Professor Chung-Kuan Cheng

#### ABSTRACT OF THE DISSERTATION

## **Off-Chip Wire Distribution and Signal Analysis**

by

### Rui Shi

Doctor of Philosophy in Computer Science

University of California, San Diego, 2008

Professor Chung-Kuan Cheng, Chair

With the steady progress of high performance electronic systems, the complexity of the electronic systems grows continuously and new features like high-speed, low power and low cost, become the key issues. The interconnection in the electronic systems distributes the power, clock and transfers the electrical signals among numerous components. As the feature size of microelectronic technology becomes smaller, the design and analysis of the interconnection are more important for the performance and cost of the system.

The escape routing design is a new important problem in the interconnection design because the number of chip/package input/output (I/O) pins has continuously been growing for high-speed high-performance system. The traditional escape routing strategy and several improvements, pins/pads special placement and routing resource exploration, could not handle large number of I/Os efficiently and usually require increased cost. We introduce a novel concept, escape sequence, develop efficient escape routing strategies based on the new concept and model the escaping wires using 3D extraction.

(1) For square grid array, we formulate and solve a maximum flow problem to analyze the escape bottleneck in area array. The layer count can be decreased dramatically by optimizing the I/O escape sequence. Two new escape routing strategies, central triangular escape routing and two-sided escape routing, are proposed and the number of escape routing layers could be reduced dramatically. We implement an automatic escape routing program to verify our analysis and to compare different escape sequence strategies. The escaping wires could be modeled as frequency dependent RLGC circuit for signal performance analysis.

(2) For hexagonal area array, we analyze its preponderant properties that the hexagonal array could increase the density of I/Os in the array remarkably. We propose three escape routing strategies for the hexagonal array: column-by-column horizontal escape routing, two-sided horizontal/vertical escape routing, and multi-direction hybrid channel escape routing. We can escape I/Os in the hexagonal array in the same or less number of routing layers compared with square grid array. Therefore, we could reduce the number of escape routing layers as well as increase the density of I/Os.

The eye diagram prediction is an important problem in the interconnection analysis because an eye diagram provides the most fundamental and intuitive view to evaluate the signal quality of high-speed communication. The traditional method to obtain the eye diagram involves performing a time domain simulation. It requires a very long simulation time and usually could not accurately characterize the communication systems because the limited length pseudorandom bit sequence (PRBS) as the input stimulus. Several eye diagram prediction methods, analytical techniques, analysis based on unit pulse response and analysis based on step response, have their application constraints because of their assumptions and usually could not handle general systems. We introduce an efficient and accurate method, the accumulative prediction method, to predict the eye diagram for high-speed signaling systems. We use the step response of the signaling system to extract the worst-case eye diagram, including the eye opening and timing jitter. Furthermore, this method generates the input data

patterns which produce the worst-case inter-symbol interference. The main advantage is that this general-purpose method can handle signals with asymmetric as well as symmetric rise/fall time. Furthermore, the complexity of the proposed method is linear O(n), where n is the number of time points of step response. This method can be applied to analyze the signal performance in escape routing. It is very useful to analyze various high speed signaling systems.

# Chapter 1

# Interconnection

# in High-speed Electronic System

Electronic system permeates our daily life as well as the advanced technology applications. As the microelectronic technology develops, the complexity of electronic systems grows rapidly. Typically, a system consists of a hierarchical structure and the interconnection plays a very important role in the system. The routing stage in the design process implements the interconnection with specific objectives. New features like high-speed, low power and low cost, become the key issues.

## 1.1 Overall View of Electronic System

The electronic systems are usually built in a hierarchical structure. The integrated circuits (ICs) are at the heart of electronic systems, a package is the housing of the ICs and high level boards assemble the packaged components together to form a system.

What is integrated circuit? An integrated circuit is a thin chip consisting of semiconductor devices, mainly transistors, as well as passive components like resistors. The integrated circuit was made possible by min-20th-century technology advancements in

semiconductor device fabrication. Only a half century after their development was initiated, integrated circuits have become ubiquitous. Computers, cellular phones, and other digital appliances are now inextricable parts of the structure of modern societies. That is, modern computing, communications, manufacturing and transport systems, including the Internet, all depend on the existence of these circuits.

As of 2004, typical chips are of size 1cm<sup>2</sup> or smaller, and contain millions of interconnected devices. The growth of complexity of integrated circuits follows a trend called "Moore's Law". Moore's Law in its modern interpretation states that the number of transistors in an integrated circuit doubles every two years.

The packages cover the ICs to assure environmental protection for the IC chips and to provide complete testing and high-yield assembly to the next level of interconnection. The electronic packaging establishes the interconnection between the chip and package and package to board, etc. and maintains a suitable operating environment for the ICs to function effectively and efficiently. There are several reasons why an IC is packaged, the primary functions are to provide electrical interconnection (both power and signal distribution), allow for efficient heat dissipation (cooling), and physically protect the IC.

Higher-level assemblies (e.g. boards, cards, or flexible substrates) are needed to connect packaged electronic devices because of the complexity of current electronic systems. Usually, the IC packages will be connected to each other through printed circuit board (PCB). And PCBs provide mechanical support as well as electrical interconnect. A PCB interconnects electronic components using flat conductive traces laminated onto a non-conductive substrate. Usually a PCB is built as a stack of layer pairs. Each pair starts as an insulating sheet with copper deposited on one or both sides. The copper sides of the sheet are first etched with different wiring patterns. Then the sheets are stacked into a sandwich separated by insulating

material. Small holes are drilled into the board and are plated with metal, so that electrical contact is made with each layer that has copper left at the hole-location.

The typical assembly hierarchy of the electronic system is shown in Figure I. 1 [15]. Chip level (zero level) packaging includes chip metallization, and provisions for chip-package interconnection. The first level packaging is the assembly of chip and substrate (organic or ceramic package) to form a single or a multiple chip module. In some cases chips may be directly attached to the card (chip-to-board, COB). The second level packaging in the assembly of chip modules and other components on PCBs. The third level packaging differs; depending on the sophistication of the system it may involve several PCBs plugged into a motherboard.

Figure I. 1 Typical assembly hierarchy of the electronic system.

## 1.2 Interconnection in Electronic System

The interconnection connects many kinds of electronic components to form a complicated system, as shown in Figure I. 2. They distribute the power and clock for all the

components and transfer the electrical signals among those components simultaneously. They work like the interleaved roads in our real world. IC chips are connected through connections and traces in the packages and boards. And inside IC chips, basic functional devices are implemented in the semiconductor substrate (silicon) and then are connected through multiple routing layers on top of the substrate.

The interconnection design directly influences the performance and cost for the whole electronic system. Along with the scaling of feature size in IC chips, the performance of on chip interconnection becomes more and more important for the circuit. The wiring delay becomes comparable with gate delay and start to dominate the delay of the circuit. The interconnection distributing clock signals consume roughly one fourth of the total power consumption of the IC. And the crosstalk (coupling effects) between signal wires becomes increasingly critical to on-chip timing and even functionality. For the package and board design, chip-to-chip interconnection is the fundamental objective. Obviously, the performance of the interconnection inside the packages and on the board will constrain the performance of the whole system. Also for the packages and boards, the number of interconnection layers and the technology for different interconnection style are directly related to the cost of the system.

The routing problem is one of the most important phases in the VLSI and PCB design. In the routing stage, the interconnection is implemented under specific objectives considering performance and cost. The electronic design automation tools help the designer to implement the interconnection efficiently and effectively. For the routing stage, the given information includes the placement of all components with physical locations, the net-list with physical locations for all terminals and related technical parameters, such as the number of routing layers, the wire width, the wire spacing and so on. Here, "terminal" means the endpoint of the interconnection, "net" represents a collection of terminals all of which are, or must be,

connected to each other electrically and "net-list" is the list of names of all nets and their terminals. After routing stage, all the interconnection will be routed using wires on different layers and the physical layout for all the interconnection will be output finally.

Figure I. 2 Interconnection in the electronic system.

## 1.3 Escape Routing

## 1.3.1 Background

The complicated practical electronic systems usually contain a great number of circuits and interconnections. A number of chips will be interconnected on organic or ceramic first-level packages. The electrical connections between the chip and the package are referred to as chip-level/first-level interconnections. Currently, there are three principal technologies in use: wire-bonding (WB), tape automated bounding (TAB) and flip-chip solders connection (C4). Because the complexity of current systems, the packaged electronic devices need to be connected to higher-level assemblies (e.g. boards, cards, or flexible substrates). These interconnections are referred to as package-to-board/second-level interconnections.

IC packaging technology is undergoing rapid change with the move to nanometer-scale ICs, becoming the critical link in the system interconnect flow. Without this key element of a comprehensive flow (silicon to package to board) the end result can easily be silicon that is difficult or expensive to implement into a system. Package and board design are facing many new challenges, such as high speed interconnections, signal integrity, cost efficiency and so on.

As the feature size of microelectronic technology becomes smaller, the complexity of electronic systems grows proportionally. With the steady progress of high performance electronic systems, the number of chip/package input/output (I/O) pins has continuously been growing. According to Rent's rule [3], the number of I/O signals of a module is a function of the number of gates in it:

$$N_p = K_p N_g^{\beta} \tag{I.1}$$

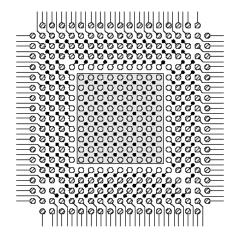

where,  $N_p$  is the number of external signal connections,  $N_g$  is the number of logic gates,  $K_p$  is a constant, and  $\beta$  is the Rent's rule constant which depends significantly on the kind of module considered. Today's high-performance ICs exhibit upwards of 2,000 I/O pins and require packages that sometimes exceed 100 layers and will go onto boards with more than 50 layers. Increasing demand for high I/O pins count prompts the packaging industry to explore new technologies, such as area array interconnection [18][25][34][37], CSP (chip scale packing), BGA (ball grid array) [38], and so on. Area array packaging contains an array of pads, pins, or solder-balls located directly underneath a unit of package area. In order to connect the area array I/Os to the next level assembly, all the I/O pins need to break out to the outside. As shown in Figure I. 3, the wires for breaking out I/O pins are referred to as Escape Routing [18][25][34][37].

Figure I. 3 Escape routing connects I/O pins to outside.

Currently, the high count and density of I/Os require multilayer for escape routing. These interconnections directly affect the cost and performance of the whole electronic systems. The increase in the number of escape routing layers will result in a higher manufacturing cost of substrates used as a package or a board. Thus an efficient and effective escape routing strategy which achieve high performance with low cost will greatly benefit the electronic product.

## **1.3.2** Problem Description

In the escape routing problem, I/Os inside the area array are the objects; the corresponding pads are the obstacles and the spaces scattering among the pads in the area array are the routing resources. Fundamentally there are three basic guidelines which are described blow.

- (i) Spacing between two wires and the width of the wire. As shown in Figure I. 4, the wire width is W and the pitch is  $(W+S_w)$ , where  $S_w$  is the spacing between the two consecutive edges of the wires.

- (ii) Minimum distance  $S_p$  between the edge of the pad and the edge of any metal, as shown in Figure I. 4.

- (iii) Diameter of the pad, D, and pitch, P, between two consecutive pads, as shown in Figure I. 4.

Figure I. 4 Fundamental parameters of package design.

Usually the spacing between two wires  $S_w$  and the spacing between pad and wire  $S_p$  are identical, we can use S to represent the spacing.

## 1.3.3 Strategies for Improving Escape Routing Performance

### 1.3.3.1 Traditional Method

Connecting the I/O pins in the area array to the outside, the traditional method is very straightforward. It breaks out the pins located in the outside rows/columns first as shown in Figure I. 5. For one routing layer, the escape routing wires for pins located inside will go through outside pins/pads. The spacing between two consecutive pads constrains the number of wires going through, thus limit the number of pins escaped for one layer. In this conventional geometry of pad and wire, increasing the number of wires between pads can only be realized by decreasing wire width and spacing. While these dimensional changes expose the substrate to cost, yield and reliability issue. Guinn et al. [17] have shown the trends in required area for packaging various devices depending on their number of I/Os, and pointed out that the progress in feature dimensional reduction technology of PWB (printed wiring board) is too slow compared with that of ICs.

Figure I. 5 Traditional escape routing.

### 1.3.3.2 Special Placement of the Pins/Pads

The usual area array is a regular grid array, while this kind of methods changes the placement of pins/pads in the array to improve the escape routing performance [18][20][31].

Hirt et al. [20] analyzed the escape routing with multilayer structure according to the conventional procedure from a concentrated I/Os of area flip chip and BGA. The escape routing wires are modeled to connect the pins/pads with a VIA to an inner layer and then go out. The VIAs for pins in the outmost rows are arranged in staggered rows and the VIAs for pins inside are located inside the array. This VIAs arrangement decreases the area overhead for escape routing and makes as many rows as possible escaped on each layer to minimize the number of layers needed.

Gasparini et al. [18] suggested a specific placement of bumps for C4 packages to minimize the number of package layers. The pins/pads are placed in staggered form to maximize the number of pins that can be routed in a single routing layer.

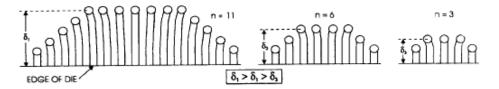

Assume the distance between two consecutive bumps in the outmost row allows n number of wires going through, and then n bumps will be placed inside in staggered form. Figure I. 6 shows the bumps placement and escape routing wires for three different values of n.

The placement with large n will increase the value of  $\delta$ , which means the depth of the bumps group from edge to inside. No bumps will be placed inside the region surrounded by the bumps group and the array edge. This region will be wasted and the larger the value of n, the bigger the wasted area. So for a given package design, there is an optimum value of n that can increase the number of bumps routed in one layer with reasonable group depth  $\delta$ .

Figure I. 6 Formation of groups of pins for three different values of n.

Each group can be routed in a single layer.

By incorporating this design method into the placement of the signal I/O, Andrews et al. [1] B. Analui, J. Buckwalter, and A. Hajimiri, "Data-dependent jitter in serial communications," *IEEE Trans. Microwave Theory Tech.*, Vol. 53, No. 11, pp. 1841-1844, Nov. 2005.

[2] have succeeded to reduce the number of layers of an organic substrate for flip chip packaging.

However, this special placement of bumps requires some changes in pad allocation, not only on the substrate, but also on the corresponding IC. To realize a universal method applicable covering package to board interconnection, in which footprint is generally standardized, it is necessary to achieve the reduction of the layer counts without changing the pad allocation on the interface.

## **1.3.3.3 Routing Resource Exploration**

Horiuchi et al. [21] studied the effects of routing manner on the layer count and

suggested a preferential routing which creates specific pad geometry resulting in a high wiring efficiency. Since nothing changed in both manufacturing processes and materials, this method is very practical for assembly of the high I/O flip chips, CSPs, and BGAs.

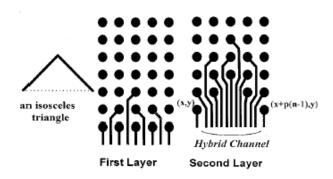

The preferential routing breaks out pins following a triangular array outline as shown in Figure I. 7. The number of pins escaped on one layer is increased because of the "hybrid channel" with high routing capacity.

Figure I. 7 The preferential routing structure.

The size of hybrid channel is 5.

Obviously, the number of wires going through the "hybrid channel" will be increased as n increases. While on the other hand, the number of "hybrid channels" will be decreased for a certain size area array. So for a given package design, there is an optimum value of n that can achieve the best improvement compared with traditional method.

# 1.4 Signaling Analysis

## 1.4.1 Background

Signals are communicated through interconnection in the electronic systems. They are propagated among function cells in the chip and among chips in the boards. The signal performance [7][10][30][33], e.g. delay, bandwidth and power, is used to evaluate the

interconnection design. Propagation delay is a measurement of the time for a signal to reach its destination. As the feature size of microelectronic technology becomes smaller, the interconnection delay becomes comparable with the gate delay and start to dominate the delay of the circuit. Reducing the signal delays in digital circuits allows them to process data at a faster rate and improve overall performance. Bandwidth is the difference between the upper and lower cutoff frequencies of the communication channel and is typically measured in hertz. It often refers to a data rate measured in bits/s in digital system because the digital data rate limit (or channel capacity) of a physical communication link is related to its bandwidth in hertz. Power consumption is the energy consumed by the digital circuits. It is limited primarily by power dissipation concerns. So low power consumption is a big issue in high speed integrated circuit design. Moreover, the distortion, noise and interference on signal waveforms will also constrain the system performance in high speed signaling system.

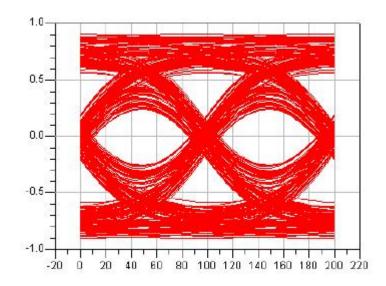

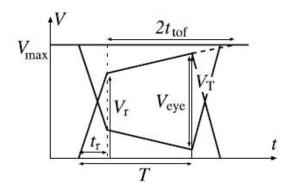

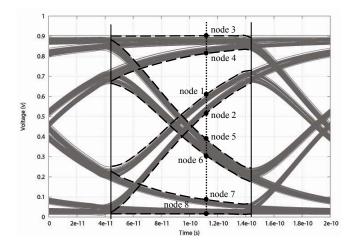

An eye diagram [4] provides the most fundamental and intuitive view to evaluate the signal quality of high speed communication. The eye diagram is an oscilloscope display in which a digital signal at the receiver side is repetitively sampled to get a good representation. It's created by taking the time domain signal and overlapping the waveform for a certain time window of multiple symbol periods, as shown in Figure I. 8. The eye diagram is a useful and intuitive technique for the qualitative analysis of signal performance in digital transmission. Eye diagrams show parametric information about the signal – effects deriving from physics. Several system performance measures can be derived from the eye diagram, e.g. the rise times, fall times, jitter, overshoot, eye opening and so on [5][29].

The traditional method to obtain the eye diagram involves performing a time domain simulation [26]. Due to the long simulation times, designers usually use a limited length pseudorandom bit sequence (PRBS) as the input stimulus. The eye diagram measurement

derived from a limited length PRBS usually is better than the worst-case for many high speed signaling systems. Fast and accurate eye diagram analysis methods are very helpful to analyze the system performance.

Figure I. 8 Eye diagram.

## 1.4.2 Eye Diagram Prediction

### 1.4.2.1 Analytical Technique

The analytical techniques estimate the eye diagram using analytical formula based on certain assumptions. Usually, it can analyze the eye diagram very fast because the analytical formula is used. However, the estimation accuracy is dependent on the approximation of the analytical formula and its applications are limited due to the assumptions for analytical formula derivation.

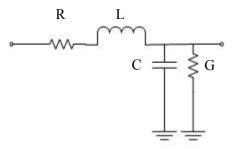

In [32], Tsuchiya et al. proposed an analytical formula to estimate the maximum eye-opening voltage. The circuit model of resistive terminated transmission-lines they investigate is shown in Figure I. 9. They model the waveform at the receiver side of transmission-lines by the PWL waveform model shown in Figure I. 10. They assume that the

driver of the interconnect achieves impedance matching and the voltage at the receiver side reaches  $V_{max}$  when the time  $2t_{tof}$  passed after rising. For simplicity, the supply voltage  $V_{dd}$  is assumed as 1V.

The maximum eye-opening voltage V<sub>eye</sub> is expressed as

$$V_{eye} = \begin{cases} 2V_r + (V_{\text{max}} - V_r) \frac{T - t_r}{t_{tof}} - V_{\text{max}} = (\frac{Z_n}{1 - 2\log n + Z_n} - \frac{nZ_n}{Z_n + 1}) (\frac{T - t_r}{t_{tof}} - 1) + \frac{nZ_n}{Z_n + 1} & \text{T-t}_r < 2t_{tof} \\ V_{\text{max}} & \text{T-t}_r > 2t_{tof} \end{cases}$$

$$(I.2)$$

The voltage  $V_r$  is rise voltage that is determined from the attenuation and the termination of the interconnect. The voltage  $V_{max}$  is the voltage level when the continuous "1" is input to the interconnect. The time  $t_r$  is the transition time of input pulse and period T is the minimum width of input pulse. The time  $t_{tof}$  is the signal time-of-flight. The parameter  $Z_n$  is the normalized impedance defined as  $Z_n = R_t/Z_0$ ,  $R_t$  is the termination resistance and  $Z_0$  is the characteristic impedance of transmission-line. The parameter n is the attenuation parameter defined as  $n = \exp(-\alpha l)$ ,  $\alpha$  is the attenuation constant of the interconnect and l is the length of the transmission-line.

The maximum estimation error in the eye opening voltage is around 10% compared with circuit simulation results. This estimation method can only be used for the resistive termination structure and the PWL approximation model will constrain it applications very much.

$$V_{\mathrm{dd}} = 1$$

near-end

$Z_0$

$R$ ,  $L$ ,  $C$

far-end

$R_t$

Figure I. 9 Circuit model of a transmission-line with resistive termination.

Figure I. 10 PWL waveform model.

### 1.4.2.2 Analysis Based on Unit Pulse Response

The unit pulse response is the output waveform when the input is unit pulse function. For digital signals with symmetric rise/fall time, the input binary data patterns can be simply modeled as combination of unit pulse function. For any linear time-invariant high speed signaling system, the signal performance can be efficiently analyzed based on the unit pulse response.

In [1], Analui et al. presented a method for predicting data dependent jitter introduced by a general linear time-invariant system based on the system's unit step response. Analytical formulas are derived for first-order system and approximated perturbation technique can be applied for general systems. The prediction has 7.5% error compared with measurement results.

In [7], Casper et al. developed the peak distortion analysis method to extract a worst-case eye diagram considering all interference sources. This method calculates the worst-case voltage or timing margin from the unit pulse response of the system and avoids tedious simulation. The eye edge due to the worst-case '1' is given by

$$s_1(t) = y(t) + \sum_{\substack{k = -\infty \\ k \neq 0}}^{\infty} y(t - kT) \big|_{y(t - kT) < 0}$$

(I.3)

and the eye edge due to the worst-case '0' is given by

$$s_0(t) = \sum_{\substack{k = -\infty \\ k \neq 0}}^{\infty} y(t - kT) \big|_{y(t - kT) > 0}$$

(I.4)

Therefore, the worst-case eye opening, e(t), is defined as

$$s_1(t) > e(t) > s_0(t)$$

(I.5)

However, these methods can analyze digital signals only with symmetric rise/fall time. It's inapplicable to analyze digital signals with asymmetric rise/fall time because the input data patterns cannot be modeled as combination of unit pulse input.

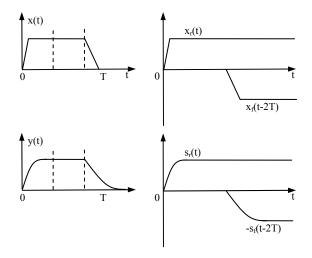

### 1.4.2.3 Analysis Based on Step Response

The step response of a general system is the time behavior of the outputs when its inputs change from zero to one in a very short time. For a signaling system, its step response implicates certain characteristics of the system. For example, the step response reveals the time-of-flight delay, the reflection and the saturation voltage for a transmission line communication.

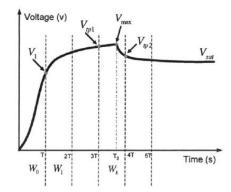

In [39], Zhu et al. predicted the eye diagram using the derived analytical formula based on step response. They assume the step response is bitonic which means the step response monotonically increases to its peak voltage and then monotonically decreases to its saturation voltage. A generic bitonic step response is shown in Figure I. 11 and its characterization is shown in Table I. 1.

Figure I. 11 A generic bitonic step response.

Table I. 1 Characterization of a generic bitonic response.

| $V_1 = V(T)$              | Voltage at time point T.                       |

|---------------------------|------------------------------------------------|

| $V_{\text{max}} = V(T_0)$ | Maximum voltage of the step response.          |

| $V_{sat} = V(\infty)$     | Final saturation voltage of the step response. |

| $V_{tp1} = V(kT)$         | 1-T < T < (1-+1)T                              |

| $V_{tp2} = V((k+1)T)$     | $kT \le T_0 \le (k+1)T$                        |

The worst-case eye opening is given by

$$V_{eye} = V_{\min}^{top} - V_{\max}^{bottom} = V_{sat} - 2(\max\{V_{tp1}, V_{tp2}\} - V_1)$$

(I.3)

The worst-case jitter is obtained from the fastest rising edge to the slowest rising edge.

The predicted jitter and eye opening are 10% deviation form HSPICE simulation results. However, the bitonic step response assumption does not hold for general signaling systems.

# Chapter 2

# **Escape Routing**

# for Square Area Array

With the steady progress of high performance electronic systems, the number of chip/package input/output (I/O) pins has continuously been growing. Increasing demand for high I/O pins count prompts the packaging industry to explore new technologies, such as area array interconnection, CSP (chip scale packing) and BGA (ball grid array). Escape routing connects the I/O pins to the next level assembly. It directly affects the cost and performance of the high-speed electronic systems. An efficient and effective escape routing strategy which achieve high performance with low cost will greatly benefit the electronic product.

The increase in the number of escape routing layers will result in a higher manufacturing cost of substrates used as a package or a board. In order to reduce the number of layers, intuitively some dimensional changes could be introduced, such as decreasing the width of wires, and the space between wires. However in these cases, the yield and reliability become concerned issues and new process technology is necessary as well. Methods to reduce the layer count without making any change in manufacturing process and footprint standard are accordingly desired.

In this chapter, we introduce a novel concept, escape sequence, which plays an important role in escape routing. We formulate and solve a maximum flow problem to analyze the escape bottleneck in area array. Based on the bottleneck analysis, we present the escape sequence concept and summarize several guidelines for escape routing design. Two new escape routing strategies are proposed and the number of escape routing layers can be reduced dramatically. We also design and implement an automatic escape routing program to facilitate investigating different escape routing strategies. The escaping wires could be modeled as frequency dependent RLGC circuit for signal performance analysis.

The area array considered in this chapter is a regular array, which is a fully populated array and is a typical square grid matrix. Totally, there are n<sup>2</sup> I/Os in an area array of size n. We also assume the blind via technology is used, which means that the connected via will disappear in the following routing layers after that I/O is escaped.

One of the main criteria of escape routing is the number of routing layers used for breaking out all I/Os in the area array, which will affect the manufacturing cost directly. Hence the reduction of the escape routing layer count is our emphasized objective.

Escape routing breaks out I/Os in the array to the outside and the objective is to minimize the number of routing layers and to break out I/Os as many as possible. In real applications, only signal IOs inside the array require breakout routing. But for analysis, all IOs are taken into consideration.

## 2.1 Escape Bottleneck and Escape Sequence Analysis

We explore the escape routing design from a bran-new point of view, escape sequence. We first analyze the escape routing bottleneck in the array, then present our escape sequence concept and summarize the critical guidelines for escape routing design.

## 2.1.1 Escape Bottleneck

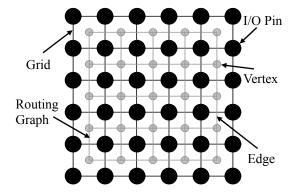

We define a routing graph G = (V, E) to extract the escape routing resources in an array and formulate a maximum flow problem on the routing graph for arrays with different I/O patterns. The maximum flow solution will reveal the bottleneck of escape routing for the array.

## 2.1.2 Maximum Flow Problem Formulation

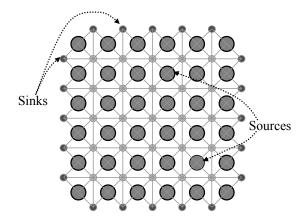

A routing graph is defined on the area array. We map the area array into grid with I/Os on the crossing points of the grid, as shown in Figure II. 1. Each grid cell corresponds to the routing space surrounded by four I/Os on its corners and is represented by a vertex in the routing graph. The edge in the routing graph connecting the vertices represents the routing channel between the adjacent grid cells. For a regular I/Os area array, the routing graph looks like a mesh. We append sink vertices, which are located on the boundary of the array, to represent the destinations of escape routing and all sinks will be connected together by a hyper-sink-vertex (Figure II. 2). I/Os in the array are referred as source vertices and similarly there's a hyper-source-vertex connecting all sources (Figure II. 2). Sink vertices will only connect to the vertex which corresponds to the nearest grid cell and source vertices will connect to four vertices which correspond to the four grid cells surrounding the I/O.

The vertices and edges are attached with a capacity, which is the number of available routing wires. The capacity of an edge is defined as the maximum number of wires that can route through two adjacent I/Os. The capacity of a vertex is defined as the maximum number of wires that can route through the diagonal of the grid cell. If some pins do not exist, which means some grid cells do not have exactly four I/Os in their corners, then we will assume that one routing wire locates at that corner. Thus the edges' capacity will constrain the number of

escape routing wires that go through horizontal or vertical channels, while the nodes' capacity will constrain the number of escape routing wires that go through the grid cells. The capacity of the edge between sink vertex and the vertex inside array is defined as the maximum number of wires that can route through the corresponding horizontal or vertical channel. The capacity of the edge between source vertex and the vertex inside array is defined as "1". Moreover the source vertex capacity is equal to "1" and the hyper-source-vertex capacity is equal to the total number of I/O pins in the area array. The capacity of sink vertex and hyper-sink-vertex is assigned infinite because they only represent the destinations and there is no routing resource constraint on them.

Figure II. 1 Routing graph.

Figure II. 2 Sink vertices and source vertices.

The maximum flow formulation from the hyper-source-vertex to the

hyper-sink-vertex in the routing graph can be summarized as follows and the maximum flow solution provides the upper bound of the number of I/Os that can be escaped in one layer for the area array.

Given: A routing graph G = (V, E)

Edge capacity  $C_e: E \rightarrow R+$

Vertex capacity  $C_v: V \rightarrow R^+$

Hyper-source-vertex s

Hyper-sink-vertex t

Find a maximum s-t flow.

#### 2.1.3 Maximum Flow Algorithm for Escape Bottleneck Analysis

We modify the typical maximum flow algorithm, Ford-Fulkerson algorithm [23], to solve our formulated problem. Ford-Fulkerson algorithm is a widely used method for solving maximum flow problem, while it can only handle edge capacity constraints. We expand this algorithm to consider both edge and vertex capacity constraints simultaneously. Figure II. 3 shows our modified Ford-Fulkerson algorithm.

Finding an augmenting path iteratively is an important process in Ford-Fulkerson algorithm. Intuitively, the I/Os inside area array will choose shortest route to the outside because longer wires will occupy more routing resources, will block more wires and will increase the possibility of crosstalk. Therefore we use Dijkstra's shortest path algorithm [23] to find augmenting path in the residual network. The length of every edge is defined as "1". We modify Dijkstra's algorithm similarly to consider the vertex capacity constraints as well as the edge capacity constraints. The augmenting path problem can be summarized as follows and the modified Dijkstra's algorithm for finding augmenting path is shown in Figure II. 4.

Given: A routing graph G = (V, E)

Edge capacity  $C_e: E \rightarrow R+$

Vertex capacity  $C_v: V \rightarrow R^+$

Flow in the graph f (e):  $E \rightarrow R$ , f(v):  $V \rightarrow R+$

Edge length  $l(e) = 1, \forall e \in E$

Hyper-source-vertex s Hyper-sink-vertex t

Find an augmenting path P from s to t.

$MaxFlow\_EB(G, C, s, t)$

Step1: Initialization

Let f be an initial feasible flow,

$f(e) = 0 \ (\forall \ e \in E) \ and \ f(v) = 0 \ (\forall \ v \in V)$

Step2: Flow Augmentation

Find an augmenting path P from s to t on the residual network.

If there is no augmenting path, go to Step5.

Step3: Flow Update

Check the minimum value, delta, of residual capacity on current augmenting path P.

Update the flow of edges and vertices along path P.

f(e) = f(e) + delta if e is a forward arc on P

f(e) = f(e) - delta if e is a backward arc on P

f(v) = f(v) + delta if the direction of flow on P is identical with previous flow

f(v) = diff(f(v), delta) if the flow on P is opposite to previous flow.

Step4: Go to Step2, repeat flow augmentation.

Step5: The present f is a maximum flow solution.

Step6: Stop.

Figure II. 3 Modified Ford-Fulkerson algorithm

```

AugPath EB(G,C,f,l,s,t)

Step1: Initialization

Let set S = \{s\}, N = \{\text{neighbors of } u \mid \forall u \in S\}

Label vertex s as "Done" and all other vertices as "No_Path"

Step2: Path Finding

Let set T = \phi.

For each vertex n in N

If some vertex u in S satisfy:

the capacity of the edge from u to n is not saturated,

the capacity of u and n is not saturated either

Then T = T \cup \{n\}.

Label all the vertices in T as "Done".

Let S = T, N = \{ \text{neighbors of } u, \text{ with "No_Path" label } | \forall u \in T \}

If t \in T, go to Step4.

If T = \phi, go to Step 5.

Step3: Go to Step2.

Step4: An augmenting path found, go to Step6.

Step5: There is no more augmenting path in the graph, go to Step6.

Step6: Stop.

```

Figure II. 4 Modified Dijkstra's algorithm.

# 2.1.4 Escape Bottleneck Analysis

We can identify the escape bottleneck in the area array from the maximum flow solution. Furthermore we can get guidelines for designing efficient escape routing strategies. In the maximum flow solution on the routing graph, we define bottleneck edge as the edge whose flow is equal to its capacity and all bottleneck edges form a bottleneck contour for the area array. This bottleneck contour constrains the maximum number of routing wires which can be routed through in one layer. The maximum flow value is the upper bound of the number of I/Os that can be escaped from the area array in one layer.

We do experiments on area array with different I/Os' patterns and identify the bottleneck edges and bottleneck contour. The size n of the area array in our experiments is 20. The pad pitch, pad diameter, line width, and spacing are 150μm, 75μm, 20μm, and 20μm respectively. Figure II. 6 shows the escape routing bottleneck and maximum flow values for five different I/Os' patterns. The black bold edges in the figures represent the bottleneck edges.

These experimental results reveal that the bottleneck contour of the area array always follows the outline of the array for usual patterns. We can say the number of I/Os that can be broken out in one routing layer will be constrained by the capacity of the array outline.

(a) Full populated area array, Maximum flow = 370.5

(b) Staggered distribution, Maximum flow = 446.23

Figure II. 5 Escape routing bottleneck.

(c) Rhombic distribution, Maximum flow = 271.62

(d) Zigzag outline (size of indention = 5), Maximum flow = 438.93

Figure II. 5 Escape routing bottleneck. (Cont.)

(e) Zigzag outline (size of indention = 7), Maximum flow = 447.26

Figure II. 5 Escape routing bottleneck. (Cont.)

# 2.2 Escape Sequence and Guidelines for Escape Routing

We introduce a new concept "escape sequence" in escape routing design. It is defined as the overall sequence of I/Os in the area array that are escaped layer by layer. The escape sequence determines the transformation of the array outline throughout the multi-layer escape routing. Based on our escape bottleneck analysis, the number of I/Os that can be broken out in one routing layer is usually constrained by the capacity of the array outline. After we escape I/Os for one routing layer, the pins left in the array will form a new pattern and the outline of the array with this new pattern constrains the number of I/Os that can be escaped in the next routing layer. Hence which I/Os escaped in current layer directly affects the escaping efficiency in the following layers. Furthermore, the pins located at the outmost positions are escaped definitely in every layer and the outline of the array inevitably shrinks to the center layer by layer. Therefore the transformation of the array outline in the escaping process is an important factor for escape routing efficiency and the escape sequence plays a critical role.

We summarize the guidelines for designing efficient escape routing as follows using

the escape sequence concept.

- (i) Maintain an appropriate shape of the array outline with large routing capacity layer by layer;

- (ii) Control the shrinking rate of the array outline in escaping process;

- (iii) Keep similar shape of the array outline for all escape routing layers for scalable consideration.

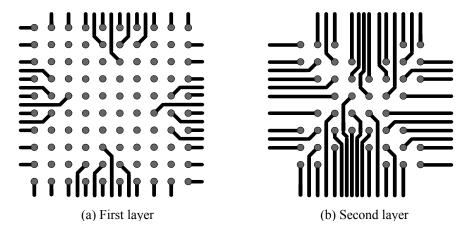

## 2.3 Escape Routing Strategies with Different Escape Sequence

We investigate different escape routing strategies from escape sequence point of view and propose two new methods which can reduce the number of escape routing layers dramatically. Those previous works can be classified as two escape sequence strategies. The escape sequence for the traditional method is straightforward sequential from outside to inside and we call it row-by-row sequence strategy. The escape sequence for the preferential escape routing method is to form zigzag array outline and we call it parallel triangular sequence strategy. According to the guidelines discussed in previous section, we propose two new escape strategies called central triangular sequence and two-sided sequence.

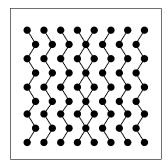

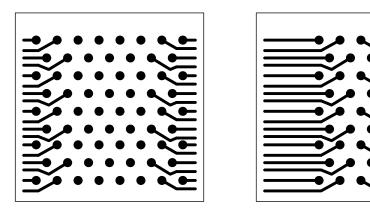

## 2.3.1 Row-by-row Escape Sequence

It is the conventional approach, as shown in Figure II. 6, which breaks out pins row by row (column by column) from outside to inside. If we assume the number of wires that can go through the vertical (horizontal) routing channel, i.e. the channel between adjacent I/Os with minimum pitch, is m.

$$m \le \frac{P - D - 2S_p + S_w}{W + S_w} < m + 1$$

(II.1)

Thus for the area array, m+1 rows (columns) can be escaped in one routing layer and the total

number of routing layers for breaking out an array with size n is

$$Num(layers)_{-}rbr = \left\lceil \frac{n}{2(m+1)} \right\rceil$$

(II.2)

This strategy is very straightforward but the array outline shrinks very rapidly layer by layer. Hence usually it needs many layers for escape routing for large size array.

Figure II. 6 Row-by-row escape routing.

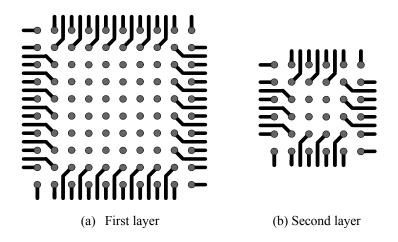

## 2.3.2 Parallel Triangular Escape Sequence

This strategy divides I/Os in the array into four parts by its two diagonals and I/Os are escaped to four directions, north, south, east and west respectively. I/Os in each part are further divided into small groups and each group is broken out following a triangular outline, as shown in Figure II. 7 (only two escape directions are shown for clarity). I/Os within the bottom triangle of each group are escaped in the first routing layer. The size of the triangle, k, defined as the number of I/Os on the bottom edge of the triangle, is decided by the vertical (horizontal) routing channel capacity m and we usually choose k as an odd number.

$$\frac{(k+1)^2}{4} \le (k-1)m + k$$

i.e.  $k \le 4m + 1$  (II.3)

In the second and following routing layers, each group has a triangular outline which supplies large routing capacity. We assume the number of wires that can go through the diagonal routing channel, i.e. the channel between diagonal adjacent I/Os, is q.

$$q \le \frac{\sqrt{2}P - D - 2S_p + S_w}{W + S_w} < q + 1 \tag{II.4}$$

As long as the condition (II.5) is satisfied, q+1 rows (columns) can be escaped in one routing layer following the triangular outline except (q-m) I/Os left. I/Os left in every layer are scattering in the array and can be escaped in the spare space.

$$q \le \frac{p - D/2 - W/2 - S_p}{W + S_w} \tag{II.5}$$

The total number of routing layers for breaking out an array with size n is

$$Num(layers) pt = 1 + \left[\frac{n-k-1}{2(q+1)}\right]$$

(II.6)

Compared with the traditional method, this escape sequence allows more pins broken out for a certain layer because of the zigzag array outline. However the array outline still shrinks layer by layer and the escape routing efficiency is greatly reduced for the last layers.

Figure II. 7 Parallel triangular escape routing.

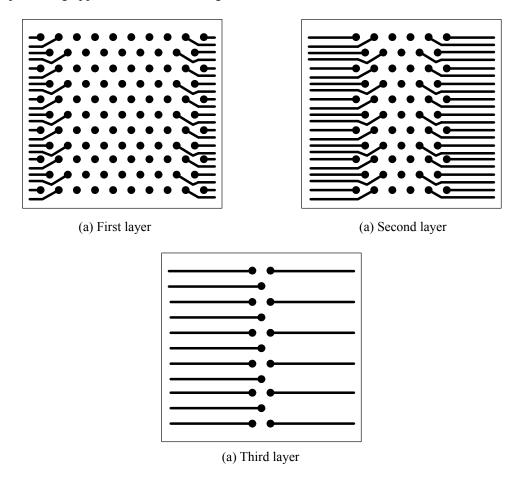

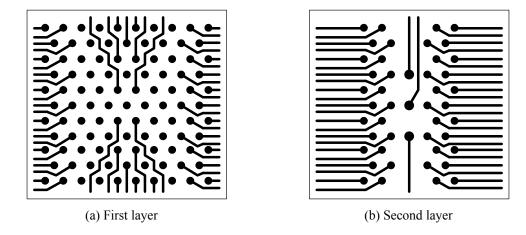

#### 2.3.3 Central Triangular Escape Sequence

This strategy also divides I/Os in the array into four parts by two diagonals and I/Os are escaped to four directions respectively. Different from the parallel triangular escape sequence, this strategy breaks out I/Os in each part from the center of the outside row and a single triangular indented outline is expanded layer by layer, as shown in Figure II. 8. I/Os within the bottom center triangle are escaped in the first routing layer. The size of the triangle, k, is defined in (II.3). In the second and following routing layers, one triangular outline is formed in each part and becomes larger layer by layer. We assume the routing capacity of the vertical (horizontal) channel is m and the routing capacity of the diagonal channel is q. As long as the condition (II.5) is satisfied, q+1 rows (columns) can be escaped in one routing layer following the triangular outline. Thus, the total number of routing layers for breaking out an array with size n is

$$Num(layers)_{ct} = 1 + \left\lceil \frac{n - k - 1}{2(q + 1)} \right\rceil$$

(II.7)

Using this method, we achieve continuously increasing array outline, i.e. the capacity of the array outline is increased continuously layer by layer. However the capacity for the first several layers is smaller than previous two strategies.

Figure II. 8 Central triangular escape routing.

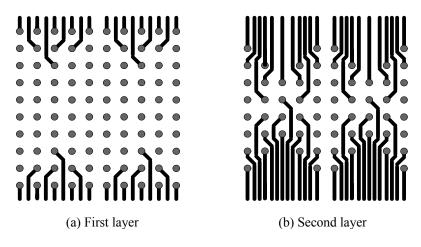

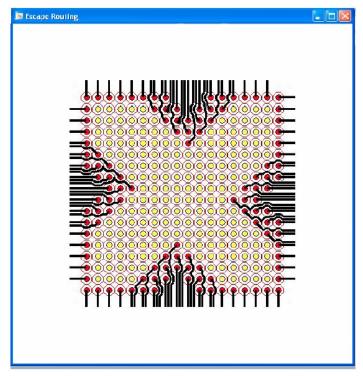

#### 2.3.4 Two-sided Escape Sequence

Same as previous two strategies, this approach divides I/Os in the array into four parts by two diagonals and I/Os are escaped to four directions respectively. It breaks out I/Os from the inside as well as from the outside, as shown in Figure II. 9. Both the outside and inside outline maintains the zigzag shape and the array outline shrinks very slowly.

This two-sided escape method applies the zigzag outline used in the parallel triangular escape method and overcomes its shortcoming to improve the escape routing efficiency. In the parallel triangular escape method, I/Os are divided into small groups in every part of the array and are escaped to form a triangular outline in each group. But the heights of those groups in each part, i.e. the number of rows, are different. The group in the middle has larger height which constrains the number of necessary routing layers, however the group in the corner has smaller height which can be broken out easily. Therefore, we can escape I/Os inside the array through the routing channels in the corner to decrease the largest height and fully utilize the routing channels in the corner. We slow down the shrinking rate of the array outline in this way. Then the total number of routing layers for breaking out an array with size n is

$$Num(layers)_{ts} \le 1 + \left\lceil \frac{n-k-1}{2(q+1)} \right\rceil$$

(II.8)

The number of I/Os broken out in each routing layer is very even. So this strategy can efficiently decrease the number of layers for escape routing and it has more advantage for large size array.

Figure II. 9 Two-sided escape routing.

## 2.3.5 Four Escape Sequence Strategies Comparison

According to our analysis and guidelines for escape routing proposed in section 2.3, the advantages and disadvantages of those four escape sequence strategies are obvious. Figure II. 10 shows the transformation of the array outline in the escaping process for the four strategies we have discussed. Because the array outline of the traditional row-by-row method shrinks quickly to the center layer by layer, the escape routing for the latter layers becomes very inefficiently. The parallel triangular approach improves the escape efficiency by maintaining zigzag array outline. The escape routing of central triangular approach becomes more and more efficient layer by layer while the number of I/Os escaped in the first several layers is too small. The two-sided escape sequence controls the array outline perfectly.

Figure II. 10 The transformation of array outline.

# 2.4 Automatic Escape Routing Algorithm

We need an automatic escape routing program to facilitate investigating different escape sequence strategies. We design and implement an escape routing algorithm because the escape routing is usually done manually in industry. This automatic escape routing program helps us to compare different escape strategies for real experiments and verify our analysis. The practical escape routing results will also benefit the signal integrity analysis and further researches.

## **2.4.1** The Characteristics of Escape Routing

The escape routing has several characteristics different from the routing in ICs

(Integrated Chip) and the routing on board.

- (i) The escape routing wires connect I/Os in the array with the destinations on the four boundaries surrounding the array and each wire has only two terminals.

- (ii) The wire breaking out one I/O is routed in only one layer.

- (ii) The escape routing wires are composed of horizontal, vertical and diagonal segments with 0°, 90°, 45° and 135° respectively.

- (iv) I/Os that haven't been escaped are obstacles for current routing wires.

I/Os are routed layer by layer according to the given escape sequence and for each layer the routing is some kind of area routing. To design the automatic escape routing algorithm, we utilize the idea of river routing algorithm [22] and devise special operations aiming at those characteristics of escape routing.

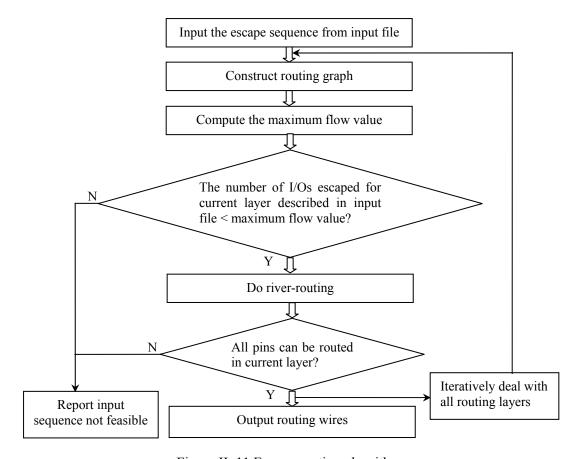

#### 2.4.2 Automatic Escape Routing Algorithm

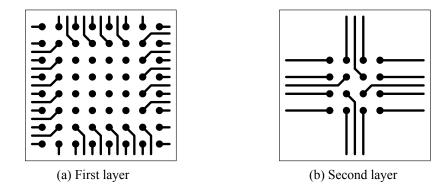

The main differences between escape routing and river routing are the location of net terminals, internal blockages and the direction of routing segments. The two terminals of each escape routing wire are located at some point in the array and some point on the array boundary respectively, while the two terminals of signal net in river routing are both located on the boundary of routing region. In escape routing problem, I/Os that haven't been escaped are obstacles, while the routing region for river routing problem cannot have internal blockage. The routing segments for escape routing can be horizontal, vertical and diagonal, while river routing can only support horizontal and vertical routing segments. Considering the characteristics of escape routing, we modify the river routing operations and devise our automatic escape routing algorithm. Figure II. 11 shows the main flow of the algorithm.

The algorithm proceeds layer by layer for a given escape sequence. We construct routing graph and calculate the maximum flow value using the same algorithm as escape

bottleneck analysis described in section 3 for every layer. If the input sequence is reasonable compared with the maximum flow value, I/Os are routed for current layer. For each routing layer, the algorithm proceeds I/O by I/O anticlockwise starting from left-bottom corner. The set of routing segments for each I/O is generated in three steps similar as river routing. First a continuous list of segments (S1) with current wire width by licking along the edge of previous wire just routed with the minimum wire spacing is generated. Then, current I/O is connected to S1 with shortest path using horizontal, vertical and diagonal segments; the crossing point of S1 and the array boundary is the other terminal for the wire; segments list (S2) including two terminals is generated in this way. Finally, if S2 crosses some obstacle, the wire will surround the obstacle clockwise at the crossing points. In order to exploit the diagonal routing segments, we use octagon to approximate the shape of I/Os. As output, all the routing wires, the number of routing layers and the number of I/Os escaped on each layer are reported.

Figure II. 11 Escape routing algorithm.

We implement this automatic escape routing algorithm and use it to do routing for real experiments using those four escape sequence strategies described in section 2.4.

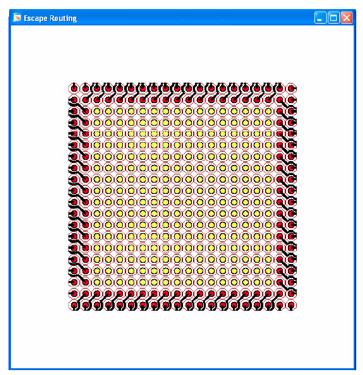

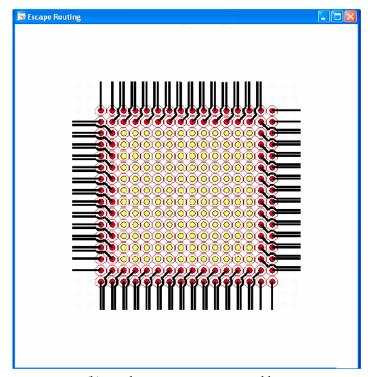

# 2.5 Experimental Results

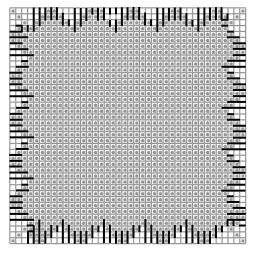

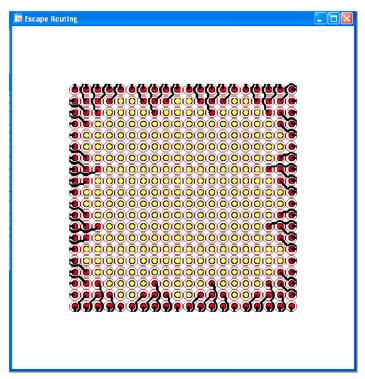

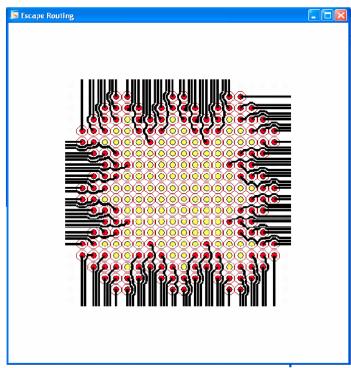

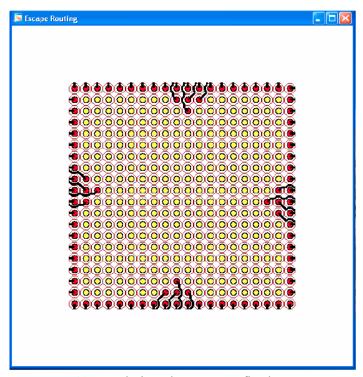

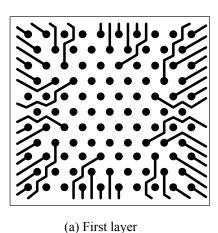

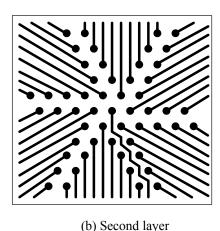

We break out a regular I/Os area array with size n=20 and n=40 using four different escape sequence strategies discussed in section 2.4. The pad pitch, pad diameter, line width, line spacing and spacing between pad and wire are 150μm, 75μm, 20μm, 20μm and 20μm respectively. Table II. 1 and Table II. 2 list the number of I/Os escaped on every layer for those four escape strategies for 40x40 and 20x20 array respectively. Figure II. 12 shows 20x20 area array escape routing results of the first two layers for four escape strategies.

The experimental results demonstrate our analysis and show that the two new escape routing strategies we proposed are very efficient, especially the two-sided escape sequence approach reduces the number of escape routing layers dramatically. We can clearly observe the advantages and disadvantages of those strategies from the results for 40x40 area array. For the traditional row-by-row method, the number of breakout I/Os decreases rapidly layer by layer. It requires 10 total layers. For the parallel triangular method, the number of breakout pins on one-layer peaks at the second layer and drops slowly afterwards. This method reduces the required number of layers from 10 to 7. For the central triangular method, the number of breakout I/Os starts from small value but keeps on increasing and thus reduces the number of layers to 6. The two-sided method is the most efficient one, which achieves the result in only 5 routing layers.

Table II. 1 The number of breakout I/Os escaped on each layer for four strategies. 20x20 area array

| Layer | Row by row | Parallel triangular | Central triangular | Two sided |

|-------|------------|---------------------|--------------------|-----------|

| 1     | 144        | 132                 | 92                 | 140       |

| 2     | 112        | 144                 | 116                | 160       |

| 3     | 80         | 96                  | 140                | 100       |

| 4     | 48         | 28                  | 52                 | -         |

| 5     | 16         | -                   | -                  | -         |

Table II. 2 The number of breakout I/Os escaped on each layer for four strategies. 40x40 area array

| Layer | Row by row | Parallel triangular | Central triangular | Two sided |

|-------|------------|---------------------|--------------------|-----------|

| 1     | 304        | 276                 | 172                | 312       |

| 2     | 272        | 340                 | 196                | 328       |

| 3     | 240        | 292                 | 220                | 308       |

| 4     | 208        | 240                 | 244                | 324       |

| 5     | 176        | 164                 | 268                | 328       |

| 6     | 144        | 124                 | 292                | •         |

| 7     | 112        | 164                 | 208                | •         |

| 8     | 80         | =                   | =                  | •         |

| 9     | 48         | =                   | =                  | •         |

| 10    | 16         | -                   | -                  | -         |

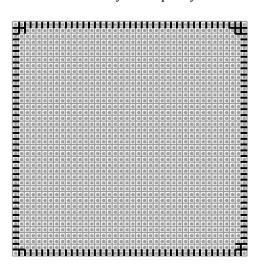

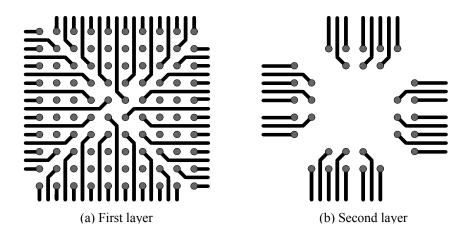

(a) row-by-row sequence, first layer

(b) row-by-row sequence, second layer

Figure II. 12 Escape routing results.

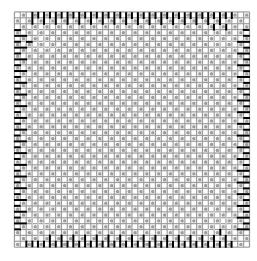

(c) parallel triangular sequence, first layer

(d) parallel triangular sequence, second layer

Figure II.12 Escape routing results. (Cont.)

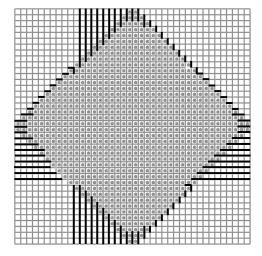

(e) central triangular sequence, first layer

(f) central triangular sequence, second layer

Figure II.12 Escape routing results. (Cont.)

(g) two-sided sequence, first layer

(h) two-sided sequence, second layer

Figure II.12 Escape routing results. (Cont.)

# 2.6 Analysis Model

The escape routing connects I/Os to the next level assembly. The signal performance is another important consideration in escape routing design. The signal integrity is a measure of the quality of the electrical signal. In high-speed electronic systems, various effects could degrade the electrical signal performance to the point where errors occur. In escape routing, many signal integrity issues should be considered, noise induced by high density wires in escape routing area, crosstalk between wires and vias, the signal skew consideration and the impedance mismatch problem. The escape routing strategy with low cost and high performance is the ultimate goal for the practical electronic systems.