# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

# **Title**

Energy-Efficient Neuromorphic Computing with CMOS-Integrated Memristive Crossbars

# **Permalink**

https://escholarship.org/uc/item/4jp0w0jc

# **Author**

Fahimi, Zahra

# **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

# Santa Barbara

Energy-Efficient Neuromorphic Computing with CMOS-Integrated Memristive Crossbars

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Zahra Fahimi

Committee in charge:

Professor Dmitri Strukov, Chair

**Professor Tim Sherwood**

Professor James Buckwalter

Professor Li-C Wang

December 2021

| Tim Sherwood     |      |  |

|------------------|------|--|

|                  |      |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

| James Buckwalter | <br> |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

| Li-C Wang        |      |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

|                  |      |  |

The dissertation of Zahra Fahimi is approved.

December 2021

Dmitri Strukov, Committee Chair

# Energy-Efficient Neuromorphic Computing with CMOS-Integrated Memristive Crossbars

Copyright © 2021

By

Zahra Fahimi

Dedicated to you.

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my advisor, Prof. Dmitri Strukov, for your patience, guidance, and support. I have benefited greatly from your wealth of knowledge. I am grateful that you took me on as a student and continued to have faith in me over the years.

Very special thanks to my colleagues especially my soulmate Dr. Mohammad Reza Mahmoodi who has supported me throughout this process and has constantly encouraged me when the tasks seemed difficult and back-breaking.

I also owe much gratitude to my parents and my brothers for their unwavering support and love.

# VITA OF ZAHRA FAHIMI Dec 2021

#### Education

Bachelor of Science in Electrical Engineering, Shahrekord University, 2011. Master of Science in Electronics, Isfahan University of Technology, 2015. Master of Science in Computer Engineering, University of California, Santa Barbara, June 2021

Doctor of Philosophy in Electronics, University of California, Santa Barbara, Dec 2021 (expected).

#### **Selected Publications**

- **Z. Fahimi**, *et al*. Mitigating Imperfections in Mixed-Signal Neuromorphic Circuits, *https://arxiv.org/abs/2107.04236*, (2021).

- **Z. Fahimi**, et al. The Impact of Device Uniformity on Functionality of Analog Passively-Integrated Memristive Circuits, *IEEE Transactions on Circuits and Systems I*, (2021).

- **Z. Fahimi**, *et al*. Combinatorial Optimization by Weight Annealing in Memristive Hopfield Networks, *Scientific Reports*, (2021).

- **Z. Fahimi**, et al. Mixed-signal computing with non-volatile memories, SRC Technical Conference (SRCTechCon'18), (2018).

- M. R. Mahmoodi, **Z. Fahimi**, *et al.* A Strong Physically Unclonable Function with >280 CRPs and <1.4% BER Using Passive ReRAM Technology, *IEEE Solid-State Circuits Letters*, (2020).

- M. R. Mahmoodi, H. Nili, **Z. Fahimi**, *et al*. Ultra-Low Power Physical Unclonable Function with Nonlinear Fixed-Resistance Crossbar Circuits, *Electron Devices Meeting (IEDM'19)*, (2019).

- M. R. Mahmoodi, H. Kim, **Z. Fahimi**, *et al*. An Analog Neuro-Optimizer with Adaptable Annealing Based on 64×64 0T1R Crossbar Circuit, *Electron Devices Meeting (IEDM'19)*, (2019).

#### **ABSTRACT**

Energy-Efficient Neuromorphic Computing with CMOS-Integrated Memristive Crossbars

by

#### Zahra Fahimi

The von Neumann architecture has been broadly adopted in modern computing systems in which the central processor unit (CPU) is separated from the memory unit. During data processing, it is necessary to transfer data between the memory and CPU. For data-intensive applications such as deep neural networks, as the size of data increases, data movement between memory and CPU becomes a significant bottleneck for high throughput and energy-efficient implementation. In-memory computing is a paradigm that tackles this challenge by allowing computation within the memory, i.e., where data are stored. Hence, in-memory computing is a promising solution for implementing energy-efficient neuromorphic systems since it minimizes data transportation between memory and the processing units. The major component in developing neuromorphic circuits is a nanoscale memory device, which is responsible for weight storage and analog computation. Resistive Random-Access Memory (RRAM) is one of the most promising memory candidates due to its long-term retention, analog storage, low-power operation, and compact nanoscale footprint.

The first part of this thesis explores the nonidealities of RRAM technology, such as temperature dependency, stuck-at-fault, and tunning error, and their impact on the accuracy of neuromorphic hardware implementation. We show that these imperfections may significantly degrade the inference accuracy of neuromorphic circuits. To mitigate them, we

have proposed a holistic approach based on hardware-aware training in which modifications are done in tunning, circuit, and training phase (ex-situ) of hardware development. The proposed method significantly decreases the accuracy drop across the 25-100 °C temperature range, allows  $2.5\times$  to  $9\times$  improvement in energy consumption of the memory arrays during inference, and improves the defect tolerance by  $>100\times$ .

In the second part of this thesis, we also study the impact of device uniformity in passive memristive circuits and the tradeoffs between computing accuracy, crossbar size, switching threshold variations, and target precision. Nonidealities are investigated in two representative deep neural networks, and several solutions, including hardware-aware training, improved tuning algorithm, and switching threshold modification, are proposed to enhance the performance. These techniques allow us to implement advanced deep neural networks (DNNs) with almost no accuracy drop, using state-of-the-art analog 0T1R technology.

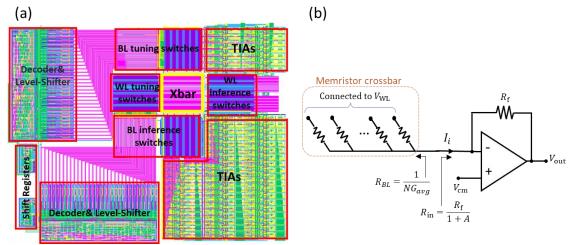

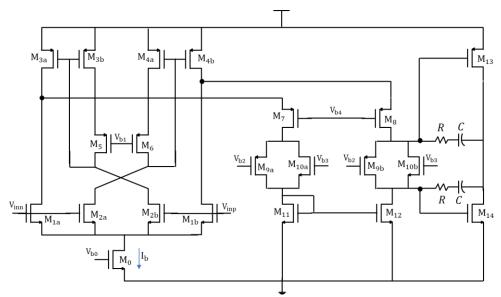

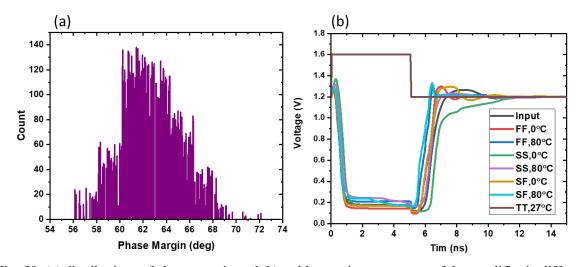

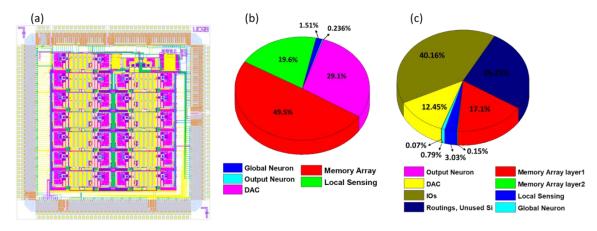

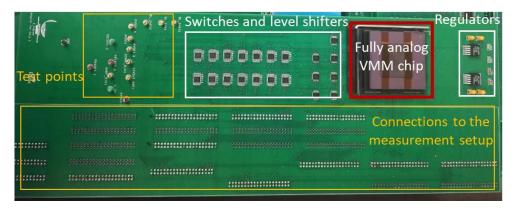

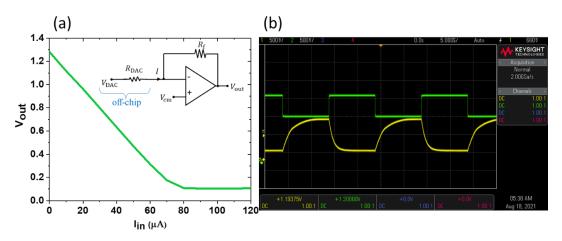

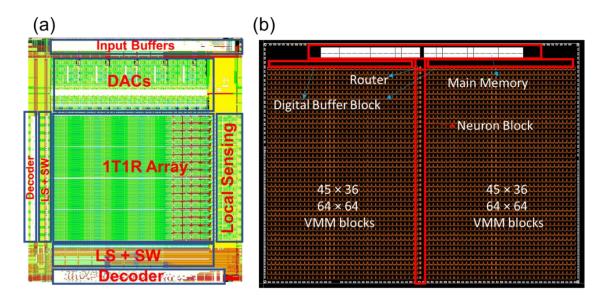

In the last part, we focus on integrating passive and active RRAM with CMOS circuits for implementing efficient demos for various applications such as neural networks. First, focusing on passive technology, we show the building block circuit that facilitates the forming, programing, reading, inference, and monitoring of RRAM circuits. We discuss several neuromorphic networks and prototype demos with integrated analog passive RRAM and CMOS. The designs are fabricated in two wafer-scale tapeout runs in 180 nm CMOS technology, and preliminary encouraging experimental results are obtained. Second, we demonstrate a massive DNN accelerator fabricated in a standard 65 nm CMOS process with integrated active analog RRAM devices. The main focus is on novelties in the design of the VMM and tuning circuits, which reduced the impact of IR drop, improved the area efficiency, and allowed massive parallel programming features in this chip.

# TABLE OF CONTENTS

| 1. | . Introduction 1                                                             |                                             |     |  |  |  |  |  |  |

|----|------------------------------------------------------------------------------|---------------------------------------------|-----|--|--|--|--|--|--|

|    | 1.1.                                                                         | Motivation                                  | 1   |  |  |  |  |  |  |

|    | 1.2.                                                                         | Background and Significance                 | 4   |  |  |  |  |  |  |

| 2. | . Mitigating Imperfections in Mixed-Signal Neuromorphic Circuits             |                                             |     |  |  |  |  |  |  |

|    | 2.1.                                                                         | Neuromorphic Benchmarks                     | 18  |  |  |  |  |  |  |

|    | 2.2.                                                                         | Device Characterization                     | 20  |  |  |  |  |  |  |

|    | 2.3.                                                                         | Simulation Framework and Device Modeling    | 29  |  |  |  |  |  |  |

|    | 2.4.                                                                         | Simulation Results                          | 32  |  |  |  |  |  |  |

|    | 2.5.                                                                         | Discussion                                  | 43  |  |  |  |  |  |  |

| 3. | 3. The Impact of Device Uniformity on Functionality of Memristive Circuits 4 |                                             |     |  |  |  |  |  |  |

|    | 3.1.                                                                         | Passive Memristive Crossbars                | 49  |  |  |  |  |  |  |

|    | 3.2.                                                                         | Simulation Framework                        | 53  |  |  |  |  |  |  |

|    | 3.3.                                                                         | Computing Precision in Nonuniform Crossbars | 54  |  |  |  |  |  |  |

|    | 3.4.                                                                         | Neuromorphic Network Simulation results     | 61  |  |  |  |  |  |  |

|    | 3.5.                                                                         | Improving the Accuracy                      | 63  |  |  |  |  |  |  |

|    | 3.6.                                                                         | Discussion                                  | 68  |  |  |  |  |  |  |

| 4. | CMOS in                                                                      | ntegrated Memristive Circuits               | 71  |  |  |  |  |  |  |

|    | 4.1.                                                                         | Wafer-Scale 0T1R Integration                | 72  |  |  |  |  |  |  |

|    | 4.2.                                                                         | DNN Accelerator with 1T1R Memories          | 101 |  |  |  |  |  |  |

| 5. | 5. Summary and Conclusion                                                    |                                             |     |  |  |  |  |  |  |

|    | Referenc                                                                     | es                                          | 106 |  |  |  |  |  |  |

# 1. Introduction

# 1.1. Motivation

Deep neural networks (DNNs) are currently the foundation for modern artificial intelligence (AI) applications [1] and have been very successful in large-scale recognition and classification tasks [1-5]. This momentum stems from two main reasons: First, the exponential increase in the computational power exhibited by graphics processing units (GPU), which harnesses extreme parallelism by using many cores, each with a dedicated or shared high-throughput connection with memory. Second, the availability of a vast amount of labeled data has abled DNNs to extract high-level features from unprocessed data. Hence, the rise of powerful GPUs and massive labeled datasets paved the way toward training DNNs in a reasonable time with high accuracies. However, pure software DNNs executed in supercomputers with thousands of CPU/GPUs suffer from high energy consumption [6] because during the execution of various computational tasks, large amounts of data need to be traveled back and forth between the processing and memory unit, and this causes high costs in latency and energy.

To overcome the need for transferring data frequently between the memory and the processing unit, and improve the energy efficiency significantly [7], novel non-von Neumann computing models are developed that, e.g., rely on the idea of in-memory, in which calculations are carried out where the data are stored [8]. Therefore, it yields to suppress the energy- and time-consuming of memory-processor communications extremely.

Among different in-memory computing schemes, designs based on computational memory devices [9-12] are one of the most effective implementations as efficient in-memory

computing generally requires fast, low-power, high-density, scalable memory devices. Analog-grade non-volatile memories (NVMs), such as those based on floating-gate transistor [13-15], phase-change [16-18], ferroelectric [19, 20], magnetic [21], solid-state electrolyte [22-24], organic [25, 26], and metal-oxide [27-30] materials are enabling components for mixed-signal circuits implementing Vector-by Matrix Multiplication (VMM), which is the most common operation in any artificial neural network. Such circuits allow for physical level in-memory computations in the analog domain using the fundamental Ohm and Kirchhoff laws, thus enabling dramatically higher energy and area efficiency in comparison with digital solutions.

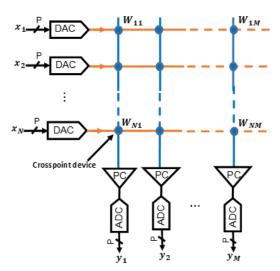

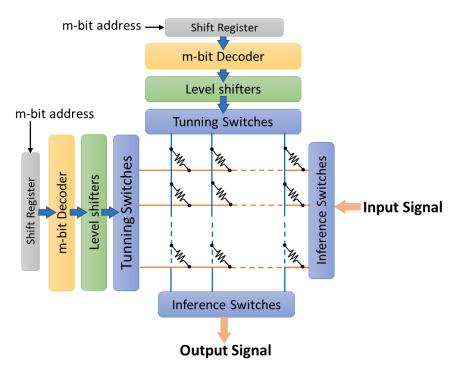

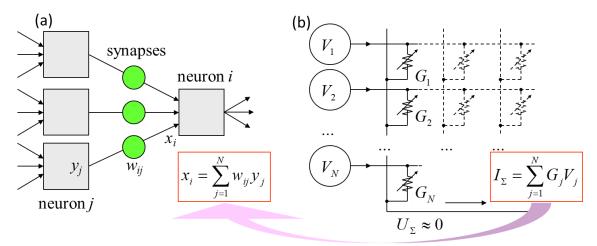

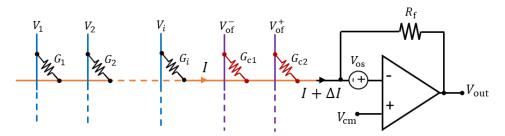

The general architecture of mixed-signal VMMs based on NVMs depicted in Fig. 1. Here, vector-by-matrix multiplication is defined as y = Wx, where  $x \in \mathbb{R}^N$  is the input vector,  $y \in \mathbb{R}^M$  is the output vector, and W is the weight matrix. N and M are the number of inputs and outputs, respectively. The input vector is presented to the digital-to-analog converters (DACs), which convert the digital input to analog signals. The predetermined weight vector is encoded to the conductance of the NVM cells. NVM cell at each crosspoint generates current proportional to the amplitude of the input signal times its conductance. As a result, the multiplication and summation operations within a memory array are performed in parallel using Ohm's law. The current in all columns is summed up based on Kirchhoff's law and sensed by the peripheral circuits (PC), which is then followed by analog-to-digital converters (ADCs).

Fig. 1: The general architecture of a mixed-signal VMM with nonvolatile memory at each crosspoint.

The most important memory device characteristics in the context of analog VMM circuits are cell size and scalability. The main advantages of using passively integrated metal-oxide memristors [28], which are also referred to as RRAMs, are their superior density and lower fabrication cost [31]. The high scalability of RRAMs makes it possible to implement very dense resistive memory arrays. Such architectures using memristive devices are of high interest for their possible applications in in-memory computing based on nonvolatile memory design [32-34], digital and analog programmable systems [35, 36], and neuromorphic computing structures [37,38].

Developing circuits based on RRAM devices faces some challenges. The first concern is related to non-idealities of the devices such as temperature dependency, tuning error, device-to-device variations, and defects, which lead to considerably degrading the performance of neural network-based RRAMs. The second challenge is the integration of memristive crossbars with CMOS circuits, which implement nonfrequent peripheral functions. The main goal of this thesis is to address these two challenges. In particular, Chapter 2 explore different types of device imperfections and their impacts on the performance of neural networks based

on RRAM crossbars. Then, we analyze each non-ideality very precisely and then introduce a holistic approach to mitigate these imperfections during training of the networks without any extra hardware. In Chapter 3, we study the impact of device uniformity on the functionality of memristor circuits, where they are used to implement either a neural network or an optimization platform.

Finally, in Chapter 4, we discuss our progress toward developing CMOS-integrated memristive crossbars and neuromorphic circuits and systems based on passive and active ReRAM circuits.

# 1.2. Background and Significance

# 1.2.1. CMOS Integrated RRAM Crossbars

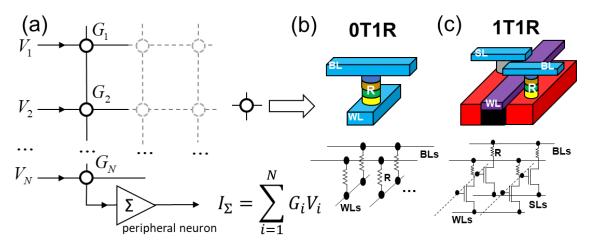

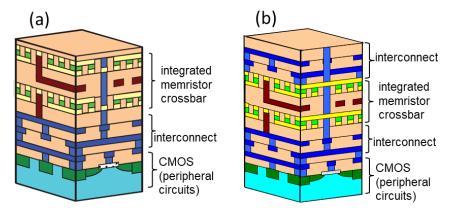

Memristive devices are categorized into two different types: 1) zero-transistor-one-memristor (0T1R), which is mainly called passive memristors, and 2) one-transistor-one-memristor (1T1R) memristors, which are commonly referred to as active memristors. In comparison with passive crossbar arrays, the 1T1R structure improves the network performance in two aspects: First, proper current compliance determined by the transistor allows a more controllable conductance update compared with that in 0T1R arrays. Second, the gate transistor can prevent disturbance to the states of unselected devices during programming. The 1T1R structure can also eliminate the sneak path problem of the passive crossbar, although the sneak path is not relevant in the context of neuromorphic computing inference. On the other side, arrays based on passive memristors are more compact and scalable. Fig. 2b and 2c indicate the structure of a passive and active memristor device used in a memristive array (Fig. 2a).

Fig. 2: (a) A memory array based on memristive devices. A structure of (b) 0T1R and (c) 1T1R memristor device

The specific focus of this section is on the state-of-the-art nonvolatile (filamentary) analog-grade 0T1R metal-oxide devices, while only a few representative works are listed for metal-oxide 1T1R and solid-state-electrolyte 0T1R circuits.

In 2015, for the first time, a  $12\times12$  transistor-free memristive crossbar consisting of bilayer metal-oxide memristors was used to experimentally demonstrate an artificial neural network based on memristive devices [39, 40]. A  $10\times6$ - and  $10\times8$ - neuromorphic pattern classifiers were implemented and trained in-situ using the Manhattan-Rule algorithm. The retention and endurance of the devices were measured > 140 hrs and > 200 K, respectively.

One year later, in 2016, the first 3-D monolithic stack of two passive  $10 \times 10$  crossbars for analog computing applications was reported in Ref. [41]. Furthermore, the crosspoint memristors are optimized for analog computing applications allowing successful forming and switching off all devices in the demonstrated crossbar circuit and, most importantly, precise tuning of the devices' conductance values within the dynamic range of operation. Using a low, less than 175 °C, temperature budget during the fabrication process and performing a

planarization step before the deposition of the second crossbar layer improved yield (~100%) and uniformity of the crosspoint devices significantly.

In 2017, several milestone papers were published. The first one was on experimental implementation of sparse coding algorithms based on a 32 × 32 crossbar array of analog 0T1R devices [42]. In this experiment, a 25 × 20 sub-array of the memristor array was utilized to validate the algorithm. The retention of the devices is reported in the order of minutes. The second work [43] was based on the demonstration of using memristor arrays to perform principal component analysis (PCA), which is a feature extraction technique commonly used in unsupervised learning. Ref. [44] introduced an implementation of a grey-scale face classification based on a 1024-cell array of 1T1R memristive devices with parallel online training.

Some breakthrough works using both 0T1R and 1T1R memristive arrays were introduced in 2018. An  $11 \times 3$  array of passive memristors was fabricated and used to implement the simulated annealing technique for solving a spin glass problem [45]. In Ref. [46], a  $16 \times 3$  fabricated passive memristor crossbar was used to demonstrate neural networks for K-means clustering analysis. The first demonstration of a multilayer perceptron (MLP) using memristive crossbar arrays was proposed in Ref. [47]. In this work, two passive  $20 \times 20$  metaloxide memristive crossbar arrays are used to implement an MLP network, which includes 16 inputs, 10 hidden-layer neurons, and 4 outputs. More than 20 hrs of high-temperature retention and 100 k endurance are reported for the devices used in the array. Ref. [48, 49] partitioned a single  $128 \times 64$  1T1R array built from high retention devices (> 10 years) to construct a 3-layer perceptron with 64 input neurons, 54 hidden neurons, and 10 output neurons trained on the MNIST dataset of handwritten digits.

In 2019, a reservoir computing hardware system based on a  $32 \times 32$  WO<sub>x</sub> memristor was reported [50] that can efficiently process temporal data. A passive memristor crossbar array was directly integrated with all the necessary CMOS circuitries on Ref. [51]. The size of the array is reported as  $108 \times 54$ , but a  $26 \times 10$  sub-array of it was used to demonstrate three models—a perceptron network, a sparse coding algorithm, and a bilayer PCA system. Retention of the devices is measured in the order of minutes. A five-layer mCNN for MNIST digit image recognition was also designed using 2,048 1T1R devices [52] in 2020.

In 2021, the largest fully functional passive crossbar was introduced [32]. A  $64\times64$  passive crossbar circuit with ~ 99% functional nonvolatile metal-oxide memristors was demonstrated to implement a vector-by-matrix multiplier used for the MNIST image classification.

Table. I show a summary of previous works implemented by memristor devices. The common feature between all discussed works is that the main operations can be performed efficiently with memristor crossbar arrays. These implementations have mostly relied on external printed-circuit boards (PCB) to provide the required parameter analyzers and control circuitries such as ADCs, DACs, peripheral/sensing circuits, tunning switching, etc., to generate and collect signals. So, the functionality of the systems can be limited to accessing these discrete circuits. To overcome this issue, implementing a system such that memristive crossbars are fully integrated with all necessary CMOS circuities is required. Therefore, integrating all the necessary circuits and memristor crossbar on one wafer allows us to scale the large computing systems and increase the computation speed. In Chapter 4, we introduce several fully integrated CMOS-RRAM chips designed for different neuromorphic applications.

**Table I**: A summary of previous work on implementing memristive crossbar arrays with 0T1R and 1T1R devices (some data are from [32])

| Cell t | ype                            | Ref.     | Crossbar<br>size | Yield<br>(%) | Demo Size  | $\begin{array}{c} \text{Cell} \\ \text{size} \\ \left(\mu m^2\right) \end{array}$ | Forming current (µA)/ Voltage(V) | Endurance<br>(cycles) | Tuning<br>Precision | Set<br>switching<br>statistics<br>μ/σ(V) | G <sub>max</sub> /G <sub>min</sub> (μS) | Retention<br>(@°C) | Type of integration /<br>patterning technique /<br>Substantial CMOS foundry<br>integration challenges |

|--------|--------------------------------|----------|------------------|--------------|------------|-----------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------|------------------------------------------|-----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|

|        | WO <sub>x</sub>                | [45]     | 11×3             | -            | 11×3       | -                                                                                 | 1000/~1.8                        | -                     | -                   | 0.85/0.05                                | -                                       | -                  | SA / lift-off / none                                                                                  |

|        |                                | [42, 50] | 32×32            | -            | 25×20      | ~9                                                                                | >170 / -                         | -                     | ~ 35%               | 1.7/-                                    | 3/1                                     | ~mins @RT          | SA / lift-off / none                                                                                  |

|        |                                | [51]     | 108×54           | -            | 26×10      | > 256                                                                             | -                                | -                     | -                   | -                                        | 2.4/1                                   | ~mins @RT          | FI-BEOL / lift-off / none                                                                             |

|        | Ta <sub>2</sub> O <sub>x</sub> | [43]     | 18×2             | ~100         | 18×2       | -                                                                                 | 250 / ~1.1                       | -                     | -                   | -                                        | 1500/850                                | -                  | SA / lift-off / none                                                                                  |

| OT1R   |                                | [46]     | 16×3             | 78           | 4×3        | -                                                                                 | 1000 / ~2                        | > 100k                | -                   | 1.25/0.1                                 | 1800/1300                               | -                  | SA / lift-off / none                                                                                  |

|        | TiO <sub>2-x</sub>             | [39, 40] | 12×12            | >50          | 10×6       | 0.16                                                                              | 200 / 1.9                        | >200k                 | -                   | 0.9/0.17                                 | 200/6                                   | >140h@76           | SA / lift-off / none                                                                                  |

|        |                                | [47]     | 20×20            | >95          | 17×20+8×11 | 0.25                                                                              | 220 /1.5                         | >100k                 | < 8%                | 1.0/0.18                                 | 200/6                                   | >20h@120           | SA / lift-off / none                                                                                  |

|        |                                | [41]     | 2×10×10          | ~100         | 2×10×10    | 0.49/2                                                                            | 100/2.5                          | -                     | -                   | 1.1/0.15                                 | 100/0.1                                 | >25h@100           | SA/ion beam milling/ none                                                                             |

|        |                                | [32]     | 64×64            | ~99          | 64×64      | 0.5625                                                                            | 100 / 3.2                        | >100k                 | < 5%                | 1.2/0.13                                 | 100/6                                   | >20h@100           | SA /RIE/ none                                                                                         |

|        | HfO <sub>2-x</sub>             | [48, 49] | 128×64           | >99          | 128×64     | ~2500                                                                             | -                                | -                     | <3.1%               | 2/-                                      | 900/100                                 | 10yr @RT           | BEOL/lift-off / none                                                                                  |

| 1T1R   |                                | [44]     | 128×8            | -            | 960        | -                                                                                 | >150 / >3                        | -                     | < 35%               | -                                        | 40/5                                    | -                  | BEOL/ lift-off / none                                                                                 |

|        |                                | [52]     | 128×16           | >99          | 128×16     | > 5                                                                               | -                                | -                     | 3.3 %               | -                                        | 20/2                                    | ~ days @RT         | BEOL/lift-off/ none                                                                                   |

# 1.2.2. Addressing non-idealities in neuromorphic circuits

The advancement of emerging technologies like RRAMs, which enable storing analog information and implement neural computation efficiently, has caused huge progress in the neuromorphic computing area. However, various device- and system-level non-idealities such as temperature dependency, defects, tuning error, etc., inherently rise in such analog circuits. These concerning factors may considerably degrade the performance/inference-accuracy of neural networks implemented based on nonvolatile memory devices.

The dependency of the devices on temperature has a very significant impact on neuromorphic circuits and systems. The weights of the network change noticeably with temperature variation followed by modifying the pre-activation signals of the neurons that results in reducing the inference accuracy [53].

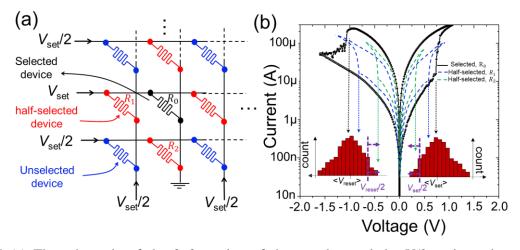

Another non-ideality in memristive devices is device-to-device variations. The switching variation between devices implies that various amounts of applied voltages will be required to tune different devices, which would lead to the half-select disturbance problem, i.e., programming a memristor device disturbs the state of other devices located in the same column or rows if they have a switching threshold less than the threshold of the programmed device.

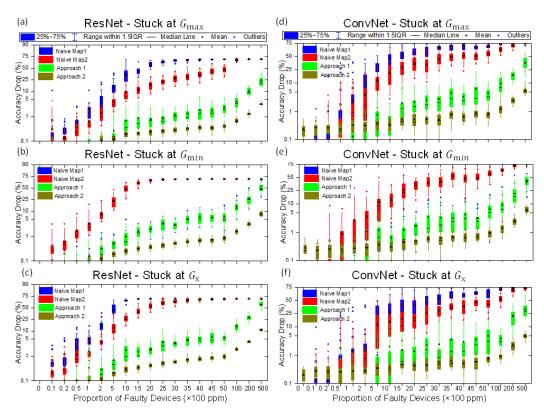

Several promising studies investigate the effect of device imperfections on network performance and propose reliable techniques to improve the accuracy. The solutions could involve hardware modifications or software training approaches. Existing hardware-based solutions cause enormous overhead and power consumption while software-based methods are more efficient.

A memristor crossbar array modeled in Ref. [55], incorporating the line resistance and device nonlinearities. Simulation results show the line resistance causes voltage and current degradation, and it may affect array operation when arrays and devices are highly scaled. Therefore, line resistance should not be ignored for relatively large crossbars. In Ref. [56], the influences of some hardware limitations such as IR-drop, device variation, and programing error are analyzed. A variation-aware off-device training scheme called "Vortex" is developed to tolerate device imperfections and design constraints. The algorithm is tested on a two-layer neural network implemented by memristor crossbars for MNIST classification. A general conversion algorithm was developed and experimentally tested in Ref. [57] to map arbitrary matrix values to memristor conductances to compensate the accuracy drop due to IR drop and nonlinearity characteristics of the devices.

In 2017, a method to eliminate the parasitic resistance across memristor arrays was presented in Ref. [58]. This technique is based on adding extra resistors to ensure that every single device sees the same parasitic resistance. Due to the limitation of the immature fabrication technology, many types of defects may exist in RRAM-based computing systems, such as hard faults and soft faults. Soft faults can be easily calibrated because the resistance of the devices is adjustable. Hard faults like Stuck at-Faults (SAFs) which faulty devices get stuck at high-resistance state (HRS) or low-resistance state (LRS) are popular in memristive

arrays. In order to mitigate this issue, a mapping algorithm with inner fault-tolerance is proposed to make multiple faulty RRAM columns eliminate the impact of SAFs on each other [59]. Another method to eradicate the effect of fault-tolerant and programing errors was proposed in Ref. [60]. The method is based on an on-chip training scheme that selects a small portion of the model parameters randomly and then, maps them to on-chip memory. After the model is mapped to the hardware, it adapts the parameters. The algorithm was demonstrated by improving the accuracy of CNNs networks for MNIST and CIFAR-10.

A defect releasing methodology to improve inference accuracy was demonstrated on an MLP network implemented by memristor arrays [61]. In this method, the weights are classified into significant and insignificant ones based on their impact on the performance. Then, a retraining algorithm is applied to compensate the device failure by re-tuning the trainable weights. A remapping algorithm that utilizes a redundancy scheme can further improve the computation accuracy, especially when a large number of defects occur in the weights.

RTN and thermal noise are critical issues in nanoscale semiconductor devices. The impact of RTN amplitude and its occurrence rate in both filamentary and non-filamentary RRAM devices are analyzed in Ref. [62]. The effect of RTN is evaluated on the pattern recognition accuracy of an MLP implemented by memristive crossbars. The investigations show that the non-filamentary RRAM has a tighter RTN amplitude distribution and a much lower occurrence rate than the filamentary devices. So, non-filamentary devices lead to less RTN impact on inference accuracy. Ref [63] proposed a method called Committee Machine (CM) employing ensemble averaging (EA) [64] to increase inference accuracy in the presence of RTN, and faulty devices, without increasing the number of memristors devices used in the

network. The network is a fully connected network, including 25 hidden layers which was tested using experimental data to extract the effect of device non-idealities. Ref. [34] used bootstrapping and tuning optimization techniques to improve the computation precision of analog VMM circuits affected by device nonlinearity, variations, and line resistance.

So far, all the studied techniques are focused on increasing the accuracy of networks based on RRAM devices by eliminating their imperfections. However, Ref. [36] developed a noise model for a mixed-signal neural network hardware accelerator based on embedded NOR flash memory technology. Using a hardware-aware training method and combining the model distortions during off-chip training make the network more robust to noise.

For the first time, we report a comprehensive characterization of critical imperfections in two analog-grade memories, passive memristors and redesigned eFlash memories [35]. Imperfections are major hurdles in the path of further progress of these technologies. Hence, a practically viable approach is developed to deal with these non-idealities and release the full potential of nonvolatile memories in neuromorphic systems. An extensive characterization of imperfections in mainstream analog-grade synaptic devices is performed, and a holistic hardware-aware ex-situ approach is developed to reduce their negative impact on the performance of DNNs. Table II summarizes the current and previous works focused on the impact of RRAM and eFlash imperfections in mixed-signal neuromorphic circuits and vector-by-matrix multipliers.

**Table. II**: A Summary of previous works focused on the effect of device imperfections in mixed-signal neuromorphic circuits

| Ref  | Device Stack  | Benchmarks          | Studied Imperfections | Method                                                                                                                                        |

|------|---------------|---------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [62] | ReRAM         | MLP                 | N                     | Impact investigation, No mitigation proposed.                                                                                                 |

| [58] | ReRAM         | VMM                 | IR                    | Adding external resistors in peripheries for average error compensation                                                                       |

| [55] | ReRAM         | VMM                 | NL, IR                | Impact investigation, No mitigation proposed.                                                                                                 |

| [63] | ReRAM         | MLP                 | N, IR                 | Averaging the outputs of multiple networks using a committee machine                                                                          |

| [59] | ReRAM         | MLP                 | FT                    | Chip-specific fault-tolerant mapping                                                                                                          |

| [65] | ReRAM         | MLP                 | NL, FT, PNL, PE       | Impact investigation, No mitigation proposed.                                                                                                 |

| [66] | PCM           | ResNet              | N, R, PE              | Partial On-chip calibration and hardware-aware training                                                                                       |

| [60] | ReRAM         | MLP and CNN         | FT, PE                | Partial On-chip calibration                                                                                                                   |

| [56] | ReRAM         | SLP                 | IR, PE                | Chip-specific calibration                                                                                                                     |

| [67] | ReRAM         | SLP                 | FT, PE                | Partial On-chip calibration                                                                                                                   |

| [66] | eFlash        | CNN                 | N                     | hardware-aware training                                                                                                                       |

| [57] | ReRAM         | VMM and MLP         | IR, NL                | Algorithmic weight conversion                                                                                                                 |

| [61] | ReRAM         | MLP                 | FT                    | Retraining and weight remapping                                                                                                               |

| [68] | ReRAM         | Lenet and ResNet    | FT                    | Impact investigation and shows Drop connect regularization helps with FT                                                                      |

| [69] | ReRAM         | MLP                 | FT, PE                | Chip-specific calibration, Temperature Compensation in neurons                                                                                |

| [65] | ReRAM         | MLP                 | IR, NL                | Bootstrapping and tuning optimization                                                                                                         |

| [35] | eFlash, ReRAM | ResNet<br>Conv. DNN | T, N, R, NL, PE, FT   | A holistic fully ex-situ approach that includes novel modifications in the training, tuning algorithm, state optimization, and circuit design |

<sup>\*</sup> T: Temperature, N: Noise, PE: programming error, in 0T1R, FT: Fault-tolerance, NL: Nonlinearity, R: Retention, IR: IR drop, PNL: programming nonlinearity.

# 2. Mitigating Imperfections in Mixed-Signal Neuromorphic Circuits

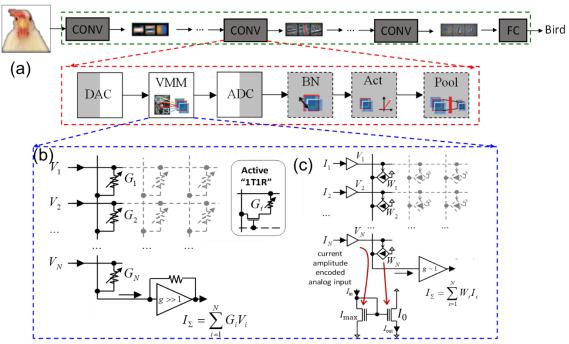

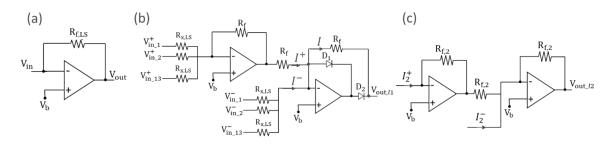

The progress in neuromorphic computing is fueled by the development of novel nonvolatile memories capable of storing analog information and implementing neural computation efficiently. The most notable candidates that excel in primary features such as long-term retention, high endurance, analog storage, low-power operation, and compact footprint are metal-oxide passive memristors [47] (Fig. 3b) and redesigned eFlash memories (Fig. 3c) [70]. Network weights are encoded into two the conductance of memristors (synapses) or the ratio of the state currents of two eFlash devices to a peripheral eFlash memory (Fig. 3b-c). The input/outputs are encoded as voltages  $(V_i)$  in memristive circuits and currents  $(I_i)$  in eFlash VMMs. Nevertheless, all synaptic devices are generally more or less prone to imperfection such as temperature dependency, yield, drift, tuning error, and static nonlinearity. While imperfections are not necessarily meant to be detrimental (see, e.g., [37]), they severely degrade the accuracy of currently popular DNNs. Indeed, imperfections are major obstacles in the path of further progress and the ultimate commercialization of these technologies. Hence, a practically viable approach should be developed to deal with these nonidealities and unleash the full potential of nonvolatile memories in neuromorphic systems.

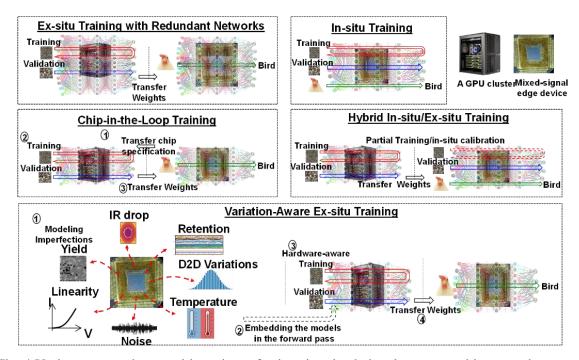

The endeavors to improve device reliability are ongoing and actively pursued. A massive number of works focus on improving synapse reliability by harnessing novel materials and stacks, e.g., reducing noise [62], enhancing uniformity [41,71], linearity [72], which is vividly the most promising approach in the long run. In the meantime, a large body of research explores circuit, system, and algorithmic techniques to mitigate these nonidealities. Such efforts are categorized into 5 approaches, as shown in Fig. 4.

Fig. 3: Mixed-signal neuromorphic circuits. (a) Major computations involved in every layer of a mixed-signal neuromorphic classifier. Highlighted in gray (white) are those typically implemented in the digital (analog) domain (BN: batch normalization, Act: activation function, Pool: an optional pooling layer, FC: fully-connected classifier). VMM implementation using (b) memristive crossbars and (c) gate-couple eFlash memory arrays.

The most predominant approach in implementing neuromorphic systems is through exsitu training, in which synaptic weights are calculated on a precursor server [36]. The synaptic weights are then transferred to numerous mixed-signal chips, which only support the inference task. A trivial approach to cope with imperfections is by adding redundancy [73]: the model and algorithm hyperparameters are selected such that the deployed model in the analog domain would tolerate a certain amount of unreliability. For example, an enormous network such as AlexNet can endure a large amount of noise that allows weight binarization [74]. In more compact models, it might be possible to lower computing precision without any impact on accuracy at the cost of redundancy. For example, the accuracy loss by changing weight precision from 4-bit to 2-bit in ResNet-18 can be compensated by doubling the model size [75]. Ref. [63] proposes to enlarge the capacity of a fully connected network through

committee machines and validate the results on the MNIST dataset. However, the major concern with this approach is the lack of evidence that this approach is scalable to complicated tasks.

Fig. 4: Various approaches to mitigate imperfections in mixed-signal neuromorphic networks.

The second approach in dealing with imperfections is through in-situ training [76,77], in which the training and inference are both performed on the mixed-signal hardware. The first drawback is the substantial areal overhead needed for the infrequent training operations, e.g., to compute and store gradients. Besides, while the chip could become resilient to some imperfections, other nonidealities associated with the dynamic behavior of devices may arise. Some works propose a hybrid approach that imposes less resource overhead, e.g., the model is initially trained ex-situ, and then an online calibration scheme modifies the weights in the run time. For example, Ref. [66] proposes an adaptive batch normalization technique that effectively compensates for the retention loss in memory cells. The drift in phase-change

memories is high (~50% conductance drift after 100 ms [78]) that an always-on compensation circuit is required.

Another solution is through chip-in-the-loop ex-situ training [57,61,79], in which specific features are measured for an individual chip (e.g., faulty synapse locations [67] or drift statistics [52]) and then applied in the training phase in the server. The adapted weights are then transferred to the chip in the deployment phase. Chip-in-the-loop ex-situ training could also be implemented by running all forward pass operations in the target device and all backward pass operations in the GPU cluster. But strategies that include device avoidance/reconfiguration/remapping or are chip-specific might present scalability challenges, despite the ability to boost the performance of an individual chip.

On the other hand, hardware-aware ex-situ training is a more scalable method in which hardware nonidealities are modeled and included in the training phase to generate a robust model. Ref. [36] uses device noise models during the training to improve the robustness of a moderate-size mixed-signal convolutional network. In Ref. [68], DropConnect regularization is introduced to enhance the accuracy drop originating from low yield without using nonideality models—at 98% yield, 17% accuracy drop on CIFAR-10 based on ResNet-18 model is reduced to 10%. Most previous works either study a particular nonideality [56,67,69] or consider redundant networks on smaller datasets [80,81]. Besides, some focus solely on simulations with no experimental data or employ practically nonviable devices for modeling purposes.

In this study, major imperfections on two prospective analog-grade synaptic devices, passively-integrated memristors, and eFlash memories, are characterized in order to determine nonidealities that severely impact mixed-signal DNNs. The choice of these promising

technologies stems from the fact that, unlike most emerging technologies, they transcend all rudimentary features, including high endurance, analog storage, long-term retention, low-power operation, and nano-scale footprint (see supplementary Table 1 in [32] for a comparison). Besides, low conductance and switching voltage range and very dense cell size  $(4F^2 \text{ and } \sim 110 F^2 \text{ for memristors and eFlash})$  allow practical implementation of large-scale mixed-signal DNNs with decently large VMMs (e.g.,  $64 \times 64$ ) [82].

In the case of eFlash memories, high precision tuning and superb analog-grade retention are reported, and excellent yield is deemed due to the maturity of the technology, making temperature variations the major issues. Passive TiO<sub>2</sub> memristive technology also offers high analog retention in an excellent areal density despite susceptibility to temperature variations, limited yield, and half select disturbance. Each factor is studied separately, and a holistic approach is proposed that includes modifications in the training, tuning, state optimization, and circuits and targets each issue individually. More importantly, the proposed method is practical in terms of implementation cost with negligible overhead and is validated on a hybrid experiment/simulation framework using two benchmarks: a moderate-size convolutional neural network (ConvNet) and ResNet-18 trained on CIFAR-10, and ImageNet datasets, respectively.

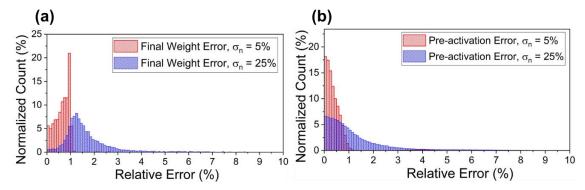

The accuracy drop is almost fully recovered in the 20 °C to 100 °C temperature range by employing three incrementally applied approaches: temperature-sweep batch training, k-reference batch normalization, and state optimization. The models are also resilient against the minor static nonlinearity (dot-product nonlinearity, i.e., *IV* nonlinearity in memristors and subthreshold slope nonlinearity in eFlash). Two techniques are proposed to overcome the limited yield in emerging technologies, pair modification that minimizes the weight mapping

error in the tuning phase and average error compensation that prevents the propagation of error through cascaded layers. High precision individual-device tuning accuracy (<1%) is experimentally showed for both devices, but passive memristors suffer from half-select disturbance due to the lack of selector. This issue is studied comprehensively in chapter 3.

# 2.1. Neuromorphic Benchmarks

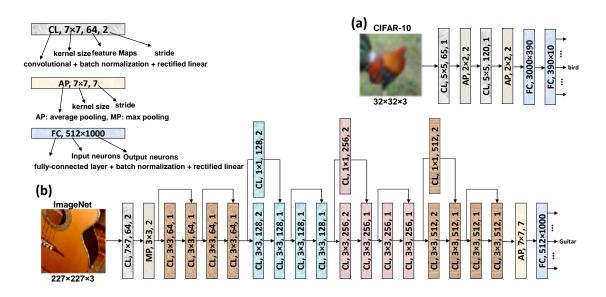

Fig. 5 shows the architecture of the neuromorphic benchmarks. The ConvNet model is based on Lenet-5 [83] architecture that includes 6 layers: Conv1, a convolutional layer with 5×5 filters and 65 feature maps; Pool1, a max-pooling layer of 2×2 regions; Conv2, a convolutional layer with 5×5 filters and 120 feature maps; Pool2, a max-pooling layer of 2×2 regions); FC1, a fully connected layer with 390 neurons; and finally FC2, a fully connected layer with 10 output neurons. Batch normalization is applied after each non-pooling layer, and rectified linear is used as the activation function in all the layers. The CIFAR-10 dataset consists of 60k 32×32 color images in 10 classes, with 6k images per class. The model is trained with 50k images and tested on the remaining 10k images of the dataset.

Standard data augmentation techniques such as zero-padding with two pixels, cropping a random 32×32 region, and performing random horizontal flipping of images are employed. No mean subtraction is performed (all input values are positive). We use ADAM optimizer, cross-entropy cost function, a batch size of 64, a learning rate of 0.001, and 220 epochs. Model initialization is performed following suggestions in [84].

The ResNet-18 implementation is based on the pre-trained model available at the official model zoo of the Pytorch. It includes 21+2 layers: a convolutional layer with 7×7 kernels and stride of 2, a max-pooling layer with 3×3 kernels and stride of 2, 4 convolutional blocks with residual connections, each including 4 convolutional layers based on 3×3 kernels and strides

of 2 and 1, a 7×7 average-pooling layer with the stride of 7, and finally a 512×1000 fully-connected layer that provides the output prediction corresponding to 1000 classes. The network is tested on 50k images and trained on ~1.3M images for 150 epochs with a batch size of 256, the learning rate of 0.1 that is divided by 0.1 every 30 epochs (step scheduling), cross-entropy cost function, weight decay of 0.0001, and stochastic gradient descent optimization with a momentum of 0.9. The two models are trained using 32-bit floating-point precision on Nvidia Titan X GPUs, and the learned parameters achieving the highest test accuracy are used as the baseline model. During the mixed-signal simulation, we convert weights into device conductance/current, incorporate the developed models and techniques in the simulation platform and baseline architecture, and execute training and inference tasks. Note that we have not mapped the network into any mixed-signal architecture (e.g., see [82]) since simulating the targeted massive benchmarks within these (mixed-signal) architectures is incompatible and practically impossible with current GPU platforms and will make our results architecture-specific.

Fig. 5: (a) A 6-layer convolutional neural network trained on the CIFAR-10 dataset. (b) The ResNet-18 model trained on the ImageNet dataset.

# 2.2. Device Characterization

Two mainstream driving force technologies in neuromorphic circuits are emerging memristive crosspoint devices and industrial-grade redesigned eFlash memories [85]. The excellent density and scaling prospects of the former enable the efficient implementation of large DNNs. However, the slow advancing pace of this technology signifies immense fabrication challenges, e.g., high uniformity requirements in the *IV* characteristics of memristors. In [32], a successful development 64×64 passive crossbar circuit with recordbreaking ~ 99% yield and < 26% normalized uniformity based on a foundry-compatible fabrication process is reported. As evidenced by the promising results from the recent demonstrations of large-scale neural networks [86], the situation is much better for floatinggate devices due to the availability of industrial-grade eFlash embedded in most CMOS processes.

A comprehensive characterization of imperfections in both memory technologies is initially performed. The experimental measurements are then used to model the average behavior of the devices and circuits. A unified parameter to describe major nonidealities in both synapses is used: the relative error of the state current,  $\Delta I/I_0$ , where  $I_0$  is the reference tuning current measured at the nominal biasing condition, and  $\Delta I$  is the current deviation from the ideal behavior. The models are then incorporated into simulation platforms (PyTorch-based libraries) to predict the fidelity loss in the benchmarks.

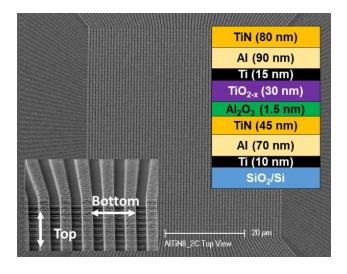

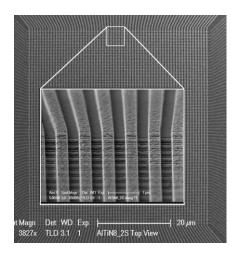

Fig. 6 shows the scanning electron microscope image of the fabricated crossbar that includes 4096 TiO<sub>2</sub> memristors—see Ref. [35] for more details on the fabrication process and relevant details on electroforming, tuning, and operation procedures.

Fig. 6: SEM image of the full 64×64 memristor crossbar array [35]. The bottom left, and bottom right insets show material layers at the device cross-section with corresponding thicknesses in nanometers and zoomed-in to a portion of the crossbar, respectively.

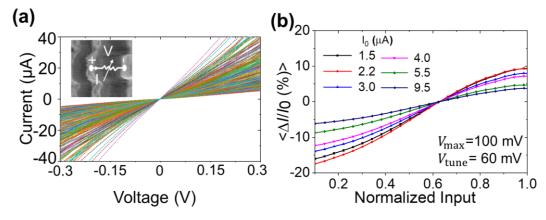

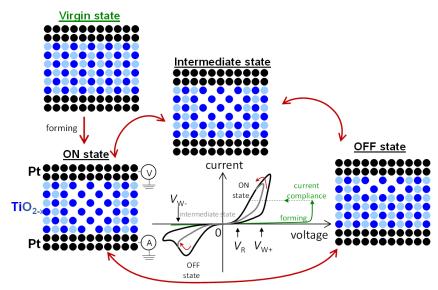

Fig. 7a shows the measured *IV* characteristics of 350 randomly selected devices in the non-disturbing low-voltage regime. Upon the application of a voltage in this regime (<0.5 V), the conductance (state) of crosspoint devices remains unchanged at a fixed voltage. However, due to the tunneling or thermionic emission charge transport mechanism, the devices become more

conductive in higher voltages and hence nonlinear. Fig. 7b shows the average relative static nonlinearity error versus applied voltage for various conductance states. It is computed with respect to the measured state current at the tuning voltage ( $V_{tune}$ ) of 60 mV and 0.1 V maximum voltage.

Fig. 7: (a) Low-voltage IV characteristics of 350 devices programmed to various states. The inset figure shows the cross-section of a device. (b) The average relative static nonlinearity error in memristor synapses  $\Delta M_0 \times 100$  for the same 350 devices, tuned in various states.

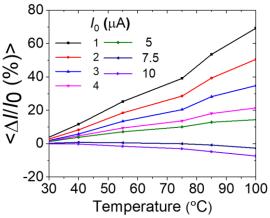

Fig. 8 shows the measurement results for the relative changes of conductance in 350 devices concerning variations in the die temperature (25–100 °C). The device conductance has proportional to absolute temperature and complementary to absolute temperature dependency in low conductive and high conductive states, respectively, due to the insulator-metal phase transition. In the case of our memristive devices, such transition occurs at  $\sim$ 70  $\mu$ S, on average. A large error, particularly in low conductive states, is observed, which could severely degrade the computational accuracy of mixed-signal models at elevated temperatures.

Fig. 8: The average relative change in state current versus temperature for 350 memristive devices tuned to various states.

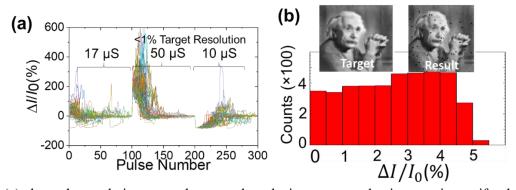

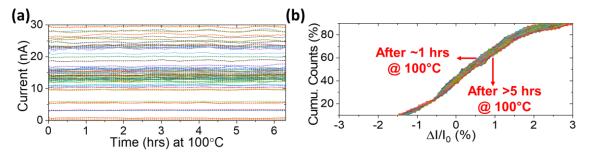

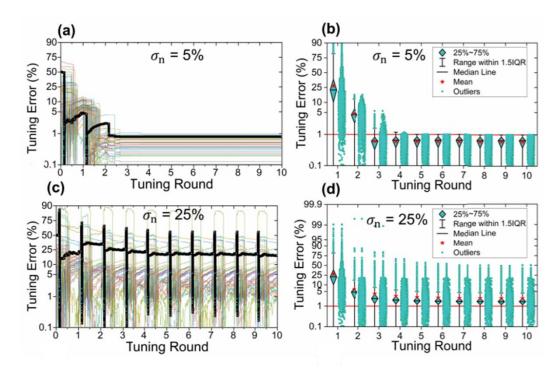

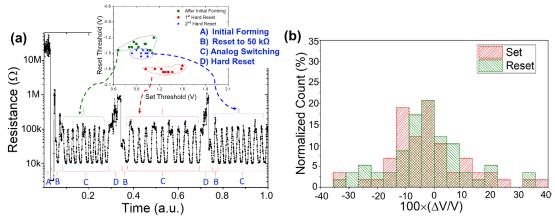

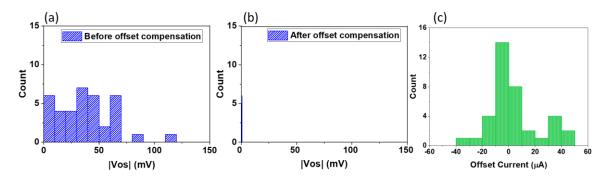

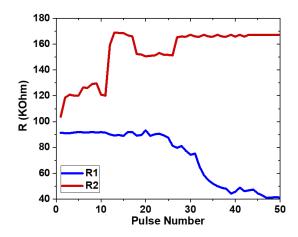

The switching characteristics of memristors determine how precisely their conductances can be adjusted. Individually, a device can be tunned with high accuracy, e.g., <1% relative error regardless of its initial conductance. The experimental results in Fig. 9a corroborate this observation on 50 randomly selected devices tuned to 1.7 µs, 50 µs, and 10 µs conductances consecutively. For each device, the desired accuracy is achieved in less than 100 pulses using a naive write-verify algorithm. However, tuning dynamics are more complicated at the crossbar level since the half-select problem imposes disturbance on already tuned 0T1R memristors. Using additional gate lines in active crossbars (1T1R) solves this problem at the cost of at least a two orders of magnitude increase in the cell size. Fig. 9b shows an example of the ultimate relative tuning error distribution after the entire 64×64 crossbar is programmed to the states that correspond to the grayscale quantized Einstein image [87]. The final tuning error distribution depends on the switching threshold distributions and the tuning algorithm. We return to this issue in the next chapter.

Fig. 9: (a) shows how relative error changes when devices are tuned using a write-verify algorithm with <1% target relative error. (b) The final tuning error distribution in  $64\times64$  crossbar after all devices are tuned.

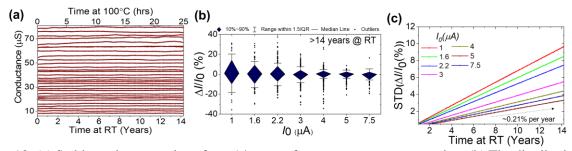

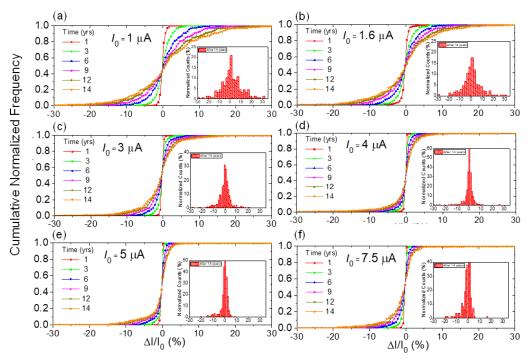

To investigate the impact of long-term retention loss, we perform accelerated retention tests and use the Arrhenius equation for the room temperature projection of the results. Fig. 10a shows the extremely stable analog-grade operation of 30 devices tuned in various states, subjected to 100 °C baking for >25 hours —translating into >14 years of room temperature operation assuming 1.1 eV activation energy [87]. Fig. 10b shows the distribution of relative retention loss error ( $\Delta M_0$ ) for 400 memristors after 14 years of projected room temperature operation where  $I_0$  is the initial sensed current for 400 memristors, each tuned to seven random states after projected 14 years of room temperature operation. Finally, Fig. 10c shows the corresponding standard deviation of the relative conductance change versus time binned to different states for these devices. The measured data show that the relative shift in conductance for most devices is expected to be <2% after several years of operation, which is adequately high for the practical implementation of ex-situ trained DNNs.

Fig. 10: (a) Stable analog operation after >14 years of room temperature operation. (b) The distribution of relative retention loss error ( $\Delta M_0 \times 100$ ). (c) the corresponding standard deviation of the relative conductance change versus time binned to different conductances. The conductance is measured at 0.1 V in these experiments.

More details of the statistical analysis of data for different states are provided in Fig. 11. Accelerated retention tests are performed at 100°C at 0.1 V for more than >25 hours. The results are then projected to room temperature using the Arrhenius equation and 1.1 eV activation energy. The insets show the histogram of the error for the case of 14 years. The results indicate that the retention loss is a bidirectional process for most devices and analog intermediate states, particularly midrange conductances. Unlike binary memristors [88], the distribution of retention loss error is relatively symmetrical in midrange analog states, i.e., the devices could move toward higher or lower conductive states. Note that we also observe unidirectional retention loss in very high (shifting toward low conductive states) or low (shifting toward high conductive states) conductance states, but we generally avoid switching the devices to extreme values. Nevertheless, the bilateral trend of retention loss of analog states is a positive feature since the tiny retention-induced errors become even smaller when they average out in large matrix multiplier kernels.

Fig. 11: Extended measurement results of accelerated retention test in memristive devices. Panels (a-f) show the cumulative normalized frequency of relative retention loss error among 400 devices tuned to various states.

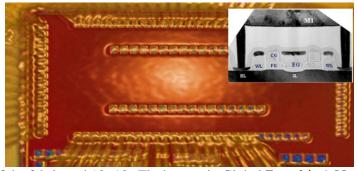

Fig. 12: Micrograph of the fabricated 12×10 eFlash array in Global Foundries' 55 nm CMOS process.

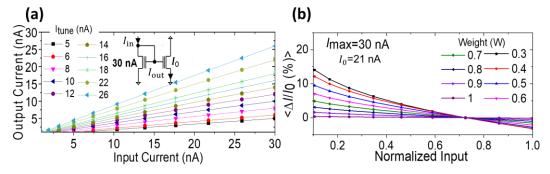

Fig. 12 shows the scanning electron microscope image of the fabricated redesigned eFlash memory array—see Ref. [35] for more details on tuning and operation procedure. First, we measure the average static input/output characteristics of 200 synapses in the gate-coupled structure (peripheral devices are tuned to the maximum state current,  $I_{max}$ =30 nA) and find the relative static nonlinearity error, which originates from the voltage-dependent capacitive

coupling. Fig. 13a-b show the static nonlinearity measurement results for multiple synaptic weights. In Fig. 13b, the devices are tuned to the desired state at  $I_{tune} = I_{in} = 21$  nA.

Fig. 13: (a) the average static input/output characteristics of 200 gate-coupled synapses given a peripheral cell tuned at 30 nA for various weight values. (b) the corresponding average nonlinearity error.

The temperature dependency of state current is also measured and demonstrated in Fig. 14a for 100 eFlash cells tuned to various states. The corresponding relative weight error in the gate-couple structure is also provided in Fig. 14b, indicating significant errors in high temperatures, which could significantly impact the accuracy of neural circuits.

Fig. 14:(a) the average relative change in current measured using 100 devices, (b) the average relative change in the synaptic weight (assuming I\_max=30 nA) of the gate-coupled structure versus temperature.

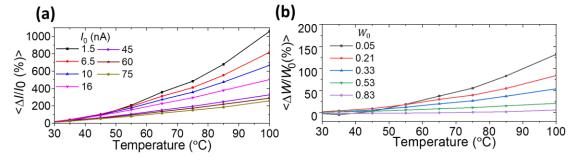

The retention characteristics of 100 eFlash memories are measured at 100°C. The measurements are performed by tuning the devices to different states within the relevant dynamic range. Fig. 15a shows the stable operation of 25 devices at 100°C for >6 hours. Regardless of the initial state, we confirm that the relative state change for most devices is comparable with the noise floor of the measurement setup (Fig. 15b). This superior

performance partially stems from much effort spent on optimizing the technology for industrial-grade applications.

Fig. 15: (a) Accelerated retention test for 100 eFlash devices tuned in 5 different states measured at 100°C and nominal tuning conditions. (b) the trend in the cumulative distribution function of the relative change in the current (@100 °C) for these devices. The relative change is within 1% for most of the devices.

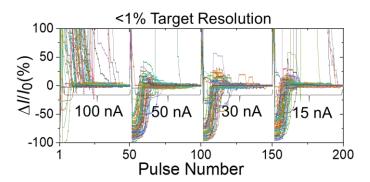

Finally, in Fig. 16, the high precision tuning capability of eFlash memories is shown for 50 devices by tuning them with 1% targeted accuracy to 100 nA, 50 nA, 30 nA, and 15 nA, consecutively, each using up to 50 pulses.

Fig. 16: High precision tunability (<1% target relative error) in 50 analog-grade redesigned eFlash memories, tuned to various target states.

The initial assessment of the experimental data indicates that the analog retention is promising in both devices; however, they are prone to variations in temperature that result in significant shifts in synaptic weights. Static nonlinearity is a fundamental bottleneck in most analog systems, and neural circuits are no exception. In both eFlash- and memristor-based neuromorphic systems, we need to optimize the circuit with respect to static nonlinearity. For

redesigned eFlash cells, high precision tuning is obtained due to the redesigned memory cell [70], and excellent yield [86] is deemed due to the maturity of the technology. However, for passive memristors, the half-select disturbance bounds the weight tuning accuracy in neuromorphic circuits built with practically viable kernel sizes, and limited percent-scale yield is a major hindrance. These identified imperfections are then modeled to study their deleterious effect in massive neuromorphic networks simulated in the PyTorch environment.

## 2.3. Simulation Framework and Device Modeling

Fig. 17 elaborates on the phenomenological modeling procedure for the temperature dependency of eFlash and memristors. Instead of using complex physics-based models that would significantly slow down the simulation time in the massive neuromorphic benchmarks, multi-order polynomial functions that decently and efficiently predict devices' average behavior were used. In both cases, the most optimum polynomial function is found manually by an exhaustive brute force search, and nonlinear least squares optimization with a trust-region algorithm is applied to find the optimum fitting parameters.

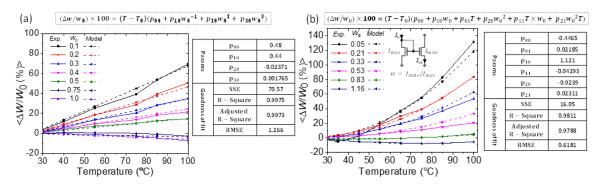

### 2.3.1. Temperature

To study temperature variations, the relative change in the weight  $(\Delta w/w_0) \times 100$ ) of every device in a synaptic pair is modeled using  $(T-T_0)(p_{00}+p_{10}w_0^{-1}+p_{20}w_0^2+p_{30}w_0^3)$  for metal-oxide memristors and  $(T-T_0)(p_{00}+p_{10}w_0+p_{10}T+p_{20}w_0^2+p_{11}T\times w_0+p_{21}w_0^2T)$  for eFlash memories in which  $w_0$  is the measured weight at nominal biasing conditions and  $T_0=25$ , T is the die's temperature in Celsius, and  $p_{ij}s$  are the fitted parameters. The fitting results show excellent goodness of fit across the temperature range for both synaptic device candidates. In Fig. 17a, a weight exactly corresponds to a device conductance (in a synaptic pair and  $\mu$ S), i.e.,  $w_0=0.1$  and  $w_0=1$  correspond to  $G_{min}$  and

$G_{max}$ , respectively. In Fig. 17b, a weight corresponds to a device state (in a synaptic pair) over the peripheral device state, i.e.,  $w_0 = 0$  and  $w_0 = 1$  correspond to  $I_{state} = 0$  and  $I_{state} = I_{max}$ , respectively. Since the peripheral state is often tuned at  $I_{max}$  (that is 30 nA in this figure),  $w_0$  equalizes the normalized weight. Note that in the case of eFlash memories, the model parameters change when a different  $I_{max}$  is used.

Note that most synaptic devices exhibit similar trends, and the similar modeling formats would apply to other devices as well. Only model parameters would be different. High-order nonidealities such as temperature dependency of nonlinearity, etc., are neglected in the simulations because they are far less impactful, and they typically devitalize each other, e.g., they become more linear and less noisy at elevated temperatures. Hence, they are neglected in our modeling here.

Fig. 17: Temperature modeling in analog-grade (a) memristors and (b) eFlash memories.

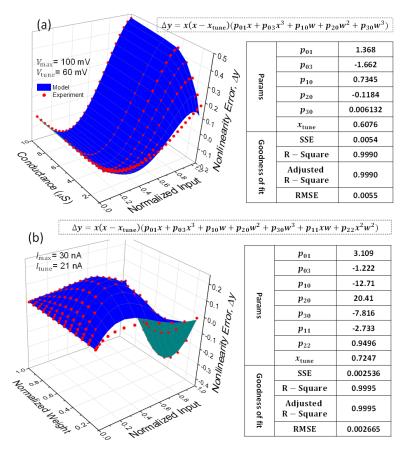

#### 2.3.2. Nonlinearity

Fig. 18 shows high goodness-of-fit in modeling the static nonlinearity of both analog memory candidates and discusses how static nonlinearity varies with the tuning condition. Like temperature modeling, a multi-order polynomial function that perfectly describes devices' average behavior without slowing down massive neuromorphic networks' simulation time is used. In both Fig. 18a and 18b, the polynomial functions' shape is manually optimized

and nonlinear least-squares optimization with a trust-region algorithm to obtain the model parameters is used.

Note that to ease the network simulation, in this part, the nonlinearity error (not the relative nonlinearity error) is modeled. The amount of nonlinearity error is a function of both conductances of the device in the tuning biasing condition, the maximum applied input signal, and the applied input signals. Hence, to avoid complicating the nonlinearity model and enhance the fitting results, we decouple it from the tuning conditions and maximum applied input signals, i.e., we perform the modeling and find the parameters for each design case once (separately). Here, the results are provided for one case in memristive circuits and one case of eFlash designs. In the former, the error in the synaptic current of a device tuned to w (the conductance of a single device in the differential pair in  $\mu S$ ) at the normalized input  $x_{tune}$ , when stimulated by x is modeled by  $\Delta y = x(x - x_{tune})(p_{01}x + p_{03}x^3 + p_{10}w + p_{20}w_0^2 +$  $p_{30}w_0^3$ ). For the latter, since the gate-coupled structure is studied, using both normalized weights and inputs makes the modeling easier. Here, when a normalized input x is applied to a synaptic device, tuned to the normalized weight of w at the normalized input  $x_{tune}$ , it creates a nonlinearity error that can be obtained by  $\Delta y = x(x - x_{tune})(p_{01}x + p_{03}x^3 + p_{10}w +$  $p_{20}w_0^2 + p_{30}w_0^3 + p_{11}xw + p_{22}x^2w^2$ ). In both models,  $p_{ij}s$  are the fitted parameters that are provided in the inset tables. For memristors, the parameters correspond to the case with  $V_{max}$ =0.1 and  $V_{tune}$ =0.06, while for eFlash,  $I_{max}$ =30 nA and  $I_{tune}$ =21 nA, i.e., the devices are tuned at the condition in which the input signals are 0.06 V (for memristors) and 21 nA (for eFlash). The fitting results show excellent goodness of fit across for both synaptic device candidates.

Fig. 18: Modeling nonlinearity for (a) passively integrated memristive devices and (b) redesigned eFlash memories.

## 2.4. Simulation Results

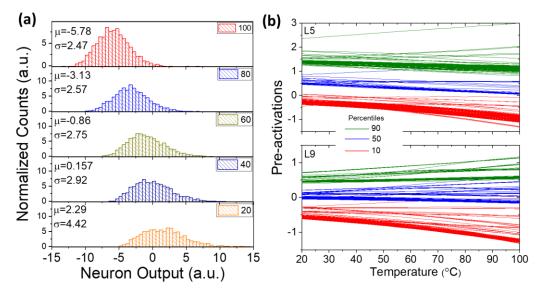

## 2.4.1. Temperature Variations

Temperature variations have the most drastic impact on mixed-signal neuromorphic circuits. The synaptic weights change dramatically with temperature, modulating the preactivation signals of the neurons. Fig. 19a shows how the preactivations received by the first neuron in the fully-connected layer of ResNet-18 change with the temperature. The modulation of the preactivation distributions occurs in all layers and neurons but with different rates. Fig. 19b shows the temperature dependency of multiple percentiles of the preactivation distributions in 2 different layers. Interestingly, such shifts are almost monotonic in most

neurons, partly because the conductance of synaptic devices (eFlash or memristors) changes monotonically with respect to the temperature.

Fig. 19: (a) The distribution of the first neuron's output activations in the fully-connected layer of ResNet-18 for 10 inference batches in several temperatures (FM2). (b) The temperature dependency of 10, 50, and 90 percentiles of the preactivation distributions (100 batches) of 100 random neurons in 2 different layers (RM1). FM2: eFlash, mapping 2. RM1: RRAM, mapping 1.

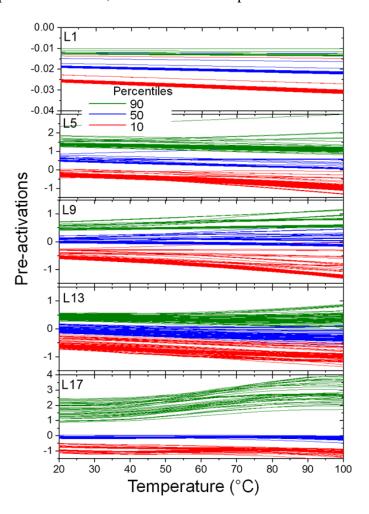

Fig. 20 also shows an almost monotonic shift in 10, 50, and 90 percentiles of preactivation statistics in 100 randomly selected neurons in various ResNet-18 layers and modulation rates. The statistics are obtained by processing 100 batches, and the temperature model of the RRAM devices using mapping 1. The proposed temperature compensation method consists of three incrementally applied approaches and aims to reduce the worst-case accuracy across the studied temperature range by modifying the circuit and training algorithm.

The first method is temperature-sweep batch training, in which we include the temperature model of synapses in the training process by considering a new hyperparameter called training temperature  $(T_{\theta})$ . Before running each forward pass of the training, we assume the model is ready for deployment in a chip that operates at an ambient temperature  $T_{\theta}$  and convert all weights to their corresponding synaptic current values. Using the device model, we adjust the

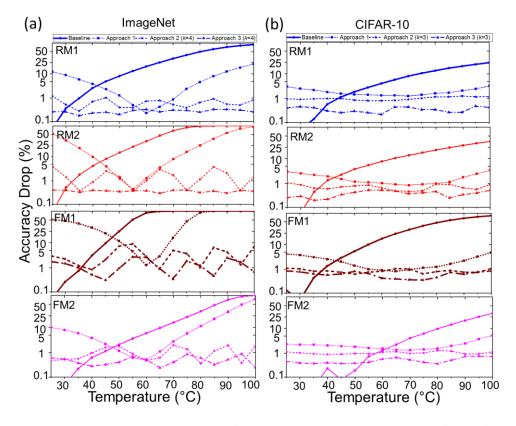

resultant synaptic current values in every step based on the training temperature value. The altered synaptic currents are converted back to the equivalent software weights before the forward pass is executed. Triangular scheduling of the training temperature is adapted, i.e.,  $T_{\theta}$  is swept from 25 °C to 95 °C and vice versa by 10 °C steps in every batch. Fig. 21a shows the reduction of the worst-case accuracy drop for different stacks and mappings in ResNet-18. Baseline corresponds to the evaluation case without any mitigation technique, while approaches 1, 2, and 3 refer to temperature-sweep batch training, k-reference batch normalization, and state optimization methods. These techniques are applied incrementally on the network. In approaches 2 and 3, we use 4 reference points.

Fig. 20:Preactivation statistics versus temperature.

For example, for RM1 (RRAM stack, mapping 1), the worst-case drop (occurs at 100 °C) is reduced from ~66% to 23% after applying approach 1. The most optimum performance is also achieved in midrange temperatures (60 °C), as expected. The improvements in ConvNet are also encouraging since the worst-case drop is decreased from ~25% to 3.3% (for RM1), as shown in Fig. 21b.

Fig. 21: The accuracy drop versus temperature in (a) ImageNet benchmark when using various synapse options to implement ResNet-18 model, (b) ConvNet to implement CIFAR-10. RM1: RRAM, mapping 1; RM2: RRAM, mapping 2; FM1: eFlash, mapping 1; FM2: eFlash, mapping 2.

Inspired by our work on increasing the reliability of hardware security primitives [89], kreference batch normalization is adopted that further enhances the performance by using ktemperature-optimized batch normalization parameters per neuron. Owing to the monotonic

change in the statistics of preactivations (i.e., the shift and stretch of the preactivations) with

respect to the temperature (Fig. 19a-b), a temperature-dependent correction signal allows us

to minimize the induced error. Since generating such neuron-specific signals with adjustable temperature-dependency are costly, we use a quantized version of it through multiple batch normalization weights that effectively shift and scale preactivations. After the model is trained with the first approach, we find k reference batch normalization parameters by retraining it in a single epoch with a learning rate of 0.001 in k reference temperatures. During the inference, the temperature of the chip is sensed by a low-cost on-chip sensor and used to determine the proper batch normalization parameters that correct the distributions Fig. 21a shows a considerable reduction of the worst-case drop in the ImageNet benchmarks after applying the second approach (k=4), e.g., from ~23% to 1.25% for RM1. In the CIFAR-10 benchmark, the worst-case drop for RM1 cases decreases from ~3.3% to 1.22%, with only 3 reference points.

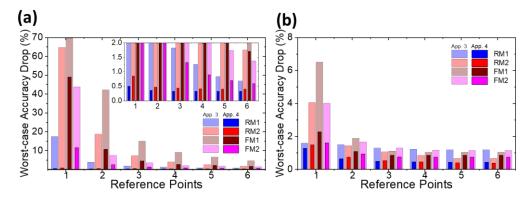

As depicted in Fig. 22a (for ResNet-18) and Fig. 22b (for ConvNet), the results can be further improved by increasing the number of reference points; a sub-percent accuracy drop is achieved with a few references (depending on the stack and mapping). Note that the model is still trained ex-situ entirely with a negligible overhead (2k parameters per neuron). Though the second approach significantly reduces the worst-case accuracy drop, if needed, the results can be improved even further by optimizing the weight mapping parameters ( $I_{min}$ ,  $I_b$ ) for each weight.

Fig. 22: The worst-case accuracy drop in the 20-100 °C temperature range versus the number of reference points for approaches 2 and 3 for (a) the ResNet-18 and (b) the ConvNet model.

The state optimization approach is the third technique that mitigates the accuracy drop in a wide temperature range. Here, the mapping parameters are optimized individually for every weight targeting the lowest weight error across the full temperature range. Such design parameters are often selected to minimize the power consumption in eFlash memories or maximize the dynamic range in memristors. However, these design parameters are not necessarily the most optimum in terms of temperature variations and reliability. Since this approach comes with power consumption addition or dynamic range reduction, a methodology that finds quasi-optimal design points in either weight-conductance mapping functions is developed.

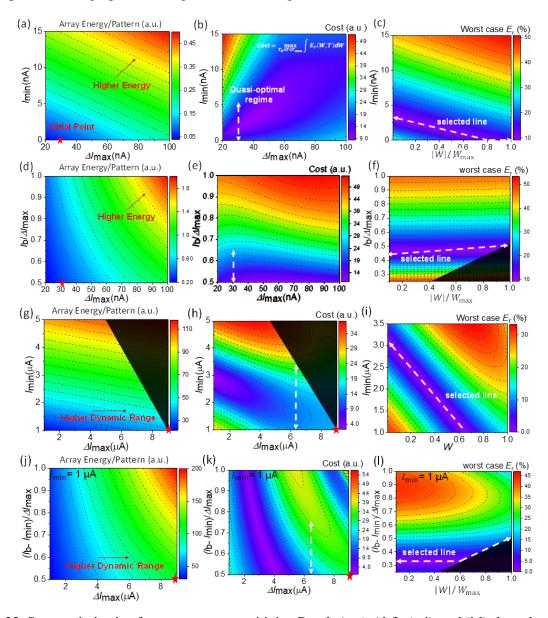

A numerical analysis of the experimental data is provided in Fig. 23. It shows a procedure for finding the quasi-optimum design parameters of each device stack and weight mapping functionality. The panels in the first column of Fig. 23 show the normalized energy consumption in synaptic arrays for a network of 10M normally distributed weights versus the dynamic range ( $\Delta I_{max}$ ). The choice of the initial design point ( $\Delta I_{max}$ ,  $I_{min}$ , and  $I_b$ ) is often in the direction of minimizing the energy consumption in eFlash circuits and maximizing the dynamic range in 0T1R memristive systems, regardless of the mapping type (the red star in the first column panels shows the initial design point).

However, the optimum sensitivity concerning temperature variations is not necessarily this design point. Since we intend to apply a secondary cost-free technique to further compensate for temperature variations, the goal in this step is to trade energy or dynamic range to improve the accuracy and find a quasi-optimum operating point that is less sensitive to temperature variations. To find a quasi-optimum design point, the cost function  $C = \max_{T_0 \le T \le T_{\text{max}}} \int_{\in +}^{1} |E_r(W,T)| dW$  is defined, which represents the worst sum of relative errors

among all (normalized) weights across all temperatures. To numerically compute the cost function, we use  $T_0 = 25$ ,  $T_{\text{max}} = 100$ , and  $\epsilon^+ = 0.01$ . The minima of the cost function give the optimum design point averaged over the weights.

Fig. 23: State optimization for temperature sensitivity. Panels (a-c), (d-f), (g-i), and (j-l) show the state optimization simulation results corresponding to mapping 1 of eFlash, mapping 2 of eFlash, mapping 1 of memristors, and mapping 2 of memristors, respectively. The shaded areas denote out-of-range regimes.

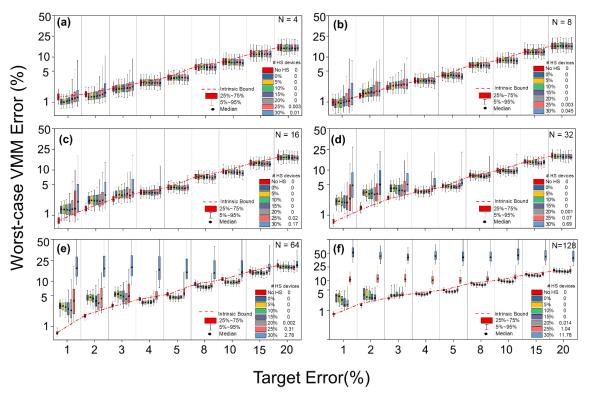

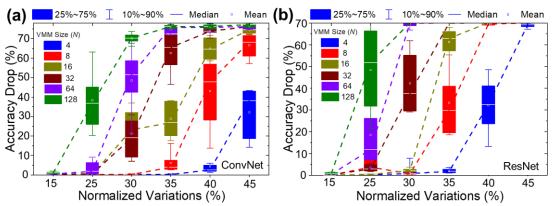

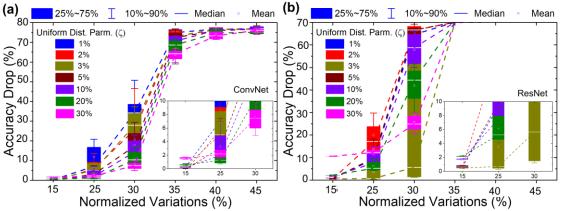

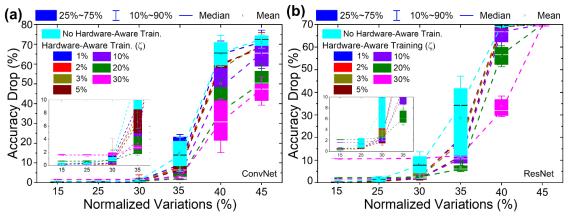

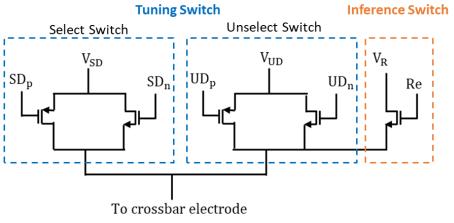

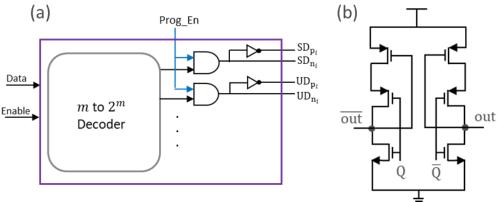

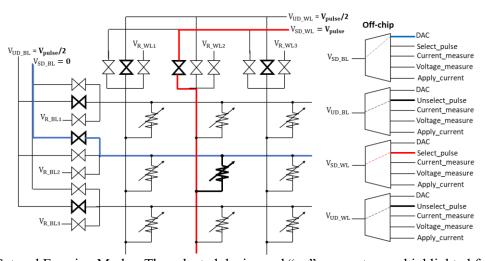

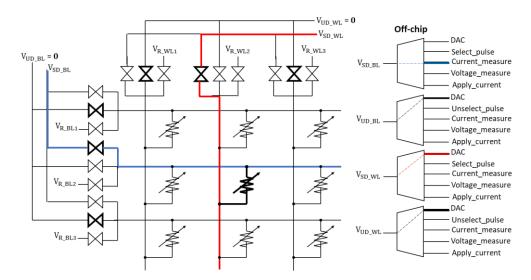

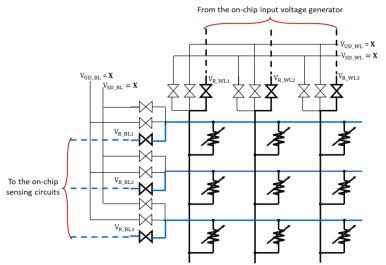

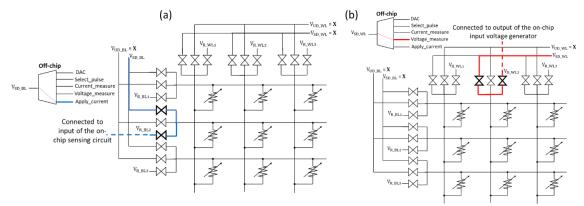

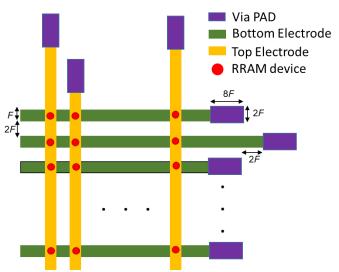

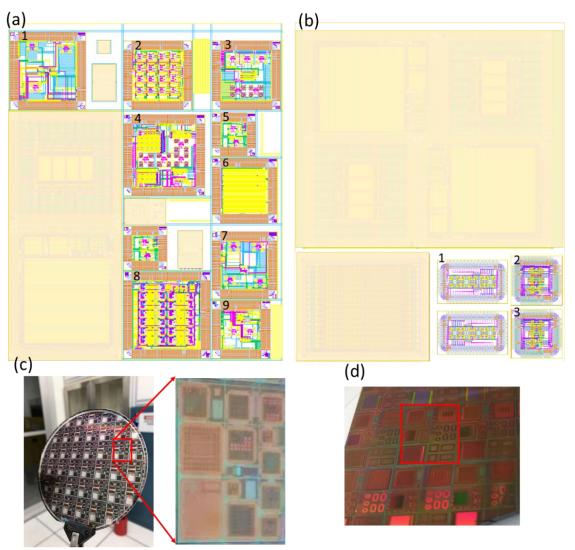

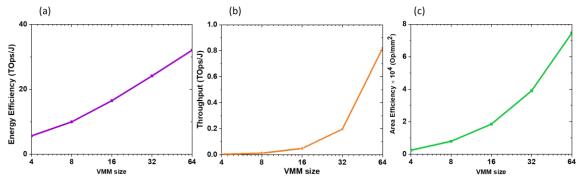

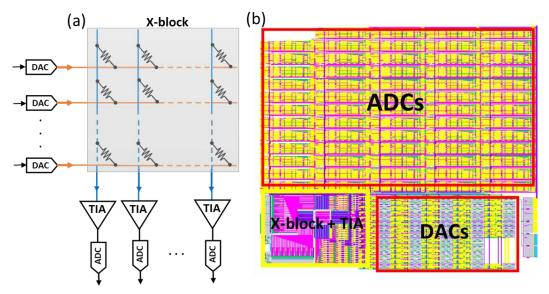

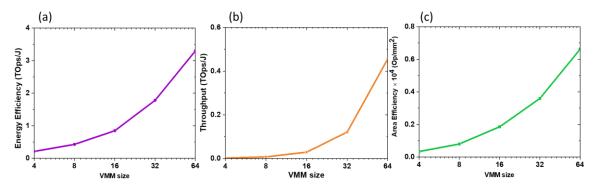

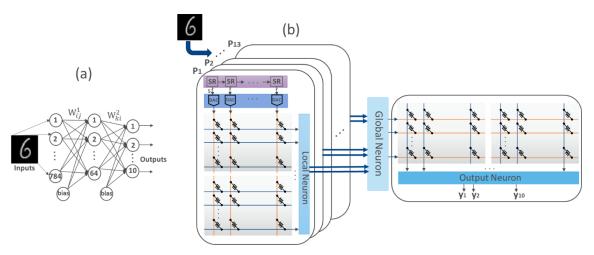

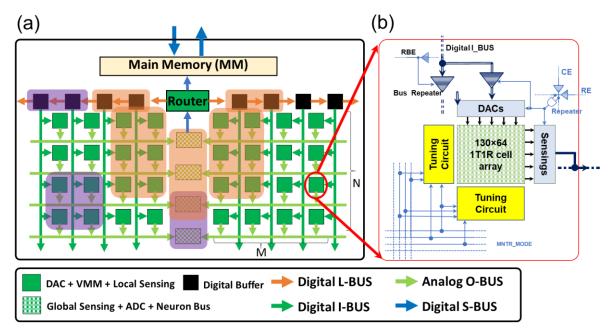

The panels in the second column show how C changes across the design space. Based on the heatmap of C,  $\Delta I_{max}$  can be selected close to the minima without overspending on energy (in eFlash) or dynamic range (in memristors). By definition,  $\Delta I_{max}$  is weight independent; however, the other design parameter ( $I_{min}$  or  $I_b$ ) may be optimized at the cost of slight power increase or dynamic range reduction.