## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

### **Title**

Smart Frame Grabber : : A Hardware Accelerated Computer Vision Framework

### **Permalink**

https://escholarship.org/uc/item/48h598vk

### **Author**

Jacobsen, Matthew Daniel

### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Smart Frame Grabber: A Hardware Accelerated Computer Vision Framework

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

by

Matthew Daniel Jacobsen

### Committee in charge:

Professor Ryan Kastner, Chair Professor Serge Belongie Professor Yoav Freund Professor Rajesh Gupta Professor Truong Nguyen

Copyright

Matthew Daniel Jacobsen, 2014

All rights reserved.

| The Dissertation of Matthew Daniel Jacobsen is approved and is accept-    |

|---------------------------------------------------------------------------|

| able in quality and form for publication on microfilm and electronically: |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

| Chair                                                                     |

University of California, San Diego 2014

### **DEDICATION**

This work is dedicated to my family and friends who have supported me throughout my studies. First and foremost, my wife Hayessa, who has put up with endless nights with me at the computer. Also to my close friends Matt and Janet Dowling who have been a constant source of reassurance and opportunity. To my oldest friend Sayf Alalusi and his generous family, who have provided (among many things) an example of how to be. Lastly, to my parents who made this possible.

### **EPIGRAPH**

Great minds discuss ideas; average minds discuss events; small minds discuss people.

Eleanor Roosevelt

Nothing is really work unless you would rather be doing something else.

J. M. Barrie

Have a good day! Don't forget to come home.

Ashton Jacobsen

## TABLE OF CONTENTS

| Signatu   | re Page                                                         | iii   |

|-----------|-----------------------------------------------------------------|-------|

| Dedicat   | ion                                                             | iv    |

| Epigrap   | h                                                               | V     |

| Table of  | Contents                                                        | vi    |

| List of F | Figures                                                         | X     |

| List of 7 | Tables                                                          | xiv   |

| Preface   |                                                                 | XV    |

| Acknow    | rledgements                                                     | XV    |

| Vita      |                                                                 | xviii |

| Abstrac   | t of the Dissertation                                           | XX    |

| Introduc  | ction                                                           | 1     |

| Chapter   |                                                                 | 4     |

| 1.1       | Motivation                                                      | 6     |

| 1.2       | Communication Component                                         | 7     |

| 1.3       | Reusable Components                                             | 9     |

| 1.4       | Contributions                                                   | 11    |

|           | 1.4.1 Framework Contributions                                   | 11    |

|           | 1.4.2 Application Contributions                                 | 12    |

| Part I    | Smart Frame Grabber Framework                                   | 15    |

| Chapter   | 2 RIFFA: A Reusable Integration Framework for FPGA Accelerators | 16    |

| -         | Introduction                                                    | 16    |

| 2.2       | Related Work                                                    | 18    |

| 2.3       | RIFFA 1.0                                                       | 19    |

|           | 2.3.1 Architecture                                              | 19    |

| 2.4       | RIFFA 2.0                                                       | 28    |

|           | 2.4.1 Design                                                    | 28    |

|           | 2.4.2 Architecture                                              | 35    |

|           | 2.4.3 Performance                                               | 41    |

| 2.5       | Conclusion                                                      | 45    |

| Part II | Smart Frame Grabber Applications                               | 47 |

|---------|----------------------------------------------------------------|----|

| Chapter | 3 FPGA Accelerated Skin Color Detection                        | 48 |

| 3.1     | Introduction                                                   | 48 |

| 3.2     | Design and Architecture                                        | 49 |

| 3.3     | Performance                                                    | 51 |

| 3.4     | Conclusion                                                     | 52 |

| Chapter |                                                                | 53 |

| 4.1     | Introduction                                                   | 53 |

| 4.2     | Algorithm                                                      | 54 |

| 4.3     | Architecture                                                   | 55 |

| 4.4     | Performance                                                    | 57 |

| 4.5     | Conclusion                                                     | 58 |

| Chapter | 5 FPGA Accelerated Face Detection                              | 60 |

| 5.1     | Introduction                                                   | 60 |

| 5.2     | Algorithm                                                      | 61 |

| 5.3     | Architecture                                                   | 62 |

| 5.4     | Performance                                                    | 65 |

| 5.5     | OpenCV Integration                                             | 66 |

|         | 5.5.1 Performance                                              | 67 |

| 5.6     | Conclusion                                                     | 68 |

| Chapter | 6 FPGA-GPU-CPU Heterogenous Architecture for Real-time Cardiac |    |

| onup w  | Physiological Optical Mapping                                  | 69 |

| 6.1     | Introduction                                                   | 69 |

| 6.2     | Related Work                                                   | 72 |

| 6.3     | Optical Mapping Algorithm                                      | 73 |

| 0.0     | 6.3.1 Normalization                                            | 73 |

|         | 6.3.2 Phase Correction Spatial Filter                          | 73 |

|         | 6.3.3 Phase Correction Algorithm                               | 75 |

|         | 6.3.4 Temporal Median Filter                                   | 75 |

| 6.4     | Application Partitioning                                       | 76 |

| 6.5     | Design and Implementation                                      | 79 |

|         | 6.5.1 Overall System                                           | 79 |

|         | 6.5.2 FPGA Design                                              | 81 |

|         | 6.5.3 GPU Design                                               | 81 |

| 6.6     | Results and Analysis                                           | 83 |

|         | 6.6.1 Experimental Setup                                       | 83 |

|         | 6.6.2 Performance                                              | 83 |

|         | 6.6.3 Accuracy                                                 | 85 |

| 6.7     | Conclusion                                                     | 86 |

| Chapter | 7 Hardware Accelerated Online Boosting for Multi-Target Tracking . | 88  |

|---------|--------------------------------------------------------------------|-----|

| 7.1     | Introduction                                                       | 88  |

| 7.2     | Related Work                                                       | 90  |

| 7.3     | Algorithm                                                          | 90  |

|         | 7.3.1 Motion Model                                                 | 92  |

|         | 7.3.2 Search Strategy                                              | 92  |

|         | 7.3.3 Appearance Model                                             | 92  |

| 7.4     | Tracking Application                                               | 96  |

| 7.5     | Hardware Design                                                    | 97  |

|         | 7.5.1 FPGA Design                                                  | 98  |

|         | 7.5.2 GPU Design                                                   | 104 |

| 7.6     | Results And Analysis                                               | 108 |

|         | 7.6.1 Software-only                                                | 109 |

|         | 7.6.2 GPU                                                          | 109 |

|         | 7.6.3 FPGA                                                         | 110 |

|         | 7.6.4 Comparison                                                   | 111 |

| 7.7     | Conclusion                                                         | 113 |

|         |                                                                    |     |

| Chapter | 8 Improving FPGA Accelerated Tracking with Multiple Online Trained |     |

| -       | Classifiers                                                        | 114 |

| 8.1     | Introduction                                                       | 114 |

| 8.2     | Related work                                                       | 116 |

| 8.3     | Algorithm                                                          | 117 |

|         | 8.3.1 Classifier Algorithm                                         | 117 |

|         | 8.3.2 Main Algorithm                                               | 120 |

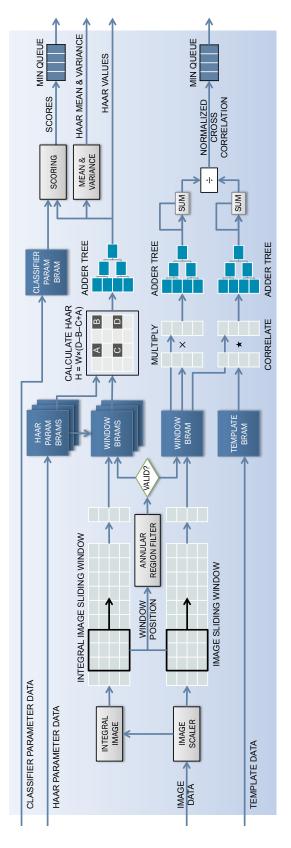

| 8.4     | FPGA-CPU design                                                    | 124 |

|         | 8.4.1 Evaluate stage                                               | 125 |

|         | 8.4.2 Update stage                                                 | 129 |

|         | 8.4.3 Train stage                                                  | 129 |

| 8.5     | Experimental results                                               | 130 |

| 8.6     | Conclusion                                                         | 134 |

| 0.0     | Conclusion                                                         | 15. |

| Chapter | 9 Future Directions                                                | 135 |

| 9.1     | Simple Compatible Interfaces                                       | 135 |

| 9.2     | Direct Device To Device Communication                              | 136 |

| 9.3     | OpenCV Integration                                                 | 136 |

|         | o.F. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.                        |     |

| Appendi | ices                                                               | 138 |

|         |                                                                    |     |

| Appendi | ix A RIFFA 1.0                                                     | 139 |

| A.1     | E                                                                  | 139 |

| A.2     | Hardware Interface                                                 | 145 |

| ۸ 3     | Software API                                                       | 151 |

| Appendi  | x B RIFFA 2.0                              | 172 |

|----------|--------------------------------------------|-----|

| B.1      | Getting Started                            | 172 |

| B.2      | Hardware Interface                         | 174 |

| B.3      | C/C++ API                                  | 178 |

|          | B.3.1 API                                  | 180 |

| B.4      | Java API                                   | 183 |

|          | B.4.1 API                                  | 186 |

| B.5      | Python API                                 | 192 |

|          | B.5.1 API                                  | 195 |

| B.6      | Design Tips                                | 199 |

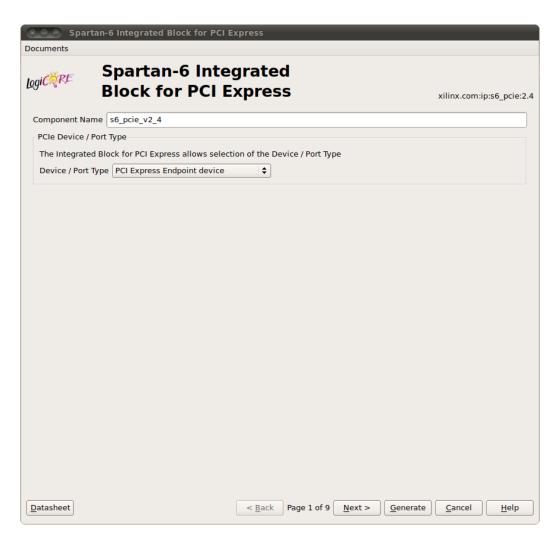

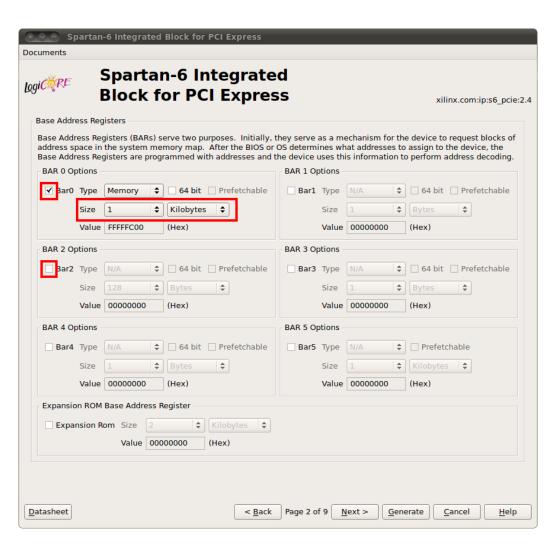

| B.7      | Design Guide - Avnet Xilinx S6LX150t - ISE | 200 |

| B.8      | Design Guide - Xilinx ML605 - ISE          | 208 |

| B.9      | Design Guide - Xilinx VC707 - ISE          | 216 |

| B.10     | Design Guide - Xilinx VC707 - Vivado       | 223 |

|          |                                            |     |

| Appendi  | x C Reusable Components                    | 234 |

| C.1      | Image Scaler                               | 234 |

| C.2      | Frame Capture                              | 234 |

| C.3      | Sliding Window Framework                   | 236 |

| C.4      | Integral Image Conversion                  | 237 |

| C.5      | Pixel Color Space Conversion               | 237 |

| C.6      | Arithmetic Operations                      | 238 |

| C.7      | Counting and Filtering                     | 239 |

| C.8      | Feature Extraction and Calculation         | 239 |

| C.9      | Clock Domain Crossing                      | 240 |

| C.10     | Data Manipulation                          | 241 |

|          | RAMs and FIFOs                             | 241 |

| C.12     | Skin Detector                              | 244 |

|          |                                            |     |

| Riblingr | anhy                                       | 245 |

## LIST OF FIGURES

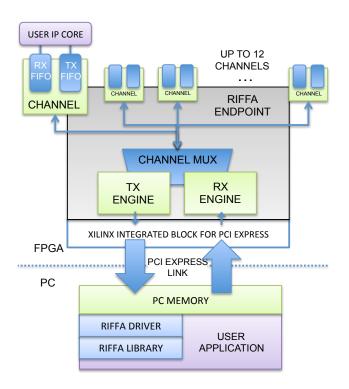

| Figure 2.1.                                                                                                                                                                                             | Architecture of RIFFA 1.0 framework. Application acceleration cores interface with the DMA Request and Central Notifier cores.                                                  |    |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| Figure 2.2.                                                                                                                                                                                             | Example usage of RIFFA 1.0 from a user application                                                                                                                              |    |  |  |  |

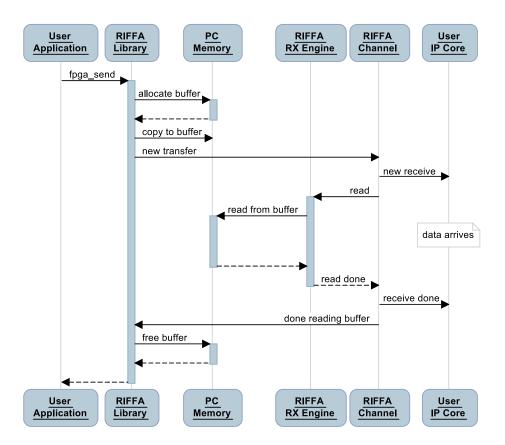

| Figure 2.3.                                                                                                                                                                                             | Example usage of RIFFA from a user application                                                                                                                                  |    |  |  |  |

| Figure 2.4.                                                                                                                                                                                             | RIFFA 2.0 software example in C                                                                                                                                                 | 33 |  |  |  |

| Figure 2.5.                                                                                                                                                                                             | RIFFA 2.0 hardware example in Verilog                                                                                                                                           | 34 |  |  |  |

| Figure 2.6.                                                                                                                                                                                             | RIFFA 2.0 architecture.                                                                                                                                                         | 36 |  |  |  |

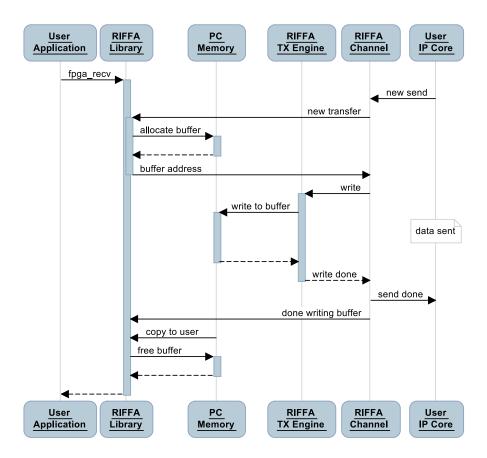

| Figure 2.7.                                                                                                                                                                                             | Downstream transfer sequence diagram                                                                                                                                            | 37 |  |  |  |

| Figure 2.8.                                                                                                                                                                                             | Upstream transfer sequence diagram                                                                                                                                              | 39 |  |  |  |

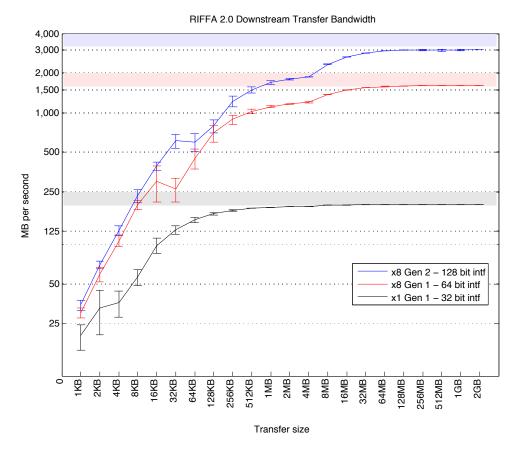

| Figure 2.9.                                                                                                                                                                                             | Downstream transfer bandwidths as a function of transfer size. Upstream bandwidths are nearly identical                                                                         | 43 |  |  |  |

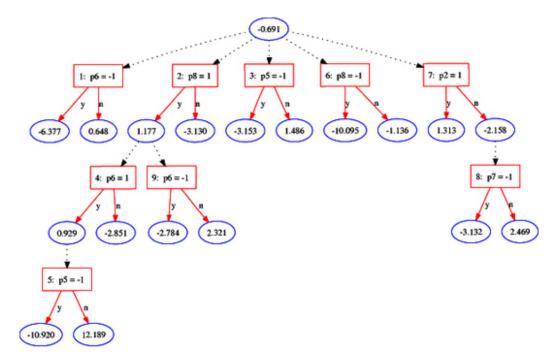

| Figure 3.1.                                                                                                                                                                                             | Alternating decision tree example                                                                                                                                               | 50 |  |  |  |

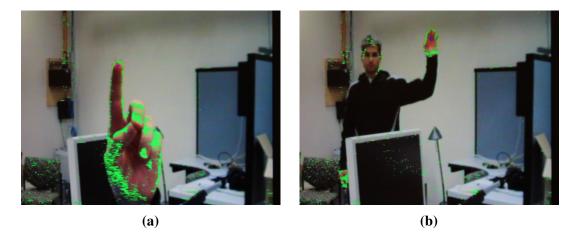

| Figure 3.2.                                                                                                                                                                                             | Image frames of skin detector evaluating live video                                                                                                                             | 52 |  |  |  |

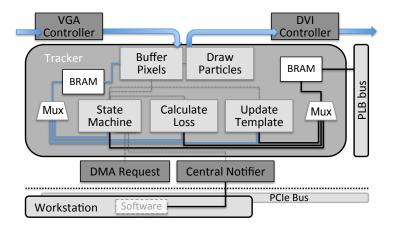

| Figure 4.1.                                                                                                                                                                                             | Tracker core architecture. The State Machine module interfaces with the DMA Request and Central Notifier cores. Software on the workstation initiates processing via interrupts | 56 |  |  |  |

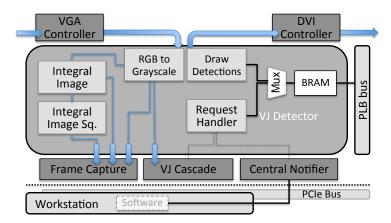

| Figure 5.1. Architecture of the VJ Detector core. The Request Handler module interfaces with the Central Notifier and VJ Cascade cores. Software on the workstation initiates processing via interrupts |                                                                                                                                                                                 |    |  |  |  |

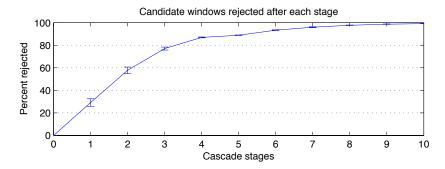

| Figure 5.2. Cumulative percentage of candidate locations rejected after evaluating cascade stages. Only first 10 stages shown                                                                           |                                                                                                                                                                                 |    |  |  |  |

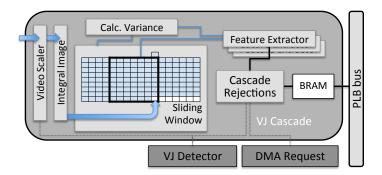

| Figure 5.3. Architecture of the VJ Cascade core. The detections from the first few stages are saved as a binary bitmap by the Cascade Rejections module.                                                |                                                                                                                                                                                 |    |  |  |  |

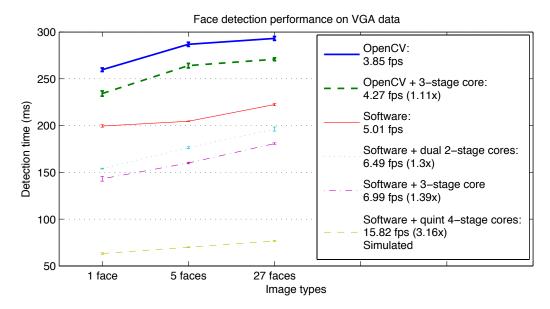

| Figure 5.4. Face detection times on VGA video. Speed up over equivalent software only version is listed in parenthesis                                                                                  |                                                                                                                                                                                 |    |  |  |  |

| 67         | 5. Pseudo code representation of modified OpenCV cascade detection function                                                                                                                                  | Figure 5.5.                                                      |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| 68         | 6. Face detection times on VGA video in frames per second                                                                                                                                                    | Figure 5.6.                                                      |  |  |  |

| 70         | Figure 6.1. Image conditioning effect (left: the grayscale image of a random frame, right: the waveform of a random pixel over time). (a) before image conditioning. (b) after image conditioning            |                                                                  |  |  |  |

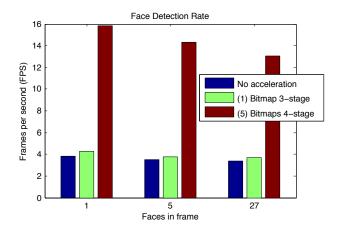

| <b>7</b> 4 | 2. Optical mapping algorithm                                                                                                                                                                                 | Figure 6.2.                                                      |  |  |  |

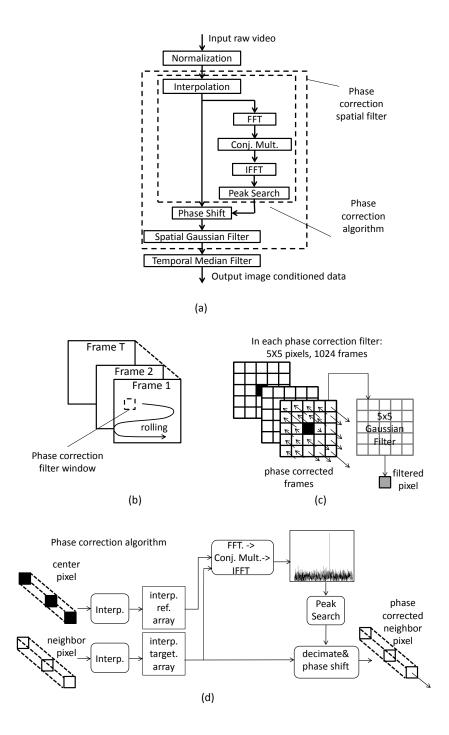

| 80         | 3. FPGA-GPU heterogenous architecture                                                                                                                                                                        | Figure 6.3.                                                      |  |  |  |

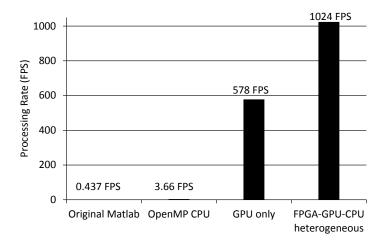

| 84         | 4. The performance of the FPGA-GPU-CPU heterogenous implementation in comparison to the original Matlab, the OpenMP C++, and the GPU only implementation.                                                    | Figure 6.4.                                                      |  |  |  |

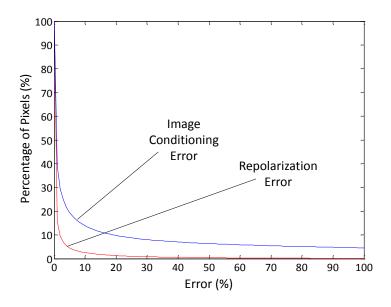

| 85         | 5. Error of the output of the optical mapping image conditioning (blue line) and error in repolarization analysis (red line)                                                                                 | Figure 6.5.                                                      |  |  |  |

| 93         | 1. <b>A.</b> Circular search region with radius $s$ (left). <b>B.</b> Circular region with radius $r$ for positive examples and sampled annular region with radii $q$ and $q'$ for negative examples (right) | with radius $r$ for positive examples and sampled annular region |  |  |  |

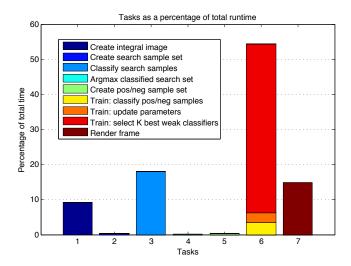

| 97         | 2. Performance of different tasks in the algorithm as a percentage of total time                                                                                                                             | Figure 7.2.                                                      |  |  |  |

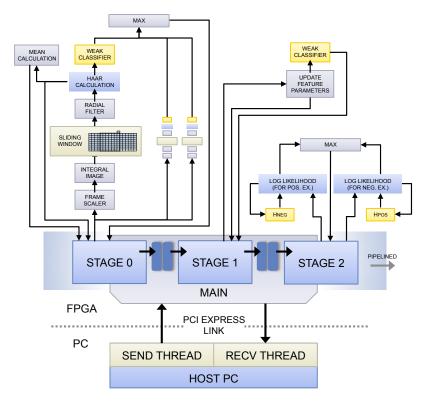

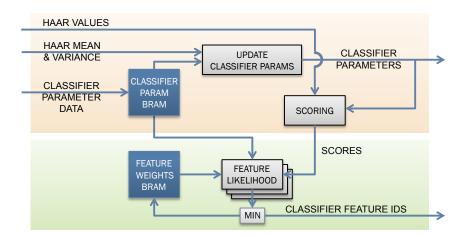

| 99         | 3. High level architecture of FPGA design                                                                                                                                                                    | Figure 7.3.                                                      |  |  |  |

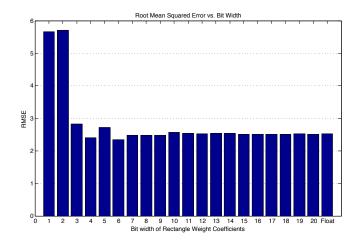

| 104        | 4. Root mean squared error of different bit widths for Haar rectangle weights over test sequences                                                                                                            | Figure 7.4.                                                      |  |  |  |

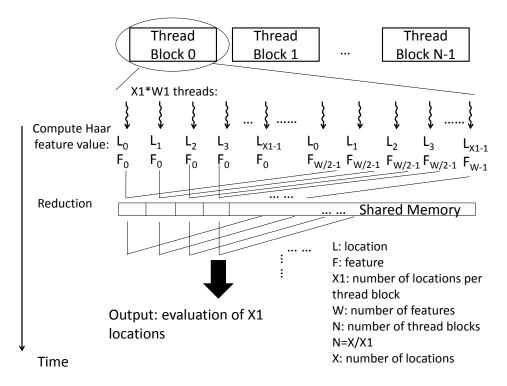

| 105        | 5. Implementation of the feature extraction kernel                                                                                                                                                           | Figure 7.5.                                                      |  |  |  |

| 107        | 6. Implementation of the feature update kernel. (a) Thread assignment; (b) Sequential iteration data flow                                                                                                    | Figure 7.6.                                                      |  |  |  |

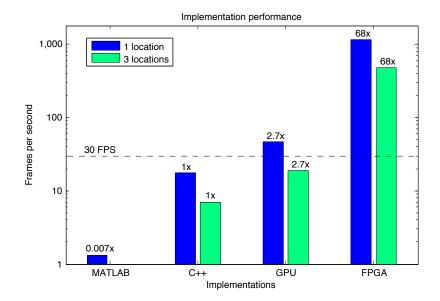

| 108        | 7. Performance of implementations. Speed up factors over the C++ implementation are shown above each bar. Y axis is logarithmic.                                                                             | Figure 7.7.                                                      |  |  |  |

| 110        | 8. Example tracking sequences (left to right). Multiple target tracking.                                                                                                                                     | Figure 7.8.                                                      |  |  |  |

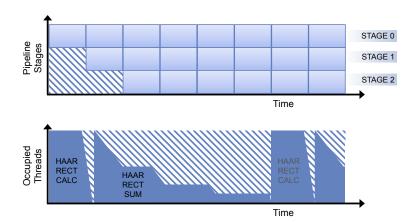

| 111        | 9. FPGA pipeline filling (top). GPU non-idle threads for feature calculation kernel (bottom). Hatched region represents idle resources.                                                                      | Figure 7.9.                                                      |  |  |  |

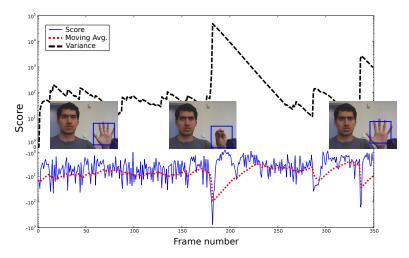

| Figure 8.1. | Classifier scores during target appearance changes. Changes produce sharp drops in score and spikes in variance.                                                                                                                         |     |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

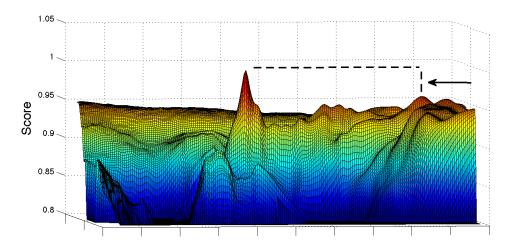

| Figure 8.2. | Plot of a classifier's score over the X and Y dimensions. This example shows a sharp peak and the next highest peak at least d pixels away                                                                                               | 121 |  |

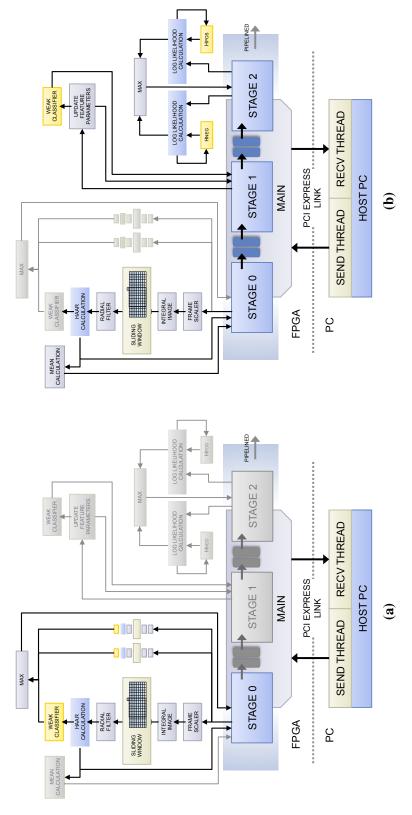

| Figure 8.3. | FPGA-CPU high level architecture                                                                                                                                                                                                         | 123 |  |

| Figure 8.4. | Evaluate stage architecture                                                                                                                                                                                                              | 126 |  |

| Figure 8.5. | Update stage (top) and Train stage (bottom) architectures                                                                                                                                                                                | 130 |  |

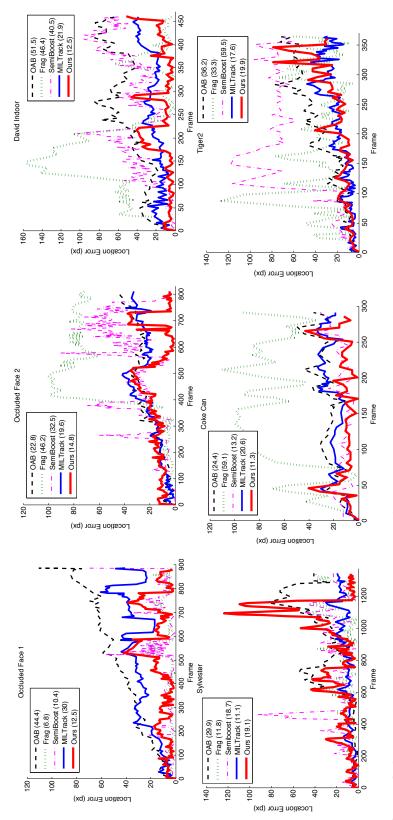

| Figure 8.6. | Location errors on video sequence from several tracking publications. Error is the difference between predicted tracking location and the ground truth, in pixels. Average pixel error over the entire sequence is shown in parentheses. | 131 |  |

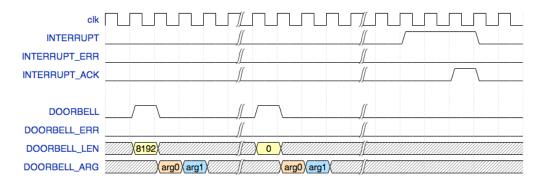

| Figure A.1. | RIFFA 1.0 timing diagram for doorbells/interrupts                                                                                                                                                                                        | 146 |  |

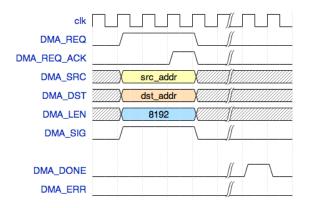

| Figure A.2. | RIFFA 1.0 timing diagram for DMA transfer                                                                                                                                                                                                | 148 |  |

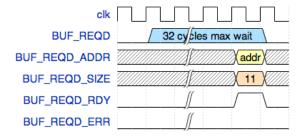

| Figure A.3. | RIFFA 1.0 timing diagram for FPGA buffer request                                                                                                                                                                                         | 148 |  |

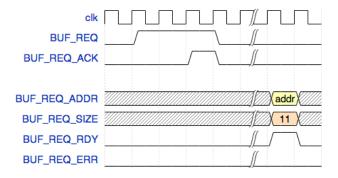

| Figure A.4. | RIFFA 1.0 timing diagram for PC buffer request                                                                                                                                                                                           | 149 |  |

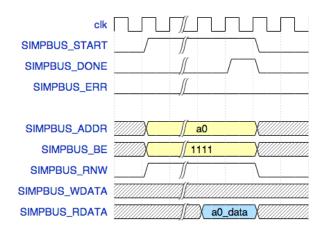

| Figure A.5. | RIFFA 1.0 timing diagram for SIMPBUS read                                                                                                                                                                                                | 150 |  |

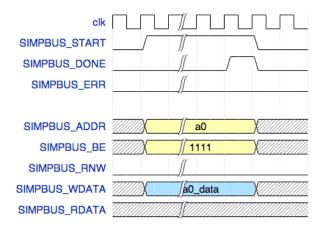

| Figure A.6. | RIFFA 1.0 timing diagram for SIMPBUS write                                                                                                                                                                                               | 151 |  |

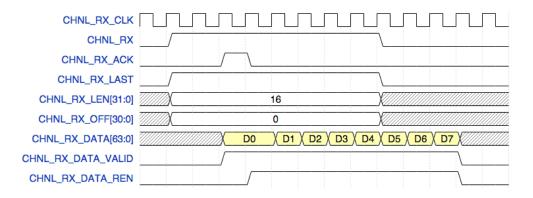

| Figure B.1. | RIFFA 2.0 timing diagram for receiving                                                                                                                                                                                                   | 174 |  |

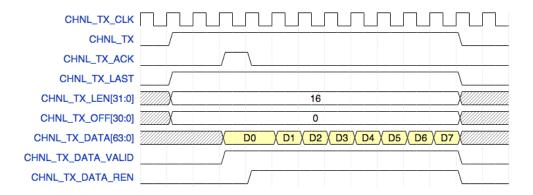

| Figure B.2. | RIFFA 2.0 timing diagram for sending                                                                                                                                                                                                     | 177 |  |

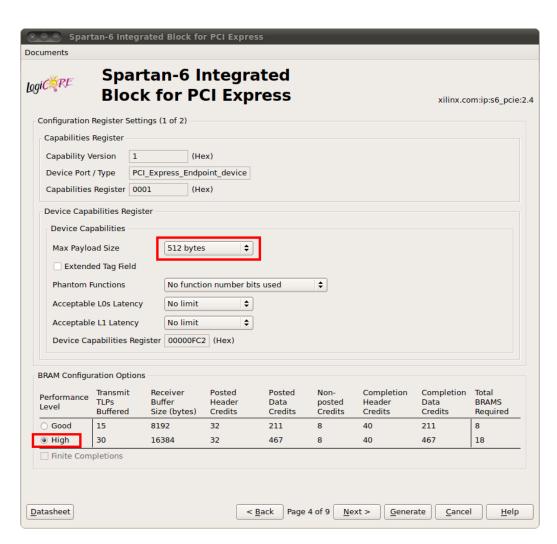

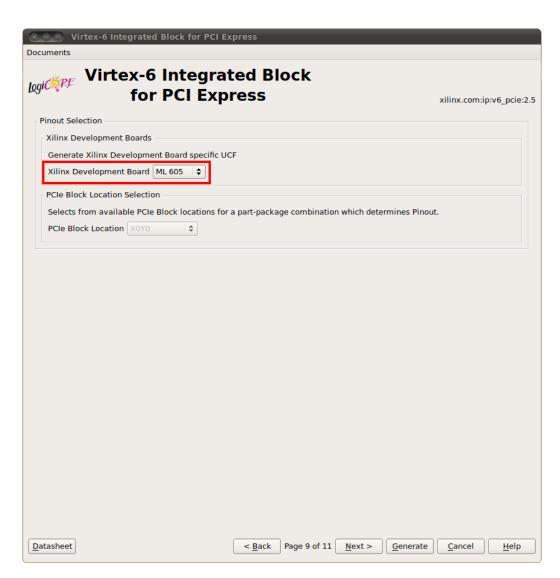

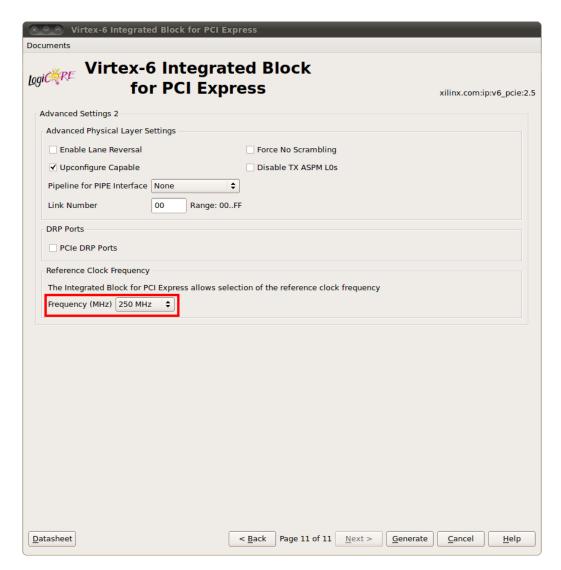

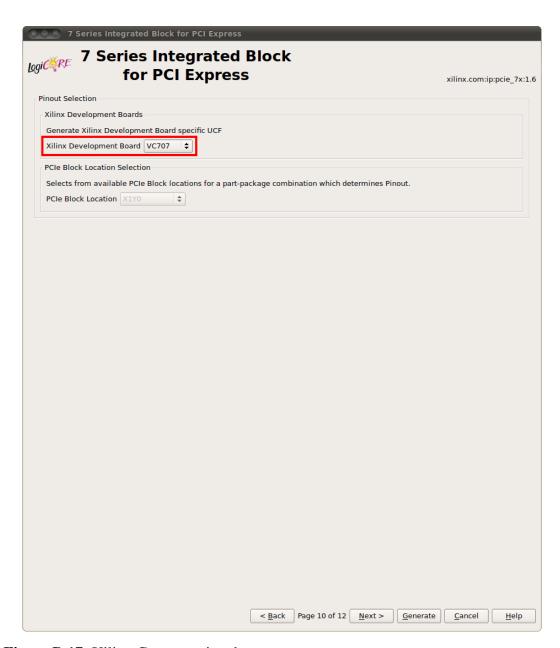

| Figure B.3. | Xilinx Coregen wizard screen.                                                                                                                                                                                                            | 203 |  |

| Figure B.4. | Xilinx Coregen wizard screen.                                                                                                                                                                                                            | 204 |  |

| Figure B.5. | Xilinx Coregen wizard screen.                                                                                                                                                                                                            | 205 |  |

| Figure B.6. | Xilinx Coregen wizard screen.                                                                                                                                                                                                            | 206 |  |

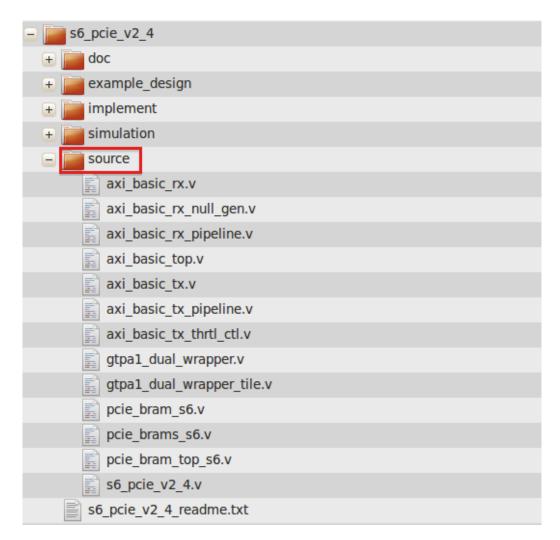

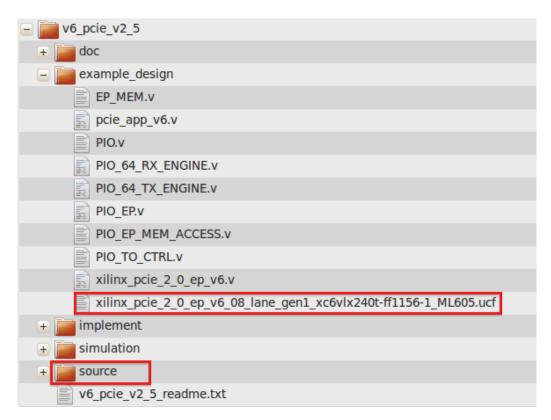

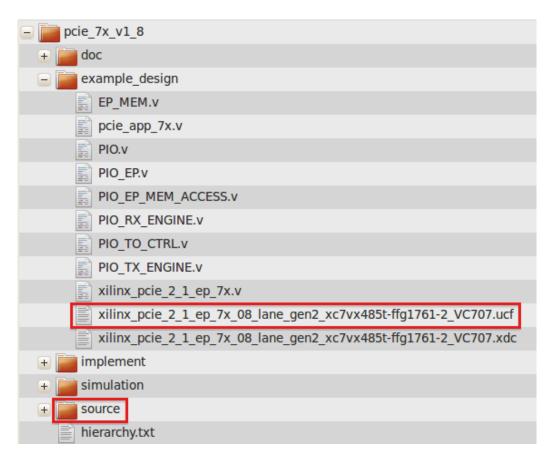

| Figure B.7. | File tree listing.                                                                                                                                                                                                                       | 207 |  |

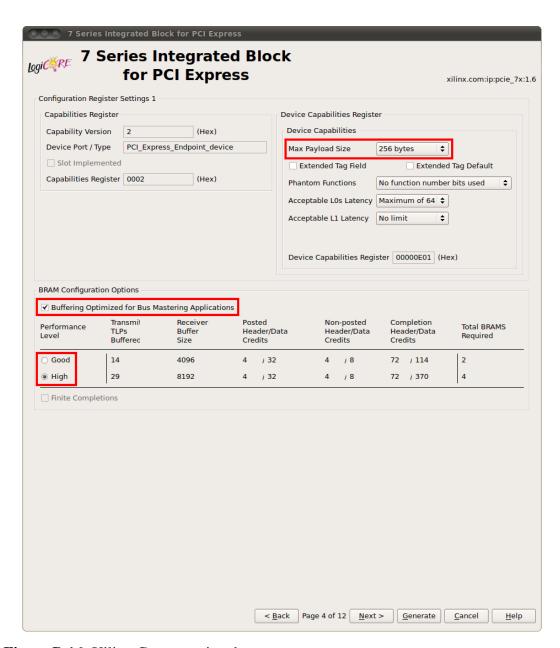

| Figure B.8. | Xilinx Coregen wizard screen.                                                                                                                                                                                                            | 210 |  |

| Figure B.9.  | Xilinx Coregen wizard screen.          | 211 |

|--------------|----------------------------------------|-----|

| Figure B.10. | Xilinx Coregen wizard screen           | 212 |

| Figure B.11. | Xilinx Coregen wizard screen           | 213 |

| Figure B.12. | Xilinx Coregen wizard screen           | 214 |

| Figure B.13. | File tree listing.                     | 215 |

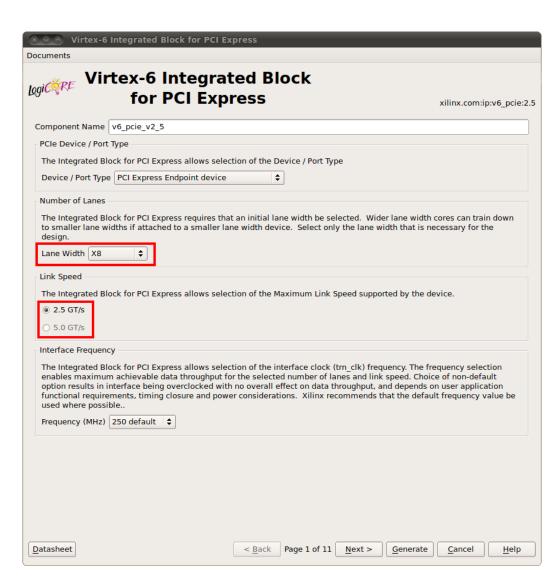

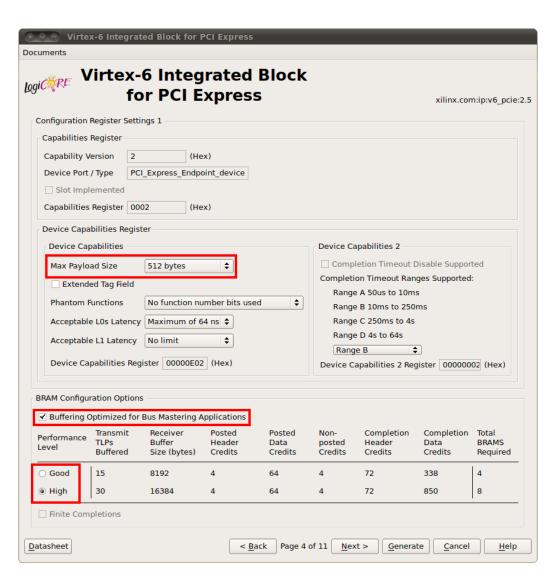

| Figure B.14. | Xilinx Coregen wizard screen           | 218 |

| Figure B.15. | Xilinx Coregen wizard screen           | 219 |

| Figure B.16. | Xilinx Coregen wizard screen           | 220 |

| Figure B.17. | Xilinx Coregen wizard screen.          | 221 |

| Figure B.18. | File tree listing.                     | 222 |

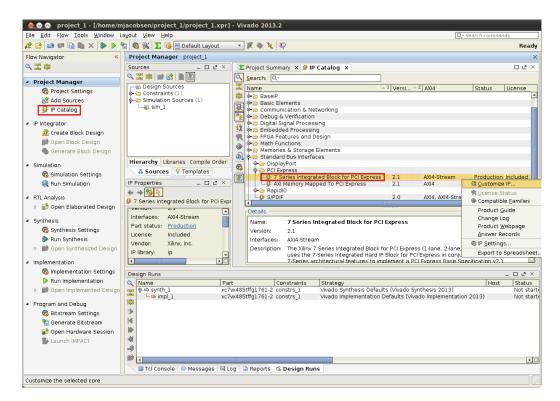

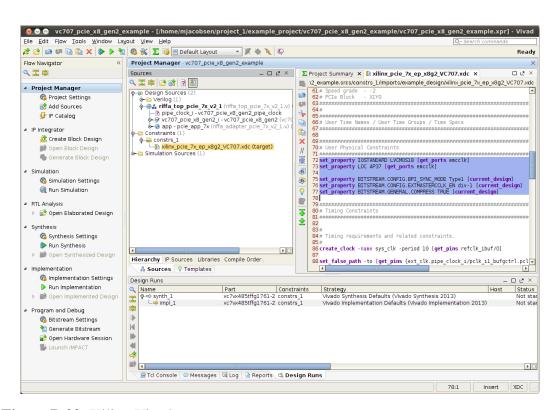

| Figure B.19. | Xilinx Vivado screen                   | 225 |

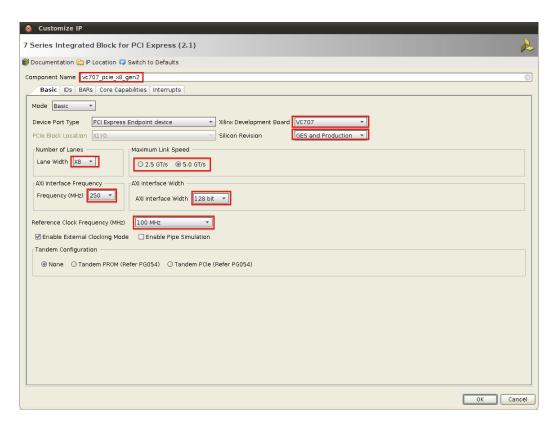

| Figure B.20. | Xilinx Vivado IP Catalog wizard screen | 226 |

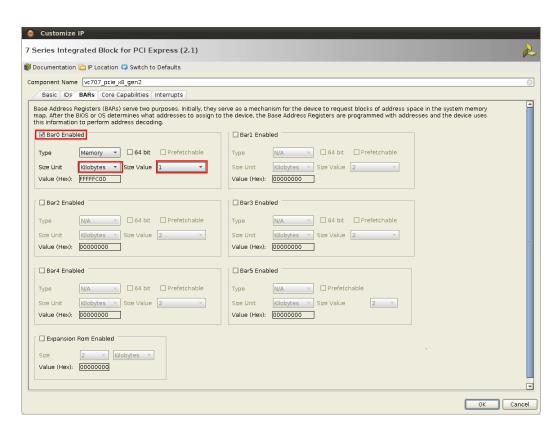

| Figure B.21. | Xilinx Vivado IP Catalog wizard screen | 227 |

| Figure B.22. | Xilinx Vivado IP Catalog wizard screen | 228 |

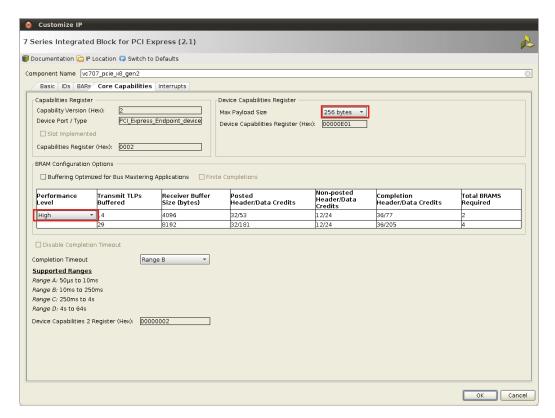

| Figure B.23. | Xilinx Vivado IP Catalog wizard dialog | 228 |

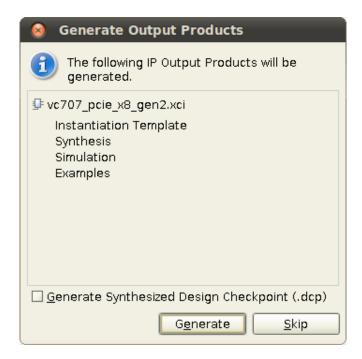

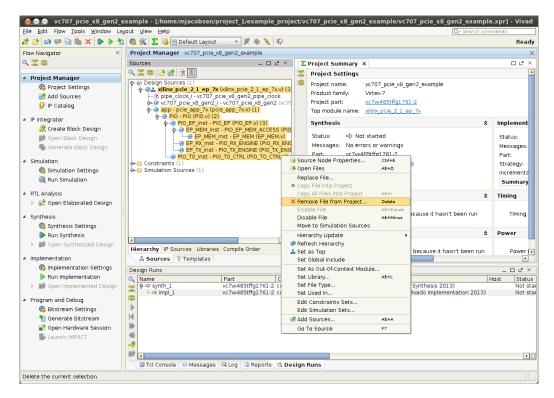

| Figure B.24. | Xilinx Vivado screen                   | 229 |

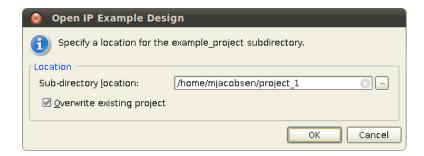

| Figure B.25. | Xilinx Vivado dialog                   | 229 |

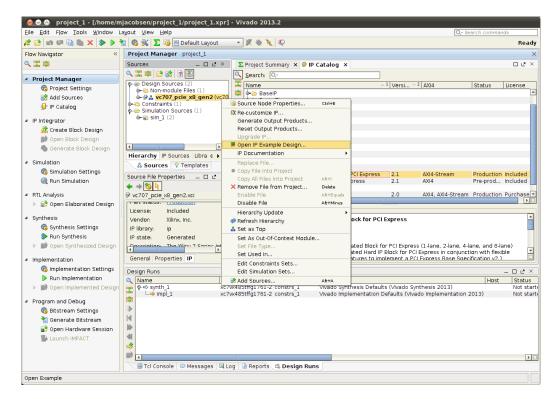

| Figure B.26. | Xilinx Vivado screen                   | 230 |

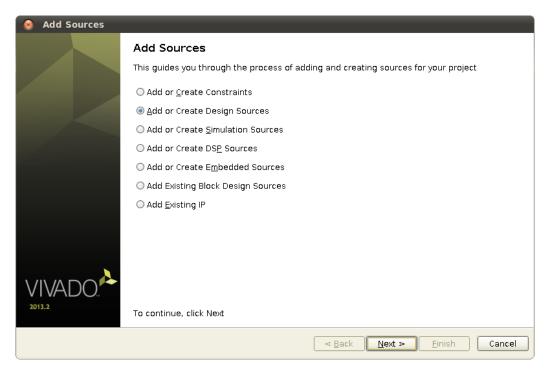

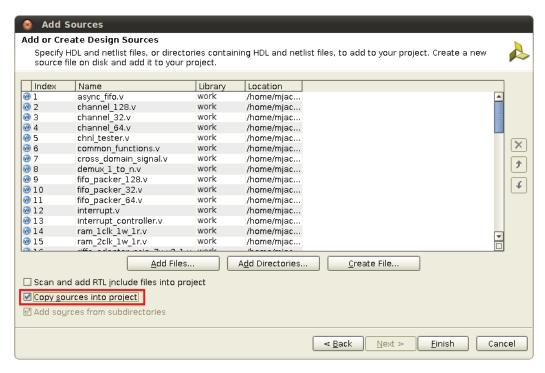

| Figure B.27. | Xilinx Vivado dialog                   | 231 |

| Figure B.28. | Xilinx Vivado dialog                   | 232 |

| Figure B.29. | Xilinx Vivado screen.                  | 233 |

## LIST OF TABLES

| Table 1.1. | Platform characterization for CPUs, GPUs, and FPGAs      |     |  |  |  |

|------------|----------------------------------------------------------|-----|--|--|--|

| Table 2.1. | RIFFA 1.0 core software functions                        | 23  |  |  |  |

| Table 2.2. | RIFFA 1.0 key latencies and bandwidths                   | 27  |  |  |  |

| Table 2.3. | RIFFA 1.0 resource utilization                           | 28  |  |  |  |

| Table 2.4. | RIFFA 2.0 software (C/C++) interface                     | 29  |  |  |  |

| Table 2.5. | RIFFA 2.0 hardware interface.                            | 32  |  |  |  |

| Table 2.6. | RIFFA 2.0 latencies                                      | 42  |  |  |  |

| Table 2.7. | RIFFA 2.0 resource utilization.                          | 44  |  |  |  |

| Table 4.1. | Tracker and related video core resource utilization      | 58  |  |  |  |

| Table 5.1. | Face detector core resource utilization.                 | 65  |  |  |  |

| Table 6.1. | Optical mapping algorithm partition decisions            | 77  |  |  |  |

| Table 7.1. | FPGA design resource and VC707 utilization               | 110 |  |  |  |

| Table 8.1. | FPGA design resource and VC707 utilization               | 133 |  |  |  |

| Table A.1. | RIFFA 1.0 hardware interface.                            | 147 |  |  |  |

| Table A.2. | RIFFA 1.0 SIMPBUS hardware interface                     | 150 |  |  |  |

| Table B.1. | RIFFA 2.0 hardware interface.                            | 175 |  |  |  |

| Table B.2. | Maximum theoretical bandwidths for PCIe 1.0 and PCIe 2.0 | 202 |  |  |  |

#### **PREFACE**

This dissertation is an original intellectual product of the author, Matthew Jacobsen. Research projects not specifically acknowledged as a collaboration are solely the result of the dissertation author.

The work described in Chapter 6 is a collaboration with Pingfan Meng. Mr. Meng was lead researcher on this project. The dissertation author's chief contributions to the project involve the FPGA design and communication framework.

The work described in Chapter 7 is a collaboration with Pingfan Meng and Siddarth Sampangi. The dissertation author was lead researcher on this project. Mr. Meng's chief contribution is the GPU design. Mr. Sampangi's chief contributions are exploration in tracking methods and error quantization.

The work described in Chapter 8 is a collaboration with Siddarth Sampangi. The dissertation author was lead researcher on this project. Mr. Sampangi's contributions are exploration in tracking methods.

### **ACKNOWLEDGEMENTS**

I would like to acknowledge Professor Ryan Kastner for his support as the chair of my committee and my research advisor. His guidance as an advisor and management style have taught me that pursuing knowledge is not only rewarding, but enjoyable as well.

I would also like to acknowledge Professor Yoav Freund for his support as my initial research advisor and committee member. He was instrumental in starting my graduate research career. Without his help, I would not have even begun my research.

Though not my advisor in any official capacity, I would like to thank committee member Professor Truong Nguyen for his help with research projects and opportunities throughout my academic pursuits. His pragmatic view of research has pushed me to achieve results that I could never have imagined.

Chapter 2 contains material as it appears in Field-Programmable Custom Computing Machines (FCCM), 2012. It also contains material as it appears in Field Programmable Logic and Applications (FPL), 2013. The dissertation author was the primary investigator and author of these papers.

Chapter 6 contains material printed in Field-Programmable Technology (FPT), 2012. The chapter also contains material that was omitted from the publication due to space constraints. The dissertation author was not the primary investigator on this paper, but is a the second author.

Chapter 7 contains material printed in Field-Programmable Custom Computing Machines (FCCM), 2014. The chapter also contains material that was omitted from the publication due to space constraints. The dissertation author was the primary investigator and author of this paper.

Chapter 8 contains material printed in Field Programmable Logic and Applications (FPL), 2014. The chapter also contains material that was omitted from the

publication due to space constraints. The dissertation author was the primary investigator and author of this paper.

#### **VITA**

| 1997      | Bachelor of Science, University of California, Berkeley                                                |  |  |

|-----------|--------------------------------------------------------------------------------------------------------|--|--|

| 2007      | Research Assistant, Department of Computer Science and Engineering University of California, San Diego |  |  |

| 2008–2011 | Teaching Assistant, Department of Computer Science and Engineering University of California, San Diego |  |  |

| 2012      | Master of Science, University of California, San Diego                                                 |  |  |

| 2012–2014 | Research Assistant, Department of Computer Science and Engineering University of California, San Diego |  |  |

| 2014      | Doctor of Philosophy, University of California, San Diego                                              |  |  |

### **PUBLICATIONS**

- "Improving FPGA Accelerated Tracking with Multiple Online Trained Classifiers" Field Programmable Logic and Applications (FPL), 2014 24th International Conference on, 2014

- "Hardware Accelerated Novel Optical De Novo Assembly for Large-Scale Genomes" Field Programmable Logic and Applications (FPL), 2014 24th International Conference on, 2014

- "FPGA Accelerated Online Boosting for Multi-Target Tracking" Field-Programmable Custom Computing Machines (FCCM), 2014 22nd IEEE Annual International Symposium on, 11 May 13 May 2014

- "RIFFA 2.0: A reusable integration framework for FPGA accelerators" Field Programmable Logic and Applications (FPL), 2013 23rd International Conference on, 2013

- "A hardware accelerated approach for imaging flow cytometry" Field Programmable Logic and Applications (FPL), 2013 23rd International Conference on, 2013

- "FPGA-GPU-CPU heterogeneous architecture for real-time cardiac physiological optical mapping" Field-Programmable Technology (FPT), 2012 International Conference on. IEEE, 2012

- "RIFFA: A reusable integration framework for FPGA accelerators" Field-Programmable Custom Computing Machines (FCCM), 2012 20th IEEE Annual International Sympo-

sium on, 29 April - 1 May 2012

"Detecting, tracking and interacting with people in a public space" In Proceedings of the 2009 international Conference on Multimodal interfaces, November 02 - 04, 2009

### FIELDS OF STUDY

Major Field: Computer Science (Computer Vision, Hardware Acceleration)

Studies in Hardware Accelerated Systems Professor Ryan Kastner

### ABSTRACT OF THE DISSERTATION

Smart Frame Grabber: A Hardware Accelerated Computer Vision Framework

by

Matthew Daniel Jacobsen

Doctor of Philosophy in Computer Science

University of California, San Diego, 2014

Professor Ryan Kastner, Chair

Real-time computer vision applications have difficult runtime constraints within which to execute. Implementing on a CPU provides a baseline for performance. But using custom parallel hardware such as graphics processing units (GPUs) and field programmable gate arrays (FPGAs) represents a cost effective method to achieve greater performance.

Greater performance can move an algorithm from non-real-time into the realm of real-time. This opens numerous possibilities for interaction that did not exist before. Tasks such as face detection can be used to set focus points in cameras if performed in

XX

real-time. Similarly, body part tracking can be used as input for consumer televisions or video game systems when run in real-time.

Acceleration using heterogeneous hardware is attractive because algorithms exhibit different models of computation at different stages of execution. Each platform can be exploited to execute when most efficient. However, it can be difficult to combine these platforms into a single application. This is due to the lack of reusable components and communication abstractions for these devices.

This work describes a framework to lower the barrier for computer vision application acceleration called the Smart Frame Grabber Framework. This framework is a collection of reusable hardware acceleration components that are commonly used for accelerating computer vision applications using CPUs and FPGAs. It allows applications to be easily partitioned across multiple heterogenous compute devices. At the heart of this framework is a communication and synchronization platform called RIFFA: A Reusable Integration Framework for FPGA Accelerators.

Using the Smart Frame Grabber Framework, researchers can design and build a hardware accelerated computer vision application in considerably less time and with less upfront effort than it would take using existing vendor provided tools alone.

## Introduction

Computer vision is the study of acquiring and analyzing images to produce information for the purpose of decision making. Many applications of computer vision have made their way into everyday life. Photo cameras perform face detection to assist automatic focus. Photo organization softwares perform face recognition within their managed collections. Home video game systems and even some televisions detect body parts using cameras and track their locations to provide touch-free interfaces. Many more applications exist in specialized fields such as autonomous vehicles, factory automation, and defense. These applications enrich lives, improve productivity, and even help protect us.

Although this field has seen many advances, there are limitations imposed by the state of the hardware upon which computer vision algorithms would run. These limitations divide the class of applications into two groups: online and offline. The combination of hardware capabilities and algorithm complexity typically make this distinction. Online applications execute quickly enough to produce results with some small amount of latency, usually a few seconds or less. Offline applications have no expectation of producing results quickly and can run for minutes, hours, or longer.

Within online applications, there is a subclass referred to as real-time. This class has the stronger requirement of running several times a second. In the context of human-computer-interaction applications, this requirement is often at least 10 times per second. This is motivated by established human biological thresholds [48, 12]. For

industrial automation this requirement can be several thousand times a second. For example, many factory production lines perform quality assurance on products as they move on conveyers at high speeds.

Regardless of the actual rate, real-time applications run quickly enough to provide decisions immediately. This immediacy makes it feasible to design systems with a feedback loop for interaction. Because the entire loop can be run in real-time, tasks that would be difficult, costly, or impossible to run offline can be achieved. For example, defective products can be dropped from the production line for repair before they are packaged and leave the factory. Similarly, humans can control input to a system sensitive enough to play music [47].

It is the class of real-time computer vision applications that is the most interesting from an interactive perspective. It is also the most challenging to run in real-time. Many algorithms that would be useful in a host of real-time applications simply cannot run fast enough on modern computers. Accelerating these algorithms using custom parallel hardware is an often successful approach for achieving real-time performance. There is however considerable effort required when using this approach. Many of the facilities provided by computers and software are not available when using custom hardware. As a result, most work in this area requires considerable investment in basic infrastructure to even begin. Moreover, the completed designs are frequently not reusable across applications. There is no common framework for hardware accelerating computer vision applications.

This dissertation describes the results of my work to remedy this situation. It describes the Smart Frame Grabber Framework, a computer vision acceleration framework that allows applications to easily leverage CPUs, field programmable gate arrays (FPGAs), and GPUs with minimal rework. This merges research from: vision, hardware acceleration, and high performance computing. It reduces the barriers to entry for accel-

erating computer vision applications with custom hardware. Lastly, it allows researchers and practitioners to focus on application logic instead of common functionality.

The rest of this document is organized as follows. Chapter 1 describes the Smart Frame Grabber Framework in detail and provides motivation. Chapter 2 describes our work in developing the RIFFA communications platform, a core component in the Smart Frame Grabber Framework. Chapters 3, 4 and 5 describe early skin color detection, tracking, and object detection applications built using the Smart Frame Grabber Framework. Chapter 6 describes an optical mapping application cardiac physiology that is partitioned across a CPU, GPU, and FPGA. It also leverages RIFFA and components in the Smart Frame Grabber Framework. Chapter 7 describes and compares two designs for hardware accelerated online boosting for tracking. One is a CPU-FPGA design, the other is a CPU-GPU design. Chapter 8 describes an algorithmic improvement to online boosting for tracking made only feasible because of the performance increase resulting from acceleration. Future directions based on our work with the Smart Frame Grabber Framework are provided in Chapter 9. Detailed descriptions of the Smart Frame Grabber components (including RIFFA) are provided in the appendices.

## Chapter 1

## **Smart Frame Grabber**

The Smart Frame Grabber Framework is a collection of reusable hardware acceleration components that are commonly used for accelerating computer vision applications using CPUs and FPGAs. Using this framework, researchers and practitioners can design and build a hardware accelerated computer vision application that easily leverages multiple heterogenous devices. In our work, we have used the framework to integrate CPUs, FPGAs, and GPUs all within the same application in considerably less time and with less upfront effort than it would take using existing vendor provided tools alone.

Algorithms exhibit different patterns of computation during execution. Some parts are highly sequential, others are completely independent and amenable to parallelization. Using multiple heterogenous devices allows each part to run on the device most efficient at that type of computation.

Consider three of the most common computation platforms used. CPUs excel at Von Neumann model sequential processing and rich programming abstractions and libraries make it the easiest platform to program. GPUs can compute two to three orders of magnitude faster than CPUs if there is sufficient independent data to process. However, GPUs are more difficult to program due to their single instruction multiple data (SIMD) execution model. Finally, FPGAs can be designed to emulate any circuit. They often perform very well when configured as stream processors because data is

**Table 1.1.** Platform characterization for CPUs, GPUs, and FPGAs.

|                   | CPU           | FPGA                  | GPU          | Smart Frame<br>Grabber |

|-------------------|---------------|-----------------------|--------------|------------------------|

| Processing units: | ~4            | ~100                  | ~1000        | ~1000                  |

| Cycle frequency:  | GHz           | MHz (low)             | MHz (high)   | GHz                    |

| Programming:      | High level    | Low level             | Medium level | Low - high level       |

| Reusable libs:    | Countless     | Few                   | Few          | Countless              |

| Dev. cycle:       | Short         | Long                  | Short        | Short                  |

| Parallelism:      | Opportunistic | Fine grain, dedicated | Massive      | Massive, dedicated     |

| Pipelining:       | Sporadic      | Fully                 | Mostly       | Fully                  |

| Scheduler:        | Dynamic       | Custom                | Dynamic      | Custom                 |

| Memory:           | Unlimited     | Small                 | Large        | Unlimited              |

| Memory latency:   | Moderate      | Low                   | High         | Low                    |

| Data access:      | Fetch         | Stream or fetch       | Fetch        | Stream or fetch        |

| Data path:        | Fixed         | Custom                | Fixed        | Custom                 |

| Computation:      | MPMD          | MPMD                  | SPMD         | MPMD                   |

| Resource growth:  | Slow          | Fast                  | Moderate     | Fast                   |

| Reconfiguration:  | Compile time  | Run time              | Compile time | Run time               |

manually scheduled and operations are typically executed by dedicated hardware. FPGA's drawback is also difficulty in programming, as compared to CPUs. Table 1.1 lists salient characteristics of these platforms.

Each platform has its strengths and weaknesses. For application acceleration purposes, it is ideal to leverage the strengths of all three platforms. This would allow one application to take advantage of the best that each platform has to offer. This is represented in the Smart Frame Grabber column of Table 1.1.

The difficulty in achieving this ideal is two fold. First, one must efficiently integrate all the devices together in one application. For this task, efficiency is paramount. Loose coupling with low bandwidth communication defeats the purpose of leveraging each device for high performance computing. The second difficulty deals with programming the devices themselves. FPGAs, for example, are difficult to program because of their low level abstractions. However when designed well, they can be extremely powerful devices. The Smart Frame Grabber Framework addresses both of these problems.

First consider application integration. Tight CPU-GPU integration has been

solved by the GPU software development kits provided by manufacturers, such as NVIDIA's CUDA SDK. However CPU-FPGA integration is not as easily accessible. This was a problem that needed to be solved, and solved in a way that was reusable and flexible enough to support multiple FPGA and mixed environment integration (e.g. CPU-GPU-FPGA). The Smart Frame Grabber Framework solves this problem. It does so while also allowing each device to be programmed independently. Any tool or language can be used to program these devices. The framework does not impose a single language or runtime environment as other solutions have. It integrates well with existing CPU based runtime libraries so that it can take advantage of other frameworks like CUDA. This helps preserve the performance characteristics of each platform and increases general applicability.

The Smart Frame Grabber Framework also helps ease the difficulty of programming these devices. In particular, FPGAs. It includes reusable components that are commonly used to perform operations in computer vision applications. These operations include: image scaling, sliding window pipelines, convolution templates, and a host of flow control modules. These components target FPGAs because they are the most challenging to program. Having a set of reusable computer vision oriented components greatly reduces the time to design and build image processing logic in FPGAs.

## 1.1 Motivation

The idea for the Smart Frame Grabber originated after designing and building several hardware accelerated vision applications. The first application was a skin color detection application. It uses a boost trained decision tree to classify image pixels as human skin. Software running on a CPU controls processing on an attached FPGA. The FPGA captures video frames from a camera, classifies the pixels in a streaming fashion, and renders the image with annotations to a monitor. The software provides parameters to

the FPGA, such as the classifier decision tree, and receives skin pixel counts for specified regions. This application is used in a game that identifies when uncovered human body parts (mostly hands and face) have entered specified regions.

The second application was also partitioned between a CPU and FPGA. It tracks multiple targets in video. Video is captured on the FPGA, processed, and the target locations are returned to the CPU. The software on the CPU updates the location and target template using a particle filter search algorithm. The cost function for each location is the sum of absolute difference between a template and the current window in the frame. This application was used to track up to 6 independent targets in multiple scales at 60 frames per second.

The next project was a hardware accelerated face detection application, again partitioned between a CPU and FPGA. By this point, it was clear that the model of computation was very similar across all these applications. For each frame, each application needed to capture video on the FPGA, transfer parameter data from the CPU to the FPGA, extract features or process image data on the FPGA, and return results to the CPU. Each application had a different set of common components that had been rebuilt several times. Clearly starting each application from scratch was inefficient. Thus the idea of the Smart Frame Grabber Framework was born.

## **1.2** Communication Component

The Smart Frame Grabber is built around a communications framework called RIFFA: A reusable integration framework for FPGA accelerators. RIFFA provides high bandwidth, low latency communication and synchronization between FPGA devices and computers equipped with a PCI Express (PCIe) connection. It provides this via simple software APIs and a FIFO hardware interface. The chief benefit of RIFFA is that it hides the complexity of transferring data over PCIe behind simple interfaces while providing

efficient use of the PCIe link.

One of the most common bottlenecks in high performance computing is moving data between computing devices. RIFFA is designed to be as efficient as possible while still providing a high level abstraction for users. Latencies are on the order of 1  $\mu$ s and transfer bandwidths between the CPU and FPGA can achieve 3.6 GB/s, which is 90% of the theoretical maximum bandwidth for the PCIe link. RIFFA isn't a substitute for on chip or even off chip local RAM as PCIe latencies are much higher than when accessing RAM. It is an interconnect between a host CPU and multiple FPGA devices so that multiple devices can be used in a single application. The current version of RIFFA supports FPGA devices from Xilinx and Altera.

RIFFA is also designed to be easily reusable. No refactoring, adjustments, or adapting is necessary between projects. Even many hardware changes are automatically accommodated. RIFFA is only dependent on the FPGA device family. It works like a reusable black box component that performs scatter gather DMA transfers. Most importantly, it does this without requiring the user learn and program a complex DMA interface.

RIFFA is an open source project. It is freely available to researchers and for non-commercial use. The open source nature of the project allows researchers to make enhancements to the architecture as well as learn from a high performing DMA design. As of this writing, RIFFA has been cited by 9 published works and has been used in projects at 14 different universities in Europe, the United States, East Asia, and India.

Documentation for RIFFA is provided in Appendices A and B. This documentation is included to provide users with a single source for RIFFA related documentation.

## **1.3** Reusable Components

There is a general lack of libraries for FPGAs when it comes to vision processing. Available solutions from vendors are often tied to expensive licenses or specific hardware. Open source components are often buggy and sporadic in terms of coverage. Solutions that leverage higher level constructs like OpenCL help alleviate this situation, but at the expense of predefined interfaces and a rigid runtime environment.

The lack of reusable FPGA libraries is not just the result of a lack of attention. Unlike CPU or GPU programming, there is no standard memory hierarchy. Therefore, data access must be scheduled manually. For efficiency reasons, data is typically streamed though a data path instead of stored in a large global memory and fetched out of order. Formulating sequential operations with random access patterns to work in this streaming manner can be complex and require considerable effort.

As an example, consider a common operation in vision processing, image resizing. On the CPU and even on the GPU, one can simply define the function necessary for bi-linear interpolation by addressing data in an array. To achieve the same on the FPGA, data must be temporarily stored in local on chip memory buffers. The interpolation function executes against local memory in a manually scheduled pipeline. At the same time, new incoming data must be captured while interpolated data is outputted. Doing these steps, while at the same time managing data flow control, is a daunting task.

Another reason FPGA libraries are not pervasive is because of the inherent difficulty in composition. Unlike software on a CPU, combining multiple FPGA modules requires care in order to meet execution timing requirements. This extra dimension forces modules to define not only what must be computed, but also how. Commonly, modules are defined to meet timing requirements when used in a specific context. But when combined with other modules in a new context, may violate these requirements. This is

due to the physical limitations of having to route signals across an FPGA device.

Lastly, reusable FPGA libraries are difficult to come by because there is no established common interface. Components are so diverse that trying to impose a common interface is untenable. High level synthesis applications, such as Xilinx Vivado HLS solve this problem by using FIFO buffers between discrete code blocks. This decouples different parts of a pipeline and produces a common interface between them. It is however inefficient and resource expensive to take this approach.

The reusable components in the Smart Frame Grabber Framework are provided as a toolbox of modules that provide several operations related to computer vision processing on FPGAs. They were developed for a specific project, but added to the framework because of their applicability to other computer vision applications. They have been written to support flow control and be used in pipelined processing. As a result, these components can be used in conjunction with modules from other designs and help reduce the amount of effort needed when building hardware accelerated computer vision applications.

The components in the Smart Frame Grabber Framework include:

- frame capture

- image scaling

- integral image transform

- sliding window processing (convolution)

- mean and variance calculation

- normalized cross correlation calculation

- Haar feature calculation

- skin color detector and generator

- color space conversion

- data buffering and flow control related modules.

The details of each component is provided in Appendix C.

## 1.4 Contributions

The primary contributions of this work are enumerated below.

### 1.4.1 Framework Contributions

These contributions relate to the Smart Frame Grabber framework, it's components and design.

### **RIFFA Scatter Gather DMA Design**

The RIFFA architecture is a high performing scatter gather DMA design over PCIe. It is capable of achieving 90% theoretical link bandwidth. It supports multiple FPGA device families and all PCIe Gen 2 configurations. It exposes a simple API in software with bindings for C/C++, Java, and Python. On the hardware side data is read and written to a FIFO interface. RIFFA supports multiple FPGAs per host CPU and can easily integrate into existing hardware and software applications.

This work has been published and is described in Chapter 2.

### **RIFFA Open Source Software**

This includes the HDL source code, Windows and Linux drivers, sample applications, installation packages, test cases, C/C++, Java, Python, and Matlab language bindings, and various configurations required for producing a packaged installable framework.

This work is available on the RIFFA website and is described in Chapter 2.

### **RIFFA Documentation**

This includes documentation provided in this dissertation as well as the RIFFA website. This is composed primarily of software API documentation, hardware interface and timing diagrams, device setup and configuration guides, and best practice guidelines.

This work is available on the RIFFA website and is documented in Appendices A and B.

### **Smart Frame Grabber Reusable Component Software**

This includes the HDL source, test cases, and documentation (provided in this dissertation and with the components).

This work documented is in Appendix C.

## **1.4.2** Application Contributions

These contributions are of accelerated computer vision applications that have been made possible by using the Smart Frame Grabber framework.

#### **FPGA Accelerated Skin Color Detection**

This work accelerates evaluation of a boosted alternating decision tree classifier. The classifier is trained to classify pixels as human skin colored. The FPGA captures frames, evaluates the classifier, and counts skin colored pixels in runtime updated regions of the frame. These values are provided to the CPU each frame at a rate of 60 frames per second.

This is early work that helped contribute to the Smart Frame Grabber framework. It is described in Chapter 3.

### **FPGA Coprocessor for Particle Filter Tracking**

This work partitions a particle filter like tracking algorithm over a CPU and FPGA. The FPGA captures video and evaluates a template based classifier for each target location within the frame. Each location samples windows from a particle distribution and returns the classification scores to the CPU. Up to 6 independent targets can be tracked concurrently at 60 frames per second using only 25 - 40% of the CPU. This represents a  $30\times$  speed up over a CPU only implementation.

This is early work that helped contribute to the Smart Frame Grabber framework. It is described in Chapter 4.

#### **FPGA Accelerated Face Detection**

This is an application of accelerated face detection using the Viola and Jones algorithm [58]. The application runs nearly all on the CPU, but image acquisition, integral image conversion, and partial classifier evaluation is performed on the FPGA. The partial evaluation results are used as a filter for the software evaluation cascade to reduce workload. The FPGA acceleration is also integrated into the highly optimized OpenCV software library. The acceleration provides a 3.16× speed up over software only.

This is early work that helped contribute to the Smart Frame Grabber framework. It is described in Chapter 5.

# FPGA-GPU-CPU Heterogenous Architecture for Real-time Cardiac Physiological Optical Mapping

This work accelerates an optical mapping application for cardiac physiology to run in real-time. Real-time in this application is 1000 frames per second. The application performs image normalization of photovoltaic optical flow video. The design leverages stream processing on a FPGA, high bandwidth GPU processing, and CPU bookkeeping

within the same application. It is able the to process video in real-time at 1024 fps with an end to end latency of 1.86 seconds. This represents a  $273 \times$  speed up over a multi-core CPU OpenMP implementation.

This work has been published and is described in Chapter 6.

### FPGA and GPU Accelerated Implementations of Online Boosting for Tracking

This work accelerates an adaptive online boosted tracking algorithm [7] using a GPU and a FPGA in two separate designs. Speed ups over the highly optimized software-only C++ implementation are 2.7× for the GPU design and 68× for the FPGA design. The FPGA design is capable of tracking 57 independent targets at 30 FPS. This is the first FPGA and GPU accelerated implementations of online boosting for tracking. This work also contributes an analysis of two hardware acceleration platforms and identifies fundamental differences that contribute to performance disparities.

This work has been published and is described in Chapter 7.

### Hardware Enabled Multiple Classifier Algorithm for Online Trained Tracking

This work describes a FPGA-CPU accelerated design for tracking objects through appearance changes, using multiple online boosted classifiers. The work presents an algorithm for learning a pool of pose-specific and tracking classifiers at runtime. It also employs a novel method for comparing multiple classifier scores using a kurtosis of the score distributions. Compared to a multi-threaded software-only CPU based implementation, the accelerated implementation boasts a  $30\times$  speed up over a highly optimized C++ implementation. This work performs at state of the art levels and shows an improvement in accuracy over existing tracking algorithms.

This work is in submission and is described in Chapter 8.

# Part I

# **Smart Frame Grabber Framework**

# Chapter 2

# RIFFA: A Reusable Integration Framework for FPGA Accelerators

### 2.1 Introduction

FPGAs and GPUs have become popular parallel computing platforms for application acceleration. Both have been successfully applied to accelerate numerous vision [42], physics [55], and other compute intensive applications [15]. They are even used in heterogenous computing environments for high performance computing [57]. Both hardware devices are capable of running highly parallel operations faster than their CPU counterparts. However, many differences exist between the hardware platforms. The focus of this paper is on the difference we feel is most critical to FPGAs continued success in application acceleration; the ability for FPGAs to easily integrate with the CPU workstation environment.

Workstation CPUs are still the dominate platform for most compute intensive applications. They are easy to program, offer considerable memory, many processing cores, and support countless software libraries. GPUs are inherently part of this environment as their primary purpose is to accelerate video rendering. The advent of OpenCL and NVIDIA's CUDA language and tool chains has made GPUs even easier to access for the purposes of general application acceleration. The literature shows a surge of applications

accelerated by GPUs since these developments. In contrast, FPGAs have not seen as much developments in accessibility.

FPGAs are flexible enough to emulate custom circuit designs and connect to virtually any device. However, this flexibility also makes it challenging to connect to virtually any device. The protocol standards that make other devices easily interoperable must be included in the FPGA's user design in order for it to interface with external devices. This can be a large obstacle to overcome for application designers. In many cases, implementing the interface logic can match or exceed the effort required for implementing the application logic. As a result, many if not most, FPGA uses involve standalone designs.

Our goal is to lower the barriers for application acceleration using FPGAs. To that end, we introduce RIFFA: A reusable integration framework for FPGA accelerators. RIFFA is an integration framework for connecting IP cores on an FPGA with software running on a computer. The framework requires a PCIe bus enabled workstation and a FPGA with a PCIe peripheral. RIFFA provides communication and synchronization capabilities with a standard interface for both software and hardware. It is comprised of Verilog IP cores, software libraries, and a device drivers. RIFFA is also open source so that researchers can focus on implementing application logic instead of basic connectivity interfaces.

In the sections that follow, we discuss previous work and existing solutions. We also present a detailed description of the RIFFA 1.0 and RIFFA 2.0 designs, example uses, and an analysis of the architecture and performance. This paper's chief contributions are:

- An open source, reusable, integration framework for multi-family FPGAs and workstations.

- An simplified hardware and software interface, offering high bandwidth, low

latency, and multi-FPGA support.

• A detailed design for PCIe based DMA bus mastering.

## 2.2 Related Work

RIFFA is not the first attempt to integrate FPGAs into traditional software environments. Many research applications exist that solve this problem. However, these solutions are typically highly customized and do not port well to other projects without considerable rework.

Industry offers many solutions for this situation. Impulse Accelerated Technologies, Pico Computing, Convey, Maxeler, and Xillybus all offer products that connect software to FPGAs via a proprietary interface. Their solutions come with software, cores, and some include their own languages, development environments, and tool chains. Many of these solutions exist to drive the purchase of the vendor's goods and services. They are not open source solutions. Nor do they allow users to use their solutions with off-the-shelf components. Moreover, they can be quite expensive. Especially compared to the price of commodity hardware.

There are freely available solutions such as OpenCPI [35] and Microsoft Research's SIRC [25]. OpenCPI is the Open Component Portability Infrastructure project designed to simplify heterogeneous computing. It supports CPUs, DSPs, FPGAs, and other real time embedded devices. As a consequence of this broad support, the setup and configuration of OpenCPI can be challenging. The interface is also overly complex for what is needed for FPGA connectivity. SIRC, a Simple Interface for Reconfigurable Computing, is a Microsoft Research project designed to connect C++ applications to FPGA cores. It is also an open source solution and has been an inspiration for RIFFA. But while SIRC is free, it is only supported on Windows. It also uses a Gigabit Ethernet

connection which limits the bandwidth between the host computer and the FPGA. RIFFA uses a PCIe link which offers more scalable performance and is better suited to integrate into workstation, supercomputing, and other high performance computing environments.

Lastly, there are a multitude of FPGA designs that include integrated CPUs. There are also approaches to simplify and allow applications to make better use of FPGA cores such as: Hthreads [51], HybridOS [43] and BORPH [10]. However these solutions utilize custom operating system kernels and often only support CPUs running on the FPGA fabric.

### 2.3 RIFFA 1.0

The initial version of RIFFA [38] is based on a set of components provided by Xilinx. It relies on a PCIe Endpoint, a PCIe Bridge, and a DMA core available in Xilinx's Embedded Development Kit. It targets Virtex 5 and Virtex 6 devices and supports a single FPGA per host PC.

#### 2.3.1 Architecture

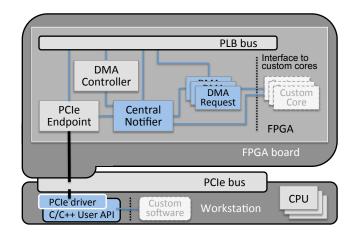

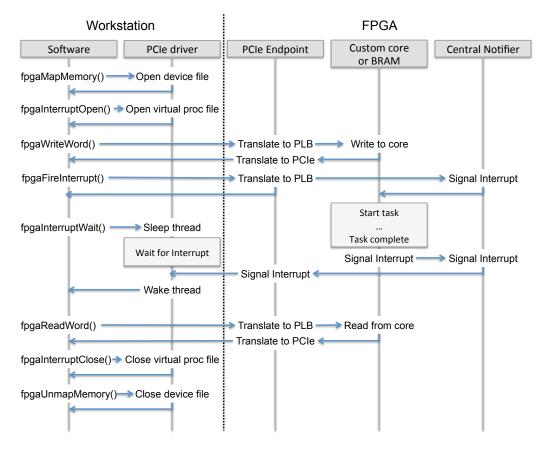

RIFFA 1.0 is a C software library and Linux device driver, on the workstation side, and set of IP cores on the FPGA side. The two are connected via a PCIe bus connection. A diagram of the RIFFA 1.0 architecture is displayed in Figure 2.1.

In designing RIFFA we sought to expose interfaces general enough for most applications, to support high communication throughput with low latency, and to be compatible with off the shelf workstations and FPGAs. For these reasons, we built our framework to use a PCIe bus. PCIe buses are common in most workstations and increasingly so in embedded systems. They offer high bandwidth connections with extremely low latency. Many FPGA boards come equipped with PCIe connections and chip makers are combining FPGAs with CPUs, connected by PCIe, in the same package

**Figure 2.1.** Architecture of RIFFA 1.0 framework. Application acceleration cores interface with the DMA Request and Central Notifier cores.

or on the same die<sup>1</sup>. We chose Linux because it is an open source platform with wide adoption and well suited for high performance application execution. Our initial version has targeted only Xilinx FPGAs. Future versions may include support for FPGAs from other vendors.

#### **Software Interface**

On the software end, we developed a PCIe Linux device driver and a set of software libraries. The device driver probes for the FPGA at boot time and assigns addresses within the workstation's PCIe address space for the PCIe Endpoint on the FPGA. During this process kernel address space is reserved for communicating with the FPGA. Once address space is assigned, the driver can access the PCIe Endpoint. In order to enable access outside of the kernel, the driver creates a virtual device file in the *dev* filesystem. This virtual device file can then be opened, read from, written to, or memory mapped by any application in user space. In this way, we expose the FPGA to user space. Accessing this virtual device file executes PCIe read or write transactions over the PCIe bus. On the FPGA, the PCIe Endpoint services these requests by translating them to

<sup>&</sup>lt;sup>1</sup>Intel ECx5C Series and Xilinx Zync platforms.

Processor Local Bus (PLB) requests via address translation. This gives applications on the workstation the ability to access individual IP cores on the FPGA using file operations or memory assignments.

To provide signaling of events, the driver establishes an interrupt channel between the workstation and PCIe Endpoint on the FPGA. Received interrupt vectors identify which IP core has signaled the interrupt. Our driver acknowledges interrupts and exposes individual interrupts by creating a set of numbered virtual files in the *proc* filesystem. When an application attempts to read or poll<sup>2</sup> any of these files, the driver returns the number of interrupts received from the corresponding IP core. If no interrupts have yet been received, the driver sleeps the calling thread and wakes it up when the appropriate interrupt is received. This design exposes many logically distinct interrupt channels using the single PCIe device interrupt in a thread efficient manner. RIFFA currently supports up to 16 interrupt channels. One drawback to this design is that interrupts must be acknowledged by the driver before another interrupt vector can be sent by the FPGA. We mitigate this problem by AND'ing pending interrupt requests on the FPGA so that a single PCIe interrupt received on the workstation can trigger multiple logical interrupt channels.

Even with a fast processor, we found that writing 32 bits of data at a time via PCIe transactions is inefficient for sending more than a few words of data. Additionally, there is no standard software facility for sending interrupts to PCIe devices from the workstation. We therefore added DMA transfer support and workstation-to-FPGA interrupts (so called "doorbells") using PCIe write transactions. Software initiated writes to a controller IP core signal the request for a DMA transfer and/or an interrupt to a specific IP core. This makes it convenient for applications to have input data DMA transferred to the appropriate IP core then have the core interrupt signaled. These IP core doorbells, manifest as line

<sup>&</sup>lt;sup>2</sup>The *poll* operation is used for asynchronous I/O.

```

void main() {