## UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Understanding the Enhanced Mobility of Solution-Processed Metal-Oxide Thin-Film Transistors Having High-k Gate Dielectrics

**Permalink** https://escholarship.org/uc/item/46g6x2v3

**Author** Zeumault, Andre

**Publication Date** 2017

Peer reviewed|Thesis/dissertation

#### Understanding the Enhanced Mobility of Solution-Processed Metal-Oxide Thin-Film Transistors Having High-k Gate Dielectrics

By

Andre Zeumault

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair Professor Sayeef Salahuddin Professor Oscar Dubon

Spring 2017

Understanding the Enhanced Mobility of Solution-Processed Metal-Oxide Thin-Film Transistors Having High-k Gate Dielectrics

> Copyright 2017 by Andre Zeumault

#### Abstract

#### Understanding the Enhanced Mobility of Solution-Processed Metal-Oxide Thin-Film Transistors Having High-k Gate Dielectrics

by

Andre Zeumault

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

Primarily used as transparent electrodes in solar-cells, more recently, physical vapor deposited (PVD) transparent conductive oxide (TCO) materials (e.g. ZnO,  $In_2O_3$  and  $SnO_2$ ) also serve as the active layer in thin-film transistor (TFT) technology for modern liquidcrystal displays. Relative to a-Si:H and organic TFTs, commercial TCO TFTs have reduced off-state leakage and higher on-state currents. Additionally, since they are transparent, they have the added potential to enable fully transparent TFTs which can potentially improve the power efficiency of existing displays.

In addition to PVD, solution-processing is an alternative route to the production of displays and other large-area electronics. The primary advantage of solution-processing is in the ability to deposit materials at reduced-temperatures on lower-cost substrates (e.g. glass, plastics, paper, metal foils) at high speeds and over large areas. The versatility offered by solution-processing is unlike any conventional deposition process making it a highly attractive emergent technology.

Unfortunately, the benefits of solution-processing are often overshadowed by a dramatic reduction in material quality relative to films produced by conventional PVD methods. Consequently, there is a need to develop methods that improve the electronic performance of solution-processed materials. Ideally, this goal can be met while maintaining relatively low processing temperatures so as to ensure compatibility with low-cost roll-compatible substrates.

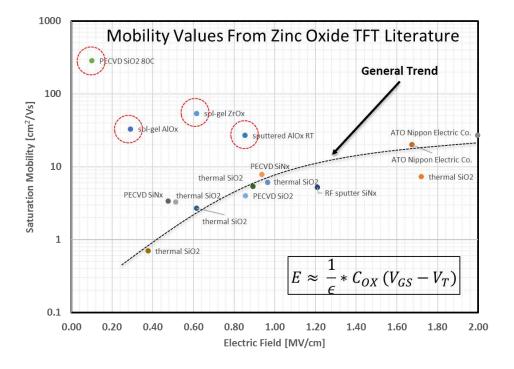

Mobility is a commonly used metric for assessing the electronic performance of semiconductors in terms of charge transport. It is commonly observed that TCO materials exhibit significantly higher field-effect mobility when used in conjunction with high-k gate dielectrics (10 to  $100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) as opposed to conventional thermally-grown SiO<sub>2</sub> (0.1 to  $20 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ). Despite the large amount of empirical data documenting this bizarre effect, its physical origin is poorly understood.

In this work, the interaction between semiconductor TCO films and high-k dielectrics is studied with the goal of developing a theory explaining the observed mobility enhancement. Electrical investigation suggests that the mobility enhancement is due to an effective doping of the TCO by the high-k dielectric, facilitated by donor-like defect states inadvertently introduced into the dielectric during processing. The effect these states have on electron transport in the TCO is assessed based on experimental data and electrostatic simulations and is found to correlate with negative aspects of TFT behavior (e.g. frequency dispersion, gate leakage, hysteresis, and poor bias stability).

Based on these findings, we demonstrate the use of an improved device structure, analogous to the concept of modulation doping, which uses the high-k dielectric film as an encapsulate, rather than a gate-dielectric, to achieve a similar doping effect. In doing so, the enhanced mobility of the TCO/high-k interface is retained while simultaneously eliminating the negative drawbacks associated with the presence of charged defects in the gate dielectrics (e.g. frequency dispersion, gate leakage, hysteresis, and poor bias stability). This demonstrates improved understanding of the role of solution-processed high-k dielectrics in field-effect devices as well as provides a practical method to overcome the performance degradation incurred through the use of low-temperature solution-processed TCOs. To my partner Shola, for being my best friend and companion especially throughout difficult times. To my mom Lori, for never losing faith in me as a youth and pushing me to excel academically. To my dad Nathaniel for teaching me, through example, quality and the meaning of hard work. To my brother Miguel for showing me persistence and dedication to my commitments. And to my curious Siberian cat Mouska for fun-filled days of laughter as well as emotional support when appropriate.

# Contents

| C  | Contents ii                                           |                                                                                                                                                                                                                                                                                                                    |                                                                                    |

|----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Li | st of                                                 | Figures                                                                                                                                                                                                                                                                                                            | iv                                                                                 |

| Li | st of                                                 | Tables                                                                                                                                                                                                                                                                                                             | x                                                                                  |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | coduction         Conventional Role of High-k Gate-Dielectrics in Field-Effect Transistors         Thin-Film Transistors         Transport in Disordered Systems         Printed Electronics for Large-Area Applications         Transparent Conductive Oxides         Method of Investigation         Composition | <b>1</b><br>1<br>3<br>6<br>13<br>13<br>16<br>17                                    |

| 2  | Qua<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                | Intifying Mobility of Disordered-Channel Thin-Film Transistors         Background                                                                                                                                                                                                                                  | <ul> <li>20</li> <li>20</li> <li>23</li> <li>29</li> <li>32</li> <li>32</li> </ul> |

| 3  |                                                       | ect of Synthetic Conditions on Density of Localized States in the TCO         nnel         Background and Introduction         Results         Discussion         Conclusion         Experimental Methods                                                                                                          | <b>37</b><br>37<br>40<br>48<br>54<br>55                                            |

| 4  | <b>Eleo</b><br>4.1<br>4.2                             | <b>ctron Donation from Donor States in High-k Gate Dielectrics</b><br>Background                                                                                                                                                                                                                                   | <b>57</b><br>57<br>60                                                              |

|              | $4.4 \\ 4.5$                                                                | Correlating $ZrO_2$ Defects to ZnO MobilityDiscussionConclusionExperimental Methods                                                                                                                                                                                                                                                                  | 62<br>66<br>68<br>68                                                                            |

|--------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 5            | <b>Diele</b><br>5.1<br>5.2<br>5.3                                           | trostatic Simulations of TCO TFTs With Donor States in the Gate         ectric         Numerical Approach          Validation of Model: General MTR Behavior          Effect of Donor-Traps in ZrO2 Dielectric          Summary and Conclusion                                                                                                       | <b>74</b><br>75<br>80<br>83<br>88                                                               |

| 6<br>7       | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Initiation Doping of TCO Channel by High-k Dielectric Encapsulation         Background and Motivation         Thin-Film Characterization of ZnO and Ga <sub>2</sub> O <sub>3</sub> /ZnO Heterostructures         TFT Characterization of ZnO and ZnO/Ga <sub>2</sub> O <sub>3</sub> Heterostructures         Conclusion         Experimental Methods | <ul> <li>93</li> <li>93</li> <li>94</li> <li>96</li> <li>98</li> <li>99</li> <li>103</li> </ul> |

|              |                                                                             | Summary of Contributions                                                                                                                                                                                                                                                                                                                             | 103<br>104                                                                                      |

| Bi           | bliog                                                                       | raphy                                                                                                                                                                                                                                                                                                                                                | 106                                                                                             |

| $\mathbf{A}$ | Quas                                                                        | si-Static Capacitance-Voltage Measurements                                                                                                                                                                                                                                                                                                           | 118                                                                                             |

| в            | Sum                                                                         | mary of Mobility Extraction Methodology                                                                                                                                                                                                                                                                                                              | 120                                                                                             |

| С            | Dens                                                                        | sity of States Extraction Method                                                                                                                                                                                                                                                                                                                     | 121                                                                                             |

| D            | D.1<br>D.2                                                                  | Ory of Spray Pyrolysis Deposition         Atomization         Transport         Decomposition                                                                                                                                                                                                                                                        | <b>123</b><br>123<br>124<br>124                                                                 |

# List of Figures

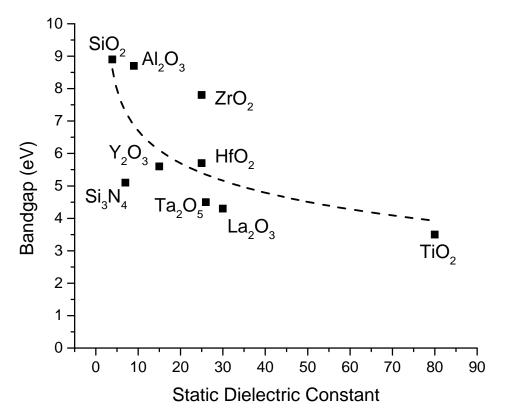

| Optical band-gap energy versus static dielectric constant for various dielectrics                                                                                                                                                                                                                    |                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| according to [91] with a logarithmic fit indicating the general trend                                                                                                                                                                                                                                | 2                                                                                                            |

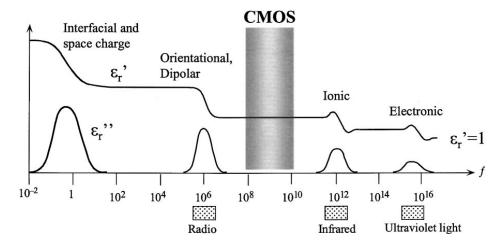

| Polarization loss mechanisms from [91].                                                                                                                                                                                                                                                              | 3                                                                                                            |

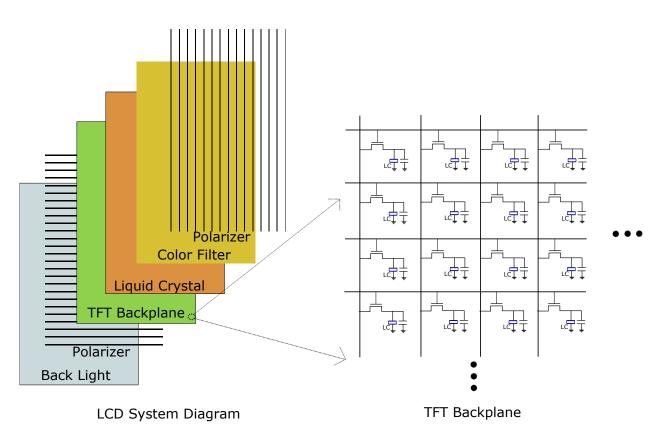

| Illustration depicting basic AMLCD system layout and TFT backplane                                                                                                                                                                                                                                   | 4                                                                                                            |

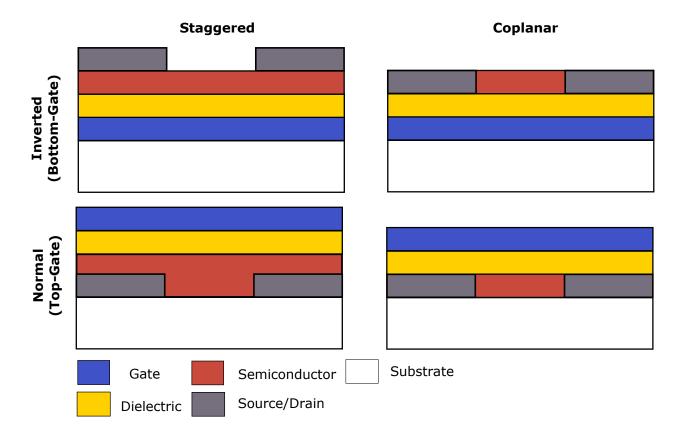

| Different types of TFT structures.                                                                                                                                                                                                                                                                   | 5                                                                                                            |

| TFT modes of operation.                                                                                                                                                                                                                                                                              | 6                                                                                                            |

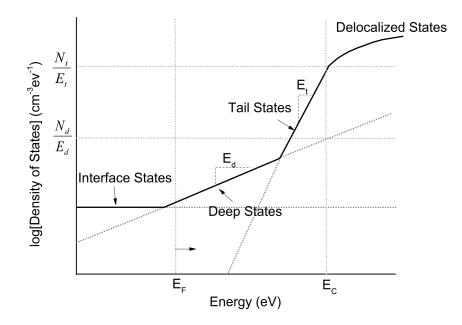

| Typical density of states for a disordered semiconductor. Band tails and deep<br>states are exponentially decreasing functions of energy, moving away from the<br>conduction band toward mid-gap. For reference, the density of states for an<br>ordered semiconductor are also shown. (dashed line) | 7                                                                                                            |

|                                                                                                                                                                                                                                                                                                      | 8                                                                                                            |

|                                                                                                                                                                                                                                                                                                      | 0                                                                                                            |

| °                                                                                                                                                                                                                                                                                                    | 12                                                                                                           |

| - •                                                                                                                                                                                                                                                                                                  | 14                                                                                                           |

|                                                                                                                                                                                                                                                                                                      | 15                                                                                                           |

| Saturation mobility values obtained from ZnO TFT literature plotted as a func-<br>tion of transverse electric field.                                                                                                                                                                                 | 17                                                                                                           |

| Typical density of states for a disordered semiconductor. Band tails and deep<br>states are exponentially decreasing functions of energy, moving away from the<br>conduction band toward midgap.                                                                                                     | 21                                                                                                           |

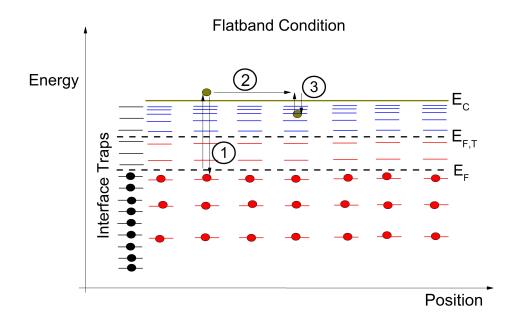

| Figure showing capture and emission processes. (1) Indicates capture and emission of deep states. (2) Indicates transport above the mobility edge. (3) Indicates                                                                                                                                     |                                                                                                              |

| capture and emission from shallow states                                                                                                                                                                                                                                                             | 23                                                                                                           |

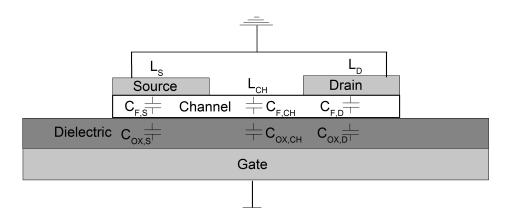

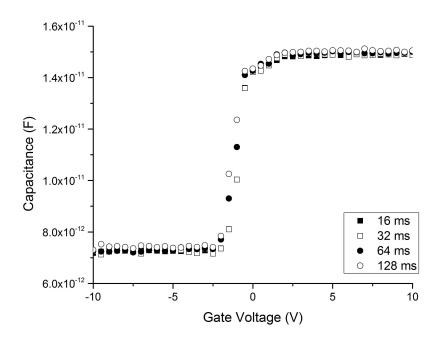

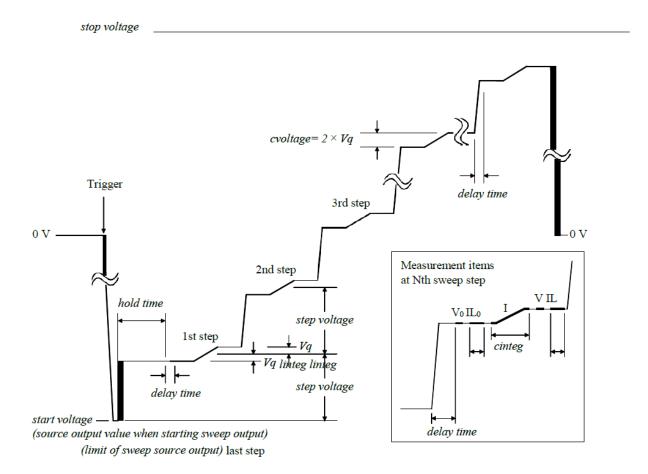

| regions determined by the source, channel, and drain geometries are indicated .<br>Quasistatic capacitance as a function of gate voltage for a ZnO TFT with 100 nm SiO <sub>2</sub> evaluated at different integration times of the charging current (16, 32, 64).                                   | 27                                                                                                           |

| and 128 ms). Amplitude applied during integration of charging current was set to 50 mV, leakage integration time used was held constant at 16 ms, corresponding                                                                                                                                      |                                                                                                              |

| to one period of the line frequency $(60 \text{ Hz})$                                                                                                                                                                                                                                                | 28                                                                                                           |

|                                                                                                                                                                                                                                                                                                      | according to [91] with a logarithmic fit indicating the general trend Polarization loss mechanisms from [91] |

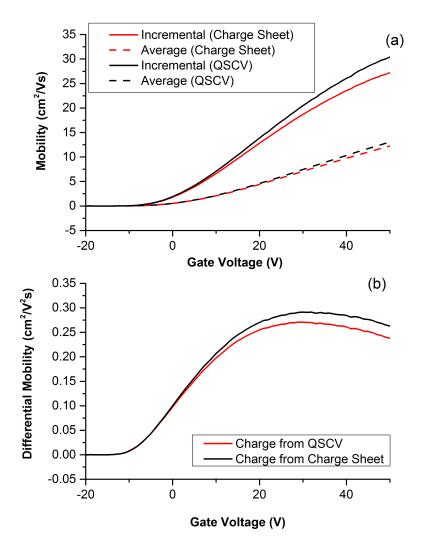

| 2.5  | Comparison of Hoffman's technique and our proposed method for high-quality ZnO TFT deposited via spray-pyrolysis at $400 ^{\circ}$ C onto $100 \text{nm SiO}_2$ . (a) Incre- |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | mental and average mobility computed using a charge obtained via the charge<br>sheet approximation and measured quasi static capacitance. (b) Differential mo-               |    |

|      | bility comparison for the charge obtained via the charge sheet approximation and                                                                                             |    |

|      | measured quasi-static capacitance                                                                                                                                            | 29 |

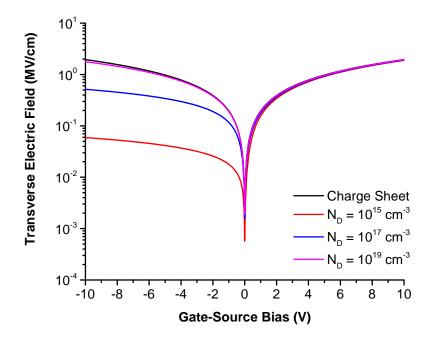

| 2.6  | Comparison of the numerically computed (Pao-Sah) and analytical (charge sheet) solution of transverse electric field for a hypothetical $\text{SnO}_2$ TFT having 20 nm of   |    |

|      | thermally-grown $SiO_2$ and a flat-band voltage of $0V$ with varying donor concentrations.                                                                                   | 20 |

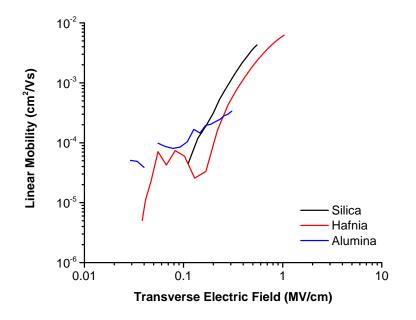

| 2.7  | Linear mobility versus the transverse electric field for identically processed mod-                                                                                          | 30 |

| 2.1  | erately annealed (400 °C) $\text{SnO}_2$ TFTs having different oxide thicknesses                                                                                             | 31 |

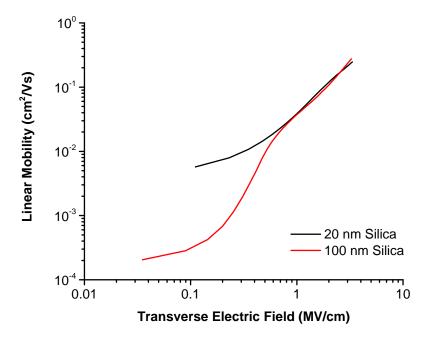

| 2.8  | Complete mobility extraction process applied to a low-temperature annealed                                                                                                   |    |

|      | (250 °C) ZnO TFT having 100 nm of thermally-grown SiO <sub>2</sub> . $V_{GS}$ was stepped from 0 to 80 V in 2 V increments. (a) Drain current vs. drain voltage at different |    |

|      | gate-source voltages. (b) Drain conductance vs. gate-source voltage extracted                                                                                                |    |

|      | from (a). (c) Gate-Source/Drain capacitance obtained via quasi-static measure-                                                                                               |    |

|      | ments. (d) Accumulation charge extracted from (c). (e) Mobility vs. gate-source voltage obtained via (b) and (d). (f) Mobility vs. transverse electric field obtained        |    |

|      | via (b) and (d) using equation (6).                                                                                                                                          | 34 |

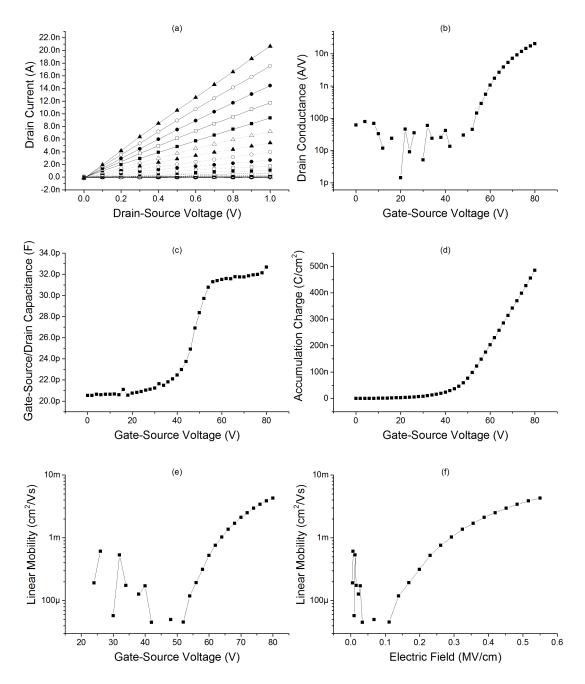

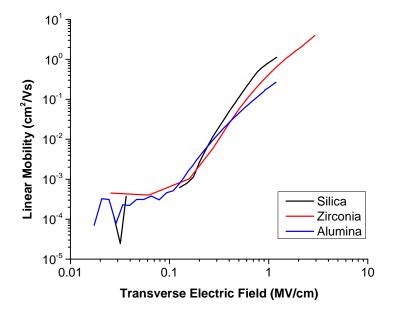

| 2.9  | Linear mobility versus empirically derived transverese electric field for moderately                                                                                         |    |

|      | annealed (400 °C) $SnO_2$ TFTs fabricated on various dielectrics                                                                                                             | 35 |

| 2.10 | Linear mobility versus empirically derived transverese electric field for low-temperatu                                                                                      |    |

| 2.11 | annealed (250 °C) ZnO TFTs fabricated on various dielectrics                                                                                                                 | 35 |

| 2.11 | $(L_{CH})$ , source electrode length $(L_S)$ , and drain electrode length $(L_D)$ used for                                                                                   |    |

|      | capacitance modeling shown in figure. Channel width (not shown) is in the z                                                                                                  |    |

|      | direction.                                                                                                                                                                   | 36 |

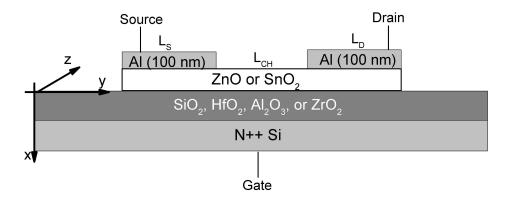

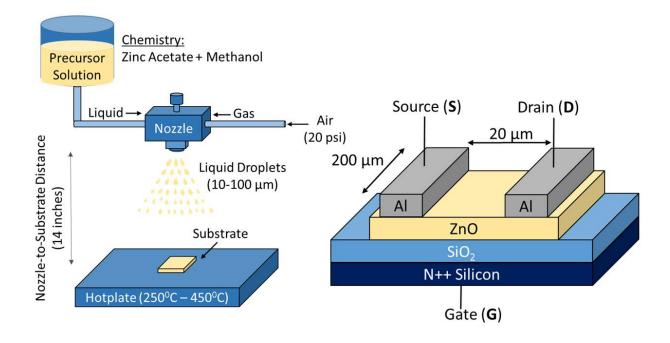

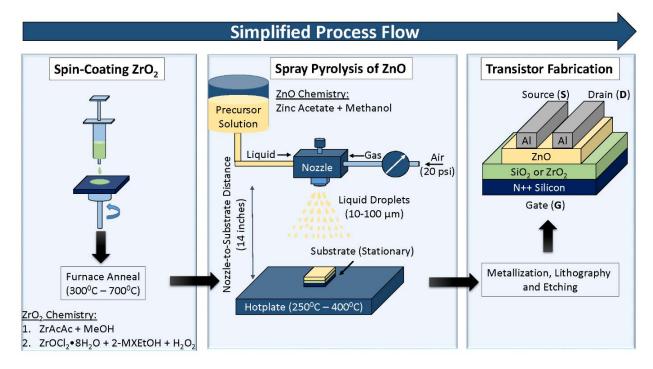

| 3.1  | Illustration showing components of spray pyrolysis setup (left) and bottom-gate                                                                                              |    |

|      | top-contact thin-film transistor structure (right)                                                                                                                           | 39 |

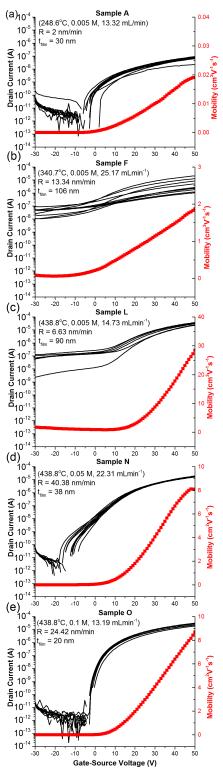

| 3.2  | (a)-(e) Transfer characteristics and linear mobility ( $V_{DS} = 0.1$ V) for each sample                                                                                     |    |

|      | measured in a $N_2$ environment at room temperature. Data for 10 devices is shown<br>in each case. Deposition parameters, including derived film growth rate and final       |    |

|      | film thickness are indicated for each condition.                                                                                                                             | 41 |

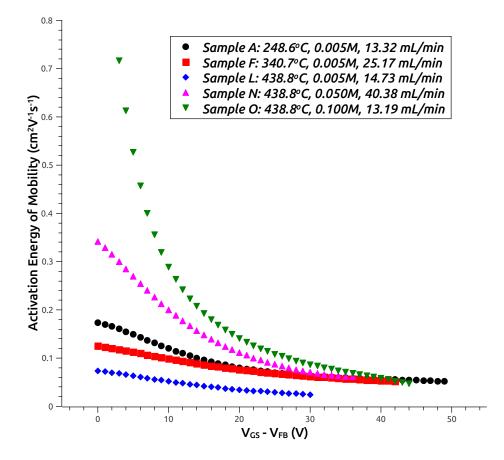

| 3.3  | Activation energy as a function of gate-source voltage above flatband for each                                                                                               |    |

|      | sample condition.                                                                                                                                                            | 42 |

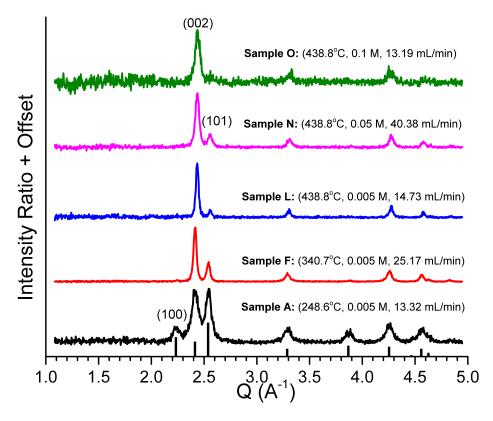

| 3.4  | Grazing incidence x-ray diffraction data for each sample condition. Reference                                                                                                |    |

|      | data shown corresponding to PDF Card 00-036-1451                                                                                                                             | 43 |

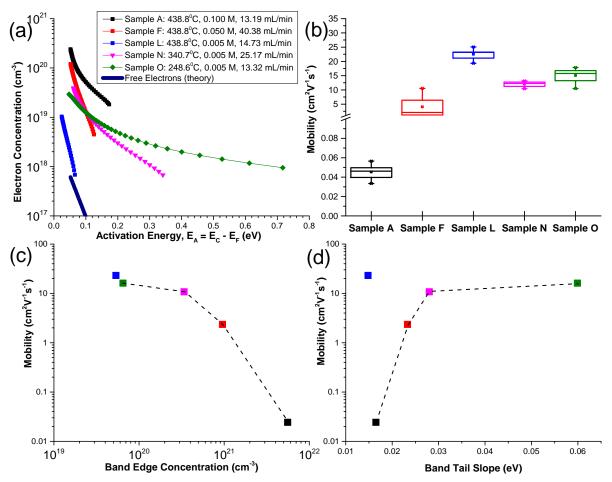

| 3.5  | (a) Extracted localized carrier concentrations as a function of energy below the conduction band edge. (b) Box-and-whisker plot summary of mobility for the                 |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | various sample conditions investigated. (c) Mobility as a function of extracted band tail concentration. (d) Mobility as a function of extracted band tail slope.           | 46 |

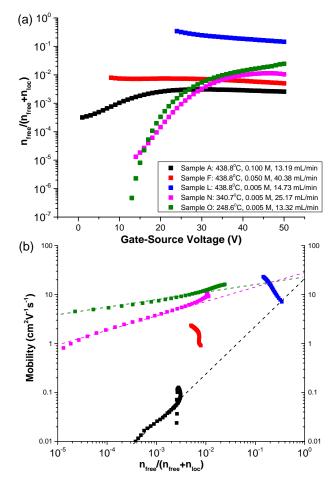

| 3.6  | (a) Fraction of free carrier concentration to total carrier concentration as a func-<br>tion of gate-source voltage. (b) Mobility as a function of fraction of free carrier |    |

|      | concentration to total carrier concentration.                                                                                                                               | 48 |

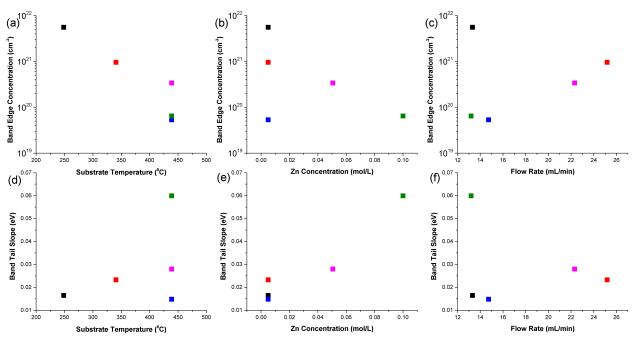

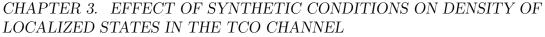

| 3.7  | (a)-(c) Influence of substrate temperature, zinc concentration and flow rate on band edge concentration and (d)-(f) band tail slope                                         | 49 |

| 3.8  | Contour plots of band tail slope (a)-(c), and band edge concentration (d)-(f) as a function of spray deposition parameters.                                                 | 50 |

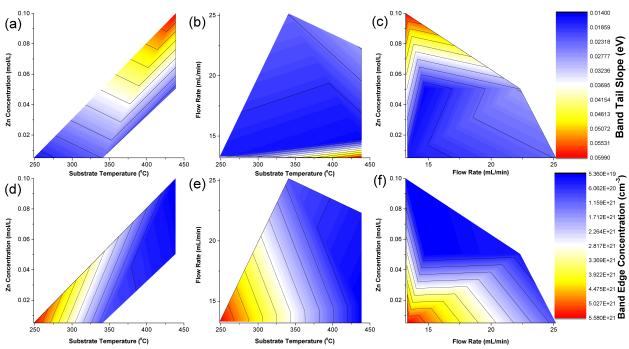

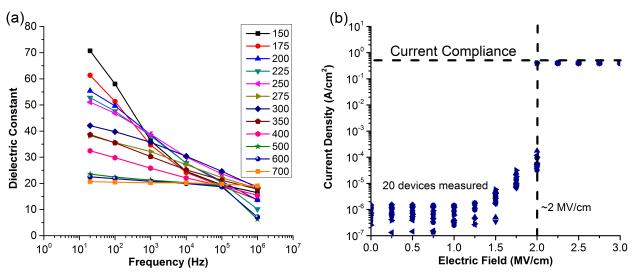

| 3.9  | (a) Grazing-incidence x-ray diffraction (GIXD) data and (b) linear mobility as a                                                                                            |    |

| 3.10 | function of $(101)/(002)$ ratio of integrated peak areas                                                                                                                    | 51 |

|      | carrier density.                                                                                                                                                            | 52 |

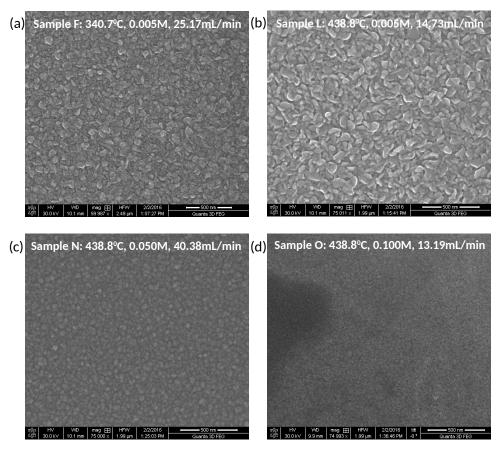

| 3.11 | X-ray photoelectron spectroscopy results of the oxygen 1s peak for (a) Sample                                                                                               |    |

|      | A, (b) Sample F, (c) Sample L, (d) Sample N and (e) Sample O. In each case,                                                                                                 |    |

|      | the raw data is shown in red. Fits for the metal-oxide (O-M) and hydroxide (O-H) contributions are also shown in green and brown along with the resulting                   |    |

|      | estimated contributions from each species by percentage area                                                                                                                | 53 |

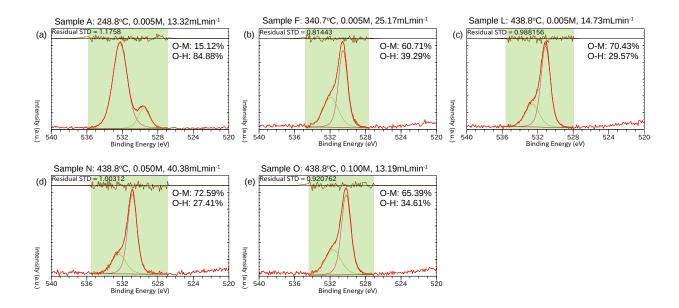

| 3.12 | (a) Mobility as a function of hydroxide content. (b) Contour plot of mobility versus hydroxide content and extent of texture, as indicated by percent OH ob-                |    |

|      | tained from $O(1s)$ peak analysis and integrated peak ratios $(101)/(002)$ from GIXD respectively.                                                                          | 54 |

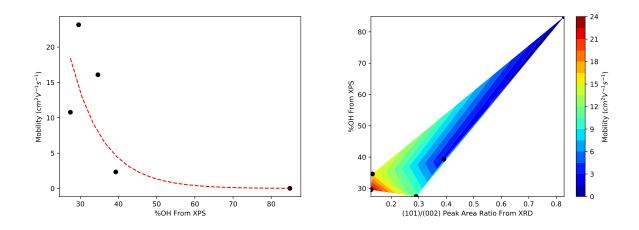

| 4.1  | Electrical data for $ZrO_2$ thin-film capacitors (N++ Si/ZrO <sub>2</sub> /Al) processed using                                                                              |    |

|      | a chemistry composed of zirconium acetylacetonate dissolved in methanol. (a)                                                                                                |    |

|      | Dielectric constant of $ZrO_2$ films as a function of frequency with annealing temperature as a parameter varied from 150 °C to 700 °C. (b) Current density as a            |    |

|      | function of electric field for 20 different devices in total                                                                                                                | 61 |

| 4.2  | Process flow and depiction of spray pyrolysis setup as well as completed bottom-                                                                                            |    |

| 4.0  | gate, top-contact thin-film transistor (TFT) structure.                                                                                                                     | 62 |

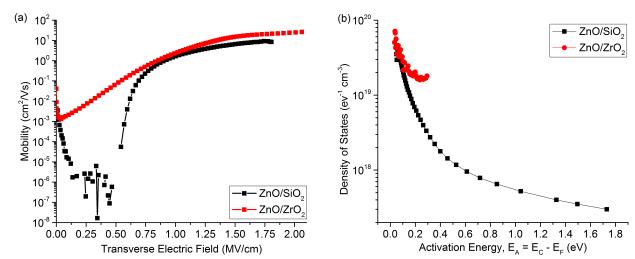

| 4.3  | Comparison of electrical data for ZnO films deposited via spray pyrolysis onto thermally group $SiO_{i}$ and $ZrO_{i}$ films (700 °C) processed using a chemistry com-      |    |

|      | thermally grown $SiO_2$ and $ZrO_2$ films (700 °C) processed using a chemistry composed of zirconium acetylacetonate dissolved in methanol deposited at 400 °C.             |    |

|      | (a) Mobility as a function of transverse electric field. (b) Density of states as a                                                                                         |    |

|      | function of activation energy                                                                                                                                               | 63 |

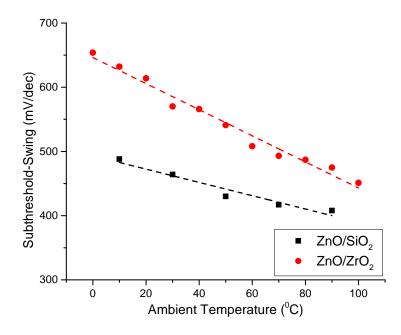

| 4.4  | Subthreshold swing as a function of temperature for ZnO TFTs having $SiO_2$ and                                                                                             |    |

|      | $\operatorname{ZrO}_2$ dielectrics                                                                                                                                          | 64 |

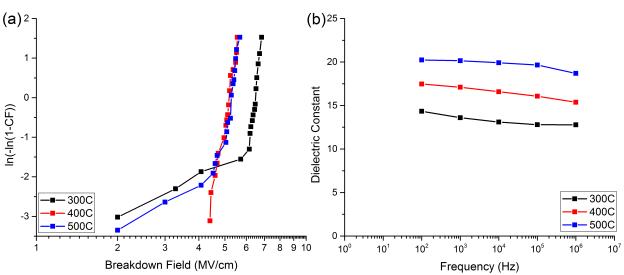

| 4.5  | Electrical data for $\text{ZrO}_2$ thin-film capacitors (N++ Si/ $\text{ZrO}_2/\text{Al}$ ) processed using<br>a chemistry composed of zirconyl chloride dissolved in 2-methoxyethanol and 4<br>molar equivalents of H <sub>2</sub> O <sub>2</sub> . (a) Statistical (Weibull) plot of dielectric breakdown<br>field measured for more than 20 devices each. (b) Dielectric constant of ZrO <sub>2</sub> films<br>as a function of frequency with annealing temperature as a parameter varied from<br>300 °C to 500 °C.                                                                                                                                                                 | 65       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

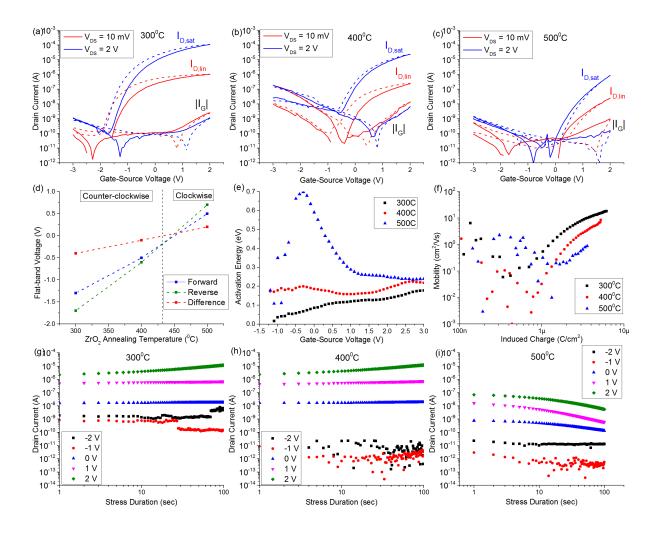

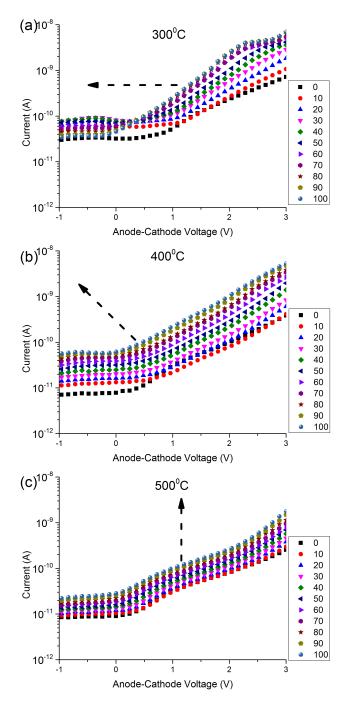

| 4.6  | Comparison of electrical data for ZnO films deposited via spray pyrolysis at 250 °C onto spin-coated ZrO <sub>2</sub> films annealed at various temperatures (300 °C to 500 °C) processed using a chemistry composed of zirconyl chloride dissolved in 2-methoxyethanol and hydrogen peroxide. (a) - (c) Drain current as a function of gate voltage. (d) Flatband voltage versus ZrO <sub>2</sub> annealing temperature. (e) Activation energy of drain conductance as a function of gate voltage evaluated between 0-100 °C under flow of N <sub>2</sub> . (f) Mobility as a function of induced charge density extracted from integration of capacitance data (not shown). (g) - (i) | 00       |

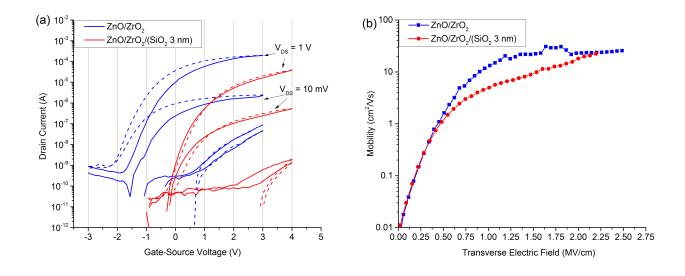

| 4.7  | Drain current as a function of stress duration for different gate-source voltages<br>Comparison of electrical data for ZnO films deposited via spray pyrolysis at 250 °C onto spin-coated $ZrO_2$ films annealed at 300 °C with and without a thin electron blocking layer of SiO <sub>2</sub> (3 nm). (a) Drain current versus gate-source voltage. (b)                                                                                                                                                                                                                                                                                                                                | 70       |

| 4.8  | Mobility versus transverse electric field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>72 |

| 4.9  | ture, (c) 500 °C annealing temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12       |

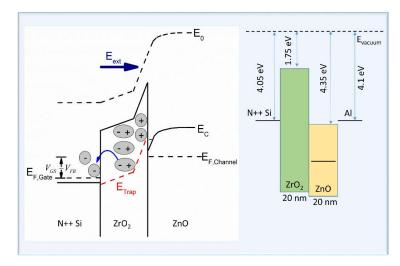

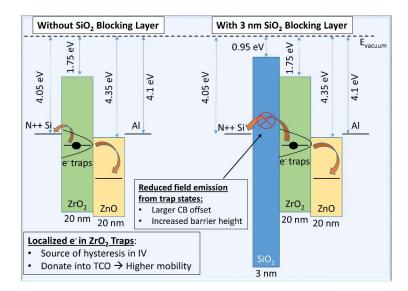

| 4.10 | formation. Band diagram before equilibrium interface formation (right)<br>Illustration of the effect of the thin blocking layer of $SiO_2$ reducing electron in-<br>jection into the gate electrode. The $SiO_2$ layer effectively prevents emission from<br>trap states within the $ZrO_2$ which otherwise lend themselves towards counter-<br>clockwise hysteresis. The trapped electrons donate to the ZnO during interface<br>formation, resulting in higher mobility.                                                                                                                                                                                                              | 73<br>73 |

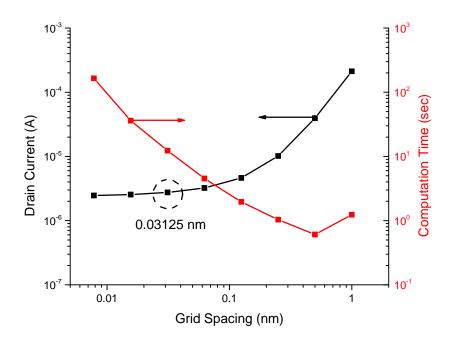

| 5.1  | Drain current and computation time versus grid spacing. Parameters describing the localized states used in this simulation were: $N_{tt} = 100N_c$ , $N_{td} = N_c$ , $E_{tt} = 0.05 \text{ eV}$ , $E_{td} = 0.5 \text{ eV}$ . Data point corresponding to a grid spacing of 0.031 25 nm                                                                                                                                                                                                                                                                                                                                                                                                |          |

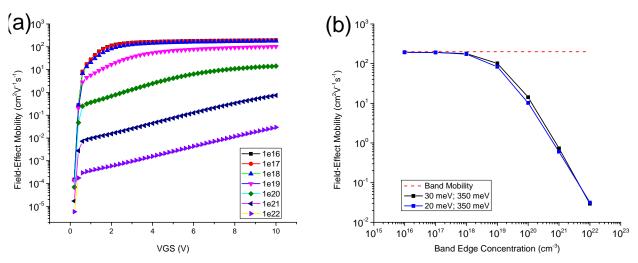

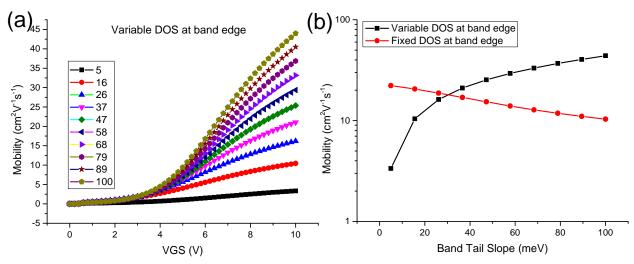

| 5.2  | <ul><li>was used throughout this work.</li><li>(a) Mobility versus gate-source voltage with band edge concentration as a parameter (b) Maximum mobility versus band edge concentration for two different band tail slopes.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81<br>82 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 04       |

| 5.3  | (a) Field-effect mobility plotted as a function of gate-source voltage with band<br>tail slope as a parameter. The density of states at the band edge was allowed to<br>vary. (b) Field-effect mobility plotted as a function of band tail slope assuming<br>either that the total density of states at the band edge is fixed (red) or variable |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.4  | as defined (black)                                                                                                                                                                                                                                                                                                                               | 83       |

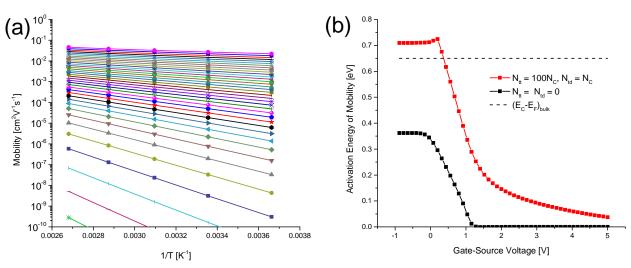

|      | of mobility as a function of gate-source voltage for the case of with (red) and without (black) traps $(N_{tt} = 100N_c, N_{td} = N_c)$                                                                                                                                                                                                          | 84       |

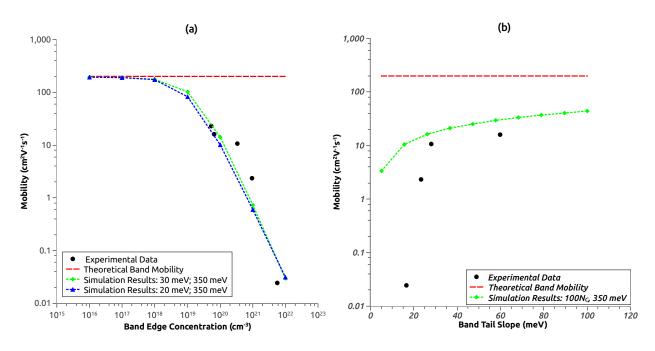

| 5.5  | Comparison of experimental mobility and simulated mobility. (a) Maximum mo-<br>bility versus band edge concentration. (b) Maximum mobility versus band tail<br>slope $(N_{tt} = 100N_c, N_{td} = N_c)$                                                                                                                                           | 95       |

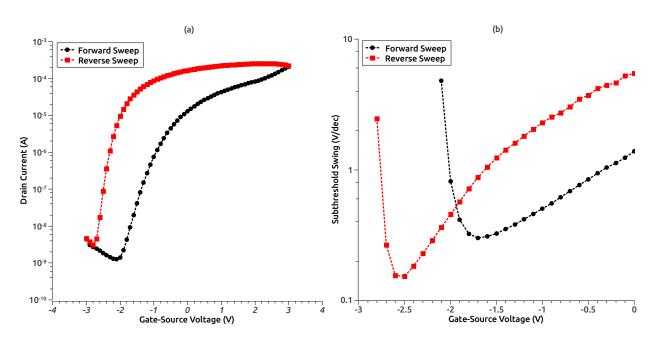

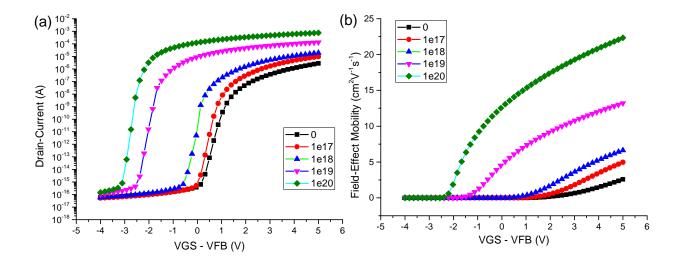

| 5.6  | (a) Drain current and (b) field-effect mobility computed for different donor ioniza-<br>tion energies for a spatially-uniform discrete in energy trap located in the $ZrO_2$ .                                                                                                                                                                   | 85       |

| 5.7  | The donor concentration used was $10^{20}$ cm <sup>-3</sup>                                                                                                                                                                                                                                                                                      | 86       |

| 5.8  | TFT in order to illustrate donor-trap behavior. A reduction in the sub-threshold<br>swing on the reverse sweep due to donor ionization is clearly shown                                                                                                                                                                                          | 87       |

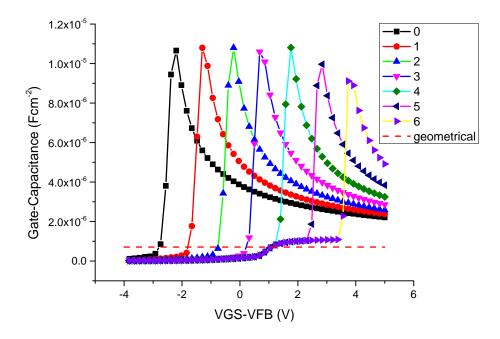

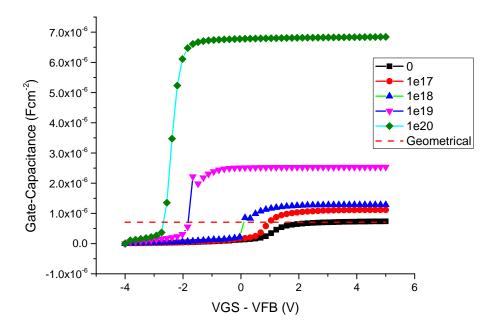

| 5.0  | Gate capacitance for different donor ionization energies for a spatially-uniform discrete in energy trap located in the $ZrO_2$ . The donor concentration used was $10^{20} \text{ cm}^{-3} \dots \dots$                                   | 88       |

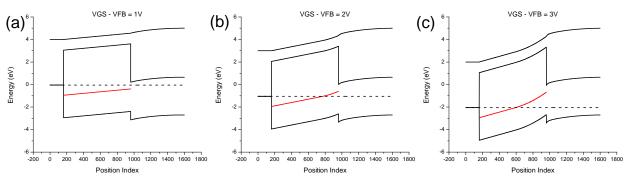

| 5.9  | Energy band diagram indicating donor level (red) relative to bands (black) at different voltages (a) $V_{GS} - V_{FB} = 1V$ , (b) $V_{GS} - V_{FB} = 2V$ and (c) $V_{GS} - V_{FB} = 3V$ . The donor ionization energy and concentration was set to 4 eV and $10^{19}$ cm <sup>-3</sup>                                                           |          |

|      | sv. The donor ionization energy and concentration was set to 4 eV and 10° cm respectively.                                                                                                                                                                                                                                                       | 89       |

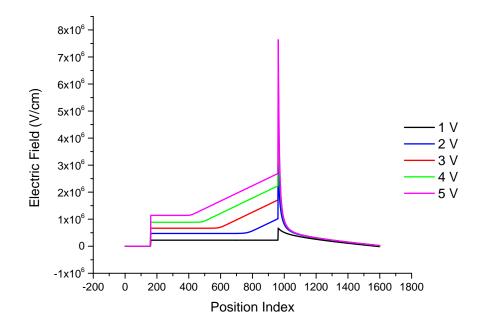

| 5.10 | Electric field for different voltages. The donor ionization energy and concentration was set to $4 \text{ eV}$ and $10^{19} \text{ cm}^{-3}$ respectively.                                                                                                                                                                                       | 90       |

|      | (a) Drain current and (b) field-effect mobility computed for different donor con-<br>centrations $(10^{17} \text{ cm}^{-3} \text{ eV}^{-1} \text{ to } 10^{20} \text{ cm}^{-3} \text{ eV}^{-1})$ for a spatially-uniform continuous                                                                                                              |          |

|      | in energy trap located in the $\text{ZrO}_2$                                                                                                                                                                                                                                                                                                     | 90       |

| 5.12 |                                                                                                                                                                                                                                                                                                                                                  |          |

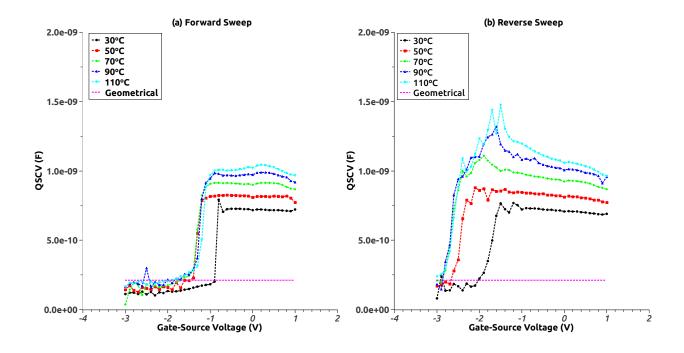

| 5.13 | for a spatially-uniform continuous in energy trap located in the $\text{ZrO}_2$<br>Measured quasi-static capacitance in the (a) forward direction and (b) reverse<br>direction as a function of temperature for a $\text{ZnO}/\text{ZrO}_2$ TFT                                                                                                  | 91<br>92 |

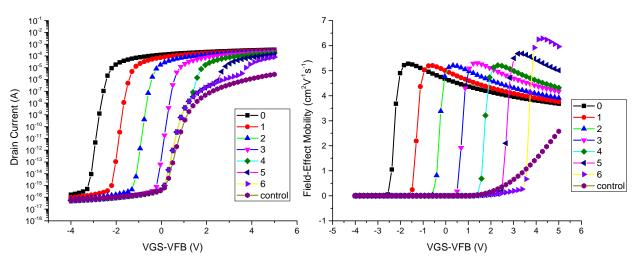

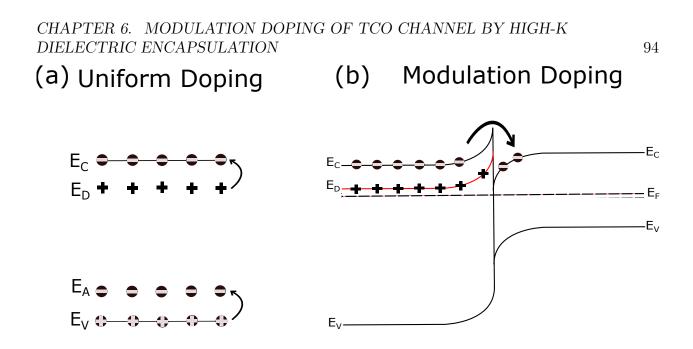

| 6.1  | Illustration showing the distinction between traditional (uniform doping) and                                                                                                                                                                                                                                                                    |          |

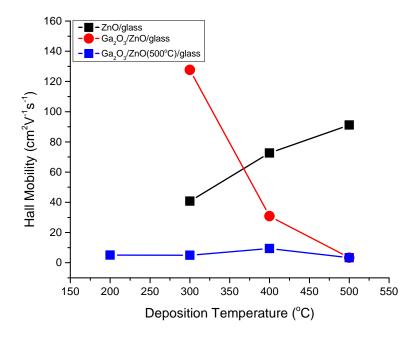

| 6.2  | modulation doping $\ldots$                                                                                                                                                                                                                                      | 94       |

| 6.3  | using a 1 T permanent magnet. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ Work function of Ga <sub>2</sub> O <sub>3</sub> and ZnO films obtained via Kelvin Probe in air at a                                                                                                                                                 | 96       |

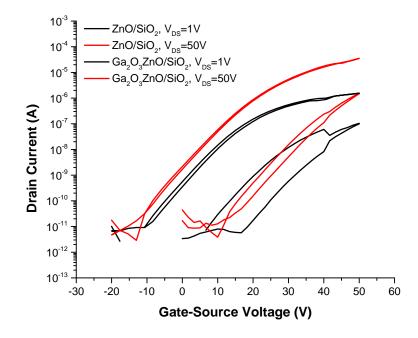

| 6.4  | relative humidity of 45 percent. $\ldots$                                                                                                                                                                                                                       | 97<br>98 |

|      |                                                                                                                                                                                                                                                                                                                                                  |          |

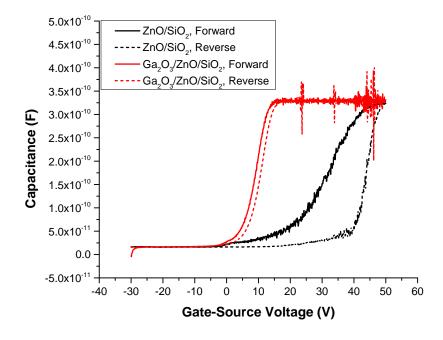

| 6.5 | Quasi-static capacitance-voltage curves of $ZnO$ and $ZnO/Ga_2O_3$ films as a func-                       |

|-----|-----------------------------------------------------------------------------------------------------------|

|     | tion of gate-source voltage showing reduction in hysteresis and improvement in                            |

|     | switching characteristics                                                                                 |

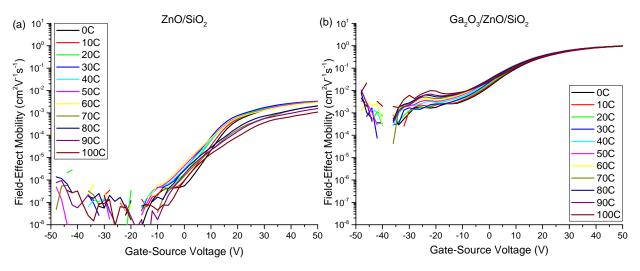

| 6.6 | Field-effect mobility of ZnO and $ZnO/Ga_2O_3$ films as a function of gate-source                         |

|     | voltage measured at different temperatures in a $N_2$ environment from 0 °C to 100 °C.100                 |

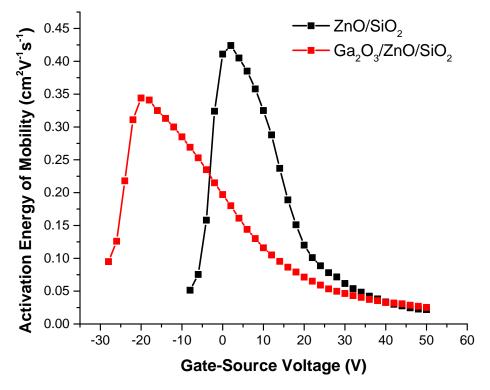

| 6.7 | Activation energy of field-effect mobility of ZnO and ZnO/Ga <sub>2</sub> O <sub>3</sub> films as a func- |

|     | tion of gate-source voltage                                                                               |

| A.1 | Figure reprinted from chapter 4 of the Agilent 4155C/4156C User's Guide Vol.2,                            |

|     | Edition 5                                                                                                 |

# List of Tables

3.1 Summary of grain size, flat-band carrier concentration, activation energy and grain boundary barrier heights computed from Seto's model for each sample assuming a dielectric constant of 10 for ZnO corresponding to the (002) orientation. Broadening factor assumed was 0.9. X-ray wavelength was 1.540 56 Å. . . . . . . 44

### Acknowledgments

Numerous individuals influenced this work in a positive way and deserve acknowledgment.

I am indebtedly grateful to my advisor, whose trust in my potential early on enabled me the opportunity to pursue my academic interests and whose guidance, through many challenging discussions, helped to polish and refine my understanding of solid-state devices from both a practical and theoretical point of view.

I am thankful for the positive interactions I've had with my fellow lab-mates over the years: Dan Soltman, Teymor "Tim" Bakshishev, Huai Yuan "Michael" Tseng, Lakshmi Jagannathan, Feng Pan, Hongki Kang, Eung Seok Park, Kyle Braam, Jaewon Jang, Rungrot "Jack" Kitsomboonloha, Sarah Swisher, Jake Sadie, Gerd Grau, Muhammed "Rumi" Ahosan Ul Karim, Jeremy Smith, Nishita Deka, Seungjun Chung, Will Scheideler, Carlos Biaou, Matt McPhail, Raj Kumar, Jacob Sporrer and Dwipayan Patnaik.

I am particularly thankful for Steve Volkman, for his wisdom and guidance through difficult times, kindness and generosity (particularly regarding coffee and beer) and a healthy skepticism and criticism (for just about every theory I proposed) which helped to establish rigor in my work. I am very grateful to have had the pleasure of working with and learning from Rungrot Kitsombolooha as an undergraduate, whose admirable work ethic and intelligence is something I still strive towards. I am thankful to Jacob Sadie for his innumerable self-less acts of service towards the lab. I am thankful to Jaewon Jang (now Professor Jang), whose initial observations in the  $SnO_2/ZrO_2$  system helped to motivate interest in this work.

I would like to thank the users, technicians and staff in the Marvell Nanofabrication Laboratory as well as the Stanford Nanofabrication Facility and Stanford Nanocharacterization Laboratory, for providing access, training, assistance and maintenance of all of the tools needed for fabrication and characterization used throughout this work.

I am grateful to Professor Sayeef Salahuddin and his students who have always been helpful in facilitating insightful theoretical discussions as well as selflessly providing assistance and resources for particular measurements.

I am thankful for the machine shop in Cory Hall at UC Berkeley for assistance with facilities and for the quality manufacturing of equipment that I used for my experimental setup.

Lastly, I am thankful for the contributions given by the Semiconductor Research Corporation, BASF and SanDisk, who provided funding and/or facilities space that contributed towards the completion of this work.

## Chapter 1

## Introduction

## 1.1 Conventional Role of High-k Gate-Dielectrics in Field-Effect Transistors

Transistor design seeks to maximize the response of the gate-induced charge in the semiconductor channel. The ability to modulate semiconductor charge is ultimately limited by the electronic properties of the gate-dielectric. Ideally, it is desirable to have gate-dielectrics with high permittivity, low loss and high breakdown fields. Unfortunately, a truly ideal gate-dielectric possessing all of these properties does not exist due to a combination of physical trade-offs and limitations. For example, materials which are good insulators (i.e. large band gaps) tend to have low dielectric constants (Figure 1.1, page 2). Furthermore, defect formation is unavoidable, leading to additional conduction pathways that enhance losses. Consequently, gate-dielectric optimization is a sensitive component of transistor design.

Historically, aggressive scaling of physical dimensions of transistors has necessitated the use of high-permittivity (i.e. "high-k") dielectrics in high-performance electronics in order to lower operating voltages and increase current density. However, frequency-dependent loss mechanisms lead to loss of electric polarization, ultimately limiting the ability to maintain high dielectric constants at high operating frequencies 1.2. These include [91]:

- 1. Ionic motion, charge trapping and space charge formation (10<sup>-2</sup> to 10<sup>2</sup> Hz; 10<sup>-17</sup> to  $10^{-13}$ eV)

- 2. Rotation of molecular dipoles ( $10^5$  to  $10^7$  Hz;  $10^{-10}$  to  $10^{-8}$ eV)

- 3. Relaxation of molecular dipoles  $(10^{11} \text{ to } 10^{13} \text{ Hz}; 10^{-4} \text{ to } 10^{-2} \text{eV})$

- 4. Electronic relaxation  $(10^{15} \text{ to } 10^{16} \text{ Hz}; 1-10 \text{ eV})$

Furthermore, high-k dielectrics routinely exhibit non-ideal insulating behavior. Apart from their characteristically high-permittivity, their integration into transistors has been

Figure 1.1: Optical band-gap energy versus static dielectric constant for various dielectrics according to [91] with a logarithmic fit indicating the general trend.

complicated by their tendency to contain various charged defects such as fixed charges, interface traps, bulk traps and mobile ions. [54] The effect this has on silicon MOSFETs is well studied and is often characterized by hysteresis in the transfer characteristics, bias/temperature instability and/or a degradation in field-effect mobility due to remote charge scattering [43].

Emergent transistor technologies based on solution-processed semiconductor materials face similar challenges when incorporating high-k gate dielectrics [94]. However, due to fundamental differences in the nature of transport in ordered (i.e. band-like) and disordered semiconductors (i.e. hopping), the interaction between the defect states of the semiconductor and dielectric do not lead to observations consistent with conventional transistor behavior [92].

Figure 1.2: Polarization loss mechanisms from [91].

## **1.2** Thin-Film Transistors

#### Historical Precedence of TFTs

Thin-film transistors (TFT) offer reduced-cost transistor functionality on unconventional substrates (e.g. glass, plastic and metal foils) for applications where the use of monolithic single-crystalline silicon MOSFETs is either unavailable or unfeasible due to cost or processing restrictions. Unlike conventional MOSFETs, the semiconductor channel in a TFT is deposited, leading towards the formation of amorphous or polycrystalline thin-films [58]. The higher degree of structural disorder present within these films leads to electronic defects that play a decisive role in transistor switching and electronic transport [42]. It is common for TFTs to exhibit low-mobility and threshold voltage instability due to a combination of high concentrations of defects, slow-electronic relaxation and lower energy barriers to defect creation [39]. For these reasons, TFTs have been largely limited to low-performance applications whereby a minimal switching delay is not a critical transistor specification. Although the predominant industrial application of TFTs is in liquid-crystal displays (LCD), they are also used in medical imagers, non-LCD flat panels, imagers/scanners/printers, photo-transistors and chemical sensors [46, 47, 42].

Higher performance (i.e. higher mobility) channel materials for TFTs tend to be polycrystalline (e.g. II-VI materials or polysilicon). A sufficiently high channel mobility, although unnecessary for LCD pixel switching, is desirable since it allows drive-circuitry to be integrated on the TFT backplane using the same transistor technology. Despite a higher mobility, polycrystalline materials have the unfortunate drawback of grain-boundaries distributed somewhat randomly over the backplane that sharply impact electrical behavior and display uniformity over large-areas [47]. Predicting the number and location of grain boundaries is a difficult task for device modeling. Consequently, the electrical properties of polycrystalline materials tend to vary over large areas. Alternatively, amorphous materials do not

Figure 1.3: Illustration depicting basic AMLCD system layout and TFT backplane

contain grain boundaries and are therefore more desirable for large-area TFT applications (e.g. displays). Historically, active-matrix liquid crystal display (AMLCD) applications have focused almost exclusively on amorphous silicon for the TFT backplane (Figure 1.3, page 4) although, in recent years, amorphous InGaZnO has emerged as a superior alternative [36].

#### Transistor Structure and the Gradual Channel Approximation

TFTs come in four possible device configurations depending on the placement of the gate electrode and source/drain contacts relative to each other: staggered, inverted-staggered, coplanar and inverted-coplanar (Figure 1.4, page 5). Coplanar devices have the semiconductor and source/drain contacts adjacent to the same side of the gate dielectric. Alternatively, staggered devices only have the semiconductor in contact to the gate dielectric. The term inverted refers to the placement of the gate electrode (top = normal, bottom = inverted).

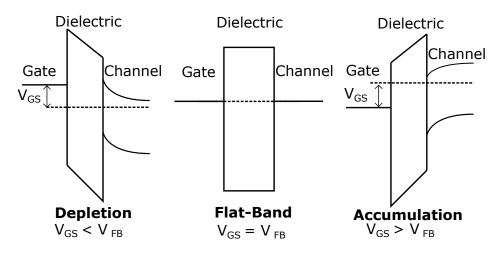

TFT operation can be qualitatively described in an analogous way to that of a MOSFET operating only in accumulation and depletion (Figure 1.5, page 6). Inversion is unlikely due to the combination of large band-gaps and the high concentrations of compensating defect states near the band edge of the majority type [87]. Consequently, metal oxide TFTs have

Figure 1.4: Different types of TFT structures.

almost exclusively unipolar transport with electrostatics essentially governed by one carrier type.

In a TFT, the *on* state corresponds to accumulation, when the majority carrier type is more abundant at the surface than the bulk. Conversely, the *off* state corresponds to depletion, when the majority carrier type is less abundant at the surface than the bulk. In practice, the channel material in a TFT is usually made very thin in order to optimize gate-control and charge-modulation. As a result, it is often convenient to approximately describe the channel in the limiting cases as being either fully-accumulated while *on* or fully-depleted while *off*.

A first order theoretical model of transport in a TFT is based on Shockley's analysis of JFETs [78] and is referred to today as the gradual channel approximation (GCA). This model assumes that the electrostatics are one-dimensional, controlled primarily by the application of a gate field. In this sense, the model is identical to simple long-channel MOSFET models where the threshold voltage has been replaced by the flatband voltage to account for accumulation-mode operation. The application of a non-zero drain-to-source voltage causes the local potential in the channel to vary between the source potential at the source and

Figure 1.5: TFT modes of operation.

the drain potential at the drain. Assuming that the dielectric is ideal and the mobility is constant, integration of the charge along the channel leads to the well-known square-law model:

$$Q_{ind}(x) = C_{ox} \left( V_{GS} - V_{FB} - \phi(x) \right)$$

(1.1)

$$I_D = W \mu_n Q_{ind} \frac{d\phi(x)}{dx} \tag{1.2}$$

$$\int_{x=0}^{x=L} I_D dx = W \mu_n C_{ox} \int_{\phi=0}^{\phi=V_{DS}} \left( V_{GS} - V_{FB} - \phi(x) \right) d\phi$$

(1.3)

$$I_{D} = \frac{W}{L} \mu_{n} C_{ox} \Big( V_{GS} - V_{FB} - \frac{V_{DS}}{2} \Big) V_{DS}$$

(1.4)

As shown in the next section, the quantitative failures of the overly simplistic square-law model stems primarily from its assumptions related to the channel mobility which is assumed to be a constant material parameter. Improved accuracy can be obtained by accounting for defects in the channel using a more appropriate transport formalisms for highly defective (i.e. disordered) semiconductors.

## **1.3** Transport in Disordered Systems

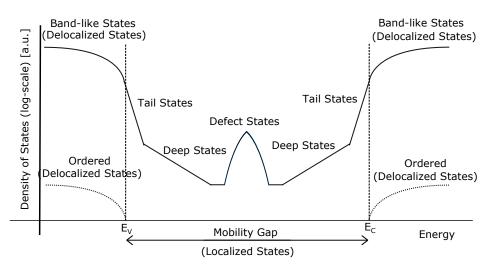

Unlike well-ordered crystalline materials, electronic transport in disordered semiconductors is not exclusively due delocalized states (i.e. band-like) but also includes contributions from localized states distributed below the conduction band. With regard to field-effect devices, the presence of such states (Figure 1.6, page 7) causes the semiconductor channel to accumulate charge via the gradual filling of trap states. These states are broadly distributed in energy, and transport can occur within a wide range of energy levels depending on the degree of orbital overlap. This ultimately leads to what is known as **dispersive transport**, as opposed to **gaussian transport** observed in ordered semiconductors 1.8. For these reasons, the device physics of TFTs differs substantially from that of conventional silicon MOSFETs. Square-law models derived from simple theories (e.g. the gradual channel approximation) developed for well-ordered silicon provide a qualitative, but quantitatively inaccurate, description of TFT behavior.

Figure 1.6: Typical density of states for a disordered semiconductor. Band tails and deep states are exponentially decreasing functions of energy, moving away from the conduction band toward mid-gap. For reference, the density of states for an ordered semiconductor are also shown. (dashed line)

Experimentally, dispersive transport is most commonly studied opto-electronically through time-of-flight or transient photoconductivity measurements [30] or electrically through measurements of thermally-activated conduction [12]. Observation of thermally-activated conduction provides a more fundamental distinction between the transport mechanism of ordered systems  $\left(\frac{\partial \mu}{\partial T} < 0\right)$  and disordered systems  $\left(\frac{\partial \mu}{\partial T} > 0\right)$ . Models describing thermally-activated conduction in disordered solids include percolation conduction [81], hopping [25], barrierlowering [77] and multiple-trap-and-release (aka trap-limited conduction) [50].

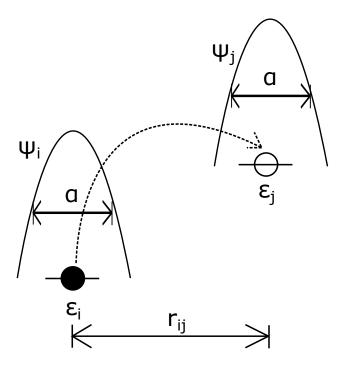

#### Hopping Conduction Between Localized States

Hopping conduction consists of a sequence of incoherent electronic transitions occurring between pairs of localized states separated in energy and/or space (Figure 1.7, page 8) [4]. Since each transition is incoherent, the electron is described as randomly "hopping" between spatially distributed localized states.

Figure 1.7: Illustration of hopping process.

The transition rate between a state at energy  $\epsilon_i$  to a state at energy  $\epsilon_j$ , separated by a distance  $r_{ij}$  is given by the following, which is essentially a Fermi's Golden Rule expression with a Bolztmann factor based on the principle of detailed balance:

$$\nu_{ij}(r_{ij},\epsilon_i,\epsilon_j) = \nu_0 e^{-\frac{2r_{ij}}{\alpha}} e^{-\frac{\epsilon_i - \epsilon_j + |\epsilon_i - \epsilon_j|}{2k_B T}}$$

(1.5)

The parameter  $\alpha$  describes the spatial extent of the wave-function corresponding to the localized state and is referred to as the localization length. As localization length increases, the wave-function extends farther radially outward becoming more spatially delocalized. Conversely, as the localization length reduces, the wave-function becomes sharply peaked about its center, overlapping less with neighboring states and therefore becoming more spatially localized.

For semiconductor devices with contacts, it is necessary to include the effect of the Fermi level on the occupation probabilities of states  $\epsilon_i$  and  $\epsilon_j$ . Taking the Fermi level into account, yields the following:

$$\nu_{ij}(r_{ij},\epsilon_i,\epsilon_j) = \nu_0 e^{-\frac{2r_{ij}}{\alpha}} e^{-\frac{|\epsilon_i - \epsilon_F| + |\epsilon_j - \epsilon_F| + |\epsilon_j - \epsilon_i|}{2k_B T}}$$

(1.6)

In order to arrive at an expression for the conductivity, the transition rate is optimized by considering the spatial coordinate as well as energy. However, simplifying assumptions based on temperature are usually made. At high temperatures, the energy difference between defect states is non-limiting since carriers can easily absorb energy from phonons present in higher concentrations. Instead, spatial separation is limiting. As a consequence, the transition rate is maximized for transitions occurring over very short distances (i.e.  $r_{ij} \rightarrow 0$ ). This is referred to as nearest-neighbor hopping (NNH). Due to the larger thermal energy, only information regarding the spatial distribution of defect states is necessary. Typically, defects are assumed to be spatially distributed at random, estimated within a sphere of radius  $R_c$ to be some constant value  $B_c$  as determined by percolation theory:

$$\frac{4\pi}{3}N_t R_c^3 = B_c \tag{1.7}$$

$$\nu = \nu_0 e^{-2\left(\frac{B_c}{\frac{4}{3}\pi\alpha^3 N_t}\right)^3} \tag{1.8}$$

Conversely, at lower temperatures, the energy difference between states is a larger fraction of the available average thermal energy  $(1.5k_BT)$ . As a result, the transition rate is maximized for transitions requiring energy much less than the thermal energy, which may involve larger spatial separations. This is referred to as variable-range hopping (VRH). Here, knowledge of the density of states in the vicinity of the Fermi energy is needed in order to express the transition rate:

$$g(\epsilon_F)\Delta\epsilon r^3(\Delta\epsilon) = 1 \tag{1.9}$$

$$\nu = \nu_0 e^{-\frac{2}{g(\epsilon_F)\Delta\epsilon\alpha^3} - \frac{\Delta\epsilon}{k_B T}} \tag{1.10}$$

The final expression for the transition rate is obtained by maximizing the above expression as a function of the energy separation  $\Delta \epsilon$ .

$$\frac{d\nu}{d\Delta\epsilon} = 0 \tag{1.11}$$

$$\Delta \epsilon = \left(\frac{2k_B T}{3g^{\frac{1}{3}}(\epsilon_F)}\right)^{\frac{3}{4}} \tag{1.12}$$

$$\nu = \nu_0 e^{-\left(\frac{T_0}{T}\right)^{\frac{1}{4}}} \tag{1.13}$$

$$T_0 = \frac{\beta}{k_B g(\epsilon_F) \alpha^3} \tag{1.14}$$

#### Multiple Trap and Release

Hopping conduction between localized states is expected whenever trap concentrations are high enough that they begin to interact. An example of this is the impurity band that forms in conventional semiconductors at high doping concentrations [16]. Hopping is also present in disordered materials due to high concentrations of defects [63]. However, hopping tends to be only practically significant at low temperatures [27]. At higher temperatures, phonons are more numerous and the thermal energy is higher, leading to phonon absorption promoting localized electrons into higher-energy extended states. By comparison, hopping events contribute negligibly to the overall conductivity:

$$\sigma_{total} = \sigma_{loc} + \sigma_{ext} \approx \sigma_{ext} \tag{1.15}$$

Particularly useful in high-mobility systems (>  $10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ), MTR theory provides quantitative agreement to empirical current-voltage data (room temperature and above) and is based on a relatively straightforward physical interpretation. Here, electrons associated with defect states (distributed arbitrarily in energy) are assumed immobile. As a result, only trap states in steady-state equilibrium with conductive states make contributions to drain current. Carrier motion is therefore diffusive, in which the energy barrier to motion corresponds to the trap depth below the conduction band edge (aka mobility edge).

These assumptions lead to the use of simple semi-classical drift/diffusion based electrostatic models derived from well-known defect profiles and provides a physically-intuitive definition of the effective mobility as the time-averaged drift mobility [82]:

$$\mu_{eff} = \frac{1}{t_{free} + t_{trapped}} \int_0^{t_{free} + t_{trapped}} \mu(t) dt \tag{1.16}$$

$$=\frac{1}{t_{free}+t_{trapped}}\left(t_{free}\mu_{free}\right) \tag{1.17}$$

$$= \left(\frac{t_{free}}{t_{free} + t_{trapped}}\right) \mu_{free} \tag{1.18}$$

The effective mobility is therefore interpreted as the band mobility weighted by the fraction of time the charge carrier is spent free. Transport therefore is approximated as a periodic sequence of regular trapping and release intervals corresponding to the lifetime of delocalized and localized states, hence the term, multiple-trap-and-release.

Regarding MTR, a rigorous approach regarding the dynamics of carrier trapping has been given by [74], however the essential properties of multiple-trap-and-release processes can be elucidated by simple models, corresponding to a set of rate equations describing electronic transitions between delocalized and localized states [30]:

$$\frac{\partial n}{\partial t} = g - \nu_0 \left(\frac{N_t}{N_c}\right) n + \nu_0 n_t e^{\frac{E_t - E_c}{k_B T}} - \frac{n}{\tau_0}$$

(1.19)

$$\frac{\partial n_t}{\partial t} = \nu_0 \Big(\frac{N_t}{N_c}\Big) n - \nu_0 n_t e^{\frac{E_t - E_c}{k_B T}} - \frac{n_t}{\tau_t}$$

(1.20)

#### CHAPTER 1. INTRODUCTION

Here,  $\tau_0$  is the lifetime of delocalized states whereas  $\tau_t$  is the lifetime of localized states. The latter describes hopping of localized electrons into deeper localized states.  $N_c$  and  $N_t$  are the effective conduction band density of states for localized states and delocalized states respectively,  $\nu_0$  is the attempt-to-escape frequency and g represents carrier generation due to light-absorption (if present). The total carrier concentration is therefore:

$$\frac{\partial(n+n_t)}{\partial t} = g - \frac{n+n_t}{\tau_r} \tag{1.21}$$

Where  $\tau_r$  is a time constant describing the decay rate of the total carrier concentration and is defined as:

$$\frac{1}{\tau_r} = \frac{1}{\tau_0} \frac{n}{n+n_t} + \frac{1}{\tau_t} \frac{n_t}{n+n_t}$$

(1.22)

MTR assumes that hopping in localized states is negligible. This simplifies  $\tau_r$  to the following:

$$\frac{1}{\tau_r} \approx \frac{1}{\tau_0} \frac{n}{n+n_t} \tag{1.23}$$

Taking the inverse and assuming an exponential density of states distribution for  $n_t$  leads to the following expression for  $\tau_r$ :

$$\tau_r = \tau_0 \frac{n + n_t}{n} \approx \tau_0 \frac{n_t}{n} = \tau_0 e^{\frac{E_c - E_t}{k_B T}}$$

(1.24)

Based on the definition of the photoconductivity, the drift mobility will be inversely proportional to the lifetime:

$$\sigma_{ph} = eg\mu\tau_0 = eg\mu_d\tau_r \tag{1.25}$$

$$\mu_d = \frac{\sigma_{ph}}{eq\tau_r} \tag{1.26}$$

This predicts that the mobility will be thermally activated and proportional to the fraction of delocalized states relative to localized states. In steady-state, this provides a defining relation for the mobility as a function of the trapped and free electron concentrations by way of the channel conductance:

$$G_D = \frac{\partial I_D}{\partial V_{DS}} = \frac{W}{L} \mu_{free} Q_{free} = \frac{W}{L} \mu_{eff} \left( Q_{free} + Q_{trapped} \right)$$

(1.27)

$$\mu_{eff} = \left(\frac{Q_{free}}{Q_{free} + Q_{trapped}}\right)\mu_{free} \tag{1.28}$$

#### CHAPTER 1. INTRODUCTION

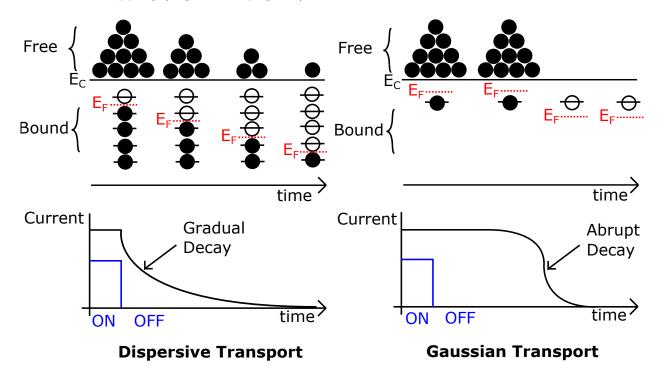

Furthermore, this simple framework also provides the theoretical basis needed to describe the characteristically broad photoconductivity decay of disordered semiconductors often referred to as "dispersive transport", as opposed to "gaussian transport" observed in ordered semiconductors. The former is often used to justify the use of a particular defect distribution over another. Observation of excited state lifetime either through capacitance (DLTS) or current (photoconductivity) provides information on the distribution of defect states. For a monoenergetic trap, thermalization occurs over a time scale corresponding to the capture time. However, for a distribution of states, the rate of thermalization is limited by the slow thermally-activated release of carriers from deep localized states whose occupation precludes free-carrier trapping (Figure 1.8, page 12).

Figure 1.8: Illustration of the difference between gaussian and dispersive transport in ordered and disordered semiconductors respectively.

It is worth noting that clear distinction between hopping and MTR, although convenient, is not straightforward. Naturally, similarities exist between hopping and MTR due to the fact that both exhibit thermally-activated behavior and a strong sensitivity to charge density. Kinetic Monte Carlo simulations have shown strong similarity between the two models. For example, Mehraeen et al argue that the *transport energy* in hopping conduction is effectively replaced by the *mobility edge* in MTR models, both of which have an activation energy that rapidly reduces upon increase in charge density leading to similar trends [60]. However, the mobility in purely hopping-based systems tends to be low and can be further distinguished based on the magnitude of the mobility.

## **1.4** Printed Electronics for Large-Area Applications

#### Introduction to Solution-Processing

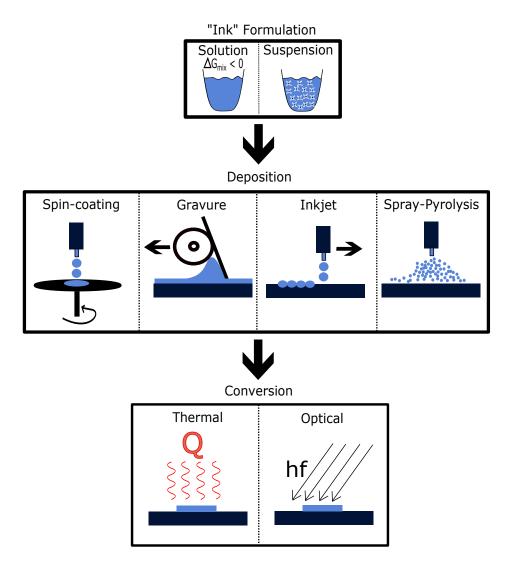

Solution-processing, is an alternative, cost-effective manufacturing technique for large-area electronics applications (e.g. displays, smart glass, solar cells, etc...) due to higher module throughput, materials utilization, lower equipment costs, and reduced overall process complexity [72]. Simple routes exist for the formation of electronic thin-films from precursor solutions which can be broadly classified as either sol-gel *solutions* or nanoparticle *suspensions* [72]. These liquids are transferred to substrates using a variety of coating (e.g. spin-coating, dip-coating, blade-coating, slot-casting), printing (e.g. screen, ink-jet, gravure, aerosol) and growth (e.g. spray pyrolysis, chemical bath deposition) techniques available (Figure 1.9, page 14). The chemical decomposition pathways and rheology of solution ultimately determine the precursors available for film formation [72]. Consequently, the electronic properties of solution-processed films tend to be strongly dependent on synthetic conditions. Ultimately, the electronic properties of solution-processed films. Thus, there is an apparent trade-off between process complexity and device performance.

#### Cost Benefit of Solution-Processing

The primary motivation for printed electronics is a reduction in manufacturing cost due to an increase in throughput (as measured in area per unit time) [85]. As such, increases in process speed and/or processing area are expected to directly result in a reduction in manufacturing cost. Data illustrating specific cost benefits are relatively scarce. Consequently, the cost benefits of solution-processing are usually taken for granted within the academic literature. It is generally assumed that total cost is reduced on a per area basis with an estimated 100 times reduction in cost ( $\$100/ft^2$  as opposed to  $\$10,000/ft^2$ ) relative to conventional manufacturing methods [61]. More detailed estimates are application specific. A highly detailed example is given by Krebs et al, in which the materials, labor, and processing costs have been itemized for each material in a screen-printed flexible polymer solar cell [44].

## **1.5** Transparent Conductive Oxides

#### **Role and Applications**

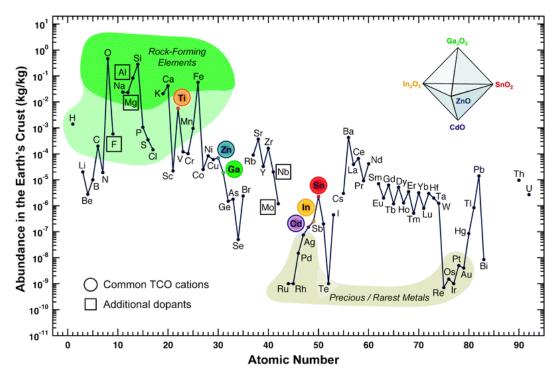

Transparent conductive oxides (TCOs) play a vital role in several important electronic device applications including energy harvesting, information display and communication due

Figure 1.9: Illustration of the solution deposition process.

to their combination of high electronic conductivity and transparency in the visible range along with absorption in the infra-red range (Figure 1.10, page 15). A thorough review of transparent conductive oxides is given by [72]. Most obvious examples of their practical use are in photovoltaic devices, such as solar cells and light emitting diodes (LEDs), which require at least one transparent electrode to allow light to penetrate in or out of the device for proper operation. Additionally, both liquid crystal and LED displays incorporate TCOs into each pixel element which are coupled to thin-film transistors (TFTs) in order to modulate the transmission of light.