### **UC Santa Barbara**

## **UC Santa Barbara Previously Published Works**

#### **Title**

InGaAs/InP DHBTs with 120-nm Collector Having Simultaneously High ft,fmax  $\> 450 \ GHz$

#### **Permalink**

https://escholarship.org/uc/item/44q5b58b

#### Journal

Electron Device Letters, 26(8)

#### **ISSN**

0741-3106

#### **Authors**

Griffith, Zach Rodwell, Mark Fang, Xiao-Ming et al.

#### **Publication Date**

2005-08-01

#### DOI

10.1109/LED.2005.852519

Peer reviewed

# InGaAs/InP DHBTs With 120-nm Collector Having Simultaneously High $f_{\tau}$ , $f_{\text{max}} \geq 450$ GHz

Zach Griffith, Mark J. W. Rodwell, *Fellow, IEEE*, Xiao-Ming Fang, Dmitri Loubychev, Ying Wu, Joel M. Fastenau, and Amy W. K. Liu, *Senior Member, IEEE*

Abstract—InP/In $_{0.53}$  Ga $_{0.47}$  As/InP double heterojunction bipolar transistors (DHBT) have been designed for increased bandwidth digital and analog circuits, and fabricated using a conventional mesa structure. These devices exhibit a maximum 450 GHz  $f_{\tau}$  and 490 GHz  $f_{\rm max}$ , which is the highest simultaneous  $f_{\tau}$  and  $f_{\rm max}$  for any HBT. The devices have been scaled vertically for reduced electron collector transit time and aggressively scaled laterally to minimize the base-collector capacitance associated with thinner collectors. The dc current gain  $\beta$  is  $\approx$  40 and  $V_{\rm BR,CEO}=3.9$  V. The devices operate up to 25 mW/ $\mu$ m² dissipation (failing at  $J_e=10$  mA/ $\mu$ m²,  $V_{\rm ce}=2.5$  V,  $\Delta T_{\rm failure}=301$  K) and there is no evidence of current blocking up to  $J_e\geq12$  mA/ $\mu$ m² at  $V_{\rm ce}=2.0$  V from the base-collector grade. The devices reported here employ a 30-nm highly doped InGaAs base, and a 120-nm collector containing an InGaAs/InAlAs superlattice grade at the base-collector junction.

*Index Terms*—Heterojunction bipolar transistor (HBT), indium phosphide (InP).

#### I. INTRODUCTION

nP-based double heterojunction bipolar transistors (DHBT) have been aggressively pursued because of their superior material transport properties over SiGe [1]. This is demonstrated by the increased value of small-signal unity current gain  $f_{\tau}$ , unity power gain  $f_{\text{max}}$ , and higher operating current density  $J_e$  that InP devices possess over SiGe at a given scaling generation [2], [3]. As Si based processing technologies are much more advanced than InP, SiGe HBTs have been scaled to dimensions where the reduction in base–collector capacitance  $C_{

m cb}$  and higher  $J_e$  are such that the speed of digital circuits in both material systems have been comparable. Over the past year, techniques to aggressively scale InP HBTs to submicrometer features vertically and laterally have resulted in record performance for  $f_{\tau}$  and  $f_{\text{max}}$  [4]–[7]. Applications for these devices include mixed-signal ICs for digital radar and advanced communication systems [8]. Efforts to simultaneously produce submicrometer InP HBTs and have high circuit yield >10000 devices per IC

Manuscript received March 25, 2005; revised May 17, 2005. This work was supported by the Office of Naval Research under contract N0001-40-4-10071 and the Defense Advanced Research Projects Agency under the TFAST Program N66001-02-C-8080. The review of this letter was arranged by Editor T. Mizutani.

Z. Griffith and M. J. W. Rodwell are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106 USA (e-mail: griffith@ece.ucsb.edu).

X.-M. Fang, D. Loubychev, Y. Wu, J. M. Fastenau, and A. W. K. Liu are with IQE, Inc., Bethlehem, PA 18015 USA.

Digital Object Identifier 10.1109/LED.2005.852519

are underway, with the first step in the realization of such a process producing static frequency dividers with an operating  $f_{\rm clk} > 150 \, {\rm GHz}[5], [9], [10].$

Continued scaling of the HBT base and collector epitaxial layers is needed, along with simultaneous reductions to the device parasitics to increase the bandwidth of digital and analog circuits [11], [12]. As discussed in [3], when the collector is thinned and the operating  $J_e$  is maintained at  $J_{\rm Kirk}$  (the electric field at the base edge of the base–collector junction becomes zero) for reduced digital IC gate delay, the major delay scales  $\tau = C_{\rm cb} \cdot \Delta V_{\rm logic}/I_c \propto T_c$ , the collector thickness. But as  $J_{\rm Kirk}$  increases  $\propto T_c^{-2}$ , the parasitic voltage drop across the emitter resistance also increases as  $\Delta V_{\rm parasitic} = I_e \cdot R_{\rm ex} \approx J_e \cdot \rho_c \propto T_c^{-2}$ . If for the same circuit the bias currents  $I_c = A_e \cdot J_{\rm Kirk} \propto A_e \cdot T_c^{-2}$  are kept constant as the collector is thinned and the devices scaled and the emitter contact resistance  $\rho_c$  is reduced  $\propto T_c^2$ ,  $\Delta V_{\rm parasitic}$  will be unchanged and circuit speed will improve.

Prior to this letter, the highest  $f_{\tau}$  reported for an InP DHBT was 406 GHz with an  $f_{\rm max}$  of 423 GHz [6], having a 35-nm base and 120-nm collector. The highest reported  $f_{\rm max}$  for a mesa DHBT is 519 GHz, with a 252 GHz  $f_{\tau}$  [7], having a 40-nm base and 150-nm collector. Here, we report a 450 GHz  $f_{\tau}$  and 490 GHz  $f_{\rm max}$  InP DHBT—the first transistor to have a simultaneous  $f_{\tau}$  and  $f_{\rm max}$  beyond 450 GHz.

#### II. DESIGN, GROWTH, AND FABRICATION

The epitaxial material was grown by commercial vendor IQE, Inc. on a 3" SI–InP wafer and the HBTs were fabricated in an all wet etch, standard triple mesa process. The device layer structure is provided in Table I and details of the base and collector design are given in [13]. The devices are passivated with and the wafer is planarized in benzocyclobutene (BCB) to minimize device leakage currents associated with semiconductor surface charge effects. BCB also provides a low-loss spacer ( $\varepsilon_r = 2.7$ ,  $T_{\rm BCB} = 1.6 \ \mu \rm m$ ) between the device interconnects and InP substrate to reduce spurious resonances from the RF measurements through substrate mode coupling. The improvements in the device design here compared to [3] include the use of an indium rich In<sub>0.85</sub> Ga<sub>0.15</sub>As emitter cap with increased doping  $N_{\rm cap} = 6 \cdot 10^{19} \, {\rm cm}^{-3}$  for a  $\approx 17\%$  reduction to the emitter contact  $\rho_c$ , and improved surface preparation to remove surface oxides (ozone plasma descum, diluted NH<sub>4</sub>OH dip) [14] prior to base metal evaporation for a 2:1 reduction in base contact  $\rho_c$ .

| Thickness (nm) | Material                                 | Doping cm <sup>-3</sup>   | Description         |

|----------------|------------------------------------------|---------------------------|---------------------|

| 5              | In <sub>0.85</sub> Ga <sub>0.15</sub> As | 6·10 <sup>19</sup> : Si   | Emitter cap         |

| 15             | In <sub>x</sub> Ga <sub>1-x</sub> As     | > 4·10 <sup>19</sup> : Si | Emitter cap grading |

| 20             | In <sub>0.53</sub> Ga <sub>0.47</sub> As | 4·10 <sup>19</sup> : Si   | Emitter             |

| 80             | InP                                      | 3·10 <sup>19</sup> : Si   | Emitter             |

| 10             | InP                                      | 8·10 <sup>17</sup> : Si   | Emitter             |

| 40             | InP                                      | 5·10 <sup>17</sup> : Si   | Emitter             |

| 30             | InGaAs                                   | 7-4 10 <sup>19</sup> : C  | Base                |

| 15             | In <sub>0.53</sub> Ga <sub>0.47</sub> As | 3·10 <sup>16</sup> : Si   | Setback             |

| 24             | InGaAs / InAlAs                          | 3·10 <sup>16</sup> : Si   | B-C Grade           |

| 3              | InP                                      | 3·10 <sup>18</sup> : Si   | Pulse doping        |

| 78             | InP                                      | 3·10 <sup>16</sup> : Si   | Collector           |

| 5              | InP                                      | 1·10 <sup>19</sup> : Si   | Sub Collector       |

| 6.5            | In <sub>0.53</sub> Ga <sub>0.47</sub> As | 2·10 <sup>19</sup> : Si   | Sub Collector       |

| 300            | InP                                      | 2·10 <sup>19</sup> : Si   | Sub Collector       |

| Substrate      | SI : InP                                 |                           |                     |

#### TABLE I DHBT LAYER COMPOSITION

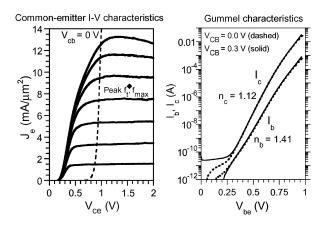

Fig. 1. Common–emitter I–V characteristics ( $I_{b, \text{step}} = 140 \ \mu\text{A}$ ) and Gummel characteristics. Device junction dimensions  $A_{\rm ie} = 0.6 \times 4.3 \ \mu \text{m}^2$ ,  $A_{\rm jc} = 1.3 \times 6.5 \ \mu \rm m^2$ .

#### III. RESULTS

Standard transmission line measurements (TLM) show the base  $\rho_s \approx 610 \Omega$  and  $\rho_c \approx 4.6 \Omega \cdot \mu \text{m}^2$ , and the collector  $\rho_s \approx 12.1 \ \Omega$  and  $\rho_c \approx 8.4 \ \Omega \cdot \mu \text{m}^2$ . The emitter  $\rho_c$  was determined from RF parameter extraction and  $\approx 8.4 \ \Omega \cdot \mu \text{m}^2$ . The HBTs have  $\beta \approx 40$ , a common-emitter breakdown voltage  $V_{\rm BR,CEO} = 3.9 \text{ V}$  (at  $I_c = 50 \ \mu\text{A}$ ), and a collector leakage current  $I_{\rm cbo}$  < 30 pA ( $V_{\rm cb,offset}$  = 0.3 V). A plot of the common-emitter current-voltage and Gummel characteristics are shown in Fig. 1. These devices show little effect of self-heating until 20 mW/ $\mu$ m<sup>2</sup> operation and function up to 25 mW/ $\mu$ m<sup>2</sup> when biased at  $J_e = 10$  mA/ $\mu$ m<sup>2</sup>,  $V_{ce} = 2.5$ V,  $\Delta T_{\rm failure} \approx 301$  K. In addition, Fig. 1 demonstrates the effectiveness of the chirped-superlattice base-collector grade with no evidence of current blocking associated with the  $\Delta E_c$ between  $In_{0.53} Ga_{0.43}As$  and InP until  $J_e \geq 12 \text{ mA}/\mu\text{m}^2$  at  $V_{\rm ce} = 2.0 \text{V}$ —well beyond the bias needed for peak  $f_{\tau}$ ,  $f_{\rm max}$ and minimum  $C_{cb}$  measured for these DHBTs.

DC-110 GHz RF measurements were carried out after performing an off wafer line-reflect-reflect-match calibration on an Agilent 8510XF network analyzer. On-wafer open and short circuit pad structures identical to the ones used by the devices were measured after calibration in order to deembed their associated

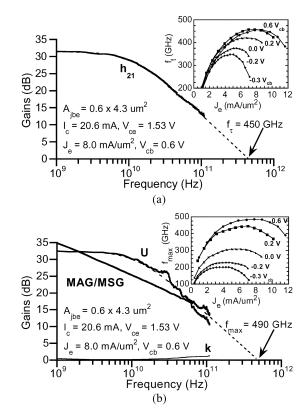

Fig. 2. Measured microwave gains. (a)  $h_{21}$  from peak extrapolated  $f_{\tau}$  (b) MSG/MAG and Mason's unilateral power gain U from peak extrapolated  $f_{\text{max}}$ .

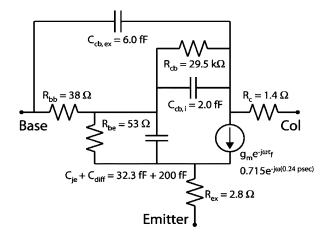

Fig. 3. Small signal hybrid- $\pi$  equivalent circuit model.

parasitics from the device measurements. A maximum 450 GHz  $f_{ au}$  and 490 GHz  $f_{

m max}$  (Fig. 2) at  $I_c=20.6$  mA and  $V_{

m ce}=1.53$  $V (V_{cb} = 0.6 \text{ V}, J_e = 8.0 \text{ mA}/\mu\text{m}^2, C_{cb}/I_c = 0.38 \text{ ps/V},$  $\Delta T \cong 106 \text{ K}$ ) was determined from extrapolation through a least-square-fit between the transfer functions

$$|h_{21}(f)|^{2} = \frac{h_{21,DC}^{2}}{1 + h_{21,DC}^{2} \cdot \left(\frac{f}{f_{\tau}}\right)^{2}}$$

$$U(f) = \frac{U_{DC}}{1 + U_{DC} \cdot \left(\frac{f}{f_{max}}\right)^{2}}$$

(2)

$$U(f) = \frac{U_{\rm DC}}{1 + U_{\rm DC} \cdot \left(\frac{f}{f_{\rm max}}\right)^2} \tag{2}$$

to the measured microwave gains  $h_{21}$  and U at measured frequencies. A small-signal hybrid- $\pi$  equivalent circuit for this

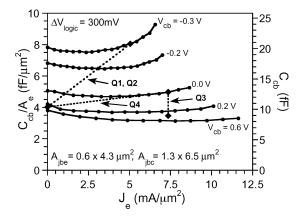

Fig. 4. Variation of  $C_{\rm cb}$  with  $J_e$  and  $V_{\rm cb}$  bias, labeled to show the corresponding device switching endpoints within the CML divider schematic (Fig. 5). Lines connecting the switching endpoints have been superimposed to act as a guide.

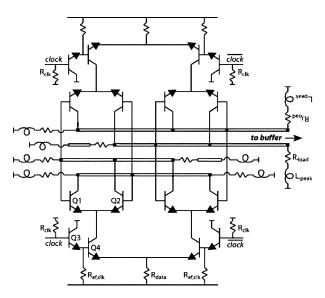

Fig. 5. Schematic of current mode logic (CML) static frequency divider.

device at peak  $f_{\tau}$  and  $f_{\rm max}$  is shown in Fig. 3. This DHBT has a  $0.6 \times 4.3~\mu{\rm m}^2$  emitter semiconductor junction area  $A_{\rm jbe}$  and 1.3- $\mu{\rm m}$  base mesa width—collector to emitter width ratio  $W_c/W_e=2.17$ . Peak  $f_{\tau}$  and  $f_{\rm max}$  for all devices is between  $J_e=7-9~{\rm mA}/\mu{\rm m}^2$  at  $V_{\rm cb}=0.6~{\rm V}$  for different device dimensions on the wafer.

The variation of  $C_{\rm cb}$  versus  $J_e$  and  $V_{\rm cb}$  for use in current mode logic (CML) circuit design is shown in Fig. 4, where switching endpoints for devices from the CML static frequency divider (Fig. 5) are shown. Lines connecting the switching endpoints have been superimposed to act as a guide. At the indicated bias points, data steering devices (Q1, Q2) have a minimum  $C_{\rm cb}/I_c \approx 1.6$  ps/V, emitter follower devices (Q3)  $C_{\rm cb}/I_c \approx 0.57$  ps/V, and clock steering devices (Q4)

$C_{\rm cb}/I_c \approx 0.67~{\rm ps/V}$  [12]. Some of the bias points have been selected beyond  $J_{Kirk}$  for reduced  $C_{\rm cb}/I_c$  ratio. While  $C_{\rm cb}$  may be increasing, inspection of the microwave gains versus  $J_e$  and  $V_{\rm cb}$  (Fig. 3) shows that the initial rolloff of  $f_{\tau}$  and  $f_{\rm max}$  is soft—this suggests that the initial field collapse in the setback layer of the base–collector interface does not significantly impact the forward delay of the HBT. Because of this, the selection of a smaller device size for a  $J_e$  slightly above  $J_{Kirk}$  will translate to a higher maximum clock rate. At  $J_e$  substantially above  $J_{Kirk}$ , the field will reverse in the collector setback and grade. The forward delay will increase rapidly—this is when the roll-off of both  $f_{\tau}$  and  $f_{\rm max}$  becomes significant, and digital circuit speed will suffer.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. J. Hacker and Dr. M. Urteaga, Rockwell Scientific Corporation for their assistance with the RF device measurements.

#### REFERENCES

- [1] P. Bhattacharya, Properties of Lattice-Matched and Strained Indium Gallium Arsenide. London, U.K.: INSPEC, 1993.

- [2] M. Khater *et al.*, "SiGe HBT technology with  $f_{\rm max}/f_{\tau}=350/300$  GHz and gate delay below 3.3 ps," in *IEDM Tech. Dig.*, 2004, pp. 247–250.

- [3] Z. Griffith *et al.*, "InGaAs/InP DHBTs for increased digital IC bandwidth having a 391 GHz  $f_{\tau}$  and 505 GHz  $f_{\text{max}}$ ," *IEEE Electron Device Lett.*, vol. 26, no. 1, pp. 11–13, Jan. 2005.

- [4] M. Urteaga et al., "Deep submicron InP DHBT technology with electroplated emitter and base contacts," in Proc. Device Research Conf., Notre Dame, IN, Jun. 21–23, 2004.

- [5] G. He *et al.*, "Self-aligned InP DHBT with  $f_{\tau}$  and  $f_{\text{max}}$  over 300 GHz in a new manufacturable technology," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 520–522, Aug. 2004.

- [6] T. Hussain et al., "First demonstration of sub-0.25  $\mu$ m-width emitter InP-DHBTs with >400 GHz  $f_{\tau}$  and >400 GHz  $f_{\rm max}$ ," in *IEDM Tech. Dig.*, 2004, pp. 553–556.

- [7] D. Sawdai et al., "Planarized InP/InGaAs hetrojunction bipolar transistors with f<sub>max</sub> > 500 GHz," in Proc. Device Research Conf., Notre Dame, IN, Jun. 21–23, 2004.

- [8] J. C. Zolper, "Super-scaled InP HBTs for 150 GHz circuits," in *IEDM Tech. Dig.*, Dec. 2003, pp. 1–4.

- [9] Z. Griffith et al., "Ultra high frequency static dividers >150 GHz in a narrow mesa InGaAs/InP DHBT technology," in Proc. IEEE Bipolar/BiCMOS Circuits Technology Meeting, Montreal, Canada, Sep. 13–14, 2004.

- [10] D. A. Hitko et al., "A low power (45 mW/latch) static 150 GHz CML divider," in Proc. IEEE Compound Semiconductor Integrated Circuit Symp., Monterey, CA, Oct. 24–27, 2004.

- [11] T. Enoki et al., "Prospects of InP-based IC technologies for 100-Gbit/sclass lightwave communications systems," Int. J. High Speed Electron. Syst., vol. 11, no. 1, pp. 137–158, 2001.

- [12] M. J. W. Rodwell et al., "Scaling of InGaAs/InAlAs HBTs for high speed mixed-signal and mm-wave ICs," Int. J. High Speed Electron. Syst., vol. 11, no. 1, pp. 159–215, Jan. 2001.

- [13] M. Dahlström et al., "Wideband DHBTs using a graded carbon-doped InGaAs base," *IEEE Electron Device Lett.*, vol. 24, no. 7, pp. 433–435, Iul. 2003

- [14] E. F. Chor et al., "Electrical characterization, metallurgical investigation, and thermal stability studies of (Pd, Ti, Au)-based Ohmic contacts," J. Appl. Phys., vol. 87, no. 5, pp. 2437–2444, 2000.