# UCLA UCLA Electronic Theses and Dissertations

## Title

Signal Processing Techniques EnablingWideband A/D Converters

Permalink https://escholarship.org/uc/item/4335n0zt

**Author** Ghosh, Abhishek

Publication Date 2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

Los Angeles

# Signal Processing Techniques Enabling Wideband A/D Converters

A dissertation submitted in partial satisfaction

of the requirements for the degree

Doctor of Philosophy in Electrical Engineering

by

## **Abhishek Ghosh**

© Copyright by

Abhishek Ghosh

2013

# Signal Processing Techniques Enabling Wideband A/D Converters

by

#### Abhishek Ghosh

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2013 Professor Sudhakar Pamarti, Chair

With an ever-widening signal spectrum and incorporation of multiple standards that share the available spectrum at the same time, research towards building wideband analog-to-digital converters (ADCs) has gained significant momentum. Furthermore, with an aim to improve spectral efficiency, increasingly complex modulation schemes are being invoked having high peak-to-average ratios, the latter translating to high dynamic ranges for the received signals. Consequently, the ADCs deployed in these receivers need to be of quite high precision as well. With these two primary goals for ADCs (high bandwidth, high resolution) in mind, this thesis presents a few different techniques for achieving them.

In the first part of this thesis, we shall explore the art of dithering to linearize an A/D converter system. In particular, a digital-signal conditioning technique (using subtractive dither) is developed as a stepping-stone for a high resolution system. The effects of filtering the dither signal to shape its spectral content outside the signal band while maintaining its benefits are studied in detail. Design

strategies for finite impulse response (FIR) filters that accomplish spectral shaping as well as allay quantizer non-linearity are derived theoretically.

In the second part of this thesis, the proposed dithering technique is used for linearizing an ADC system that is intrinsically non-linear, namely a VCO-based ADC. Ring voltage-controlled oscillator (VCO)-based ADCs have surfaced as elegant alternatives to the traditional  $\Delta - \Sigma$  modulators primarily due to their mostly digital nature. They offer low power, low area and simplicity of design benefits. However, they are known to be notoriously non-linear that can be attributed to the non-linear nature of the frequency-voltage tuning curve of the VCO. In the proposed scheme, the ring VCO-based ADC is preceded by a coarse flash ADC. The former processes the quantization error (residue), a signal with much smaller dynamic range, from the coarse ADC thereby lessening the impact of the non-linearity. The proposed dithering technique further helps in alleviating the non-linearity. It helps condition the signal to the VCO nonlinearity. The technique, thus obviates the need for power-hungry digital calibration techniques or expensive front-end loop-filters. A prototype implementation (in 65nm CMOS) based on the technique achieves 10-b ENOB in digitizing signals with 50MHz bandwidth consuming 8.2mW at an FoM of 90fJ/conv.step.

In the third part of this thesis, a very popular technique of bandwidth enhancement through time-interleaving multiple A/D converters is examined. Time-interleaved A/D converters enable high conversion bandwidths with quite high precisions. However, inevitable mismatch errors typical of any integrated circuit fabrication process degrades the achievable dynamic range of such A/D converters. Multiple techniques have been proposed over the past two decades to alleviate the problems of mismatch errors. This chapter takes a detailed look at most of these techniques bringing out their strengths and weaknesses. The chapter provides a hitherto unavailable common platform to look at analog and digital intensive techniques towards solving this issue motivating the development of a novel solution to this problem in the subsequent section.

In the fourth chapter, a power-efficient technique to combat mismatches for time-interleaved systems is proposed. The proposed technique adaptively selects finite impulse response filters that take advantage of the signal characteristics. The sub-band outputs from the ADC are passed through these filters to correct for errors at a minimal hardware expense. Simulation results sub-stantiating the claims and thorough analyses of the technique are subsequently presented to high-light the efficacy of the technique.

Chapter 1 of this thesis has been published in full in the *International Conference on Acoustics*, *Speech and Signal Processing(ICASSP)*, 2013. The dissertation author is the primary investigator and author of this paper. Professor Sudhakar Pamarti supervised the research which forms the basis for this paper.

Chapter 2 of this thesis is a reprint of a paper under preparation to be submitted in part or in full to the *IEEE Journal of Solid-States Circuits (JSSC)*. The dissertation author is the primary investigator and Professor Sudhakar Pamarti supervised the research which forms the basis for this paper. By the virtue of being (or to be) independent papers, there is a slight degree of overlap in content between Chapters 1 and 2, but this is essential to maintain the continuity of the chapters.

Chapter 3 of this thesis is a reprint of a paper under preparation to be submitted in part or in full to the *IEEE Transactions of Circuits and Systems-1 (TCAS-1)*. The dissertation author is the primary investigator and Professor Sudhakar Pamarti supervised the research which forms the basis for this paper.

Chapter 4 of this thesis is also a reprint of a paper under preparation to be submitted in part or in full to the *IEEE Transactions of Circuits and Systems-1 (TCAS-1)*. The dissertation author is the primary investigator and Professor Sudhakar Pamarti supervised the research which forms the basis for this paper. The dissertation of Abhishek Ghosh is approved.

Milos Ercegovac

Chih Kong Ken Yang

Sudhakar Pamarti, Committee Chair

University of California, Los Angeles

2013

To Ma and Baba

# TABLE OF CONTENTS

| 1  | Filte  | ering of subtractive discrete dither in quantizers: some new results   | 1  |

|----|--------|------------------------------------------------------------------------|----|

|    | 1.1    | Introduction                                                           | 1  |

|    |        | 1.1.1 Dithered quantization                                            | 2  |

|    |        | 1.1.2 Prior-art                                                        | 3  |

|    |        | 1.1.3 Contribution                                                     | 4  |

|    | 1.2    | Behavioral model                                                       | 4  |

|    | 1.3    | Main result: theory                                                    | 6  |

|    | 1.4    | Main results: simulation                                               | 13 |

|    | 1.5    | Conclusion                                                             | 14 |

| Re | eferen | ces                                                                    | 15 |

| 2  | Line   | earization through dithering: A 50MHz bandwidth, 10-b ENOB, 8.2mW VCO- |    |

| ba | sed A  | DC                                                                     | 16 |

|    | 2.1    | Introduction                                                           | 16 |

|    | 2.2    | Ring oscillator based VCO-ADC                                          | 18 |

|    | 2.3    | Prior-art                                                              | 21 |

|    |        | 2.3.1 Feedback Loop                                                    | 21 |

|    |        | 2.3.2 Foreground Calibration                                           | 22 |

|    |        | 2.3.3   | Background calibration                                            | 23 |

|----|--------|---------|-------------------------------------------------------------------|----|

|    |        | 2.3.4   | Input conditioning                                                | 23 |

|    |        | 2.3.5   | Pipelining                                                        | 24 |

|    | 2.4    | Propos  | ed Technique: System Level                                        | 25 |

|    |        | 2.4.1   | A brief on dithering in ADCs                                      | 28 |

|    |        | 2.4.2   | Performance Bounds                                                | 32 |

|    | 2.5    | Propos  | ed Technique: Circuit Level and other digital signal conditioning | 35 |

|    |        | 2.5.1   | Coarse Stage                                                      | 35 |

|    |        | 2.5.2   | Fine Stage and Other Digital Conditioning                         | 37 |

|    | 2.6    | Measu   | rement Results                                                    | 41 |

|    | 2.7    | Conclu  | ision                                                             | 45 |

|    | 2.8    | Ackno   | wledgement                                                        | 46 |

| Re | eferen | ces .   |                                                                   | 47 |

| 3  | Phas   | se Mism | natches in Time-Interleaved ADCs: A tutorial                      | 50 |

|    | 3.1    | Introdu | action                                                            | 50 |

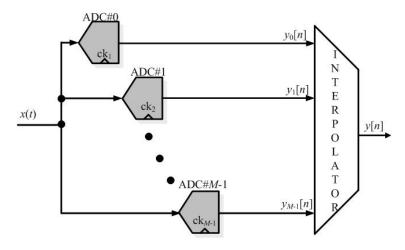

|    | 3.2    | Time-I  | Interleaved ADCs: modeling and effects                            | 51 |

|    | 3.3    | Offset  | and gain calibration methods                                      | 57 |

|    | 3.4    | Timing  | g mismatch calibration in time-interleaved ADCs                   | 58 |

|    |        | 3.4.1   | Analog                                                            | 58 |

|     |         | 3.4.2    | Digital                                                                 | 62 |

|-----|---------|----------|-------------------------------------------------------------------------|----|

|     | 3.5     | Bandw    | vidth Mismatch Calibration                                              | 73 |

|     | 3.6     | Conclu   | ision                                                                   | 76 |

| Re  | eferen  | ces .    |                                                                         | 77 |

| 4   | Phas    | se Mism  | natches in Time-Interleaved ADCs: Adaptive signal-dependent digital so- |    |

| lut | tion to | ) an ana | alog problem                                                            | 81 |

|     | 4.1     | Introdu  | uction                                                                  | 81 |

|     | 4.2     | Propos   | ed technique                                                            | 81 |

|     |         | 4.2.1    | Architecture                                                            | 81 |

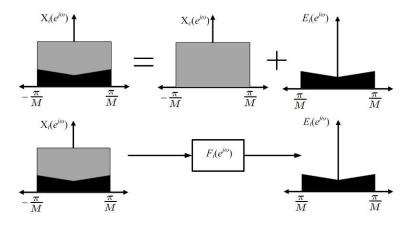

|     |         | 4.2.2    | Signal processing                                                       | 82 |

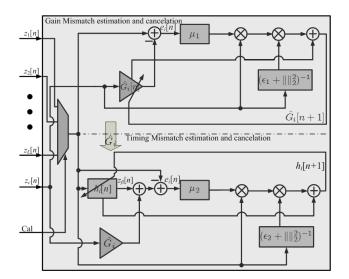

|     |         | 4.2.3    | Calibration algorithm details                                           | 85 |

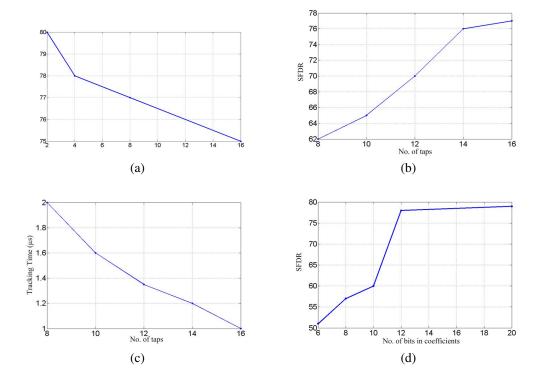

|     | 4.3     | Simula   | ation Results, Implementation Details and Practical Considerations      | 88 |

|     |         | 4.3.1    | Signals                                                                 | 90 |

|     |         | 4.3.2    | Channels                                                                | 91 |

|     |         | 4.3.3    | Taps                                                                    | 91 |

|     |         | 4.3.4    | Bits                                                                    | 92 |

|     |         | 4.3.5    | Comparing with state-of-the-art                                         | 93 |

|     | 4.4     | Conclu   | ision                                                                   | 93 |

| References | • | • | • | • | • | • | • | • | • |  | • |  | • | • |  |  |  | • | • |  | • |  | • |  |  |  | 96 | 6 |

|------------|---|---|---|---|---|---|---|---|---|--|---|--|---|---|--|--|--|---|---|--|---|--|---|--|--|--|----|---|

|            |   |   |   |   |   |   |   |   |   |  |   |  |   |   |  |  |  |   |   |  |   |  |   |  |  |  |    |   |

# LIST OF FIGURES

| 1.1  | Mid-tread quantizer                                                                      | 3  |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Dithered Quantizers: (a) Subtractive (b) Non-subtractive/Additive (c) Filtered-          |    |

|      | subtractive                                                                              | 4  |

| 1.3  | Simulation results                                                                       | 10 |

| 2.1  | ADC performance and applications                                                         | 17 |

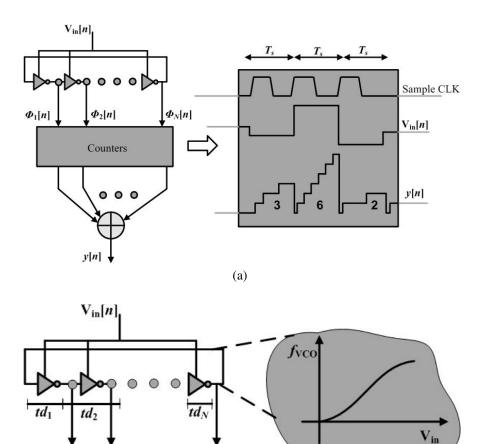

| 2.2  | VCO-based ADC (a) The Good (b) The Bad and the Ugly                                      | 19 |

| 2.3  | Representative signal processing view of VCO-based ADC                                   | 20 |

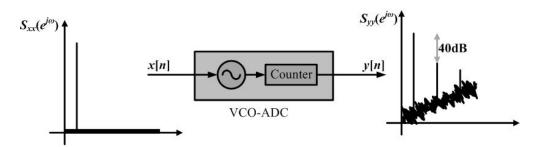

| 2.4  | VCO-based ADC prior-art (a) Negative feedback through $\Delta - \Sigma$ loop (b) Nonlin- |    |

|      | earity calibration (c) Input conditioning (d) Pipelining                                 | 22 |

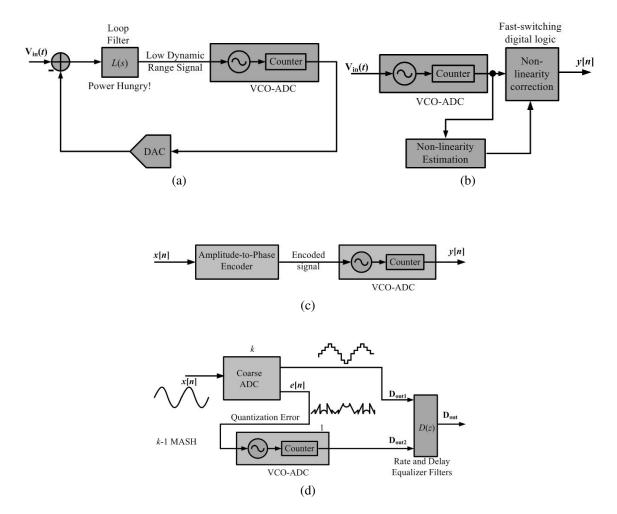

| 2.5  | Coarse dithering to linearize VCO-based ADC (a) Behavioral model (b) Simula-             |    |

|      | tion result                                                                              | 25 |

| 2.6  | Proposed filtering of coarse dither to linearize VCO-based ADC                           | 27 |

| 2.7  | Probability mass function (p.m.f) shaping due to filtering                               | 27 |

| 2.8  | Simulation results on the use of an arbitrary filter instead of the prescribed filter    | 28 |

| 2.9  | Signal processing model of total system                                                  | 30 |

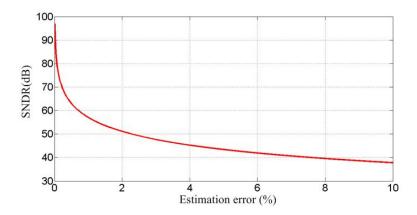

| 2.10 | Achievable SNDR vs. VCO-gain estimation error based on Eqn. 2.3                          | 32 |

| 2.11 | Coarse ADC and DAC structure                                                             | 34 |

| 2.12 | Filtered dither generation                                                               | 35 |

| 2.13 | Coarse flash ADC components: (a) Preamplifier (b) Dynamic latch                | 36 |

|------|--------------------------------------------------------------------------------|----|

| 2.14 | Differential ring VCO                                                          | 37 |

| 2.15 | Segmented coarse DAC                                                           | 38 |

| 2.16 | Overall structure in IC prototype                                              | 39 |

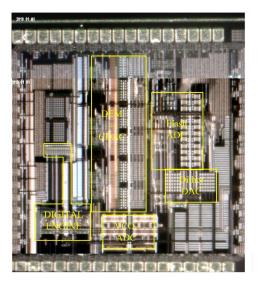

| 2.17 | Die micrograph                                                                 | 40 |

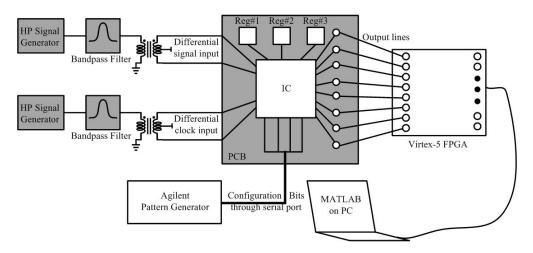

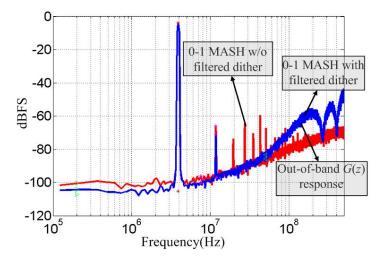

| 2.18 | Representative test setup                                                      | 42 |

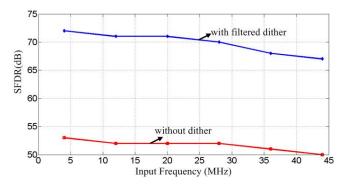

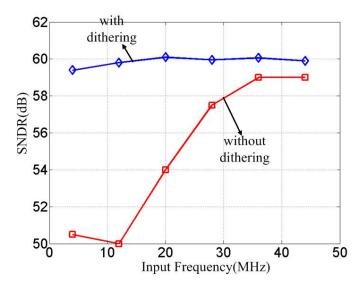

| 2.19 | Measured performance with and without technique                                | 43 |

| 2.20 | Measured SFDR vs. input frequency                                              | 43 |

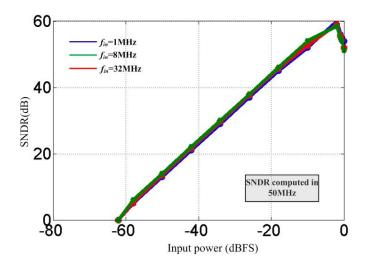

| 2.21 | Measured SNDR vs. input frequency                                              | 44 |

| 2.22 | Measured dynamic range of the system for different input frequencies           | 45 |

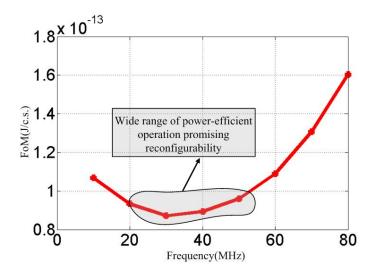

| 2.23 | Measured FoM of the system for varying noise-integration bandwidths            | 46 |

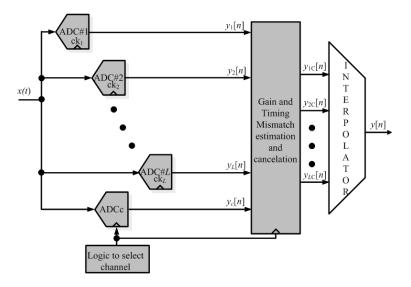

| 3.1  | Time-interleaved ADC: model                                                    | 52 |

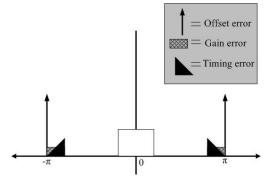

| 3.2  | Time-interleaved ADC: error sources                                            | 53 |

| 3.3  | Mismatch effects on output spectrum for a 2-channel ADC                        | 55 |

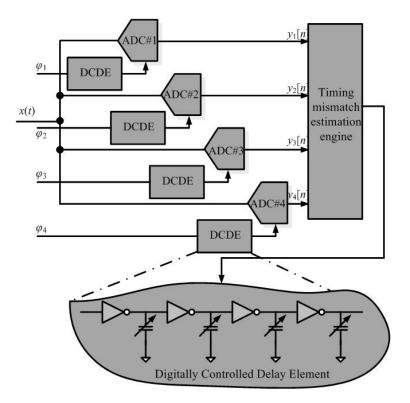

| 3.4  | Analog correction of phase errors                                              | 58 |

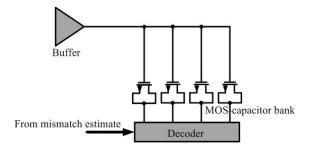

| 3.5  | Representative digitally controlled delay element                              | 59 |

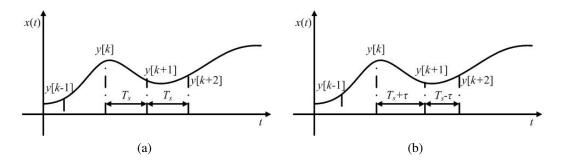

| 3.6  | Correction principle in [10, 11, 15] (a) A two-channel output waveform without |    |

|      | mismatch (b) A two-channel output waveform with mismatch                       | 59 |

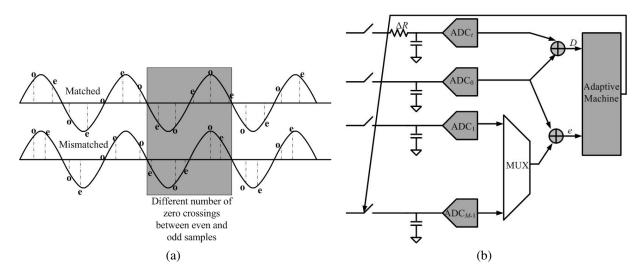

| 3.7  | Correction principle (a) Zero crossing variation without and with mismatch [5] (b)  |    |

|------|-------------------------------------------------------------------------------------|----|

|      | Structure in [7]                                                                    | 61 |

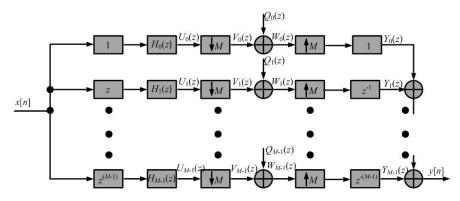

| 3.8  | Filterbank model of time-interleaved ADC                                            | 63 |

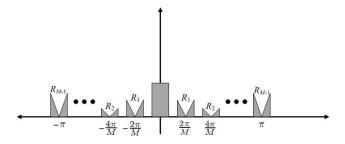

| 3.9  | Representative output spectrum due to timing mismatch errors in a $M$ -channel ADC  | 64 |

| 3.10 | Fractional Delay Filter correction applied to filter-bank model of time-interleaved |    |

|      | ADC                                                                                 | 65 |

| 3.11 | Farrow structure to realize fractional delay                                        | 67 |

| 3.12 | Modification of synthesis filters for easy realization in [26]                      | 67 |

| 3.13 | Estimation structure in [27]                                                        | 68 |

| 3.14 | Principle of mismatch estimation in [13] (a) Output spectrum (b) Output spectrum    |    |

|      | chopped by $(-1)^n$ (c) Output spectrum chopped by $(-1)^n$ and Hilbert transformed | 69 |

| 3.15 | Direct alias cancellation structure: general                                        | 72 |

| 3.16 | Direct alias cancellation structure: in [32]                                        | 72 |

| 3.17 | Direct alias cancelation applied to a 2-channel case to show modulation being re-   |    |

|      | alized through Hadamard transform [34]                                              | 73 |

| 3.18 | Bandwidth mismatch calibration in [23] and [24] using polynomial expansion          | 74 |

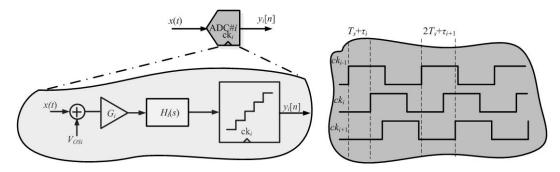

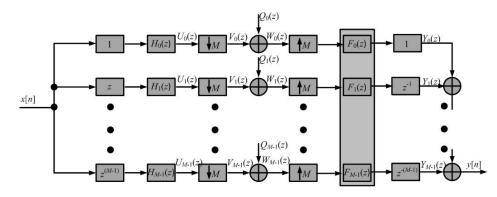

| 4.1  | Proposed architecture: top                                                          | 83 |

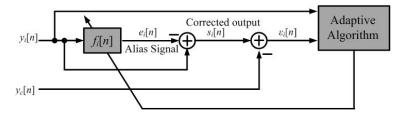

| 4.2  | Proposed architecture: sub-band                                                     | 84 |

| 4.3  | Proposed architecture: signal processing                                            | 84 |

| 4.4  | Proposed architecture: Correction Algorithm                                         | 86 |

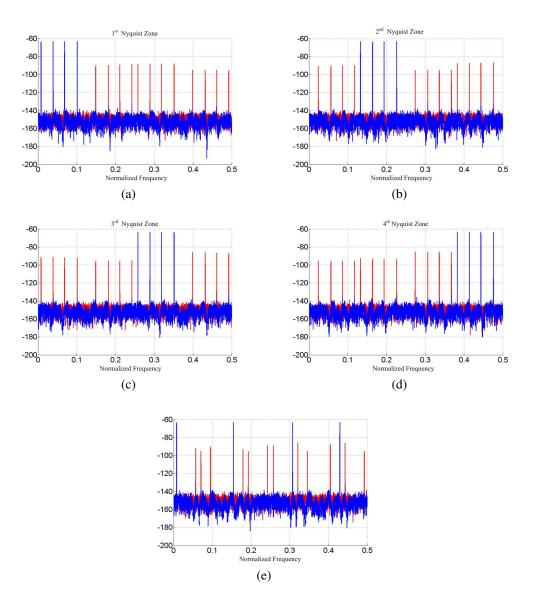

- 4.6 Simulation results for the proposed technique with rich inputs in(a) Nyquist zone1 (b) Nyquist zone 2 (c) Nyquist zone 3 (d) Nyquist zone 4 (e) All Nyquist zones . 94

# LIST OF TABLES

| 2.1 | Comparison with state-of-the-art | 41 |

|-----|----------------------------------|----|

|     |                                  |    |

| 4.1 | Comparison with state-of-the-art | 91 |

#### **ACKNOWLEDGMENTS**

I will take this opportunity to thank my advisor Dr. Sudhakar Pamarti for his support, encouragement and professionalism. His depth of knowledge, his mathematical skills, his intuitive abilities have left me in awe many a times and hopefully I have been able to inculcate bits and pieces of these during this journey of six years. Furthermore, his humility and friendly demeanor is greatly rewarding in this cold, competitive world.

I would like to thank my committee members Dr. Babak Daneshrad, Dr. Chih Kong Ken Yang and Dr. Milos Ercegovac for their important inputs during and after the defense process. I would also like to thank Dr. Behzad Razavi for his technical advice.

I would like to thank my group-members Nitesh, Nitin, Jeffrey, Neha, Manas, Sameed and Farid with whom I have had some fierce brain-storming sessions over coffee-walks, cubiclemarker-timepass, sushi-dosa-chronicles etc. Truly, I owe a lot of whatever I understand of electrical engineering to you guys. I would like to particularly thank Nitesh for showing me how amazingly beautiful signal processing can be and Neha for reviewing some of my papers.

I would also like to thank my UCLA friends who made my stay that much more bearable away from home. Nitin, Vaibhav, Joseph, Manas, Sameed, Richa, Amrutha, Pritika, Varun, Shaunak, Gaelen, Sneha, Preeti, Naresh, Gauresh, Nikhilesh, Mukesh, Hari, Vikrant (and several names that I don't recall now) have eased my life to unimaginable extents with night-outs, blood-spatteredwound-cures, culinary experiments, dinners, movies, crazy dance moves and the list is endless.

I would like to thank my undergraduate friends Chiranjib, Subhankar, Rudrajit, Amartya (and Snehal), Kaushik, Swarnavo, Shreepriya for the national park trips, weekend chats and calls that helped refresh in several ways. I would particularly like to thank Chiru for the intense technical discussions that we had during countless hours on PCH and IHOP which helped in more ways than he knows.

I will be indebted to my MaxLinear colleagues: Raja, Elias, Sheng, Vamsi, Sangeetha, AJ, Subhangshu, Sanjayan etc. for introducing me to the rungs of professionalism in industry and also thank them for my added bank balance!

This section would remain incomplete without thanking my fiancee Shweta. Her unflinching support during this entire journey, her childish jokes and taunts, her technical inputs, her practicality (in the face of my utopian existence) have all provided me with that post that one needs away from home. Thanks again dear and hope I can be of equal help in your times of need. On a related note, I would also like to thank Sanjay uncle, Snehal aunty and Sameer for their good wishes and support.

Lastly, I would like to thank my parents. It is they who have made me what I am today. Right from my kindergarten days to middle-school, from high-school to college, from college to PhD degree they have provided me with everything that I may have needed in all ways possible. Sitting 8000 miles away from each other has been a difficult experience for both of us, and hopefully the end justifies the means! Thanks again ma and baba and I dedicate this work to you.

#### VITA

| 1984      | Born, Calcutta (that was what this city was called then), West Bengal, India.  |

|-----------|--------------------------------------------------------------------------------|

| 2003–2007 | Bachelor of Technology, Electronics and Electrical Communication Engineer-     |

|           | ing, Indian Institute of Technology, Kharagpur, West Bengal, India             |

| 2007-2009 | Master of Science, Electrical Engineering, University of California, Los Ange- |

|           | les, California, USA                                                           |

| 2010-2013 | Research Assistant, Electrical Engineering, University of California, Los An-  |

|           | geles, California, USA                                                         |

#### PUBLICATIONS

- Abhishek Ghosh and Sudhakar Pamarti,"On the properties of filters for subtractive discrete dither in quantizers", in preparation for publication in *IEEE Trans. on Signal Processing*.

- Abhishek Ghosh and Sudhakar Pamarti, "Phase Mismatch Calibrations in Time-Interleaved ADCs: A Tutorial", in preparation for publication in *IEEE Trans. on Circuits and Systems-1*

- Abhishek Ghosh and Sudhakar Pamarti, "Linearization through dithering: A 50MHz bandwidth, 10-b ENOB, 8.2mW VCO-based ADC", in preparation for publication in *IEEE Journal of Solid-States Circuits*

- Abhishek Ghosh and Sudhakar Pamarti,"Phase Mismatches in Time-Interleaved ADCs: Adaptive signal-dependent digital solution to an analog problem", in preparation for publication in *IEEE Trans. on Circuits and Systems-I*.

- Abhishek Ghosh, Sudhakar Pamarti, "Enabling high-speed, high-resolution ADCs using adaptive signal conditioning techniques", *IEEE Mid-West Symposium on Circuits and Systems(MWSCAS)*, 2013

- Abhishek Ghosh, Sudhakar Pamarti, "A 50MHz bandwidth, 10-b ENOB, 8.2mW VCObased ADC enabled by filtered-dithering based linearization", *IEEE Custom Integrated Circuits Conference(CICC)*, 2013

- Abhishek Ghosh, Sudhakar Pamarti, "Filtering of subtractive discrete dither in quantizers: some new results", *International Conference on Acoustics, Speech and Signal Processing(ICASSP)*, 2013

- Abhishek Ghosh, Sudhakar Pamarti, "Mitigating timing errors in time-interleaved ADCs: a signal conditioning approach", *IEEE International Symposium on Circuits and Systems(ISCAS)*, 2013

- Abhishek Ghosh, Sudhakar Pamarti, "Adaptive signal conditioning algorithms to enable wideband signal digitization", *IEEE International Conference on Communications(ICC)*, 2013

- Chiranjib Choudhuri, Abhishek Ghosh, Urbashi Mitra, Sudhakar Pamarti, "Robustness of Xampling-based RF receivers against analog mismatches", *International Conference on Acous-*

tics, Speech and Signal Processing(ICASSP), 2012

- Abhishek Ghosh, Sudhakar Pamarti, "A novel quantization noise-cancelation technique in wideband D/A converters" *IEEE Mid-West Symposium on Circuits and Systems(MWSCAS)*, 2011

- Nitesh Singhal, Nitin Nidhi, Abhishek Ghosh, Sudhakar Pamarti, "A 19 dBm 0.13µm CMOS Parallel Class-E Switching PA with Minimal Efficiency Degradation under 6 dB Back-off" *Radio Frequency Integrated Circuits Conference(RFIC)*, 2011

- Venkat Rangan, Abhishek Ghosh, Vladimir Aparin, Gert Cauwenberghs, "A subthreshold aVLSI implementation of the Izhikevich simple neuron model", *IEEE Annual Conference, Engineering in Medicine and Biology Society(EMBS)*, 2010

## **CHAPTER 1**

# Filtering of subtractive discrete dither in quantizers: some new results

#### **1.1 Introduction**

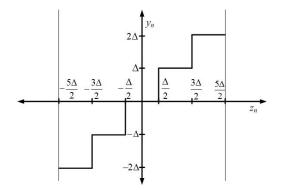

Quantizers are the portals to digital signal processing of all real-world signals and hence serve as the main interface between natural and machine-based signal processing. An example midtread quantizer is shown in Figure 1.1. As can be seen, the input-output characteristic of any example quantizer, is non-linear and hence signals when *quantized* result in errors which have significant dependence on the input signal and hence are spectrally non-white [1–3, 5]. A major understanding from these works is that the input signal to the quantizer needs to be equipped with certain statistical properties in order to ensure that the quantization error is white and its power is the ubiquitous  $\Delta^2/12$  ( $\Delta$  being the quantization step size). In most practical scenarios though, it is highly infeasible to handle signals with the required statistical properties. So, a small signal, random in nature (called *dither*) is added to the input in order to make the composite signal samples *unpredictable* at any given time.

#### 1.1.1 Dithered quantization

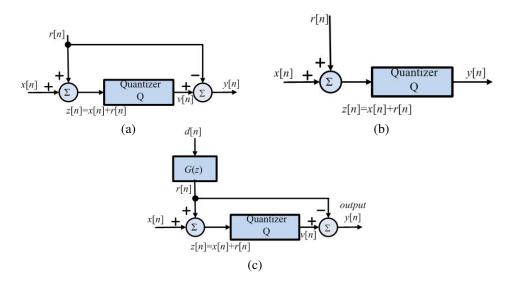

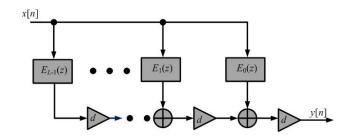

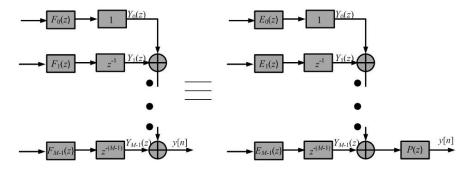

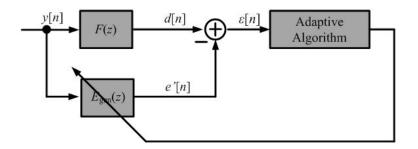

Let us define a dithered quantizer more formally. A behavioral schematic is presented in Figure 1.2. A random signal r[n] is added to the signal to be quantized x[n] and the composite signal z[n] = x[n] + r[n] is passed through the quantizer. A dithered quantizer can be implemented in a few different flavors, each unique in the properties it imparts to the quantization error, Figures 1.2(a)-(c).

In Figure 1.2(a), the added dither signal r[n] is subtracted digitally from the quantized value y[n] and hence is called a *subtractively dithered quantizer*. Likewise, Figure 1.2(b) refers to a nonsubtractively dithered quantizer (commonly phrased as additive dithered quantizer). The added dither, r[n] is usually constrained to be bounded between one least significant bit (LSB) of the quantizer. Separate conditions [3] have been theoretically derived for either case to ensure that the error-samples (e[n] = y[n] - z[n] for Figure 1.2(a) and e[n] = y[n] - x[n] for Figure 1.2(b)) are independent (among themselves as well as of the input) and uniformly distributed both in terms of first and second order statistics. Henceforth, such error would be called *well-behaved* in this paper. It is found that a well-behaved quantization error can be guaranteed, for a subtractive dithered quantizer, if the dither statistics satisfies certain properties. The simplest class of dither conforming to these statistics is a uniformly distributed dither. However, for an additive dither situation, such conditions are not easily derivable [3].

Unfortunately, a uniformly distributed white dither signal, r[n] would contribute too much noise to the quantizer output. In fact, a uniformly distributed dither signal spanning one quantizer LSB would degrade the overall signal-to-noise ratio (SNR) by 3dB. Furthermore, it may be im-

Figure 1.1: Mid-tread quantizer

possible or at least extremely challenging to digitally generate such analog dither [6]. The second problem is solved using hardware-friendly digital dither (that spans only a finite set of values), while the first problem is solved by spectrally shaping such dither out of the band of interest using digital filters [4]. Such an architecture is presented in Figure 1.2(c) as an extension of Figure 1.2(a), where d[n] is a Bernoulli signal with equal probability of a 0 or 1. However, filtering a signal tantamounts to modifying its statistical properties. Consequently, the error signal e[n] in Figure 1.2(c) may not be well-behaved as noted above even if d[n] is sample-wise independent, identically distributed (i.i.d.) and white.

#### 1.1.2 Prior-art

There have been some very interesting works treating filtered dither signals and their efficacies in whitening the quantization error [4,7,8]. With reference to Figure 1.2(c), in [4], a detailed analysis is done on the properties of r[n] where d[n]'s are i.i.d. random variables. However, the analysis is specific to additive dithered quantizers and imposes very strict conditions on the filter-coefficients (finite (FIR) or infinite (IIR) impulse response). In [8], a simplified condition is derived for FIR filters. However, the quantizer treated in [8], works on integer valued inputs only while the work

Figure 1.2: Dithered Quantizers: (a) Subtractive (b) Non-subtractive/Additive (c) Filtered-subtractive

in [7] provides conditions for the impulse response of an IIR filter (integrator in feed-forward path of a sigma-delta modulator).

#### 1.1.3 Contribution

The main contribution of this work is the formulation of conditions for integer-valued FIR filters operating on continuous-valued inputs for a subtractively dithered quantizer. We theoretically derive conditions for the error-sequence, subject to such filtering, to be well-behaved. In the next section, we detail the behavioral model to be used in all subsequent derivations. Section 1.3 furnishes the main theoretical results accompanied by some relevant proofs while Section 1.4 provides an insight into the simulation results to validate the theory. We conclude the paper in Section 1.5.

#### **1.2 Behavioral model**

The model is as presented in Figure 1.2(c). Let us define an i.i.d. Bernoulli sequence d[n] that follows the statistics:  $\mathbb{P}r(d[n] = 0) = \mathbb{P}r(d[n] = 1) = 0.5$ . The sequence d[n] is passed through a digital filter G(z) having a finite impulse response  $g[n] \in \mathbb{Z}$  of length K to produce an output r[n]. The filter gain is so adjusted that the output r[n] spans  $\Delta$ , LSB of the quantizer. Consequently, the filtered output r[n] can be expressed as

$$r[n] = \frac{\Delta}{L} (g[0]d[n] + g[1]d[n-1] + \dots$$

....+ g[K-1]d[n-K+1]) (1.1)

where  $L = \sum_{i=0}^{K-1} |g[i]|$ . The quantity  $\Delta/L$  can be thought of as the dither LSB (the minimum resolution of the added signal  $r_n$ ). The input signal x[n] is assumed to be of arbitrary distribution and bounded in  $[-(Q - 1)\Delta/2, (Q - 1)\Delta/2]$  for a Q-level quantizer ( $Q \in \mathbb{N} \cap (1, \infty)$ ). The signal r[n] is added with the input x[n] to result in the composite signal z[n] = x[n] + r[n]. z[n] is quantized to generate v[n]. The added dither signal r[n] is subtracted from v[n] to result in the actual output y[n]. The resultant quantization error is defined as e[n] = y[n] - x[n] =v[n] - x[n] - r[n].

*Note-1*: Since the dither resolution is finite, namely  $\Delta/L$ , hence any input of the form  $x[n] = [x[n]] + \langle x[n] \rangle$  where  $[x[n]] = k\Delta, k \in \mathbb{Z}$  and  $\langle x[n] \rangle < \Delta/L$  will not *see* the effect of the added dither, and hence the quantization error will not be guaranteed to be well-behaved. In the remainder of the paper, we shall assume that the input signal x[n] excludes the above special class of signals.

*Note-2*: In the following arguments,  $w_j$  and w[j] would refer to the same quantity and will be used interchangeably.

#### **1.3** Main result: theory

**Theorem 1.** For a dithered quantizer, modeled in Section 1.2,

*P.1)* The error sequence  $e_n$  is an identically distributed uniform random variable independent of the input  $x_{n-m}$ ,  $\forall k_1 \in \mathbb{Z}$ ,  $\forall m \in \mathbb{Z}$  if and only if  $(\langle \rangle_T \text{ operator denotes modulo-}T \text{ operation})$

C.1) A non-negative integer i < K exists such that  $\langle g_i k_1 \rangle_L = L/2$

P.2) The error sequence pair  $(e_n, e_{n-p}) \forall p \in \mathbb{Z} \cap (0, K)$  is pairwise independent, each being an identical uniform distribution  $\forall (k_1, k_2) \neq (0, 0)$  if and only if either of the following are true

C.2) A non-negative integer l < p exists such that  $\langle g_l k_1 \rangle_L = L/2$

C.3) A non-negative integer  $1 \le r \le p$  exists such that  $\langle g_{K-r}k_2 \rangle_L = L/2$

C.4) A non-negative integer  $p \le m < K$  exists such that  $\langle g_m k_1 + g_{m-p} k_2 \rangle_L = L/2$

*P.3)* The error sequence pair  $(e_n, e_{n-p}) \forall p \in \mathbb{Z} \cap [K, \infty)$  is pairwise independent, each being an identical uniform distribution  $\forall (k_1, k_2) \neq (0, 0)$  if both the following conditions hold

C.5) The FIR filter coefficients g[k] are of the form  $2^i$  where *i* takes on each value in [0, s - 1] at least once and

C.6)

$$L = \sum_{i=0}^{K-1} |g[i]| = 2^s$$

where  $s \in \mathbb{Z} \cap (1, K]$

*Remark*: For notational convenience, all properties are denoted as P.'s while all conditions are denoted as C.'s. Both P.1 and P.2 are *if and only if* conditions while P.3 is only a sufficiency condition. The strategy of the proof would be to proceed with P.2 first. The proof of P.1 would follow next while P.3 would be proved as a consequence of P.2 and would form the main result of this work, providing easy-to-use closed form solutions for the shaping filter G(z). Let us proceed

with P.2 now.

*Proof.* The proof would use characteristic functions [9] to derive conditions on the specific properties of the added dither signal. This is a commonly used technique for such applications [8]. In fact, from [3], we know, that the joint characteristic function (jcf) for error-samples  $(e_n, e_{n-p})$  can be written as,  $\forall p \in \mathbb{Z} \cap (0, K)$  for  $(k_1, k_2) \in \mathbb{Z}^2$

$$\Phi_{e_n,e_{n-p}}(u_1,u_2) = \sum_{k_1=-\infty}^{\infty} \sum_{k_2=-\infty}^{\infty} \frac{\sin(\pi\Delta(u_1 - k_1/\Delta))}{(\pi\Delta(u_1 - k_1/\Delta))}$$

$$\frac{\sin(\pi\Delta(u_2 - k_2/\Delta))}{(\pi\Delta(u_2 - k_2/\Delta))}$$

$$\Phi_{x_n,x_{n-p}}(\frac{-2\pi k_1}{\Delta}, \frac{-2\pi k_2}{\Delta})$$

$$\Phi_{r_n,r_{n-p}}(\frac{-2\pi k_1}{\Delta}, \frac{-2\pi k_2}{\Delta})$$

(1.2)

Hence, for the joint density of  $(e_n, e_{n-p})$  to be uniform and pairwise independent, it suffices to show [3],

$$\Phi_{r_n, r_{n-p}}\left(\frac{-2\pi k_1}{\Delta}, \frac{-2\pi k_2}{\Delta}\right) = 0$$

$$\forall (k_1, k_2) \in \mathbb{Z}^2 - (0, 0)$$

(1.3)

The jcf of the dither samples  $(r_n, r_{n-p})$  is defined as

$$\Phi_{r_{n},r_{n-p}}(u_{1},u_{2}) = \mathbb{E}(e^{j(u_{1}r_{n}+u_{2}r_{n-p})})$$

$$= \mathbb{E}(e^{j\frac{\Delta}{L}(u_{1}\sum_{m=0}^{K-1}g_{m}d_{n-m}+u_{2}\sum_{l=0}^{K-1}g_{l}d_{n-p-l})})$$

$$= \prod_{l=0}^{p-1} \Phi_{d}(\frac{\Delta}{L}u_{1}g_{l})$$

$$\prod_{m=p}^{K-1} \Phi_{d}(\frac{\Delta}{L}(u_{1}g_{m}+u_{2}g_{m-p})))$$

$$\prod_{r=1}^{p} \Phi_{d}(\frac{\Delta}{L}u_{2}g_{K-r})$$

(1.4)

Now, for a Bernoulli dither  $d_n$ , with  $\mathbb{P}r(d_n = 0) = \mathbb{P}r(d_n = 1) = 0.5$ ,

$$\Phi_d(v) = e^{(-jv/2)} \cos(v/2)$$

(1.5)

From Eqn. (1.3), we need to evaluate Eqn. (1.4) for  $u_{1,2} = 2\pi k_{1,2}/\Delta$ . Thus, from Eqns. (1.4) and (1.5), we can write  $\forall (k_1, k_2) \in \mathbb{Z}^2 - (0, 0)$

$$|\Phi_{r_{n},r_{n-p}}(-\frac{2\pi k_{1}}{\Delta},\frac{-2\pi k_{2}}{\Delta})| = \prod_{l=0}^{p-1} |\cos(\frac{\pi k_{1}g_{l}}{L})|$$

$$\prod_{m=p}^{K-1} |\cos(\frac{\pi (k_{1}g_{m}+k_{2}g_{m-p})}{L})|$$

$$\prod_{r=1}^{p} |\cos(\frac{\pi k_{2}g_{K-r}}{L})|$$

(1.6)

This proves the *sufficiency* of the theorem, since if any one of the product series terms is zero (C.2-4), P.2 is satisfied.

Necessity: The necessity conditions can be likewise argued, and is omitted here for brevity.

*Discussion*: It may not be always possible to design FIR filter coefficients satisfying conditions C.2-4 of Theorem 1 since the filter coefficients are not available in a closed-form solution. Furthermore, it's not practically possible to evaluate the characteristic function in Eqn. (1.6). at all integer values of  $(k_1, k_2)$  to identify an appropriate filter structure. P.3 addresses this issue in further detail.

For the proof of P.1, we write the probability density function (pdf) of the error sequence  $e_n$ conditioned on the input  $x_{n-m} \forall m \in \mathbb{Z}$  as

$$p_{e_n|x_{n-m}}(a|b) = \sum_{l=-\infty}^{\infty} p_{z_n|x_{n-m}}(-a+l\Delta|b)$$

(1.7)

Now, it is not difficult to see that

$$p_{z_n|x_{n-m}}(c|b) = p_{x_n+r_n|x_{n-m}}(c|b)$$

$$= p_{x_n|x_{n-m}}(c|b) * p_{r_n}(c)$$

(1.8)

since  $r_n$  is independent of both  $x_n$  and  $x_{n-m}$  where a, b and c are in the appropriate domains and \* denotes convolution.

Thus, from Eqns. (1.7) and (1.8), the characteristic function (cf) of  $e_n$  conditioned on  $x_{n-m}$ ,

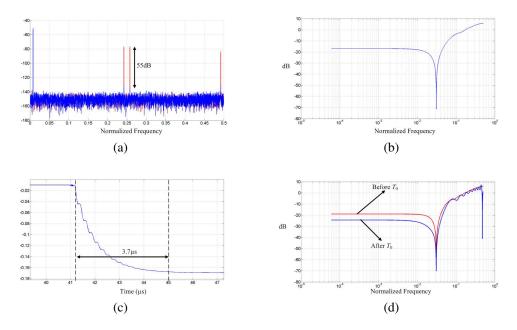

(e) Output spectrum for three different scenarios

Figure 1.3: Simulation results

can be written as

$$\Phi_{e_{n}|x_{n-m}}(u) = \frac{1}{\Delta} \sum_{k=-\infty}^{\infty} \Phi_{x_{n}|x_{n-m}}(-u)$$

$$\prod_{i=0}^{K-1} \Phi_{d_{n}}(-ug_{i}\frac{\Delta}{L}) \frac{\sin(\pi\Delta(u_{1}-k_{1}/\Delta))}{(\pi\Delta(u_{1}-k_{1}/\Delta))}$$

(1.9)

For the error-sequence  $e_n$  to be independent of  $x_{n-m}$  and be uniformly identically distributed,  $\Phi_{e_n|x_{n-m}}(-\frac{2\pi k_1}{\Delta})$  must evaluate to 0 for every  $k_1 \neq 0$ . For this to happen, for any arbitrary input, from the proof of P.2,

$$\prod_{i=0}^{K-1} |\Phi_{d_n}(\frac{-2\pi k_1 g_i \frac{\Delta}{L}}{\Delta})| = \prod_{i=0}^{K-1} |\Phi_{d_n}(\frac{-2\pi k_1 g_i}{L})| = \prod_{i=0}^{K-1} |\cos(\frac{\pi k_1 g_i}{L})| = 0$$

(1.10)

Eqn. 1.10 holds if and only if C.1 holds (the argument of at least one cosine term is driven to an odd multiple of  $\pi/2$ ) hence proving P.1

The proof of P.3 will lead from that of P.2 through an important observation. Since,  $p \ge K$ , hence it is not difficult to see that,

$$p_{r_n,r_{n-p}}(r_1,r_2) = p_{r_n}(r_1)p_{r_{n-p}}(r_2)$$

$$\Phi_{r_n,r_{n-p}}(u_1,u_2) = \Phi_{r_n}(u_1)\Phi_{r_{n-p}}(u_2)$$

(1.11)

Now, from Eqn. (1.3), we need to prove that  $\Phi_{r_n,r_{n-p}}(\frac{-2\pi k_1}{\Delta},\frac{-2\pi k_2}{\Delta})$  goes to zero for all values

of  $(k_1, k_2) \in \mathbb{Z}^2 - (0, 0), \forall p \in \mathbb{Z} \cap [K, \infty)$ . Based on Eqns. (1.4)-(1.6), this is equivalent to proving

$$\prod_{i=0}^{K-1} |\cos(\frac{\pi k_1 g_i}{L})| |\cos(\frac{\pi k_2 g_{K-1-i}}{L})| = 0$$

(1.12)

for all values of  $(k_1, k_2) \in \mathbb{Z}^2 - (0, 0), \forall p \in \mathbb{Z} \cap [K, \infty).$

It is interesting to note that Eqn. (1.12) leads to an *L*-periodic sequence (in  $k_1$  or  $k_2$ ) if condition C.1 is satisfied. Consequently, it suffices to evaluate the cf of Eqn. (1.12) in a finite set of  $L^2$  points. Now it becomes useful to consider the following cases,  $\forall (k_1, k_2) \in [-L/2 + 1, L/2]$  assuming the conditions in Theorem 1 hold (sufficiency).

- $k_1 = odd, k_2 = odd$  One product term of the right-hand side of Eqn. (1.12) can be written as  $\cos(\pi k_j \frac{2^r}{2^s}), j = 1, 2$ . Hence for r = s 1, we can write the product term as  $\cos(\frac{\pi}{2}k_j)$  which goes to 0 since  $k_{1,2}$  are odd.

- $k_1 = odd, k_2 = even$  Here,  $k_1$  will drive the product term to 0 for r = s 1. The symmetric case of  $k_2 = odd, k_1 = even$  similarly can be shown to equate to 0.

- $k_1 = even, k_2 = even$  Here, let  $k_{1,2} = 2^l(2m+1), l \le s-1$  for any integer m. Then the product term containing r = s 1 l would yield  $\cos(\frac{\pi}{2}(2m+1))$  which again goes to 0.

*Discussion*: C.5 and C.6 give easy formulae to design the dither-shaping filter. The proposed solution to Eqn. (1.12) may not be unique (under investigation), but the aforementioned conditions are in tune with powers-of-2 FIR filters [10], and hence amenable to facile design. It should further be noted that condition C.5 is a subset of C.1 and hence ensures an uniformly distributed

error sequence independent of the input. It is of interest to observe that though P.5 proves pair-wise independence only for error samples separated by more than K, for all practical purposes the error is white with a uniform distribution.

#### **1.4 Main results: simulation**

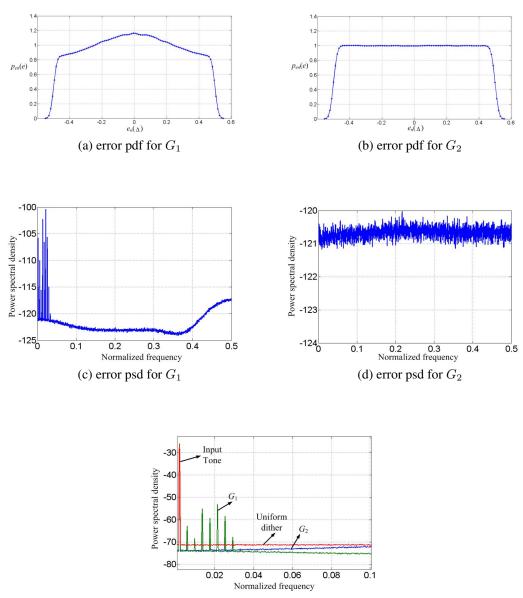

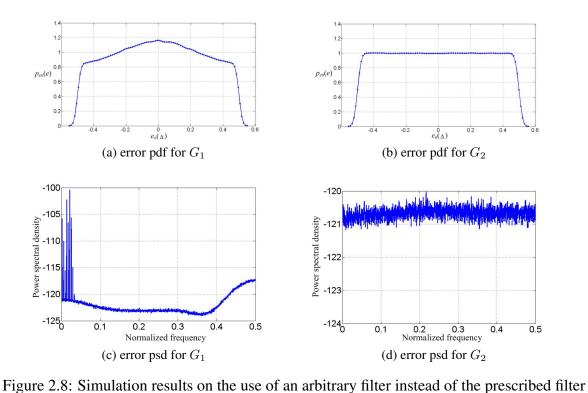

Let us consider two filters,  $G_1(z)$  and  $G_2(z)$  (z-transforms of 2 example filters  $g_1[n]$  and  $g_2[n]$ respectively) such that the former satisfies neither of C.5 and C.6 while the latter satisfies both.

$$G_{1}(z) = 1 - 3z^{-1} + 5z^{-2} - 9z^{-3} + 3z^{-4} - 3z^{-5}$$

$$+ 9z^{-6} - 5z^{-7} + 3z^{-8} - z^{-9}$$

$$G_{2}(z) = -1 - 2z^{-1} - 4z^{-2} - 8z^{-3} + 16z^{-4} - z^{-5}$$

The input x[n] is chosen to be a continuous-valued sinusoid at a normalized frequency of 0.002 with an amplitude of  $2\Delta$ . The signal is quantized into Q = 5 levels as in Figure 1.1. In Figure 1.3(a),(b), we plot the pdf of the error sequence  $e_n$  for both the cases, while Figure 1.3(c)(d) shows the spectra of the error signal. As can be clearly seen, the proposed filter, namely  $G_2$ , whitens the error-sequence and exhibits an almost uniform pdf (Figure 1.3(b)) while  $G_1$  shows an almost triangular pdf (Figure 1.3(a)) for the error samples. The error power spectral density (psd) for  $G_2$ (Figure 1.3(d)) is *white*, while the error psd for  $G_1$  exhibits multiple spurious tones at harmonic frequencies (as is expected from a lookup table type non-linearity) (Figure 1.3(c)). In order to make a fair comparison, a third case where a uniform dither signal r[n] (the case in Figure 1.2(b)) is added to the input signal before quantizing, is also considered. The spectra of y[n] = x[n] + e[n] is plotted for all the three cases:  $G_1, G_2$  and uniform dither in Figure 1.3(e). As can be seen, the uniform dithered quantizer contributes the maximal in-band power while whitening the output spectrum completely.  $G_2$  shapes the in-band dither power, as well as gets rid of any spurious components, while  $G_1$  has the least in-band dither power contribution but engenders harmful spurious tones at the quantizer output. This is expected since, from P.1 e[n] being independent of x[n] bequeaths the well-behaved properties of e[n] on y[n].

## 1.5 Conclusion

A filtered dithering technique in quantizers is proposed. Theoretical conditions on the filter structure are derived to ensure independence, whiteness and uniform distribution of the quantization error signal. Behavioral simulation results are presented to corroborate the proposed results and claims.

## REFERENCES

- Sripad, A.; Snyder, D.; , "A necessary and sufficient condition for quantization errors to be uniform and white," *Acoustics, Speech and Signal Processing, IEEE Transactions on*, vol.25, no.5, pp. 442- 448, Oct 1977

- [2] Widrow, B.; Kollar, I.; , "Quantization Noise: Roundoff Error in Digital Computation, Signal Processing, Control, and Communications," *Cambridge University Press*, Cambridge, UK

- [3] Lipshitz, S.P.; Wannamaker, R.A.; Vanderkooy, J.; Wright, J.N.; , "Quantization and dither: a Theoretical Survey," in *J.AudioEng.Soc.*, ,Vol.40, no.5, May 1992.

- [4] Wannamaker, R.A.; Lipshitz, S.P.; Vanderkooy, J.; , "Dithered quantizers with and without feedback," *Applications of Signal Processing to Audio and Acoustics*, 1993. Final Program and Paper Summaries., 1993 IEEE Workshop on , vol., no., pp.140-143, 17-20 Oct 1993

- [5] Gray, R.M.; Stockham, T.G., Jr.; , "Dithered quantizers," *Information Theory, IEEE Transac*tions on , vol.39, no.3, pp.805-812, May 1993

- [6] Borkowski, M.J.; Kostamovaara, J.; , "On randomization of digital delta-sigma modulators with DC inputs," *Circuits and Systems, 2006. ISCAS 2006. Proceedings. 2006 IEEE International Symposium on*, vol., no., pp.4 pp., 21-24 May 2006

- [7] Pamarti, S.; Welz, J.; Galton, I.; , "Statistics of the Quantization Noise in 1-Bit Dithered Single-Quantizer Digital DeltaŰSigma Modulators," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.54, no.3, pp.492-503, March 2007

- [8] Pamarti, S.; Delshadpour, S.; , "A Spur Elimination Technique for Phase Interpolation-Based Fractional- N PLLs," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol.55, no.6, pp.1639-1647, July 2008

- [9] Papoulis, A.; Pillai, S.; , "Probability, Random Variables and Stochastic Processes," *McGraw Hill*, 2001

- [10] Y. Lim and S. Parker, "FIR filter design over a discrete powers-of-two coefficient space," *IEEE Trans. Acoust., Speech, Signal Process*, vol.31, no.3, pp.583Ű591, 1983

# **CHAPTER 2**

# Linearization through dithering: A 50MHz bandwidth, 10-b ENOB, 8.2mW VCO-based ADC

## 2.1 Introduction

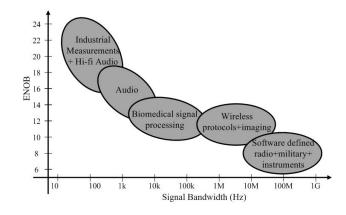

With both wireless communication and imaging applications pushing for higher data rates there is an ever-increasing demand for wideband, high resolution analog-to-digital converters (ADCs). Figure 2.1 projects the wireless and imaging industry requirement in perspective with other popular electronic industries. As can be seen from Figure 2.1, signals in the few tens of MHz range need to be digitized to about 10 - 12 bits accuracy for our target application [1]. Furthermore, such ADCs are often assembled in millions (imaging) or deployed in portable devices imposing strict power consumption limits on a single ADC for enhanced battery-life leading to ease of portability. Several prominent candidates viz. successive approximation register (SAR), oversampling converters lay claim to this application with excellent results [2–4].

SAR ADCs have enjoyed a renewed interest owing to the immense power benefits they offer, particularly in finer technology nodes [2]. However, SAR ADCs are often found to have limited dynamic ranges owing to issues of comparator noise and mismatches between the capacitive

Figure 2.1: ADC performance and applications

digital-to-analog converter (CDAC) elements. Oversampling noise-shaping converters are also being revived in swathes for the power-efficiency they offer for low-moderate bandwidth signals. Furthermore, continuous-time sigma-delta modulators offer an inherent anti-aliasing that relaxes the requirements on the ADC dynamic range by a great amount [3,4]. However, the problem with noise-shaping ADCs stems from the fact that loop-filters embedded in the loop prove to be a major power sink owing to the high unity gain-bandwidth requirements on them [3]. In addition, the feedback DACs need to be linearized to a high degree for a high-resolution operation which imposes extra power-consumption constraints on the overall design. Furthermore, the largely analog implementation does not admit an easy scaling with process technology that is critical for finer complementary metal-oxide semiconductor (CMOS) nodes.

Voltage-controlled oscillator (VCO)-based ADC has surfaced as a power-efficient, technologyscalable and simple alternative to conventional  $\Sigma - \Delta$  modulators [5–14]. The fact that VCO-based architectures are mostly digital makes them amenable to a digital synthesis flow and hence highly attractive from a simplicity-of-design point of view. In spite of all its attractiveness, VCO-based ADCs are plagued by the problem of frequency-voltage non-linearity typical of the VCO core that limits the overall achievable dynamic range of the entire system. Several approaches have been proposed to allay the non-linearity problem in VCO-ADCs. However, most of these approaches are prohibitively power-hungry, or are not real-time. We shall look into some of these approaches in some detail in the subsequent sections.

In contrast, this work proposes a dithered feed-forward system wherein the input to the VCO is made to look like *white noise* [15]. As a result, the non-linearity in the VCO can only further scramble this noise losing potency to produce spurious signal content. Oversampling in the system suppresses the impact of the scrambled noise within the signal spectrum. The architecture avoids brute-force calibration as well as power-consuming op-amps to suppress the VCO non-linearity.

As a starting basis, however, we shall look into the basic operation of a VCO-ADC first in Section 2.2. Section 2.3 delves into the prior-art that aims to alleviate the non-linearity to develop a high resolution system. Section 2.4 presents the proposed architecture and explains the signal processing details followed by the circuit design nuances in Section 2.5. Section 2.6 shows the test setup and the measurement results for the prototype. Section 2.7 concludes the paper.

## 2.2 Ring oscillator based VCO-ADC

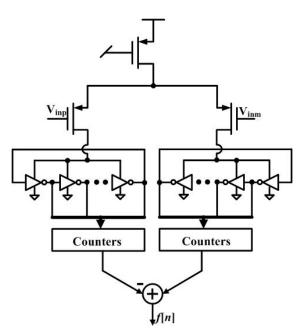

The basic concept of a VCO-based ADC is shown in Figure 2.2(a). The input signal  $V_{in}[n]$  is applied to the control voltage of a ring-VCO. The frequency of oscillation is proportional to  $V_{in}[n]$ as shown in Figure 2.2(a). Digital counters following the VCO count the number of rising/falling edges of the VCO output(s),  $\Phi_i[n]$ , during each sample period  $T_s$ . The counter outputs are accumulated to result in the final digital output, y[n]. As a result, depending on the frequency of

(b)

To counters

Figure 2.2: VCO-based ADC (a) The Good (b) The Bad and the Ugly

oscillation (that is a direct function of the input voltage), the count y[n] gives a quantized measure of the input, which is the basic principle of any ADC. A VCO-based ADC essentially works upon the principle of phase quantization. Consequently, to maintain continuity in phase between two consecutive sample periods, the present cycle remembers the residual phase of the previous cycle. Based on this argument, it can be shown that the noise introduced due to phase-quantization gets first-order shaped spectrally  $(1 - z^{-1})$  [5, 6, 8]. Hence, ring VCO-based ADCs implement, in effect, a first-order  $\Delta - \Sigma$  system at a minimal power expense in a low complexity, mostly digital regime [10, 11]. Also note from Figure 2.2(a) that the VCO-based ADC is free of expensive analog blocks such as amplifiers and is mostly digital. This offers several benefits most of which improve with technology scaling: it can operate at low supply voltages unlike traditional amplifier based ADC designs; it occupies very little die area and consumes very little power. These benefits make the VCO-based ADC particularly suitable for the target application (Figure 2.1).

Figure 2.3: Representative signal processing view of VCO-based ADC

However, as hinted in the last section, ring VCOs are quite non-linear. As shown in Figure 2.2(b), the voltage vs. frequency curve of the VCO (often called a tuning curve) is not at all linear. This causes elevated noise floor and spurious tones, thus degrading the spurious free dynamic range (SFDR) and the signal-to-noise-and-distortion-ratio (SNDR) of the ADC.

Besides, there is an additional issue that needs to be dealt with that proves to be a hurdle to building a high-resolution system. The ring-VCO is constituted of multiple delay elements in cascade. Nominally the delays through these elements are matched. However, as illustrated in Figure 2.2(b), inevitable mismatches in the integrated circuit (IC) fabrication process induce mismatch in these delays. Furthermore, voltage-temperature (VT) variations across the die also effect delay mismatches. The mismatches act as look-up table type of non-linearity further degrading the SFDR. However, typically impact of the mismatch is at a much lower level than that of the tuning curve non-linearity and poses as a second-order effect.

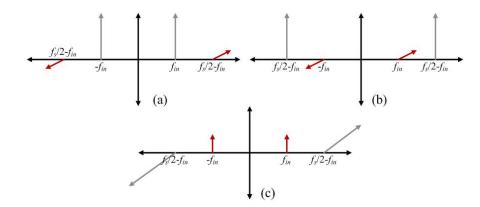

Figure 2.3 plots a representative spectrum of the case where a tonal input x[n] is passed through a VCO-based ADC resulting in y[n]. Note the first-order shape of the accompanying quantization error in  $S_{yy}(e^{j\omega})$ . The harmonic content visible in  $S_{yy}(e^{j\omega})$  underscores the non-linear behavior of the system, limiting the achievable SNDR to only about 6 - 7 bits.

## 2.3 Prior-art

Multiple approaches have been proposed to linearize such an ADC to enhance its dynamic range. The major classes of calibration styles for VCO-ADCs can be categorized into four major groups.

#### 2.3.1 Feedback Loop

Like all non-linear systems, feedback is invoked here as well to reduce the effects of non-linearity. Specifically, the VCO-ADC is embedded within a  $\Delta - \Sigma$  loop acting as the quantizer illustrated in Figure 2.4(a). The quantizer is preceded by an analog loop-filter of high order ( $\geq 3$ ). As a result, the VCO sees a small dynamic range signal (the error signal from negative feedback) thereby exercising a small portion of the VCO tuning curve, hence reducing the effects of the non-linearity. However, the analog loop-filter is composed of power-hungry opamps which burn large amounts of static power in order to effect a high filter order [5–7]. Thus, the overall power-efficiency of the system degrades. Furthermore, the opamps in the signal path impose bandwidth constraints and negate several of the aforementioned scaling benefits offered by VCO-based ADCs.

Figure 2.4: VCO-based ADC prior-art (a) Negative feedback through  $\Delta - \Sigma$  loop (b) Nonlinearity calibration (c) Input conditioning (d) Pipelining

#### 2.3.2 Foreground Calibration

The VCO-nonlinearity is estimated by applying some known signals in a separate calibration phase. The non-linearity, so estimated is fitted to a polynomial and stored in a look-up table. During actual operation, the ADC output is queried against the look-up table to produce the calibrated result as shown in Figure 2.4(b). However, such techniques are beset with multiple problems. Firstly, looking up a memory for calibration has to happen at the sample-rate of the ADC and can involve a large amount of power consumption. Secondly, the estimated non-linearity is not tracked

real-time and hence overlooks temperature variations, that may prove critical in system-on-chip (SoC) environments [8,9].

#### 2.3.3 Background calibration

The VCO non-linearity is estimated continuously with the signal without any separate calibration phase (Figure 2.4(b)). Multiple approaches have been proposed to implement the calibration. In [10, 11], the estimation is done using digital dither as a polynomial expansion using multiple digital correlators. The ADC output is subsequently calibrated using the inverse non-linearity, so estimated. This is an attractive approach in the spirit of digital leanings, but can become quite power-hungry since a significant amount of complex digital circuitry switches at the high sampling speed of the ADC [10]. In [12], a replica VCO is used to construct the look-up table in real-time that attempts to track the variations in the actual ADC. The correction is obviously done real time similar to the look-up table queries as described in the foreground mode. This approach is also beset by problems of high power consumption due to high-speed memory access.

#### 2.3.4 Input conditioning

In a few implementations, the input to the VCO-based ADC is suitably conditioned so that it exercises the tuning curve of the VCO in a *linear* manner. An interesting way to effect such conditioning is to encode the amplitude information of the input signal as phase/duty-cycle/pulse-width etc shown in Figure 2.4(c). Such techniques are quite common in transmitter topologies. The work in [13] converts the input signal into a pulse-width modulated (PWM) signal which in an amplitude sense excites only two points of the tuning curve, an operation that is inherently linear.

However, the pulse-width modulator itself consumes significantly large amounts of power and if not designed with caution can spawn undesired non-linear components of its own.

#### 2.3.5 Pipelining

The VCO-ADC is preceded by a coarse-stage ADC such that the former only processes the residue from the coarse stage illustrated in Figure 2.4(d) [7, 14]. The idea is thematically similar to the negative feedback approach for here also the idea is to *show* the VCO a small dynamic range signal to elicit lower non-linearity effects. Depending on the resolution of the coarse-stage the VCO input can have a quite small dynamic range. The outputs of the 2 ADCs are subsequently combined (like in a pipelined ADC) to result in the overall output. However, this approach has to deal with multiple issues. Firstly, to maintain an overall power-budget, the coarse ADC is typically of low resolution ( $\leq 3$  bits). Consequently, the residue fed to the VCO is highly correlated with the input signal [17]. As a result, the non-linearity in the VCO brings out these correlations even further leading to uncorrected input-dependent spurious content in the VCO-ADC output. Representative time-domain waveforms for a sinusoidal input accompany Figure 2.4(d) to emphasize the abovementioned point. In particular, note the periodicities in the residue signal e[n] that corroborates the demerit of the approach. A second issue is that the gain through the VCO-ADC is an unknown quantity, which needs to be accounted so that the ADC outputs can be combined with minimal coarse-error (e[n]) (from Figure 2.4(d)) leaking to the overall output. Typically ad-hoc approaches are resorted to wherein this gain is manually estimated, that makes the system impractical for continuous operations.

With a different approach to tackle the problem in a power-efficient way, this work employs

Figure 2.5: Coarse dithering to linearize VCO-based ADC (a) Behavioral model (b) Simulation result

shaped digital dither to essentially randomize the input to the VCO-based ADC in a 0 - 1 MASH architecture, thereby rendering it insensitive to VCO non-linearity [15].

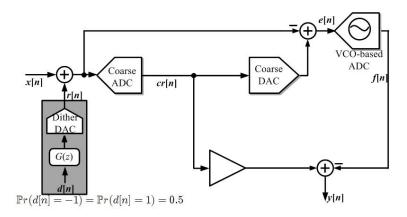

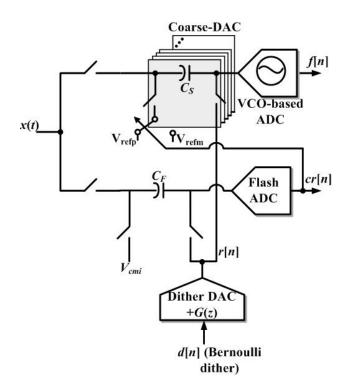

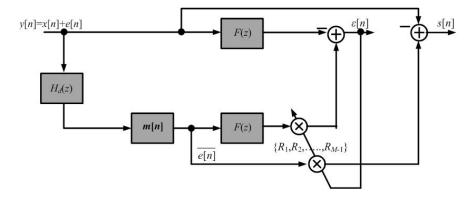

# 2.4 Proposed Technique: System Level

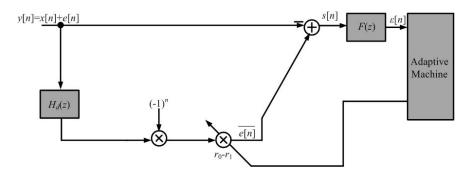

For notational convenience, in the art of noise-shaping modulators, i - j MASH refers to a cascaded structure where a *i*-th order noise-shaped modulator is followed by a *j*-th order one. In that paradigm, [14] implements a 1 - 1 MASH structure (the second "1" refers to the VCO-ADC) while [16] implements a 0-3 structure ("3" is a conventional  $\Delta - \Sigma$  modulator). We noted from the pipelining approach (in the last section, Figure 2.4(d)), that for a low-resolution coarse ADC, the residue (quantization error) is deeply correlated with the input signal. As a result, the fine stage (VCO-ADC) further brings out these correlations that remain uncorrected in the overall output. One possible way to further randomize the input to the VCO is to dither the coarse-stage ADC as shown in Figure 2.5(a). An uniformly distributed random signal spanning a coarse-LSB ( $\Delta$ ), dither, is injected to the input signal. Note that Figure 2.4(d) has been redrawn into a 0-1 structure in Figure 2.5(a) with the dithering introduced. Such class of dithering is called subtractive, since the dither signal is subtracted from the quantized output to generate the residue<sup>1</sup>. In a behavioral simulation, a sinusoidal input is passed through the structure in Figure 2.5(a) and the power spectral density of the total output y[n] is plotted in Figure 2.5(b). The quantization error from the coarse stage is completely whitened (uncorrelated with the input). However, the coarse ADC output contains this dither and it being at the coarse level (only 2-3 bits below the full-scale) degrades the overall SNR severely as shown in Figure 2.5(b). Evolution of an illustrative signal spectrum for a tonal input in Figure 2. 5(a) further clarify the difficulty with a simple coarse-dither.

The way to retrieve the SNR is by pushing the dither energy out of the signal spectrum and concentrating it out-of-band, or in other words by filtering the dither, so that the coarse-stage ADC output is not corrupted by in-band elevated noise floor. The proposition is shown in Figure 2.6. A 2-level, zero-mean Bernoulli random sequence, d[n] (independent and identically distributed with

<sup>&</sup>lt;sup>1</sup>In other words, the quantization error is free of the dither

Figure 2.6: Proposed filtering of coarse dither to linearize VCO-based ADC

Figure 2.7: Probability mass function (p.m.f) shaping due to filtering

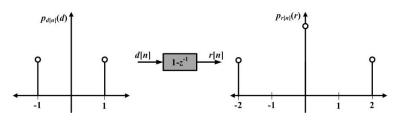

$\mathbb{P}r(d[n] = -1) = \mathbb{P}r(d[n] = 1) = 0.5)$ , is digitally high-pass filtered (G(z) in Figure 2.6) and added to the input of the coarse-ADC using a digital-to-analog converter (DAC). The gain of the DAC is chosen such that the resultant additive dither is bounded within  $[-\Delta/2, \Delta/2]$ , where  $\Delta$  is the quantization step-size of the coarse ADC. However, filtering a signal is equivalent to altering its statistical properties as well. Let's take a simple example.

If we have a simple first-order filter  $1 - z^{-1}$ , the output of the filter for a Bernoulli input d[n]will be r[n] = d[n] - d[n - 1]. The probability mass function (pmf) of the input and the output are shown in Figure 2.7. Clearly, a random signal d[n] has now become correlated and r[n] is not equiprobable to assume any value (unlike d[n]). A dither of this type is not guaranteed to ensure a completely white error signal e[n] [17–20] in Figure 2.6. Consequently, the filter g[n] needs to be chosen in such a way that the filtered dither output, r[n] is equipped with the statistical properties

desired [18] as well as being appropriately shaped. To this end, the authors have proposed some specific conditions [21, 23] in which the coefficients of the filter q[n] are specially structured so

that the output r[n] is well-behaved. This point is further highlighted in the following brief.

## 2.4.1 A brief on dithering in ADCs

Consider the coarse-ADC model shown in Figure 2.4(d). We shall define the residue (quantization error) from an ADC to be *well-behaved* if it satisfies the following conditions.

P.1) e[n] is independent of  $e[n-m] \forall n \in \mathbb{Z}, m \in \mathbb{Z} - \{0\}$

P.2) e[n] is independent of  $x[n-m]\forall n, m \in \mathbb{Z}$

P.3) e[n] is uniformly distributed

The primary condition imposed on any LSB dither signal to ensure these conditions is that the dither signal should be uniformly distributed <sup>2</sup>. Let us now focus our attention to the filtered dithering scheme shown in Figure 2.6. Remember that for any filtering scheme if the input is uniformly distributed the filtered output is not guaranteed to be uniform anymore (Figure 2.7). Let us assume the dither filter has a finite impulse response (FIR) that vanishes after *K* samples.

## We propose that if

C.1) The FIR filter coefficients g[k] are of the form  $2^i$  where i takes on each value in [0, s-1] at least once

C.2)

$$L = \sum_{i=0}^{K-1} |g[i]| = 2^s$$

where  $s \in \mathbb{Z} \cap (1, K]$

then the error sequence pair  $(e_n, e_{n-p}) \forall p \in \mathbb{Z} \cap [K, \infty)$  is pairwise independent, each being an identical uniform distribution  $\forall (k_1, k_2) \neq (0, 0)$ . Furthermore, the aforementioned conditions guarantee that  $e_n$  is an identically distributed uniform random variable independent of the input  $x_{n-m}, \forall k_1 \in \mathbb{Z}, \forall m \in \mathbb{Z}$ . Consequently, these are sufficient conditions to ensure the error signal e[n] is well-behaved. Behavioral simulation results are shown in Figure 2.8. Two different G(z) filters are used for the scheme shown in Figure 2.6.

$$G_{1}(z) = 1 - 3z^{-1} + 5z^{-2} - 9z^{-3} + 3z^{-4} - 3z^{-5}$$

$$+ 9z^{-6} - 5z^{-7} + 3z^{-8} - z^{-9}$$

$$G_{2}(z) = -1 - 2z^{-1} - 4z^{-2} - 8z^{-3} + 16z^{-4} - z^{-5}$$

<sup>&</sup>lt;sup>2</sup>This is only a sufficient condition for there can be many other classes of dither distribution viz. triangular [18] that may ensure this, but this is the most obvious and easy-to-meet distribution

Figure 2.9: Signal processing model of total system

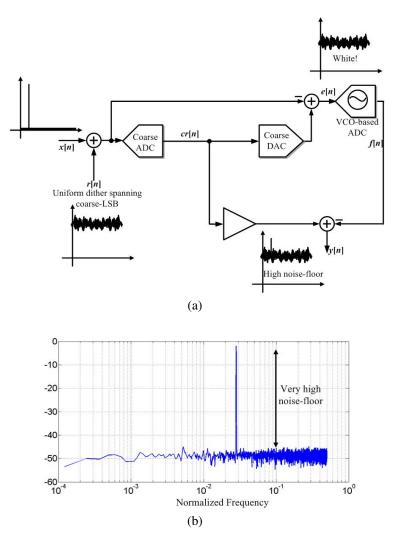

Clearly,  $G_1(z)$  does not satisfy any of the conditions above while  $G_2(z)$  satisfies both the conditions C.1 and C.2. The probability density function (pdf) of the error signal e[n] is plotted in Figure 2.8(a,b) for the two different filters.  $G_1$  results in a non-uniform pdf while  $G_2$ , as promised, results in a uniform error pdf. Likewise, the power spectral density of the error signal is also plotted for the two different cases in Figure 2.8(c,d). While  $G_1$  renders an input dependent spectrum,  $G_2$  allows a completely white error spectrum.

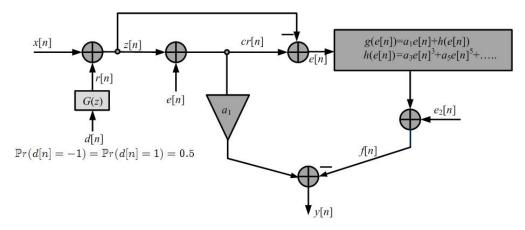

It should, however be noted that imparting a very aggressive shape to the response of G(z) is difficult satisfying both C.1 and C.2. Hence, we relax the conditions and impose only C.1 on the chosen filter. It is found that the properties enlisted in P.1-3 are met approximately, with the error signal showing a very weak dependence on the input and is almost white with a uniform pdf. It should be understood, that intuitively the effort should be to have a short filter with the smallest possible dither-LSB. The first condition stems from the fact that for longer filters, a large number of dither samples (within the filter length) will be dependent, while the second condition is an attempt to emulate uniform dither as closely as possible. The advantage of the approach can now be appreciated. Since the VCO non-linearity only acts on white noise from independent sources, hence it loses potency to produce tones. Mathematically, if the VCO characteristics can be written as  $f[n] = a_1e[n] + h(e[n])$  where h(u) is a memoryless polynomial nonlinear function, then from Figure 2.6,

$$cr[n](\text{Coarse-ADC output}) = x[n] + e[n] + r[n]$$

$$f[n](\text{Fine-ADC output}) = a_1e[n] + h(e[n]) + e_2[n]$$

$$y[n](\text{Total output}) = a_1cr[n] - f[n]$$

$$= a_1x[n] + a_1r[n] - h(e[n])$$

$$- e_2[n]$$

(2.1)

where r[n], e[n] and  $e_2[n]$  are the filtered dither, quantization error from the coarse-ADC and quantization error from the fine (VCO-based) ADC respectively.

From Eqn. 2.1, since r[n] has negligible in-band content so it does not corrupt the SNR. Also the dither makes the VCO-input e[n] white, which makes the resultant error (h(e[n])) in Eqn. 2.1) devoid of any spurious tones and spreads it in  $[0, F_s/2]$ . The resultant elevated noise-floor causes negligible error owing to oversampling. A top-level signal-processing model is shown in Figure 2.9. The coarse-stage ADC has been modeled as an input-dependent additive error. The VCO-ADC has been modeled as a polynomial non-linearity in conjunction with an additive fine stage quantization error  $e_2[n]$ .

Figure 2.10: Achievable SNDR vs. VCO-gain estimation error based on Eqn. 2.3

The dithering scheme allows another implicit benefit. As explained in Section 2.2, the nonmatched delays between the individual elements in a ring-VCO causes additional non-linearity<sup>3</sup> in the ADC operation. The whitening of the VCO-input enables this non-linear behavior to be also combatted in a similar fashion since the entries in the look-up table are now chosen randomly! It is perhaps of interest to note that a similar dither filter had been used in a previous work [22] to combat non-linearities in a fractional-N PLL.

## 2.4.2 Performance Bounds

From Figures 2.4(d), 2.5(a) and 2.6, the total output y[n] is obtained by combining the outputs of the constituent ADCs, namely cr[n] and f[n]. For a perfect cancelation of the coarse-stage quantization error e[n], the coarse-stage output cr[n] must be scaled with the accurate gain that e[n] "sees" through the fine path. Inaccuracies in the gain-estimation will limit the performance benefits of the overall system. The magnitude of the limit can be understood using the following relations. For the sake of argument, let us consider that the VCO-ADC is a completely linear

<sup>&</sup>lt;sup>3</sup>though of a look-up type, different from a polynomial representation

element having a gain of  $a_1$ . Suppose that  $a_1$  is estimated with an error  $\epsilon$ . As a result, based on Eqn. 2.1, the total output can be written as

$$y[n] = a_1(1+\epsilon)x[n] + a_1(1+\epsilon)r[n] + a_1\epsilon e[n] - e_2[n]$$

(2.2)

From Eqn. 2.2, assuming the dither filter pushes out most of the energy of r[n] out of the spectral content of x[n], the only polluting quantity would be the term  $\epsilon e[n]$ . In fact, assuming a white  $e[n]^4$ , it is not difficult to show that the SNR will be limited as

$$10\log_{10}\left[\frac{3}{2} \times (1+\frac{1}{\epsilon})^2 \times \frac{F_s}{B} \times 2^{2m}\right]$$

(2.3)

where  $F_s$  is the sampling frequency, B/2 is the maximum signal bandwidth and m is the resolution of the coarse-ADC. Thus, the ratio  $F_s/B$  denotes the oversampling ratio.

Based on Eqn. 2.3, Figure 2.10 plots the achievable theoretical SNDR as a function of the estimation error  $\epsilon$ . From Figure 2.10,  $\epsilon$  is required to be in the 1% regime for realizing a > 10bit system. In the subsequent section, we shall see how we have resorted to a correlation-based gain estimator [10,25] to estimate the linear gain to a very high accuracy.

As we had seen before, the filtered dithering scheme enables the VCO to process a white noise input that eliminates spurious signal-dependent content from showing in the total output. However, non-linearity acting on the white signal results in an elevated noise floor that folds back in the signal band. Depending on the amount of oversampling the achievable SNR may be curtailed due to this

<sup>&</sup>lt;sup>4</sup>this may be an over-simplified assumption for low resolution coarse-ADCs but suffices for the argument we want to put forth

Figure 2.11: Coarse ADC and DAC structure

mechanism. In fact, if the non-linearity of the VCO can be expressed as a third-degree polynomial (admissible for weak-to-moderate non-linearities)

$$y = a_1 x - a_3 x^3 \tag{2.4}$$

then, the folded-in power due to the non-linearity over the entire band can be calculated as

$$\frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} x^6 dx = \frac{\Delta^6}{448}$$

(2.5)

where  $\Delta$  is the coarse-ADC step size. The aforementioned noise sources should be budgeted to be below the desired resolution from the ADC, depending on the value of the chosen input amplitude, resolution of the coarse stage, the oversampling ratio and the accuracy of the gain-error estimate

Figure 2.12: Filtered dither generation

etc. We shall cover some of these design choices in the next section.

## 2.5 Proposed Technique: Circuit Level and other digital signal conditioning

## 2.5.1 Coarse Stage

A top-level circuit description for the coarse-stage is presented in Figure 2.11. The incoming signal x(t) is sampled on a bank of capacitors ( $C_s + C_F$ ) using bootstrapped switches.  $C_F$  is the set of capacitors that is dedicated for the coarse-ADC while  $C_s$  is entrusted with sampling the input signal and subtracting the coarse-ADC decision to result in the residue that is fed to the VCO-ADC. The sampling is done in a 3-way time-interleaved mode (with only one high-speed coarse-ADC structure) to relax the settling requirements on the DAC. The three way interleaved structure is nominally matched, with no extra calibration done for residual mismatches since any images so formed do not corrupt the in-band signal content due to the large oversampling involved. The sets of capacitors  $C_s$  and  $C_F$  are sized appropriately to ensure a low kT/C noise within the

Figure 2.13: Coarse flash ADC components: (a) Preamplifier (b) Dynamic latch quantization noise budget.

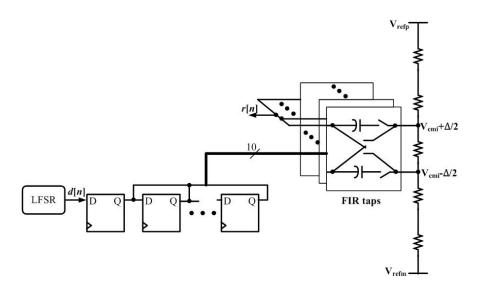

The filtered dither is generated as shown in Figure 2.12. The dither filter used in this work is

$$G(z) = 1 - 4z^{-1} + 4z^{-2} - z^{-3} + 2z^{-4} - 2z^{-5} + z^{-6} - 4z^{-7} + 4z^{-8} - z^{-9}$$

This filter choice is not unique and as discussed in Section 2.2, out of the several filters that effectively whiten the VCO input [23], this filter ensured minimal SNDR degradation from the added dither due to its aggressive high-pass shape. A pseudo-random dither signal d[n] with equal probability of being 0 or 1 is passed through a shift register, with the outputs from the shift register (Figure 2.12),  $Q_i$  switching a weighted capacitor array (based on the FIR filter weights). The sign inversions in G(z) are effected through a differential swapping between the positive and the negative nodes as shown in Figure 2.12. It should be borne in mind that errors in the dither-DAC (mismatches in the capacitors) introduce negligible errors, by virtue of the randomness of the dither input. The dither-DAC output is used as the common-mode for the sampling operation of  $C_s$  and  $C_F$  [24].

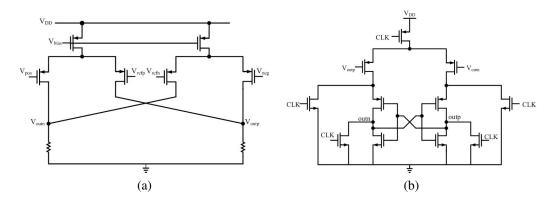

Figure 2.14: Differential ring VCO

The bootstrapped switches used in this design are based on [30]. The coarse-ADC is implemented as a 2 - b flash architecture. The implementation is shown in Figure 2.13. The flash architecture consists of 4 identical comparators that are made up of a low-power preamplifier and a dynamic latch [31]. The coarse-DAC is implemented as a passive structure with the residue being generated without any active circuitry to save power [25,26]. The accompanying parasitic-induced errors are accounted for by another signal conditioning technique discussed next.

#### 2.5.2 Fine Stage and Other Digital Conditioning

The VCO-based ADC is implemented as a 33-stage differential architecture as shown in Figure 2.14 [6]. The differential input voltage is passed through a  $g_m$ -stage and the resulting signal currents control the oscillation frequency. The passive-DAC structure and the subsequent  $g_m$  stage, without any *virtual ground* effect realized through high gain amplifiers, is reminiscent of the open-

Figure 2.15: Segmented coarse DAC

loop residue amplification techniques treated in [28, 29].

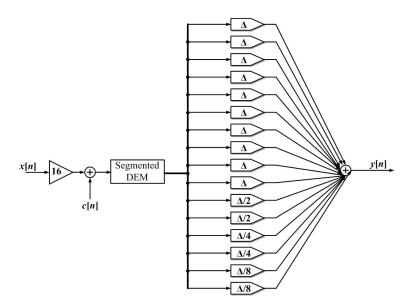

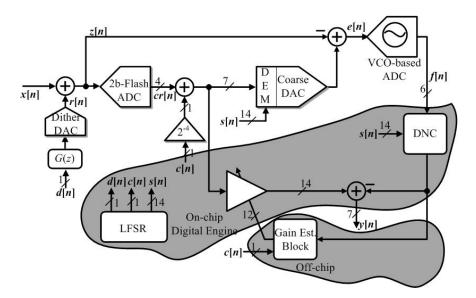

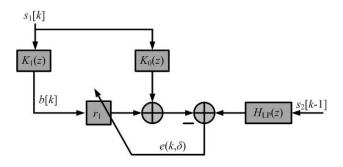

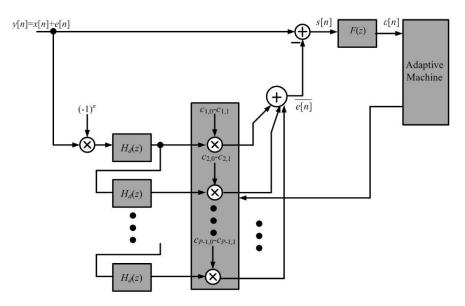

The outputs of the flash-ADC and the VCO-ADC are combined using background gain calibration based on a correlation based gain estimator [25]. A random sequence c[n] which follows the statistics  $\mathbb{P}r(c[n] = -\Delta/16) = \mathbb{P}r(c[n] = \Delta/16) = 0.5)$  (referred to the coarse-DAC output) is added to the coarse-stage output cr[n] as shown in Figure 2.16. Consequently, c[n] traverses the same path as the error signal e[n] and hence when the fine-stage output f[n] is correlated against c[n], the gain through the coarse-stage DAC and the fine-stage can be estimated. This gain estimation takes care of the parasitic errors arising due to the complete passive operation as well. It should be noted that the non-linear term in the tuning curve (Eqn. 2.4) pollutes the gain-estimate so obtained, hence some additional signal processing needs to be performed to cancel its effect [26].

Any errors in the coarse-stage arising out of mismatches in the coarse-DAC would have shown as degraded SNDR in the overall output. Dynamic element matching (DEM) is employed to counter any static mismatches from the coarse DAC [32] using random sequences s[n], as shown in

Figure 2.16: Overall structure in IC prototype

Figures 2.15 and 2.16. The addition of the random calibration sequence c[n] to the Flash-ADC output cr[n] at a much lower level enhances its effective dynamic range. Consequently, a segmented DEM architecture [33, 34] is chosen. The DEM block output is a 14-bit sequence that drives the segmented coarse-DAC structure as shown in Figures 2.15 and 2.16. Programmability options to first-order shape the DEM switching sequences s[n] are also provided. It should be noted that since the coarse-DAC scrambles/shapes the error only up to a resolution of the coarse stage, hence an elevated noise floor deteriorates the SNR to a large extent. As a result, the static DAC errors  $\Delta_i$  are estimated by correlating the fine stage output with the switching sequences s[n] [25, 27] and then the scaled random sequences  $\Delta_i s_i[n]$  are subtracted from the overall output. This technique is popular in technical art as DAC noise cancelation for high-resolution systems [25, 27]. It should be understood that the estimations of the static quantities, namely the DAC errors  $\Delta_i$  or the gain through the coarse-DAC and VCO combination are expected to change ever so slowly and hence they are carried out off-the-chip in a MATLAB environment at a downsampled rate of

Figure 2.17: Die micrograph

1MHz to save power. However, the corrections are done continuously using low-power on-chip digital engines.

The random quantities essential in the operation of the chip namely the digital dither whitening the VCO input d[n], the calibration sequence c[n] and the DEM sequences  $s_k[n], k = 1, 2, ..., 14$ are generated using a linear-feedback shift register (LFSR) that is architected in an interpolated manner [35] to ensure a large degree of independence between the sequences in a power-efficient way.