# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

## **Title**

Silicon and Silicon Carbide Nanowires: Synthesis, Characterization, Modification, and Application as Micro-Supercapacitor Electrodes

## **Permalink**

https://escholarship.org/uc/item/3k9463pp

### **Author**

Alper, John Paul

## **Publication Date**

2014

Peer reviewed|Thesis/dissertation

# Silicon and Silicon Carbide Nanowires: Synthesis, Characterization, Modification, and Application as Micro-Supercapacitor Electrodes

By

John Paul Alper

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

**Chemical Engineering**

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Roya Maboudian, Chair Professor David B. Graves Professor Liwei Lin

Spring 2014

#### Abstract

Silicon and Silicon Carbide Nanowires: Synthesis, Characterization, Modification, and Application as Micro-Supercapacitor Electrodes

by

John Paul Alper

Doctor of Philosophy in Chemical Engineering

University of California, Berkeley

Professor Roya Maboudian, Chair

For applications in mobile and remote sensing platforms, microsupercapacitors are attractive energy storage devices due to their robust lifetimes and high specific power capacity. Utilization of green electrolytes in these devices reduces environmental impact and simplifies packaging by avoiding the stringent oxygen and moisture free conditions required for organic and ionic liquid based electrolytes. Porous silicon nanowire based microsupercapacitor electrode materials are promising for on-chip applications using an environmentally benign aqueous electrolyte, 1 M KCl, however they are prone to oxidation. A silicon carbide coating was found to mitigate this issue. The fabrication techniques, involving low-temperature electroless etching of silicon, are compatible with current integrated circuit processing methods and may be readily integrated at the micro-device level. The electrode materials are in good electrical contact with the underlying substrate and require no additional current collector. The base porous silicon nanowires are coated with a thin silicon carbide passivation layer by low pressure chemical vapor deposition. The demonstrated capacitance of the electrode materials, ~1700 µF/cm<sup>2</sup> projected area, is comparable to other carbon based microsupercapacitor electrodes, remains stable over many charge/discharge cycles, and maintains capacitive behavior over a wide range of charge/discharge rates.

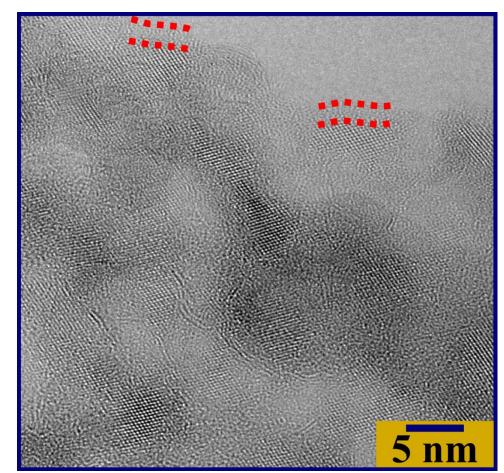

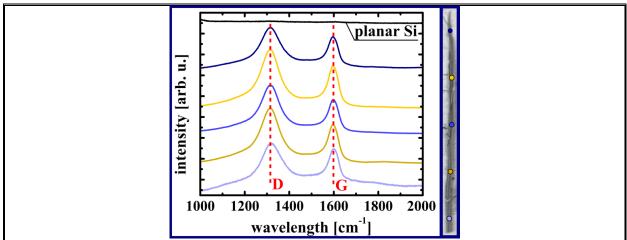

An improved passivation method for the porous silicon nanowires has also been developed. The selective coating procedure deposits an ultra-thin (~ 1-3 nm) carbon sheath over the nanowires and passivates them. The ultra-thin nature of the coating enables solvent access to the pore area and hence a large improvement of active specific surface over the SiC coated PSiNWs discussed above. The electrochemical performance of these coated nanowires is characterized in both an aqueous electrolyte and an ionic

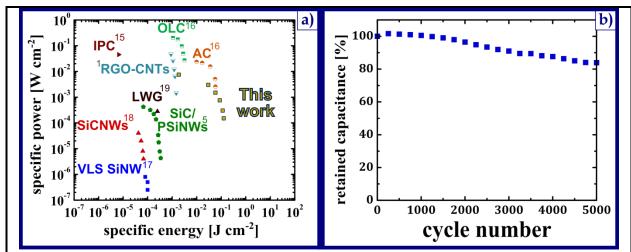

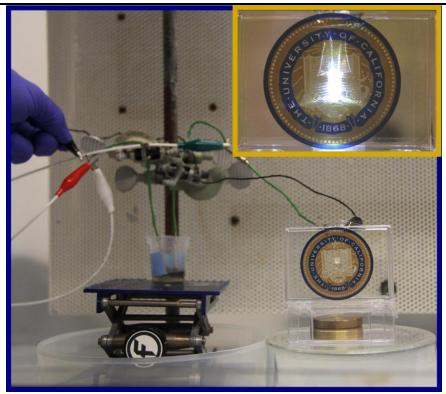

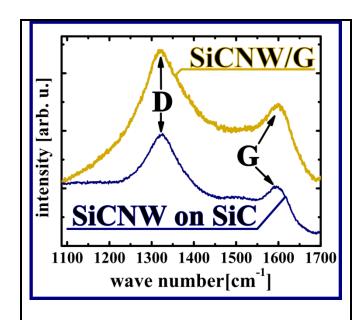

liquid electrolyte. Specific capacitance values reaching 325 mF cm<sup>-2</sup> are achieved in ionic liquid, and calculations indicate that the theoretical maximum capacitance of the pristine wires is reached. TEM studies confirm the coating thickness and its conformality. Raman spectroscopy indicates that the carbon in the coating is mainly sp<sup>2</sup> hybridized, with corresponding high conductivity. At the time of writing, these materials represent the largest specific energy microsupercapacitor electrode published. A test device is prepared and demonstrated powering an LED.

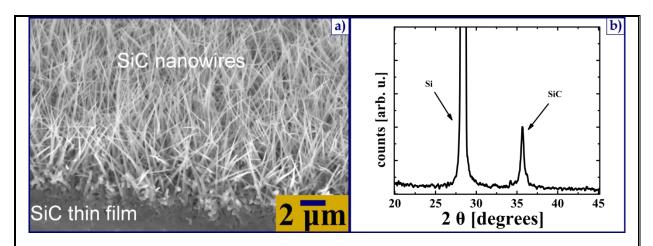

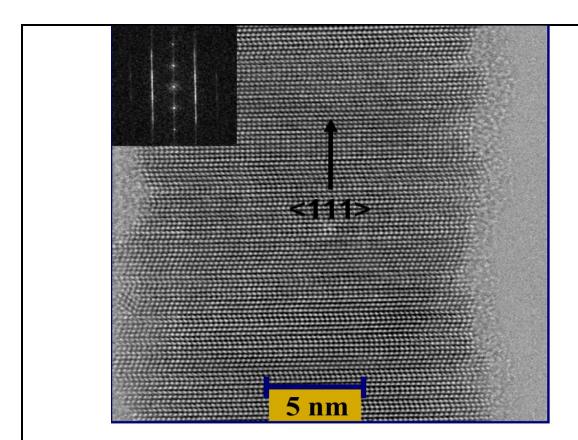

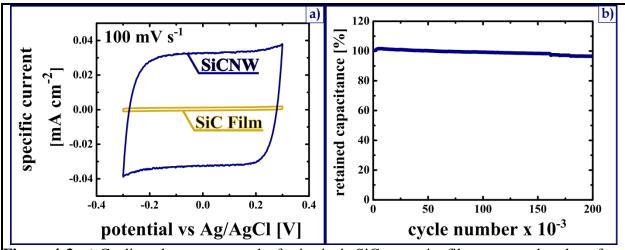

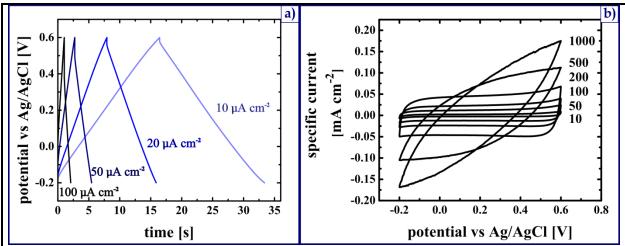

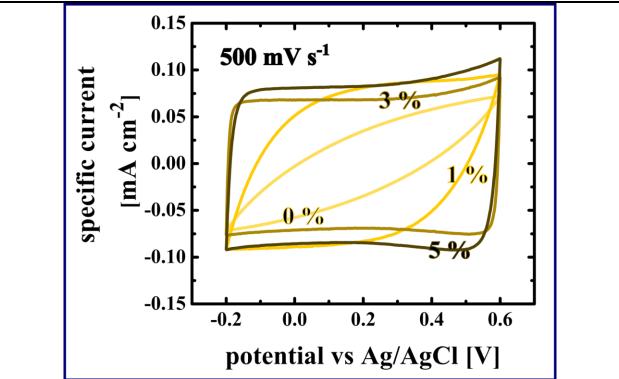

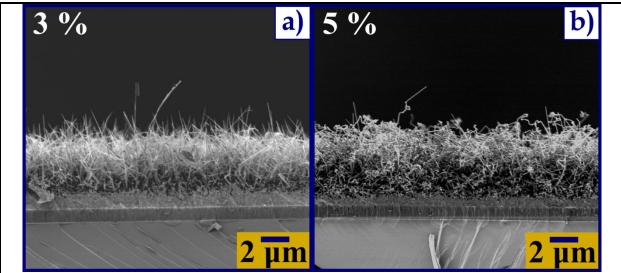

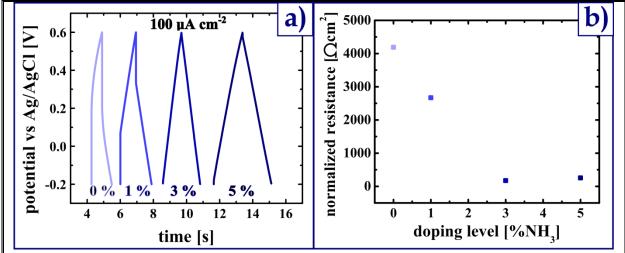

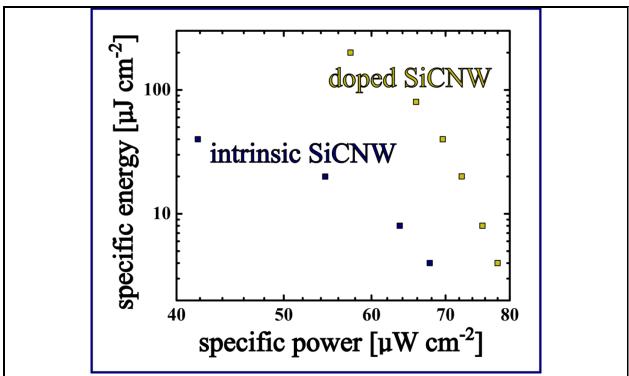

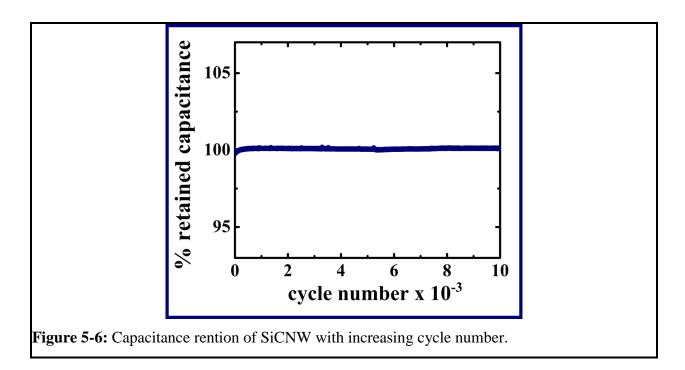

The testing results of silicon carbide (SiC) nanowires (NW) as an electrode material for micro-supercapacitors is described. SiC NWs are grown on a SiC thin film coated with a thin Ni catalyst layer via chemical vapor deposition. A specific capacitance of ~240  $\mu F$  cm $^2$  is demonstrated. Charge-discharge studies demonstrate the SiC nanowires exhibit exceptional stability, with 95% capacitance retention after 2×10 $^5$  charge/discharge cycles in an environmentally benign, aqueous electrolyte. Doping of the nanowires with nitrogen through the addition of 5 at% ammonia to the precursor gas flow rate improves the conductivity of the nanowire films by over an order of magnitude leading to increased power capabilities.

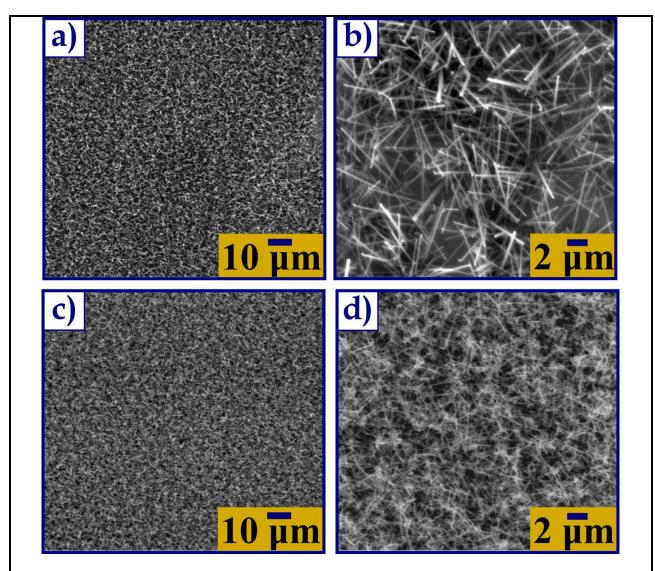

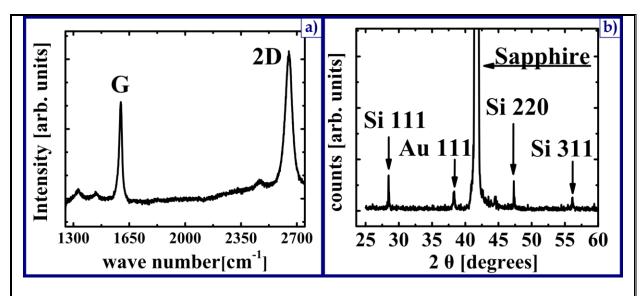

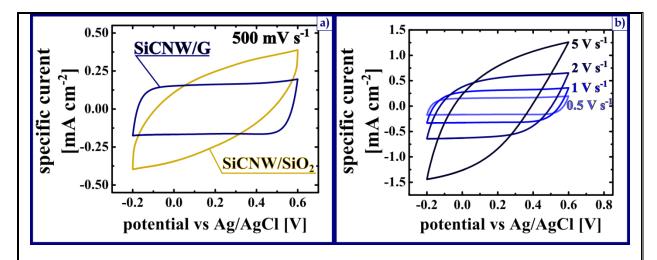

A method to transfer silicon and silicon carbide nanowire arrays to arbitrary substrates while maintaining electrical contact through the entire array is elucidated. The nanowires are grown on graphene sheets on  $SiO_2$  coupons. The graphene acts as both the flexible material for maintaining structural continuity and electrical contact through the array during transfer. The  $SiO_2$  acts as the sacrificial growth substrate which is etched after growth in order to release the nanowire/graphene hybrid. The nanowire/graphene hybrids are structurally characterized by XRD and electron microscopy. Good electrical contact is confirmed through testing of the SiCNW/graphene hybrids as supercapacitor electrode materials in an aqueous electrolyte. The specific capacitance,  $\sim 340~\mu F$  cm<sup>-2</sup>, is similar to SiCNW arrays grown on oxide while the electrical conductivity is improved and cycling stability tests show less than a 1% decrease in capacitance after 10,000 cycles.

# Acknowledgements

This document is the culmination of years of work during which I have had the good fortune to interact with many excellent researchers and teammates. I thank them all for their help in picking fruitful paths and spotting dead ends.

And for keeping me excited.

A special thanks to Roya, for believing I might just really like graduate school.

# **Table of Contents**

| Chapter 1: Overview: nanowires and supercapacitors                                                                                    | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Chapter 2 Silicon carbide coated porous silicon nanowires as microsupercapacitor electrodes                                           | 22 |

| Chapter 3 Carbon coated porous silicon nanowires as micro-supercapacitor electrodes                                                   | 36 |

| Chapter 4 Silicon carbide nanowires as highly robust electrodes for microsupercapacitors                                              | 52 |

| Chapter 5 Growth of semiconducting nanowires on graphene                                                                              | 65 |

| <b>Chapter 6</b> Looking forward                                                                                                      | 79 |

| Appendix I Theoretical maximum capacitance for porous silicon nanowires                                                               | 81 |

| Appendix II  Preliminary results: SiCNW growth kinetics, flow rate dependency, substrate dependant orientation, and crystal structure | 83 |

# Chapter 1 - Overview: nanowires and supercapacitors

#### Introduction

Nano-materials represent a broad class of materials in which at least one dimension of the material is measured on the order of a nanometer. They may be characterized as 0-d (quantum dots) [1], 1-d (carbon nanotubes [2,3], nanowires [4]), 2-d (graphene) [5] or 3-d (buckminsterfullerene) [6] depending on the number of dimensions extending beyond the nanometer range. Over the past few decades nanomaterials have received much interest due to novel characteristics intrinsic to their nanoscale including magnetic, opto-electronic and thermal properties as well as increased reactivity [7]. For instance, quantum dots have been shown to exhibit size dependent band gap energies, resulting in size dependent coloration [8]. Nobler metals such as platinum have also been demonstrated to have size dependent reactivity and hence geometrically dependent catalytic properties [9]. Graphene exhibits ballistic electron transport and large scale sheets (~30 inch on the diagonal) can be produced with resistances as low as 125  $\Omega$   $\square$ -1 [10]. Nanomaterials' geometries also results in high surface area to volume and surface area to mass ratios, termed specific surface area and measured described as either [area volume-1] or [area mass-1]. It is the latter characteristic of nanowires with which the following manuscript is mainly concerned, specifically for the high power density storage of electrical energy through capacitance. The results from the author's work on the synthesis, characterization and application of semiconductor nanowires as electrochemical double layer capacitor electrodes will be discussed. A hybridization scheme between graphene and semiconductor nanowires will also be described that takes the field a step closer towards integration of semiconductor nanowires with actual devices. This chapter will provide an overview as to what nanowires are and various methods of synthesizing them. Following that, electrochemical double layer capacitors will be described including their benefits and shortcomings as energy storage devices. Finally the driving forces behind their implementation on the microscale and the methods used to characterize them will be elucidated.

#### **Nanowires**

Nanowires are wire shaped materials 1-100's of nanometers in diameter, while being unconstrained in size in the axial direction. Due to their nanoscale, the properties of these materials may vary greatly from that of a bulk sample of the same material. At such scales, the surface states of the material begin to play an observable role in the electronic properties such as charge transport and trapping [11]. When one dimension of the nanowire approaches the wavelength of incident light, the material's optical response is affected [12]. Surface roughness approaching the order of the material's smallest dimension may have strong effects on reducing thermal transport [13]. Finally the extremely high aspect ratios which may be achieved with these materials, lead to

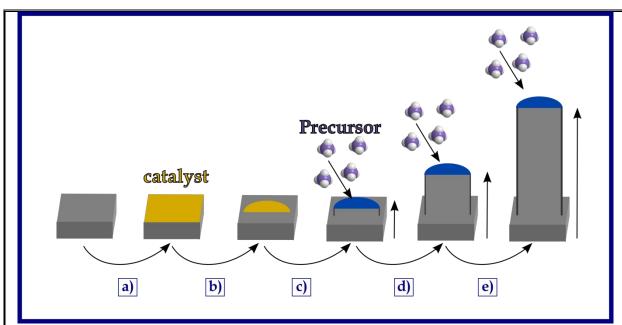

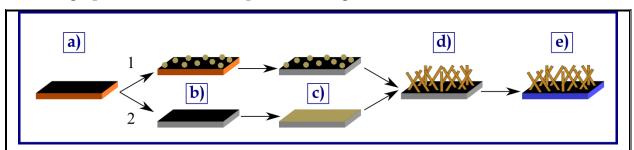

**Scheme 1-1:** A typical VLS based nanowire synthesis scheme. The process begins with a), the deposition of metal catalyst onto the growth substrate. In b) the substrate is heated to a temperature where the metal catalyst becomes molten. Precursors for the desired nanowire are added in c), which react on the catalyst surface and saturate the molten catalyst, forming a precursor/catalyst alloy. With continued addition of precursor the nanowire precipitates from the catalyst alloy and the nanowire extends in length through d) and e).

high surface area to volume ratios, difficult to obtain on the macroscale. As a result nanowires are an interesting area of study for a variety of applications including

catalysis [14], energy storage [15], energy generation [16] and sensing [17], where active materials' specific surface area plays a role in performance. The following work focuses on homogeneous semiconducting nanowires. For further reading on compound [18], metallic [19], metal oxide [20], and polymer [21] nanowires the reader is directed to relevant sources in the literature.

Nanowire synthesis - chemical deposition based

The growth of semiconductor nanowires began with the discovery of metal catalyzed growth from precursors in the vapor form in the 1960's [4]. The first step in this growth technique, known as vapor-liquid-solid (VLS) growth, is the deposition of nanoscale metallic films or droplets onto a growth substrate. The substrate is subsequently introduced into a furnace and heated to form nano-droplets of molten catalyst. A precursor containing the atoms of the desired nanowire's elemental composition is then introduced into the furnace. The precursor reacts on the surface of the molten catalyst, forming a semiconductor-metal alloy. Eventually with further addition of the precursor

the alloy droplet becomes supersaturated. Precipitation of the semiconductor nanowire then begins. Further addition of the precursor results in continued precipitation and growth of the nanowire structure. The process is summarized in Scheme 1-1. Visualization has confirmed VLS as the mechanism for growth through in situ electron microsopy [22]. To date the VLS method has been used to generate homogeneous semiconductor nanowires of numerous types with a variety of metal catalysts deposited through many techniques and employing a multitude vapor precursors. A summary of the rich variety of combinations used in VLS growth is provided by Werner et al. [23]. Since the initial discovery of VLS growth a number of other possible metal catalyzed chemical vapor nanowire synthesis mechanisms have been identified including vapor-solid-solid (where the catalyst remains solid), solution-liquid-solid (where the precursors are deposited from solution), and solid-liquid-solid (where the catalyst remains solid and the nanowire precursor material is in the solid phase) [24].

Control of nanowire arrangement on a surface is often desirable, rather than relying on the random arrangement obtained from blanket deposition catalyst deposition techniques. As the nanowires grow only from the metal catalyst in this mechanism, by patterning the catalyst onto the surface, control of the nanowire position and density is possible. For evaporated catalysts, lift-off techniques [25], nanosphere lithography [23], and shadow masking [26] are a few of the ways to control growth location and density. Catalysts deposited via electro- or electroless deposition have been patterned for both location and metal droplet spacing using membranes [27] and encapsulation of metal salt solutions in polymeric micelles [28] among other methods. Control of the electrical properties is also important for certain applications such as photovoltaics, and additional gases may be added to the vapor phase during growth for in situ doping [29], or post growth for ex situ doping [30]. Orientational control may also be achieved by judicious selection of the composition and crystallographic orientation of the underlying substrate [31,32], including epitaxial growth branching from other nanowires [33]. VLS is a truly versatile process which has yielded promising material for applications ranging from next generation transitors [26], to photovoltaics [34], and high frequency resonators [35]. One major drawback of the metal catalyzed VLS growth however is the incorporation of catalyst atoms into the final structure which may alter the electrical properties and hinder performance. For this reason a well thought out selection of the metal catalyst is important during initial process design, and is application dependent. In the following work silicon carbide nanowires have been studied using a single source precursor (methyltrichlorosilane, MTS) and a nickel catalyst film, which results in a dense array of nanowires with moderate electrical conductivity. In situ doping with ammonia has also been used to tune the electrical conductivity.

Nanowire synthesis - wet etch based

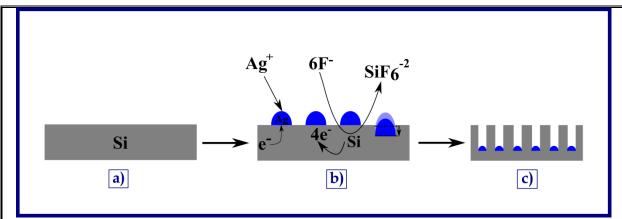

**Scheme 1-2:** A proposed mechanism for the wet etching of silicon nanowires with an in situ oxidant, Ag<sup>+</sup> ions. Silicon a), is immersed in a solution containing Ag<sup>+</sup> and F<sup>-</sup> species in b). The Ag<sup>+</sup> ions extract electrons from the proximal silicon, oxidizing it and resulting in metallic Ag being deposited onto the surface. The F<sup>-</sup> species react with the oxidized silicon, removing it from the wafer. The metallic Ag catalyzes further silicon oxidation resulting in continued etching of local silicon, and "sinking" of the Ag particles as shown in b). With time, a nanowire array is left, comprised of the unetched silicon, as in c).

Besides vapor deposition techniques, metal-catalyzed wet etching is another method for synthesizing silicon nanowires [36],[37]. Silicon is introduced into a bath containing an

oxidant and a preferential silicon oxide etch, typically HF. Metal on the surface of the silicon catalyzes the oxidation reaction, increasing the local etch rate. The metal may be deposited ex situ (e.g. by evaporation, electro- or electroless deposition) or in situ using electroless deposition. In the former case the oxidant used during etching is typically H<sub>2</sub>O<sub>2</sub> while in the latter case the oxidant is the metal salt and the arrangement of nanowires is based on the thermodynamics of the system. By varying oxidant and etchant ratios, silicon crystal orientation, silicon doping type (n- vs p-), and dopant concentration control of the resulting nanowires electrical properties, roughness, porosity, and tapering may be achieved [13], [36], [38], [39]. Templating methods, similar to those discussed above for chemical deposition based synthesis, are also viable options, however the negative of the metal pattern will be developed in the case of etching. As this work utilizes solely in situ catalyst deposition methods, that will be the focus of the rest of this discussion. For further reading on ex situ metal deposition and subsequent etching methods the reader is directed towards this helpful review [36].

Electroless deposition of metal onto silicon in the presence of HF to form large scale arrays of nanowires was first discussed in 2002 by Peng et al. [37]. Silver nitrate was utilized as the oxidant, resulting in Ag nanoparticles being deposited onto the surface and acting as a catalyst for further oxidation and subsequent etching, removing material in the immediate vicinity of the metal. A proposed mechanism is presented in Scheme

1-2, and adapted from [36]. As the etching continues, more silicon is removed from underneath the metal catalyst and thus the length of the wires may be controlled by total etching time. Finally, as the materials are exposed from the bulk of the substrate, they maintain the initial crystallography of the substrate. It should be noted that the exact mechanism and thermodynamics of the system have not yet been conclusively described in the literature.

Arrays of silicon nanowires formed in this way have been applied as photovoltaic structures [40], photocatalysts for water splitting [41], supercapacitor electrodes [15], field emission electrodes [42], and thermoelectrics [13]. Chapters 2 and 3 in this work will describe the synthesis of porous silicon nanowires from heavily boron doped p-type silicon with an in-situ metal catalyst/reductant etch bath, for application as supercapacitor electrode materials.

# **Supercapacitors**

"Supercapacitor" is actually a term coined for a device storing electrical energy in the electrochemical double layer. Electrochemical double layer (ECDL) capacitor is the formal name of these devices. Based on the specific capacitance achievable with these devices in comparison to the standard parallel plate capacitor there is good reason to refer to them as supercapacitors or ultracapacitors (another common alternative). The first proposal of such a device came in the mid 20th century in the form of a patent awarded to Becker in 1957 in which was described a device storing energy in the ECDL formed at the interface between activated carbon in contact with an aqueous electrolyte [43]. Since then the use of organic electrolytes has been identified as a way of increasing the energy density of these devices by increasing the working voltage, as the total energy scales with the voltage (V) squared. Organic electrolytes with tetralkylammonium salts can operate in voltange ranges of 3.4-4 V vs. that of aqueous electrolytes with a working voltage range of ~1 V [43]. More recently focus has shifted to ionic liquids with even large stable voltage windows. Some may even approach 6V [44], although the toxicity and long term health hazards for these these novel electrolytes is still unknown.

While the reader is most likely familiar with the mechanism of electrical energy storage in batteries and parallel plate capacitors, the capacitance of the electrochemical double layer may be a new concept. It is thus worth comparing the operation of these various devices.

Comparison of batteries, parallel plate capacitors and supercapacitors

At the most fundamental level, in terms of purpose, batteries, parallel plate capacitors, and supercapacitors all function as electrical energy storage devices. Batteries do so

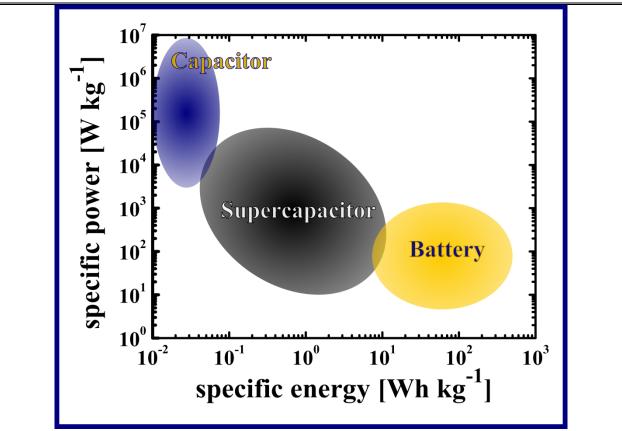

**Figure 1-1:** Ragone plot comparing the typical specific power and energy ranges of batteries, capacitors, and supercapacitors as extracted from [45].

through the pairing of electrochemical redox reactions, such as the well known Li-ion system, which occur at opposing electrodes. During discharge, metal species yield electrons to an external circuit, powering a load while traveling down the potential energy slope to the opposing electrode, where they recombine with metal ions in a

thermodynamically favored arrangement. Charging is achieved by an external energy source forcing the reverse reaction. Thus electrical energy is stored in the chemical bonds of the charged electrode. Parallel plate capacitors on the other hand, store energy via electrostatics. Two plates, separated by a dielectric, are charged via an external energy source. Upon removal of the source, the charges are "stuck" on the plates until the circuit is completed by a load. The charges then recombine as they move down the potential energy slope, powering the load. In this case electrical energy is stored on the surface of the electrode, leading to more rapid discharge (higher power) than batteries, but lower total energy storage capabilities. ECDL capacitors are a bridging device, straddling the difference in energy and power density between capacitors and batteries, as depicted in the ragone plot in Figure 1-1. Supercapacitors are comprised of two

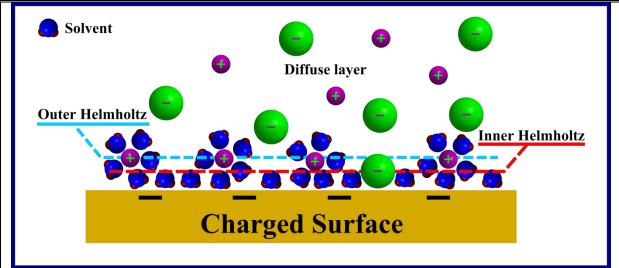

electrodes which are in contact with an electrolyte. Upon charging of the electrodes, the electrolyte becomes polarized, yielding a higher density of opposite charged ions at each electrode. In order to satisfy charge neutrality in the bulk of the solution, a second layer of counterions forms just outside of this region and this interphase between the electrode and the bulk is hence called the electrochemical double layer. Grahame's proposed model of 1947 is still used to describe this phenomena and the structure is

**Figure 1-2:** Visual description of the Grahame model for the electrochemical double layer, formed when a charged surface is in contact with an electrolyte solution [46]. Ions of the opposite charge are attracted to the surface. For charge neutrality an equal number of counterions form a second layer in close proximity, before the diffuse bulk is reached. The outer Helmholtz plane represents the closest approach for cations encapsulated by a solvation layer. The inner Helmholtz plane represents the plane of closest approach for specifically adsorbed anions. The solvent is not shown in the diffuse region for increased clarity.

depicted in Figure 1-2 [46]. The two labeled planes, inner and outer Helmholtz, refer to the plane of closest approach for the anion and cation respectively. Anions have a tendency to become specifically adsorbed onto electrode surfaces whereas cations are separated from the electrode at a further distance by a strong solvation layer. The plane of concentrated ions, opposing the charge on the electrode, represents a second "parallel plate" and gives rise to a capacitance which can be described in the same way as that of the double plate capacitor, given in Equation (1):

$$C = \frac{A}{d}\varepsilon\varepsilon_o \tag{1}$$

Where C is the capacitance, A is the interfacial area, d is the separation distance between the two "plates",  $\varepsilon$  is the dielectric constant of the interlayer (or the adsorbed solvent

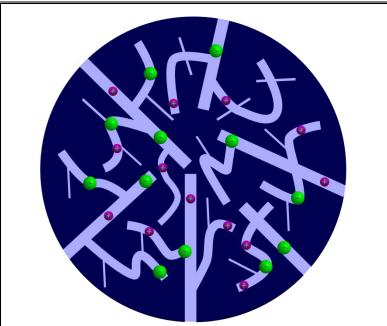

**Figure 1-3:** Depiction of magnified view into porous media typically utilized as supercapacitor electrode materials. Some pores are too small to allow ion penetration and thus will not actively participate in energy storage.

layer for a supercapacitor), and  $\varepsilon_0$  is the dielectric of a vacuum. Another important aspect of the supercapacitor design is that as the double layer forms at any surface which is wetted by the electrolyte. This enables the use of porous media with high specific surface areas. Various porous carbon materials, with specific surface areas  $\sim 1000 \text{ m}^2 \text{ g}^{-1}$ , are typically employed due to their abundance, low cost, and reasonable conductivity [47]. It should be noted that the reported surface areas of these materials does not necessarily coincide with active area, as some pores will be too small to allow

ion penetration, as depicted in Figure 1-3. The structure of the double layer has also been observed to change upon ion confinement in micropores (<1 nm in diameter), with substantial capacitance increases in capacitance measured in pores approaching the relevant ion's radius [48]. A rigorous new model to explain these phenomena has to date not been demonstrated.

By considering Equation (1), in comparison to a parallel plate capacitor, EDCL capacitors have a much larger potential area which is active and the distance between the "plates" is extremely small (~1 nm) [43]. For these reasons, supercapacitor is an accurate term, with specific capacitances reaching ~100x that of parallel plate capacitors. It may have occurred to the reader from this discussion, that a supercapacitor is actually two parallel plate capacitors in series. Indeed this is the case and the total capacitance is then given by equation (2):

$$1/C_{total} = 1/C_1 + 1/C_2 \tag{2}$$

where  $C_1$  and  $C_2$  are the capacitances of the individual electrodes. This is an important point to remember and will be brought up again when the characterization methods for

these devices are discussed below. The total energy stored in a capacitor is proportional to the capacitance and is described by Equation (3):

$$E = 1/2CV^2 \tag{3}$$

where *E* is energy and *V* is the voltage window of discharge as limited by the electrochemical stability of the electrode material and electrolyte. Thus supercapacitors are able to store larger amounts of energy than parallel plate capacitors. However the charge and discharge cycles of supercapacitors require ion transport through porous media and results in added resistances. These are often modeled as set of series resistances (or transmission line resistance model) corresponding to the different size pores and these resistances result in real charge/discharge rate limitations [49]. The porous nature of supercapacitor electrodes then leads to lower power capabilities than those of parallel plate capacitors. A further discussion comparing the thermodynamics of the battery and supercapacitor systems may be found in Reference [45].

A final note in comparing these devices is that in capacitors and supercapacitors, all energy is stored via electrostatics and no degradation mechanism to the electrode is inherent to their operation as opposed to batteries which undergo chemical reactions and thus changes in electrode volume and morphology. Lifetimes of supercapacitors are subsequently ~1000x (in terms of number of charge/discharge cycles) that of batteries [43]. Due to their relatively high energy and power capabilities and their long cycle lifetimes, supercapacitors have been employed to date as backup power supplies, storage devices for regenerative braking systems and energy sources for fail-safe positioning devices [50].

## *Microsupercapacitors*

Microelectromechanical system (MEMS) based remote sensors play an ever increasing role in human society including monitoring the structural health of major civil works, the physical health of human patients and the environmental presence of toxic or explosive compounds [51–53]. Integration of high power, robust, micro scale energy storage devices with these sensors is important in terms of device reliability, providing burst energy for data relay, and allowing for the continuing densification of components by reducing bulky external power sources. Micro-batteries based on 3-d architectures have been proposed for application in high-power devices and boast scalable energy capacity. However these devices have not yet been demonstrated to overcome typical battery failure modes resulting from material degradation during cycling [54]. Microsupercapacitors are attractive candidates to fill this important energy market due to their high specific power capacity and robust cycling stability (~106 cycles vs ~10³ cycles for batteries) [55].

# Chapter 1 – Overview: nanowires and supercapacitors

Microsupercapacitors typically utilize planar geometries and thus are able to achieve much smaller form factors than typical cylinder or box-like geometries. Several planar micro-supercapacitors have already been reported in the literature[15], [56–63]. A significant challenge to developing planar devices is integration of the electrode material. Activated carbon, which is the most common material used in macroscale supercapacitors, is difficult to integrate in planar technology, due to such issues as precise placement and the uniformity needed to pattern the electrode [57]. As a consequence, for on chip supercapacitor development, research has focused largely on nanomaterials. The development and testing of semiconducting nanowires synthesized via chemical deposition and wet etch methods microsupercapacitor electrodes will be discussed in detail in the upcoming chapters.

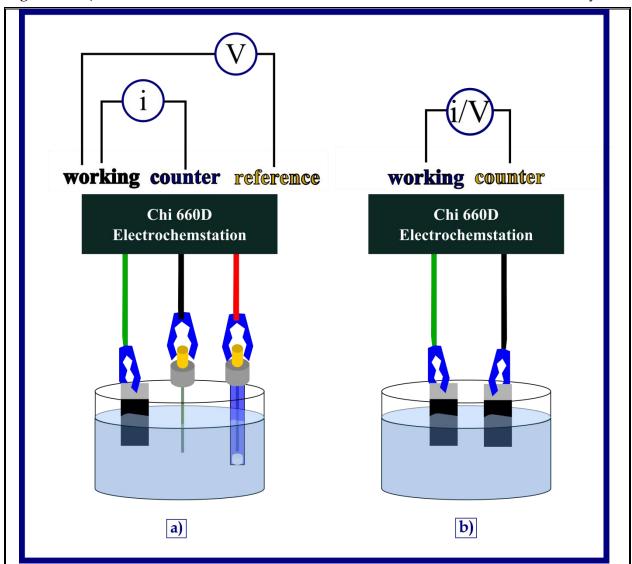

# Supercapacitor performance characterization

The main figures of merit for supercapacitor materials are specific capacitance, specific energy, specific power, and cycling stability or lifetime. All may be tested utilizing straightforward techniques enabled by a basic electrochemical station. Namely the methods of cyclic voltammetry (CV), galvanostatic charge/discharge (GD) and impedance spectroscopy are used to quantify the performance metrics of supercapacitor materials. These tests may be performed in either a two-electrode or three-electrode configuration. In the latter a reference electrode is used to fix the potential over the working electrode (material being tested) while a current is applied or measured between the working and counter electrode (current sink). By having a separate reference, the electrochemical stability of the electrode/electrolyte can be probed at the same time as the specific capacitance of the electrode material under investigation. The two electrode configuration employs a symmetric (in this work) working and counter electrode, where the counter electrode acts a pseudo-reference, enabling the potential difference to be measured, but the true potential cannot be controlled. As an actual device is two electrodes it is the more accurate configuration for characterizing the energy and power characteristics of an actual supercapacitor comprised of the electrode materials being tested [64]. The two configurations are shown schematically in Figure 1-4.

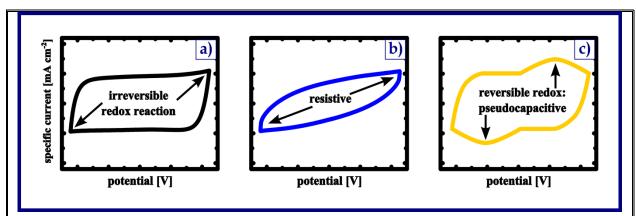

# Cyclic voltammetry

The method of cyclic voltammetry applies a constantly changing potential between the working and reference electrode, while monitoring the current between the working and counter electrode. The output is a plot of current vs. potential and the capacitance of the electrode material is calculated from Equation (4):

$$C = \frac{i}{dV/dt} \tag{4}$$

where i is the measured current and dV/dt is the potential sweep rate. An ideal supercapacitor would thus result in a square wave current vs. potential plot. However in real ECDL capacitors the output deviates from this square wave in three typical ways [47]. The first is in current peaks at the high and low potential ranges, shown in Figure 1-5 a), which result from electrochemical instability of the electrode or electrolyte. Resistances in the material give rise to a skewing of the i-V relationship, depicted in Figure 1-5 b). If reversible redox reactions occur between the electrode and electrolyte,

**Figure 1-4:** Comparison of three electrode a), and two electrode b), testing setups used for characterizing supercapacitor performance.

**Figure 1-5:** Description of different deviations from ideality typical during CV measurements of supercapacitors including a) Irreversible redox reactions, b) resistive behavior, and c) reversible redox reactions which contribute to energy storage.

this can result in a CV such as that in Figure 1-5 c), increasing the total energy storage capabilities of the system through the phenomenon called pseudocapacitance. Although this subject is not directly related to the work described herein, Conway's monograph contains a thorough discussion on the topic [43].

Analysis of CV results, in the face of non-idealities, may be performed with three different methods which can yield different results for capacitance. One may chose a single potential at which to analyze the current and through a judicious choice, avoid including contributions from faradaic reactions occurring during the voltage sweep. Averaging the current over the forward and reverse scans is a second choice and

averaging the current over the reverse scan direction (i.e., discharging) is a third. These are summarized in Table 1-1. In the following work, in an effort to characterize the pure double layer capacitance of the material, a single potential is chosen at which the current is used to determine capacitance.

It should be recognized that when performing this measurement in the three-electrode configuration, the capacitance measured is that for a single electrode. A device comprised of two of these electrodes would hence have a total capacitance, in the case that they are completely symmetric, of 1/2 that of a single electrode, based on Equation (2). Normalization of the capacitance calculated is important for being able to rationally compare different materials' performance. For microscupercapacitors, the typical metric utilized is capacitance per projected area, as the area occupied on a chip is the most relevant for on chip applications. It should be stated clearly whether the capacitance being reported is based on a three or two electrode method and whether the projected area is that of the total device or the active electrode material, so that accurate comparisons can be made.

Chapter 1 – Overview: nanowires and supercapacitors

Cycling stability may be determined utilizing CV. If CV is used, it should be conducted over the entire voltage window and at a relevant scan rate to operation. This will ensure

| Table 1-1                        |                                                                     |                                                                                                                               |  |  |

|----------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| Method                           | Equation                                                            | Description                                                                                                                   |  |  |

| Current at a single potential    | $C = \frac{i _{V=x}}{dV/dt}$                                        | Enables the calculation of capacitance based purely on double layer contributions.                                            |  |  |

| Average current over entire scan | $C = \frac{i_{forward avg} + i_{reverse average}}{2 \frac{dV}{dt}}$ | Includes both<br>pseudocapacitive and<br>irreversible faradaic<br>reactions                                                   |  |  |

| Average over discharge<br>scan   | $C = rac{i_{reverse\ average}}{dV/_{dt}}$                          | Includes both pseudocapacitive and irreversible faradaic reactions. May closer resemble capacitance achieved during discharge |  |  |

that the results accurately represent the lifetime of the materials under expected use conditions.

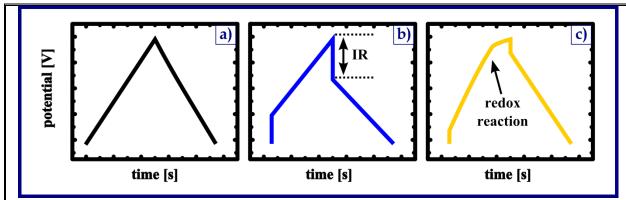

# Galvanostatic charge/discharge

In GD a constant current is applied between the working electrode and the counter electrode, while the potential over the working electrode is measured. Threshold high

and low potentials are also set. When the system reaches these, the polarity of the current is reversed. The typical output for this technique is a plot of potential vs. time and an ideal supercapacitor yields a sawtooth potential-time relationship as shown in Figure 1-6 a). Common deviations from ideality include a vertical region upon reversal of the current polarity, shown in Figure 1-6 b), which is a result the sum total of resistances through the supercapacitor and is referred to as the IR drop accordingly. Analysis of this feature enables computation of the equivalent series resistance, or ESR, which includes the contributions from ionic resistance in the electrolyte, transport resistance in the porous media, electronic resistance in the electrode material and any resistances through the external circuit [43]. When determining the ESR from this method it should be calculated using Equation (5):

$$ESR = \Delta V_{IR}/I \tag{5}$$

where *I* is the absolute current being applied and . This value should be checked for consistency by utilizing results from a variety of current values [65]. A second deviation from ideality is curvature in the potential-time relationship, depicted in Figure 1-6 c), which is a result of redox reactions occurring during charge or discharge [65].

Capacitance may be calculated from GD results utilizing Equation (4) where dV/dt is now the average over the entire discharge. GD is also the preferred method for calculating energy and power density as the ESR, and thus power limitations, are accounted for. Energy is calculated using Equation (3) and power may then be calculated by Equation (6):

**Figure 1-6:** a) Ideal potential vs. time relationship obtained from galvanostatic testing of supercapacitors. b) Potential vs. time relationship obtained from galvanostatic testing of supercapacitors with resistive contributions. c) Potential vs. time relationship obtained from galvanostatic testing of supercapacitors with redox reactions occurring.

# Chapter 1 – Overview: nanowires and supercapacitors

Where *P* is power and *t* is the time for discharge. Caution should be used when comparing the energy and power results for supercapacitor materials tested in two vs. three electrode systems as even the configuration of electrodes has been shown to effect these results [66]. As with normalized capacitance reporting energy and power "density" as per projected area of the device is typical in the literature.

GD may also be used to determine lifetime stability. During these tests the full voltage range should be utilized and the current applied should be relevant to expected operational conditions.

# Impedance spectroscopy

This method applies an AC current between the working electrode and counter electrode over a narrow potential range. The results are then typically plotted as a nyquist or bode plot and various models have been proposed in order to relate the results to properties of the supercapacitor system including ionic resistance of the electrolyte and ESR. This method is not utilized in the current work as the relevant properties of the materials tested were well characterized by CV and GD. However it is mentioned for completeness as it is often reported in the supercapacitor literature. For more information on the technique and interpretation the reader is directed to the relevant literature [43].

# Summary

Nanowire synthesis methods provide a wealth of new materials which are attractive for energy storage applications as a result of their geometrically dependent properties. Microsupercapacitors are extremely promising energy storage devices to bridge the energy and power gap between batteries and capacitors, and for implementation in distributed sensor networks and other MEMS applications where moderate energy, high power and high reliability are required. The following chapters will be concerned with the synthesis of nanomaterials and their characterization, both in terms of physico-chemical traits and energy storage performance.

### References

- [1] A. I. Ekimov, A. L. Efros, and A. A. Onushchenko, "QUANTUM SIZE EFFECT IN SEMICONDUCTOR MICROCRYSTALS," *Solid State Communications*, vol. 56, no. 11, pp. 921–924, 1985.

- [2] L. V. Radushkevich and V. M. Lukyanovich, "O strukture ugleroda, obrazujucegosja pri termiceskom razlozenii okisi ugleroda na zeleznom kontakte," *Zurn Fisic Chim*, vol. 26, pp. 88–95, 1952.

- [3] M. Monthioux and V. L. Kuznetsov, "Who should be given the credit for the discovery of carbon nanotubes?," *Carbon*, vol. 44, no. 9, pp. 1621–1623, Aug. 2006.

- [4] R. S. Wagner and W. C. Ellis, "VLS mechanism of single crystal growth Wagner and Ellis APL 1964.pdf," *Applied Physics Letters*, vol. 4, no. 5, pp. 89–90, 1964.

- [5] K. S. Novoselov, "Electric Field Effect in Atomically Thin Carbon Films," *Science*, vol. 306, no. 5696, pp. 666–669, Oct. 2004.

- [6] H. W. Kroto, J. R. Heath, S. C. O'Brien, R. F. Curl, and R. E. Smalley, "C60: Buckminsterfullerene," *Nature*, vol. 318, pp. 162–163, 1985.

- [7] R. Vajtai, *Springer Handbook of Nanomaterials*. Dordrecht Heidelberg London New York: Springer, 2013.

- [8] L. Brus, "Quantum crystallites and nonlinear optics," *Applied Physics A*, vol. 53, no. 6, pp. 465–474, 1991.

- [9] R. K. Sharma, P. Sharma, and A. Maitra, "Size-dependent catalytic behavior of platinum nanoparticles on the hexacyanoferrate(III)/thiosulfate redox reaction," *Journal of Colloid and Interface Science*, vol. 265, no. 1, pp. 134–140, Sep. 2003.

- [10] S. Bae, H. Kim, Y. Lee, X. Xu, J.-S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H. Ri Kim, Y. I. Song, Y.-J. Kim, K. S. Kim, B. Özyilmaz, J.-H. Ahn, B. H. Hong, and S. Iijima, "Roll-to-roll production of 30-inch graphene films for transparent electrodes," *Nature Nanotechnology*, vol. 5, no. 8, pp. 574–578, Aug. 2010.

- [11] T. Hanrath and B. A. Korgel, "Influence of Surface States on Electron Transport through Intrinsic Ge Nanowires," *The Journal of Physical Chemistry B*, vol. 109, no. 12, pp. 5518–5524, Mar. 2005.

- [12] R. Agarwal and C. M. Lieber, "Semiconductor nanowires: optics and optoelectronics," *Applied Physics A*, vol. 85, no. 3, pp. 209–215, Oct. 2006.

- [13] A. I. Hochbaum, R. Chen, R. D. Delgado, W. Liang, E. C. Garnett, M. Najarian, A. Majumdar, and P. Yang, "Enhanced thermoelectric performance of rough silicon nanowires," *Nature*, vol. 451, no. 7175, pp. 163–167, Jan. 2008.

- [14] M. Wang, X. Wang, J. Li, and L. Liu, "In situ synthesis of 3D platinum nanoflowers on porous silicon for monolithic integrated micro direct methanol fuel cells," *Journal of Materials Chemistry A*, vol. 1, no. 28, p. 8127, 2013.

- [15] J. P. Alper, M. Vincent, C. Carraro, and R. Maboudian, "Silicon carbide coated silicon nanowires as robust electrode material for aqueous micro-supercapacitor," *Applied Physics Letters*, vol. 100, no. 16, p. 163901, 2012.

- [16] A. P. Goodey, S. M. Eichfeld, K.-K. Lew, J. M. Redwing, and T. E. Mallouk, "Silicon Nanowire Array Photoelectrochemical Cells," *Journal of the American Chemical Society*, vol. 129, no. 41, pp. 12344–12345, Oct. 2007.

- [17] M. C. McAlpine, H. Ahmad, D. Wang, and J. R. Heath, "Highly ordered nanowire arrays on plastic substrates for ultrasensitive flexible chemical sensors," *Nature Materials*, vol. 6, no. 5, pp. 379–384, May 2007.

- [18] X. Duan and C. M. Lieber, "General synthesis of compound semiconductor nanowires," *Advanced Materials*, vol. 12, no. 4, pp. 298–302, 2000.

- [19] Z. L. Wang, Nanowires and Nanobelts: Materials, Properties and Devices Metal and Semiconductore Nanowires. New York: Springer, 2003.

- [20] E. Comini, C. Baratto, G. Faglia, M. Ferroni, A. Ponzoni, D. Zappa, and G. Sberveglieri, "Metal oxide nanowire chemical and biochemical sensors," *Journal of Materials Research*, vol. 28, no. 21, pp. 2911–2931, Nov. 2013.

- [21] S. Chen, Y. Li, and Y. Li, "Architecture of low dimensional nanostructures based on conjugated polymers," *Polymer Chemistry*, vol. 4, no. 20, p. 5162, 2013.

- [22] Y. Wu and P. Yang, "Direct Observation of Vapor–Liquid–Solid Nanowire Growth," *Journal of the American Chemical Society*, vol. 123, no. 13, pp. 3165–3166, Apr. 2001.

- [23] H. J. Fan, P. Werner, and M. Zacharias, "Semiconductor Nanowires: From Self-Organization to Patterned Growth," *Small*, vol. 2, no. 6, pp. 700–717, Jun. 2006.

- [24] K. Kolasinski, "Catalytic growth of nanowires: Vapor-liquid-solid, vapor-solid-solid, solution-liquid-solid and solid-liquid-solid growth," *Current Opinion in Solid State and Materials Science*, vol. 10, no. 3–4, pp. 182–191, Jun. 2006.

- [25] S. Han, W. Jin, T. Tang, C. Li, D. Zhang, X. Liu, J. Han, and C. Zhou, "Controlled growth of gallium nitride single-crystal nanowires using a chemical vapor deposition method," *Journal of materials research*, vol. 18, no. 02, pp. 245–249, 2003.

- [26] V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess, and U. Gösele, "Realization of a Silicon Nanowire Vertical Surround-Gate Field-Effect Transistor," *Small*, vol. 2, no. 1, pp. 85–88, Jan. 2006.

- [27] K.-K. Lew, C. Reuther, A. H. Carim, J. M. Redwing, and B. R. Martin, "Template-directed vapor-liquid-solid growth of silicon nanowires," *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures*, vol. 20, no. 1, p. 389, 2002.

- [28] G. S. Doerk, C. Dhong, C. Politi, I. Laboriante, C. Carraro, and R. Maboudian, "Micellar block copolymer templated galvanic displacement for epitaxial nanowire device integration," *Journal of Materials Chemistry*, vol. 21, no. 24, p. 8807, 2011.

- [29] H. Schmid, M. T. Björk, J. Knoch, S. Karg, H. Riel, and W. Riess, "Doping Limits of Grown in <i/>

i/> situ Doped Silicon Nanowires Using Phosphine," *Nano Letters*, vol. 9, no. 1, pp. 173–177, Jan. 2009.

- [30] G. S. Doerk, G. Lestari, F. Liu, C. Carraro, and R. Maboudian, "Ex situ vapor phase boron doping of silicon nanowires using BBr3," *Nanoscale*, vol. 2, no. 7, p. 1165, 2010.

- [31] A. I. Hochbaum, R. Fan, R. He, and P. Yang, "Controlled Growth of Si Nanowire Arrays for Device Integration," *Nano Letters*, vol. 5, no. 3, pp. 457–460, Mar. 2005.

- [32] S. J. Rathi, D. J. Smith, and J. Drucker, "Guided VLS Growth of Epitaxial Lateral Si Nanowires," *Nano Letters*, vol. 13, no. 8, pp. 3878–3883, Aug. 2013.

- [33] D. Wang, F. Qian, C. Yang, Z. Zhong, and C. M. Lieber, "Rational Growth of Branched and Hyperbranched Nanowire Structures," *Nano Letters*, vol. 4, no. 5, pp. 871–874, May 2004.

- [34] T. Song, S.-T. Lee, and B. Sun, "Silicon nanowires for photovoltaic applications: The progress and challenge," *Nano Energy*, vol. 1, no. 5, pp. 654–673, Sep. 2012.

- [35] X. L. Feng, R. He, P. Yang, and M. L. Roukes, "Very High Frequency Silicon Nanowire Electromechanical Resonators," *Nano Letters*, vol. 7, no. 7, pp. 1953–1959, Jul. 2007.

- [36] Z. Huang, N. Geyer, P. Werner, J. de Boor, and U. Gösele, "Metal-Assisted Chemical Etching of Silicon: A Review: In memory of Prof. Ulrich Gösele," *Advanced Materials*, vol. 23, no. 2, pp. 285–308, Jan. 2011.

- [37] K.-Q. Peng, Y.-J. Yan, S.-P. Gao, and J. Zhu, "Synthesis of large-area silicon nanowire arrays via self-assembling nanoelectrochemistry," *Advanced Materials*, vol. 14, no. 16, p. 1164, 2002.

- [38] K. Peng, Y. Wu, H. Fang, X. Zhong, Y. Xu, and J. Zhu, "Uniform, Axial-Orientation Alignment of One-Dimensional Single-Crystal Silicon Nanostructure Arrays," *Angewandte Chemie International Edition*, vol. 44, no. 18, pp. 2737–2742, Apr. 2005.

- [39] C. Chiappini, X. Liu, J. R. Fakhoury, and M. Ferrari, "Biodegradable Porous Silicon Barcode Nanowires with Defined Geometry," *Advanced Functional Materials*, vol. 20, no. 14, pp. 2231–2239, Jun. 2010.

- [40] G. Fan, H. Zhu, K. Wang, J. Wei, X. Li, Q. Shu, N. Guo, and D. Wu, "Graphene/Silicon Nanowire Schottky Junction for Enhanced Light Harvesting," *ACS Applied Materials & Interfaces*, vol. 3, no. 3, pp. 721–725, Mar. 2011.

- [41] Y. J. Hwang, A. Boukai, and P. Yang, "High Density n-Si/n-TiO <sub>2</sub> Core/Shell Nanowire Arrays with Enhanced Photoactivity," *Nano Letters*, vol. 9, no. 1, pp. 410–415, Jan. 2009.

- [42] N. S. Das, D. Banerjee, and K. K. Chattopadhyay, "Enhancement of electron field emission by carbon coating on vertically aligned Si nanowires," *Applied Surface Science*, vol. 257, no. 22, pp. 9649–9653, Sep. 2011.

- [43] B. E. Conway, *Electrochemical Supercapacitors: Scientific Fundamentals and Technological Applications*. New York: Springer, 1999.

- [44] A. B. McEwen, H. L. Ngo, K. LeCompte, and J. L. Goldman, "Electrochemical properties of imidazolium salt electrolytes for electrochemical capacitor applications," *Journal of the Electrochemical Society*, vol. 146, no. 5, pp. 1687–1695, 1999.

- [45] M. Winter and R. J. Brodd, "What Are Batteries, Fuel Cells, and Supercapacitors?," *Chemical Reviews*, vol. 104, no. 10, pp. 4245–4270, Oct. 2004.

- [46] D. C. Grahame, "The electrical double layer and the theory of electrocapillarity," *Chemistry Reviews*, vol. 41, pp. 441–501, 1947.

- [47] E. Frackowiak and F. Beguin, "Carbon materials for the electrochemical storage of energy in capacitors," *Carbon*, vol. 39, no. 6, pp. 937–950, 2001.

- [48] J. Chmiola, "Anomalous Increase in Carbon Capacitance at Pore Sizes Less Than 1 Nanometer," *Science*, vol. 313, no. 5794, pp. 1760–1763, Sep. 2006.

- [49] W. G. Pell and B. E. Conway, "Analysis of power limitations at porous supercapacitor electrodes under cyclic voltammetry modulation and dc charge," *Journal of Power Sources*, vol. 96, no. 1, pp. 57–67, 2001.

- [50] R. Kötz and M. Carlen, "Principles and applications of electrochemical capacitors," *Electrochimica Acta*, vol. 45, no. 15, pp. 2483–2498, 2000.

- [51] N. A. Tanner, J. R. Wait, C. R. Farrar, and H. Sohn, "Structural Health Monitoring Using Modular Wireless Sensors," *Journal of Intelligent Materials Systems and Structures*, vol. 14, no. 1, pp. 43–56, Jan. 2003.

- [52] U. Kawoos, G. K. Mugalodi, M. R. Tofighi, S. Neff, and A. Rosen, "A permanently implantable intracranial pressure monitor 2005.pdf," in *Proceeds of the IEEE*, 2005.

- [53] T. K. Bhattacharyya, S. Sen, D. Mandal, and S. K. Lahiri, "Development of a wireless integrated toxic and explosive MEMS based gas sensor," in *VLSI Design*, 2006. Held jointly with 5th International Conference on Embedded Systems and Design., 19th International Conference on, 2006, p. 4–pp.

- [54] D. R. Rolison, J. W. Long, J. C. Lytle, A. E. Fischer, C. P. Rhodes, T. M. McEvoy, M. E. Bourg, and A. M. Lubers, "Multifunctional 3D nanoarchitectures for energy storage and conversion," *Chemical Society Reviews*, vol. 38, no. 1, p. 226, 2009.

- [55] P. J. Hall, M. Mirzaeian, S. I. Fletcher, F. B. Sillars, A. J. R. Rennie, G. O. Shitta-Bey, G. Wilson, A. Cruden, and R. Carter, "Energy storage in electrochemical capacitors: designing functional materials to improve performance," *Energy & Environmental Science*, vol. 3, no. 9, p. 1238, 2010.

- [56] Y. Q. Jiang, Q. Zhou, and L. Lin, "Planar MEMS supercapacitor using carbon nanotube forests," in *Micro Electro Mechanical Systems*, 2009. MEMS 2009. IEEE 22nd International Conference on, 2009, pp. 587–590.

- [57] D. Pech, M. Brunet, P.-L. Taberna, P. Simon, N. Fabre, F. Mesnilgrente, V. Conédéra, and H. Durou, "Elaboration of a microstructured inkjet-printed carbon electrochemical capacitor," *Journal of Power Sources*, vol. 195, no. 4, pp. 1266–1269, Feb. 2010.

- [58] F. Liu, A. Gutes, I. Laboriante, C. Carraro, and R. Maboudian, "Graphitization of n-type polycrystalline silicon carbide for on-chip supercapacitor application," *Applied Physics Letters*, vol. 99, no. 11, p. 112104, 2011.

## Chapter 1 – Overview: nanowires and supercapacitors

- [59] C. Liu, Z. Yu, D. Neff, A. Zhamu, and B. Z. Jang, "Graphene-Based Supercapacitor with an Ultrahigh Energy Density," *Nano Letters*, vol. 10, no. 12, pp. 4863–4868, Dec. 2010.

- [60] J. Chmiola, C. Largeot, P. L. Taberna, P. Simon, and Y. Gogotsi, "Monolithic Carbide-Derived Carbon Films for Micro-Supercapacitors," *Science*, vol. 328, no. 5977, pp. 480– 483, Apr. 2010.

- [61] M. Beidaghi and C. Wang, "Micro-supercapacitors based on three dimensional interdigital polypyrrole/C-MEMS electrodes," *Electrochimica Acta*, vol. 56, no. 25, pp. 9508–9514, Oct. 2011.

- [62] J. W. Choi, J. McDonough, S. Jeong, J. S. Yoo, C. K. Chan, and Y. Cui, "Stepwise Nanopore Evolution in One-Dimensional Nanostructures," *Nano Letters*, vol. 10, no. 4, pp. 1409–1413, Apr. 2010.

- [63] M. Beidaghi, W. Chen, and C. Wang, "Electrochemically activated carbon micro-electrode arrays for electrochemical micro-capacitors," *Journal of Power Sources*, vol. 196, no. 4, pp. 2403–2409, Feb. 2011.

- [64] M. D. Stoller and R. S. Ruoff, "Best practice methods for determining an electrode material's performance for ultracapacitors," *Energy & Environmental Science*, vol. 3, no. 9, p. 1294, 2010.

- [65] J. R. Miller and A. F. Burke, "Electric Vehicle Capacitor Test Procedures Manual." DOE, 1994.

- [66] D. Pech, M. Brunet, T. M. Dinh, K. Armstrong, J. Gaudet, and D. Guay, "Influence of the configuration in planar interdigitated electrochemical micro-capacitors," *Journal of Power Sources*, vol. 230, pp. 230–235, May 2013.

# Chapter 2 – Silicon carbide coated porous silicon nanowires as microsupercapacitor electrodes

# **Chapter Summary**

For application in mobile and remote sensing platforms, microsupercapacitors are attractive energy storage devices due to their robust lifetimes and high specific power capacity. Utilization of green electrolytes in these devices reduces environmental impact and simplifies packaging by avoiding the stringent oxygen and moisture free conditions required for organic and ionic liquid based electrolytes. This chapter describes the development of silicon carbide coated porous silicon nanowire based microsupercapacitor electrode materials for on-chip applications using an environmentally benign aqueous electrolyte, 1 M KCl. The fabrication techniques described below, involving low-temperature electroless etching of silicon, are compatible with current integrated circuit processing methods and may be readily integrated at the micro-device level. The electrode materials are in good electrical contact with the underlying substrate and require no additional current collector. The base porous silicon nanowires, which corrode readily in an aqueous environment, are coated with a thin silicon carbide passivation layer by low pressure chemical vapor deposition. The demonstrated capacitance of the electrode materials, ~1700 µF/cm<sup>2</sup> projected area, is comparable to other carbon based microsupercapacitor electrodes, remains stable over many charge/discharge cycles, and maintains capacitive behavior over a wide range of charge/discharge rates.

## Introduction

All silicon-based materials produced with low temperature methods using chemistries compatible with basic lithography techniques are promising in simplifying all aspects of processing and integration, making them an attractive electrode material for microsupercapacitors. As mentioned in the introductory chapter, high surface area and conductivity are two key requirements of an electrode material for use in these devices. Dense arrays of highly doped crystalline silicon nanowires (PSiNWs) in electrical contact with the underlying silicon meet both of these requirements. Previously PSiNWs produced via the well-established vapor-liquid-solid (VLS) mechanism were demonstrated as supercapacitor electrode material [1]. These were made porous by repeated Li-ion insertion and removal cycles, (i.e., Li-ion battery cycling) achieving specific surface areas of  $\sim 100 \text{ m}^2/\text{g}$ . PSiNWs fabricated with a low-temperature, one-step electroless metal assisted etch technique discussed above [2], avoids the metal catalyst pre-seeding step and high temperature chemical vapor deposition growth

conditions required for VLS type wires, as well as the complexities associated with doping of bottom-up NWs. When the metal assisted etch is performed on a highly p-doped silicon wafer, the resulting nanowires are also porous with a specific surface area of ~340 m²/g, a large improvement over the more complex VLS-battery cycling synthesis. Specifically here a wet etch using a one-step oxidant/etchant bath of AgNO3 and HF respectively, at a bath temperature of 50 °C, is employed. It has been shown that this PSiNW production technique is compatible with standard lithography and patterning technologies [3]. Furthermore via increased etch time the nanowires are scalable to longer lengths and hence increased surface area and energy storage.

# **Experimental**

# PSiNW formation

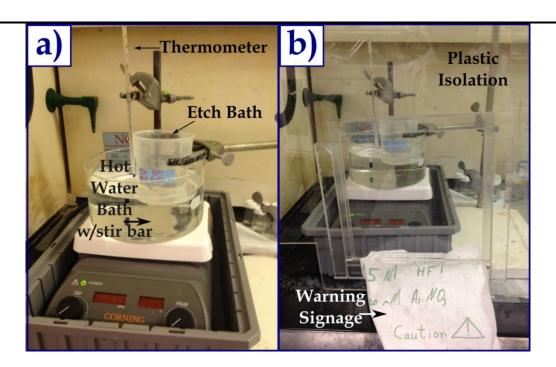

The etching of the PSiNW arrays was performed using procedures previously published[2]. First p-type Si(100) coupons (single side polished, 1 cm x 1 cm, boron doped, 1 – 5 m $\Omega$ –cm), were pre-cleaned to ensure any contaminants such as dust, organic matter, and oxide would not be present. Surface contamination can lead to nonuniform etching by protecting the surface from the surrounding solution. The cleaning process follows a protocol where the coupons were first degreased through sonication for 10 minutes in acetone and then isopropyl alcohol. Subsequently the surface oxide was removed by a 10 minute immersion in 5 M HF. \*NOTE: HF is a highly toxic acid and should only be used after specific training on the hazards, protocol in case of spill or exposure, and safe working practices. Residual organic matter removal by a 10 minute UV-Ozone treatment followed. A clean and oxide free surface was finally obtained by a second 10 minute immersion in 5 M HF. The unpolished sides were then protected from etching with a nylon based polymer resist. In addition, a thin strip at the top of the polished side was protected by the polymer resist for making later electrical contact. Electroless metal-assisted etching was performed in a 5 M HF/20 mM AgNO<sub>3</sub> (Fischer Scientific, >99.8%) aqueous solution, maintained in thermal equilibrium with a 50 °C water bath, for varying times. A clear plastic chemical splash guard was placed around the entire apparatus to mitigate any hazards of a spill during etching. The reaction apparatus is depicted in Figure 2-1. After etching the samples were dip rinsed in deionized water (DeIO,  $\sim$ 17.9 M $\Omega$ -cm) three times to wash off residual acid and metal salts. During the etching process a macroporous mat of Ag dendrites was deposited on the Si surface which was mechanically removed carefully by peeling. Samples were left free of residual Ag by immersion in ~3.5 M HNO<sub>3</sub>. The end of this etching process was detected by a color change on the surface. Immediately after removal of the bulk silver, the nanowire arrays had a slight burnt orange color with

some silver spots. As soon as the surface was noticed to be uniformly dark grey, NO<sub>3</sub> etching was stopped. This point was of importance as continuing to expose the nanowire arrays to the nitric acid resulted in oxidation and dissolution of the array. Nanowire arrays were then washed with DeIO. The polymer resist was subsequently removed by acetone rinsing. Samples were held in acetone until subsequent cleaning and drying of the nanowires.

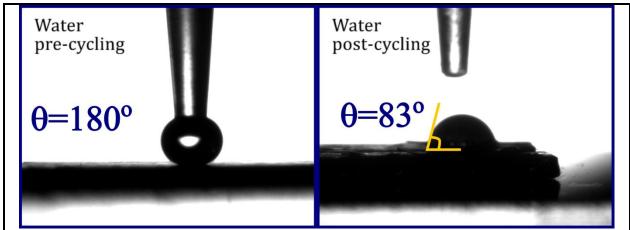

# Cleaning and drying of the nanowires

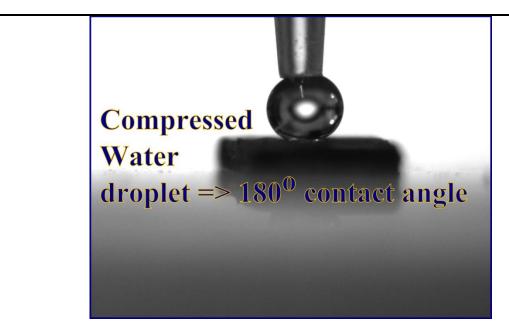

Nanowires were cleaned of any oxide present in a dilute ~1.5M ethanolic HF solution (5:25 ethanol:DeIO by volume) for 10 minutes. This was done to ensure that the resulting nanowire arrays were in good contact electrical contact with the subsequent SiC coating, important in maximizing active surface area and resulting capacitance. The concentration of HF was chosen to reduce bubble formation on the surface and thus reduce delamination of the nanowire arrays. An ethanolic solution was utilized to ensure good wetting within the pores of the silicon nanowires which are superhydrophobic as shown in Figure 2-2.

**Figure 2-1:** a) Image of etching reactor in hot water bath. A thermometer allows the hot water bath temperature to be monitored. b) Etching reactor behind plastic isolation with warning.

**Figure 2-2:** Image of water contact angle with PSiNW array. The drop would not transfer to the surface and compression of the drop against the array indicates superhydrophobicity.

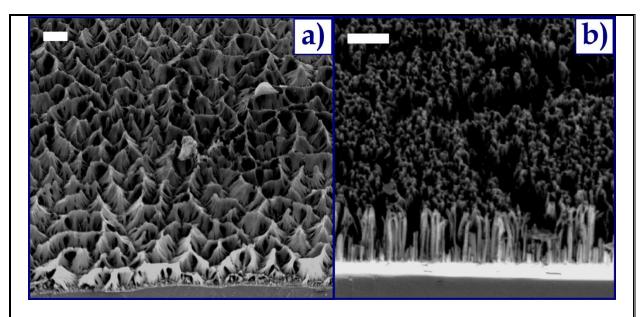

After removal of the oxide, the nanowires were transferred into pure IPA and loaded into the critical point dryer. Critical point drying is the process of drying by going through the critical point of a liquid and into the supercritical fluid regime and then pumping out the critical fluid from the drying chamber. The purpose of CPD was to mitigate any meniscus formation during the drying process, as this can result in collapse of the nanowire structures into bundles. During standard drying, and subsequent meniscus recession between the nanowires, the resulting capillary forces pull the nanowires together, as observed in Figure 2-3 a). Critical point dried nanowires remain vertically aligned as shown in Figure 2-3 b). An excellent review of the mechanics underlying the collapse process may be found in Jansen, 1996 [4]. A tousimis AUTOSAMDRI®-815B, which utilizes CO<sub>2</sub> as the supercritical drying fluid at 1400 psi and 38 °C, was utilized for the critical point drying step.

# SiC chemical vapor deposition

Polycrystalline SiC was deposited via a low-pressure chemical vapor deposition process utilizing a procedure described in detail elsewhere [5]. Growth was performed in a commercial LPCVD reactor (Tek-Vac CVD-300-M) utilizing 1,3 Disilabutane (DSB)

(Gelest Inc., >95% purity) as the SiC source. PSiNW samples were placed in the reactor immediately after oxide removal and drying. SiC deposition took place at 800  $^{\circ}$ C and 5  $\mu$ Torr with a flow of 5 sccm DSB. Deposition time was varied from 30 seconds to 3 minutes corresponding to film thicknesses of 20 to 90 nm as measured on planar Si coupons coated alongside the PSiNW samples.

**Figure 2-3:** SEM images of PSiNW arrays. a) An array which was not supercritically dried. Visible clumping of the wires is due to collapse from capillary forces during drying. b) An array which was supercritically dried. Vertical alignment of the wires is maintained. Scale bars are 10 μm.

# Physico-chemical PSiNW characterization

PSiNW morphology was characterized utilizing a NovelX mySEM scanning electron microscope. TEM images were acquired with a JEOL 2010 operated at 100 kV. Raman spectra were acquired with a HoribaJY LabRAM spectrometer in backscattering configuration with an excitation line provided by a HeNe laser (633 nm).

# Capacitance testing

The electrical double layer capacitance of the resulting electrodes was analyzed utilizing cyclic voltammetry measurements in a 3 electrode configuration consisting of a

platinum wire counter electrode and an Ag/AgCl reference electrode. The nanowire arrays acted as the working electrode. Electrical connection was made directly to the sample in the planar region protected from PSiNW etching. Measurements were performed utilizing a Chi Instruments Electrochemical Analyzer 600D. Scans were taken between a voltage range of -0.2 to 0.6 V vs. Ag/AgCl electrode. 1 M KCl was used as the electrolyte. Electrodes were cycled at least 20 times prior to data recording to ensure removal of any adsorbed contaminants. Capacitance was calculated from Equation (1):

$$C = i \frac{dt}{dV} \tag{1}$$

where i is the current density (A cm<sup>-2</sup>) at V=0.2 V during the positive sweep and dV/dt is the scan rate used for the measurement. Choosing to read the current at 0.2 V leaves out any contribution from redox reactions which may be occurring at the extremes of the voltage range and is thus a good estimate of the pure double layer capacitance of the sample.

#### **Results and Discussion**

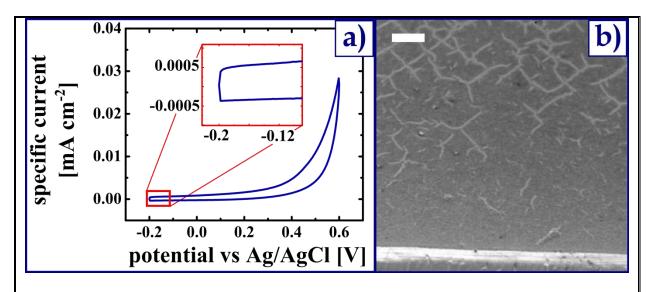

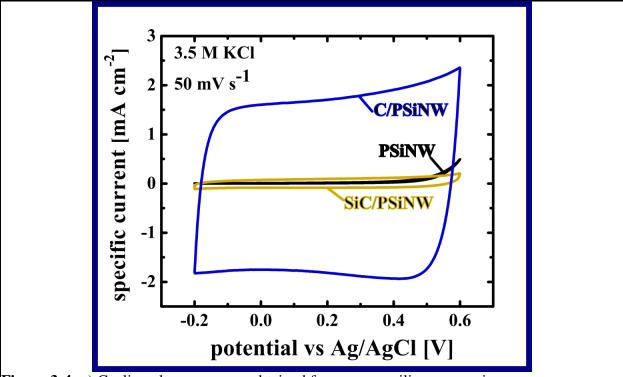

Electrochemical results - bare PSiNWs

The I-V response for the bare nanowires tested in aqueous solution, Figure 2-4 a), yields a specific capacitance is ~10  $\mu F$  cm<sup>-2</sup>, which is similar to values observed on planar silicon. An electrochemical reaction beginning during the positive potential sweep at around 0.5 V is also observed. The location and shape of this peak implies the oxidation of silicon to SiO<sub>2</sub> [6]. This was further confirmed by performing 500 charge-discharge cycles and subsequently immersing the PSiNWs in dilute HF, which selectively etches SiO<sub>2</sub>, for 10 min. Total loss of the PSiNWs after this treatment, shown in Figure 2-4 b), confirms the conversion of PSiNW's to SiO<sub>2</sub> during cycling. Rapid oxidation explains the limited capacitance values as after oxidation the nanowires are no longer electrically active. Thus, these PSiNW's as formed, are not stable in an aqueous environment, preferable for environmental impact and device packaging considerations mentioned above. This is also consistent with the fact that the VLS-grown PSiNWs have only been reported as supercapacitor electrodes in non-aqueous electrolytes [1].

Physical analysis and electrochemical analysis - SiC coated PSiNWs

**Figure 2-4:** a) Cyclic voltammetry results for uncoated PSiNW array. Note large oxidation peak and low specific current during cycling. b) SEM image of bare PSiNW array after 500 charge discharge cycles and HF etch. Note complete loss of the nanowires. Scale bar is 10 μm.

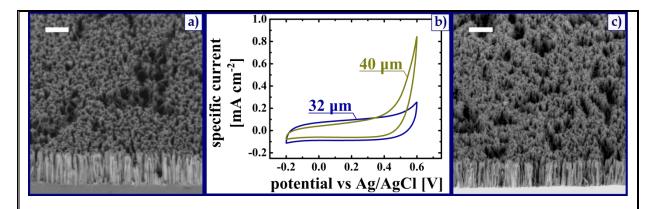

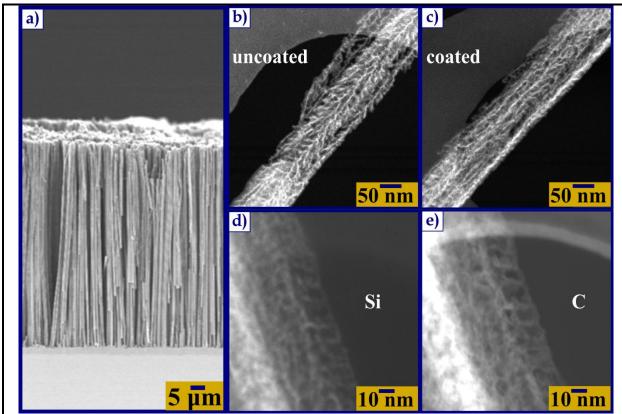

It is well known that SiC coatings are stable in harsh chemical environments [7] and thus a thin SiC layer is selected for chemically passivating the PSiNWs. SiC films are deposited onto PSiNW arrays via low pressure chemical vapor deposition after removal of surface oxide by dilute HF rinsing as described above. The SiC films appear to coat the PSiNWs conformaly as indicated by a representative SEM image of a 3 minute coating provided in Figure 2-5 a), corresponding to a 90 nm coating on a planar silicon sample. It is interesting to note that the thickness of the coating on the nanowire surface is clearly thinner than the film as measured on the planar silicon surface. A 90 nm coating of SiC on the nanowire surfaces would bridge the gap between the nanowires and result in a dense film. The exact reason for the thinness of the nanowire coating is not known for sure. However, by comparing the cyclic voltammetry results for a ~32 μm and 40 μm SiC/PSiNW array, as seen in Figure 2-5 b), the increase in oxidation peak and decrease in specific capacitive current for the latter indicate that the longer nanowires are not completely coated. While the near ideal square wave result for the 32 um array, exhibiting only a minor oxidation peak, suggests that the shorter nanowires are conformally coated. A similar cycling and HF etching was performed on the shorter coated array as that for the uncoated array discussed above. The negligible change in appearance of the array, as shown in Figure 3-5 c), also supports that the

**Figure 2-5:** a) SEM image of SiC coated PSiNW array after a coating time of 3 minutes. b) Cyclic voltammetry results for SiC/PSiNW arrays of 32 and 40 μm in length. Scale bar is 10 mm. c) SEM image of SiC/PSiNW arrays after 500 charge/discharge cycles and HF etching. Scale bars are 10 μm.

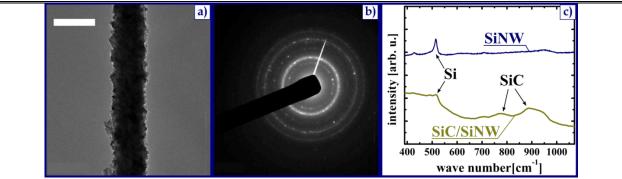

shorter nanowire arrays are conformally coated. These facts support the proposition that transport limitations for the precursor gas into the array are a factor and may be the reason for the coating on the nanowires being thinner than that on a flat substrate. TEM analysis of the nanowires, see Figure 2-6 a), indicates a highly roughened surface which is expected for the SiC deposition parameters used [13]. Diffraction patterns for the coated wires also indicate polycrystalline material, as shown in Figure 2-6 b), in contrast to the single crystalline underlying PSiNWs expected from the etching conditions [2]. Raman analysis confirms the presence of SiC on the wires, as presented in Figure 2-6 c). The SiC coating also renders the surface hydrophilic, exhibiting a near  $0^{\circ}$  contact angle with water.

**Figure 2-6:** a) TEM image of SiC/PSiNW nanowire showing evidence of a rough exterior coating. b) Diffraction pattern for single SiC/PSiNW. Sharp dots are indicative of crystalline interior, while ring pattern indicates polycrystalline material, as expected in the coating from the deposition parameters. c) Raman spectra for bare PSiNW array and SiC/PSiNW array.

**Figure 2-7:** a) Cyclic voltammetry results for SiC/PSiNW ararys with coatings of varying thickness, as marked by different coating deposition times. b) Stability results from cycling of the SiC/PSiNW array indicating ~95% capacitance retention after 1000 complete cyclic voltammetry cycles.

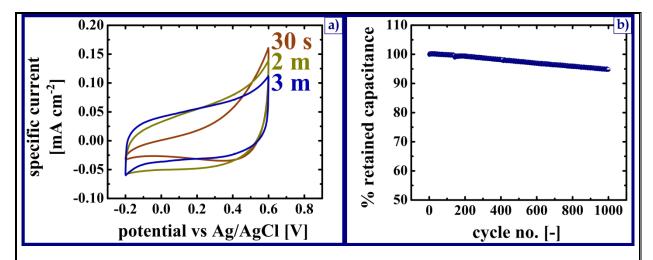

Although 3 minute coatings appear to be sufficient for corrosion mitigation, thinner coatings are attempted in order to reduce processing time. All coated samples' CV results indicate improved capacitive behavior and some measure of passivation in comparison to the uncoated nanowires. However, the corrosion peak height, normalized to the projected area of the samples, increased with decreasing coating thickness, shown in Figure 2-7 a). These results suggest that thinner coatings lead to decreased robustness during cycling, an important aspect of supercapacitor energy storage devices. Thus, the longest coating time (3 minutes) used in the initial feasibility experiment is selected for use in all further work. This coating thickness is found sufficient to maintain 95% of the initial capacitance values over the course of 1000 charge-discharge cycles, see Figure 2-7 b).

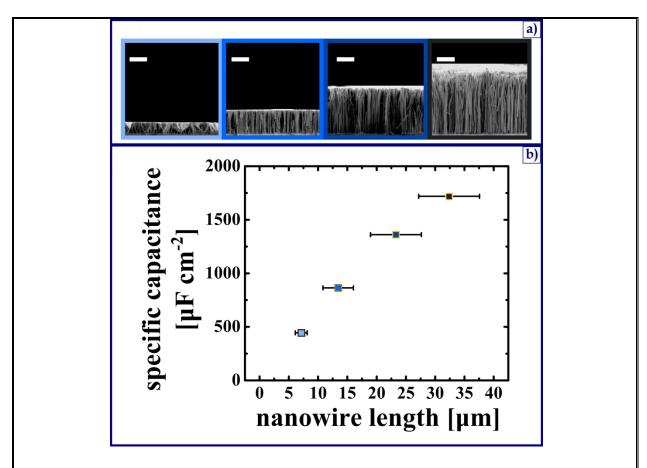

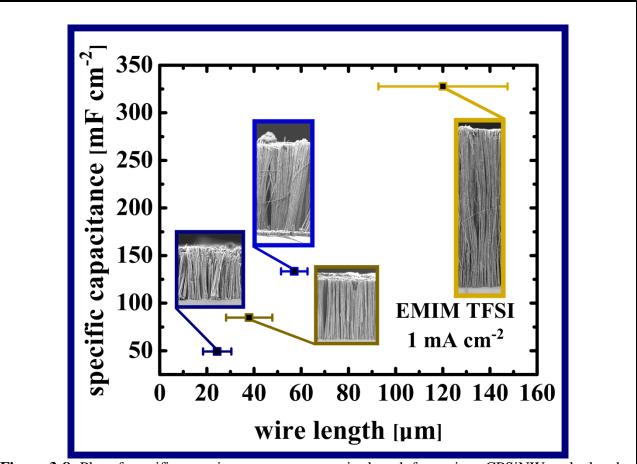

The scalability of these materials, in terms of energy storage, is investigated by generating wires of various lengths, controlled by immersion time in the PSiNW etch bath, shown in Figure 2-8 a). As is clear from Figure 2-8 b), by increasing the length of the wires, the capacitance increases linearly. For a ~32  $\mu$ m array, the longest nanowires to be conformally coated, the specific capacitance is determined to be ~1700  $\mu$ F/cm² projected area at a 50 mV/s scan rate, comparable to carbon based microsupercapacitor electrodes [9]–[13]. This corresponds to an energy storage capability of ~850  $\mu$ J/cm² projected area. Beyond this wire length, the capacitance decreases and the corrosion peak height increases, as described above. This is most likely due to issues with mass transport along the length of the wires, hindering SiC deposition at the base of the NWs.

**Figure 2-8:** a) SEM images of SiC/PSiNW arrays of different lengths, achieved by etching for varying lengths of time. Scale bars are 10 μm. b) Specific capacitance vs. SiC/PSiNW array length. Specific capacitance scales linearly with increasing length, as expected.

It appears that this is a limitation to the utilized coating process, though not to the general principle presented. Theoretical calculations, described in a later chapter, imply that the electrolyte has been excluded from the pores resulting in capacitance values expected for non-porous nanowires. Application of alternative coating methods that work well for very high aspect ratio features and are controllable at thicknesses ~1 nm, such as atomic layer deposition or those described in a later chapter, may provide a solution to these issues and yield materials with even greater energy storage capabilities.

In addition to the advantages in terms of processing and scalability of these materials in comparison to typical microsupercapacitor electrodes, the aligned nanowire configuration may provide for enhanced transport of ions to the active surface area. As

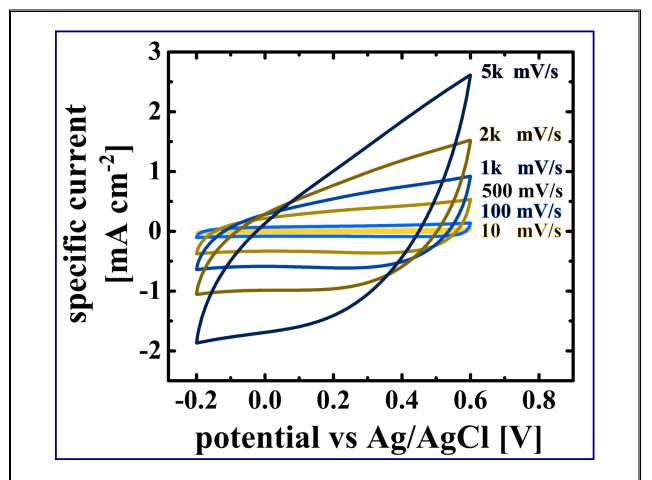

opposed to porous carbons, which typically have tortuous pathways commonly viewed as a problem for ions accessing all the available active surface area, the presented aligned nanowires have spacing of  $\sim \! 100$  nanometers, which allows for rapid ion transport during high charge-discharge rates. In order to investigate this, CV measurements are performed over a wide range of scan rates, from 10 mV/s to 5 V/s. The capacitive behavior of the materials is maintained over this range, see Figure 2-9, although a more tilted I-V response, characteristic of resistive behavior, is observed [14]. This may be mitigated through the use of doped SiC, films which are currently under investigation.

**Figure 2-9:** Cyclic voltammetry results for 32 μm long SiC/PSiNW array over a range of scan rates.

#### **Conclusions**

The application of SiC coated wet-etch formed PSiNWs as high-performance supercapacitor electrode materials for use with green electrolytes has been demonstrated. The materials are fabricated in a facile and IC compatible scheme. Capacitances of up to  $1700~\mu\text{F}/\text{cm}^2$  are achieved, and remain stable over  $10^3$  charge/discharge cycles. As well, the nanowires as formed are in electrical contact with the underlying substrate, mitigating the requirement of an additional current collector and implying straight forward integration with Si chip based devices. Limitations in the coating method include inability to coat wires of ~40  $\mu$ m and above, limiting the total energy storage capability of the SiC/PSiNW structure. Furthermore the SiC coating method results in pore blockage, mitigating the added surface area resulting from the use of porous silicon nanowires. In the following chapter an improved coating method, resulting in an ultrathin protective barrier, will be discussed and the resulting materials' performance characterized.

#### Note:

Material from the previous chapter has been adapted in part from the publication:

J. P. Alper, M. Vincent, C. Carraro, and R. Maboudian, "Silicon carbide coated silicon nanowires as robust electrode material for aqueous micro-supercapacitor," *Applied Physics Letters*, vol. 100, no. 16, p. 163901, 2012.

#### References

- [1] J. W. Choi, J. McDonough, S. Jeong, J. S. Yoo, C. K. Chan, and Y. Cui, "Stepwise Nanopore Evolution in One-Dimensional Nanostructures," *Nano Letters*, vol. 10, no. 4, pp. 1409–1413, Apr. 2010.

- [2] A. I. Hochbaum, D. Gargas, Y. J. Hwang, and P. Yang, "Single Crystalline Mesoporous Silicon Nanowires," *Nano Letters*, vol. 9, no. 10, pp. 3550–3554, Oct. 2009.

- [3] M. Zahedinejad, M. Khaje, A. Erfanian, and F. Raissi, "Successful definition of nanowire and porous Si regions of different porosity levels by regular positive photoresist using metal-assisted chemical etching," *Journal of Micromechanics and Microengineering*, vol. 21, no. 6, p. 065006, Jun. 2011.

- [4] N. Tas, T. Sonnenberg, H. Jansen, R. Legtenberg, and M. Elwenspoek, "Stiction in

surface micromachining," *Journal of Micromechanics and Microengineering*, vol. 6, no. 4, p. 385, 1996.

- [5] C. R. Stoldt, C. Carraro, W. R. Ashurst, D. Gao, R. T. Howe, and R. Maboudian, "A low-temperature CVD process for silicon carbide MEMS," *Sensors and Actuators A: Physical*, vol. 97, pp. 410–415, 2002.

- [6] F. Jing, H. Tong, and C. Wang, "Cyclic voltammetry study of silver seed layers on p-silicon (100) substrates," *Journal of Solid State Electrochemistry*, vol. 8, no. 11, pp. 877–881, Oct. 2004.

- [7] M. Mehregany, C. A. Zorman, N. Rajan, and C. H. Wu, "Silicon carbide MEMS for harsh environments," *Proceedings of the IEEE*, vol. 86, no. 8, pp. 1594–1609, 1998.

- [8] R. Maboudian, C. S. Roper, C. Carraro, and R. T. Howe, "Silicon Carbide Thin Films using 1,3-Disilabutane Single Precursor for MEMS Applications A Review," 2006, vol. 3, pp. 267–280.

- [9] Y. Q. Jiang, Q. Zhou, and L. Lin, "Planar MEMS supercapacitor using carbon nanotube forests," in *Micro Electro Mechanical Systems*, 2009. *MEMS* 2009. *IEEE* 22nd *International Conference on*, 2009, pp. 587–590.

- [10] F. Liu, A. Gutes, I. Laboriante, C. Carraro, and R. Maboudian, "Graphitization of n-type polycrystalline silicon carbide for on-chip supercapacitor application," *Applied Physics Letters*, vol. 99, no. 11, p. 112104, 2011.

- [11] J. Chmiola, C. Largeot, P. L. Taberna, P. Simon, and Y. Gogotsi, "Monolithic Carbide-Derived Carbon Films for Micro-Supercapacitors," *Science*, vol. 328, no. 5977, pp. 480–483, Apr. 2010.

- [12] P. Huang, M. Heon, D. Pech, M. Brunet, P.-L. Taberna, Y. Gogotsi, S. Lofland, J. D. Hettinger, and P. Simon, "Micro-supercapacitors from carbide derived carbon (CDC) films on silicon chips," *Journal of Power Sources*, vol. 225, pp. 240–244, Mar. 2013.

- [13] D. Pech, M. Brunet, H. Durou, P. Huang, V. Mochalin, Y. Gogotsi, P.-L. Taberna, and P. Simon, "Ultrahigh-power micrometre-sized supercapacitors based on onion-like carbon," *Nature Nanotechnology*, vol. 5, no. 9, pp. 651–654, Sep. 2010.

- [14] E. Frackowiak and F. Beguin, "Carbon materials for the electrochemical storage

Chapter 2 – Silicon carbide coated porous silicon nanowires as microsupercapacitor electrodes of energy in capacitors," *Carbon*, vol. 39, no. 6, pp. 937–950, 2001.

## Chapter 3 – Carbon coated porous silicon nanowires as microsupercapacitor electrodes

## **Chapter summary**

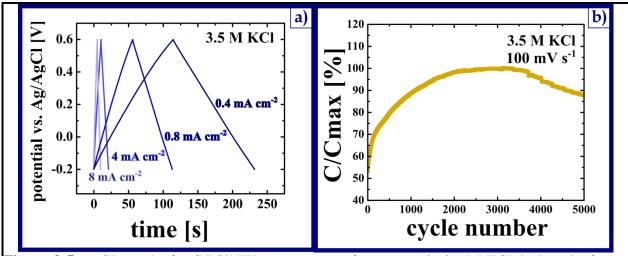

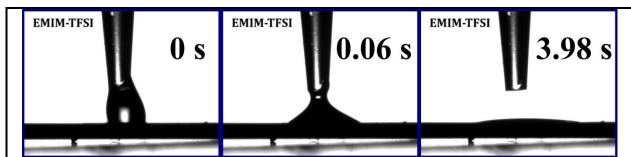

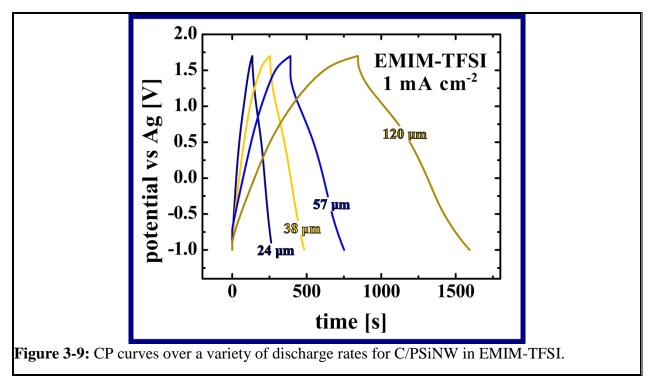

In this chapter an improved passivation method for the porous silicon nanowires discussed above is demonstrated. The thrust of the chapter is the testing of a selective coating procedure for depositing an ultra-thin (~ 1-3 nm) carbon sheath over the nanowires to passivate them. The ultra-thin nature of the coating enables solvent access to the pore area and hence a large improvement of active specific surface over the SiC coated PSiNWs discussed above. The electrochemical performance of these coated nanowires is characterized in both an aqueous electrolyte and an ionic liquid electrolyte. Specific capacitance values reaching 325 mF cm-² are achieved in ionic liquid, and calculations indicate that the theoretical maximum capacitance of the pristine wires is reached. TEM studies confirm the coating thickness and its conformality. Raman spectroscopy indicates that the carbon in the coating is mainly sp² hybridized, with corresponding high conductivity. At the time of writing, these materials represent the largest specific energy of any microsupercapacitor electrode published. A test device is prepared and demonstrated powering an LED.

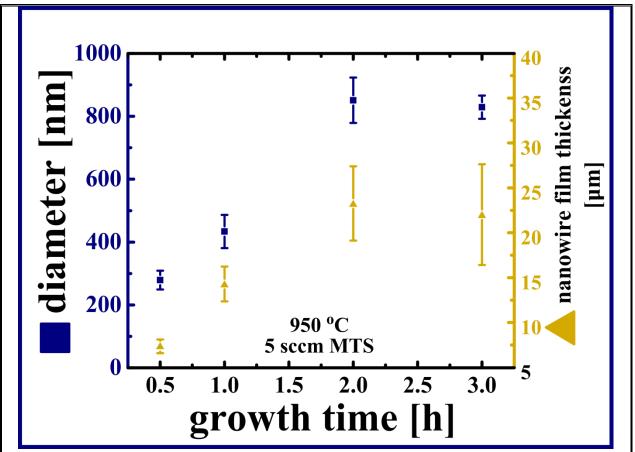

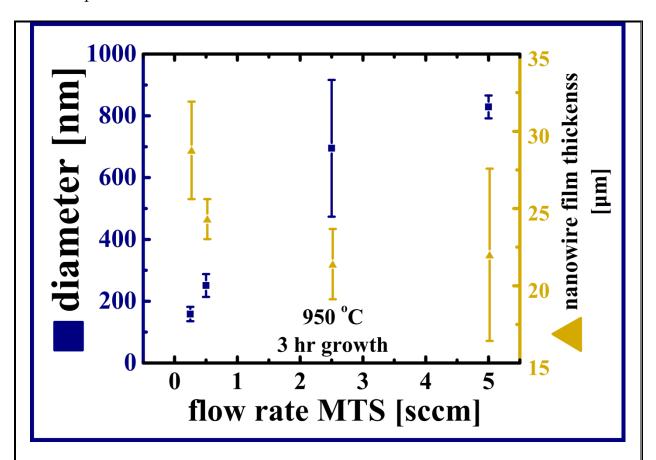

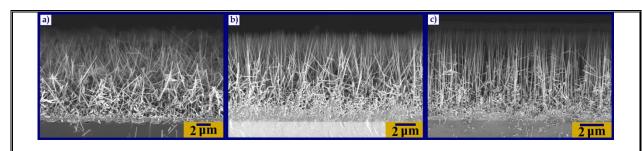

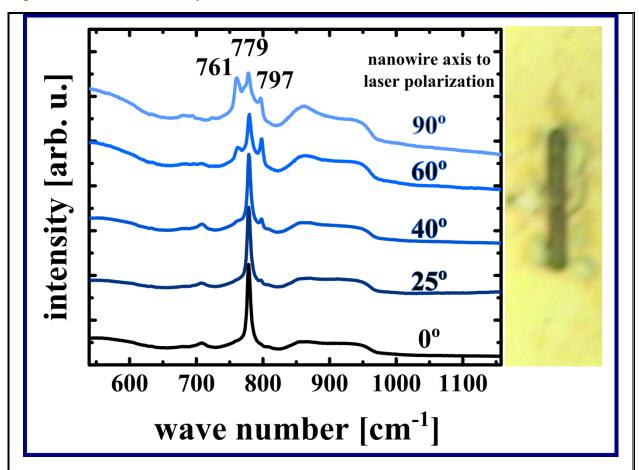

#### Introduction