## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

### Title

Regrown Extrinsic Base InP HBT with Sub-100nm Emitter Contact

### Permalink

https://escholarship.org/uc/item/3k44x071

### **Author** Fang, Yihao

**Publication Date** 2021

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

# Regrown Extrinsic Base InP HBT with Sub-100nm Emitter Contact

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Yihao Fang

Committee in charge:

Professor Mark J.W. Rodwell, Chair Professor Umesh K. Mishra Professor James F. Buckwalter Professor Jonathan Klamkin

September 2021

The Dissertation of Yihao Fang is approved.

Professor Umesh K. Mishra

Professor James F. Buckwalter

Professor Jonathan Klamkin

Professor Mark J.W. Rodwell, Committee Chair

August 2021

Regrown Extrinsic Base InP HBT with Sub-100nm Emitter Contact

Copyright  $\bigodot$  2021

$\mathbf{b}\mathbf{y}$

Yihao Fang

#### Acknowledgements

I have been incredibly privileged to have spent the last 5 years in beautiful Santa Barbara, working with the most brilliant minds in III-V semiconductors and high-frequency circuits across multiple research groups at UCSB. My advisor, Professor Mark Rodwell, has not only trained me in the technical aspects of high-frequency transistors, but also has inspired me to acquire the ability of critical thinking as a scientist in the broader sense – always pay attention to the minute details of bold claims, and analyze from first principles. Because " the devil is in the details" and "only the paranoid survives." Mark's relentless meticulousness, albeit sometimes lacking political finesse, to scientific rigor is a truly exceptional quality. He has shown me what it takes to become a great engineer. I am also grateful to my Ph.D. committee members, Professor James Buckwalter, Professor Umesh Mishra, and Professor Jonathan Klamkin, for their teaching in circuit design, device physics, and MOCVD epitaxy as well as the valuable advice and criticism during my qualifying exam and defense.

I would like to express my immense gratitude to Kang Ning, and Rob Maurer for teaching me the nitty-gritty of RF power amplifiers, and providing me with the opportunities to further my understanding of device physics from a design engineer's perspective. At the end of the day, a transistor is only as good as how much a design engineer can extract out of it. The other circuit designers, Arda Simsek, Ahmed Ahmed, Ali Farid, Utku Soylu, and Jeff Chien have also contributed to the synergy between the circuit and device teams at UCSB as well. I am indebted to Dr. Bei Shi, Lei Wang, and Simone Šuran Brunelli for introducing me to MOCVD growth of InP-related materials. Without their expertise in growth mechanisms and interpretation of morphological phenomena, I would have been clueless about how to proceed with the regrown extrinsic base process module of my thesis. I want to thank my peer device engineers, Hsin-Ying Tseng, Logan Whitaker, Brian Markman, and Matt Guidry, for help in the cleanroom and measurement lab. Though we each worked on a different project, the transfer of process modules and exchange of conversations extended my grasp of electronic devices in general.

The entire UCSB nanofab staff deserves my sincere acknowledgement. Biljana Stamenic spent days with me on the GCA Autostep to improve overlay accuracy when I first arrived at UCSB. Brian Lingg and Don Freeborn performed more late-night repairs of the ALD, PECVD, ICP, and E-beam systems than they are obliged to when few people are in the cleanroom, and are simply awesome to hang out with. Brian Thibeault, Bill Mitchell, Aidan Hopkins, Mike Day, Tino Sy, Luis Zuzunaga, Tom Reynolds, Tony Bosch, Lee Sawyer, Mike Silva, and Demis John have worked tirelessly to keep the UCSB nanofab one of, if not the best academic cleanrooms in the country. Aidan Taylor of the microscopy lab at CNSI offered tremendous help with the FIB and TEM systems and went out the way to take atomic resolution images for the Rodwell research group.

A special thanks goes to Audra Pearce, and Val De Veyra for helping me navigate the complicated bureaucratic and logistic problems I encountered. I am also thankful for the professional advice and encouraging comments during the difficult COVID-19 times from my SRC liaisons, Han Wui Then, Paul Fischer, Phillip Chang, and Bob Lempkowski.

Last but not least, I want to thank my colleague and girlfriend, Hsin-Ying Tseng, again for being the emotional support in and out of the cleanroom. When not a single process step stays in specs in the cleanroom, thank you for standing by my side through the most stressful times of my career. Thank you.

### Curriculum Vitae Yihao Fang

### Education

| 2021 | Ph.D. in Electrical and Computer Engineering,                     |

|------|-------------------------------------------------------------------|

|      | University of California Santa Barbara, Santa Barbara, CA         |

| 2020 | M.S. in Electrical and Computer Engineering,                      |

|      | University of California Santa Barbara, Santa Barbara, CA         |

| 2016 | B.S. in Materials Science and Engineering (Electronic Materials), |

|      | University of California Los Angeles, Los Angeles, CA             |

### Publications

- 1. H.-Y. Tseng, Y. Fang, W. Mitchell, A. Taylor, M. Rodwell, "Atomic Layer Deposition of TiN/Ru Gate in InP MOSFETs" *Applied Physics Letters, Submitted, AIP.*

- M. Rodwell, B. Markman, Y. Fang, H.-Y. Tseng, A. Ahmed, "Transistors for 100-300GHz Wireless," 2021 European Solid-State Device Research Conference, Grenoble, France.

- K. Ning, Y. Fang, M.J.W. Rodwell, J.F. Buckwalter, "A 130-GHz Power Amplifier in a 250-nm InP Process with 32% PAE," 2020 Radio Frequency Integrated Circuits (RFIC) Symposium, IEEE.

- 4. K. Ning, Y. Fang, N. Hosseinzadeh, J.F. Buckwalter, "A 30-GHz CMOS SOI Outphasing Power Amplifier With Current Mode Combining for High Backoff Efficiency and Constant Envelope Operation," *IEEE Journal of Solid-State Circuits*, 1411-1421, *IEEE*.

- J.P. Sculley, B. Markman, U. Soylu, Y. Fang, M.E. Urteaga, A.D. Carter, M.J.W. Rodwell, P.D. Yoder, "Monte Carlo Investigation of Traveling Accumulation Layers in InP Heterojunction Bipolar Transistor Power Amplifiers," 2019 IEEE BiC-MOS and Compound semiconductor Integrated Circuits and Technology Symposium (BCICTS), 1-4, IEEE.

- 6. Y. Fang, H.Y. Tseng, M.J.W. Rodwell, " $W_e = 100$ nm InP/lnGaAs DHBT with Self-aligned MOCVD Regrown p-GaAs Extrinsic Base Exhibiting  $1\Omega \mu m^2$  Base Contact Resistivity," 2019 Device Research Conference (DRC), 179-180, IEEE.

- J.P. Sculley, Y. Fang, B. Markman, M.E. Urteaga, A.D. Carter, M.J.W. Rodwell, P.D. Yoder, "First Principles Study of Collector Transit Time Modulation in Double Heterojunction Bipolar Transistors," 2019 Device Research Conference (DRC), 105-106, IEEE.

- H.Y. Tseng, Y. Fang, S. Zhong, M.J.W. Rodwell, "InP MOSFETs Exhibiting Record 70 mV/dec Subthreshold Swing," 2019 Device Research Conference (DRC), 183-184, IEEE.

- M. Urteaga, A. Carter, Y. Fang, B. Markman, M.J.W Rodwell, J. Sculley, D. Yoder, "Development of a High Power Density Millimeter-Wave InP HBT Technology," 2019 GOMACTech Conference, Albuquerque, NM.

- M.J.W. Rodwell, Y. Fang, J. Rode, J. Wu, B. Markman, S.T. Suran Brunelli, J. Klamkin, M. Urteaga, "100-340ghz systems: Transistors and applications," 2018 IEEE International Electron Devices Meeting (IEDM), pp. 14-3, IEEE.

- 11. Y. Fang, J.P. Sculley, M.E. Urteaga, A.D. Carter, P.D. Yoder, M.J.W. Rodwell, "Design of InP Segmented-collector DHBTs with Reduced Collector Transit Time  $\tau_c$  for Large Power Bandwidth Power Amplifiers," 2018 Device Research Conference (DRC), pp. 1-2, IEEE.

- 12. J. Wu, Y. Fang, B. Markman, H.Y. Tseng, M.J.W. Rodwell, " $L_g = 30$  nm InAs Channel MOSFETs Exhibiting  $f_{max} = 410$  GHz and  $f_t = 357$  GHz," *IEEE Electron Device Letters 39 (4), 472-475.*

- 13. Y. Fang, H.Y. Tseng, H.W. Chiang, B. Markman, M.J.W. Rodwell, "90nm Emitter Width InGaAs/InP DHBTs with DC Current Gain  $\beta > 40$ ," 2018 Lester Eastman Conference on High Performance Devices, Columbus, OH.

- Q. Chen, H. Zhou, Y. Fang, A.Z. Stieg, T. Song, H.H. Wang, X. Xu, Y. Liu, S. Lu, J. You, P. Sun, J. McKay, M.S. Goorsky, Y. Yang, "The optoelectronic role of chlorine in CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub>(Cl)-based perovskite solar cells," *Nature Communications* 6, 7269.

- 15. H.H. Wang, Q. Chen, H. Zhou, L. Song, Z. St. Louis, N. De Marco, Y. Fang, P. Sun, T. Song, H. Chen, Y. Yang, "Improving the TiO<sub>2</sub> electron transport layer in perovskite solar cells using acetylacetonate-based additives," *Journal of Materials Chemistry A 3 (17), 9108-9115.*

#### Abstract

Regrown Extrinsic Base InP HBT

#### with Sub-100nm Emitter Contact

#### by

#### Yihao Fang

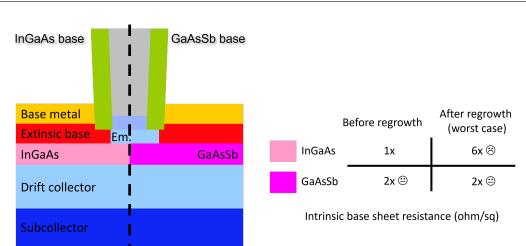

This work presents the efforts pursued to optimize InP HBTs for power amplifiers above 100 GHz. Emitter width  $W_e$  reduction to sub-100nm dimension is achieved using a novel cosputtered  $Ti_{4wt\%}W$  emitter metal, and high power ICP dry etching. The cosputtering process enables fine-tuning of TiW alloy composition for vertical dry etch profile along sidewalls of the 600nm tall emitter metal, retaining sub-100nm emitter width from top to bottom. Base contacts are formed by low-temperature MOCVD regrowth (490 °C) of thick p-GaAs (>  $4 \times 20 \, cm^{-3}$ ) extrinsic base on the intrinsic p-InGaAs or p-GaAsSb base layer, and subsequent UV i-line lift-off of e-beam deposited Pt/Ti/Pd/Au metal stack. Low overall base contact resistivity  $\rho_{b,c}$  is extracted by TLM on scaled sub-100nm  $W_e$  DC "large area" devices to be  $0.98 \pm 0.4 \Omega$ - $um^2$ , which meets the requirement for >2THz  $f_{max}$  scaling. The larger bandgap of p-GaAs allows direct abutment of the regrown extrinsic base against sides of the n-InP emitter semiconductor, while blocking undesired electron injection into the extrinsic base. The extended regrown extrinsic base, thus, lowers  $R_{gap}$  by a factor of >2 between the base contact metal and emitter semiconductor, a significant contributor to  $R_{bb}$  in deep submicron HBTs, thanks to the much lower sheet resistance of the extrinsic base ( $\rho_{s,ex} < 300\Omega/\Box$ ). Hydrogen passivation of carbon dopants in the p-InGaAs intrinsic base layer is found, and partially reversed with an in-situ  $N_2$  anneal in MOCVD before temperature ramp down. Lateral hydrogen out-diffusion is believed to limit carbon dopant reactivation as the smallest  $W_e$  devices showed the lowest apparent intrinsic base sheet resistance  $(\rho_{s,in} = 1900\Omega/_{\Box})$  after the  $N_2$  anneal. While the added base spreading resistance  $R_{spread}$  underneath emitter semiconductor is manageable in sub-100nm  $W_e$  devices, DC devices with a GaAsSb intrinsic base are studied as a passivation-proof alternative to InGaAs for maximum  $R_{bb}$  scaling. Collector-base capacitance  $C_{cb}$  scaling is intentionally excluded in this work, so is vertical epitaxial scaling for higher  $f_T$ , as both face challenges in terms of lithographic and semiconductor doping limits. RF device integration faced tremendous logistic difficulties due to the pandemic lockdown. Nevertheless, working RF devices with  $f_{max}$  in excess of 300GHz are demonstrated. In addition, a detailed review of conventional InP HBT scaling roadmap shows drawbacks of continued  $C_{cb}$ , and  $f_T$  scaling in sub-100nm  $W_e$  process (e.g., high  $R_{gap}$ , and stagnating  $C_{cb}$ ) previously overlooked due to simplified assumptions. It can be shown that conventional beyond-130-nm technology nodes offer comparable or worse device performance, a trend that can be reversed by the insertion of the regrown extrinsic base process module already a reality in SiGe HBT.

## Contents

| Cu  | irric                                                        | ulum Vitae                                                                                                                                                                                                                                                                                                                                                                                          | $\mathbf{v}$                                                                                          |

|-----|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Ał  | ostra                                                        | $\mathbf{ct}$                                                                                                                                                                                                                                                                                                                                                                                       | viii                                                                                                  |

| Lis | st of                                                        | Figures                                                                                                                                                                                                                                                                                                                                                                                             | xii                                                                                                   |

| Lis | st of                                                        | Tables                                                                                                                                                                                                                                                                                                                                                                                              | viii                                                                                                  |

| 1   | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8 | oductionTransistor Technologies for RF Power Amplifiers $f_T \& f_{max}$ Scaling, $JFOM$ , and $P_{sat-50\Omega}$ $f_{50\Omega}$ – Lumped or Distributed Element?Relation between Power Combining and $f_{50\Omega}$ $Z_{conj}$ and $Z_{OPT}$ Mismatch and $PAE$ LimitApproaches to Off-Roadmap InP HBT ScalingTransferred-substrate Low Thermal Conductivity InP HBTRegrown Extrinsic Base InP HBT | 1<br>4<br>10<br>14<br>16<br>23<br>23<br>26                                                            |

|     | 1.9<br>Refe                                                  | Conclusions                                                                                                                                                                                                                                                                                                                                                                                         | 27<br>29                                                                                              |

| 2   | $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6$                     | ign of Intrinsic InP HBT         Principle of Operation         Conventional InP HBT Scaling Roadmap         Intrinsic Epitaxial Design for 130 nm InP HBT         TLM Resistance Test Structure         RF Device Measurement         Conclusions         rences                                                                                                                                   | <ul> <li><b>35</b></li> <li>42</li> <li>47</li> <li>50</li> <li>52</li> <li>58</li> <li>60</li> </ul> |

| 3   | <b>Ana</b><br>3.1<br>3.2<br>3.3                              | Ilysis of Regrown p-GaAs Extrinsic Base InP HBTTheory of Regrown Extrinsic Base InP HBTDerivation and Simulation of $R_{bb}$ with Extrinsic BaseSimulated 50 $\Omega$ Power Cell Performance                                                                                                                                                                                                        | <b>67</b><br>68<br>71<br>76                                                                           |

|          | 3.4 Conclusions                                                  | 79  |

|----------|------------------------------------------------------------------|-----|

|          | References                                                       | 80  |

| 4        | Process Module Development                                       | 83  |

|          | 4.1 Development of Self-aligned Sub-100 nm Emitter Metal Contact | 84  |

|          | 4.2 Development of p-GaAs Selective Growth by MOCVD              | 88  |

|          | 4.3 Sub-100 nm Emitter DC Large Area Regrown Extrinsic Base HBT  | 95  |

|          | 4.4 Base-collector Diode with Extrinsic Base                     | 98  |

|          | 4.5 Ultra-low Contact Resistivity to p-type Semiconductors       | 100 |

|          | 4.6 Conclusions                                                  | 104 |

|          | References                                                       | 106 |

| <b>5</b> | Device Results                                                   | 111 |

|          | 5.1 DC Large Area Device – RG62B                                 | 112 |

|          | 5.2 DC Large Area Device – RG67A                                 | 117 |

|          | 5.3 DC Large Area Device – RG67D                                 | 121 |

|          | 5.4 RF Process Integration – RG64RF-F                            | 125 |

|          | 5.5 Conclusions                                                  | 130 |

|          | References                                                       | 132 |

| 6        | Conclusions                                                      | 135 |

|          | 6.1 Summary                                                      | 135 |

|          | 6.2 Future Work                                                  | 136 |

|          | References                                                       | 141 |

| A        | Regrown Extrinsic Base HBT Process Flows                         | 143 |

| в        | Process Recipes                                                  | 171 |

## List of Figures

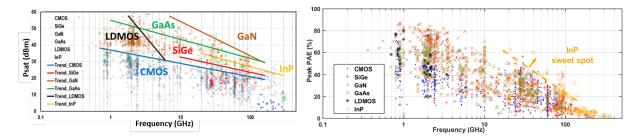

| 1.1  | RF PA $P_{sat}$ (left), and peak $PAE$ (right) vs. frequency in various processes            | 2  |

|------|----------------------------------------------------------------------------------------------|----|

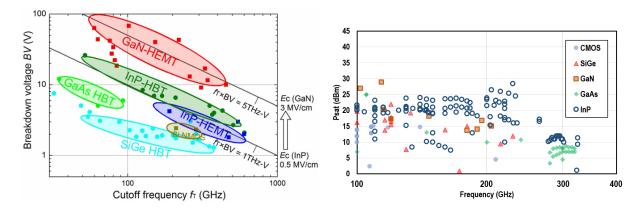

| 1.2  | $BV$ vs. $f_T$ with $JFOM$ asymptotes (left); $P_{sat}$ vs. frequency > 100 GHz              |    |

|      | (right)                                                                                      | 3  |

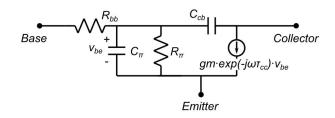

| 1.3  | Basic hybrid- $\pi$ small-signal model of an HBT $\ldots \ldots \ldots \ldots \ldots \ldots$ | 4  |

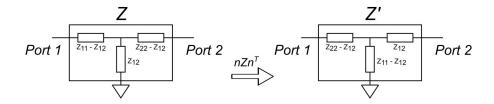

| 1.4  | $Z' = n_{perm} Z n_{perm}^T$ rotates the three terminals counter-clockwise                   | 6  |

| 1.5  | Maximum power gain matching for U that requires $Z_{conj}$ load matching.                    | 7  |

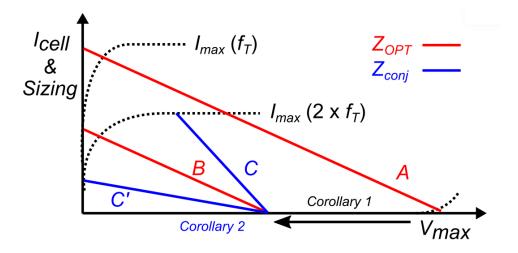

| 1.6  | A $2 \times f_T$ shifts loadline A to B for a 1:4 $P_{sat}$ (Corollary 1), and the mismatch  |    |

|      | between loadlines B and C & C' due to mismatch between $Z_{conj}$ and $Z_{OPT}$              |    |

|      | (Corollary 2)                                                                                | 8  |

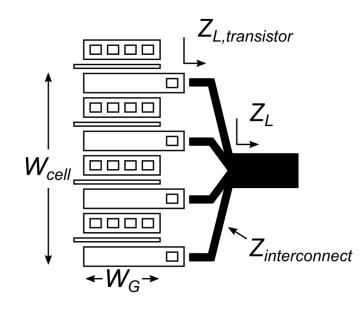

| 1.7  | Schematic of a CMOS PA cell with only output wiring shown for clarity .                      | 10 |

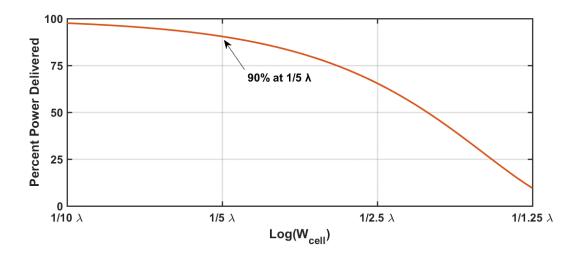

| 1.8  | Tradeoff between power delivery efficiency vs. power cell width $W_{cell}$ due               |    |

|      | to phase mismatch                                                                            | 11 |

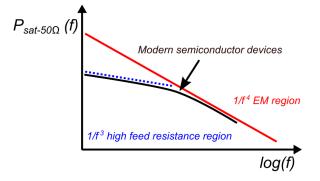

| 1.9  | $P_{sat-50\Omega}$ as a function of frequency for high feed resistance transistors (Si       |    |

|      | CMOS), and low feed resistance transistors (III-Vs)                                          | 12 |

| 1.10 | $I_{cell}$ decreases in proportion to cell sizing with constant $I_{max}$ at frequency       |    |

|      | above $f_{50\Omega}$ , whereas $V_{cell}$ becomes less than transistor $V_{max}$             | 13 |

| 1.11 | Conventional Wilkinson N-way power combiners using $log_2(N)$ sections of                    |    |

|      | $\lambda/4$ transmission line (left) vs. single-section $\lambda/4$ transmission line N-way  |    |

|      | corporate power combiners (right)                                                            | 14 |

| 1.12 | Loss of single-section $\lambda/4$ transmission line N-way corporate power com-              |    |

|      | biners in typical BCB wiring environment in InP HBT                                          | 15 |

| 1.13 | Theoretical $P_{sat}$ of power-combined PA in various technologies up to cor-                |    |

|      | responding $f_{max}$ , including effects of $f_{50\Omega}$ and power combining (finger       |    |

|      | length is kept constant for low RC delay)                                                    | 16 |

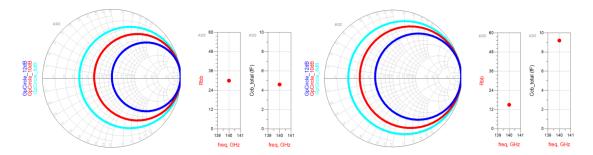

| 1.14 | Common-emitter $G_p$ circles of a $3\mu$ m-long 250 nm InP HBT (left) vs.                    |    |

|      | those of a modified HBT with half the $R_{bb}$ and twice the $C_{cb}$ (right)                | 16 |

| 1.15 | Common-base $G_p$ circles of a $3 \mu$ m-long 250 nm InP HBT (left) vs. those                |    |

|      | of a modified HBT with half the $R_{bb}$ and twice the $C_{cb}$ (right)                      | 17 |

| 1.16 | $P_{out}$ modeled as a fraction of $MSG$ due to the mismatch between $Z_{OPT}$               |    |

|      | and $\operatorname{Re}\{Z_{conj}\}$                                                          | 17 |

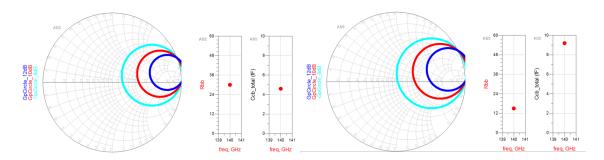

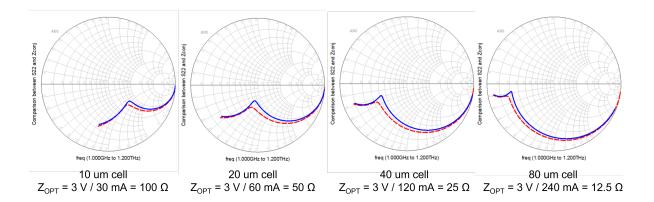

| 1.17 | A comparison between power cell $Z_{out}$ and $Z_{conj}$ at different transistor<br>sizings in 130 nm InP HBT where the blue curves are exact $S_{22}$ of the |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | hyrid- $\pi$ model, and red dashed lines approximations per Eq. 1.15                                                                                          | 19 |

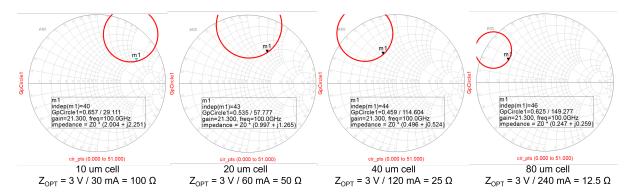

| 1.18 | 21.3 dB operating gain $G_P$ at 100 GHz with various transistor sizings and                                                                                   | 10 |

|      | associated $Z_{OPT}$ in 130 nm InP HBT                                                                                                                        | 19 |

| 1.19 | 10.5 dB operating gain $G_P$ at 24 GHz with various transistor sizings and                                                                                    | 10 |

|      | associated $Z_{OPT}$ in 75 nm GaN HEMT                                                                                                                        | 20 |

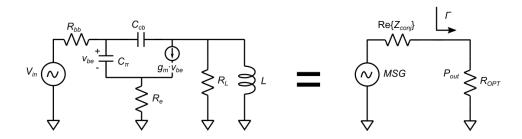

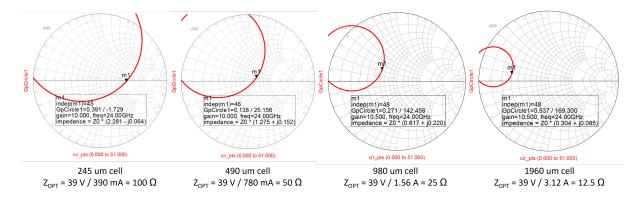

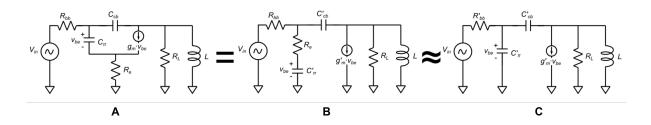

| 1.20 | Hyprid- $\pi$ models for alternative large-signal gain analysis                                                                                               | 21 |

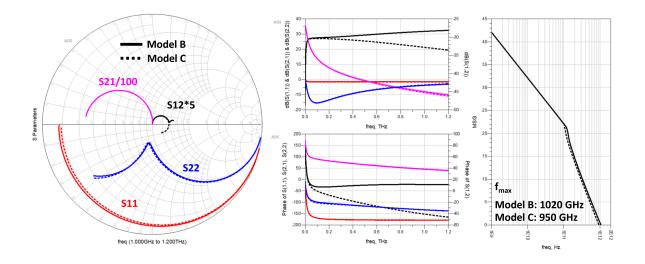

|      | Comparison between a $0.13 \times 20 \ \mu m^2 \ 50 \ \Omega$ InP HBT modeled by Model                                                                        |    |

|      | B & C in terms of S parameters in the Smith chart (left), dB and phase                                                                                        |    |

|      | of S parameters (center), and transistor MSG (right)                                                                                                          | 22 |

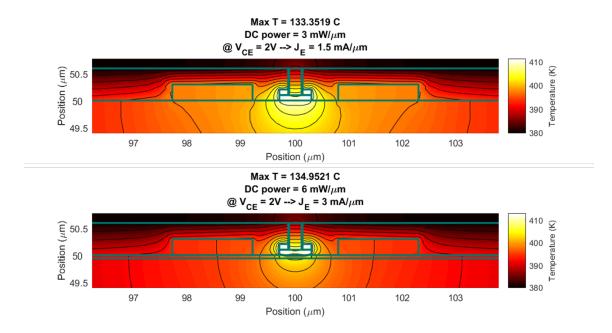

| 1.22 | Temperature profile of conventional 250 nm InP HBT under typical bias                                                                                         |    |

|      | conditions (top) vs. transferred-substrate InP HBT with Au subcollector                                                                                       |    |

|      | 50 nm below device drift collector (bottom)                                                                                                                   | 24 |

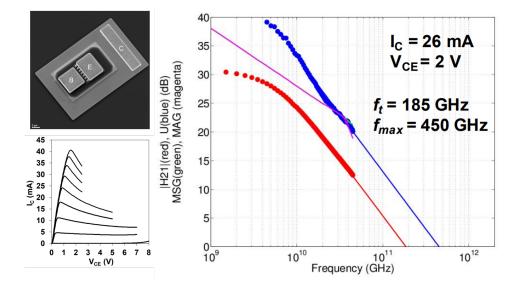

| 1.23 | An 8-finger $0.25 \times 5\mu m^2$ transferred-substrate InP reported by Teledyne                                                                             |    |

|      | Scientific & Imaging                                                                                                                                          | 25 |

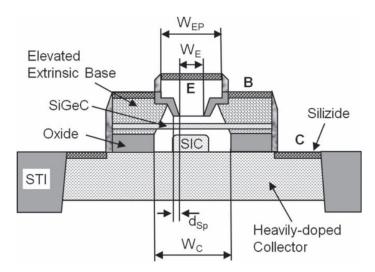

| 1.24 | Schematic cross-section of a SiGe HBT with the elevated extrinsic base .                                                                                      | 26 |

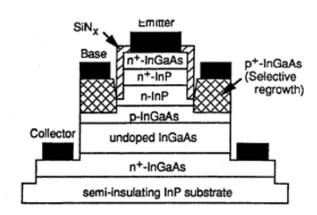

| 1.25 | Regrown extrinsic base InP HBT with a realigned emitter contact reported                                                                                      |    |

|      | in 1996                                                                                                                                                       | 27 |

| 2.1  | Band alignment of a graded heterojunction InP HBT with doping-graded                                                                                          |    |

| 2.1  | base (left); Early onset of $\gamma$ degradation in an <i>abrupt</i> InP/InGaAs emitter-                                                                      |    |

|      | base junction (right)                                                                                                                                         | 35 |

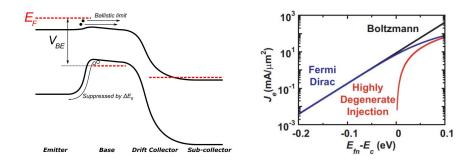

| 2.2  | $\rho_{c,b}$ to base (left), $\rho_{sh}$ of 30nm thick p-InGaAs (center), and $\beta_F$ vs. doping                                                            | 00 |

| 2.2  | $p_{c,b}$ to base (100), $p_{sh}$ of boinn thick p induits (center), and $p_F$ vs. doping conc. (right)                                                       | 37 |

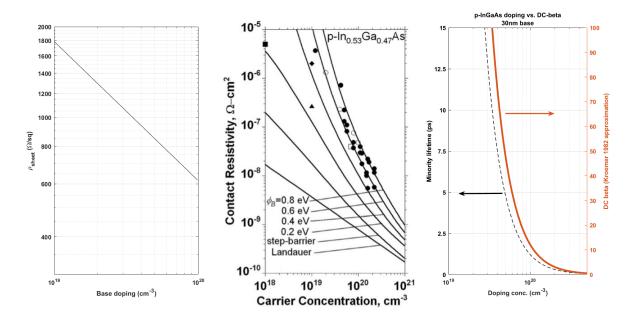

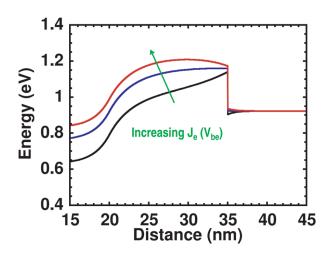

| 2.3  | Electric field profils in the collector when $J_c < J_{crit}$ , $J_c = J_{crit}$ , and $J_c < J_{Kirk}$                                                       | 39 |

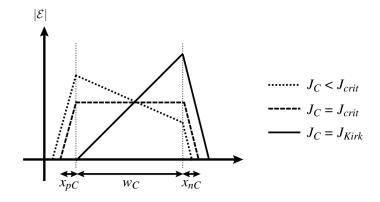

| 2.4  | Monte Carlo results (left) show comparable extent of velocity overshoot                                                                                       | 00 |

|      | vs. empirical calculations (right)                                                                                                                            | 40 |

| 2.5  | Emitter starvation under high current injection                                                                                                               | 41 |

| 2.6  | correspondence between physical elements and small signal model circuit                                                                                       |    |

|      | components                                                                                                                                                    | 42 |

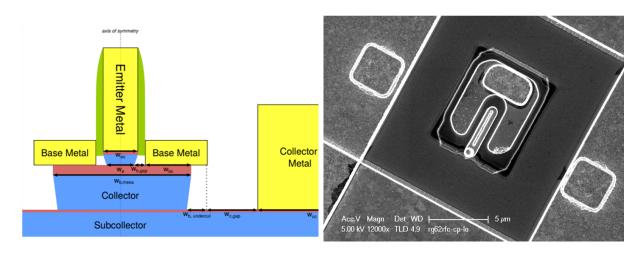

| 2.7  | Cross-sectional schematic of a conventional InP mesa HBT with critical                                                                                        |    |

|      | dimensions indicated (left), and a top-down view of an InP HBT embedded                                                                                       |    |

|      | in TRL wiring environment prior to BCB planarization (right)                                                                                                  | 43 |

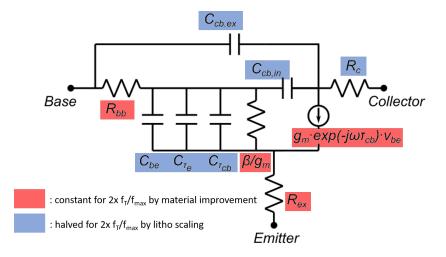

| 2.8  | Improvement in small-signal parameters categorized into lithographic fea-                                                                                     |    |

|      | ture size driven (blue) and materials science driven (red)                                                                                                    | 46 |

| 2.9  | TLM modeling for contact resistance                                                                                                                           | 50 |

| 2.10 | Block diagram of a fictious VNA without an internal bias-tee along port                                                                                       |    |

|      | 1's signal path, and with an internal bias-tee along port 2's signal path .                                                                                   | 53 |

|      | Two-tier calibration scheme to move reference plane to transistor                                                                                             | 54 |

| 2.12 | Calibration validation on a 3 ps delay line standard for return loss and                                                                                      |    |

|      | phase vs. frequency                                                                                                                                           | 55 |

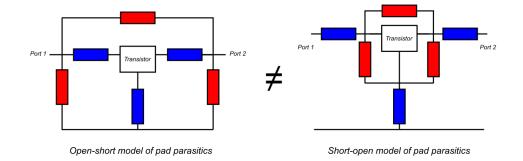

| 2.13         | Equivalent models for open-short embedding and short-open embedding,<br>where red boxes denote parallel Y-components, and blue series Z-components                                                                                                             |          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              |                                                                                                                                                                                                                                                                | 56       |

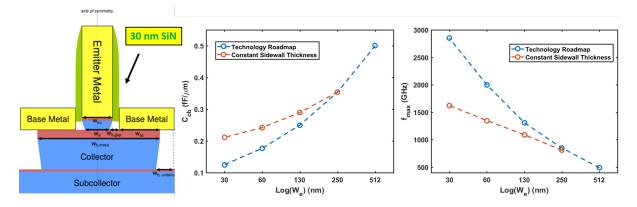

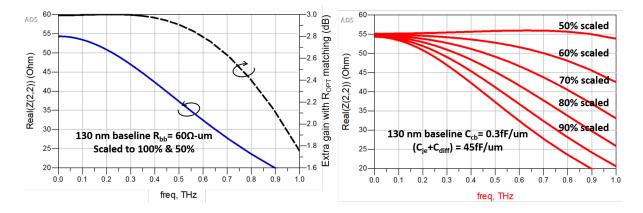

| 3.1          | $C_{cb}$ non-scaling due to constant emitter dielectric sidewall thickness, and resultant slow-down in $f_{max}$ scaling                                                                                                                                       | 68       |

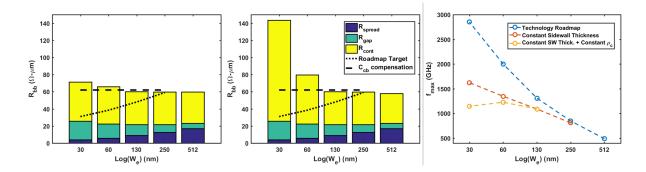

| 3.2          | $R_{bb}$ non-scaling due to constant sidewall thickness (left), together with<br>non-scaling 5 $\Omega$ - $\mu$ m <sup>2</sup> contact resistivity $\rho_{b,c}$ (center), and resultant slow-                                                                  |          |

|              | down in $f_{max}$ scaling (right)                                                                                                                                                                                                                              | 69       |

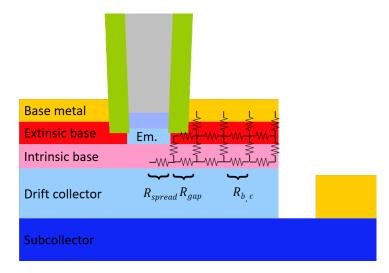

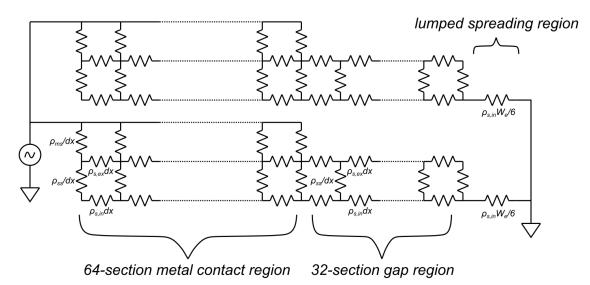

| $3.3 \\ 3.4$ | Schematic cross section of a regrown extrinsic HBT with gap region underfill 96-section FEM model for $R_{bb}$ ADS simulations $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                     | 70<br>72 |

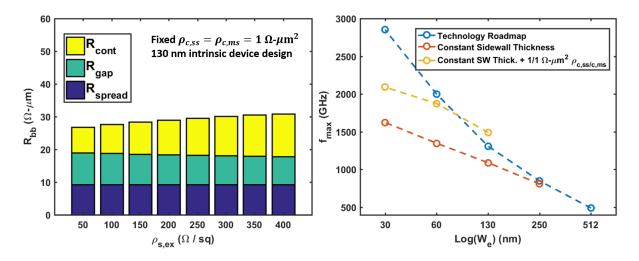

| 3.5          | $R_{bb}$ as a slow varying function of $\rho_{s,ex}$ between 50 $\Omega/\Box$ and 400 $\Omega/\Box$ (left),<br>and simulated $f_{max}$ across scaling generations with $\rho_{c,ss} = \rho_{c,ms} = 1 \ \Omega - \mu \mathrm{m}^2$                             | 73       |

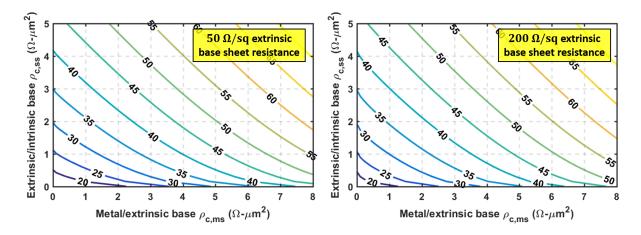

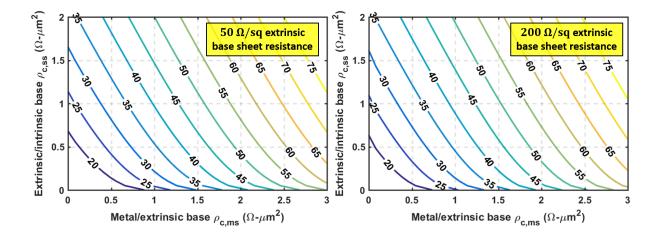

| 3.6          | $R_{bb}$ ( $\Omega$ - $\mu$ m) as a function of contact resistivities $\rho_{c,ss}$ and $\rho_{c,ms}$ , assuming 130 nm intrinsic device parameters                                                                                                            | 74       |

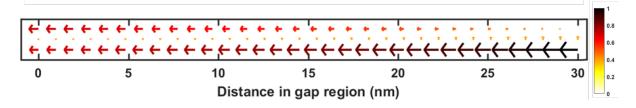

| 3.7          | Simulated current distribution in the gap region with $850/200 \ \Omega/\Box$ intrin-<br>sic/extrinsic sheet resistances, and $1 \ \Omega-\mu m^2$ regrown interfacial resistivity<br>(Note the small vertical vectors denote current flows across the intrin- |          |

|              | sic/extrinsic interface)                                                                                                                                                                                                                                       | 75       |

| 3.8          | $R_{bb}$ ( $\Omega$ - $\mu$ m) as a function of contact resistivities $\rho_{c,ss}$ and $\rho_{c,ms}$ , assuming                                                                                                                                               |          |

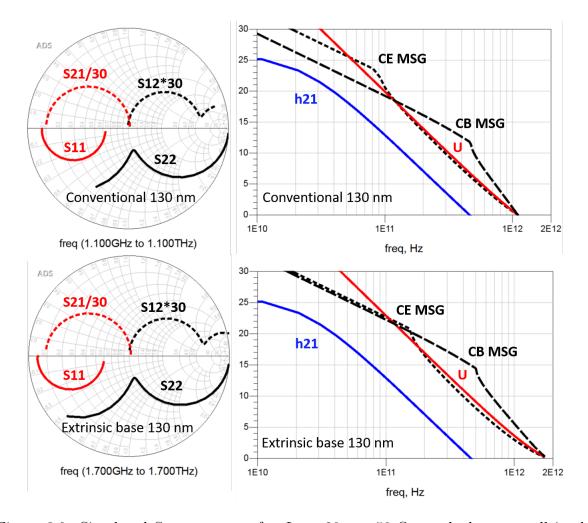

| 3.9          | 30 nm intrinsic device parameters $\dots \dots \dots$                                                                                                          | 76       |

|              | the conventional 130 nm technology (top), compared to that in a regrown                                                                                                                                                                                        | 77       |

| 3.10         | extrinsic 130 nm technology with $0.5 \times R_{bb}$                                                                                                                                                                                                           | 77       |

|              | vs. in a fictious HBT technology with its $C_{cb}$ scaled to 50%                                                                                                                                                                                               | 78       |

| 4.1          | Improved conventional dual-layer W/Ti <sub>10wt%</sub> W emitter metal stack by pre-                                                                                                                                                                           |          |

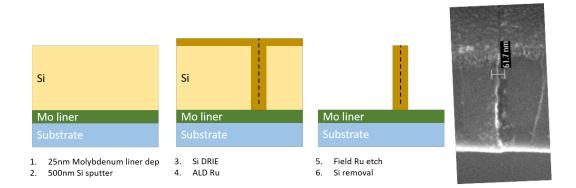

| 4.2          | vious group members (left), and notching at the dual-layer interface (right) ALD Ru semi-damascene process (left), and a 60 nm wide 500 nm via                                                                                                                 | 84       |

|              | filled with Ru before etch back (right)                                                                                                                                                                                                                        | 85       |

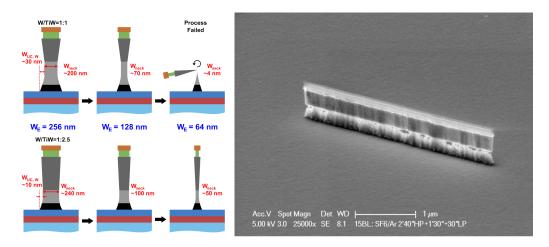

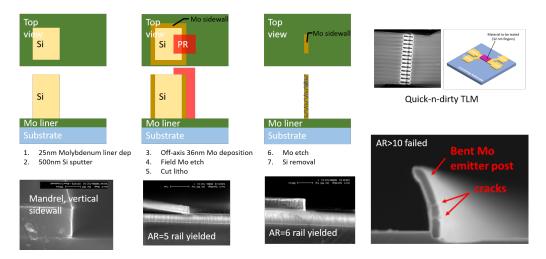

| 4.3          | Double-patterning Si sidewall process with bent emitter metal structures                                                                                                                                                                                       | 00       |

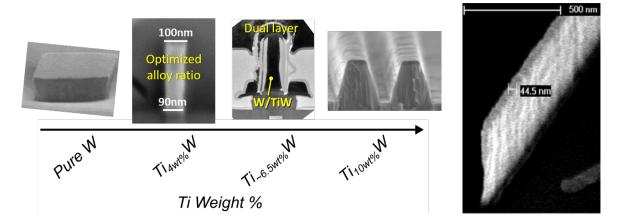

| 4.4          | above 10 aspect ratio $\ldots$ Ti weight percent in $Ti_{xwt\%}W$ vs. sidewall profile (left), and sub-60 nm                                                                                                                                                   | 86       |

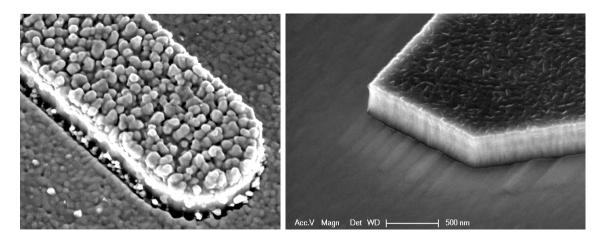

| 4.5          | scaling capability of homogeneous $Ti_{4wt\%}W$ alloy composition GaAs phase diagram appropriate for MOCVD growth                                                                                                                                              | 87<br>88 |

| 4.5<br>4.6   | In-rich precipitates on a test emitter metal structure (left) vs. good growth                                                                                                                                                                                  |          |

| A 🗁          | selectivity (right)                                                                                                                                                                                                                                            | 89       |

| 4.7          | Amphoteric doping of carbon in GaAs as a function of V/III ratio $\ldots$                                                                                                                                                                                      | 90       |

| 4.8  | At constant TMIn, TMGa, and TBAs flows, a 17 sccm $CBr_4$ flow yields al-                                                                                                                                                          |        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|      | most pure relaxed InAs (left), whereas a 150 sccm $CBr_4$ flow yields almost                                                                                                                                                       |        |

|      | pure relaxed GaAs (right)                                                                                                                                                                                                          | 91     |

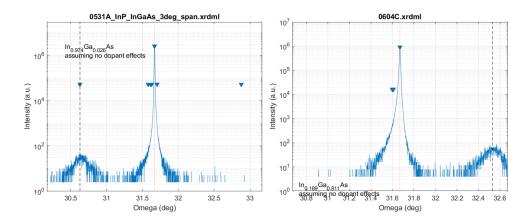

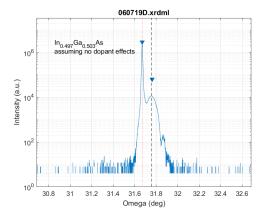

| 4.9  | Close to lattice-match carbon-doped InGaAs grown at 500°<br>C $\hdots$                                                                                                                                                             | 92     |

| 4.10 | Cross-hatches visible after growth (left), and undercut along cross-hatches after isolation (right)                                                                                                                                | 93     |

| 4.11 | Tungsten emitter structure oxidized after RTA anneal (left) vs. no oxida-<br>tion after in-situ MOCVD anneal                                                                                                                       | 93     |

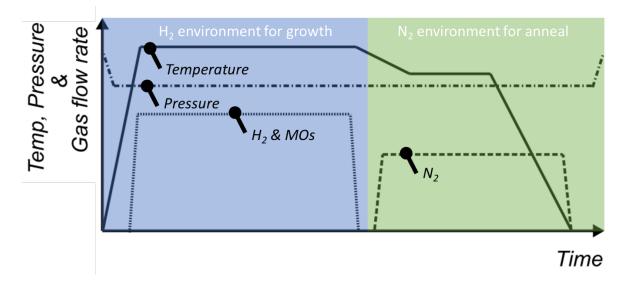

| 4.12 | Optimized MOCVD regrowth sequence with an in-situ $N_2$ anneal $\ldots$                                                                                                                                                            | 94     |

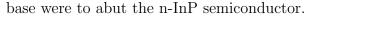

|      | Band alignment between the extrinsic/intrinsic base and the intrinsic emitter semiconductor (left), and that between the extrinsic and intrinsic bases                                                                             |        |

|      | $(right)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                         | 95     |

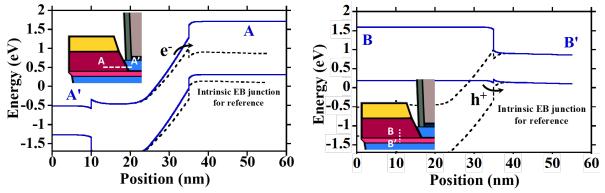

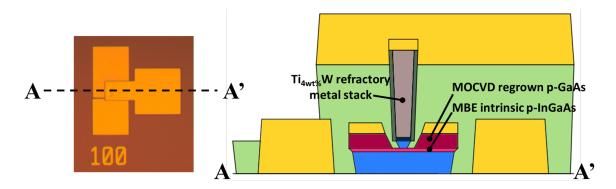

| 4.14 | Schematic cross section of a DC large area regrown extrinsic base HBT where "100" denotes $W_e = 100 \text{ nm} \dots \dots$ | 96     |

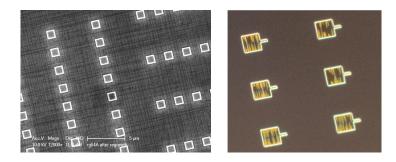

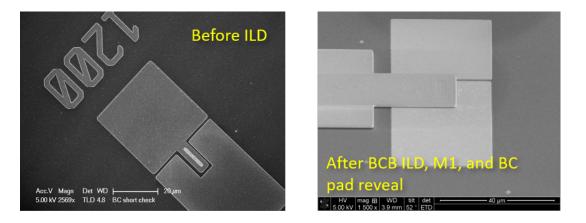

| 4.15 | A finished DC large area device with a $W_e = 1200$ nm emitter before BCB planarization (left), and after field BCB removal to reveal base & collector                                                                             |        |

|      | contact pads                                                                                                                                                                                                                       | 97     |

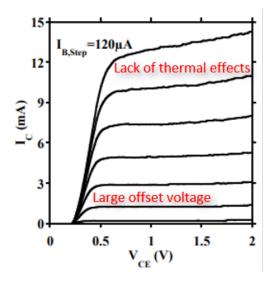

| 4 16 | Output characteristics of a typical DC large area device with unique feature                                                                                                                                                       |        |

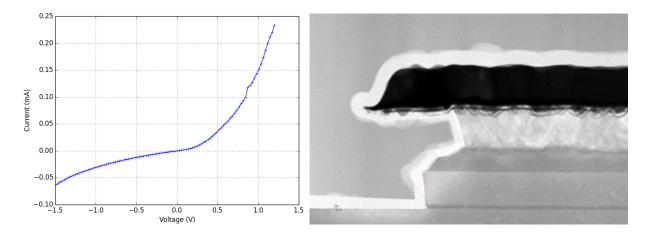

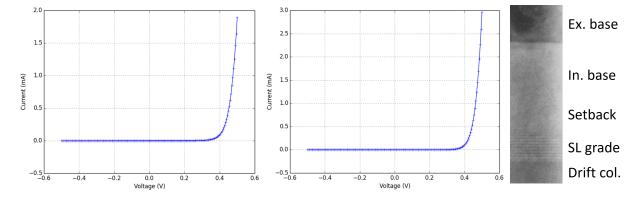

|      | Base-collector test diode characteristics of RG62B (left) and TEM cross                                                                                                                                                            | 99     |

| 4.18 | section of the diode structure                                                                                                                                                                                                     | 99     |

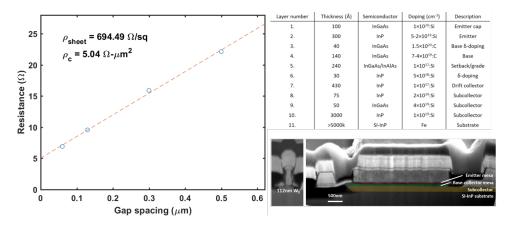

| 4 10 | good epitaxial quality throughout the extrinsic & intrinsic structure (right 5 $\Omega$ - $\mu$ m <sup>2</sup> base metal contact resistivity measured in a 90 nm EBL defined                                                      | 5) 100 |

| 4.19 | HBT                                                                                                                                                                                                                                | 101    |

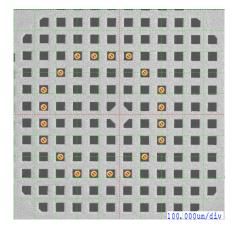

| 4 20 | AE (Absorbed Electron) mark grid in the JEOL EBL system                                                                                                                                                                            | 102    |

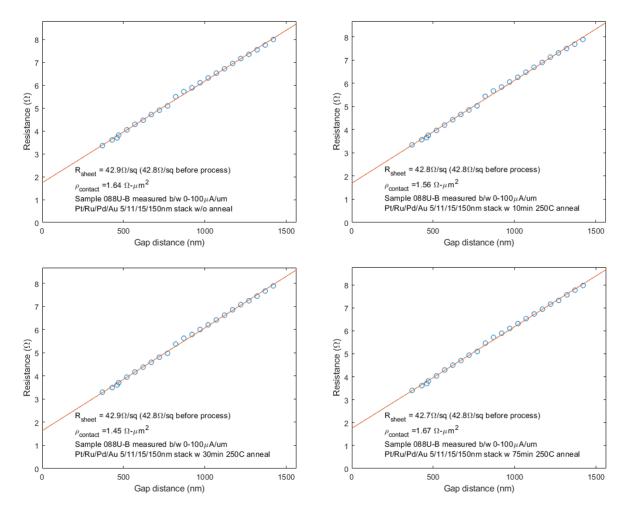

|      | TLM results of $Pt/Ru/Pd/Au$ contact to p-GaAsSb as deposited and an-                                                                                                                                                              | 102    |

|      | nealed at 250 °C for up to 75 minutes                                                                                                                                                                                              | 103    |

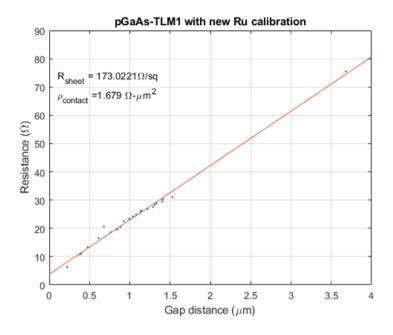

| 4.22 | TLM results of Pt/Ru/Pd/Au contact to p-GaAs annealed at 250 °C for                                                                                                                                                                |        |

|      | 75 minutes                                                                                                                                                                                                                         | 104    |

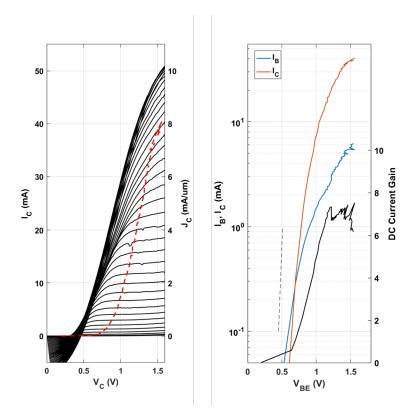

| 5.1  | Common-emitter output characteristics of RG62B (left), and spurious $% \left( {\left[ {{{\rm{A}}} \right]_{\rm{A}}} \right)_{\rm{A}}} \right)$                                                                                     |        |

|      | Gummel characteristics of RG62B (right)                                                                                                                                                                                            | 112    |

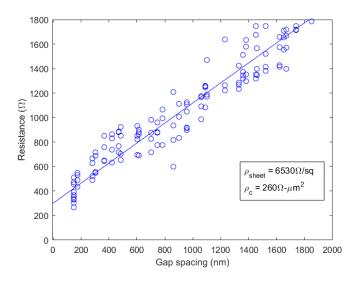

| 5.2  | Pinched TLM results of RG62B with large absolute resistance values as                                                                                                                                                              |        |

| - 0  | well as a large variance                                                                                                                                                                                                           | 113    |

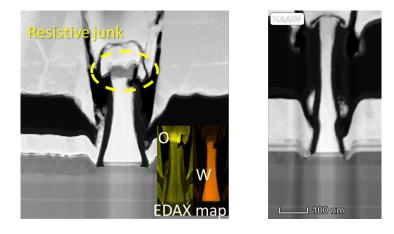

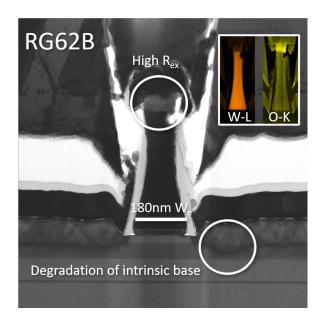

| 5.3  | TEM cross section of RG62B showing possible causes of the high $R_{ex}$ and $R_{bb}$                                                                                                                                               | 114    |

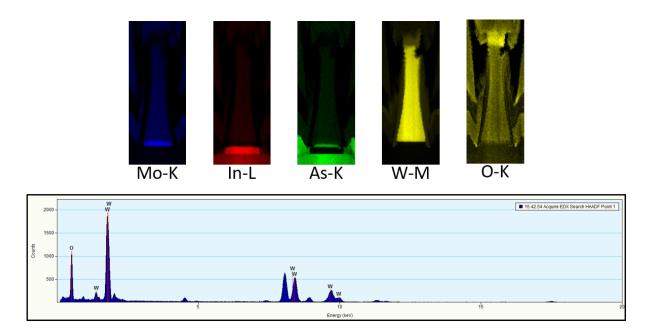

| 5.4  | EDS mapping of the emitter contact metal and semiconductor region (top),                                                                                                                                                           |        |

|      | and EDS quasi-quantitative analysis of the top of the emitter metal contact                                                                                                                                                        |        |

|      | showing a high oxygen peak (bottom)                                                                                                                                                                                                | 115    |

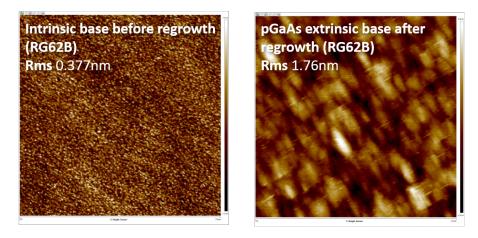

| 5.5  | Surface morphology before the RG62B regrowth process (left), and after                                                                                                                                                             |        |

|      | the RG62B regrowth process (right)                                                                                                                                                                                                 | 116    |

| 5.6 Abutment of regrown extrinsic base to intrinsic n-InP semiconductor ob-<br>served in RG62B, suggesting possible reduction in $R_{qap}$ as designed                                           | 116   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

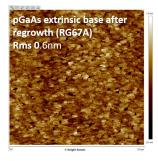

| 5.7 Improved surface morphology of regrown extrinsic base of device run RG67                                                                                                                     | A117  |

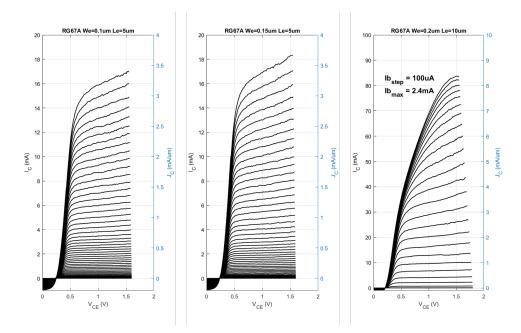

| 5.8 Common-emitter output characteristics of RG67A device run with 100 nm                                                                                                                        |       |

| (left), 150 nm (center), and 200 nm emitter width (right) $\ldots \ldots \ldots$                                                                                                                 | 117   |

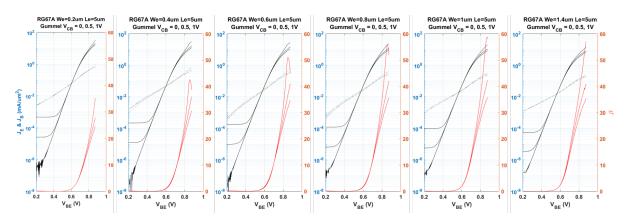

| 5.9 Gummel characteristics of devices of increasing emitter contact width in                                                                                                                     |       |

| RG67A                                                                                                                                                                                            | 118   |

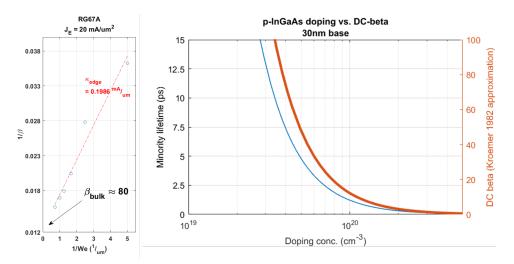

| 5.10 $1/\beta$ vs. $1/W_e$ of RG67A suggesting a $\beta_{bulk} = 80$ (left), and a corresponding $1-2 \times 10^{19}$ cm <sup>-3</sup> active dopant concentration in the intrinsic base (right) | 119   |

| 5.11 TLM resistance measurements of RG67A showing pinched intrinsic base                                                                                                                         |       |

| sheet and contact resistances (left), and unpinched extrinsic base sheet                                                                                                                         |       |

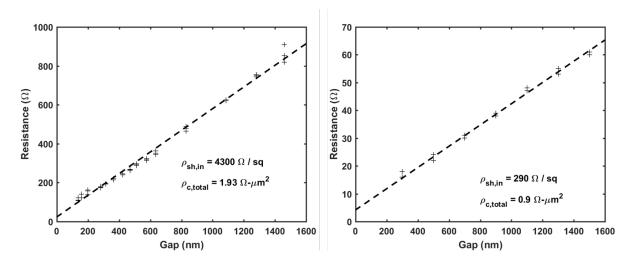

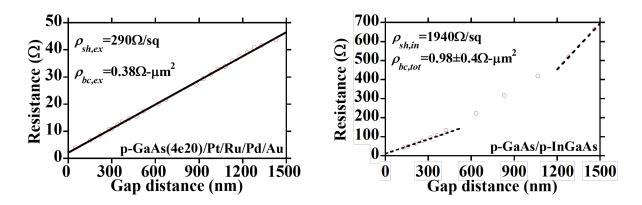

| and contact resistances (right)                                                                                                                                                                  | 120   |

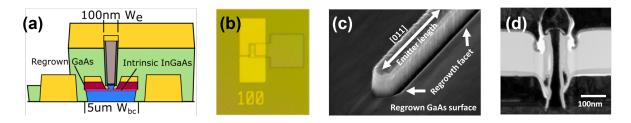

| 5.12 Schematic cross section of an 100 nm emitter width DC device in RG67D                                                                                                                       |       |

| (a), top view of an nominal 100 nm emitter width HBT (b), tilted SEM                                                                                                                             |       |

| view of the regrown p-GaAs extrinsic base surrounding the emitter metal                                                                                                                          |       |

| stack with (111) and (113) crystal facets (c), and TEM cross section of a                                                                                                                        | 101   |

| nominal 100 nm emitter width device $(d) \dots \dots \dots \dots \dots \dots \dots$                                                                                                              | 121   |

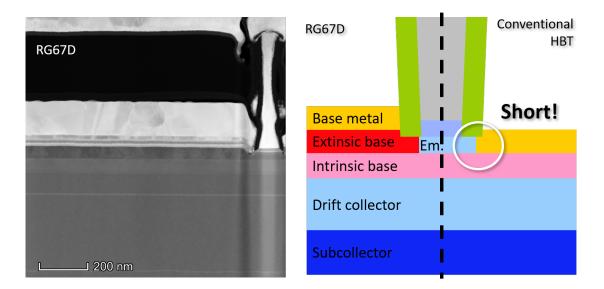

| 5.13 TEM cross sectional view of an 80 nm (100 nm nominal) device in RG67D                                                                                                                       |       |

| showing excellent regrown extrinsic base crystal quality as well as intrinsic device epi structure (left), and prevention of base-emitter junction shorts                                        |       |

| by abutment of extrinsic base regrowth (right)                                                                                                                                                   | 122   |

| 5.14 TLM resistance measurements of RG67D showing a low base metallization                                                                                                                       | 122   |

| resistance (left), and a non-linear TLM resistance vs. gap distance relation                                                                                                                     |       |

| indictive of incomplete intrinsic base dopant reactivation (right)                                                                                                                               | 123   |

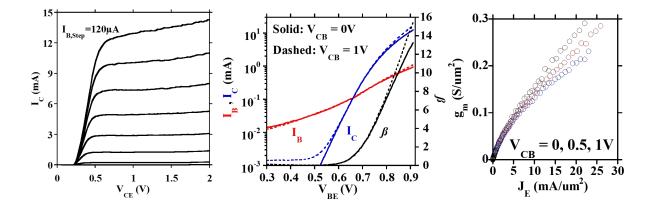

| 5.15 Common-emitter output characteristics of an 80 nm emitter width device                                                                                                                      |       |

| in RG67D (left), Gummel characteristics at different $V_{CB}$ (center), and                                                                                                                      |       |

| transconductance $g_m$ vs. $J_E$ (right)                                                                                                                                                         | 124   |

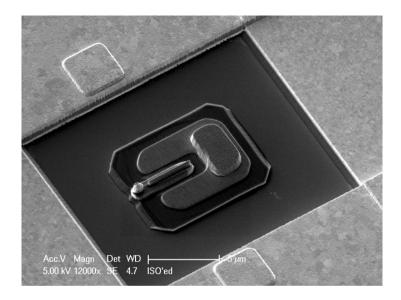

| 5.16 SEM image of a RG64RF-F HBT in TRL environment before BCB ILD                                                                                                                               |       |

| planarization                                                                                                                                                                                    | 125   |

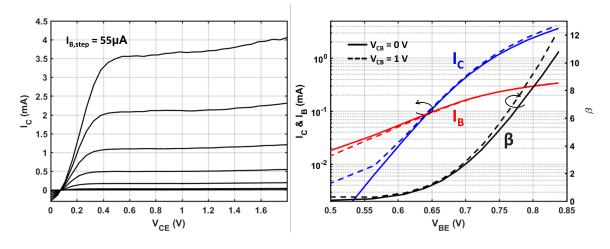

| 5.17 Common-emitter output and Gummel characteristics of a 300 nm emitter                                                                                                                        | 1.0.0 |

| contact width RF HBT in RG64RF-F                                                                                                                                                                 | 126   |

| 5.18 Low frequency extraction of $R_{ex} + R_{bb}/\beta$ with limited accuracy (left) due                                                                                                        | 100   |

| to strong collector Kirk and/or emitter starvation effects (right) 5 10 Maggunad small signal S parameters of a 0.2 × .2 ym² derives in BC64DE                                                   | 126   |

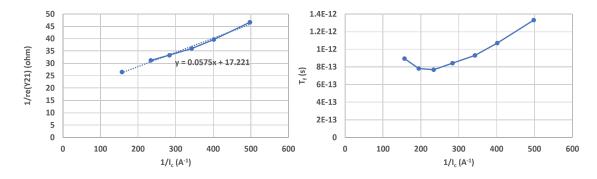

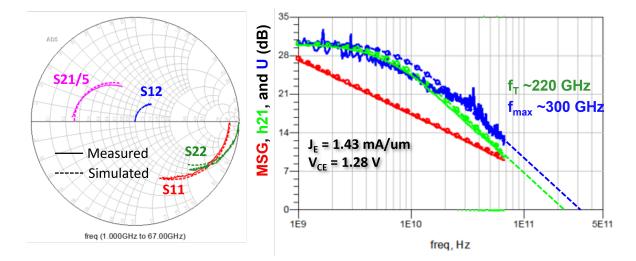

| 5.19 Measured small-signal S-parameters of a $0.3 \times 3 \ \mu\text{m}^2$ device in RG64RF-<br>F (left), and $h_{21}$ , $MSG$ , and U of the same device with 220/300 GHz                      |       |

| $f_T/f_{max}$ (right)                                                                                                                                                                            | 127   |

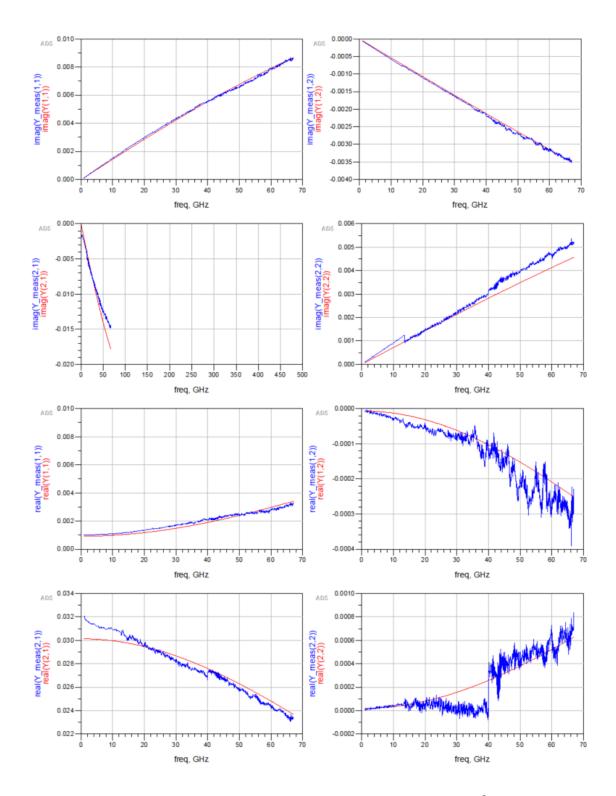

| 5.20 Y-parameter fitting between the measured $0.3 \times 3 \mu\text{m}^2$ device (blue) and                                                                                                     | 141   |

| the equivalent small-signal model (red)                                                                                                                                                          | 128   |

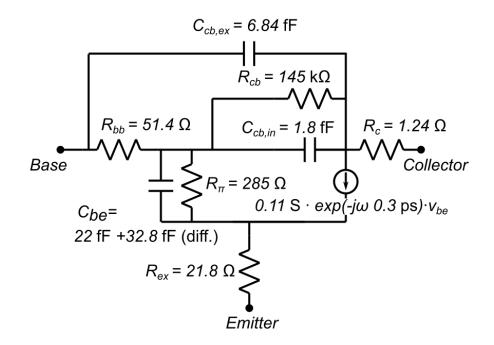

| 5.21 A hybrid- $\pi$ small-signal equivalent circuit for the HBT at peak $f_{max}$                                                                                                               | 129   |

|                                                                                                                                                                                                  |       |

| 6.1 Comparison between InGaAs and GaAsSb intrinsic base HBT                                                                                                                                      | 137   |

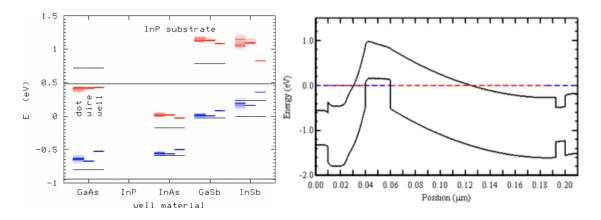

| 6.2 | Calculated band alignment of common III-V semiconductors strained to                         |     |

|-----|----------------------------------------------------------------------------------------------|-----|

|     | InP (left), and simulated intrinsic band alignment of the proposed InP/GaAs                  |     |

|     | /InP HBT (right)                                                                             | 138 |

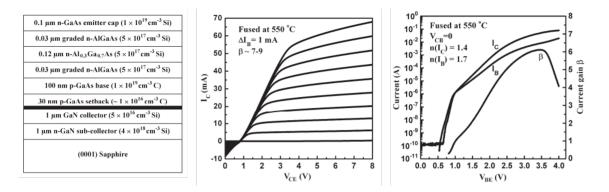

| 6.3 | Device layer structure of the fused AlGaAs/GaAs/GaN HBT, with the                            |     |

|     | fused interfaced highlighted (left), common-emitter I-V characteristics of                   |     |

|     | a 100 $\times$ 120 $\mu$ m <sup>2</sup> emitter mesa device, and the associated Gummel char- |     |

|     | acteristics (right)                                                                          | 139 |

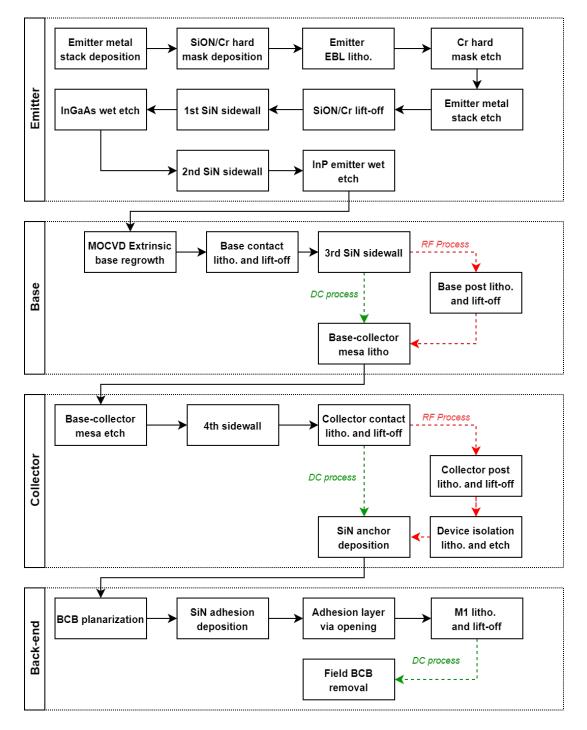

| A.1 | Process flow chart for DC and RF processes                                                   | 169 |

## List of Tables

| 1.1 | Calculated $Z_0$ of microstrip transmission lines in common materials with                       |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | reasonable aspect ratios                                                                         | 9  |

| 1.2 | $P_{sat-50\Omega}$ of 3 generations of InP HBT vs. competing RF technologies                     | 10 |

| 1.3 | $f_{50\Omega}$ of 3 generations of InP HBT vs. competing RF technologies                         | 14 |

| 1.4 | Mismatch between optimal power matching $Z_{OPT}$ and maximum power                              |    |

|     | gain $Z_{conj}$ calculated for various technologies                                              | 18 |

| 1.5 | $f_{max}$ of small-signal operation vs. $f_{power,1}$ and $f_{power,2}$ calculated for $Z_{OPT}$ |    |

|     | matching condition for various technologies                                                      | 21 |

| 2.1 | Conventional InP HBT scaling roadmap with issues discussed in text $\therefore$                  | 45 |

| 2.2 | Design of DHBT64 with a base contact layer compared to old HBT64 $\ldots$                        | 47 |

| 2.3 | Design of DHBT67 with a 30 nm thick p-InGaAs base                                                | 48 |

| 2.4 | Design of DHBT90-Sb with a 20 nm thick p-GaAsSb base $\ldots$                                    | 49 |

| 3.1 | Simulated $R_{bb}$ in a 130 nm technology with a 200 $\Omega/\Box$ extrinsic base                | 75 |

## Chapter 1

## Introduction

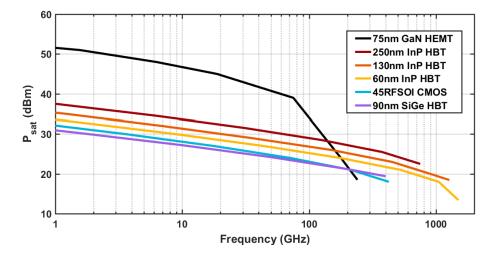

This chapter reviews current transistor technologies in both Si and III-V material systems, and state-of-the-art RF amplifier circuits at 28-39 GHz and > 100 GHz. Despite progress in device current gain cut-off frequency  $f_T$  and maximum power gain cut-off frequency  $f_{max}$ , circuit-level performance gains, in terms of saturated output power  $P_{sat}$  and poweradded efficiency PAE, have so far eluded requirements for widespread commercialization – e.g.  $P_{sat} > 30$  dBm, and  $PAE_{6dB-backoff} > 30\%$  for power-constrained user equipment. An analysis of  $f_T$ ,  $f_{max}$ , and Johnson's figure of merit JFOM reveals their limited suitability at guiding device scaling for RF applications. A new pair of parameters  $f_{50\Omega}$ and  $P_{sat-50\Omega}$  are proposed to better assess a technology's RF potential within a given frequency band, and help guide further device optimization.

### **1.1** Transistor Technologies for RF Power Amplifiers

Indium phosphide heterojunction bipolar transistors achieve higher  $f_T/f_{max}$  than other transistor technologies at a given lithographic feature size. Current state-of-the-art 130 nm InP HBT exhibits  $f_T/f_{max}$  in excess of 0.52/1.1 THz [1]. Current record high *PAE*  and  $P_{sat}$  RF power amplifiers above 100 GHz are all demonstrated in a 250 nm InP process [2, 3, 4]. Yet, InP HBT has seen little widespread commercialization apart from niche applications in defense and test instrumentation [5, 6], and certainly not in commercial RF communication. The lack of commercial InP processes might be attributed to the higher cost compared to their GaAs counterparts [7]. From a performance perspective, however, for sub-10 GHz RF PA, the mature 250 nm 350/700 GHz  $f_T/f_{max}$  InP HBT provides a similar maximum stable gain  $MSG \sim 30$  dB and a less than half normalized saturated power density  $\frac{P_{sat}}{L_E} \sim 1.5$  mW/ $\mu$ m compared to a 50/175 GHz  $f_T/f_{max}$  GaAs HBT from the 1980s [2, 8]. While  $f_T/f_{max}$  do provide the upper limit at which power amplification is possible,  $f_T/f_{max}$  alone are inadequate in predicting RF power amplifier performance in a given technology.

Figure 1.1: RF PA  $P_{sat}$  (left), and peak PAE (right) vs. frequency in various processes [9]

Si CMOS, Si LDMOS, SiGe HBT, GaAs HBT, GaAs HEMT, and more recently GaN HEMT with lower  $f_T/f_{max}$  have dominated the commercial sub-10 GHz RF PA arena both in terms of  $P_{sat}$  and peak PAE (Fig. 1.1) [9]. A widely accepted parameter that evaluates the promise of a transistor technology for RF power amplification – Johnson's figure of merit JFOM – is the product of the charge carrier saturation velocity  $v_{sat}$ in a semiconductor and the dielectric strength  $E_{breakdown}$  under same applied bias [10]. Equivalently, JFOM is  $f_T \times BV$ , where BV is the breakdown voltage of the transistor. Fig. 1.2 (left) shows BV vs.  $f_T$  for the aforementioned transistors [12]. Despite a high

Figure 1.2: *BV* vs.  $f_T$  with *JFOM* asymptotes (left) [11];  $P_{sat}$  vs. frequency > 100 GHz (right) [9]

JFOM and sufficient  $f_T/f_{max}$ , GaN HEMT does not currently offer superior saturated output power  $P_{sat}$  or power added efficiency PAE between 100 - 300 GHz (Fig. 1.1 & 1.2). Other factors such as electromagnetic limits on realizable cell sizes, optimal power matching impedance  $Z_{OPT}$ , maximum power gain impedance  $Z_{conj}$ , and availability of efficient power combining should be considered for RF power amplifier applications where  $P_{sat}$  and PAE are of chief concern.

## **1.2** $f_T \& f_{max}$ Scaling, JFOM, and $P_{sat-50\Omega}$

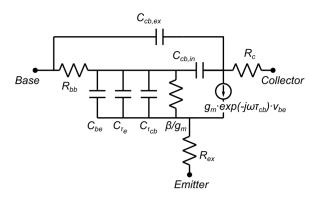

Figure 1.3: Basic hybrid- $\pi$  small-signal model of an HBT

A bipolar junction transistor<sup>i</sup> represented by the hybrid- $\pi$  model in Fig. 1.3 has a high frequency short-circuit current gain  $h_{21}$  as followed, assuming  $R_{\pi} \gg \frac{1}{i\omega C_{\pi}}$

$$h_{21} = \frac{i_{out}}{i_{in}} \approx \frac{g_m - j\omega C_{cb}}{j\omega (C_\pi + C_{cb})} \tag{1.1}$$

Current gain cut-off frequency  $f_T$  is defined as the frequency at which  $|h_{21}| = 1$ . Thus, when  $\omega \gg g_m/C_{cb}$ , we have

$$f_T = \frac{g_m}{2\pi (C_\pi + C_{cb})}$$

(1.2)

Using  $g_m = \beta/R_{\pi}$  where  $\beta$  is the DC current, and because  $g_m$  is proportional to the slope of the exponential emitter-base I-V characteristics, we have

$$\frac{1}{2\pi f_T} = \frac{1}{g_m} (C_{je} + C_{cb} + C_{b,t} + C_{b,\Delta Q_c}) = \frac{1}{g_m} (C_{je} + C_{cb}) + \frac{1}{g_m} (C_{b,t} + C_{b,\Delta Q_c})$$

(1.3)

$$= \underbrace{\frac{1}{g_m}(C_{je} + C_{cb})}_{g_m} + \underbrace{\frac{1}{\beta}(\tau_b + \tau_C)}_{g_m}$$

(1.4)

$$\propto$$

junction areas  $\propto$  electron transit times

where  $C_{je}$  and  $C_{cb}$  are the junction capacitances of the emitter-base and base-collector junctions.  $C_{b,t}$  and  $C_{b,\Delta Q_c}$  are differential capacitances due to charging of electrons in the base (charge control) terminal.  $\tau_b$  and  $\tau_c$  are the base and collector electron transit

<sup>&</sup>lt;sup>i</sup>or a MOSFET, or any charge control transistor device

times.  $f_T$  scales with smaller junction areas and thinner device structure for faster electron transit times. In an HBT, these correspond to lateral lithographic scaling, and vertical epi scaling as detailed in [13].

Therefore, a 2:1 increase in  $f_T$  leads to a constant maximum current per emitter length  $I_{max}$  (mA/ $\mu$ m), and a 1:2 scaling in maximum voltage  $V_{max}$  (V) due to a 1:2 scaling in the collector thickness.<sup>ii</sup> On a per emitter length basis, this corresponds to a 1:2 scaling in loadline impedance, and a 1:2 scaling in output power. To maintain a constant optimal power matching  $Z_{OPT}$  for a PA power cell, the emitter finger length must be scaled by 1:2, for a 1:4 scaling in  $P_{sat}$ .

### **Corollary 1:** Higher $f_T$ leads to *smaller* PA cell sizing for a given $Z_{OPT}$

The power gain cut-off frequency  $f_{max}$  is defined as the frequency at which the transistor has unity power gain. A transistor modeled by a single-pole system shows a -6 dB/octave roll-off in its Mason's unilateral power gain up to  $f_{max}$  [16]. In reality, transistors are not single-pole systems and have "non-dominant" poles and often zeros at high frequencies [17, 18]. Consider again the single-pole transistor model in Fig. 1.3 represented by its Z-parameters

$$Z = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} = Z_S + Z_A$$

(1.5)

where  $Z_{21}$  may or may not be equal to  $Z_{12}$ . The matrix can be separated into a symmetric part  $Z_S$  where  $Z_{S,ij} = Z_{S,ji}$  for  $i \neq j$ , and an associated antisymmetric part where  $Z_A$ where  $Z_{A,ij} \neq Z_{A,ji}$  for  $i \neq j$ . It can be shown that any lossless passive (reciprocal) embedding N around Z can only perform one or a combination of the following elemental

<sup>&</sup>lt;sup>ii</sup>This is a pessimistic position because it ignores velocity overshoot effects in highly scaled devices. Measured  $V_{max}$  in modern bipolar and FET devices scales sublinearly with regard to  $f_T$  [13, 14, 15].

Real transformation:

$$Z' = n Z n^T$$

(1.6a)

Reactive padding:

$$Z' = Z + j\chi$$

(1.6b)

Inversion:

$$Z' = Z^{-1}$$

(1.6c)

where n in Eq. 1.6a is the real transformation matrix. n can be, for instance, constructed with quarter-wavelength transmission lines for impedance transformation. One important n is the permutation matrix  $n_{perm}$

$$n_{perm} = \begin{bmatrix} 1 & -1 \\ 0 & -1 \end{bmatrix}$$

(1.7)

which rotates the original Z matrix to obtain Z' (Fig. 1.4). From a circuit perspective,  $n_{perm}$  links the common-emitter, common-base, and common-collector configurations.

Figure 1.4:  $Z' = n_{perm} Z n_{perm}^T$  rotates the three terminals counter-clockwise

$\chi$  in Eq. 1.6b is the *passive* reactance padding matrix with  $\chi_{ij} = \chi_{ji}$ . Therefore, for any Z, one has

$$(Z + j\chi) + \overline{(Z + j\chi)} = Z + \overline{Z} = \text{invariant w.r.t. Eq. 1.6b}$$

(1.8)

$$(Z + j\chi) - (Z + j\chi)^T = Z - Z^T = \text{invariant w.r.t. Eq. 1.6b}$$

(1.9)

Equivalently, padding a transistor with ideal lossless reactive embedding will not change its  $Z + \overline{Z}$  or  $Z - Z^T$ . Note, however, that  $Z + \overline{Z}$ , and  $Z - Z^T$  are not the original Z, and, thus, do *not* represent the original device as included reactances of the original device cannot be inferred from either expression. Any expression also stays invariant with regard to Eq. 1.6a must be of the form  $f[(Z + \overline{Z}), (Z - Z^T)]$ . One such matrix found by Mason was  $\Delta[Z - Z^T]/\Delta[Z + \overline{Z}]$  because

$$\Delta[(n(Z - Z^T)n^T)(n(Z + \overline{Z})n^T)^{-1}] = \Delta[n] \cdot \Delta[Z - Z^T] \cdot \Delta[(Z + \overline{Z})^{-1}] \cdot \Delta[n^{-1}] = \Delta[Z - Z^T] \cdot \Delta[Z + \overline{Z}]^{-1} = \text{invariant w.r.t. Eq. 1.6a, 1.6b}$$

(1.10)

Finally, because  $\{\Delta[Z - Z^T]/\Delta[Z + \overline{Z}]\}^{-1} = -\Delta[Z - Z^T]/\Delta[Z + \overline{Z}]$ , we arrive at the Mason's unilateral gain U

$$U = \frac{\left|\Delta(Z - Z^T)\right|}{\Delta(Z + \overline{Z})} = \text{invariant w.r.t. Eq. 1.6a, 1.6b, 1.6c}$$

(1.11)

$$\Gamma_{S} = S_{11}^{*}$$

$$Lossless Embedding$$

$$\Gamma_{L} = S_{22}^{*}$$

$$Z_{L} = Z_{conj} = Z_{0} \left[\frac{1 + \Gamma_{L}}{1 - \Gamma_{L}}\right]$$

Figure 1.5: Maximum power gain matching for U that requires  $Z_{conj}$  load matching

Physically, U can be achieved by methodically embeddeding a transistor in one configuration (CE for example) with lossless matching networks, rotating it to other configurations and matching again to get an overall real  $Z_{overall}$  before transforming it to the 50  $\Omega$  environment with quarter-wave transformers.  $f_{max}$  is derived at the frequency where U = 1. Therefore, a high  $f_{max}$  does not guarantee a high power gain as the required

Figure 1.6: A  $2 \times f_T$  shifts loadline A to B for a 1:4  $P_{sat}$  (Corollary 1), and the mismatch between loadlines B and C & C' due to mismatch between  $Z_{conj}$  and  $Z_{OPT}$  (Corollary 2)

$Z_{conj}$  could be rather complex, and may or may not overlap with  $Z_{OPT}$  (Fig. 1.5). The power gain under optimal load matching  $Z_{OPT}$  is the operating gain  $G_P$  and is usually less than or equal to U extrapolated from  $f_{max}$ .<sup>iii</sup> Therefore, we have

**Corollary 2:** Gain extrapolated from  $f_{max}$  corresponds to  $Z_{conj}$ , not necessarily  $Z_{OPT}$ When  $G_P$  is less than U due to the mismatch between  $Z_{conj}$  and  $Z_{OPT}$ ,  $PAE \propto \frac{1}{1-G_P}$  is less than that suggested by U extrapolated from  $f_{max}$ . Loadline C in Fig. 1.6 corresponds to  $Z_{conj} < Z_{OPT}$ , where the transistor is *current-limited*. A current-limited transistor would benefit from an increase in  $I_{max}$  if  $V_{max}$  can be kept constant. On the other hand, loadline C' corresponds to  $Z_{conj} > Z_{OPT}$ , where the transistor is *voltage-limited*. A voltage-limited transistor would benefit from an increase in  $V_{max}$  if  $I_{max}$  can be kept constant. In Section 1.5, it will be shown that whether a transistor is current- or voltagelimited is independent of its finger-length and  $Z_{OPT}$ .

Because the feasible load impedance realizable on wafe is constrained, loadlines A & B in Fig. 1.6 cannot be of arbitrary impedance. Calculated characteristic impedance  $Z_0$

<sup>&</sup>lt;sup>iii</sup>In general,  $G_P \leq G_{max} = (2U-1) + 2\sqrt{\frac{U}{U-1}} \approx 4U$  at a frequency well below  $f_{max}$  [19]. But  $G_{max}$  approaches unity at  $f_{max}$  as well.

of a microstrip transmission line embedded in various materials and of common aspect ratios is tabulated in Table 1.1 [20]. For ILDs on the order of a few  $\mu$ m, reasonable  $Z_0$  is between 20  $\Omega$  and 150  $\Omega$ , with a geometric mean very close to the 50  $\Omega$  standard impedance.

|                 | Aspect ratio $(w/h)$ |     |    |    |    |    |    |  |

|-----------------|----------------------|-----|----|----|----|----|----|--|

|                 |                      | 0.1 | 1  | 2  | 3  | 5  | 10 |  |

|                 | 2.2 (PTFE)           | 204 | 95 | 66 | 51 | 36 | 20 |  |

|                 | 2.6 (BCB)            | 192 | 89 | 61 | 48 | 33 | 19 |  |

|                 | 4 (SiO)              | 162 | 74 | 51 | 39 | 27 | 15 |  |

| $\varepsilon_r$ | 8.9 (GaN)            | 114 | 51 | 35 | 27 | 18 | 10 |  |

|                 | 11.7 (Si)            | 101 | 45 | 31 | 24 | 16 | 9  |  |

|                 | 12.5 (InP)           | 98  | 44 | 30 | 23 | 16 | 9  |  |

|                 | 12.9 (GaAs)          | 96  | 43 | 30 | 23 | 16 | 9  |  |

|                 | $Z_0 (\Omega)$       |     |    |    |    |    |    |  |

Table 1.1: Calculated  $Z_0$  of microstrip transmission lines in common materials with reasonable aspect ratios

Loadline impedances of power cells in RF PAs operating close to or above 100 GHz in different transistor technologies are within the 20-150  $\Omega$  range readily realizable on wafer, with III-V & nitride FETs closer to the high end, while HBTs and CMOS closer to 50  $\Omega$  [2, 3, 4, 21, 22, 23, 24]. With a typical 50  $\mu$ m substrate and a low  $g_m$  forbidding the use of ILDs, III-V & nitride FETs' closer to 100  $\Omega$  loadline impedance matches the calculated values in Table 1.1.

The combined effect of Collorary 1 & Collorary 2 and realizable  $Z_0 \approx 50 \ \Omega$ , therefore, determines cell sizing in an RF PA. Cell sizing is *not* a free variable in RF PA design. In an RF PA, a 2:1 scaling in  $f_T$  implies a 1:2 scaling in PA cell size, reducing  $P_{sat}$  of the power cell. Here  $P_{sat-50\Omega}$  is defined as the saturated output power of a PA cell with a sizing that matches 50 $\Omega$ .  $P_{sat-50\Omega}$  of 3 generations of InP HBT [1, 13, 25], record GaN HEMT [26], Globalfoundries 45RFSOI [27], and IBM 90nm SiGe HBT [28] are given in Table 1.2. Although a large  $V_{max}$  leads to higher  $P_{sat-50\Omega}$  in a 50  $\Omega$  PA cell as suggested

| Technology                     | 250  nm      | 130 nm       | $60 \text{ nm}^*$ | 75  nm           | 45RFSOI | 90nm     |

|--------------------------------|--------------|--------------|-------------------|------------------|---------|----------|

| Technology                     | InP HBT      | InP HBT      | InP HBT           | GaN HEMT         | CMOS    | SiGe HBT |

| $I_{max} (mA/\mu m)$           | 3            | 3            | 3                 | 1.6              | 0.65    | 3        |

| $V_{max}$ (V)                  | 4.2          | 3.5          | 2.5               | 40               | 2.4     | 1.8      |

| $V_{knee}$ (V)                 | 0.6          | 0.6          | 0.5               | 1                | 0.3     | 0.2      |

| $P_{sat-1\mu m} (mW)$          | 1.4          | 1.1          | 0.8               | 7.8              | 0.17    | 0.6      |

| $Z_{L-1\mu\mathrm{m}}(\Omega)$ | 1200         | 970          | 700               | 24300            | 3200    | 550      |

| 50 Ω cell size (n×L- $\mu$ m)  | $4 \times 6$ | $4 \times 5$ | $4 \times 3.5$    | $13 \times 37.5$ | 64×1    | 11×1     |

| $P_{sat-50\Omega}$ (dBm)       | 15.1         | 13.4         | 10.2              | 35.8             | 10.4    | 8.2      |

\*: Extrapolated

Table 1.2:  $P_{sat-50\Omega}$  of 3 generations of InP HBT vs. competing RF technologies

by JFOM, the transistor size required in such PA cell could be a concern due to its ratio to the electrical length the associated RC delay [29].

In section 1.3, a second parameter,  $f_{50\Omega}$ , related to  $P_{sat-50\Omega}$  is introduced in an attempt to explain the observed dominance of PA in InP HBT at > 100 GHz.

## **1.3** $f_{50\Omega}$ – Lumped or Distributed Element?

Figure 1.7: Schematic of a CMOS PA cell with only output wiring shown for clarity

A power cell in an RF PA is treated as a lumped element in elementary analysis. Because interconnect wiring between parallel devices is of variable length, the impedance presented to each transistor finger  $Z_{L,transistor}$  is not identical. To maintain a consistent overall  $Z_L$  and  $Z_{L,transistor}$  the interconnect needs to be much shorter than a wavelength [30]. Therefore, maximum cell width is limited by the phase and impedance differences between the outer and inner transistors in 1.7. For efficient power delivery > 90%, amplitude sum of the outer and inner transistors  $exp(-j\frac{\phi_{mismatch}}{2}) + exp(j\frac{\phi_{mismatch}}{2})$  should be > 95%, leading to a maximum electrical length of  $1/10 \lambda$  for  $\frac{1}{2}W_{cell}$ . Depending on design tradeoffs,  $W_{cell}$  can be adjusted for a higher  $P_{sat}$  at the expense of a lower PAE. Fig. 1.8 shows the drop in power delivery efficiency of a 4-transistor cell shown in the previous schematic as a function of  $W_{cell}$  due to phase mismatch. For the purpose of guiding device optimization,  $P_{sat}$  vs. PAE tradeoff is not considered, and a fixed  $W_{cell} = 1/5\lambda$  is used for analysis. Therefore,  $W_{cell} \propto 1/f$ .

Figure 1.8: Tradeoff between power delivery efficiency vs. power cell width  $W_{cell}$  due to phase mismatch

Similarly, transistor finger length  $W_G$  is ultimately limited by the electrical length of electromagnetic waves in materials. Therefore,  $W_G \propto 1/f$ , and is limited to  $1/10\lambda$  for the

analysis. One subtlety exists for transistors with high feed resistance – e.g. poly-gated Si CMOS with gate sheet resistance on the order of 10  $\Omega/_{\Box}$  [31]– where distributed RC delay along the finger length dominates. Because  $R \propto W_G$  and  $C \propto W_G$ ,  $W_G \propto 1/\sqrt{f}$  in transistors with a high feed resistance. Given that

$$I_{cell,max} \propto W_G \times W_{cell} \tag{1.12}$$

$$P_{sat} = \frac{1}{8} I_{cell,max}^2 Z_{OPT} \tag{1.13}$$

$$Z_{OPT} = 50\,\Omega\tag{1.14}$$

we have  $P_{sat-50\Omega}(f) \propto 1/f^4$  in general, and  $P_{sat-50\Omega}(f) \propto 1/f^3$  for high feed resistance transistors as shown in Fig. 1.9.

Figure 1.9:  $P_{sat-50\Omega}$  as a function of frequency for high feed resistance transistors (Si CMOS), and low feed resistance transistors (III-Vs)

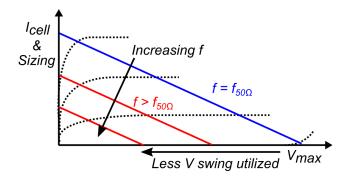

Since  $P_{sat-50\Omega}(f)$  is a function of the PA operating frequency, maximum  $P_{sat-50\Omega}$  defined in previous section corresponds to a characteristic frequency,  $f_{50\Omega}$ , defined as the frequency at which full voltage swing of the transistor is utilized. At frequency greater than  $f_{50\Omega}$ , the PA power cell is current-limited, and cannot access its full voltage supporting capability as shown in Fig. 1.10.

$f_{50\Omega}$  of transistors found in Table 1.2 are calculated by first finding the minimum spacing between transistor fingers due to thermal and resistive effects [32, 33, 34], and

Figure 1.10:  $I_{cell}$  decreases in proportion to cell sizing with constant  $I_{max}$  at frequency above  $f_{50\Omega}$ , whereas  $V_{cell}$  becomes less than transistor  $V_{max}$

then balancing  $W_G$  and  $W_{cell}$  to fit into a  $1/10\lambda \times 1/5\lambda$  area. Finally,  $f_{50\Omega} = \frac{c_0}{\lambda\sqrt{\varepsilon_r}}$ . Effective dielectric constant for microstrip transmission line on GaN is assumed to be 6.0, 2.6 for transmission line in BCB on InP [20], and 3.8 for transmission line in SiO<sub>x</sub> on Si. The results are given in Table 1.3.

With the exception of GaN HEMT, all other transistor technologies have  $f_{50\Omega}$  in excess of their  $f_T/f_{max}$ . In other words, InP HBT, 45RFSOI, and SiGe HBT are voltagelimited and would benefit from a higher breakdown voltage if possible. GaN HEMT, on the other hand, is current-limited even for the record 75 nm devices above 75 GHz. To operate above 100 GHz, mature and larger node GaN HEMT processes must give up their higher breakdown voltage for a realizable loadline matching. The lack of high  $P_{sat}$ GaN HEMT PA above 100 GHz compared to InP HBT PA seen in Fig. 1.2 is, thus, explained.

In this section, it has been shown that by taking into account electromagnetic phenomena, GaN HEMT's higher *JFOM* and breakdown voltage are not fully exploitable at > 100 GHz because of its low  $f_{50\Omega}$  for realizable loadline matching. Compared to 45RFSOI, 90 nm SiGe HBT, and its smaller node counterparts, 250 nm InP HBT is less voltage-limited, and is more suitable for > 100 GHz PA applications. The first utility of  $f_{50\Omega}$  is that it provides a quantitative measure for guiding both technology selection for

| Technology               | 250  nm         | 130  nm         | $60 \text{ nm}^*$ | 75  nm          | 45RFSOI   | 90nm      |

|--------------------------|-----------------|-----------------|-------------------|-----------------|-----------|-----------|

|                          | InP HBT         | InP HBT         | InP HBT           | GaN HEMT        | CMOS      | SiGe HBT  |

| $P_{sat-50\Omega}$ (dBm) | 16.5            | 14              | 12                | 36              | 12        | 9.2       |

| Finger pitch $(\mu m)$   | 6               | 5               | 4.5               | 25              | 0.5       | 1         |

| $f_{50\Omega}$ (GHz)     | 1500            | 1800            | 2100              | 75              | 850       | 2400      |

| Frequency<br>Dependence  | $1/f^{4\sim 3}$ | $1/f^{4\sim 3}$ | $1/f^{4\sim 3}$   | $1/f^{4\sim 3}$ | $1/f^{3}$ | $1/f^{3}$ |

\*: Extrapolated

Table 1.3:  $f_{50\Omega}$  of 3 generations of InP HBT vs. competing RF technologies

PA design at a given frequency, and a direction device scaling should take to optimize for PA applications. In section 1.4, relation between  $f_{50\Omega}$  and limit of efficient power combining using corporate power combiners are discussed.

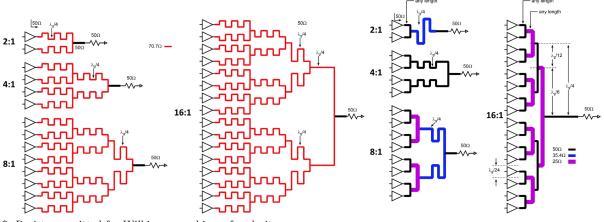

### 1.4 Relation between Power Combining and $f_{50\Omega}$

\*: Resistors omitted for Wilkinson combiners for clarity

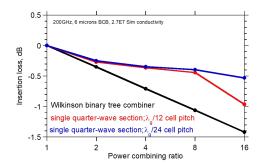

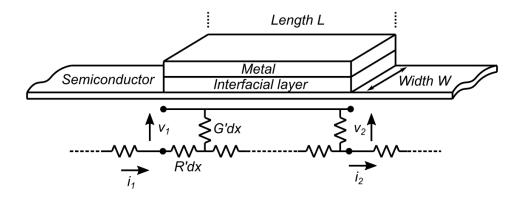

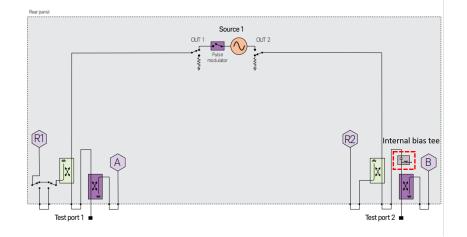

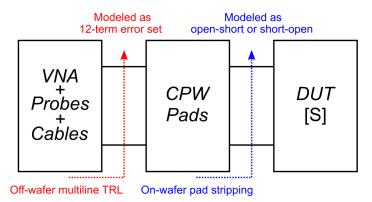

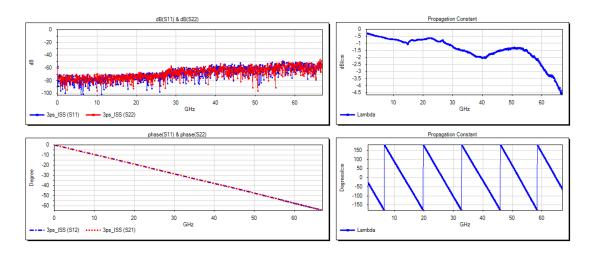

Figure 1.11: Conventional Wilkinson N-way power combiners using  $log_2(N)$  sections of  $\lambda/4$  transmission line (left) vs. single-section  $\lambda/4$  transmission line N-way corporate power combiners (right)