# Lawrence Berkeley National Laboratory

**LBL Publications**

# Title

An automated and portable method for selecting an optimal GPU frequency

# Permalink

https://escholarship.org/uc/item/3cz016cf

# Authors

Ali, Ghazanfar Side, Mert Bhalachandra, Sridutt <u>et al.</u>

# **Publication Date**

2023-12-01

# DOI

10.1016/j.future.2023.07.011

# **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <u>https://creativecommons.org/licenses/by/4.0/</u>

Peer reviewed

# An Automated and Portable Method for Selecting an Optimal GPU Frequency

Ghazanfar Ali<sup>a</sup>, Mert Side<sup>a</sup>, Sridutt Bhalachandra<sup>b</sup>, Nicholas J. Wright<sup>b</sup>, Yong Chen<sup>a</sup>

<sup>a</sup>Texas Tech University, 2500 Broadway, Lubbock, 79409, TX, USA <sup>b</sup>Lawrence Berkeley National Laboratory, 1 Cyclotron Rd, Berkeley, 94720, CA, USA

### Abstract

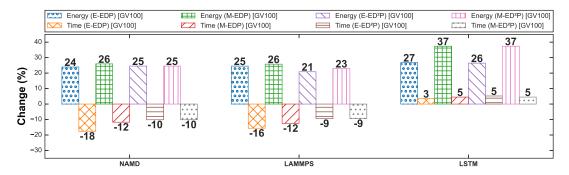

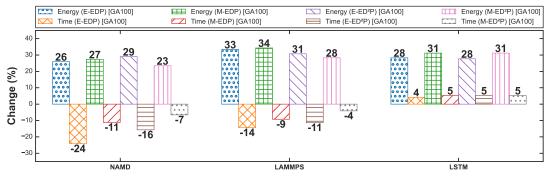

Power consumption poses a significant challenge in current and emerging graphics processing unit (GPU) enabled high-performance computing systems. In modern GPUs, dynamic voltage frequency scaling (DVFS) appears to be a reliable control to regulate power consumption and performance. However, the DVFS design space is large - hence, brute-force approaches are infeasible to select the optimal frequency. Furthermore, no single frequency can be universally optimal for applications with varying computational intensities. Thus, the application's complexity and the availability of a wide range of frequency settings are a challenge in selecting the optimal frequency configuration for a given GPU workload. To that end, this paper proposes a systematic approach that consists of three steps. The feature characterization study identifies the fine-grain GPU utilization metrics that influence the power consumption and execution time of a given workload. To understand the performance, power, and energy consumption behaviors of a workload across GPU's DVFS design space, we derived analytical power and performance models using the identified fine-grain features. It is shown that the same set of GPU utilization metrics can estimate both the power consumption and execution time while being agnostic of changes to frequency and input sizes. Applying a power control with the single objective of reducing power may cause performance degradation, leading to more energy consumption. A multi-objective approach is proposed to select the optimal GPU DVFS configuration for a workload that reduces power consumption with negligible degradation in performance. The evaluation was conducted using SPEC ACCEL benchmarks and three real applications - NAMD LAMMPS, and LSTM on NVIDIA GV100, GA100, and AMD MI210 GPUs. On average, real applications showed 29.6% energy savings with a performance loss of 5.2% on GA100 and 22.6% energy savings with a performance loss of 4.7% on GV100. Moreover, the proposed models are portable to real applications, GPU architectures, and vendors, and require metric collection at only the default frequency rather than all supported DVFS configurations. Additionally, we conducted a comparison between our models and the GPU assembly instructions (PTX)-based static models. The results revealed a significant reduction in the average error rates, with a decrease from 19.7% to 3.1% for power models and from 29.4% to 5.2% for performance models.

*Keywords:* GPU frequency selection, DVFS, GPU power modeling, GPU performance modeling, energy delay product, multi-objective function, energy efficiency

#### 1. Introduction

In the new era of post-Moore's law, GPUs are likely to be crucial in accelerating computing capacity for current and future high-performance computing (HPC) systems. While GPUs are performant, they increasingly consume a significant amount of power. For example, today, a single advanced GPU consumes power up to 500 W [1] which is close to a traditional HPC node [2]. As such, the power consumption of HPC systems built with GPUs is limited by power. An exascale system built with current generation GPUs expects to consume more than the desired 20 MW power budget [3] (e.g., the Frontier [4]), even without considering the infrastructure and cooling overheads. Furthermore, HPC data centers have been more concerned about performance historically; however, in more recent times due to the "dark silicon" phenomenon [5], there has been a paradigm shift toward striking a balance between power and execution time [6]. For example, literature [7] estimated that a 5% decrease in power consumption of the Summit supercomputer could generate savings of around 1 million dollars. Therefore, it is increasingly critical to develop GPU power management strategies that can lower power consumption with a minimum impact on execution time.

There are several challenges to designing efficient power management strategies for GPUs. First, the complexity of GPU workloads in terms of their utilization of computational resources can lead to diverse power consumption needs. Second, GPUs offer a wide array of power consumption controls, and understanding the impact of these power controls on power consumption and performance is non-trivial. For example, the NVIDIA GA100 (Ampere) and GV100 (Volta) GPUs provide 81 core DVFS configurations in the range of 210 - 1410 MHz and 167 DVFS configurations in the range of 135 - 1380 MHz, respectively. While this flexibility is certainly favorable for saving power, it also makes the GPU's DVFS design space more complex in selecting a DVFS configuration that provides optimal power consumption and execution time simultaneously. Given the complexity of different workloads and power controls, it is not realistic for HPC system architects and operators to select the optimal GPU frequency manually.

Limitations of state-of-art approaches: Many studies have

explored to improve GPU power, performance, and energy efficiency [8, 9, 10, 11, 12, 13, 14]. The major research areas include DVFS space exploration, optimal frequency determination, analytical and machine learning (ML) based models using utilization metrics, and static code analysis. However, the existing approaches have some caveats: (1) features derived using static code analysis or utilization metric are not always best representative of a workload (often workload or architecturespecific), and (2) multi-objective functions provide a range of best frequencies rather a definitive optimal frequency [15, 7].

Experimental methodology and artifact availability: To address these challenges, the Optimal GPU Frequency Selection [16] has been proposed to automate the selection of the optimal DVFS configuration for a workload that requires three steps. First, characterization and identification of the GPU features that directly influence power and performance. We used the mutual information technique to prune the features most relevant to power and performance. Second, modeling of power and performance behaviors across DVFS design space to enable model-based estimation of a workload's power and execution time using the workload's utilization requirements. Third, the determination of the optimal DVFS configuration based on the estimated power and execution time profiles across all DVFS configurations. Flexible optimal frequency selection techniques were devised using multi-objective functions. These techniques included energy-delay product (EDP) [6, 17, 18, 19] and energy-delay-square product (ED<sup>2</sup>P). EDP takes the optimality of both energy and execution time (delay) into consideration simultaneously while selecting the optimal frequency. ED<sup>2</sup>P provides double-weight to the execution time.

Although the Optimal Frequency Selection has been previously described, a methodology to make it portable across different GPU architectures and real applications have remained undeveloped. In this study, we approached this by performing data collection for real applications on new GPU architecture, several inter-architectural analyses, and an extension of the power model. In particular, we analyze the portability of the features selected in study [16] on the NVIDIA GA100 GPU. The power model proposed in [16] is extended to mitigate interarchitectural power consumption variations. The applicationlevel portability is evaluated by estimating optimal frequencies of real applications using the models developed with microbenchmarks. The GPU architecture-level portability is evaluated by estimating the optimal frequencies of real applications on GA100 using the models developed with micro-benchmarks on GV100. We provided more evaluation data (selected frequencies, energy savings, changes in performance), useful insights, and example usage of our methodology in a production environment. The source codes, including data collection, power controls, data analysis, and implementation of analytical models, are publicly available [20].

**Key insights and contributions:** Overall, this study makes the following contributions.

1. Features Portability: The initial characterization of features using micro-benchmarks in study [16] confirms the impact of GPU utilization features on power usage, energy, and execution time. In this study, we evaluate the portability of features in terms of different input sizes, other GPU architectures, and vendors. We observe that the selected features are portable across architectures and vendors.

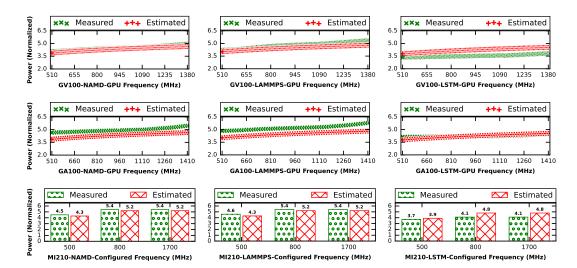

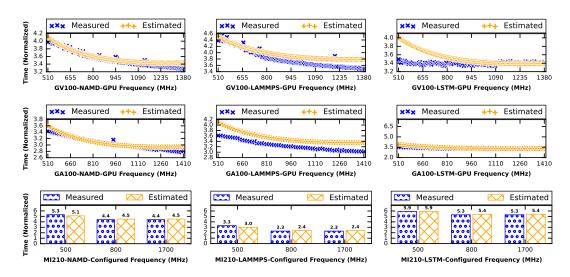

- 2. Models portability: Based on the characterization study, analytical models for execution time and power were proposed in the study [16]. We evaluated the portability of the models using real-world HPC and machine-learning workloads (application-level portability), NVIDIA GA100 GPUs (architecture-level portability), and AMD MI210 GPUs (vendor-level portability). The metric collection is required only at the GPU's maximum DVFS configuration for a given workload. These metrics are used to estimate a workload's power and performance for the remaining DVFS configurations using the proposed models. We evaluated the portability of the proposed methodology in study [16] for real-world applications. On NVIDIA GV100, using real-world applications, these models estimated power and performance up to 95.2% and 96.9%, respectively. Furthermore, we have evaluated the portability of the models across different GPU architectures and vendors. The power and performance models, developed using GV100's data (thermal design power (TDP) of 250W), estimated power and execution time of real applications on GA100 (TDP of 500 W) with accuracies of up to 97.9% and 98.2%, respectively. To evaluate vendor-level portability, we have mapped the feature set utilized in constructing the models from NVIDIA to a corresponding feature set available in AMD. The power and performance models, utilizing data from GV100, accurately estimated the power consumption and execution time of real applications on the AMD Instinct MI210 GPU, achieving accuracies of up to 96.1% and 99%, respectively.

- 3. Energy-performance trade-offs: The efficacy of the multi-objective optimal functions is evaluated. The energy profiles chosen by the ED<sup>2</sup>P-based optimal frequency achieved an energy saving of up to 29.6% with a performance loss of 5.2% for real applications on GA100.

- 4. Comparison with state-of-the-art models: We conducted a comparison between our models and the GPU assembly instructions (PTX)-based static models [7]. The results revealed a significant reduction in the average error rates, with a decrease from 19.7% to 3.1% for power models and from 29.4% to 5.2% for performance models.

**Limitations of the proposed approach:** The models require a given workload to be run at the maximum frequency to acquire utilization metrics. The models can only be used in association with DVFS. Other power controls, like power capping, are beyond the current scope of this work.

This paper is organized as follows. Section 2 provides the background and motivation of this research. Section 3 describes the experimental setup. Section 4 presents an overview of the methodology, data collection, feature analysis, analytical modeling, and explains the multi-objective algorithm for selecting the optimal frequency. Section 5 and 6 present the evaluation results. Section 7 provides a comparison of models with state-

of-the-art research. We discuss other related work and comparison in Section 8. Section 9 provides sample deployment options and Section 10 discusses concluding remarks.

## 2. Motivation

This section discusses the impact of DVFS on performance, power, and energy patterns on compute- and memory-intensive workloads. It also explains why multi-objective optimal functions are needed to select the optimal DVFS configuration.

## 2.1. Impact of DVFS on Compute-Intensive workload

DVFS technique is one of the widely used techniques to regulate power and performance by clocking the GPU core to different frequency configurations. Several previous works [10, 9] observed that the impact of DVFS on power and execution time depends on GPU architecture and application intensity. Hence, GPU workloads with different computational intensities show different power and execution time behaviors for a given core DVFS configuration. As a preliminary step, we tested DGEMM and STREAM [21, 22] GPU micro-benchmarks to understand the power and execution time characteristics of compute- and memory-intensive applications. Even though we have tested all supported GPU configurations, configurations below 510 MHz showed high performance penalties leading to a higher power and thus are infeasible. Hence, we only use configurations in the range of 510 - 1410 MHz (61 configurations) for GA100 and 510 - 1380 MHz (117 configurations) for GV100. It is worth noting that unlike some previous GPU architectures, which provide multiple memory frequency configurations, GA100 and GV100 support a single high bandwidth memory (HBM) frequency, i.e., 1593 MHz and 877 MHz, respectively.

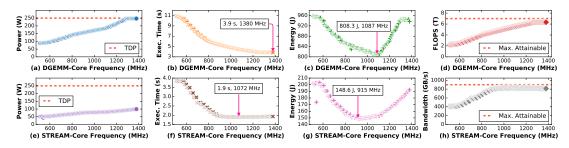

Figure 1 (a) to (d) show variations in power, execution time, energy, and execution time (floating-point operations per second (FLOPS)) across 117 DVFS configurations for the compute-intensive workload (i.e., DGEMM). It is observed that power is approximately a direct linear function of GPU core frequency. Performance degradation of up to 3x was observed when the GPU core frequency was changed from the maximum to the minimum frequency. We also noted that performance degradation is negligible for the frequencies in the range of 1250 - 1380 MHz. These frequencies can potentially be a viable opportunity for energy-performance trade-offs. Overall, it shows that for compute-intensive applications, DVFS is an effective technique to scale power. The power behavior can be scaled down to less than half of the GPU's TDP at the lower configuration (e.g., 510 MHz). On the other hand, the power can be ramped up to its TDP limit at the maximum frequency.

The execution time exhibits an indirect nonlinear relationship with DVFS configurations, as shown in Figure 1 (b). Performance degradation of up to  $\sim$ 3x was observed when the DVFS configuration was swayed from the maximum to the minimum configuration. We also noted that the performance degradation is negligible in the  $\sim$ 1250 - 1380 MHz frequency range. This frequency range can potentially be viable options for energy and performance trade-offs for compute-intensive workloads. Figure 1 (c) shows that energy is a parabolic (i.e., quadratic relationship) function of DVFS configuration. The energy metric for each DVFS configuration was computed as a product of power (a) and execution time (b). In general, the global minimum energy point across DVFS configurations is considered the optimal frequency where the compute-intensive DGEMM can save energy up to  $\sim 15.8\%$ .

Figure 1 (d) shows nearly a direct linear relationship between FLOPS and DVFS configurations. Like the execution time, the increment in FLOPS after 1250 MHz is insignificant.

To summarize, we can infer two main corollaries. First, the power consumption is highly dependent on the DVFS configuration. Second, an application's performance (both time and FLOPS) does not improve after reaching a particular DVFS configuration. Hence, any further increase in frequency causes increased in power without noticeable performance gain.

#### 2.2. Impact of DVFS on Memory-Intensive workload

Figures 1 (e) to (h) show variations in power, execution time, energy, and bandwidth across supported DVFS configurations for STREAM. Like DGEMM, power for STREAM is nearly linear with DVFS configuration as shown in Figure 1 (e). The power at the maximum DVFS configuration (1380 MHz) is  $\sim$ 100W and can be reduced up to  $\sim$ 50W at the minimum DVFS configuration (510 MHz) used in this study. Figure 1 (f) shows an indirect nonlinear relationship between execution time and DVFS configurations. It is worth noting that the execution time does not change for over 800 MHz. Thus, this configuration is optimal for the execution time. This phenomenon is also reflected in Figure 1 (h) showing that the bandwidth does not improve after ~ 800 MHz. Figure 1 (g) depicts the quadratic relationship between the frequency and energy. It is worth noting that the frequency providing the lowest energy point for STREAM (with energy savings of ~33%) is not the same frequency as DGEMM, suggesting that the optimal frequency of an application is driven by its computational intensity.

The HBM data rate is nearly a direct linear function of DVFS configuration as demonstrated in Figure 1 (h). The increase in GPU frequency also speeds up the data rate of the HBM. In alignment with (f), bandwidth does not improve after a DVFS configuration.

**Two key takeaways:** First, the execution time, power, and energy patterns of compute- and memory-intensive workloads indicate - (a) the change in GPU frequency effectively changes the execution time, power, and energy metrics. (b) The intensity of the change in these metrics is highly dependent on the workload's computational intensity. Second, the lowest DVFS configuration consumes the lowest power. However, the same configuration degrades performance at maximum. Furthermore, the maximum configuration can provide maximum performance; on the other hand, it may not be optimal for power and energy saving.

#### 2.3. Can One DVFS Configuration Fit All?

The optimal DVFS configuration for an application refers to a GPU operating frequency that reduces the power at the

Figure 1: Power, execution time, energy, and FLOPS variations across different frequency configurations for DGEMM (upper) and STREAM (lower), respectively.

cost of no performance degradation (ideally) or achieves the best trade-off between performance degradation and reduction in power and energy. However, empirical results in Figures 1 (b) and (c) show that the optimal execution time and optimal power consumption are exhibited by different DVFS configurations for an application. Furthermore, these configurations are not portable across applications (Figure 1 (b) and (f) or (c) and (g)). Comparatively, the optimal execution time was achieved at higher frequencies than the frequencies that delivered the optimal energy, and optimizing one objective can adversely affect the other. Thus, selecting the optimal frequency automatically for an arbitrary application is not a trivial task due to conflicting criteria of high performance and low power and energy. This observation supports a need for a multi-objective solution that simultaneously considers both execution time and power consumption for an application to determine the optimal DVFS configuration, which is the ultimate objective of this work.

#### 3. Experimental Setup

#### 3.1. Target Applications

In this study, we used three real applications, two microbenchmarks, and 19 industry benchmark applications in the SPEC ACCEL suite.

## 3.1.1. Real Applications

In this study, we used three GPU-enabled real-world applications, including: (1) Nanoscale Molecular Dynamics (NAMD) [23, 24], a large biomolecular systems simulation program; (2) Large-scale Atomic/Molecular Massively Parallel Simulator (LAMMPS) [25, 26], a particle simulator that models solidstate, soft matter, and coarse-grained materials; and (3) Long short-term memory (LSTM) [27] algorithm, a TensorFlowbased [28] implementation of binary sentiment classification of large movie review dataset [29]. The domains for these applications are shown in Table 1

## 3.1.2. Benchmark Applications

The proposed models were validated using the SPEC ACCEL<sup>®</sup> benchmark suite [30]. The application domains for the benchmarks in the SPEC ACCEL are shown in Table 2.

Table 1: The real applications used in our evaluations.

| Benchmark | Language    | Domain                                                                |

|-----------|-------------|-----------------------------------------------------------------------|

| NAMD      | C++/Charm++ | Parallel molecular dynamics<br>code for large biomolecular<br>systems |

| LAMMPS    | C++         | Large Atomic Simulations,<br>Molecular Simulations                    |

| LSTM      | Python      | Binary classification, Senti-<br>ment Analysis                        |

Table 2: The SPEC ACCEL benchmarks suite containing 19 OpenCL enabled benchmarks.

| Benchmark | Langua | gĐomain                                        |  |

|-----------|--------|------------------------------------------------|--|

| tpacf     | C++    | Astrophysics                                   |  |

| stencil   | C++    | Thermodynamics                                 |  |

| lbm       | C++    | Fluid Dynamics                                 |  |

| fft       | С      | Signal processing                              |  |

| spmv      | C++    | Sparse Linear Algebra                          |  |

| mriq      | C      | Medicine                                       |  |

| histo     | C      | Silicon Wafer Verification                     |  |

| bfs       | C      | Electronic Design Automation, Graph Traversals |  |

| cutcp     | С      | Molecular Dynamics                             |  |

| kmeans    | C++    | Dense Linear Algebra, Data Mining              |  |

| lavamd    | C      | N-Body, Molecular Dynamics                     |  |

| cfd       | C++    | Unstructured Grid, Fluid Dynamics              |  |

| nw        | C++    | Dynamic Programming, Bioinformatics            |  |

| hotspot   | С      | Structured Grid, Physics Simulation            |  |

| lud       | C++    | Dense Linear Algebra, Linear Algebra           |  |

| ge        | C++    | Dense Linear Algebra, Linear Algebra           |  |

| srad      | С      | Structured Grid, Image Processing              |  |

| heartwall | С      | Structured Grid, Medical Imaging               |  |

| bplustree | С      | Graph Traversal, Search                        |  |

## 3.2. Target Systems

In this study, we collected the utilization metrics for SPEC ACCEL, DGEMM, and STREAM, real applications (LAMMPS, NAMD, and LSTM) using NVIDIA Ampere A100 GPU node at the National Science Foundation (NSF)'s Chameleon CHI@UC site [31], AMD Instinct MI210 node at AMD site, and Volta V100 GPU node at High Performance Computing Center of Texas Tech University, managed by the Slurm Scheduler [32]. Table 3 lists the configurations of these systems. To avoid any interference from other jobs, all our experiments were performed using an NVIDIA GV100 with CUDA version 11.2 and driver version 450, and GA100 with CUDA version 11.5 and driver version 465. For MI210, we used ROCm 5.4, rocprof 2.0, and rocm-smi 5.4. Data analysis and

Table 3: Platforms used for our evaluations.

| Site            | Platform                 | CPU                                 | Memory | OS           | GPU        | GPU Memory  | GPU TDP |

|-----------------|--------------------------|-------------------------------------|--------|--------------|------------|-------------|---------|

| Chameleon@UC    | Dell PowerEdge XE8545    | 2 x 64 cores × AMD EPYC 7763        | 512 GB | CentOS 8     | GA100 SXM4 | 80 GB HBM2e | 500 W   |

| Chameleon@UC    | Dell PowerEdge C4140     | 2 x 24 cores × Intel Xeon Gold 6230 | 128 GB | CentOS 7     | GV100 PCIe | 32GB HBM2   | 250 W   |

| HPCC@TTU        | Dell PowerEdge R740      | 2 x 20 cores × Intel Xeon Gold 6242 | 384 GB | CentOS 8     | GV100 PCIe | 32GB HBM2   | 250 W   |

| Test Server@AMD | SUPERMICRO AS-4124GS-TNR | 2 x 64 cores × AMD EPYC 7742        | 528 GB | Ubuntu 18.04 | MI210 PCIe | 64GB HBM2e  | 300 W   |

modeling was performed using Python 3.10.1 64-bit.

#### 4. Methodology

This section introduces the overall methodology, data collection process, feature analysis, power modeling, performance modeling, and the multi-objective approach to selecting the optimal frequency.

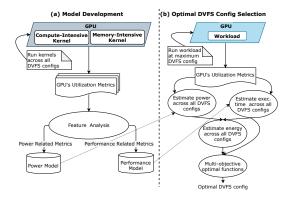

Figure 2: (a) Functions related to power and performance models development. (b) Functions related to the selection of the optimal frequency for a workload using the proposed models and multi-objective techniques.

#### 4.1. Overview

Our methodology consists of two phases: (1) building analytical models for power and execution time and (2) selecting the optimal frequency selection for a given workload using multiobjective optimal functions based on estimated power and execution time using analytical models.

Figure 2 (a) shows the process of building analytical models for power and execution time, which are built using workloads' GPU utilization metrics across GPU's DVFS design space. The following functions were involved in developing power and performance models: workload execution across GPU's DVFS design space, metric collection, feature analysis, and model construction. For developing models, we used utilization metrics of only DGEMM (representative of compute-intensive workloads) and STREAM (representative of memory-intensive workloads) micro-benchmarks. The GPU's utilization metrics were collected across the GPU's DVFS design space for the entire execution duration at the sampling interval of 20 ms. To mitigate statistical errors such as run-to-run variations, these benchmarks were run three times for each frequency. As demonstrated in Figure 1, extensive analyses were performed to understand the impact of different frequencies on power, execution

time, energy, bandwidth, and FLOPS. The metrics were characterized to find their relationship with power and execution time, as shown in Section 4.3. Finally, power and performance models were constructed empirically using the features which showed the highest correlations with power and execution time, respectively. One of the main objectives of these models is the portability and applicability of this methodology to a wide variety of applications and other GPU architectures. We modeled GPU architectural characteristics, which are instrumental in mitigating the changes in power and execution time for a target GPU architecture. These models do not require readjustment based on the target GPU architecture.

As shown in Figure 2 (b), to determine the optimal GPU DVFS configuration, the following steps are involved. First, a workload was run three times for data collection. As performance is paramount to HPC workloads, we collected GPU's utilization metrics at the GPU's maximum DVFS configuration. Furthermore, the power and performance profile at the maximum configuration was used as a reference point for the power and performance profile at the selected DVFS configuration. GPU's metrics were collected at a sampling interval of 20 ms for each run of the workload. Second, the workload's power and execution time were estimated via the proposed power and performance models, respectively. These estimations were performed for each GPU DVFS configuration using the workload's utilization metrics acquired at the maximum frequency. This model-based estimation of power and execution time across a GPU's supported DVFS configurations eliminates the need for the execution of a workload across these different DVFS configurations. The energy for a workload was computed using the estimated power and execution time for each DVFS configuration. Finally, multi-objective functions were used to determine the optimal frequency among the GPU's supported frequencies. These multi-objective functions use EDP and ED<sup>2</sup>P, which establish energy-performance trade-offs by simultaneously taking energy savings and performance degradation into account. The EDP function computes the score for each frequency by multiplying the energy and execution time of the DVFS configuration. The DVFS configuration with the lowest score is determined as the optimal frequency. The ED<sup>2</sup>P function is similar to EDP; however, ED<sup>2</sup>P applies more weight to the execution time. The ED<sup>2</sup>P always selects a higher DVFS configuration than the EDP for a given workload. Thus, it is useful in enabling performance-centric energy-saving trade-offs.

#### 4.2. Data Collection

We collected 12 GPU utilization metrics (seemingly relevant to power and performance) for DGEMM, STREAM, SPEC ACCEL benchmarks, and three real applications (LAMMPS, NAMD, and LSTM) across 117 DVFS configurations on the NVIDIA GV100. The same metrics were collected for real applications across 61 DVFS configurations on the NVIDIA GA100. We used the state-of-the-art NVIDIA Data Center GPU Manager interface (DCGMI) [33] interface for metric acquisition. The same interface was used to change the DVFS configuration of the GPU. Table 4 provides the description of the collected metrics. As described above, metrics related to DGEMM and STREAM were used to build the power and performance models. The metrics related to the SPEC ACCEL and real applications were used as the measured data in the model validation demonstrated in Sections 5 and 6. Section 6 also evaluates the inter-architectural portability of the proposed models and the selection of the optimal frequency mechanism using the real applications.

| Table 4: | Feature | Description |

|----------|---------|-------------|

|----------|---------|-------------|

| Feature          | Description                                                                                                                                                                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| power_usage      | Last measured power draw for the entire board. [From DCGMI.]                                                                                                                                                                                                                                                                                                               |

| dram_active      | Fraction of cycles where data was sent to or<br>received from device memory. It reports a<br>value between 0 and 1 that represents an av-<br>erage activity over a time interval. For ex-<br>ample, an activity of 0.2 indicates that 20%<br>of the cycles read from or write to device<br>memory over the time interval. [DCGMI.]                                         |

| fp64_active      | Fraction of cycles where the FP64 (double precision) pipe was active. It reports a value between 0 and 1 that represents an average over a time interval. [DCGMI.]                                                                                                                                                                                                         |

| fp32_active      | Fraction of cycles where the FP32 (single precision) pipe was active. The value is defined similarly to fp64_active feature. [DCGMI.]                                                                                                                                                                                                                                      |

| gr_engine_active | Overall graphics engine activity. The value (between 0 and 1 represents an average over a time interval. [DCGMI.]                                                                                                                                                                                                                                                          |

| sm_app_clock     | Application level SM clock frequency (MHz). [DCGMI.]                                                                                                                                                                                                                                                                                                                       |

| sm_active        | Fraction of time at least one warp was active<br>on a multiprocessor, averaged over all multi-<br>processors. Warps both performing actively<br>computing and waiting on memory requests<br>are considered active. The value [0:1] repre-<br>sents an average over a time interval. Usu-<br>ally, a value of 0.8 or higher indicates effec-<br>tive usage of GPU. [DCGMI.] |

| sm_occupancy     | Fraction of resident warps on a multiproces-<br>sor, relative to the maximum number of con-<br>current warps supported on a multiproces-<br>sor. The value [0:1] represents an average<br>over a time interval. The higher occupancy<br>does not always represent optimum GPU us-<br>age. [DCGMI.]                                                                         |

| pcie_tx_bytes    | Bytes sent by PCIe. [DCGMI.]                                                                                                                                                                                                                                                                                                                                               |

| pcie_rx_bytes    | Bytes received by PCIe. [DCGMI.]                                                                                                                                                                                                                                                                                                                                           |

| gpu_utilization  | Fraction of time the compute pipe was busy.<br>The value represents an average over a time<br>interval. [DCGMI.]                                                                                                                                                                                                                                                           |

| run_time         | Execution time of a specific benchmark ker-<br>nel. Sourced as <i>wall time</i> .                                                                                                                                                                                                                                                                                          |

Figure 3: Dependency between GPU's utilization metrics, power and time

#### 4.3. Feature Engineering

In this section, we discuss the process of selecting finegrained features which directly impact power and execution time. Furthermore, we analyze the impact of different DVFS configurations and input sizes on the selected features, and the portability of these features across GPU architectures.

### 4.3.1. Selection of the Fine-Grain Features

Feature analysis was performed to choose features that directly impact an application's power usage and execution time. These features are critical to developing accurate, reliable, and scalable analytical models for power and execution time estimation. We used the Mutual Information (MI) technique [34, 35, 36] to identify the features correlated with power and execution time. MI estimates distances using nonparametric knearest neighbors algorithm. This approach shows an unbiased correlation, which is more effective than the correlation (often algorithm-specific) shown by a machine learning algorithm. As a representative of compute-intensive and memory-intensive applications, the feature analysis used the dataset for DGEMM and STREAM benchmark applications only. Figure 3 shows the dependency between power\_usage and run\_time, and other GPU utilization features. The feature with a higher mutual correlation value (close to 1) is indicative of a higher dependency. Out of these features, we observed that *fp\_active*, *sm\_app\_clock*, and *dram\_active* are the most prominent features that influence both power usage and execution time.

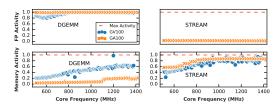

The *fp\_active* and *dram\_active* are instrumental in understanding the computational intensity of a workload. In general, compute-intensive applications show higher *fp\_active* than the memory-intensive applications as depicted in Figure 4 where floating-point activity (fp\_active) for DGEMM is higher than STREAM. While DGEMM is also shown to have considerable memory activity (dram\_active), the value for STREAM is much higher. Moreover, we observed that the inclusion of *gpu\_utilization* does not improve the prediction accuracy, and the *pcie\_\** metrics did not provide any significant improvement for our models either.

The  $sm_app\_clock$  is used to scale the power and execution time of an application. For both benchmarks, power decreases (as depicted in Figure 1-(a) and (e)) with  $sm_app\_clock$ while the execution time increases (as illustrated in Figure 1 (b) and (f)). It shows that a change in GPU frequency changes the power and execution time in a computational intensityaware way. Therefore, it can be deduced that the GPU metrics *fp\_active, dram\_active*, and *sm\_app\_clock* are reliable features for controlling an application's power usage and time.

### 4.3.2. Impact of DVFS on Computational Activities

We further investigated the impact of changes in DVFS configurations on the computational activities (i.e., fp\_active and dram\_active) of memory- and compute-intensive applications. DGEMM and STREAM were tested by changing the DVFS configurations at maximum input sizes on GA100 and GV100 architectures. As demonstrated in Figure 4, the floatingpoint activity is almost unaffected by the change of DVFS configurations for both compute- and memory-intensive applications; however, memory-activity shows variations for both applications. We also observed that DGEMM exhibited different memory usage behaviors across GV100 and GA100. We will explain the rationale behind this deviation later.

Figure 4: Impact of DVFS on the computational activities (i.e., *fp\_active* and *dram\_active*) of memory- and compute-intensive applications.

#### 4.3.3. Impact of Input Size on Computational Activities

We investigated the impact of changes in input sizes on the computational activities of memory- and compute-intensive applications. DGEMM and STREAM were tested using different input sizes at the maximum core frequency on GA100 and GV100 architectures, as depicted in Figure 5.

As in the case of changes in frequency, we observed similar patterns concerning the change of input sizes on computational activities. The floating-point activity is approximately unaffected by the change of input sizes for both applications on both GPU architectures. The memory activity of DGEMM showed variations within and across both architectures. Unlike in the previous case, the memory activity of STREAM was observed to be mostly unaffected by the change in input sizes on both architectures. In addition, our preliminary analyses confirm that a change in input sizes of memory and compute-intensive applications does not change their power signature [37].

#### 4.3.4. Features Portability Across GPU Architectures

We analyzed the portability of fp\_active and dram\_active reported by memory-intensive (STREAM) and computeintensive (DGEMM) kernels across GV100 and GA100 architectures. Figure 4 and Figure 5 corroborate five findings concerning to portability of these features across GPU architectures: (1) floating-point activity for memory- and computeintensive kernels was reported the same on both architectures and were unaffected by the change in DVFS configuration and the change in input size; (2) memory activity is nearly unimpacted by the change in input size for a memory-intensive kernel; (3) memory activity to some extent showed variation with the change in DVFS configuration for both kernels; and (4) nonuniform memory activity patterns on GV100 and GA100 for DGEMM benchmark.

While GA100 memory frequency (i.e., 1593 MHz) is significantly higher than the GV100 memory frequency (i.e., 877 MHz), results showed comparatively low memory activity on GA100 for DGEMM. We investigated this deviation by looking into the architectural characteristics of both GPUs. We found that GA100 is enhanced with double-precision tensor cores, which support double-precision matrix multiply-accumulate (DMMA) instruction. A single DMMA instruction (on GA100) is equal to eight traditional FP64 instructions (on GV100) [38]. This architectural enhancement enables GA100 to save significant memory space and bandwidth. The reduction in memory activity for DGEMM on GA100 (Figure 4) is due to its support for Double-Precision Tensor Cores capability.

**Summary:** MI technique confirms fp\_active, dram\_active, sm\_app\_clock as the top three features exhibiting a strong relationship with power and execution time. sm\_app\_clock (DVFS configuration) is a hardware feature of the target GPU. fp\_active is unaffected by the change in sm\_app\_clock, the change in the input size, and the change of GPU architecture. dram\_active is slightly affected by the change in sm\_app\_clock, the change in the input size, and the change in GPU architecture. Overall, fp\_active and dram\_active of an application can uniquely identify power and execution time signature for a given GPU sm\_app\_clock.

## 4.4. Power Modeling

To develop a power model, it is essential to consider the aspects of applications and architectures that directly influence power. Our empirical analysis indicates that the floating-point and memory activities directly impact the (dynamic) power at a given core frequency. This implies that the floating-point and memory activities are reliable features to identify an application's power signature. The power is shown to increase approximately in a linear manner up to the GPU's TDP, depending upon the application's activity. With these underlying basics, we use floating-point activity ( $FP_{act}$ ), memory activity( $DRAM_{act}$ ), and core frequency (f) to model activity-driven power ( $P_f$ ) behavior of an application as shown in Equation 1.

$$P_f = \alpha \cdot FP_{act} + \beta \cdot DRAM_{act} + \gamma \cdot f + C \pm \lambda \tag{1}$$

where  $\alpha$ ,  $\beta$ , and  $\gamma$  represent regression coefficients for floatingpoint activity, memory activity, and core frequency, respectively, and *C* is a constant. These coefficients are estimated using metrics data from DGEMM and STREAM benchmarks.  $\lambda$ is a constant factor that essentially scales up or down power for other GPU architectures. Its value is a ratio of the target GPU's core count to the base GPU's core count. When the core count of the target GPU is *more* than the core count of the base GPU, the resultant value is calculated by adding this value. However,

Figure 5: Impact of different input sizes on the computational activities (i.e., fp\_active and dram\_active) of memory- and compute-intensive applications.

when the cores count of the target GPU is *less* than the cores count of the base GPU, the resultant value is estimated by subtracting this value. Moreover, computing the coefficients for the models has no noticeable overhead. In our evaluations, the estimation of power and execution time, along with the selection of the optimal frequency, took less than a second.

## 4.5. Performance Modeling

While the execution time of individual kernels is predictable based on their computational activities, repetitive tasks and different data input sizes involved in real-world applications make execution time estimation complicated. The execution time depends on the input size, and literature [39] confirms our observations. The proposed performance model requires the execution time of a workload at the maximum-frequency, and then our model scales the execution time for other frequencies. Another key point in designing a DVFS-based performance model is to consider the impact of frequency scaling on time. Based on our observations, the execution time exhibits nonlinear inverse relation with GPU's core frequencies, as shown in Figure 1-(b) and (f). To address this challenge, researchers use the application's execution time at maximum core frequency as the application's default execution time and linearly estimate the variations in the execution time for the remaining core frequencies. For example, recent literature [39] tried to estimate the change in execution time in relation to a change in core frequency by using the application's default execution time as an input execution time. Our evaluation of [39] shows two fundamental shortcomings. First, the execution time estimation is limited to compute-intensive applications. Second, the change in the estimated execution time when the frequency is changed from the GPU's highest frequency is estimated in linear rather than the desired nonlinear fashion. Therefore, we model these nonlinear (nearly parabolic) behaviors demonstrated in Figure 1-(b) and (f) as a second-degree polynomial function of floating-point activity  $(FP_{act})$  and change in frequency  $(\Delta f)$ . The performance model is derived using Equations 2, 3, and 4. The performance model is intended to estimate nonlinear variations in the application's execution time between the highest core frequency and the remaining core frequencies.

$$T_f = T_{f_{max}} + T_{f_\Delta} \tag{2}$$

where  $T_f$  denotes the execution time at frequency f,  $T_{f_{max}}$  represents the execution time at the highest frequency, and  $T_{f_A}$  refers

to the change in execution time from the maximum core frequency to the given core frequency f, which is determined using Equation 3.

$$T_{f_{\Delta}} = \beta_1 \cdot FP_{act} + \beta_2 \cdot \Delta f + \beta_3 \cdot FP_{act}^2 + \beta_4 \cdot FP_{act} \cdot \Delta f + \beta_5 \cdot \Delta f^2$$

(3)

where  $FP_{act}$  refers to the application's FP activity at maximum frequency and  $\Delta f$  denotes the change in frequency from maximum to the given frequency as shown in Equation 4.

$$\Delta f = f_{max} - f \tag{4}$$

The  $\beta_1$ ,  $\beta_2$ ,  $\beta_3$ ,  $\beta_4$ , and  $\beta_5$  are polynomial coefficients, which are estimated using variations in execution time corresponding to changes in frequency configurations and application's FP activity. These estimations were empirically computed using metrics data from DGEMM and STREAM benchmarks. The inclusion of FP activity is critical because it reflects the application's computational activity (see Figure 1 (b) and (f)).

## 4.6. Optimal Frequency Selection

As already discussed in Section 2.3, the optimal frequency is the one that reduces the power with no performance degradation (ideally) or achieves the best trade-off between execution time and power. The optimal frequency for an application is selected using a multi-objective approach including EDP [6, 17, 18, 19] and ED<sup>2</sup>P. These approaches require energy and execution time estimations. The energy is computed for each frequency (f) using Equation 5 based on the power usage and execution time estimated via the proposed power and performance models.

$$E_{f_{estimated}} = P_{f_{estimated}} \times T_{f_{estimated}}$$

(5)

The algorithm for selecting the optimal frequency among supported DVFS configurations is straightforward and shown in Algorithm 1. This algorithm takes three lists, including energy (E), execution time (T), and frequency (F) as input. It outputs the optimal f setting based on the  $ED^2P$  score. The algorithm involves two major steps: First, the  $ED^2P$  score for each set of energy and time is computed by multiplying the energy with the square of execution time. Second, the lowest score decides the optimal energy-delay profile out of the given sets of energy and time for the given workload. The frequency (f) corresponding to the lowest score is the optimal frequency and will be selected as the optimal frequency. The optimal frequency selection using EDP is similar to this algorithm. The only difference is that

| on using ED <sup>2</sup> P |                            |

|----------------------------|----------------------------|

| 0                          | on using ED <sup>2</sup> P |

| <b>Require:</b> $E_1 \ldots E_N, T_1 \ldots T_N, F_1 \ldots F_N$ | ▹ list of energies, run               |

|------------------------------------------------------------------|---------------------------------------|

| times, and frequencies                                           |                                       |

| Ensure: f                                                        | <ul> <li>optimal frequency</li> </ul> |

|                                                                  |                                       |

| 1: <b>f</b> | <b>function</b> Optimal( $E[], T$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [], <i>F</i> [])             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 2:          | $EDP \leftarrow E \times T^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | compute list of EDP scores   |

| 3:          | $min \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 4:          | index $\leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |

| 5:          | $N \leftarrow length(ED^2P)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |

| 6:          | <b>for</b> <i>k</i> = 1 to <i>N</i> <b>do</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ▶ find the minimum EDP score |

| 7:          | if $ED^2P_k < min$ the second | hen                          |

| 8:          | $min \leftarrow ED^2P_k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

| 9:          | index $\leftarrow K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                              |

| 10:         | $f \leftarrow F_{index}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ▷ optimal frequency          |

the EDP score is calculated instead of the  $ED^2P$  score, where the energy is multiplied by the execution time (i.e., energy and time are given equal weights).

## 5. Evaluation with SPEC ACCEL Benchmarks

This section provides evaluation results for 19 benchmark applications in the SPEC ACCEL suite (see Table 2). Their utilization metrics were unseen by our proposed models.

#### 5.1. Estimation of Power and Performance

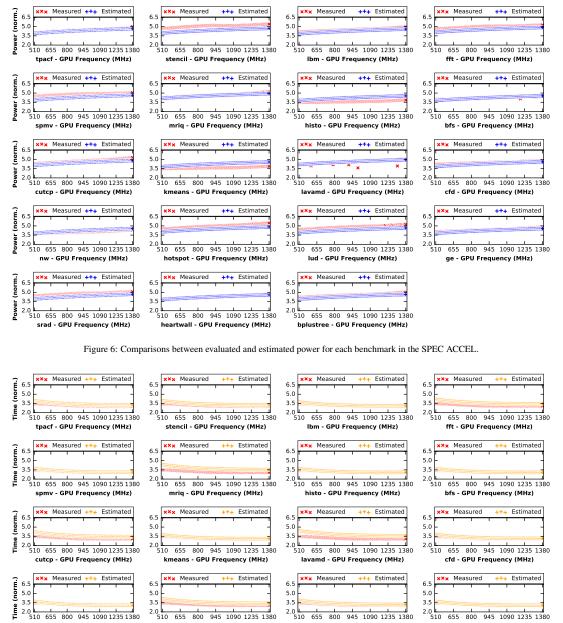

The power usage and execution time were estimated for the SPEC ACCEL benchmarks across 117 DVFS configurations on GV100 using the proposed power and performance models.

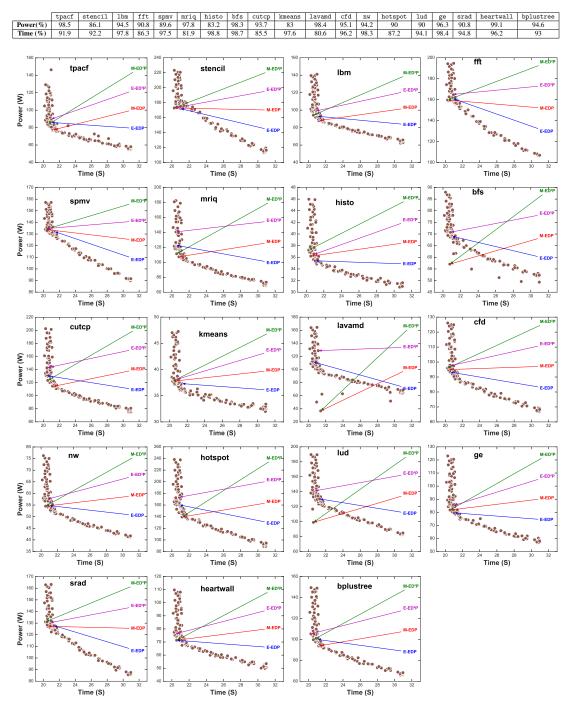

An application's power was estimated using the frequency along with the FP and DRAM activities acquired at the maximum frequency. Figure 6 compares the estimation power generated by the proposed power model and measured power for each benchmark in the SPEC ACCEL. We used the mean absolute percentage error (MAPE) metric to understand the accuracy of the proposed models. As shown in Table 5, the proposed power model estimated power usage for 15 of the benchmarks in the SPEC ACCEL with an accuracy of over 90% (and up to 99.1%). However, the model slightly overestimated or underestimated power usage for the benchmarks with significantly low or high computational activities. For example, hist (FP=0.0005, DRAM=0.0235) and kmean (FP=0.0243, DRAM=0.3197) overestimated power usage. Conversely, stencil (FP=0.2781, DRAM=0.7301) underestimated power usage.

For estimating the execution time, only frequency and FP activity were used. Figure 7 compares the execution time estimated by the proposed performance model and measured execution time for each benchmark in the SPEC ACCEL. The execution time was estimated with an accuracy of more than 90% (and up to 98.8%) for 15 benchmarks, as shown in Table 5. We did not observe any underestimation of execution time. However, the proposed model is likely to slightly overestimate execution time for a benchmark exhibiting higher FP activity (e.g., lavamd, mriq).

#### 5.2. Optimal Frequency Selection

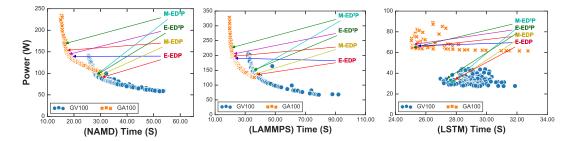

The (measured) M-EDP and M-ED<sup>2</sup>P optimal frequencies refer to the optimal frequencies selected via EDP and ED<sup>2</sup>P approaches using *measured* energy and execution time metrics. Similarly, (estimated) E-EDP and E-ED<sup>2</sup>P optimal frequencies refer to the optimal frequencies selected via EDP and ED<sup>2</sup>P approaches using energy and execution time metrics *estimated* by the proposed models. Figure 8 shows the optimal frequencies selected via M-EDP, E-EDP, M-ED<sup>2</sup>P, and E-ED<sup>2</sup>P approaches for each benchmark in the SPEC ACCEL on GV100. Table 6 lists M-EDP, E-EDP, M-ED<sup>2</sup>P, and E-ED<sup>2</sup>P optimal frequencies for each SPEC ACCEL benchmark on GV100.

In general, the M-EDP, E-EDP, M-ED<sup>2</sup>P, and E-ED<sup>2</sup>P optimal frequencies for each benchmark were less than the GPU's maximum frequency. This observation confirms our hypothesis that the GPU's maximum frequency is not always optimal. Further, E-ED<sup>2</sup>P optimal frequency selected for each benchmark was always higher than the E-EDP optimal frequency. This outcome affirms our assumption that ED<sup>2</sup>P approach is useful in defining more performant trade-offs. We also observed a symbiotic relationship between models accuracy, and P-EDP and E-ED<sup>2</sup>P optimal frequencies: (1) A higher accuracy in estimation of power usage and execution time for a benchmark lead to the selection of more accurate E-EDP and E-ED<sup>2</sup>P optimal frequencies (e.g., ge, nw); (2) an overestimated power lead to the selection of comparatively lower E-EDP and E-ED<sup>2</sup>P optimal frequencies (e.g., kmean, histo); and (3) an overestimated execution time lead to selection of comparatively higher E-EDP and E-ED<sup>2</sup>P optimal frequencies (e.g., lavamd, mriq). The actual energy-performance trade-offs are evaluated below.

## 5.3. Energy and Performance Evaluation

The effectiveness of the optimal frequency is measured by its ability to save energy with minimal performance degradation. The change in execution time and energy savings of the optimal frequency are calculated with reference to the GPU's highest frequency. The change in execution time can be computed using Equation 6:

$$T\_Change(\%) = 100 \cdot \left(\frac{T_{maximum} - T_{optimal}}{T_{maximum}}\right)$$

(6)

where  $T_{maximum}$  and  $T_{optimal}$  are the measured execution times for the application at maximum and optimal frequencies, respectively. The *T\_Change* can be either positive or negative. A positive value indicates performance gain, and a negative value suggests performance degradation using the optimal frequency. The energy savings can be computed using Equation 7:

$$E\_Savings(\%) = 100 \cdot \left(\frac{E_{maximum} - E_{optimal}}{E_{maximum}}\right)$$

(7)

where  $E_{maximum}$  and  $E_{optimal}$  are energy consumed as measured at the maximum and optimal frequencies, respectively.

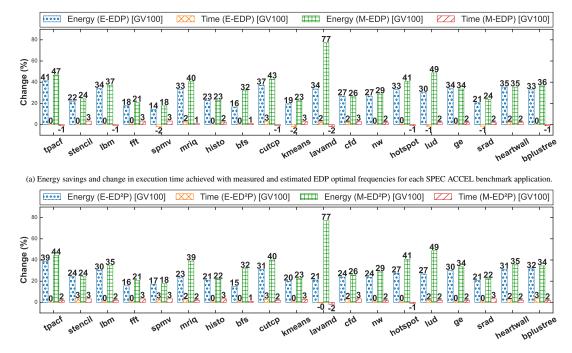

Figure 9 shows energy savings and changes in execution time achieved with (a) measured and estimated EDP optimal frequencies and (b) measured and estimated ED<sup>2</sup>P optimal frequencies for each SPEC ACCEL benchmark application. On

2.0 510 655 800 945 1090 1235 1380 srad - GPU Frequency (MHz) - GPU Frequ ncy (MHz) ustree - GPU Frequency (MHz) bpl

ncy (MHz)

Estimated

6.

5.0

3 5

Figure 7: Comparisons between evaluated and estimated execution time for each benchmark in the SPEC ACCEL.

2.0 **---**510

lud - GPU Frequency (MHz)

655 800 945 1090 1235 1380

Estimated

Measured

otspot - GPU Freque

Measured

average, M-EDP and E-EDP (Figure 9 (a)) saved energies 36% and 28.6% with performance gains 0.3% and 1.2%, respectively. Similarly, M-ED<sup>2</sup>P and E-ED<sup>2</sup>P (Figure 9 (b)) collec-

Estimated

6.5

5.0

35

nw - GPU Frequency (MHz)

Measured

norm.) 6.5 5.0

lime

35

tively saved energies 35.2% and 25.2% with performance gains 1.3% and 2%, respectively. We noted that energy savings attained with estimated optimal frequencies are less than the en-

Table 5: Power and performance estimation accuracy for SPEC ACCEL benchmark applications.

Figure 8: The optimal DVFS profiles at GV100 selected with measured-EDP, estimated-EDP, measured-ED<sup>2</sup>P and estimated-ED<sup>2</sup>P for each benchmark in the SPEC ACCEL shown along with the power and execution time for each supported DVFS configurations.

(b) Energy savings and change in execution time achieved with measured and estimated ED<sup>2</sup>P optimal frequencies for each SPEC ACCEL benchmark application.

Figure 9: Energy savings and change in execution time achieved with (a) measured and estimated EDP optimal frequencies and (b) measured and estimated ED<sup>2</sup>P optimal frequencies for each SPEC ACCEL benchmark application.

|           | Optimal Frequency (MHz) |           |                   |           |  |

|-----------|-------------------------|-----------|-------------------|-----------|--|

| Benchmark | EDP                     |           | ED <sup>2</sup> P |           |  |

|           | Measured                | Estimated | Measured          | Estimated |  |

| tpacf     | 907                     | 1020      | 997               | 1110      |  |

| stencil   | 1102                    | 1020      | 1102              | 1102      |  |

| lbm       | 907                     | 982       | 997               | 1065      |  |

| fft       | 1102                    | 1065      | 1102              | 1155      |  |

| spmv      | 1102                    | 990       | 1102              | 1072      |  |

| mriq      | 960                     | 1117      | 997               | 1207      |  |