## **UC Santa Cruz**

#### **UC Santa Cruz Electronic Theses and Dissertations**

#### **Title**

Materials Growth and Characterization of Thermoelectric and Resistive Switching Devices

#### **Permalink**

https://escholarship.org/uc/item/3b20674g

#### **Author**

Norris, Kate Jeanne

## **Publication Date**

2015

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SANTA CRUZ

## MATERIALS GROWTH AND CHARACTERIZATION OF THERMOELECTRIC AND RESISTIVE SWITCHING DEVICES

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

by

Kate J. Norris

June 2015

| he Diss | ertation of Kate J. Norris is approved |

|---------|----------------------------------------|

| Profess | or Nobuhiko Kobayashi, chair           |

| Profess | or Jeol Kubby                          |

| Jianhua | Yang, Ph.D.                            |

Tyrus Miller

Vice Provost and Dean of Graduate Studies

Copyright © by

Kate J. Norris

2015

## **Table of Contents**

| Li         | List of Figures |                                                                        | V    |

|------------|-----------------|------------------------------------------------------------------------|------|

| Li         | st of Table     | es                                                                     | vii  |

| Ał         | stract          |                                                                        | viii |

| De         | edication       |                                                                        | xi   |

| Ac         | knowledg        | gments                                                                 | xii  |

| 1 <b>]</b> | Introduc        | etion                                                                  | 1    |

|            | 1.1             | Thermoelectric devices.                                                | .1   |

|            | 1.2             | Nanowire Networks                                                      | 2    |

|            | 1.3             | Metal Organic Chemical Vapor Deposition                                | 5    |

|            | 1.4             | Transmission Electron Microscopy                                       | 6    |

| Pa         | rt I The        | ermoelectric Materials Growth and Characterization                     |      |

| 2          | MOCV            | D Growth of Erbium Monoantimonide Thin Film and Nanocomposite          | S    |

|            | for The         | rmoelectrics                                                           | 11   |

| 3          | Reflecti        | ion absorption infrared spectroscopy analysis of the evolution of ErSb | on   |

|            | InSb            |                                                                        | 26   |

| 4          | Nanoim          | nprint Lithography based Selective Area Growth of Indium Phosphide     |      |

|            | Nanopil         | llar Arrays on Non single-crystal Templates                            | .40  |

| 5          | Grapher         | ne Mediated Growth of Polycrystalline Indium Phosphide Nanowires       | and  |

|            | Monocr          | rystalline-Core, Polycrystalline-Shell Silicon Nanowires on Copper     | 59   |

| 6          | Silicon         | Nanowire Networks for Multi-stage Thermoelectric Modules               | .80  |

| 7   | Nonline   | ar Current-Voltage Characteristics of Semiconductor Nanov | vire Network |

|-----|-----------|-----------------------------------------------------------|--------------|

|     | based D   | ouble-stage Thermoelectric Devices                        | 96           |

| Pai | rt II Res | sistive Switching Materials Growth and Charact            | erization    |

| 8   | Investiga | ation of a Nanoscale TaOx Resistive Switching Device      | 117          |

| 9   | Self-Ali  | gned NbO2 nano-cap for Negative Differential Resistance F | Resistive    |

|     | Switchin  | ng Devices                                                | 128          |

| 10  | Future    | e Work                                                    | 139          |

|     | 10.1      | Thermoelectric Devices.                                   | 139          |

|     | 10.2      | Resistive Switching Devices                               | 140          |

| * A | hihliaara | why will be contained at the end of each chanter          |              |

## List of Figures

| 1.1           | Basic schematic of how a thermoelectric device operates                                          | 2   |

|---------------|--------------------------------------------------------------------------------------------------|-----|

| 1.2           | TEM image of a nanowire intersection at higher magnification                                     | 5   |

| 1.3           | Bright field image and diffraction pattern of a crystalline Si substrate                         | 9   |

| 2.1           | ErSb thin film deposition rate on InSb (100) substrates                                          | .16 |

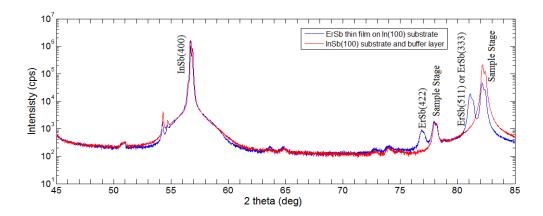

| 2.2           | XRD profile of an ErSb thin film grown on an InSb (100) substrate                                | .18 |

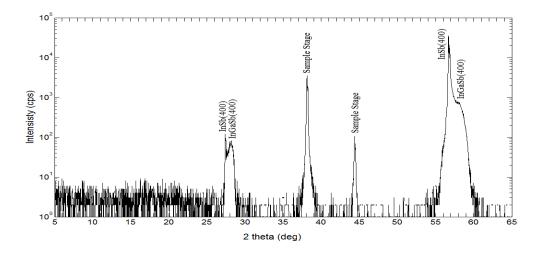

| 2.3           | XRD profile of the ErSb/In <sub>1-x</sub> Ga <sub>x</sub> Sb:Zn (x=0.975) nanocomposite          | .19 |

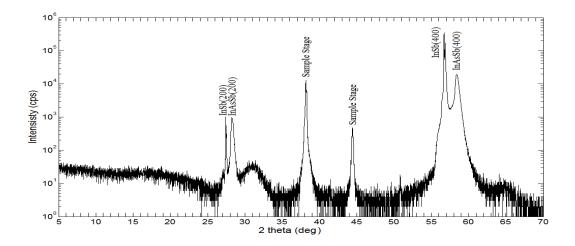

| 2.4           | XRD profile of the ErSb/ InSb <sub>1-y</sub> As <sub>y</sub> :Zn (y=0.406) nanocomposite         | .20 |

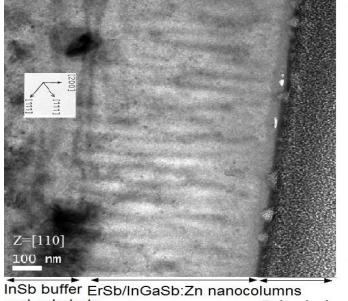

| 2.5           | TEM of the ErSb/InGaSb:Zn nanocomposite                                                          | 22  |

| 2.6           | TEM of the ErSb/InSbAs:Zn nanocomposite                                                          | .22 |

| 3.1<br>tempe  | ErSb thin film deposition rate on InSb (100) substrates as a function of erature and Sb/Er MFRR. | 30  |

| 3.2           | Reflection Absorption Infra-red Spectroscopy (RAIRS) configuration                               | 31  |

| 3.3           | RAIRS spectra of four ErSb samples on InSb                                                       | 34  |

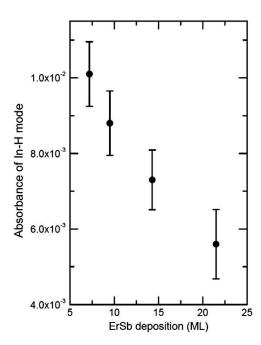

| 3.4<br>deposi | Peak absorbance of In-H vibrational mode plotted as a function of ErSb ition.                    | 35  |

| 3.5           | AFM of two ErSb layers on InSb surfaces.                                                         | 36  |

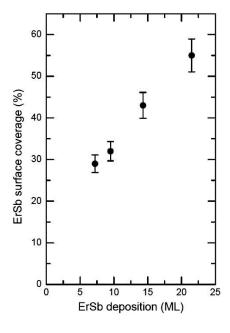

| 3.6           | ErSb surface coverage on the InSb buffer layer                                                   | 36  |

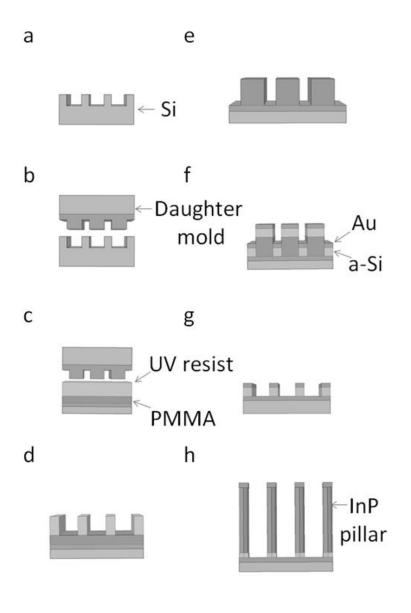

| 4.1           | Nanoimprint lithography fabrication procedure for nanopillars                                    | 44  |

| 4.2           | SEM of InP nanopillars growth by MOCVD in growth progression                                     | 46  |

| 4.3           | XRD of the InP nanopillars                                                                       | 49  |

| 4.4           | Cross sectional TEM of a InP nanopillar                                                          | 51  |

| 4.5           | Photoluminescence of the InP nanopillars                                                         | 55  |

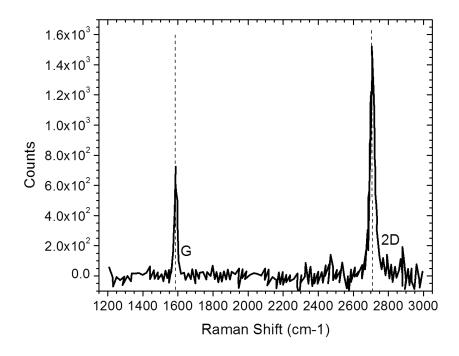

| 5.1           | Raman Spectroscopy on a carbon-trated copper substrate                                           | 65  |

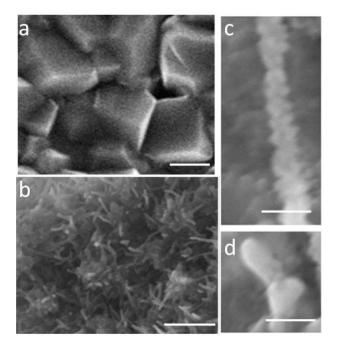

| 5.2           | SEM images of InP nanowires grown by MOCVD on copper                                             | 66  |

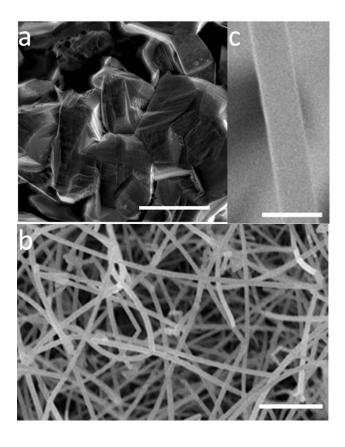

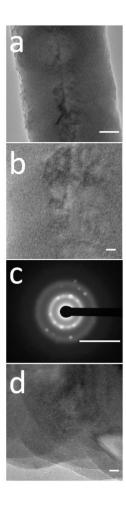

| 5.3           | TEM images of a InP nanowire grown by MOCVD on copper                                            | 67  |

| 5.4           | SEM images of Silicon nanowires grown by PECVD on copper                                         | 68  |

| 5.5           | TEM of a Si nanowire grown by PECVD on copper.                                                   | 70  |

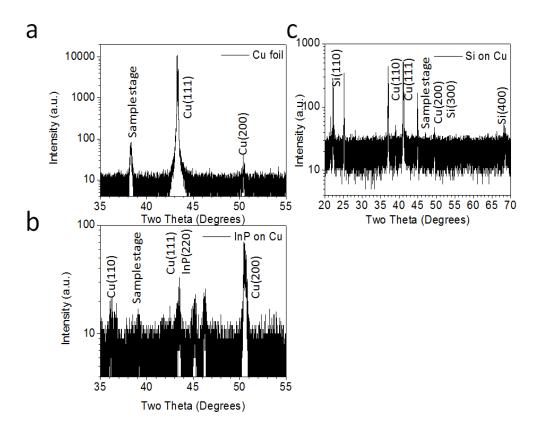

| 5.6           | XRD of a copper substrate, InP nanowires, and Si nanowires                                       | 71  |

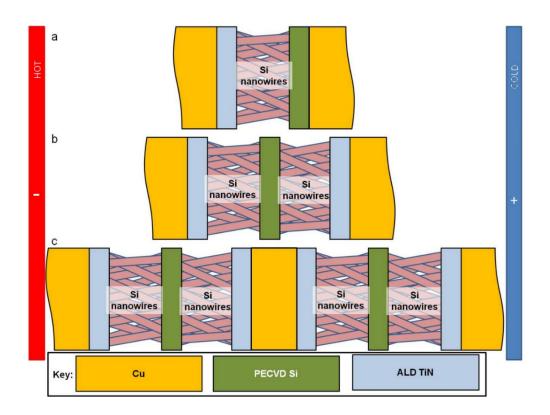

| 6.1<br>networ  | Schematic of three thermoelectric (TE) modules of stacked Si nanowire ks85                                              | 5 |

|----------------|-------------------------------------------------------------------------------------------------------------------------|---|

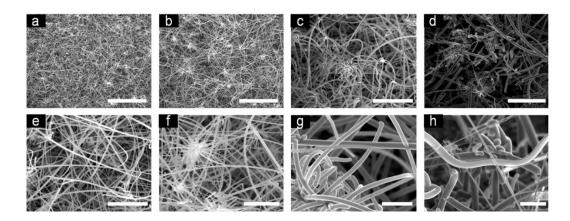

| 6.2            | SEM images of p-type Si nanowire networks grown by PECVD86                                                              | 5 |

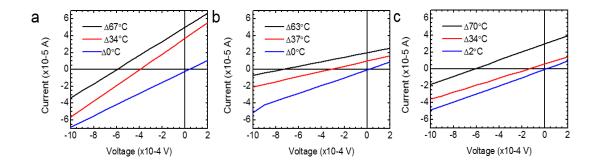

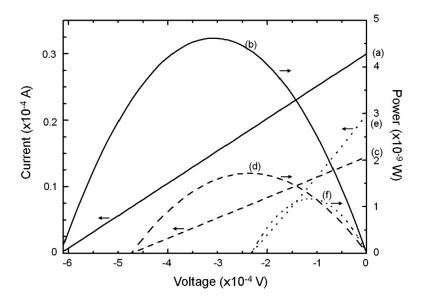

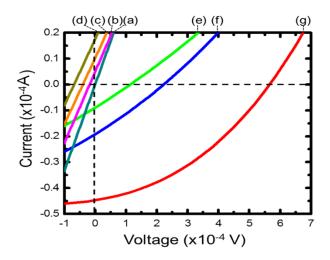

| 6.3            | Current-Voltage curves for three TE modules                                                                             | 9 |

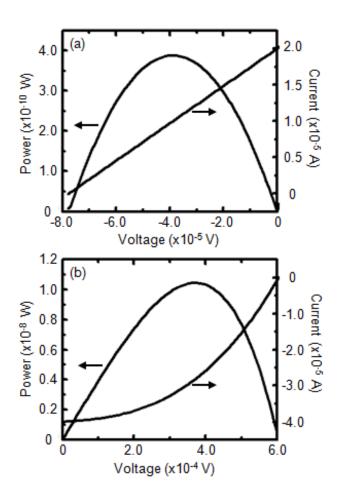

| 6.4<br>gradiei | Power and current-voltage curves for three TE modules with a temperature at of 18°C across each network                 | ) |

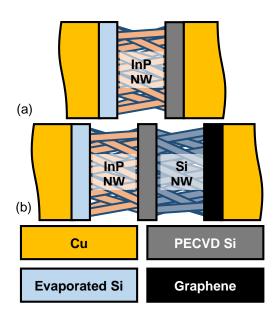

| 7.1<br>InP/Si  | Schematic of two TE devices, a single stage InP TE device and a double stage TE device                                  |   |

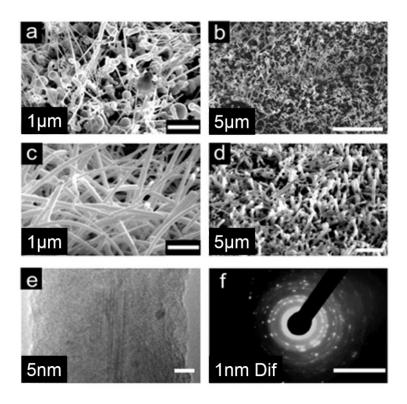

| 7.2            | SEM and TEM of the InP nanowire networks used in the InP TE deivce10                                                    | 5 |

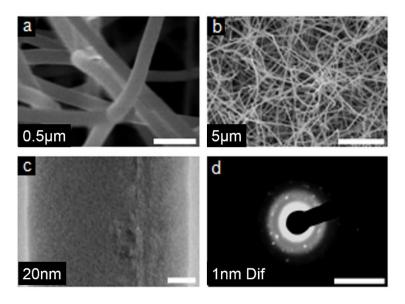

| 7.3            | SEM and TEM of the Si nanowire networks used in the InP/Si TE deivce106                                                 | 5 |

| 7.4<br>varied  | Current vs. voltage curves of the InP TE device and the InP/Si TE devices at temperatures                               | 0 |

| 7.5<br>InP/Si  | Power and current vs voltage curves at 50°C for the InP TE device and the TE device                                     | 2 |

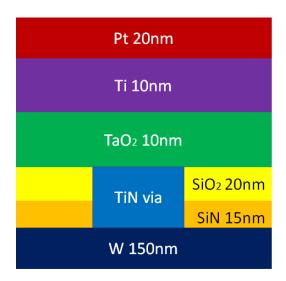

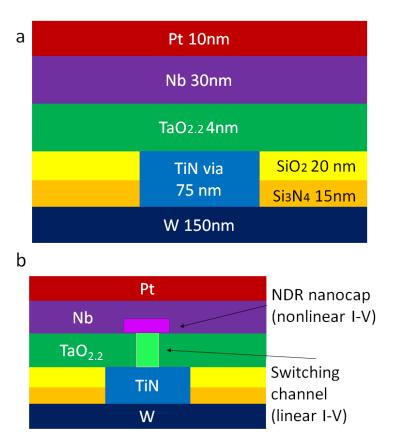

| 8.1<br>top ele | Schematic of a resistive switching device with a TaO <sub>2</sub> switching layer and a T ctrode                        |   |

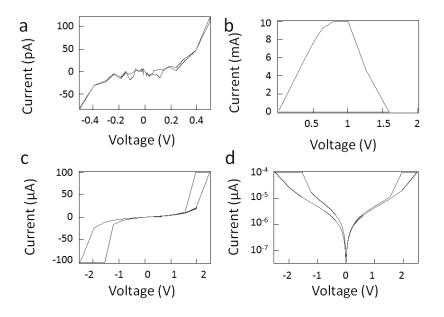

| 8.2<br>of thes | Current-voltage curves of three devices showing the virgin, on and off states e devices                                 | 1 |

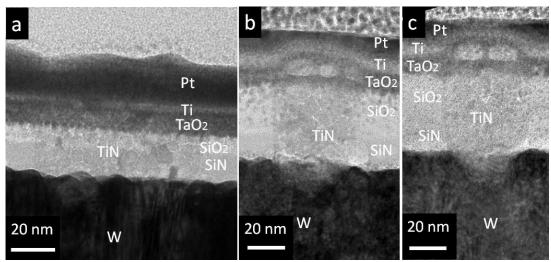

| 8.3            | Cross sectional HRTEM of three devices in the virgin, on, and off states124                                             | 4 |

| 8.4            | Core-Loss EELS mapping of three devices in the virgin, on, and off states.125                                           | 5 |

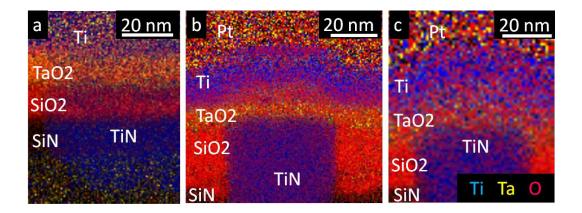

| 9.1<br>Nb top  | Schematic of a resistive switching device with a TaO <sub>2.2</sub> switching layer and a electrode                     |   |

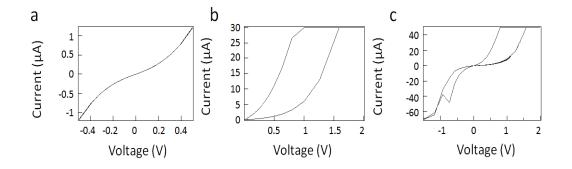

| 9.2<br>nonline | Current-voltage curves showing the history of electrical operation of the ear TaO <sub>2.2</sub> cross sectioned device | 4 |

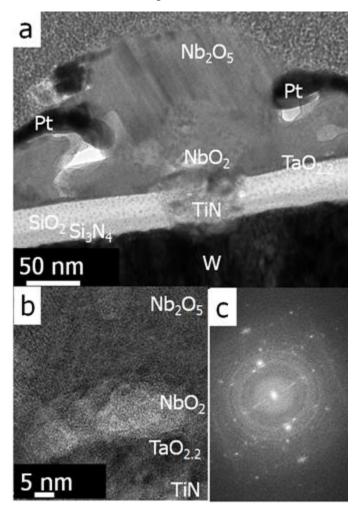

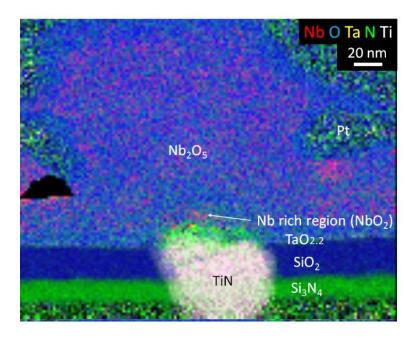

| 9.3            | Cross sectional HRTEM of the nonlinear device                                                                           | 5 |

| 9.4            | Core-Loss EELS mapping of the nonlinear device                                                                          | 6 |

## List of Tables

| 6.1 | Si nanowire diameter range and growth time                                            | .87 |

|-----|---------------------------------------------------------------------------------------|-----|

| 6.2 | Per nanowire network values of $P_{max}$ , $I_{sc}$ , and $V_{oc}$ for each TE module | 91  |

| 7.1 | Values of $P_{max}$ , $I_{sc}$ , and $V_{oc}$ for each TE device at ~50°C             | 110 |

#### **Abstract**

# MATERIALS GROWTH AND CHARACTERIZATION OF THERMOELECTRIC AND RESISTIVE SWITCHING DEVICES

by

#### Kate J. Norris

In the 74 years since diode rectifier based radar technology helped the allied forces win WWII, semiconductors have transformed the world we live in. From our smart phones to semiconductor-based energy conversion, semiconductors touch every aspect of our lives. With this thesis I hope to expand human knowledge of semiconductor thermoelectric devices and resistive switching devices through experimentation with materials growth and subsequent materials characterization. Metal organic chemical vapor deposition (MOCVD) was the primary method of materials growth utilized in these studies. Additionally, plasma enhanced chemical vapor deposition (PECVD), atomic layer deposition (ALD), ion beam sputter deposition, reactive sputter deposition and electron-beam (e-beam) evaporation were also used in this research for device fabrication. Scanning electron microscopy (SEM), Transmission electron microscopy (TEM), and Electron energy loss spectroscopy (EELS) were the primary characterization methods utilized for this research. Additional device and materials characterization techniques employed include: current-voltage measurements, thermoelectric measurements, x-ray

diffraction (XRD), reflection absorption infra-red spectroscopy (RAIRS), atomic force microscopy (AFM), photoluminescence (PL), and raman spectroscopy.

As society has become more aware of its impact on the planet and its limited resources, there has been a push toward developing technologies to sustainably produce the energy we need. Thermoelectric devices convert heat directly into electricity. Thermoelectric devices have the potential to save huge amounts of energy that we currently waste as heat, if we can make them cost-effective. Semiconducting thin films and nanowires appear to be promising avenues of research to attain this goal. Specifically, in this work we will explore the use of ErSb thin films as well as Si and InP nanowire networks for thermoelectric applications. First we will discuss the growth of erbium monoantimonide (ErSb) thin films with thermal conductivities close to or slightly smaller than the alloy limit of the two ternary alloy hosts. Second we consider an ex-situ monitoring technique based on glancing-angle infraredabsorption used to determine small amounts of erbium antimonide (ErSb) deposited on an indium antimonide (InSb) layer, a concept for thermoelectric devices to scatter phonons. Thirdly we begin our discussion of nanowires with the selective area growth (SAG) of single crystalline indium phosphide (InP) nanopillars on an array of template segments composed of a stack of gold and amorphous silicon. Our approach enables flexible and scalable nanofabrication using industrially proven tools and a wide range of semiconductors on various non-semiconductor substrates. Then we examine the use of graphene to promote the growth of nanowire networks on flexible copper foil leading to the testing of nanowire network devices for thermoelectric

applications and the concept of multi-stage devices. We present the ability to tailor current-voltage characteristics to fit a desired application of thermoelectric devices by using nanowire networks as building blocks that can be stacked vertically or laterally. Furthermore, in the study of our flexible nanowire network multi-stage devices, we discovered the presence of nonlinear current-voltage characteristics and discuss how this feature could be utilized to increase efficiency for thermoelectric devices. This work indicates that with sufficient volume and optimized doping, flexible nanowire networks could be a low cost semiconductor solution to our wasted heat challenge.

Resistive switching devices are two terminal electrical resistance switches that retain a state of internal resistance based on the history of applied voltage and current. The occurrence of reversible resistance switching has been widely studied in a variety of material systems for applications including nonvolatile memory, logic circuits, and neuromorphic computing. To this end we next we studied devices in each resistance state of a TaOx switch, which has previously shown high endurance and desirable switching behavior, to better understand the system in nanoscale devices. Finally, we will discuss a self-aligned NbO2 nano-cap demonstrated atop a TaO2.2 switching layer. The goal of this device is to create a nanoscale RRAM and selector device in a single stack. These results indicate that ternary resistive switching devices may be a beneficial method of combining behaviors of different material systems and that with proper engineering a self-aligned selector is possible.

## To my grandfather,

#### Harold Cozad,

Who instilled a love of technology and learning in me while teaching me I could do anything I set my mind to

### To Edward Cremata,

Who cheered me on the whole way and sacrificed in the name of science for this thesis

#### Acknowledgments

First and Foremost I would like to express my gratitude to my advisor,

Nobuhiko P Kobayashi for inspiring me, teaching me, and always believing in me.

You made me the engineer and researcher I am today. Working for you has been a

pleasure I can't hope to top, I enjoyed working for you. I worked hard for you

because you inspired me to work hard. I couldn't hope for a better supervisor.

During my time as a student at UCSC I have been taught by so several and collaborated with many fine persons. I would like to express my appreciation to Dr. Andrew Lohn who took the time to train me in MOCVD and thermoelectric theory, his discussions and brain challenges are appreciated and cherished. Elane Coleman grew all Silicon nanowire samples discussed in this work. Mike Oye has been a consistent supporter.

I am thankful to Dr. Stanely Williams and all of Hewlett Packard Labs for the ability to work alongside some of the best researchers in the nation and be trained in their image. Max Zhang, Xuema Li, Katy Samuels, and Steven Barcelo thought me fabrication techniques and built many samples in this work with me. Jiaming Zhang has graciously trained me in EELS and improved my TEM abilities. Perhaps most of all I learned how to design resistive switches from Dr. Jianhua Yang, a wonderful teacher and mentor.

The text of this thesis includes the following previously published material:

Norris, K.; Lohn, A.; Onishi, T.; Coleman, E.; Wong, V.; Shakouri, A.; Tompa, G.;

Kobayashi, N. *J. Electron. Mater.* **2012**, *41*, 971–976. Norris, K. J.; Wong, V. K.;

Onishi, T.; Lohn, A. J.; Coleman, E.; Tompa, G. S.; Kobayashi, N. P. *Surf. Sci.* **2012**, *606*, 1556–1559. Norris, K. J.; Zhang, J.; Fryauf, D. M.; Gibson, G. A.; Barcelo, S. J.; Kobayashi, N. P. *J. Cryst. Growth* **2014**, *386*, 107–112. Norris, K. J.; Garrett, M.;

Coleman, E.; Tompa, G. S.; Zhang, J.; Kobayashi, N. P. *J. Cryst. Growth* **2014**, *406*, 41–47. Norris, K. J.; Garrett, M. P.; Zhang, J.; Coleman, E.; Tompa, G. S.;

Kobayashi, N. P. *Energy Convers. Manag.* **2015**, *96*, 100–104.

The research performed for this thesis would not be possible without my fine co-authors; Andrew J. Lohn, Takehiro Onishi, Elane Coleman, Vernon Wong, Ali Shakouri, Gary S. Tompa, Nobuhiko P. Kobayashi, Junce Zhang, David M. Fryauf, Gary A. Gibson, Steven J. Barcelo, Matthew Garrett, and J. Joshua Yang.

#### Chapter 1

#### Introduction

#### 1.1 Thermoelectric Devices

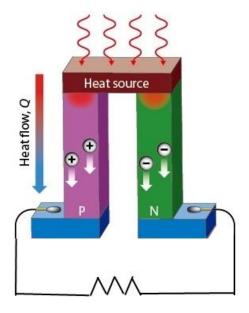

Thermoelectric devices are composed of materials that create an electrical potential when placed under a temperature gradient. This phenomena is caused by a net diffusion of charge carriers from the hot to the cool side as shown in Figure 1.1. The dimensionless figure of merit ZT breaks down the qualities that make good thermoelectric materials,  $ZT = S^2 \sigma T / \kappa$  where S is the Seebeck coefficient,  $\sigma$  is electrical conductivity, T is absolute temperature, and  $\kappa$  is thermal conductivity. Essentially, for thermoelectric materials to work effectively, the material needs to be a poor thermal conductor but also a good electrical conductor. Metallic materials have desirable electrical thermal conductivity levels however they have high thermal conductivity and therefore are a poor thermoelectric material. Insulators have the opposite problem of natural low thermal conductivity levels as is ideal however their low thermal conductivity levels make them poor candidates. Innately optimizing ZT is a difficult problem as  $\sigma$  and  $\kappa$  are inherently related in a manner not suitable for ideal thermoelectric devices. Therefore semiconductors are the best option for thermoelectric materials, as they can achieve reasonable values of ZT. To compete with the current industry standard, Bismuth Telluride, a minimum ZT of 1 is required[1].

Figure 1.1 Basic schematic of how a thermoelectric device operates.

#### 1.2 Nanowires Networks

Material properties change significantly at the nanoscale. When semiconducting materials are controlled at the nanoscale, the wavefunction describing the charge carriers of the device are confined and an altered density of states is observed. This creates a separation in the energy states of the material making the band gap tunable. Quantum confinement occurs in structures with dimensions comparable to the De Broglie wavelength of their carries, on the scale of tens of nanometers. This correlates to limited motion in the confined dimension(s) with infinite motion in the unconfined dimension(s) introducing quantization of energy states. Therefore quantum wells, or thin films, have one dimension of confinement, nanowires have two dimensions of confinement, and quantum dots have three dimensions of confinement.

Theoretical analysis has been reported to show that the Seebeck coefficient for quantum well (QW) structures increases linearly with decreasing QW thickness. Therefore when the thickness becomes less than a few nanometers based on the assumption that the enhancement of Seebeck coefficient arises mainly from an increase in the density of states near the conduction band edge when the carrier electrons are confined in such a narrow space[2], [3]. It has been shown that due to quantum confinement, nanowires also exhibit a large reduction in thermal conductivity compared with their bulk materials which would considerably increase the dimensionless figure of merit,  $ZT=S^2\sigma T/\kappa$  [4], [5]. The reduced dimensions of nanowires cause the scattering of phonons at the surface because charge carriers have much smaller wavelength than the majority of the phonon spectrum. Therefore thin films and nanowires are promising forms of semiconductors for thermoelectric applications.

In the study presented here nanowire networks were strongly considered. Specifically the intersections of nanowire networks are of interest, creating thick mesh like structures. The Boltzmann transport equation (BTE), utilized for transport theory in solids, treats electrons and phonons as particles but overlooks the wave nature with its well known scattering mechanisms [6]. Nanowires can experience strong quantum confinement and have dimensions comparable to the phonon wavelength, especially in nanowire networks with a large number of intersections. Previously it has been suggested that a Coulomb blockade model can explain the electron transport through an intersection [7]. An electron wave can experience a finite reflection at a potential barrier created by a different environment at the fused portion[7]. We hypothesize that

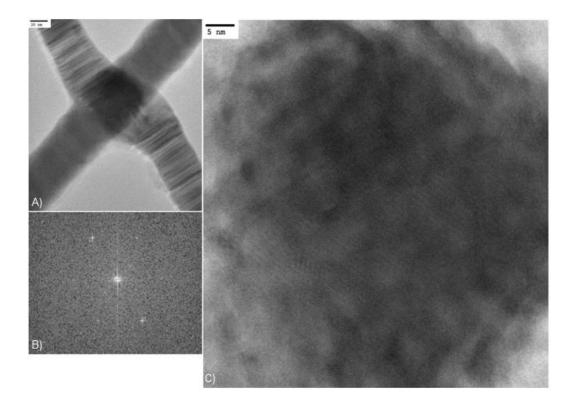

a phonon could also be reflected at the fused portion, as the crystal structure through which a phonon travels may vary suddenly, resulting in a reduction in thermal conductivity at intersections in a nanowire network. Furthermore, if phonons see the intersection as a virtual surface different from a continuous bulk material, surface phonon modes could be excited, which results in many different phonon polarizations than those found in bulk semiconductors[6]. Our current comsol multi-physics modeling described above is purely geometrical, therefore microscopic factors cannot be ruled out in thoroughly describing electrical and thermal properties of nanowire networks. Figure 3 shows transmission electron microscope (TEM) images collected at the center of an intersection where two indium phosphide nanowires are fused. Two fringe directions crossing according to the lattice of the two nanowires prior to fusing can be seen here. There also appears to be some distortion in atomic arrangement. Phonon waves could potentially experience the atomic arrangement distortion at the intersection as the electrons experience the potential barrier. If this is in fact occurring, it could result in decreased thermal conductivity at the intersection.

Figure 1.2: A) Lower magnification bright field image of the intersection illustrating the fused quality of the nanowires, B) associated selected area Fast Fourier Transform with points, not rings, indicating a high level of crystallinity, C) Bright field TEM image of a nanowire intersection at higher magnification.

#### 1.3 Metal Organic Chemical Vapor Deposition

Metal Organic Chemical Vapor Deposition (MOCVD) started in 1968-9 with the work of Manasevit and Simpson though the growth of single crystal GaAs on lattice mismatched substrates [8]. MOCVD is an interesting material growth method because it is scalable, economical for high quality semiconductor production, flexible, high purity, and can produce abrupt interfaces. The drawbacks to utilizing this method of growth is the required precursors are expensive and hazardous. Additionally, this method has the most parameters to control, a disadvantage inherent to desirable flexibility.

For the MOCVD growth of III-V nanowires the vapor-liquid-solid (VLS) method was used. VLS is a bottom up method of fabrication requiring a catalyst. Au was used as the catalyst material in our studies. In this process a vapor, the carrier gas with precursor, flows over the surface of the substrate. Once the organic bonds are thermally cracked near the substrate from heat, the metal atoms are free to react on the substrate. A small "diffusion layer" is present over the surface of the substrate causing the precursors to diffuse to the surface of the substrate. The Au catalyst turns to liquid as the substrate is heated and is a preferred site for the vapor to condense, supersaturating the catalyst. Once supersaturated, the nucleation of small clusters within the liquid alloy droplet align with the substrate interface. As the cluster grows out of the droplet forcing the droplet upward with the precipitation of the compound. Generally crystal growth requires a single crystalline substrate as the nanowire will align to the crystallographic direction of the substrate. However, single crystalline substrates are expensive, thick, and inflexible. Therefore, we explore the use of thin film a on flexible metallic substrates to allow the growth of nanowire networks with the requirement that the polycrystalline grains of the thin film exceed the diameter of the nanowires growing aligned with them.

#### 1.4 Transmission Electron Microscopy

Knoll and Ruska first developed Transmission Electron Microscopy as a characterization technique in 1932 [9]. A current heats a filament emitting electrons that are accelerated down the column, then focused by lenses and transmitting through the sample. The electron beam is both transmitted through the thin specimen and

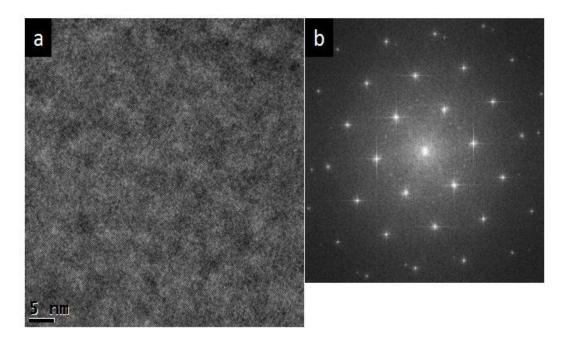

diffracted. The wavelength of the accelerated electrons allow for imaging of a single column of atoms. This creates a diffraction pattern when the Bragg conditions are met. The resultant pattern allows you to determine the material you are imaging as well as which plane of the material we are observing. This is confirmed through fringe spacing. Figure 1.3 a) shows the bright field TEM image of a Si wafer aligned to the zone axis, or the electron beam, while b) depicts the diffraction pattern created by the [100] Si wafer along the [110] zone axis. Image contrast is affected by sample thickness and composition. The heavier, higher atomic number, the material is, the darker it will appear.

The specimen must be thin enough for the electron beam to transmit through the sample limiting the thickness to ~100nm maximum. This requirement makes the sample preparation for TEM experiments time consuming and difficult. The simplest method used in these studies was drop casting of nanowires which were ultrasonicated. To cross section a device for a TEM study an ion beam was used to remove the region of interest and polish it to less than 100nm for viewing. Platinum and Carbon were used as protective layers to prevent the region of interest from ion damage. A cross sectional TEM view of a nanowire or semiconductor device can yield important information about crystal growth and device fabrication. TEM is a useful method when atomic resolution is required. This method can shed light on device behavior and actual structure.

TEM equipment can be equipped with electron energy loss spectroscopy (EELS) measurement tools. EELS is a very powerful form of spectroscopy because it

can take spectra with the same area of a STEM probe, down to ~.5nm in diameter. In EELS the specimen is exposed to the beam of electrons with a narrow range of kinetic energy as it was accelerated at a set energy to form the beam. Some of the electrons will transmit without any interaction and will form the zero loss peak as they have lost no energy passing through the specimen. A strong zero loss peak without secondary peak indicate a good quality, thin specimen, likely around 30nm thick. Some electrons however experience inelastic scattering passing through the specimen, meaning that the electron beam interacts with an electron and lose energy deflecting their path slightly in a random direction. The amount of energy lost in the interaction can be measured by a spectrometer and interpreted to yield extensive information about the specimen. The possible events that an electron can experience correlate to the various regions of the EELS spectra. First the zero loss peak represents the transmitted beam that loss no energy as it did not interact. Then we have the plasmonic region, energy losses up to 50eV that reflect plasmon excitations, resonance of valence electrons, and interband transitions, outershell electron interactions. The shape of the plasmonic region is directly related to the band structure of the material. Finally, we have the core loss region reflecting interactions with inner shell electrons, the excitation to unoccupied higher level shells above the Fermi level creating a characteristic 'edge' of the energy to transition to that shell. The fine structure of the core loss peaks can yield information about bonding. Therefore EELS is capable of measuring atomic composition, chemical bonding, as well as valence and conduction band electronic properties. EELS is most effective with low atomic numbers where the excitation edges are sharp and relatively easy to measure.

Figure 1.3 a) bright field image of a crystalline Si substrate and b) the diffraction pattern of the Si aligned to the [110] zone.

#### References

- [1] G. Chen and a. Shakouri, "Heat Transfer in Nanostructures for Solid-State Energy Conversion," *J. Heat Transfer*, vol. 124, no. April, p. 242, 2002.

- [2] L. D. Hicks and M. S. Dresselhaus, "Effect of quantum-well structures on the thermomagnetic figure of merit," *Phys. Rev. B*, vol. 47, no. 19, pp. 727–731, 1993.

- [3] H. Ohta, S. Kim, Y. Mune, T. Mizoguchi, K. Nomura, S. Ohta, T. Nomura, Y. Nakanishi, Y. Ikuhara, M. Hirano, H. Hosono, and K. Koumoto, "Giant thermoelectric Seebeck coefficient of a two-dimensional electron gas in SrTiO3.," *Nat. Mater.*, vol. 6, pp. 129–134, 2007.

- [4] D. Li, Y. Wu, P. Kim, L. Shi, P. Yang, and A. Majumdar, "Thermal conductivity of individual silicon nanowires," *Appl. Phys. Lett.*, vol. 83, no. 14, p. 2934, 2003.

- [5] L. D. Hicks and M. S. Dresselhaus, "Thermoelectric figure of merit of a one-dimensional conductor," *Phys. Rev. B*, vol. 47, no. 24, pp. 16631–16634, Jun. 1993.

- [6] D. G. Cahill, W. K. Ford, K. E. Goodson, G. D. Mahan, A. Majumdar, H. J. Maris, R. Merlin, and S. R. Phillpot, "Nanoscale thermal transport," *J. Appl. Phys.*, vol. 93, no. 2003, pp. 793–818, 2003.

- [7] T. Yamada, H. Yamada, A. J. Lohn, and N. P. Kobayashi, "Room-temperature Coulomb staircase in semiconducting InP nanowires modulated with light illumination," *Nanotechnology*, vol. 22, no. 5, p. 55201, 2011.

- [8] Schubert, E. Fred. *Doping in III-V Semiconductors*. Cambridge [England: Cambridge UP, 1993. Print. ISBN: 0 521 41919 0

- [9] Runyan, W. R., and T. J. Shaffner. *Semiconductor Measurements and Instrumentation*. New York: McGraw Hill, (1998). ISBN: 0-07-057697-1

## Part I Thermoelectric Materials Growth and

## Characterization

Chapter 2

# MOCVD growth of erbium monoantimonide thin film and nanocomposites for thermoelectrics

Kate J. Norris<sup>1,2</sup>, Andrew J. Lohn<sup>1,2</sup>, Takehiro Onishi<sup>1</sup>, Elane Coleman<sup>3</sup>, Vernon Wong<sup>1,2</sup>, Ali Shakouri<sup>1</sup>, Gary S. Tompa<sup>3</sup>, and Nobuhiko P. Kobayashi<sup>1,2</sup>

<sup>1</sup>Baskin School of Engineering, University of California, Santa Cruz, Santa Cruz, CA 95064, U.S.A.

<sup>2</sup>Nanostructured Energy Conversion Technology and Research (NECTAR),

Advanced Studies Laboratories (ASL), University of California Santa Cruz, and

NASA Ames Research Center, Moffett Field, CA 94035, U.S.A.

<sup>3</sup>Structred Materials Industries Inc., Unit 102/103, 201 Circle Drive North, Piscataway, NJ 08854, U.S.A.

#### **Abstract**

We report the growth of erbium monoantimonide (ErSb) thin films on indium antimonide(100) substrates by low-pressure metal organic chemical vapor deposition. The growth rate of ErSb thin films shows strong dependency on the growth

temperature and the Sb/Er precursor molar flow rate ratio. Scanning electron microscopy, energy dispersive x-ray spectroscopy, and x-ray diffractometry (XRD) were employed to study the ErSb thin films grown under the growth conditions that gave the maximum growth rate in the range we investigated. We also report the growth of two types of nanocomposites in which ErSb nanocolumns or nanoslabs with lengths ~500 nm and diameters 20-30 nm are embedded in Zn doped InGaSb (ErSb/InGaSb:Zn) and ErSb nanoparticles with diameters of ~30 nm are embedded in Zn doped InSbAs (ErSb/InSbAs:Zn). These nanocomposites were intended to increase phonon scattering in a mid-to-long phonon wave length range to reduce lattice thermal conductivity. We used time domain thermo reflectance to measure total thermal conductivity for the two types of nanocomposites, and we obtained  $4.0 \pm$ 0.6 and  $6.7 \pm 0.8$  W/m.K for the ErSb/InAsSb:Zn and ErSb/InGaSb:Zn nanocomposites, respectively, suggesting that the thermal conductivity was close to or slightly smaller than the alloy limit of the two ternary alloy hosts. The two nanocomposites were further studied with transmission electron microscopy to reveal their microscopic features and XRD to assess their crystalline structures.

#### Introduction

Demand for green energy has spurred the search for carbon free energy sources by harvesting wasted energy. Thermoelectrics are environmentally friendly power sources under growing investigation that convert a temperature gradient into electric power. The standard guideline of efficient thermoelectric materials search for low-temperature applications is to identify narrow band gap semiconductors with

high carrier mobility [1]. The efficiency of a thermoelectric material is a function of the dimensionless figure of merit ZT, where  $ZT=S^2\sigma T/\kappa$ ; S is the Seebeck coefficient,  $\sigma$  is electrical conductivity, T is absolute temperature,  $\kappa$  is thermal conductivity [2]. A  $ZT\sim1$  for bismuth telluride, BiTe, alloys near room temperature discovered in the 1950s is necessary for practical applications. However due to the interdependence of the components of the dimensionless figure of merit it has been difficult to achieve a ZT>1[3]. To improve ZT, one can increase the power factor,  $S^2\sigma$ , and/or reduce thermal conductivity,  $\kappa$ . There are various approaches to achieve higher ZT, such as: introducing peaks in the density of states [4], phonon scattering with "guest atoms"[5], one-dimensional nanostructures[3], and superlattices [6]. A record high ZT of 2.65 and a thermal conductivity of 0.031 W/mK was measured for a Bi<sub>2</sub>Te<sub>3</sub> single thin layer prepared by laser ablation [7]. Additionally, a ZT of  $\sim$ 2.4 has been reported for a Bi<sub>2</sub>Te<sub>3</sub>/Sb<sub>2</sub>Te<sub>3</sub> superlattice by Venkatasubramanian [6].

We focused on reducing thermal conductivity. Thermal conductivity,  $\kappa$ , is broken into the contribution from lattice vibrations (i.e., phonons) and from charged carriers. The lattice contribution can be suppressed by using the concept of "nanocomposites", semimetallic nanoparticles embedded in an alloy host semiconductor. Recent advances utilizing ErAs semimetallic nanoparticles embedded in an alloy host semiconductor made of one of group III-V compound semiconductors have shown that the lattice thermal conductivity can be reduced to near its theoretical limit[8, 9, 10, 11]. Much remains to be explored in the understanding of phonon transport in nanostructured materials despite attempts [12].

To further enhance the thermoelectric properties of nanocomposites we designed nanocomposites with ErSb nanostructures embedded in two types of alloy host semiconductors;  $In_xGa_{1-x}Sb$  and  $InSb_{1-y}As_y$ . Embedded semimetallic nanoparticles, for instance, can maintain electrical properties and optimize heat transport properties of the host semiconductors by working as mid to long-wavelength phonon scattering sources[13, 14], along with dopants [15]. The thermoelectric power factor  $(S^2\sigma)$  is also enhanced by nanoparticles [9]. It was also reported that ZT increased with the reduction in embedded nanoparticle size [8].

While ErSb has been grown exclusively by molecular beam epitaxy [9, 16, 17], we demonstrated the growth of ErSb by metal organic chemical vapor deposition (MOCVD) on InSb(100) substrates. In our demonstration, ErSb was deposited in the form of either thin films or nanostructures in a host semiconductor as mentioned earlier. Two types of ErSb nanostructures have been identified; nanoparticles and nanocolumns embedded in a host (In<sub>1-x</sub>Ga<sub>x</sub>Sb or InSb<sub>1-y</sub>As<sub>y</sub>) ternary alloy. Our research has demonstrated the potential of nanocomposites that would reduce thermal conductivity below the alloy limit, practically improving *ZT* and providing a method to grow ErSb-based nanocomposites by MOCVD for a wide range of viable applications.

#### **Experimental Procedure**

ErSb thin films on InSb(100) substrates

Low-pressure MOCVD was used to grow ErSb thin films on epi-ready InSb(100) substrates. An InSb(100) substrate was placed on a susceptor held in a reaction chamber made of quartz. The surface of InSb(100) substrate was thermally deoxidized before the deposition of an InSb buffer layer and a subsequent ErSb thin film. The precursors; triethylantimony(TESb) and tris-isopropylcyclopentadienyl erbium (iPrCp 3Er), were carried by purified hydrogen gas to the reaction chamber. The growth temperature, pressure, molar flow rates were 485°C, 180 Torr, 5.58x10<sup>-5</sup> moles/min of TESb, and 1.37x<sup>-5</sup> moles/min of iPrCpEr, respectively. The growth was performed with plasma assisted deposition.

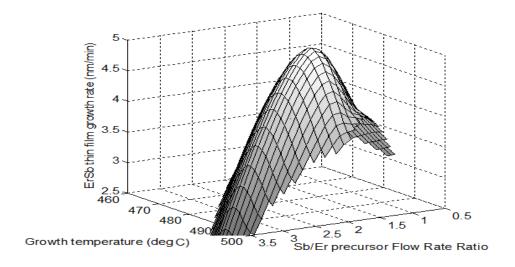

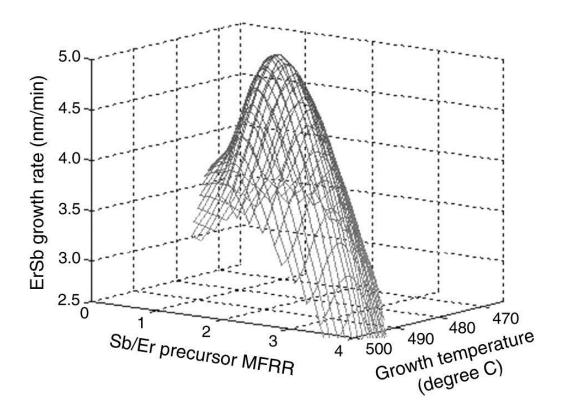

Fig. 2.1 shows the deposition rate of ErSb thin films on InSb(100). As clearly shown in Fig. 2.1, the growth rate of an ErSb thin film was found to be strongly dependent on both the growth temperature and the Er/Sb precursor flow rate ratio.

Fig. 2.1 indicates a sharp peak of .0833 nm/sec at a substrate temperature of 485 °C and a precursor V/III molar flow rate ratio of 2.25. An interesting feature is that the deposition rate falls off slower at lower precursor flow rates and higher growth temperatures while reducing faster at higher flow rates. The incorporation of Er on initial InSb surfaces in the high temperature regime in Fig. 2.1 may have been reduced by significant preferential desorption of Sb from InSb expected at temperatures close to the melting temperature of InSb, 527°C. In addition, the growth rate is most likely suppressed at lower precursor ratios because of a deficiency of Sb. Once formed the ErSb should be thermally stable within the growth temperatures investigated in Fig. 2.1 as the melting temperature of ErSb is above 2000 °C.

Figure 2.1 - ErSb thin film deposition rate on InSb(100) substrates.

#### Nanocomposite: ErSb nanostructures embedded in a ternary alloy host

After completing the calibration of ErSb thin film growth, we conducted epitaxial growth of nanocomposites in which ErSb nanostructures were embedded in either Zn-doped InGaSb or Zn-doped InSbAs host grown on InSb(100) substrates by low-pressure MOCVD. For both hosts, MOCVD growths were conducted at a substrate temperature of 485° C and a reactor pressure of 200 Torr. The precursors; trimethylindium, triethylantimony, and triethylgallium were used for the InGaSb:Zn host with molar flow rate ratio of 1.05:1.49:0.92, respectively. The precursors for the InSbAs:Zn host were trimethylindium, triethylantimony, and triethylarsine with a molar flow rate ratio of 1.05:1.49:0.89. Diethylzinc (Zn) was flowed at 1.93x10<sup>-6</sup> moles/min for both host materials. For both host materials, the erbium precursor, tris-

isopropylcyclopentadienyl-erbium, was injected to the reaction chamber at  $1.70 \times 10^{-4}$  moles/min.

#### **Results and Discussion**

#### ErSb thin films on InSb(100) substrates

Even at the highest growth rate, the grown ErSb thin films showed smooth surface morphology. Energy dispersive x-ray spectroscopy (not shown) confirmed that both Er and Sb were present in the thin films as well as the In and Sb from the substrate. The XRD profiles collected from the grown ErSb thin film on an InSb(100) substrate is shown in Fig. 2.2. Based on multiple diffraction peaks present in the InSb(100) substrate and InSb buffer layers, the buffer layers are likely to be polycrystalline, at best, highly-oriented textured films. As indicated in Fig. 2.2, we were unable to index some peaks even though these unidentified peaks did not impact relevant analyses. Two distinct peaks indexed ErSb(422) and ErSb(511) or ErSb(333) indicate that the ErSb thin film has two preferential growth orientations over [100] direction expected for a simple epitaxial growth on InSb(100) substrates. This suggests that the grown ErSb thin film has crystallographic registry with rotated and/or tilted with respect to the substrate as previously reported by Palmstrøm, et al.[18]. The polycrystalline nature of the buffer layer could also explain why ErSb takes on these unusual orientations.

To further investigate the microscopic crystal structure of the ErSb thin film we referred to the structure factor of the rock salt crystal structure to obtain

F(422)=280 and F(511)=34 [19-20], therefore; the intensity of the ErSb(422) peak should have been  $(280/34)^2$  = 67.8 times stronger than the ErSb(511) peak if two types of crystallites having these two planes as preferential orientations had the same volume fraction. In Fig. 2.2, we obtained the ratio of the two diffraction peak intensities; I(511)/I(422) =16670/826= 20.18, then we calculated the ratio of the number of unit cells that would result in the obtained ratio of the diffraction peak intensities. ; N(511)/N(422) ~37 [19]. Therefore the grown ErSb thin film has volume ratio of approximately 97.4 % ErSb(511) majority orientation and 2.6 % ErSb(422). These results indicates that, in an ErSb thin film grown on an InSb(100) substrate, ErSb(511) oriented phases dominate with the small fraction of ErSb(422) phases. In contrast, peaks associated with ErSb(n00) families did not appear in Fig. 2.2 suggesting that the grown ErSb thin film does not have a crystallographic registry typically expected from epitaxial thin films.

Figure 2.2 - XRD profile of an ErSb thin film grown on an InSb buffer layer on an InSb(100) substrate compared to that of an InSb(100) substrate.

Nanocomposite: ErSb nanostructures embedded in a ternary alloy host

The XRD profiles in Figs. 2.3 and 2.4 were collected from two types of nanocomposites; ErSb/InGaSb:Zn nanocomposite and ErSb/InSbAs:Zn nanocomposite, respectively. Embedded ErSb nanostructures did not appear on the XRD profiles presumably because the volume of each nanostructure spatially isolated from others is too small to make up sharp and intense diffraction peaks. While the grown InSb buffer layer are likely polycrystalline based on the XRD profile in Fig 2.2, it is possible a selection process of a dominant crystallographic orientation can induce epitaxial growth of a subsequent layer during the growth of the InGaAs/ErSb and InAsSb/ErSb nanocomposites[21]. From the (004) and (002) peak shifts in Figs. 2.3 and 4, alloy compositions were obtained for the In<sub>1-x</sub> Ga<sub>x</sub>Sb:Zn (x=0.975) and the InSb<sub>1-y</sub>As<sub>y</sub>:Zn (y=0.406). There is a possible compositional variation in the InGaSb host material that would be overlaid onto the contrast created by the host and embedded ErSb.

Figure 2.3 – XRD profile of the ErSb/In<sub>1-x</sub>Ga<sub>x</sub>Sb:Zn (x=0.975) nanocomposite.

Figure 2.4 – XRD profile of the ErSb/InSb<sub>1-y</sub>As<sub>y</sub>:Zn (y=0.406) nanocomposite.

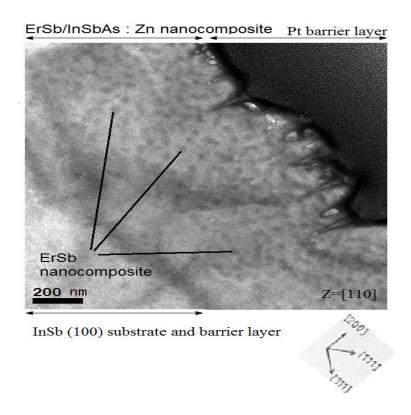

Cross-sectional TEM was used to analyze structural characteristics of the two types of nanocomposites; ErSb/InGaSb:Zn and ErSb/ InSbAs:Zn as shown in Fig. 2.5 and 6, respectively. The TEM images were collected with [110] zone-axis. Fig. 2.5 reveals that a group of 20-30 nm diameter ErSb nanocolumns or nanoslabs formed in the InGaSb:Zn host. These nanometer scale structures seen in Figure 2.5 could be "nanoslabs", long-range periodical structures such as ErSb/InGaSb lateral super lattice, or nanocolumns, or nanocolumns. However the nanocolumn arrangement has been reported elsewhere [22]. Most of the nanocolumns appear to be parallel to each other. This would indicate that the ErSb nanocomposites grew with preference to the InSb(100) substrate's crystallographic orientation. Fig. 2.6 shows a large number of ~30 nm diameter ErSb nanoparticles formed in the InAsSb:Zn host. The nanoparticles appear to be distributed throughout the sample. The formation of ErSb nanoparticles is likely to be spontaneous [8]. Higher concentrations of erbium along with a

relatively high erbium diffusion rate on the surface could have allowed larger ErSb nanoparticles to gradually grow into ErSb nanocolumns [22].

As described earlier, one of the key thermoelectric characteristics that directly influence ZT is thermal conductivity of a material. We used time domain thermoreflectance (TDTR) [23] to determine thermal conductivity of the two types of nanocomposites at room temperature. TDTR measurements provide total thermal conductivity (i.e., the sum of the lattice and the electronic contributions to thermal conductivity). Surface roughness on the Al layers affects the TDTR results through the variation in the Al layer thickness. The Al layers were measured with an acoustic echo in the TDTR measurement. This systematic error is estimated to be  $\pm$  5% reflecting the fact that the variation in the Al thickness. Other sources of error include the uncertainties of the laser beam sizes and the layers heat capacities. The thermal conductivities obtained for the ErSb/InSbAs:Zn at room temperature was 4.0± 0.6 W/mK. This is slightly lower than ~5 W/mK obtained for the InSbAs alloy limit at the composition we experimentally examined [24]. We also determined the thermal conductivity of the ErSb/InGaSb:Zn at room temperature to be  $6.7 \pm 0.8$ W/mK, which is slightly higher than the alloy limit of ~5 W/mK [25]. We would have seen observable reduction in the lattice contribution as theoretical predictions expect the nanocomposites to behave as mid to long-wavelength phonon scattering sources [13, 14] if the size of the embedded ErSb nanostructures were appropriately tuned.

and substrate Pt barrier layer

Figure 2.5– TEM image of the ErSb/InGaSb:Zn nanocomposite showing a group of 20 ~ 30 nm diameter nanocolumns or nanoslabs.

Figure 2.6 – TEM image of the ErSb/InSbAs:Zn showing a large number of 20 ~ 35 nm diameter nanoparticles.

# **Summary**

We demonstrated MOCVD growth of ErSb thin films on InSb(100) substrates. While the EDX analysis confirmed the grown ErSb thin films are made of all expected chemical elements, the XRD profile suggested that ErSb(511) or ErSb(333) phase dominates the thin film. We also demonstrated the growth of two types of nanocomposites; ErSb/In<sub>1-x</sub>Ga<sub>x</sub>Sb:Zn and ErSb/InSb<sub>1-y</sub>As<sub>y</sub>:Zn by lowpressure MOCVD. In the InGaSb:Zn host, the TEM analysis revealed that ErSb grew as nanopillars with ~500 nm length and 20-30 nm diameter almost vertical to the substrate while ErSb nanoparticles with diameter of ~30 nm were identified in the InSbAs:Zn host. The measured thermal conductivities of the two types of nanocomposites showed promising results, however further tuning (e.g., size and volume fraction of ErSb nanostructures) is necessary to validate the concept of nanocomposites within the context of thermoelectric materials and further investigation is required to address specific growth mechanisms that have resulted in the two types of ErSb nanostructures (i.e., nanocolumns/slabs and nanoparticles) depending on the types of hosts.

### Acknowledgment

This work was supported by DARPA/DSO, DoE, and ONR. We would like to thank Dr. Jae Hun Seol of UC Berkeley and Dr. Gilles Pernot of UC Santa Cruz for sample preparation and TDTR measurement. The authors are grateful to Dr. Stephan Kraemer, Dr. Hong Lu, and Prof. Art Gossard for the TEM imaging at UC Santa Barbara. The authors would also like to thank Hewlett-Packard Labs (Palo Alto, California) for their support and the use of equipment.

#### References

- [1] I. Terasaki, Y. Sasago, K. Uchinokura. (1997) doi: 10.1103/PhysRevB.56.R12685

- [2] G. Chen, T. Caillat, M.S. Dresselhaus, G. Dresselhaus, J.P. Fleurial. (2003) doi: 10.1179/095066003225010182

- [3] C. J. Vineis, A. Shakouri, A. Majumdar, and M. G. Kanatzidis. (2010) doi: 10.1002/adma.201000839

- [4] J. Lee, J. Wu, J. C. Grossman. (2010) doi: 10.1103/PhysRevLett. 104.016602

- [5] G. Mahan, S. Brian, J. Sharp. (1997) doi: 10.1063/1.881752

- [6] R. Venkatasubramanian, E. Siivola, T. Colpitts, and B. O'Quinn. (2001) doi:10.1038/35098012

- [7] J. Walachová, R. Zeipl, J. Zelinka and V. Malina. (2005) doi: 10.1063/1.2001755

- [8] J. M. Zide, D. O. Klenov, S. Stemmer, A. C. Gossard, G. Zeng, J. E. Bowers, D. Vashaee, and A. Shakouri. (2005) doi: 10.1063/1.2043241

- [9] H. Lu, P.G. Burke, A. C. Gossard, G. Zeng, A. T. Ramu, J. –H. Bahk, and J.E. Bowers. (2011) doi: 10.1002/adma.201100449

- [10] W. Kim, J. M. O. Zide, A. C. Gossard, D. O. Klenov, S. Stemmer, A. Shakouri, A. Majumdar. (2006) doi: 10.1103/PhysRevLett.96.045901

- [11] W. Kim, S. L. Singer, A. Majumdar, J. M. O. Zide, D. Klenov, A. C. Gossard, S. Stemmer. (2008) doi:10.1021/nl080189t

- [12] W. Kim, A. Majumdar. (2006) doi:10.1063/1.2188251

- [13] D. G. Cahill, K. Goodson, and A. Majumdar. (2002) doi:10.1115/1.1454111

- [14] D. G. Cahill, W. K. Ford, K. E. Goodson, G. D. Mahan, A. Majumdar, H. J. Maris, R. Merlin, and S. R. Phillpot. (2003) doi:10.1063/1.1524305

- [15] D. C. Driscoll, M. Hanson, C. Kadow, and A. C. Gossard. (2001) doi:10.1063/1.1355988

- [16] A. Guivarch, Y. Ballini, Y. Toudic, M. Minier, P. Auvray, B.Guenais, J.Caulet, B. Le Merdy, B. Lambert, A. Regreny. (1994) doi: 10.1063/1.356181

- [17] M. P. Hanson, D. C. Driscoll, C. Kadow, and A. C. Gossard. (2004) doi:10.1063/1.1639932

- [18] C. J. Palmstrom, Annu. Rev. Mater. Sci. 25, 389 (1995)

- [19] B.E. Warren, X-RAY DIFFRACTION. (Dover, New York, 1969), pp. 29-41

- [20] D. T. Cromer and J. B. Mann. (1968) doi:10.1107/S0567739468000550

- [21] K. Hiramatsu, et al., "Growth mechanism of GaN growth on sapphire with AlN buffer layer by MOCVD", J. Crystal Growth, **115**, 628, (1991).

- [22] T. E. Buehl, C. J. Palmstrøm, and A. C. Gossard (2011) doi: 10.1116/1.3549888

- [23] Y. K. Koh, S. L. Singer, W. Kim, J. M. O. Zide, H. Lu, D. G. Cahill, A. Majumdar, and A. C. Gossard. (2009) doi: 10.1063/1.3078808

- [24] S. Adachi. (2007) doi: 10.1063/1.2779259

- [25] Feser, J.. Scalable Routes to Efficient Thermoelectric Materials. Ph.D. dissertation, University of California, Berkeley, United States -- California. Retrieved July 14, 2011, from Dissertations & Theses @ University of California. (Publication No. AAT 3444631)

# Chapter 3

# Reflection absorption infrared spectroscopy analysis of the evolution of ErSb on InSb

Kate J. Norris<sup>a, b, 1</sup>, Vernon K. Wong<sup>a, b, 1</sup>, Takehiro Onishi<sup>a, 1</sup>, Andrew J. Lohn<sup>a, b</sup>, Elane Coleman<sup>c</sup>, Gary S. Tompa<sup>c</sup>, Nobuhiko P. Kobayashi<sup>a, b, ,</sup>

<sup>a</sup> Baskin School of Engineering, University of California Santa Cruz, Santa Cruz, CA, United States

b Nanostructured Energy Conversion Technology and Research (NECTAR),

Advanced Studies Laboratories, University of California Santa Cruz and NASA

Ames Research Center, Moffett Field, CA, United States

<sup>c</sup> Structured Materials Industries, Inc., Piscataway, NJ, United States

#### Abstract

We discuss an ex-situ monitoring technique based on glancing-angle infrared-absorption used to determine small amounts of erbium antimonide (ErSb) deposited on an indium antimonide (InSb) layer epitaxially grown on an InSb (100) substrate by low pressure metal organic chemical vapor deposition (MOCVD). Infrared absorption from the indium–hydrogen (In—H) stretching mode at 1754.5 cm<sup>-1</sup> associated with a top most surface of an epitaxial InSb layer was used to compare varying levels of surface coverage with ErSb. Among four samples of varying coverage of ErSb

deposition (7.2 to 21.5 monolayers), detected infrared absorption peaks distinct to In —H weakened as ErSb surface coverage increased. In the early stage of ErSb deposition, our study suggests that outermost indium atoms in the InSb buffer layer are replaced by Er resulting in increase in absorption associated with the In—H mode. Using this simple ex-situ technique, we show that it is possible to calibrate the amount of ErSb deposited atop each individual InSb substrate for depositions of few to tens of monolayers.

Keywords: ErSb; InSb; Infrared absorption; MOCVD; AFM; Evolution; Island; Surface coverage

#### Introduction

Combining nanometer-scale materials of particular chemical composition within a bulk host material of differing chemical composition often leads to unique modifications of the bulk host material's physical properties [1], [2] and [3]. This phenomenon has been especially studied to optimize the thermoelectric figure-of-merit ZT – an indicator of thermoelectric material performance – of a bulk thermoelectric material. A material's ZT can be enhanced with an increase in electrical conductivity or Seebeck coefficient, or with a decrease in thermal conductivity at a given temperature. Thermoelectric properties of ternary group III–V compound semiconductor host materials such as indium gallium antimonide (InGaSb) and indium antimony arsenide (InSbAs) are expected to be largely improved by embedding nanometer-scale semi-metallic particles such as erbium antimonide (ErSb)

nanoparticles into the aforementioned host materials [2]. The inclusion of these semi-metallic nanoparticles with an appropriate diameter creates desirable scattering centers for mid-wavelength phonons and provides additional charge carriers to the host material [3]. Therefore, the host material's thermoelectric figure-of-merit ZT is enhanced because of decreased thermal conductivity by the reduced contribution from lattice thermal conductivity and increased electrical conductivity at a given doping concentration by supplying additional charge carriers available for conduction. In addition, the Schottky barriers created at the interface between a host material and embedded semi-metallic nanoparticles can be tuned to alter the electron energy distribution around the Fermi level, which can result in an increased Seebeck coefficient [4].

It is predicted that an optimal nanoparticle size and volume density exist where thermal conductivity is minimized and electrical conduction properties of the host material are improved [1]. This prediction illuminates the need for accurate control of the size and volume density of ErSb nanoparticles deposited and formed atop an InSb surface. Unlike molecular beam epitaxy equipped with an in-situ growth monitoring system (e.g., reflection high-energy electron diffraction) that works in ultra-high vacuum, an in-situ growth monitoring system capable of estimating the presence of a small amount of a material on a growth front is not generally available in metal organic chemical vapor deposition (MOCVD). Yet, the great success in growing high-quality III–V compound semiconductors by MOCVD is indisputable. Therefore, we explore an ex-situ calibration technique, reflection absorption infrared

spectroscopy (RAIRS), based on glancing-angle infrared-absorption used to collect information on vibrational modes of chemical species that make up a surface and to obtain the amount of a small quantity of ErSb delivered onto InSb surfaces. RAIRS has proven to be a particularly useful technique in catalyst surface characterization for its ability to evaluate surface vibrational modes and resolve closely positioned absorption peaks due to high spectral resolution [5]. Metal nanoparticles such as Au supported by Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, FeO (111), CeO<sub>2</sub>, and TiO<sub>2</sub> thin films have been extensively studied with great success using RAIRS [6]. In addition to RAIRS, atomic force microscopy (AFM) is also used to further evaluate the surface morphology and concentration of ErSb nanoparticles formed on the InSb surface.

# **Experiment**

When exposed to vapor phase chemicals, solid surfaces can serve as a growth platform for crystal formation. ErSb deposited atop an InSb surface forms ErSb nanoparticles largely due to thermodynamic differences in the enthalpy of formation between the two materials [7]. Four samples with four different amounts of ErSb deposited on InSb surfaces were made on InSb (100) substrates by low-pressure MOCVD [8] and [9]. Prior to ErSb deposition, a 500 nm unintentionally doped InSb buffer layer was grown on an InSb(100) substrate, creating a smooth surface that served as a growth platform for ErSb deposition. Tris(isopropyl-cyclopentadienyl) erbium and trimethyl-antimony were used for the growth of ErSb on the InSb buffer layer. Shown in Fig. 3.1 is a deposition rate of ErSb plotted against temperature and

molar flow rate ratio between Sb and Er precursors. The figure shows a deposition rate peak of 4.9 nm/min at a temperature of 485 °C and precursor molar flow rate ratio of 2.25. Fig. 1 clearly shows that the ErSb deposition rate is very sensitivity to both temperature and molar flow rate ratio. The peak deposition rate shown in Fig. 3.1 was used for each of the four samples hosting different amounts of ErSb deposited on the InSb buffer layer. By varying the ErSb growth time, each sample yielded a specific amount of deposited ErSb ranging from 7.2 to 21.5 monolayers (ML).

Figure 3.1. The deposition rate of ErSb on InSb(100) surfaces plotted as a function of deposition temperature and the Sb/Er precursor molar flow rate ratio (MFRR). A peak deposition rate of 4.9 nm/min was obtained at 485 °C and molar flow rate ratio at 2.25.

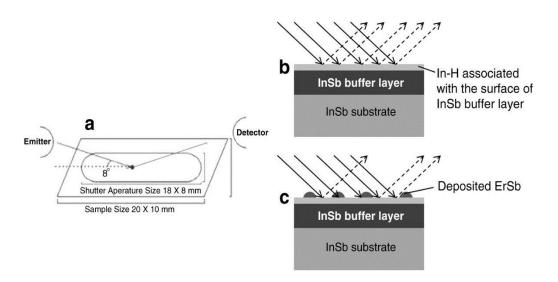

Fig. 3.2 illustrates the configuration of our RAIRS measurement. An infrared beam is collimated onto the surface of the sample at an approximate incident angle of 8°. A portion of the emitted infrared beam is absorbed by the vibrational modes associated with In—H bonds present on InSb surfaces partially covered by ErSb deposition. The remaining unabsorbed incident infrared light is reflected and collected by a detector. Detection of the reflected infrared spectrum reveals absorption peaks characteristic to the stretching mode of exposed In—H bonds present on the surface of the InSb buffer layer. In our RAIRS measurement, absorption spectra were obtained with respect to a reference sample that provided a surface of an InSb buffer layer without ErSb, therefore the RAIRS spectrum collected from the 0 ML sample shows no spectroscopic features associated with In—H bonds.

Figure 3.2. (a) Reflection absorption infra-red spectroscopy (RAIRS) configuration.

(b) and (c) Schematics showing that an increase in surface coverage of ErSb results in

a decrease in the number of detected In—H bonds exposed on the InSb buffer layer surface.

#### Results and discussion

Considerable amounts of hydrogen and hydrogen radicals are present in our low-pressure MOCVD growth environment. This is, in particular, expected because we use rather low V/III ratio, 15/1, for the growth of InSb in contrast to typical growth conditions for group III-arsenide and –phosphide for which much higher V/III ratio is used. Prior to ErSb deposition, In—H surface bonds are formed and characterized by their distinct vibrational modes. These vibrational modes are capable of infrared absorption in the 1660–1682 cm<sup>-1</sup> range reported for hydrogen-terminated indium phosphide (InP) surfaces [10] and 1754.5 cm<sup>-1</sup> range reported for the In—H stretching mode of InH<sub>3</sub>[11]. Based on this information, we studied chemical and morphological evolution of the surface of the InSb buffer layers upon ErSb deposition.

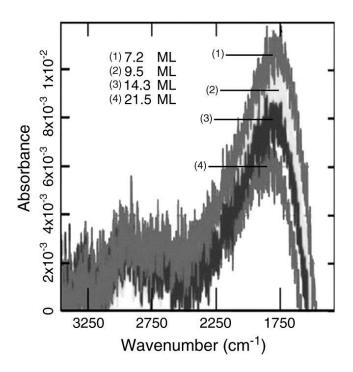

Fig. 3.3 shows RAIRS spectra obtained from the four samples with different growth times at a given deposition rate as calibrated in Fig. 3.2. Each sample is covered with a specific amount of ErSb ranging from 7.2 to 21.5 ML. In Fig. 3.4, the peak absorption intensity is plotted as a function of ErSb deposition showing linear correlation between these two quantities based on the trend seen in the range of ErSb deposition of 7.2–21.5 ML. It is apparent in Fig. 3.3 that as the amount of deposited ErSb increases and covers the InSb surface, the RAIRS absorption peaks associated

with the In—H bonds decrease. This simple picture, however, does not appear to describe the evolution from 0 ML (i.e., the reference sample) to 7.2 ML ErSb sample. As mentioned earlier, our RAIRS measurement is a comparative measurement done on the four InSb surfaces covered with different amounts of ErSb using an InSb surface with 0 ML ErSb deposition (i.e., the reference sample). If we assume that the surface of the reference sample was completely occupied by In—H bonds, the In—H absorption on the 7.2 ML ErSb sample would have shown reduced absorption, in other words, in our RAIRS measurement, the absorption of the 7.2 ML ErSb sample should have been recorded as "negative" absorption. Therefore, the positive absorption of the 7.2 ML ErSb sample seen in Fig. 3 suggests that the number of In\_\_\_ H bonds on the 7.2 ML ErSb sample is indeed larger than that on the reference sample. Qualitative description for the evolution from 0 ML to 7.2 ML ErSb sample is as follows; under our specific growth conditions, the surface of the InSb buffer layer (i.e., the reference sample with 0 ML ErSb) is covered predominantly with antimony. It is also highly likely that a small number of In—H bonds coexist. The heat of formation of Er\_Sb and In\_Sb is - 286.8 kJ/mol and - 34.1 kJ/mol, respectively [12] and [13], thus, upon the deposition of 7.2 ML ErSb, at least during the early stage of ErSb deposition, there is a strong thermodynamic driving force for indium atoms in the InSb buffer layer being replaced by Er to form ErSb. This replacement process creates more free indium atoms available to form additional In —H bonds on the 7.2 ML ErSb sample leading to the "positive" absorption as seen in Fig. 3. Further deposition of ErSb results in complete coverage of the InSb buffer

layer and the number of In—H bonds that participate in the absorption decreases as nominal thickness of ErSb increases. Also notable in Fig. 3.3 is the capability of RAIRS to clearly distinguish a 2.3 ML difference of deposition between a 9.5 ML ErSb sample and 7.2 ML ErSb sample.

Figure 3.3. RAIRS spectra of the four samples with varying coverage of ErSb on In

—H terminated InSb surfaces. Detected infrared absorption peaks distinct to the In—

H stretching mode at 1754.5 cm<sup>-1</sup> weakened as ErSb surface coverage increased.

Figure 3.4. Peak absorbance at 1754.5 cm<sup>-1</sup> of In\_H vibrational mode plotted as a function of ErSb deposition.

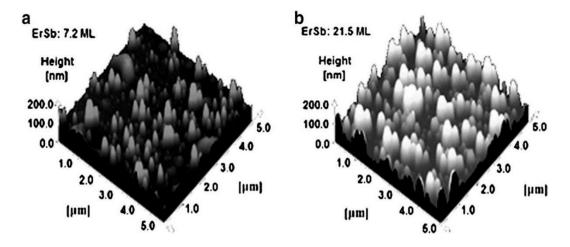

To further assess the small amount of ErSb deposition profiled by the RAIRS experiments, we evaluated the samples by atomic force microscopy (AFM). The two samples representing the upper and the lower bounds of ErSb deposition range we studied; 7.2 ML (a) and 21.5 ML (b) are shown in Fig. 3.5. Clearly seen are ErSb islands covering the surfaces of the InSb buffer layers. Surface coverage of ErSb was also obtained by AFM and plotted in Fig. 3.6. Extrapolating to 0 ML does not seem to traverse 0%, which may indicate the significance of the replacement process occurring between erbium and indium as described earlier. The 7.2 ML sample surface is approximately 29% covered and the 21.5 ML sample surface is approximately 55% covered. These AFM results are qualitatively consistent with the

RAIRS results and further qualify RAIRS as a competent ex-situ calibration technique for evaluating the deposition of few to tens of ML surface coverage.

Figure 3.5. AFM images collected on two of the samples with varying coverage of ErSb on In.—H terminated InSb surfaces. ErSb covers approximately 29% of the InSb surface for the 7.2 ML sample (a) and approximately 55% of the InSb surface for the 21.5 ML sample (b).

Figure 3.6. ErSb surface coverage on the InSb buffer layer.

RAIRS offers two main advantages over alternative characterization techniques. First, it can be performed in non-vacuum environments since it is an optical technique. Second, even at adsorption as low as 0.01%–2%, the RAIRS signals associated with the number of surface adsorbing molecules is generally recorded at relatively high resolution using modern FTIR spectrometers. Also, while the technique is not surface-specific, it can be shown theoretically that the best sensitivity for IR measurements on metallic surfaces is obtained using grazing-incidence reflection of the IR light [5]. Our studies take advantage of these benefits of RAIRS and use the reflection IR technique to measure mono-layer amounts of ErSb on In—H terminated InSb surfaces. The technique can also be used to measure mono-layer amounts of materials other than ErSb deposited on similar surfaces, making material deposition rates of differing materials easy to compare.

# **Summary**

In developing enhanced thermoelectric materials with embedded nanoparticles, it is necessary to monitor the size and volume density of grown nanoparticles. An optimal nanoparticle size and volume density may exist where the figure-of-merit ZT of the host thermoelectric material is optimized. Therefore, we discuss an ex-situ monitoring technique based on glancing-angle, infrared-absorption called RAIRS used to measure the amount of ErSb nanoparticles deposited atop InSb substrates. After exposing the surface of the InSb substrates to a shallow angle infrared beam, we

detected distinct absorption peaks associated with In—H surface bonds found on the substrate surface before and after ErSb deposition. The difference in the absorption peaks measured before and after ErSb deposition revealed the amount of ErSb deposited atop the substrate surface. We used AFM to visualize the surface topology of the InSb substrates with grown ErSb nanoparticles. Results from both RAIRS and AFM correlated well with one another, qualifying RAIRS as a competent ex-situ monitoring technique for evaluating the deposition of mono-layer amounts of ErSb on In—H terminated InSb surfaces.

#### Acknowledgments

This work is funded by the DARPA/DSO, ONR, and DoE. We are grateful to Hewlett-Packard Laboratories for their continuous support in our work. We thank the Materials Analysis for Collaborative Science (Univ. of California Santa Cruz and NASA Ames Research Center) for their facilities and assistance in our studies.

#### References

- [1] N. Mingo, et al., Nano Lett. 9 (2) (2009) 711.

- [2] J.M.O. Zide, et al., Thermoelectrics 2006 ICT'06 25th International Conference (2006).

- [3] M. Zebarjadi, et al., J. Electron. Mater. 38 (66) (2009).

- [4] D. Vashaee, A. Shakouri, Phys. Rev. Lett. 92 (10) (2004) [106103/1-4].

- [5] N. Sheppard, J. Erkelens, Appl. Spectrosc. 38 (4) (1984) 471.

- [6] E. Wilson, et al., J. Phys. Chem. C 114 (15) (2010) 6879.

- [7] T. Onishi, et al., Proceeding of MRS 2010 Spring Meeting Symposium DD Paper 250 Number 763327 (2010).

- [8] K.J. Norris, et al., J. Electron. Mater. 41 (5) (2012) 971.

- [9] K.J. Norris, et al., Proc SPIE 8106 (2011) 81060Q.

- [10] K. Raghavachari, et al., J. Am. Chem. Soc. 124 (50) (2002) 15119.

- [11] P. Pullumbi, et al., Chem. Phys. 185 (1994) 25.

- [12] K. Yamaguchi, et al., Mater. Trans. 35 (1994) 396.

- [13] B.D. Schultz, et al., Phys. Rev. B 73 (2006) 241407.

# Chapter 4

# Nanoimprint Lithography based Selective Area Growth of Indium Phosphide Nanopillar Arrays on Non single-crystal Templates

Kate J. Norris<sup>1,2</sup>\*, Junce Zhang<sup>1,2</sup>, David M. Fryauf<sup>1,2</sup>, Gary A. Gibson<sup>3</sup>, Steven J. Barcelo<sup>3</sup>, Nobuhiko P. Kobayashi<sup>1,2</sup>

<sup>1</sup>Baskin School of Engineering, University of California Santa Cruz, Santa Cruz, CA 95064 U.S.A

<sup>2</sup>Nanostructured Energy Conversion Technology and Research (NECTAR), Advanced Studies Laboratories, Univ. of California Santa Cruz – NASA Ames Research Center, Moffett Field, CA 94035

<sup>3</sup>Hewlett-Packard Laboratories, 1501 Page Mill Rd., Palo Alto, California 94304, USA

#### **ABSTRACT**

Selective area growth (SAG) of single crystalline indium phosphide (InP) nanopillars was demonstrated on an array of template segments composed of a stack of gold and amorphous silicon. The template segments were patterned by UV nanoimprint lithography on a silicon substrate covered with a natural oxide, and the SAG was achieved by metal organic chemical vapor deposition. Our SAG is different from conventional SAG in one critical aspect. In our SAG, growth of InP takes place selectively on a pre-defined array of template segments made of non-single crystal materials on a foreign substrate. The grown InP nanopillars were

studied for their structural, chemical and optical properties. The new SAG process is not limited to the specific materials such as InP nanopillars and silicon substrate used in this demonstration; our approach enables flexible and scalable nanofabrication using industrially proven tools and a wide range of semiconductors on various non-semiconductor substrates.

**Keyword:** A3. Metalorganic chemical vapor deposition; A1. Nanostructures; B1. Oxides; B2. Semiconducting III-V materials

#### Introduction

Arrays of semiconductor nanostructures fabricated by selective area growth (SAG) have gained interest as a platform for many applications [1-3]. Conventional SAG of semiconductor thin films achieved by growing materials within openings predefined by a mask on a single-crystal semiconductor substrate was demonstrated decades ago [4]. Conventional SAG has further evolved and is currently used for growing semiconductor nanostructures [5]. Two limitations of conventional SAG of semiconductor nanostructures are: (1) a single-crystal semiconductor substrate is required for epitaxial growth and (2) semiconductor nanostructures grown in an array are epitaxially connected to a single-crystal semiconductor substrate [5]. These two aspects restrict the choice of nanostructure and substrate materials and the design of devices that employ these nanostructures [6-8]. Use of single-crystal semiconductor substrates in conventional SAG rules out device fabrication on glass or metal substrates. To address this issue, a group has used a poly-Si substrate with a Silicon

dioxide mask to produce nanowires in selected areas to reduce the need for a single crystal substrate<sup>[9]</sup>. Furthermore, the fact that nanostructures in an array are all connected to a single-crystal substrate makes it difficult to electrically access a specific nanostructure within the array. In this paper, we present a new type of SAG of semiconductor nanostructures. Our SAG process is unique in that growth of nanostructures is initiated on an array of template segments formed on non-single crystal foreign substrates. Our SAG approach on non-crystal substrates could open the door for many applications not feasible through the conventional SAG. For example, individual nanostructures fabricated on an array of metallic template segments on an insulator substrate can be individually electrically addressed through the associated metallic template segment. Also, our method uses only proven, cost effective industrial techniques: nanoimprint lithography and metal organic chemical vapor deposition (MOCVD).

#### **Experiment**

Figure 4.1 illustrates the steps for growing an array of nanopillars on template segments. For this demonstration we chose three materials, silicon (Si) with native oxide, a stack of gold (Au) and amorphous silicon (a-Si), and indium phosphide (InP) for non-single crystal substrate, template segment, and nanopillar. The substrate preparation process utilized UV nanoimprint lithography (NIL) to transfer a pattern of template segments to a polymeric reverse tone mold using a custom-designed nanoimprint machine [10]. A four inch wafer mold was used to template the substrate with 130-150 nm diameter segments in a repeating hexamer pattern, as seen in Figure

2a. The NIL process depicted in Figure 4.1 is summarized as follows: (a) a mask is made on a four inch silicon wafer using deep UV lithography - this mask is subsequently used to make a daughter mold by NIL as shown in (b); (c) the daughter mold is used to imprint the array pattern into UV resist prepared on a PMMA layer based on the bilayer structure model [11] on a Si substrate with native oxide; UV irradiation forms a polymer mask shown over the PMMA. The UV resist is then etched using Reactive Ion Etching (RIE) to expose the pattern in PMMA, as shown in (d). A second RIE step removes the PMMA revealing the pattern on the substrate as shown in (e). Next, a layer of a-Si with a nominal thickness of 10 nm followed by a layer of Au with a nominal thickness of 5 nm are deposited by electron beam evaporation at normal incidence to form the a-Si/Au template segments in (f) and an acetone lift off process is used to leave the a-Si and Au segments, as shown in (g). Because the patterns can be precisely defined by the initial deep UV lithography and reproduced faithfully by NIL, an array of the template segments with an arbitrary geometrical pattern can be fabricated uniformly over a large area. Figure 1(h) illustrates the InP nanopillars grown from the a-Si/Au template segments. The processes described in Figure 4.1 were implemented on a four inch n-type silicon (100) wafer. A native silicon dioxide layer (~1.5nm thick) was intentionally left on the wafer, to allow later release of the InP nanopillars from the Si substrate, if desired, and to inhibit InP growth outside of the a-Si/Au template segments. While the native oxide suppressed the growth of InP in unwanted regions, it is certainly possible a small amount of InP was deposited in these regions. Metal organic chemical vapor

deposition (MOCVD) was used to grow InP nanopillars on the template segments. Typical growth conditions were; growth pressure 75 torr, V/III ratio of  $\sim$ 5 and temperature 505°C. The precursors for the MOCVD growth were ditertiary butylphosphine (DTBP) and trimethylindium (TMIn) at molar flow rates of 40.12 x10<sup>-5</sup>moles/min) and  $8.34x*10^{-5}$ moles/min, respectively, for 20 minutes.

Figure 4.1: Fabrication procedure for the nanopillars: (a) The fabrication of the nanopillar array silicon mold using deep UV lithography. (b) The making of the daughter mold using nanoimprinting, (c, d) The fabrication of the seed layers from the polymer d The fabrication of the seed layers from the polymer daughter mold using nanoimprinting. (e) the negative of the array pattern in pmma is left to (f) deposit the seed layer for growth using e-beam deposition, 10nm of amorphous Silicon and 5nm of gold, shown after lift off in (g). (h) After the substrate preparation shown in a-g the InP pillars are grown by mocvd.

#### **Results and Discussion**

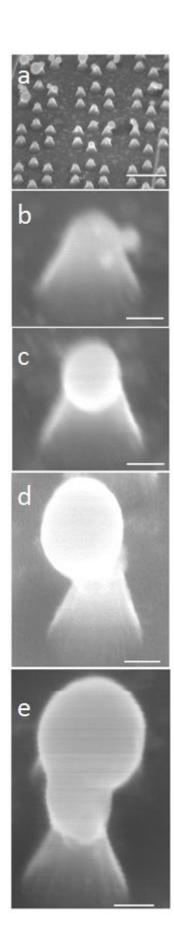

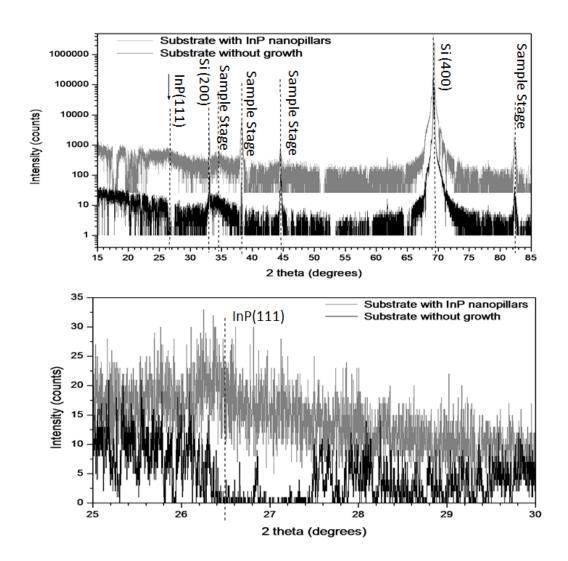

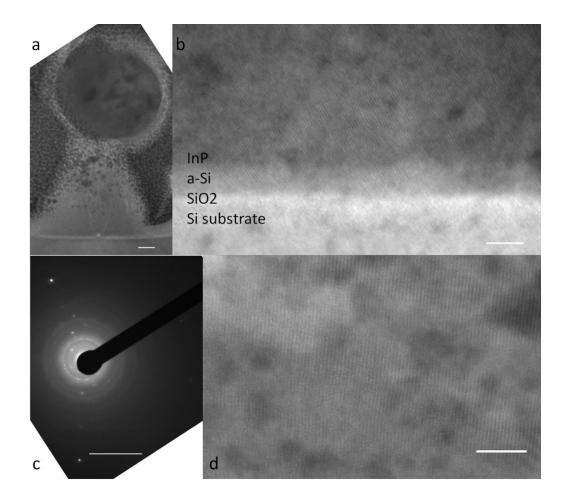

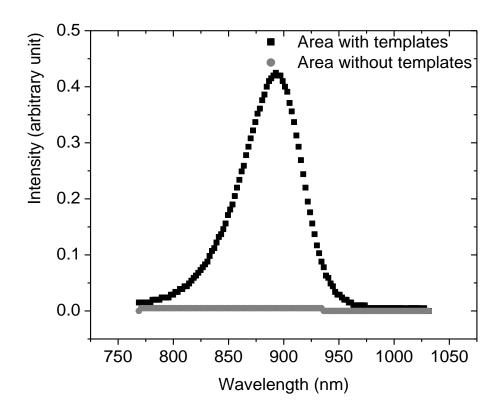

Figure 4.2 shows scanning electron microscope (SEM) images of representative InP nanopillars. Figure 4.2(a) shows InP nanopillars grown out of an array of hexamer clusters of a-Si/Au template segments and illustrates the consistency achieved. Shown in Figure 4.2(b)-(e) are magnified images of the pillars in different stages of growth. Figure 4.2(b) depicts the beginning stage of a nanopillar in the form of a circular cone with gold on top. Next a spherical tip begins to develop in 4.2(c), and expands in 4.2(d), which continues until the pillar resumes vertical growth with nearly constant radius as in 4.2(e). The majority of fully developed pillars shown in Figure 4.2(e) are ~300 nm in length with an average maximum diameter of ~140nm, of which the diameter can be tuned by controlling the size of the template segments [5]. The nanopillar height is a reflection of growth time and parameters, should a longer nanopillar be desired a longer growth time or an increase in temperature should be employed.

Figure 4.2: Scanning electron microscope (SEM) images of indium phosphide nanopillars grown by MOCVD a) showing the repeating pattern, scale bar is 500nm, and b-e) showing the progression of pillar growth, scale bar is 50 nm.