# **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Efficient Acceleration of Computation Using Associative In-memory Processing

#### **Permalink**

https://escholarship.org/uc/item/3939f48b

#### **Author**

YANTIR, Hasan Erdem

## **Publication Date**

2018

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Efficient Acceleration of Computation Using Associative In-memory Processing DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Hasan Erdem Yantır

Dissertation Committee: Professor Fadi J. Kurdahi, Chair Professor Ahmed M. Eltawil Professor Rainer Dömer

# **DEDICATION**

I would like to dedicate this dissertation to my family

for their invaluable support and unconditional love

throughout my life.

# TABLE OF CONTENTS

|                  |                | P                                           | age          |

|------------------|----------------|---------------------------------------------|--------------|

| LI               | ST (           | OF FIGURES                                  | $\mathbf{v}$ |

| LI               | ST (           | OF TABLES                                   | viii         |

| $\mathbf{A}^{0}$ | CKN            | OWLEDGMENTS                                 | ix           |

| $\mathbf{C}$     | URR            | ICULUM VITAE                                | x            |

| $\mathbf{A}$     | BST            | RACT OF THE DISSERTATION                    | xiii         |

| 1                | Intr           | oduction                                    | 1            |

|                  | 1.1            | Motivation                                  | 1            |

|                  | 1.2            | Background                                  | 4            |

|                  |                | 1.2.1 Computation Types                     | 4            |

|                  |                | 1.2.2 Non-volatile memories                 | 7            |

|                  | 1.3            | Contributions                               | 9            |

|                  | 1.4            | Thesis Overview                             | 11           |

| <b>2</b>         | $\mathbf{Ass}$ | ociative Processor                          | 12           |

|                  | 2.1            | Introduction                                | 12           |

|                  | 2.2            | Architecture                                | 15           |

|                  |                | 2.2.1 SRAM Associative Processor (SAP)      | 17           |

|                  |                | 2.2.2 Resistive Associative Processor (RAP) | 20           |

|                  | 2.3            | Instructions                                | 23           |

|                  |                | 2.3.1 Logical Instructions                  | 23           |

|                  |                | 2.3.2 Arithmetic Instructions               | 26           |

|                  | 2.4            | System Architectures                        | 34           |

|                  | 2.5            | Simulator                                   | 40           |

| 3                | Tra            | deoffs in APs                               | 42           |

|                  | 3.1            | Introduction                                | 42           |

|                  | 3.2            | Performance                                 | 43           |

|                  | 3.3            | Energy                                      | 46           |

|                  | 3.4            | Reliability                                 | 47           |

|                  |                | 3.4.1 Write Endurance                       | 47           |

|    | 3.5   | 3.4.2 Process Variations                   |     |

|----|-------|--------------------------------------------|-----|

| 4  | Apı   | proximate In-Memory Computing              | 60  |

| _  | 4.1   | Approximate Computing                      | 60  |

|    | 4.2   | Approximate Memristive In-memory Computing | 64  |

|    |       | 4.2.1 Bit Trimming                         | 64  |

|    |       | 4.2.2 Memristance Scaling                  | 66  |

|    |       | 4.2.3 Experimentation                      | 68  |

|    | 4.3   | A Hybrid Approach                          | 77  |

|    |       | 4.3.1 Motivation                           | 77  |

|    |       | 4.3.2 Design Flow                          | 80  |

|    |       | 4.3.3 Dynamic Approximation                | 81  |

|    |       | 4.3.4 Experimentation                      | 83  |

|    | 4.4   | Conclusion                                 | 89  |

| 5  | Met   | thods for Low-power APs                    | 92  |

|    | 5.1   | Low-Power SAP                              | 92  |

|    |       | 5.1.1 Motivation                           | 93  |

|    |       | 5.1.2 Low-Power Methodologies              | 96  |

|    |       | 5.1.3 Experimentation                      | 101 |

|    | 5.2   | Multi-compare for RAPs                     | 108 |

|    |       | 5.2.1 Motivation                           | 108 |

|    |       | 5.2.2 Methodology                          | 111 |

|    |       | 5.2.3 Evaluation                           | 112 |

|    | 5.3   | Conclusion                                 | 114 |

| 6  | Two   | o-dimensional AP                           | 115 |

|    | 6.1   | Introduction                               | 115 |

|    |       | 6.1.1 Motivation                           |     |

|    | 6.2   | Proposed Architecture (2D AP)              |     |

|    | 6.3   | Evaluation                                 | 122 |

|    | 6.4   | Experimentation                            | 124 |

|    |       | 6.4.1 Simulation Framework                 | 124 |

|    |       | 6.4.2 Energy & Performance                 | 127 |

|    |       | 6.4.3 Figure of Merit                      | 131 |

|    | 6.5   | Conclusion                                 | 132 |

| 7  | Cor   | nclusion & Future Work                     | 133 |

|    |       |                                            |     |

| Ri | hlios | granhy                                     | 136 |

# LIST OF FIGURES

|      |                                                                                       | Page  |

|------|---------------------------------------------------------------------------------------|-------|

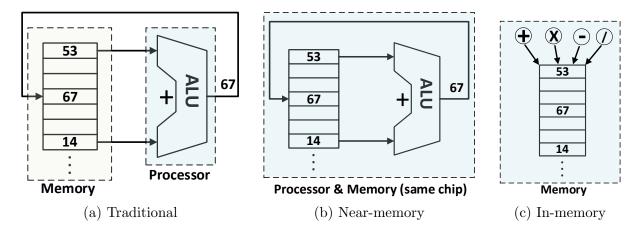

| 1.1  | Computation types with respect to the memory organization                             | 5     |

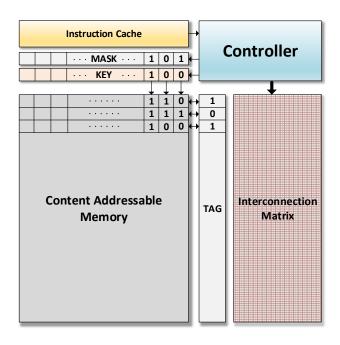

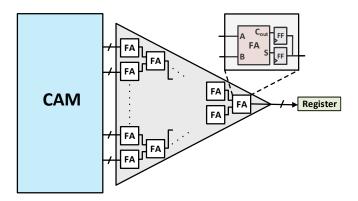

| 2.1  | General architecture of an associative processor                                      | 17    |

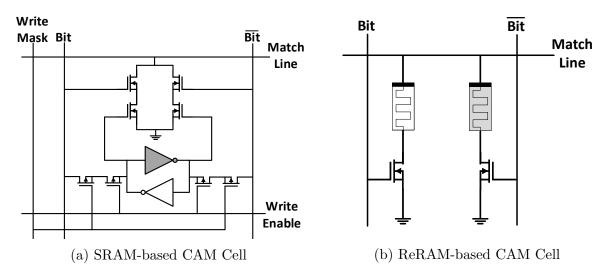

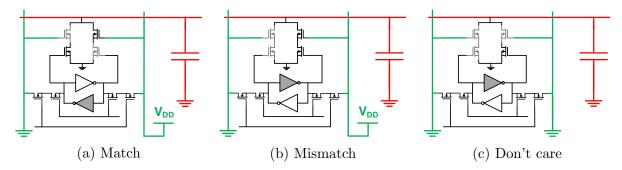

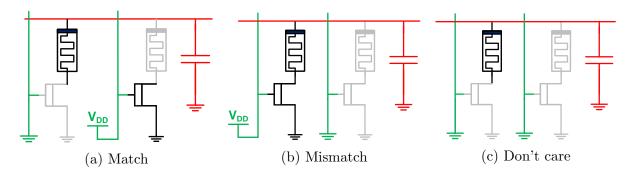

| 2.2  | CAM cell implementations                                                              | 18    |

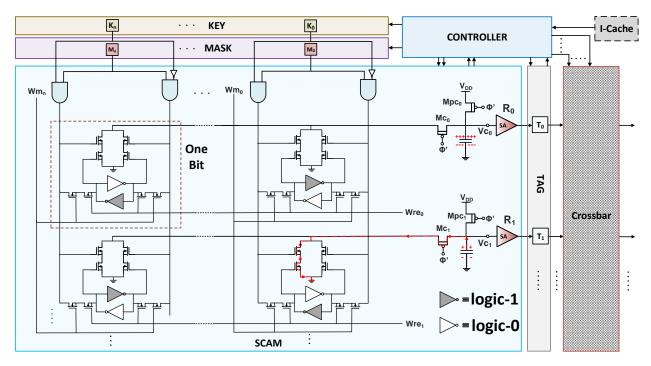

| 2.3  | Architecture of an SRAM-based Associative Processor (SAP)                             | 19    |

| 2.4  | Typical evaluation phases of a SAP cell for the match (a), mismatch (b), and          |       |

|      | don't care (c) states                                                                 | 20    |

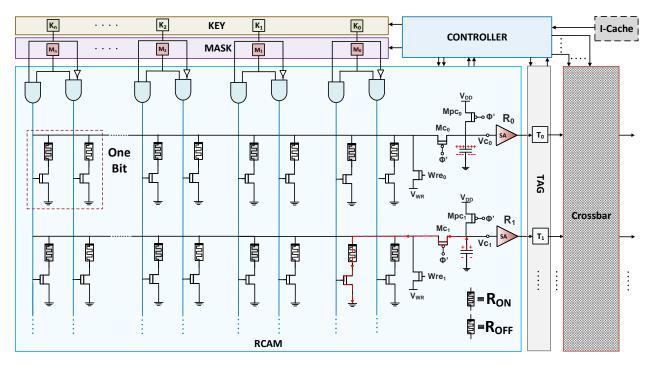

| 2.5  | Architecture of an ReRAM-based Associative Processor (RAP)                            | 21    |

| 2.6  | Typical evaluation phases of a RAP cell for the match (a), mismatch (b), and          |       |

|      | don't care (c) states                                                                 | 22    |

| 2.7  | AND operation on the AP                                                               | 24    |

| 2.8  | Spice simulation of two consecutive cycles in SAP and RAP respectively cor-           |       |

|      | responding to the AND operation in Figure 2.7                                         | 25    |

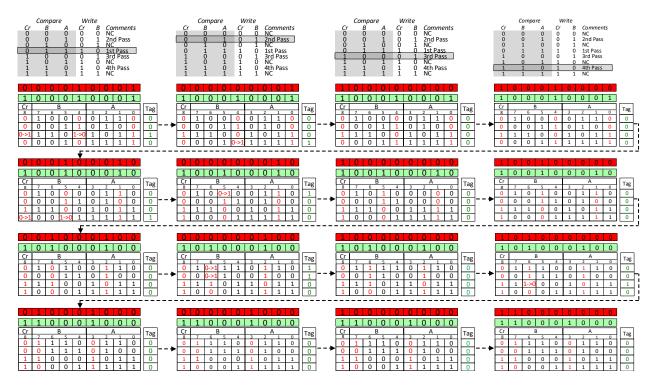

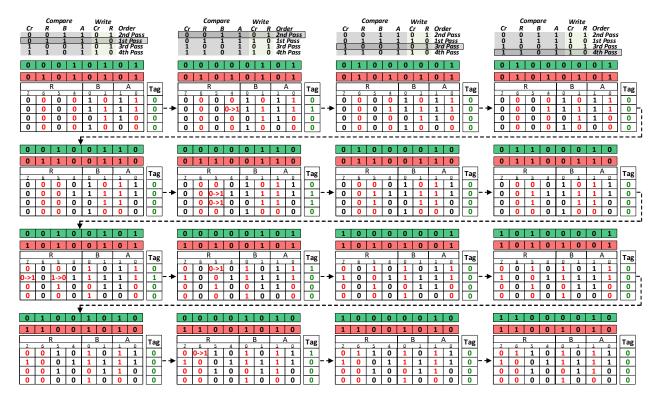

| 2.9  | Vector Add Operation. The sequence of compare and write operations are                |       |

|      | shown for a complete vector addition                                                  | 28    |

| 2.10 | Vector subtraction operation on 4-bit four number pairs. The sequence of              |       |

|      | compare and write operations are shown for a complete vector subtraction              | 29    |

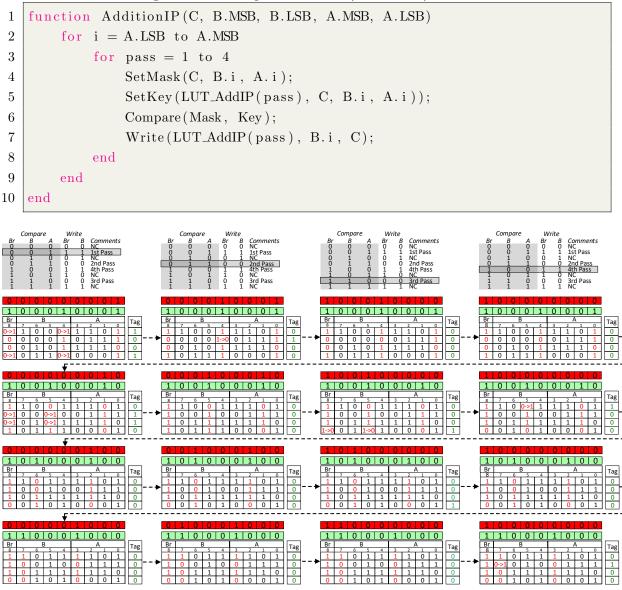

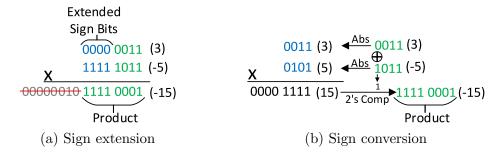

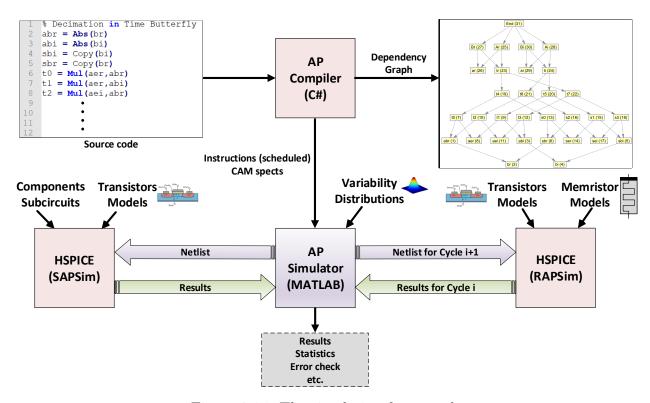

| 2.11 | Signed multiplication methods on the AP                                               | 33    |

| 2.12 | Vector multiplication operation. The sequence of compare and write opera-             |       |

|      | tions are shown for a complete unsigned vector multiplication                         | 35    |

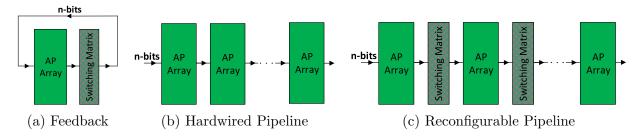

|      | System-level AP Architectures                                                         | 35    |

|      | Interconnection matrix between the two CAMs                                           | 36    |

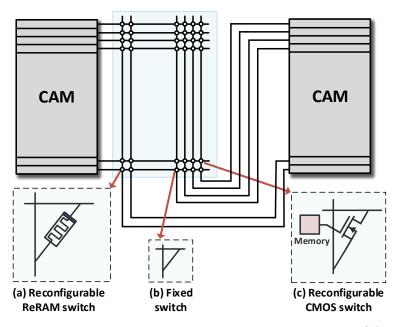

| 2.15 | The simulation framework                                                              | 40    |

| 3.1  | The comparison of CPU, GPU, and AP architectures                                      | 43    |

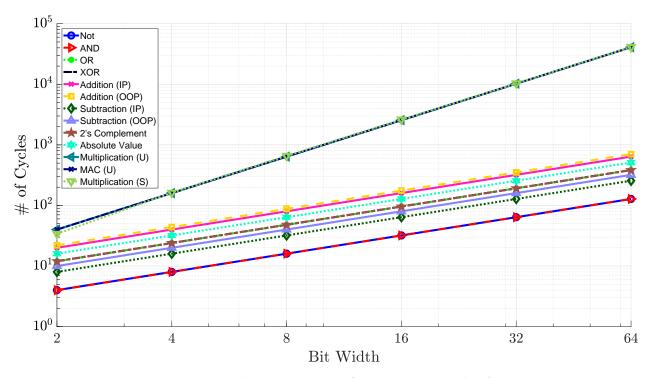

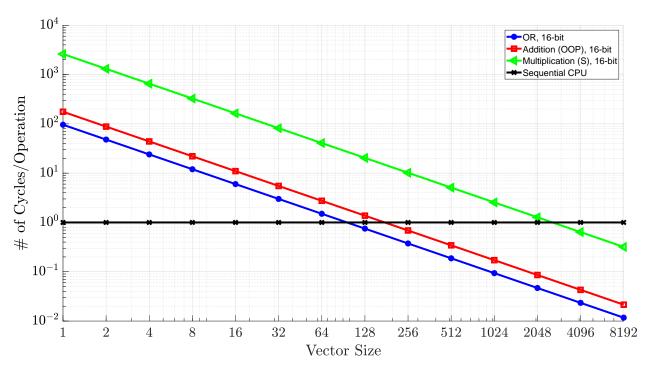

| 3.2  | The comparison of operations on the AP                                                | 45    |

| 3.3  | The comparison of a sequential processor with some AP operations on 16-bit            | 10    |

| 0.0  | operands                                                                              | 45    |

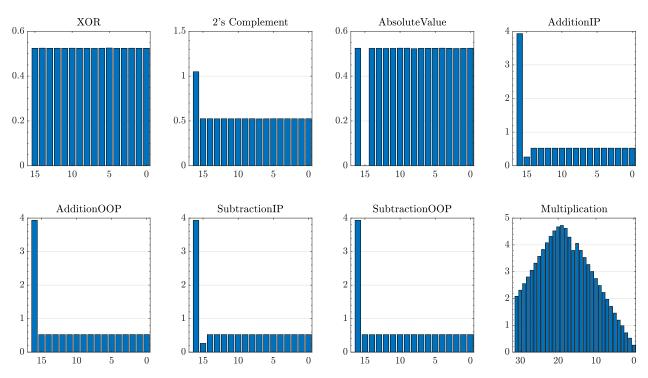

| 3.4  | Column write density of the fundamental operations on the AP                          | 47    |

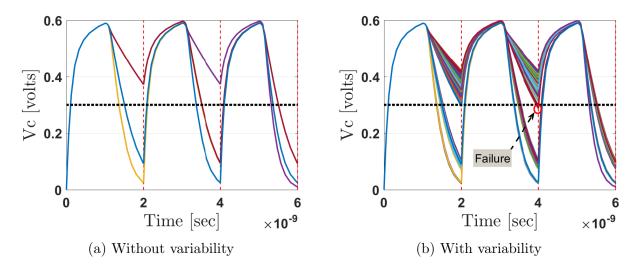

| 3.5  | Effect of process variation on Vc                                                     | 51    |

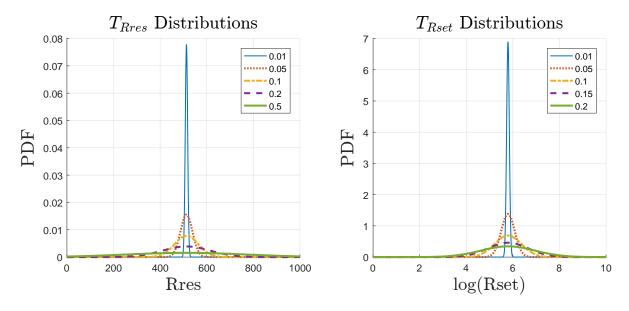

| 3.6  | The distributions for Rres and Rset tolerances                                        | 52    |

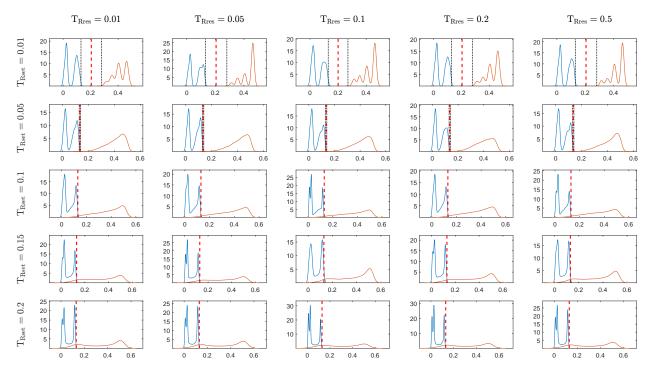

| 3.7  | Kernel densities with respect to tolerances and obtained $V_{th}s$ (red vertical line |       |

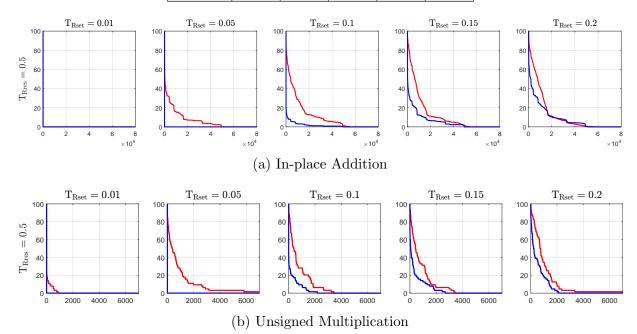

| 3.8  | The cumulative distribution functions (CDFs) of deviation in the results. (The        | -,    |

|      | red line corresponds to untrained results and the blue one is the trained result      | s) 55 |

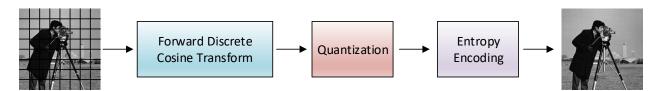

| 3.9  | JPEG Block Diagram                                                                    | 57    |

| 3.10         | Comparison of JPEG results for $T_{Rset} = 0.01$ and $T_{Rres} = 0.5$                                                       | 58  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

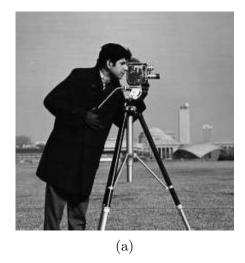

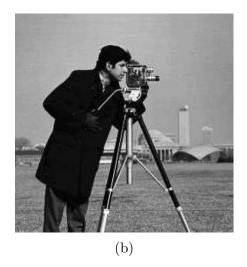

| 4.1          | Full (a) and approximate (b) compressed images where PSNRs are 31.74 and 31.52 respectively                                 | 61  |

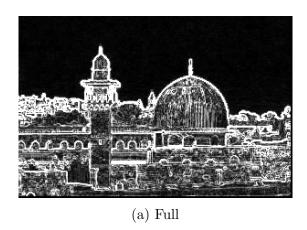

| 4.2          | Full (a) and approximate (b) outputs of the sobel filter algorithm on a image where PSNR is 33.17 for the approximate image | 62  |

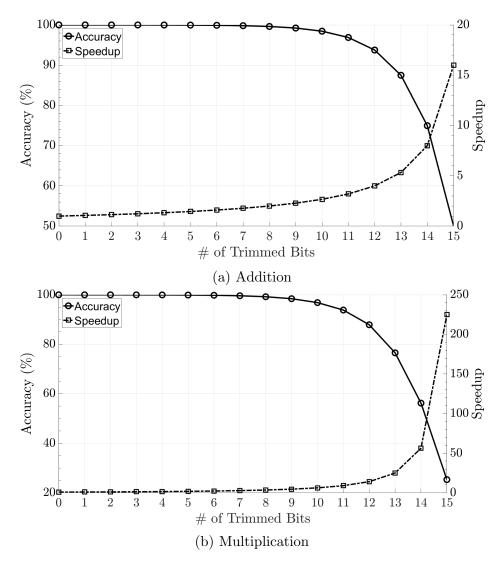

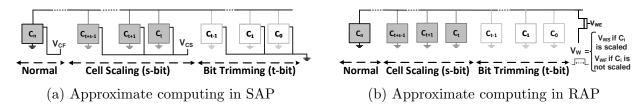

| 4.3          | Bit trimming in the MAP                                                                                                     | 64  |

| 4.4          | Number of trimmed bits vs. accuracy & speedup for the addition and multi-                                                   |     |

|              | plication operations in the RAP                                                                                             | 65  |

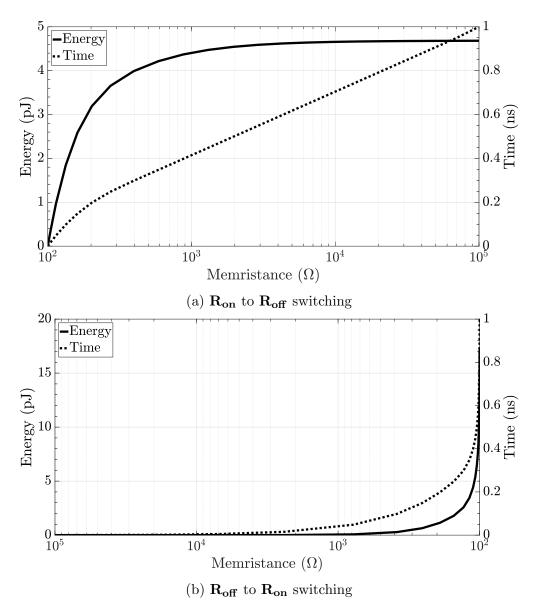

| 4.5          | An example case showing memristance-energy and memristance-time relations                                                   | 0.  |

| 1 C          | for switching the memristor in [114] between Roff (100 k $\Omega$ ) and Ron (100 $\Omega$ )                                 | 67  |

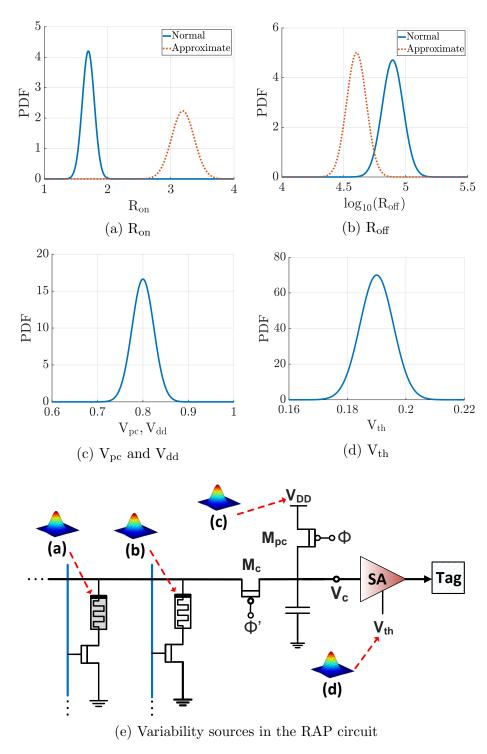

| $4.6 \\ 4.7$ | Variability sources and variations in RAP                                                                                   | 70  |

| 4.1          | and right bars correspond to energy and time respectively for each benchmark                                                | 71  |

| 4.8          | Comparison of approximation methods on RAP, ASIC, CPU, and GPU plat-                                                        | ' 1 |

|              | forms with different benchmarks with 10% maximum quality degradation                                                        | 74  |

| 4.9          | Area comparison of RAP+BT & Axilog[180]                                                                                     | 76  |

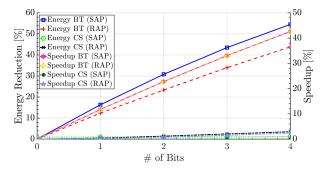

| 4.10         | The effect of bit trimming and cell scaling on SAPs and RAPs                                                                | 78  |

|              | Hybrid approximate computing in associative processors (APs)                                                                | 79  |

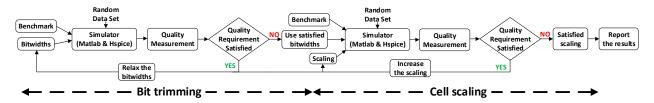

|              | The design flow for approximate AP systems                                                                                  | 80  |

|              | Dynamic cell scaling in APS                                                                                                 | 81  |

|              | Dynamic approximate computing in SAPs                                                                                       | 83  |

| 4.10         | platforms with different benchmarks with 10% maximum quality degradation                                                    | 90  |

| 5.1          | Waveform of single-bit subtraction which corresponds to the second row of                                                   | 0.4 |

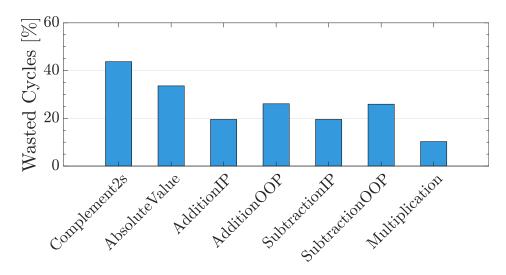

| 5.2          | Figure 2.10                                                                                                                 | 94  |

| 0.2          | ations in the AP                                                                                                            | 95  |

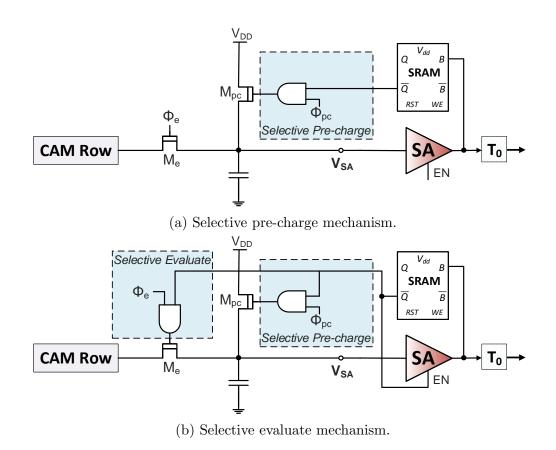

| 5.3          | Selective pre-charge (a) and evaluate (b) mechanisms for low-power AP                                                       | 97  |

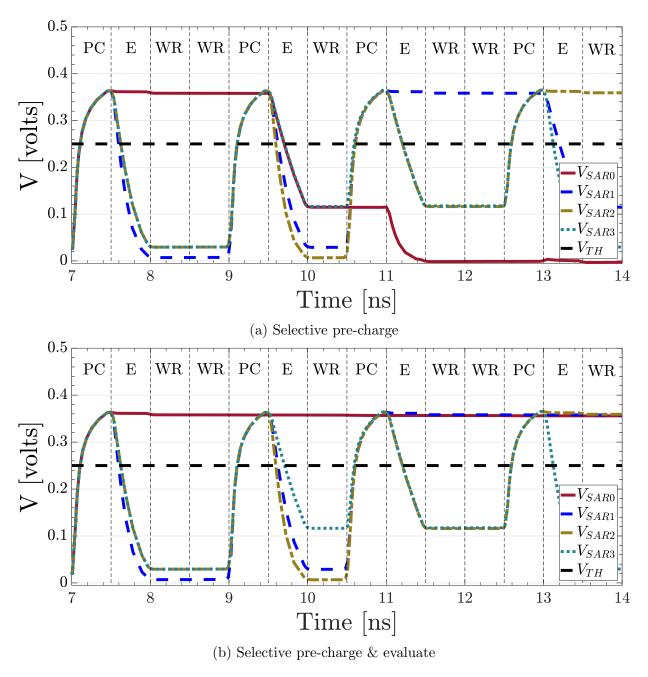

| 5.4          | Waveform of single-bit addition which corresponds to the second row of Figure                                               |     |

|              | 2.10 when selective pre-charge (a) and evaluate (b) mechanisms enabled                                                      | 99  |

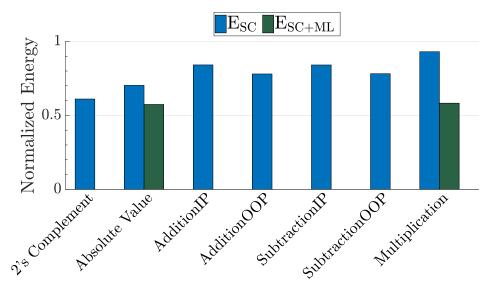

| 5.5          | Energy reduction in arithmetic operations when selective compare and modi-                                                  |     |

|              | fied LUTs are enabled                                                                                                       | 103 |

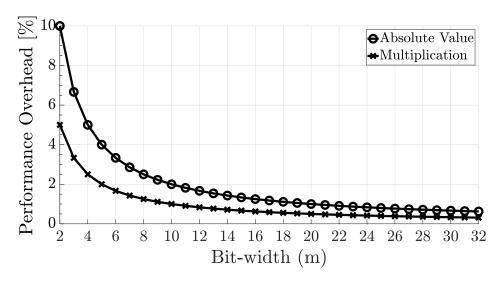

| 5.6          | The performance overhead in 2's complement and multiplication due to the modified LUTs                                      | 103 |

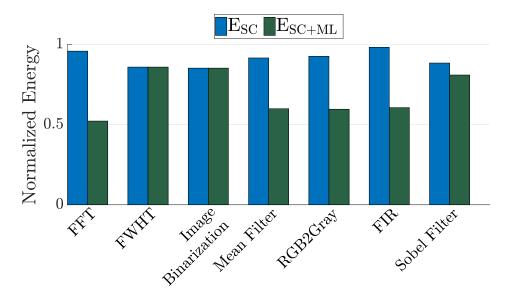

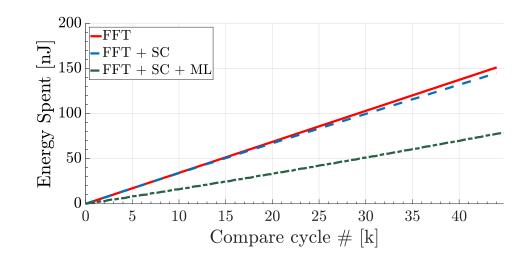

| 5.7          | Normalized energy consumption of the benchmarks when selective compare                                                      | 100 |

| J.,          | and modified LUTs are enabled                                                                                               | 105 |

| 5.8          | Energy consumption during the FFT benchmark runs of all three cases                                                         | 105 |

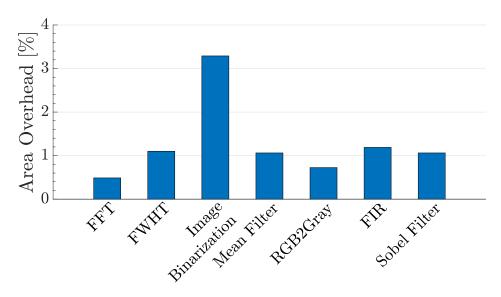

| 5.9          | Area overhead of the benchmarks when selective compare and modified LUTs                                                    |     |

|              | are enabled                                                                                                                 | 106 |

| 5.10         | ,                                                                                                                           |     |

|              | The waveform for the noise margin of the three cases during a compare cycles                                                |     |

| 5.12         | Noise margins for each case and the maximum number of compared columns                                                      | 112 |

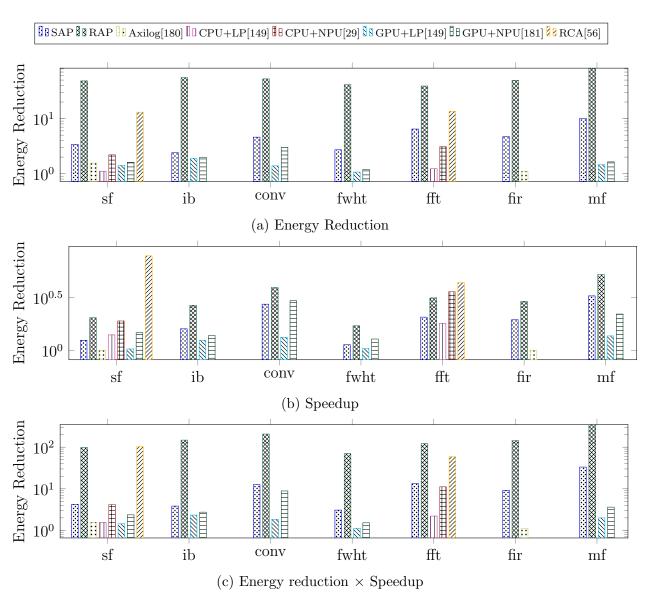

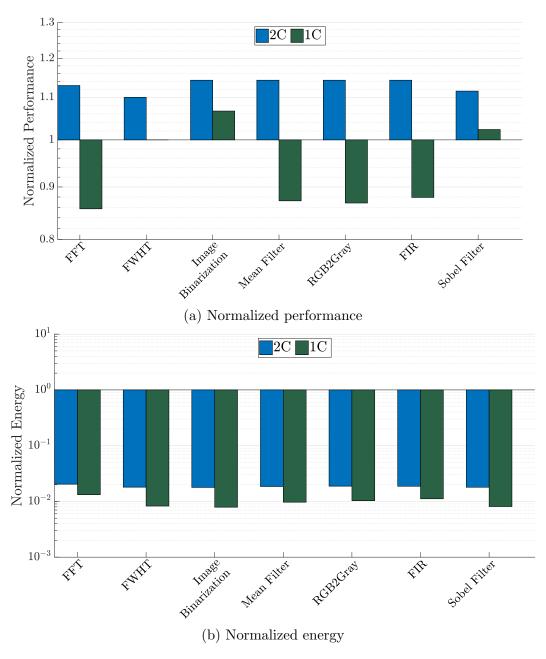

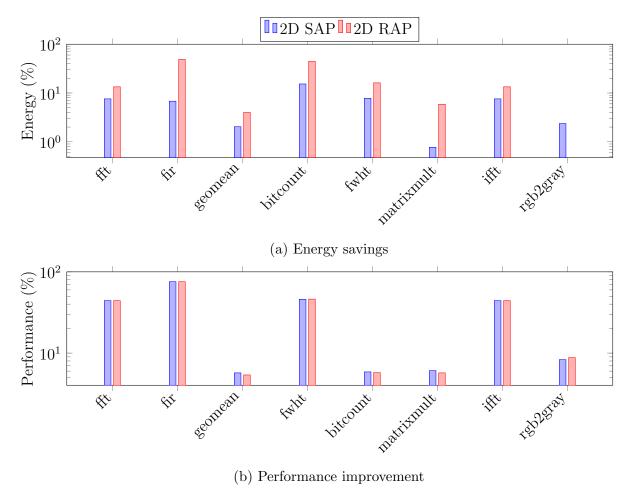

| 5.13 | The normalized performance and energy results of the benchmarks for 2-  |     |

|------|-------------------------------------------------------------------------|-----|

|      | column and 1-column compare cases                                       | 113 |

|      |                                                                         |     |

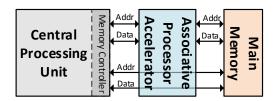

| 6.1  | Overall system architecture with AP accelerator                         | 116 |

| 6.2  | 1D AP with Adder Tree                                                   | 116 |

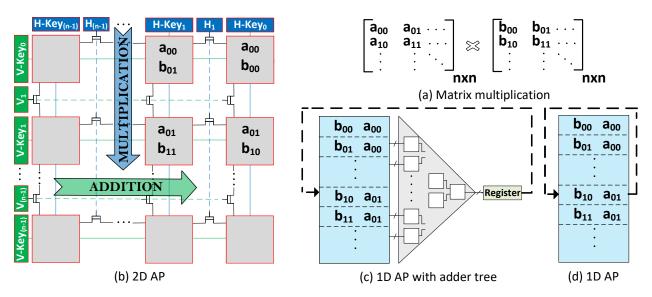

| 6.3  | Proposed 2D associative processor (AP) architecture                     | 118 |

| 6.4  | $n \times n$ matrix multiplication on 2D AP, 1D AP w/o adder tree       | 121 |

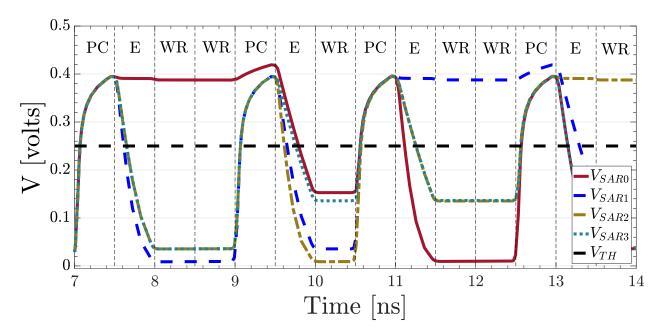

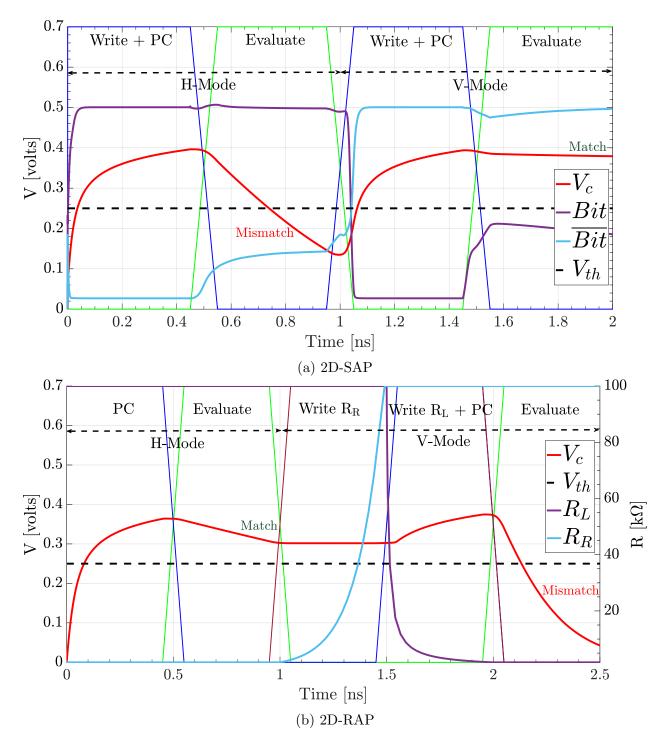

| 6.5  | Spice simulation of two consecutive write and compare cycles in H and V |     |

|      | mode respectively in 2D AP                                              | 125 |

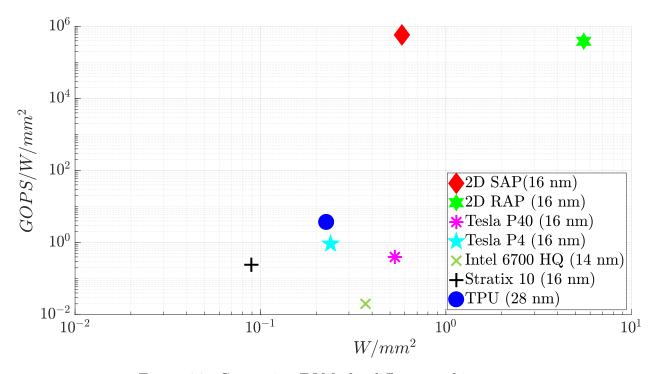

| 6.6  | 2D SAP and 2D RAP performance improvement and energy savings vs. 1D     |     |

|      | SAP and 1D RAP, respectively                                            | 128 |

| 6.7  | Comparing FOMs for different architectures                              | 131 |

|      |                                                                         |     |

# LIST OF TABLES

|                                               |                                                                                                                                                                                                                                                                               | Page                                          |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1.1                                           | ITRS report for emerging memory technologies [66] and their comparison with traditional memories based on recent literature [45, 171, 70, 106]                                                                                                                                | 8                                             |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6        | Logical operations and their LUTs  LUT for addition and subtraction  LUT for multiplication  LUT for 2's complement  LUT for absolute value  Reduction tree and switching matrix comparison                                                                                   | 25<br>27<br>32<br>32<br>32<br>39              |

| 3.1<br>3.2<br>3.3<br>3.4                      | Running time and area evaluation of primitive AP operations/instructions . Energy consumption results for both SAP and RAP cells                                                                                                                                              | 44<br>47<br>55<br>56                          |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | The evaluated benchmarks, their platforms, and quality metrics from [179]. Cases for memristance scaling and their corresponding energy and timing result. The evaluated benchmarks, their platforms, and quality metrics from [179]. Cell scaling in AP for both SAP and RAP | 72<br>84<br>85<br>87                          |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Modified LUT for the multiplication                                                                                                                                                                                                                                           | 100<br>100<br>101<br>102<br>104<br>106<br>110 |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Theoretical complexity of various kernels where complexity order between the cells is green < blue < red                                                                                                                                                                      | 122<br>126<br>127                             |

| 0.5                                           | The evaluated benchmarks, then leatures, and the provided input                                                                                                                                                                                                               | 141                                           |

#### ACKNOWLEDGMENTS

All praise be to Allah, Lord of the worlds.

This dissertation would not have been possible without the help of so many people in so many ways. It is the product of my educational, professional, and personal attainments through my discussions with people.

I would like to express my deepest gratitude to my advisor, Professor Fadi J. Kurdahi, who provided me with the guidance and support in all aspects of my research at UC Irvine and even after UC Irvine. I learned a lot from his guidance and valuable suggestions. His support and courage in the worth of this research especially during the many difficult times were an invaluable motivation source for me.

I would also like to thank my Co-advisor Prof. Ahmed M. Eltawil. The insightful discussions with him opened several prospects to me and enriched my research contributions from different fields. He always promoted my work and encouraged me in going further cordially.

I would like to thank Prof. Rainer Doemer for being in my committee. Even though I could not find an opportunity to conduct research with him, my observations on his professional as well as friendly academic life will be a good guider on my overall academic life.

I would like to thank Prof. Smail Niar for directing me in the hard paths of the academic life as like an academic coach.

I would also acknowledge the support from my research colleagues, especially Mohammed Fouda, Dr. Wael Mahmoud Elsharkasy, Ayoub Neggaz, Dr. Ahmed Nassar, and Dr. Ihsen Alouani.

I would also like to thank all my other colleagues and friends, especially Rasul Torun, Dr. Enver Adas, Dr. Volkan Gunes, Atila Ucar, Dr. Ahmet Tekin, Yasir Ak, and Mert Bayer for making all those years at Irvine a great and enjoyable experience while away from the family.

I would like to thank IEEE and ACM for granting me the permission to use my own publications as part of this dissertation.

Finally, and most importantly, I would like to express my deepest gratitude to my parents and my wife, who gave me encouragement and supported me cordially with their best wishes. Their guidance and constant support have always helped me to overcome the challenges that I have faced throughout my life. Therefore, I can never thank them enough for all they have done for me.

# CURRICULUM VITAE

### Hasan Erdem Yantır

#### **EDUCATION**

| Ph.D. in Electrical and Computer Engineering          | 2018                            |

|-------------------------------------------------------|---------------------------------|

| University of California, Irvine                      | Irvine, CA                      |

| M.Sc. in Computer Engineering<br>Boğaziçi University  | <b>2014</b> İstanbul, Turkey    |

| B.Sc. Minor in Electrical and Electronics Engineering | <b>2011</b>                     |

| Yeditepe University                                   | İstanbul, Turkey                |

| B.Sc. in Computer Engineering Yeditepe University     | <b>2011</b><br>İstanbul, Turkey |

#### RESEARCH EXPERIENCE

| Graduate Research Assistant      | 2014 – 2018      |

|----------------------------------|------------------|

| University of California, Irvine | Irvine, CA       |

| Graduate Research Assistant      | 2011–2014        |

| Boğaziçi University              | İstanbul, Turkey |

### TEACHING EXPERIENCE

| Teaching Assistant University of California, Irvine                                                           | 2015–2018<br>Irvine, California |

|---------------------------------------------------------------------------------------------------------------|---------------------------------|

| EECS 113 - Processor Hardware/Software Interfaces EECS 152B - Digital Signal Processing Design and Laboratory |                                 |

| EECS 22 - Advanced C Programming                                                                              |                                 |

EECS 20 - Assembly Language and C Programming EECS 12 - Introduction to Programming

#### REFEREED JOURNAL PUBLICATIONS

Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "A two-dimensional associative processor." *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2018

Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "Approximate memristive in-memory computing." ACM Transactions on Embedded Computing Systems (TECS), 16(5s):129, 2017

Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "A hybrid approximate computing approach for associative in-memory processors." *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, 2018 (Under Review)

Hasan Erdem Yantır, Ahmed M Eltawil, Smail Niar, and Fadi J Kurdahi. "Power optimization techniques for associative processors." *Journal of Systems Architecture, Elsevier*, 2018 (Under Revision)

Rana A Abdelaal, Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "Optimizing energy through adaptive bit width adjustment on resistive associative processors." *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2018 (Under Review)

Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "A 1K In-memory Fast Fourier Transform Processor." *IEEE Design & Test*, 2018 (Under Preparation)

Bashar Romanous, Hasan Erdem Yantir, Walid Najjar, Ahmed M. Eltawil, ad Fadi J. Kurdahi. "Accelerating Convolutional Neural Networks (CNNs) using Associate In-memory Processor. ACM TACO, 2018 (Under Preparation)

#### REFEREED CONFERENCE PUBLICATIONS

Mohamed Ayoub Neggaz, Hasan Erdem Yantır, Smail Niar, Ahmed M Eltawil, and Fadi J Kurdahi. "Rapid in-memory matrix multiplication using associative processor." *In Design, Automation Test in Europe Conference Exhibition (DATE)*, 2018, March 2018

Wael M Elsharkasy, Hasan Erdem Yantır, Amin Khajeh, Ahmed M Eltawil, and Fadi J Kurdahi. "Efficient pulsed-latch implementation for multiport register files: work-in-progress." In Proceedings of the 2017 International Conference on Compilers, Architectures and Synthesis for Embedded Systems Companion, page 5. ACM, 2017

Hasan Erdem Yantır, Mohammed E Fouda, Ahmed M Eltawil, and Fadi J Kurdahi. "Process variations-aware resistive associative processor design." *In Computer Design (ICCD)*, 2016 *IEEE 34th International Conference on*, pages 49-55. IEEE, 2016

Hasan Erdem Yantır and Arda Yurdakul. "An efficient heterogeneous register file implementation for fpgas." In Parallel & Distributed Processing Symposium Workshops (IPDPSW), 2014 IEEE International, pages 293-298. IEEE, 2014

Gorker Alp Malazgirt, Hasan Erdem Yantır, Arda Yurdakul, and Smail Niar. "Application specific multi-port memory customization in fpgas." In Field Programmable Logic and Applications (FPL), 2014 24th International Conference on, pages 1-4. IEEE, 2014

Hasan Erdem Yantır, Salih Bayar, and Arda Yurdakul. "Efficient implementations of multi-pumped multi-port register files in fpgas." In Digital System Design (DSD), 2013 Euromicro Conference on, pages 185-192. IEEE, 2013

Hasan Erdem Yantır, Ahmed M Eltawil, and Fadi J Kurdahi. "A Systematic Approach for Low-Power & High Endurance Resistive Associative Processor Design." *ASP-DAC*, 2019 (Under Preparation)

Hasan Erdem Yantr, Ahmed M Eltawil, and Fadi J Kurdahi. "APSim: An Open-Source Associative Processor Simulator with Benchmark Suite" ASP-DAC, 2019 (Under Preparation)

#### **SOFTWARE**

APSim https://github.com/hasaney/APSim

A cycle-accurate Associative Processor Simulator

### ABSTRACT OF THE DISSERTATION

Efficient Acceleration of Computation Using Associative In-memory Processing

By

#### Hasan Erdem Yantır

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2018

Professor Fadi J. Kurdahi, Chair

The complexity of the computational problems is rising faster than the computational platforms' capabilities. This forces researchers to find alternative paradigms and methods for

efficient computing. One promising paradigm is accelerating compute-intensive kernels using in-memory computing accelerators since memory is the major bottleneck that limits

the amount of parallelism and performance of a system and dominates energy consumption in computation. Leveraging the memory intensive nature of big data applications,

an in-memory-based computation system can be presented where logic can be replaced by

memory structures, virtually eliminating the need for memory load/store operations during

computation. The massive parallelism enabled by such a paradigm results in highly scalable

structures.

The present thesis is studied against this background. The objective is to conduct a broad perspective research on in-memory computing. For this purpose, associative computing architectures (i.e., Associative Processors, or AP) are built by both traditional (SRAM) and emerging (ReRAM) memory technologies together with their corresponding software frameworks. For ReRAM-based APs, the reliability concerns coming with the emerging memories are resolved. Architectural innovations are developed to increase the energy efficiency. Furthermore, approximate computing approach is introduced for APs to perform efficient/low-

power approximate in-memory computing for the tasks which can tolerate some accuracy lost. The works also propose a novel two-dimensional in-memory computing architecture to cope with the existing deficiencies of the traditional one-dimensional AP architectures.

# Chapter 1

# Introduction

### 1.1 Motivation

The explosive growth of the Internet coupled with readily available powerful computing platforms has created the perfect conditions for wide-spread adoption. It is widely recognized

that the most significant obstacle to the transformative vision of ubiquitous access to computing resources is the power/energy consumption barrier, limiting the extent, scope and

longevity of billions of computing devices. Over the last decade, there has seen a sharp

increase in the need for ultra-efficient computation platforms that necessitates robust, lowpower processing cores. This need becomes more urgent due to the increased need for scaling

computation to tackle key computations such as deep learning, artificial intelligence and their

tremendous requirement of efficient big data processing. A key enabler to such vision is the

availability of computing power that can process vast amounts of information rapidly, reliably, and at a low power budget. On the other hand, the research community speculates

that CMOS scaling could end in around 2024 [68], making it unlikely that further area, performance, and energy improvements would be purely based on fabrication technology. There

is a general consensus of the researchers that computing based on traditional architectures is approaching its limits in terms of scalability and power consumption [67, 68]. For these reasons, researchers have begun to develop alternative computing methods. To cope with these standing barriers facing the future of computing, one must look into other means of improving the efficiency of computation by increasing parallelism rather than depending on transistor feature reduction [13]. Heterogeneous computing has been adopted as a mean to cope with the increased need for performance and power efficiency, whereby specialized engines are entrusted with domain-specific (e.g., video) or function specific tasks (e.g., vector/matrix processing) relying on GPUs, FPGAs, etc. However, this approach becomes insufficient if processing elements cannot be fed by the memory at the desired processing rate, leading to a significantly degraded overall performance despite the advancement in the process technology and parallelism. The requirements for these devices, which are necessary to support the future computing needs, such as small area, low power and high performance are in conflict with the realities of high performance computing systems using traditional architectures. Unfortunately, current processor solutions have not been adopted because they are significantly less efficient than ASICs in terms of power and area (or GOPS/W/mm<sup>2</sup>). Perhaps the two most formidable barriers are (1) the gap between processing and memory speed, and (2) the power consumption barrier for a given performance target, limiting the extent, scope, size, weight, and longevity of the computing systems.

Clearly a radical shift from current approaches is needed to meet the demands of future computing systems at both the architecture and the device levels. In fact, it is well recognized that the lower limits of system power consumption are orders of magnitude below state-of-the-art low power realizations. Consider a case-in-point where a study to simulate one second of the human brain activity required 82,944 processors running for 40 minutes [96]. This is especially intriguing when one realizes that the brain consumes approximately 10 watts while performing an estimated  $10^{12}$  -  $10^{14}$  operations per second. The problem is exacerbated when considering mobile devices where power and area are crucial enablers. Modern multicore

processor chips rely extensively on very large cache hierarchies (L1, L2 and L3). In fact, these account for over 80% of the chip area and an even larger percentage of the energy budget [72]. To address these processing requirements of the ever-increasing amount of information, new computing paradigms started to emerge that focus more on the memory bottleneck problem together with the emerging semiconductor technologies. Broadly, these architectures aim to perform operations directly in the memory or near the memory to eliminate the data movement costs. This allows the creation of the new architectures on which von Neuman bottleneck has a minimal effect.

Theoretically and intuitively, the most memory efficient computing paradigm is in-memory computation where all computations are performed inside the memory without moving the data. Associative processors (AP) are excellent in-memory computational platforms for massively parallel (Single Instruction Multiple Data) computing that combine the memory and the processor in the same location [32]. In associative computing, the operations are carried out on the rows of a memory simultaneously. This feature inherently solves the memorywall problem of traditional processor architectures since the memory and the processor are integrated. Even though numerous associative processors (AP) architectures were proposed in 1970's and 1980's [32, 142], their adoption was limited due to the unmanageable area and power requirements [32]. This reality has been changing with the availability of new semiconductor technologies (such as ReRAM [154], STT-RAM [4], and MRAM [140]), materials, and ultra scaling in transistors that allow for extremely dense memory structures. As described later in this section, Table 1.1 shows a summary of the emerging nonvolatile memory technologies [66] to point out this reality. As shown in the table, these devices provide ultra-high density when compared with traditional memory technologies such as SRAM together with non-volatility.

As a consequence, the improvements in the semiconductor industry lead to a resurrection of the AP approach in the research community [176, 42], and even in the commercial semiconductor industry as an end product [38, 33, 61, 123]. In-memory based accelerators where logic can be replaced by memory structures, virtually eliminating the processor-memory traffic can achieve at least an order of magnitude more energy-efficiencies per area (GOPS/W/mm<sup>2</sup>), when compared to existing systems. In this dissertation, the main focus is on the architectures of associative processors ranging from low-power computing to reliable in-memory processing and approximate in-memory computing. The approaches presented in this dissertation contribute to the design of in-memory processors/accelerators based on associative processing.

# 1.2 Background

### 1.2.1 Computation Types

There are many categorization of computation types such as with respect to the number of concurrent instruction and the data streams processed on the architecture (i.e., Flynn's taxonomy [31]), the degree of the parallelism (i.e., Feng's classification [11]), or pipelining and parallelism (i.e., Handlers Classification [7]). Irregardless of these classifications and processing features of the architecture, another categorization type is the organization of the processor with respect to the memory. From this perspective, there are three computation types which are defined by the relative placement of the memory and the processor. Referencing this classification, any computing system can be fall into one of these three classes; traditional(out-memory), near-memory, or in-memory. The following three subsections details this classification.

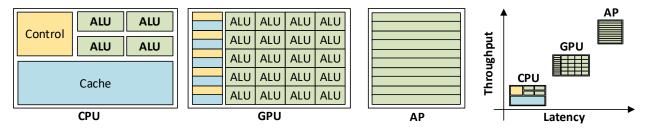

Figure 1.1: Computation types with respect to the memory organization

#### Traditional (Out-memory)

As the traditional and most commonly used computational method, out-memory architectures place the memory and processor in separate chips. During the computation, the data stored in the memory is fetched to the processor. The processors performs the operations by the arithmetic logic unit (ALU) and the results are sent back to the memory. The communication between processor and memory is handled through high-speed buses. The von Neuman (Princeton) [162] and Harward architectures are the examples of out-memory computation and they differ in terms of where the instructions and the data are stored [47].

#### **Near-memory**

As the von Neuman architecture faces the memory bottleneck problems, the researchers have come up with the idea of placing both memory and processor inside the same chip in order to enable higher bandwidth between them, thus to obtain the faster communication and computation. In this organization, the data read from the memory can reach to the processor much faster (and vice versa) than a traditional architecture since they are in the same chip. The study of intelligent RAM (IRAM) [93] is one example for near-memory computation where DRAM is integrated with the processor by eliminating the memory cache to optimize

the cost and performance trade-off [92].

#### In-memory

In-memory computation aims to perform the operation directly inside the memory (i.e., not inside the same memory chip as in near-memory computation). There are different realizations of in-memory computing architectures. The most basic one is placing a small arithmetic logic units within the memory to perform some operations on a group of data [43]. In some cases, the operations are performed by using the analog or digital processing capability of emerging technologies such as memristor [46, 104]. As another method, associative processing described in the next chapter (Chapter 2) performs the in-memory computation by using look-up tables of the arithmetic and logical operations. Unlike the von Neuman or near-memory computation in which the data sent to processor for computation, associative processors sent the functionality or operation over data without moving it.

In here, it is worth to mention that associative processing term is commonly used for the architectures employing associative memories (i.e., CAM) for computing. For example, even though associative computing architectures proposed in [69, 43, 52, 54, 51] uses a CAM structure, the operation is not done inside the CAM or memory. The CAM is only used for associative search and the search results are processed either using a small, basic processor near the memory (inside the same chip) or the main processor. On the other hand, the associative processor referenced in this thesis perform the processing within the memory directly. In other worlds, the computation is done inside the CAM without using any additional processor. Therefore, there are differences between the two processor types. Unfortunately, associative computing terms are used for both architectures since they are based on the associativity of the memory. In reality, their computation methods are totally different.

#### 1.2.2 Non-volatile memories

There are many alternatives in the memory design and each alternative has its own ff. For in-memory computing, the memory structure in which computation is done also plays an important role. Traditionally, designers depended on a hierarchical memory structure to balance the requirements of speed, power and area across the various layers. However, emerging memory technologies are providing alternative means to flatten the hierarchy, while maintaining or surpassing the best features of current state of the art architectures. Table 1.1 shows a detailed comparison between traditional (current) and emerging memory technologies [72]. In the case of traditional memories, there exists a clear trade-off between speed and density, where SRAM provides the highest speed with low density. On the other hand, Flash memories are very dense but much slower. Emerging technologies provide means to avoid this tradeoff. Three of the four main emerging technologies are resistive based memories (ReRAMs), namely Phase Change Memory (PCM), Spin-Transfer Torque (STT), and memristors based on the REDOX phenomenon. From an architecture point of view, the three technologies are quite similar; nevertheless, memristor seem to be the most promising, since it provide the highest density among all the emerging technologies and the lowest access latency [72]. Moreover, memristors can scale much easier than STT-RAMs, offer better read times and generally better or comparable write times and energy per bit. When compared to PCM-RAMs, memristors use much less energy per bit, and are better on almost all other metrics such as density, read and write times [49]. However, there are many challenges that need to be addressed before Resistive memories can genuinely replace current memory technologies. Among these challenges are manufacturability, variability, and as will become clear later, power density. Some of these challenges are being addressed in industry and academia. Recently, Intel and Micro Technologies announced their 3D Xpoint Memory technology bearing many of the characteristics of memristors such as density, speed, and crossbar architecture, and claiming to be 10x denser than DRAM and 1000x faster than NAND flash. These memories have started to be packaged into Non Volatile-DIMMs and Solid State Drives [165, 64].

Table 1.1: ITRS report for emerging memory technologies [66] and their comparison with traditional memories based on recent literature [45, 171, 70, 106].

|                                 | Traditional Memories |            |               | Emerging Memories |       |         |       |       |

|---------------------------------|----------------------|------------|---------------|-------------------|-------|---------|-------|-------|

|                                 | SRAM                 | DRAM       | NAND<br>FLash | NOR<br>Flash      | FeRAM | STT-RAM | PCM   | ReRAM |

| Cell Element                    | 6T                   | 1T1C       | 1T            | 1T                | 1T1C  | 1(2)T1R | 1D1R  | 1R    |

| Feature Size (nm)               | 45                   | 36-65      | 45            | 16                | 180   | 65      | 45    | 5     |

| Density (Gbit/cm <sup>2</sup> ) | 0.4                  | 0.8-13     | 4.9           | 97.6              | 0.14  | 1.2     | 12    | 1000  |

| Read time (ns)                  | 0.2                  | 2-10       | 15            | $10^{5}$          | 45    | 35      | 12    | -     |

| Write time (ns)                 | 0.2                  | 2-10       | $10^{3}$      | $10^{5}$          | 65    | 35      | 100   | < 1   |

| Nonvolatile                     | No                   | No         | Yes           | Yes               | Yes   | Yes     | Yes   | Yes   |

| Endurance [45]                  | >1e16                | >1e16      | 1e15          | 1e15              | 1e14  | >1e12   | 1e9   | 1e15  |

| Retention Time                  | -                    | << seconds | Years         | Years             | Years | Years   | Years | Years |

<sup>\*</sup> The abbreviations used are: T-transistor, C-capacitor, R-resistor, and D-diode. The bold font indicates the best value per row.

The Memristor (memory resistor) is a nonlinear passive device that changes its state according to the net charge passing through its two terminals, and maintains its state after the electrical bias is removed. The Memristor is widely considered as the fourth basic two terminal passive element, alongside with resistor, capacitor, and inductor. The existence of such a device was postulated since 1970s [19, 20], however it was not until 2008 when a fabricated device was related to the theory [154]. While the memristive phenomenon has been observed for quite some time [131], recent fabrication advances [167, 172, 82, 37, 89, 75] make it very appealing where the resistance of the [8] device represents a memory state [17, 26, 87, 184, 48, 163]. In addition to memory systems, memristors find many applications such as programmable analog circuits [148, 127, 21], logic and arithmetic circuits [34, 136, 113, 35, 101, 166], neural networks [1, 74, 85, 126, 62, 81, 99], electronic oscillators [24, 185, 186, 156, 157, 22], filters [23], and cryptography [108]. Several behavioral, circuit, and physical models have been introduced in order to facilitate the emerging technology [5, 132, 12, 164, 160, 71].

### 1.3 Contributions

The objective of this thesis is to explore the design space, system architecture, software and micro-architecture, enabling low-power in-memory accelerators for large-scale data intensive applications. The primary contributions of this study can be summarized as follows:

- Architecture and Trade-offs of Associative Processors: The understanding of the associative processing and processors are described in detail together with the newly defined operations and system-wide configuration schemes. The proposed system architectures allow reprogrammability in memory-based computation and they are uniquely suited for vector based operations, while fully benefiting from the extreme parallelism. It is shown that emerging memory technologies make it possible to build CAMs that deliver one to three orders of higher GOPS/W/mm² than current parallel architectures. The architectural innovations are proposed that reduce or eliminate the need for any supporting logic, thus addressing the two main barriers to adoption and making AP based on CAMs an excellent candidate for the development of in-memory accelerators. The statement are supported by the trade-off analysis in terms of energy, performance and reliability.

- Approximate In-memory Computing: For the first time, approximate in-memory computing is introduced for the APs. For ReRAM-based APs, two approximate computing methodologies are proposed; bit trimming and memristance scaling. It is emphasized that the two methods are naturally supported by the APs as dynamic and tunable. Later, these concepts are extended for the SRAM-based APs where bit trimming and cell voltage scaling is applied. Furthermore, the hybrid approximate computing is introduced for both AP architectures in which bit trimming and voltage scaling (in SRAM)/cell scaling (in ReRAM) are combined and a design flow is proposed to optimize the system efficiency with a minimum impact on the accuracy.

- Low-power Associative Processor: A low-power SRAM-based AP implementation is suggested by proposing novel architectural improvements to decrease the switching activity. Furthermore, some traditional operations are modified to allow better energy efficiency. For ReRAM-based APs, a considerable energy reduction is provided by multi-compare architectures where ReRAM switching range is scaled without sacrificing the reliability constraints.

- Software Framework for Associative Processors: A cycle accurate simulator for Associative Processors is delivered along with the broad range of benchmarks such as large-scale data mining, signal processing, and deep learning. The simulator is highly configurable with more than 50 parameters and can facilitate circuit-level simulation as well as system-level simulations. The simulator works as fully automated in which the cooperation between the system-level simulator (Matlab) and circuit-level simulator (HSpice) is coordinated seamlessly.

- Two-dimensional Associative Processor: Even though traditional in-memory processor architectures together with emerging semiconductor technologies show promise for improving the efficiency of parallel computing, they lack some vital requirements such as flexibility and sequential execution. For this reason, a novel two-dimensional in-memory computing architecture is proposed. The proposed Associative Processing (AP) architecture is implemented by both CMOS/SRAM and ReRAM technologies and employed as an accelerator. The proposed architecture facilitates very efficient in-memory parallel computing together with a high degree of flexibility that results in faster running time in fundamental benchmarks. Furhermore, the developed architectural innovations reduce or eliminate the need for any supporting logic, thus addressing the barriers to adoption for more benchmarks.

### 1.4 Thesis Overview

After this brief introduction on the fundamentals, contributions, and previous works, the rest of the thesis is organized as follows. The thesis is divided into seven chapters; Architecture and trade-offs (Chapters 1-2), power optimization techniques for APs (Chapters 3-4), and architectural extension and future work (Chapters 6-7). Chapter 2 gives the detailed information on the architecture and operation of the APs in detail which is the fundamental background referenced through the thesis for in-memory computation. The chapter gives information for both SRAM-based and ReRAM-based designs. In Chapter 3, the APs implementations are compared with each other and with other processors to exhibit the trade-offs. The section also presents some studies to escalate the reliability issues. Next, Chapter 3 focuses on the energy efficient AP architectures and proposes some methods and modifications to decrease the power consumption and increase the efficiency of APs. The Chapter 4 also introduces the approximate in-memory computing. Then, Chapter 6 proposes a novel two-dimensional AP architecture which is capable of performing parallel operations on both horizontal and vertical directions. Finally, Chapter 7 concludes the thesis with a summary and starts a discussion on the potential directions as venues for future investigations.

# Chapter 2

# Associative Processor

In this chapter, the overall architecture of an associative processor implemented by ReRAM-based and SRAM-based CAM cells are described. The chapter aims to comprehend the understanding of the traditional APs by including the new materials such as newly defined operations and their corresponding look-up tables. The chapter also includes the proposed in-house simulator for associative processors.

### 2.1 Introduction

An associative processor can be considered as a variant of the single-instruction multiple-data processor (SIMD) that combines storage and processing in the same device. In APs, a key is matched by all the rows in memory, and bits are modified depending on (1) the key mask and (2) whether or not a match occurred. By correctly sequencing matching steps, vector based arithmetic operations can be performed in place. In this way, it performs the SIMD processing inside the memory directly.

The idea of Associative processors has its roots back in the 1970s and 1980s with the work of

Scherson, Elgin, Foster, and many others [144, 32, 147, 143]. In these studies, basic addition algorithms were derived and other operations studied for integer and floating point operations. One of the earliest commercial APs was STARAN [138] in the 1970s by Goodyear Aerospace Corporation. STARAN was interfaced with a conventional general purpose computer. STARAN's main component was the "main frame" memory which enables associative addressing and parallel processing capabilities for array arithmetic operations. An associative programming language (APPLE stands for Associative Processor Programming LanguagE [138]) as well as software for the standalone processing mode of STARAN [9] were developed. Further enhancements to STARAN include multi-dimensional memory access [9] to enable bit-slice and word-slice accesses. Applications such as FFT, Sonar post-processing and string search were accelerated on STARAN [9]. Since then, numerous studies of AP architectures [129, 32] have demonstrated their out performance of traditional processors on various applications ranging from searching and sorting, to FFT, matrix multiplication and sparse linear algebra [141, 143, 177, 178] as well as signal, image, and video processing [139, 6, 147, 3]. Algorithms for the acceleration of spares matrix multiplication using AP are described in [178] where four algorithms were studied, covering fully associative sparse matrix multiplication and a hybrid of AP and CPU computations reducing the computational complexity of such multiplication on AP to O(m). In [177] the authors proposed replacing the on-chip last-level cache with an AP that would work as both memory as well as massively parallel SIMD accelerator.

All of the former APs rely on traditional old CMOS technology which limited the widespread adoption of APs due to large chip area and high power consumption which in turn limited the maximum parallelism practically achievable. The other drawback was the limited scope of compute operations that could benefit from existing CAM structures. This reality has been changing with the availability of new semiconductor technologies (such as ReRAM [154], STT-RAM [4], and MRAM [140]), materials, and ultra scaling in transistors that allow for

extremely dense memory structures (sub-16 nm). Memristor (ReRAM) <sup>1</sup> is a new device technology, which is a nonlinear passive component that changes its state according to the net charge passing through its two terminals, and maintains its state after the electrical bias is removed [19]. Therefore, It is possible to use memristor with two resistance levels to represent a single bit. Memristors technology has revolutionized memory manufacturing by enabling the accommodation of large memory sizes on small chip area with low power consumption. They offer a way out of the status quo due to their suitability to implement CAM structures and crossbar connections that are crucial components for Associative Processors. With the advent of emerging memory technologies, research efforts were geared towards harnessing the advantages of these technologies to make CAMs and APs more attractive. A resistive ternary CAM (TCAM) accelerator based on PCM, and using 3T3R cells (three transistors three resistors per cell) was designed as a DDR3-compatible DIMM [40]. The design allowed the resistive TCAM to work with a general purpose CPU as both content addressable memory as well as conventional address-based RAM memory. AC-DIMM, a further enhancement to this design [42, 41] uses STT-MRAM with 2T1R cells to extend its functionality to associative search and in-memory processing. More recent work on Associative Processors include [42], using STT-RAMs, and [176], using bipolar resistive RAM, to build CAM-based APs. In [176] a resistive AP using diodes is proposed with an area and power intensive CMOSbased reduction tree for population count and reduction operations. The study in [119] provides a matrix multiplication on ReRAM-based AP in O(m) complexity for the traditional matrices. As another application from machine learning, the study in [77] proposes inmemory acceleration for K-means and K-nearest neighbors tasks.

In addition to APs, numerous significant contributions are made in CAM structures which is the principal component of an AP having the ability to perform a search on a large collection of words in a single step or cycle. An energy efficient TCAM, Multiple-Access Single-Charge

<sup>&</sup>lt;sup>1</sup>In this thesis, the terms ReRAM and memristor are used interchangeably since memristor is referenced for AP implementation as the emerging memory technology.

(MASC), was proposed in [55, 54]. The proposed TCAM saves energy by using a search operation scheme that is contrary to the one used in traditional CAMs. By having the mismatched rows maintain the precharge voltage while the matching row discharge theirs. The voltage from mismatched rows is used to precharge the match rows again. This allows for additional search operations to be performed while skipping a precharge cycle. Search results are produced by the TCAM within 1-2 bit Hamming distances of the exact value. This TCAM doesn't have any processing capabilities on its own. It can be used as an accelerator along side a GPU. TCAM can be used to skip performing frequent floating point (FP) operations, such as addition, multiplication and square root by fetching FP operation results from TCAM instead of utilizing the FP unit. This is done by caching frequent patterns of operands and the results of those operations in the TCAM. Profiling is needed for each application in order to detect those frequent computational patterns used in FP operations. A low energy Resistive Multi-stage Associative Memory (ReMAM) was proposed by [53]. Energy saving are achieved by dividing searches in the TCAM onto smaller searches and performing searches in several stages. However, both MASC and ReMAM can only function as associative memory which provides storage and content-based search, requiring other computational blocks to perform near-memory computing.

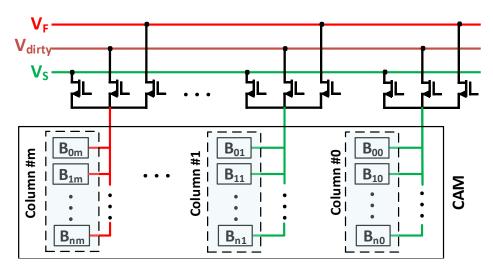

### 2.2 Architecture

The idea of associative processing is based on a content addressable memory (CAM) which is a special type of memory used in computer systems that requires fast data searching operations [122]. As the building blocks of APs, CAMs have the ability to perform a search on a large collection of words in a single step or cycle. Unlike the traditional computer memories like random-access memory (RAM) where the data is located with a a memory address, the CAM memories search the content (data word) inside the memory to decide on its existence

and the location (address). Shortly, the RAM is optimized for address based access and the CAM is optimized for content/data-based access. For this reason, even though a search operation inside the traditional computer memory takes  $\mathcal{O}(n)$  complexity, the CAMs decrease it to  $\mathcal{O}(1)$ . Since an associative processor requires to process the data inside the memory by using these fast data searching operations, the main component forming the architecture of an associative processor is the CAM. While CAMs have been studied and used, on a very small scale, for decades, their implementation in traditional technologies (e.g. CMOS) is very onerous in area and power. New device technologies however, such as Phase Change Memory (PCM), Spin-Transfer Magnetic RAM (STT-MRAM), and Memristors, offer the possibility of building large-scale memories that are much smaller in area and require less energy per bit, and are non-volatile; features that offer transformational potential in how CAMs can be used.

The architecture of an associative processor (AP) is presented in Figure 2.1. The AP consists of a content addressable memory (CAM), controller, instruction cache, specific registers, and an optional interconnection circuit. In the processor, instruction cache holds the instructions that are performed on the CAM. The controller generates the required mask and key values for the corresponding instruction. The *key* register is used to store the value that is written or compared against. *Mask* register indicates which bit or bits are activated during comparison or write. The rows matched by the compare operation are marked in the *tag* field. The rows tagged with logic-1 means that the corresponding CAM row has been matched with the given key and mask value. For example, if we use key 100 and mask 101 to the CAM, the tag bits of the corresponding rows whose first and third bits are logic-0 and logic-1 respectively becomes logic-1 as shown in the figure.

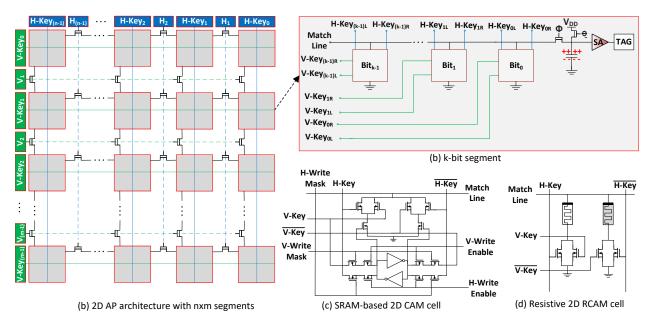

In order to process data inside the CAM, APs must have masked search and parallel column write operations. These requirements can be fulfilled by various CAM cells built using the gated memory cells. Figure 2.2 shows the two possible implementations of a CAM cell

Figure 2.1: General architecture of an associative processor

which are SRAM-based and ReRAM-based CAM cells. When a CAM is implemented by resistive memory technology, it is named as Resistive CAM (RCAM) and the AP composed of RCAMs is named as ReRAM-based AP or Resistive AP (RAP) as opposed to the traditional CMOS/SRAM-based CAMs, which we refer to in this thesis as SRAM CAM, or SCAM, and the corresponding AP as SRAM-based AP, or SAP, while the terms CAM and AP refer to the generic content-addressable memory and associative processing architectures, respectively. The following two subsections explains the SAP and RAP architectures in detail.

### 2.2.1 SRAM Associative Processor (SAP)

In SAP, the CAM is consists of the SRAM-based CAM cells in which the storage is achieved through the SRAM-cells [91, 15]. As the traditional way, an SRAM-based cell can be used to store one-bit together with an additional logic for masked search and write operations (Figure 2.2a) [122]. In this cell, the one-bit data is stored by a coupled inverter where each inverter supports to other to keep its logical value. For this reason, the cell consumes the

Figure 2.2: CAM cell implementations

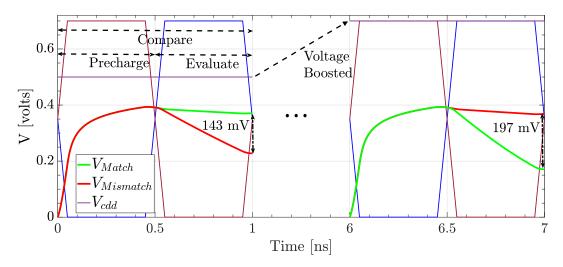

static energy as well as the dynamic energy. The data of the cell can be accessed through the outer circuitry. Figure 2.3 shows the detailed architecture of a SAP. For the sake of a better demonstration, the inverters which output logic-1 is shown as grayed and the ones output logic-0 is shown as white. As the fundamental operations of the associative processing, the compare and write operations on the CAM are performed as follows:

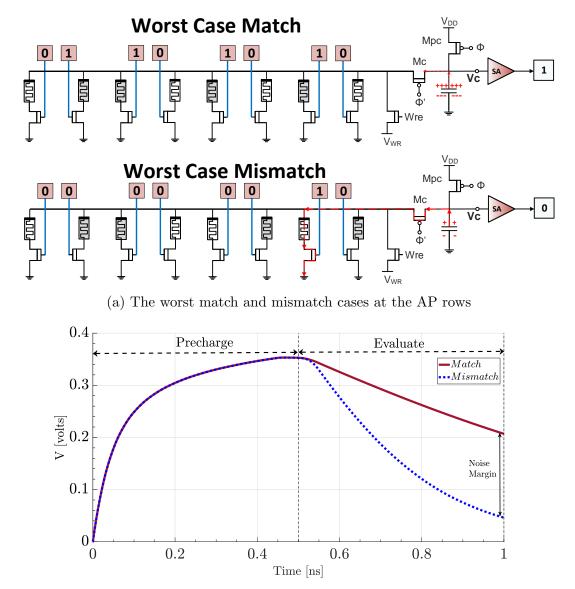

Compare: During the compare, a matching circuit attached to each row distinguishes the rows that matched with the combination of given key and mask values from the mismatched ones [176]. Basically, this circuit uses two phases to differentiate the matched and mismatched rows; pre-charge and evaluate. In the pre-charge phase, the capacitors at each row (row capacitors) of the CAM are pre-charged. During the evaluate, a search word is applied to the columns. Only rows carrying matching data will retain charge because their transistors switched off on the leakage path and the other rows leaks their charges since transistors conduct. On the other hand, the rows matched by a compare operation retain the charge on the capacitor. As seen in Figure 2.3, the key is masked and then applied with its reverse. In this case, to look for logic-1, "01" is sent to the columns and for logic-0, "10" is sent. To exclude the columns from the match operation, simply "00" (don't care) is applied. For both cell types, these data are applied to the matching transistors. Figure 2.4 shows these tree

Figure 2.3: Architecture of an SRAM-based Associative Processor (SAP)

cases explicitly for the SRAM-based CAM (SCAM) cell. In the SCAM cell, if the stored bit is the reverse of the searched bit, the matching transistors (on the top of the coupled inverter in Figure 2.2a) forms a short path to the ground and the charge across the capacitor leaks on this path. If they are same, the path becomes closed and only a small amount of charge can leak. The figure indicates the paths of the closed transistors as black and the closed paths as gray. The charges on a row capacitance leak from the mismatched cell, where the both series transistor are of open state creating a path to the ground, as shown in Figure 2.4b. On the other hand, Figure 2.4a shows the state of the SAP cell in case of a match. In the figure, the CAM-cell stores a logic-1 value and the "01" pattern is applied to the cell to look for logic-1. Since this a match case, the inverter feeding to the right matching circuit closes the transistor while other one opens. On the other hand, "01" pattern closes the left matching transistor and opens the right one where no path to the ground is available through the matching transistors. SRAM-based cell cannot provide a don't care state. On the other hand, the cell can be excluded from the compare operation as shown in 2.4c where the columns are excluded from the compare operation. This provides a mechanism to

perform don't care as column-wise. Following the evaluate phase, a sense amplifier existing at each row senses the residual charge across the capacitor and compares it with a given reference voltage ( $V_{th}$ ). As a result of comparison, it generates a logical correspondences of match and mismatch cases as logic-1 and logic-0 respectively. For example, if we set the key to 100 and mask to 110, the tag bits of the corresponding rows whose third and second bits are logic-1 and logic-0 respectively becomes logic-1 and the rest is logic-0.

Figure 2.4: Typical evaluation phases of a SAP cell for the match (a), mismatch (b), and don't care (c) states.

Write: After a compare operation, the sense amplifier connected to the output of the matching circuit differentiate the matched and mismatched rows by tagging them either as logic-1 or logic-0 respectively. The rows matched by a compare operation are marked in the tag field, that is, the rows tagged with logic-1 means that the corresponding CAM rows have been matched with the given key and mask value. Following a compare operations, the associative processor needs to write to the specific columns of the tagged rws. In order to write to the specified columns of the matched SCAM rows, both write enable and write mask inputs of the cell is asserted. Then, the value and its reverse are applied to bit and bit columns respectively.

# 2.2.2 Resistive Associative Processor (RAP)

SRAM-based CAMs are traditional and well studied in the past. However, the cells are area inefficient since a single cell consists of 12 transistors. Fortunately, with the advent of

Figure 2.5: Architecture of an ReRAM-based Associative Processor (RAP)

new semiconductor materials, one of the most promising candidates for a basic CAM cell is presented in [103], which is made of two memristors (ReRAM) and two transistors (Figure 2.2b). This cell complies with the requirements of the associative computing and exists as a commercial product [33], [61], [123]. In this cell, binary data is stored in the form of "Low" ( $R_{on}$ ) and "High" ( $R_{off}$ ) resistances (i.e., they correspond to logic-1 and logic-0 respectively) in a complementary mode. Therefore, the device can work as a storage element and a switch at the same time, as in the SRAM cell. Unlike the SRAM cell which stores the data as binary, the ReRAM-based CAM cell stores the data as ternary since there are two ReRAMs inside a cell. In this case, a binary value is coded by exploiting these two ReRAMs. If the right and left ReRAMs are set as high and low respectively, the cell corresponds to logic-1. In the reverse case, the cell stores the logic-0. This cell also supports the ternary CAM operations where the cell can be excluded from a search operation on the corresponding column be setting the two memristors as both high ( $R_{off}$ ).

Compare: Similar to the SRAM-cells, the compare operation in the RAPs is achieved by

Figure 2.6: Typical evaluation phases of a RAP cell for the match (a), mismatch (b), and don't care (c) states.

pre-charging the capacitors on all the rows of the array, and then applying a search word (i.e., key) to the columns. However, in here, the charges on a row capacitance leaks the mismatched cell, where the memristor and the series transistor are of low resistance creating a path to the ground, as shown in Figure 2.6b. The data is stored in a "2T2M" cell in a complimentary mode, since the high resistance device will not leak charges to the ground even in case of mismatch, however its complement device will do so. Figure 2.6a shows the state of the CAM cell in case of a match, where no path to ground is available. In this case, the both columns of the cell form a high resistance path through either the closed transistor or the memristor with high resistance state (R<sub>off</sub>). A "Dont care" state can be stored on the cell by setting its two memristors to High resistance, where no path is created to the ground independent of the search bit, as shown in Figure 2.6c.

Write: In ReRAMs, the write operations is performed by changing the resistance of ReRAMs either from  $R_{on}$  to  $R_{off}$  or  $R_{off}$  to  $R_{on}$ . If the used memristor has a threshold for the writing [105], the value of the ReRAMs can be set by applying a proper voltage across the memristor. The amount of the voltage should be higher than the write threshold voltage of the memristor and the polarity must be set according to the written memristance (high or low). Writing to RCAM-cell in an RAP system is performed using a one column at a time scheme. However, this is translated into two writing steps, since a complimentary data column is electively made of two columns of the CAM array. The bits to write are loaded to the match

lines of the rows, with a search word of logic-0 or logic-1 at the column of interest and "Dont Care" elsewhere is written to the columns to activate the column of interest. This eliminates the need for any modification to the column driving circuitry used for compare.

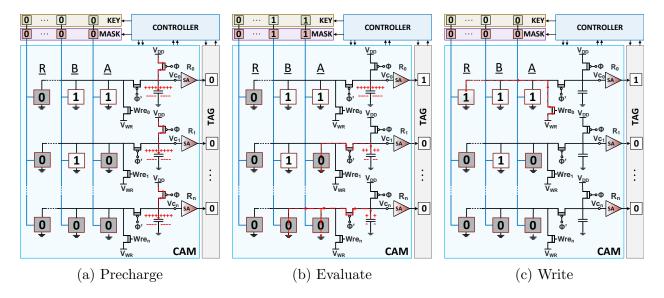

## 2.3 Instructions

An instruction/operation on AP consists of consecutive compare and write phases. During the compare phase, the matched rows are selected and in the write phase, the corresponding masked key values are written onto tagged CAM words. Depending on the desired arithmetic operation, the controller sets the mask and key values by referencing a lookup table (LUT). In the compare phase, the key and mask fields are set and compared with CAM content, while in the write phase, tagged rows are changed with the key. In other words, the truth table of the function is applied (in an ordered sequence) to the CAM to implement the required function. Utilizing consecutive compare and write cycles with a corresponding truth table, any function that can be performed on a sequential processor can be implemented on the AP as a parallelized operation. In the following subsections, the basic logical and arithmetic operations performed on the AP are detailed.

## 2.3.1 Logical Instructions

As stated in the previous section, the operations are performed on the AP by utilizing their corresponding LUT tables irrespective of whether it is a SAP or RAP. As an example of a basic operation on the AP circuit, Figure 2.7 shows how a parallel AND (R = A&B) operation is performed on the AP where the first and second columns corresponds to the A and B respectively and the last column is R (initially all 0). The LUT operation in the CAM can be simply performed by looking for "11" in the A and B columns of the CAM and

Figure 2.7: AND operation on the AP

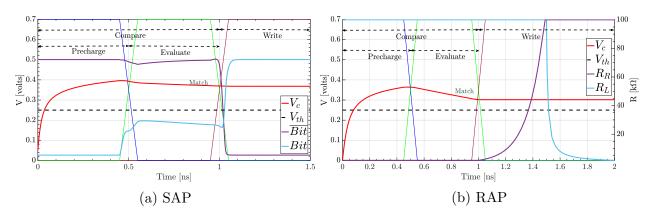

writing logic-1 to the result column of the matched rows as indicated by the AND. Since the other combinations of A and B have no effect on the R (i.e., already logic-0 as default), there is no need to look for them in the CAM. During the operation, firstly, all rows of the CAM is pre-charged (Figure 2.7a) to perform the subsequent evaluate operation. Then the LUT of AND operation is applied to the CAM where CAM is searched for "11" in the input columns (A and B) (Figure 2.7b). The second and third rows leak the charge stored across the capacitor, so only second row matches with the given key and mask values. Finally, "1" is written to the result column (R) of the tagged row in Figure 2.7c. Figure 2.8 shows the voltage and the memristance changes on a SCAM row (Figure 2.8a) and a RCAM row (Figure 2.8b) during the of AND. In both figures, the red line shows the voltage change on the input of the sense amplifier (i.e., the voltage change across the capacitor of the first row) where there is a match at the end of the evaluate cycle, that is, (V<sub>c</sub>) voltage is bigger than the threshold (V<sub>th</sub>). After the compare phase, the write operations are performed where the new data is written into the cell. In SCAM (Figure 2.8a), this operation takes one cycle and simply logical value of the coupled inverter changes. In RCAM (Figure 2.8b), the write operation is performed in two cycles where two complementary ReRAMs change their memristances from R<sub>off</sub> to R<sub>on</sub> and vice versa. The right vertical axis of Figure 2.8b shows the memristance values of the left and right ReRAMs respectively.

In a similar way to the AND operation, other logical operations are performed on the CAM in a bit-serial, row-parallel manner by using their corresponding LUTs. Table 2.1) shows the LUTs of primitive logical operations on the AP which are NOT, AND, OR, and XOR. The other logical operations can also be performed on the AP easily by using their corresponding LUT tables. For the bit shifting operations, the location of the key column which points to the first bit of a value can be shifted to right or left simply, thus APs inherently support the bit shifting operations.

Figure 2.8: Spice simulation of two consecutive cycles in SAP and RAP respectively corresponding to the AND operation in Figure 2.7

Table 2.1: Logical operations and their LUTs

| (a) NOT             | (b) AND                | (c) OR                                                | (d) XOR                                               |  |

|---------------------|------------------------|-------------------------------------------------------|-------------------------------------------------------|--|

| (a) NOT             | $B  A \mid R  Comment$ | $B  A \mid R  Comment$                                | $B  A \mid R  Comment$                                |  |

| $A \mid R  Comment$ | $0  0 \mid 0  NC$      | $0  0 \mid 0  NC$                                     | $0  0 \mid 0  NC$                                     |  |

| $0 \mid 1  1stPass$ | 0  1  0  NC            | 0  1  1  1stPass                                      | 0  1  1  1stPass                                      |  |

| $1 \mid 0 \mid NC$  | 1  0  0  NC            | 1  0  1  2ndPass                                      | 1  0  1  2ndPass                                      |  |

|                     | 1 1 1 1stPass          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |

## 2.3.2 Arithmetic Instructions

#### Addition and Subtraction

In traditional computer arithmetic, 2's complement is the most widely accepted representation in signed arithmetic operations. For this reason, APs use this notation while storing the numbers. In the implementation of addition or subtraction, the result can be written into one of two locations; replace one of the inputs or a new location. The former one is referred to as in-place and later one is out-of-place.

Table 2.2a illustrates the look-up table (LUT) for both in-place and out-of-place additions. In all tables, R and Cr represent result and carry respectively. A and B indicate the inputs. Depending on the operation, the controller sets the mask and key values by referencing the corresponding LUT. In the compare phase, the key and mask fields are set and compared with CAM content according to the left side of the table. In the write phase, the mask and key values are set similarly by observing the right side of the table. However, in this cycle, values in the tagged rows are changed. The comment column in the table specifies the run order of this key combination where a NC (no change) means that the given input combination does not alter any content in the CAM. To ensure correct operation, entries must be appropriately ordered while applying the truth table, to avoid corrupting the values. For example, the operation order and truth table order for in-place addition is not the same. The fourth entry is run before the second entry. This is because that if "001" is searched first for Cr, B, A respectively, and B values of tagged rows changed to logic-1, then when "011" is searched as second, the same rows are tagged again and changed twice. Such situations cause erroneous results and can be avoided by correct sequencing.

The operations on the AP are performed by applying the truth table of the function in an ordered sequence to the CAM. To illustrate a complete operation on the AP, Algorithm

Table 2.2: LUT for addition and subtraction

#### (a) LUT for addition

#### (b) LUT for subtraction

|    |   |   | In-place |   |         | C  | ut- | of-place |

|----|---|---|----------|---|---------|----|-----|----------|

| Cr | B | A | Cr       | B | Comment | Cr | R   | Comment  |

| 0  | 0 | 0 | 0        | 0 | NC      | 0  | 0   | NC       |

| 0  | 0 | 1 | 0        | 1 | 2ndPass | 0  | 1   | 1stPass  |

| 0  | 1 | 0 | 0        | 1 | NC      | 0  | 1   | 2ndPass  |

| 0  | 1 | 1 | 1        | 0 | 1stPass | 1  | 0   | 5thPass  |

| 1  | 0 | 0 | 0        | 1 | 3rdPass | 0  | 1   | 3rdPass  |

| 1  | 0 | 1 | 1        | 0 | NC      | 1  | 0   | NC       |

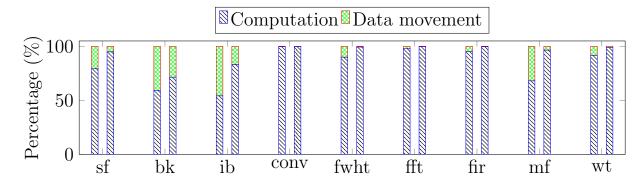

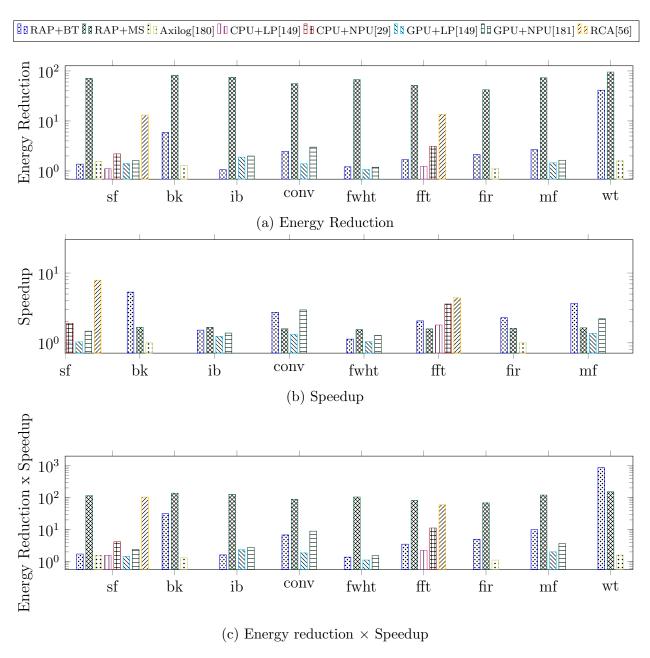

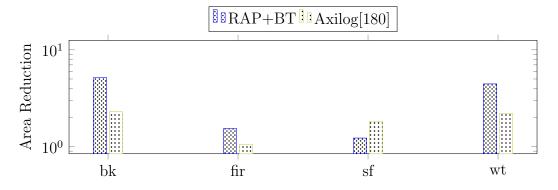

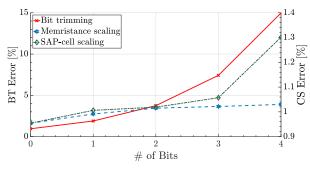

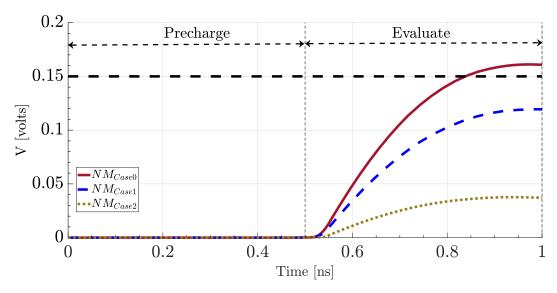

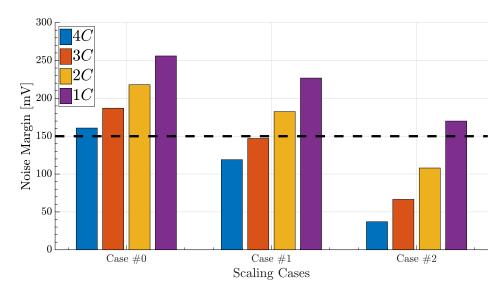

| 1  | 1 | 0 | 1        | 0 | 4thPass | 1  | 0   | NC       |