## **UC Irvine**

### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Semiconductor Chip Electrical Interconnection and Bonding by Nano-Locking

#### **Permalink**

https://escholarship.org/uc/item/34z5q94t

#### **Author**

Guo, Jielin

### **Publication Date**

2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

# Semiconductor Chip Electrical Interconnection and Bonding by Nano-Locking

#### **DISSERTATION**

submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in Engineering

by

Jielin Guo

Dissertation Committee: Professor Frank G. Shi, Chair Professor James Earthman Professor Lizhi Sun

### **DEDICATION**

To

my distinguished professor Frank G. Shi, my dearest husband, my beloved parents, and my friends with their unconditional love and support to offer me strength and courage and made it possible for me to complete this work.

Thank you all.

# TABLE OF CONTENTS

|                                                                       | Page  |

|-----------------------------------------------------------------------|-------|

| LIST OF FIGURES                                                       | vi    |

| LIST OF TABLES                                                        | xiii  |

| ACKNOWLEDGMENTS                                                       | xiv   |

| CURRICULUM VITAE                                                      | xvi   |

| ABSTRACT OF THE DISSERTATION                                          | xviii |

| CHAPTER 1: Introduction and Background                                | 1     |

| 1.1 Overview of Microelectronic Packaging                             | 3     |

| 1.2 Die-Attach Materials in Semiconductor Package                     | 7     |

| 1.3 Flip-chip Interconnection Technology                              | 9     |

| 1.4 Light Emitting Diode (LED)                                        | 12    |

| 1.5 Thermal Management in Semiconductor Packaging: Role of Die-atta   | ach   |

| Material                                                              | 15    |

| 1.6 Reliability for Chip Interconnection and Bonding                  | 17    |

| CHAPTER 2: New Methodology: "Nano-locking" (NL) Chip Bonding          | 25    |

| 2.1 "Nano-locking" (NL) Chip Bonding Method                           | 25    |

| 2.1.1"Nano-Locking" Structure for Electrical Interconnection          | 25    |

| 2.1.2 Surface Topographical Characterization of Metallic Pads on      |       |

| Chip and Substrate                                                    | 28    |

| 2.2 Fabrication of Packaged Devices Enabled by NL Bonding Method      | 31    |

| 2.2.1 Fabrication of the Pure Dielectric Adhesive for Off-chip Bondin | g     |

| and Interconnection                                                   | 31    |

| 2.2.2 Fabrication of Packaged Devices with Different BLTs             | 33    |

| 2.3 Microstructure of NL Bonding Method                               | 35    |

| 2.3.1 SEM/FIB Technique                                               | 35    |

| 2.3.2 SEM/FIB Observation of Packaged with Different Bond-line        |       |

| Thickness                                                             | 38    |

| 2.4 Electrical and Thermal Conduction Mechanism of NL Bonding Method       | 40 |

|----------------------------------------------------------------------------|----|

| 2.5 Adhesion Strength of NL Bonding with Ultra-thin BLT                    | 41 |

| 2.6 Summary                                                                | 42 |

| CHAPTER 3: Devices Enabled by NL Bonding Method                            | 45 |

| 3.1 Introduction                                                           | 45 |

| 3.2 Electrical Performance of Packaged Devices                             | 46 |

| 3.2.1 I-V Characterization of Packaged Devices                             | 46 |

| 3.2.2 Electrical Resistance for NL Bonding Method                          | 47 |

| 3.3 Thermal Performance of Packaged Devices                                | 50 |

| 3.3.1 Junction Temperature and Thermal Resistance Measurement              | 52 |

| 3.3.2 Results and Discussion                                               | 54 |

| 3.4 Optical Performance of Packaged Devices                                | 57 |

| 3.4.1 Optical Performance of Packaged Devices                              | 57 |

| 3.4.2 Results and Discussion                                               | 61 |

| 3.5 Summary                                                                | 64 |

| CHAPTER 4: Reliability Tests for Devices Enabled by NL Bonding Method      | 68 |

| 4.1 Introduction                                                           | 68 |

| 4.2 Wet High Temperature Operation Life (WHTOL) Reliability Test           | 69 |

| 4.2.1 Experimental Procedure                                               | 69 |

| 4.2.2 Results and Discussion                                               | 71 |

| 4.3 Thermal Cycling Test                                                   | 74 |

| 4.3.1 Experimental Procedure                                               | 75 |

| 4.3.2 Results and Discussion                                               | 76 |

| 4.4 Summary                                                                | 77 |

| CHAPTER 5: Effect of Bond-line Thickness (BLT) on Device Performance by NL |    |

| Bonding Method                                                             | 80 |

| 5.1 Introduction                                                           | 80 |

| 5.2 Device Performance and Reliability Dependence on Bond-line Thickness.  | 80 |

| 5.2.1 Electrical Performance Dependence on BLT                             | 80 |

| 5.2.2 Thermal Performance Dependence on BLT                                | 82 |

| 5.2.3 Lumen Performance Dependence on BLT                                  | 8r |

| 5.2.4 Reliability Dependence on BLT86                                          |

|--------------------------------------------------------------------------------|

| 5.3 Summary87                                                                  |

| CHAPTER 6: Device Performance and Reliability Dependence on Surface Morphology |

| 89                                                                             |

| 6.1 Introduction89                                                             |

| 6.2 AFM Analysis for Surface Roughness Heights Distribution on                 |

| Metallic Pads90                                                                |

| 6.3 Device Performance and Reliability Dependence on Surface Roughness         |

| Heights Distribution95                                                         |

| 6.3.1 Electrical Performance Dependence on Surface                             |

| Roughness Heights95                                                            |

| 6.3.2 Thermal Performance Dependence on Surface Roughness                      |

| Heights97                                                                      |

| 6.3.3 Optical Performance Dependence on Surface Roughness                      |

| Heights98                                                                      |

| 6.3.4 Reliability Dependence on Surface Roughness Heights                      |

| Distribution                                                                   |

| 6.4 Summary101                                                                 |

| CHAPTER 7: Conclusion and Future Perspectives                                  |

# **LIST OF FIGURES**

|                                                                                                                                                                                                                                                                           |                                                                                                                                              | Page         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

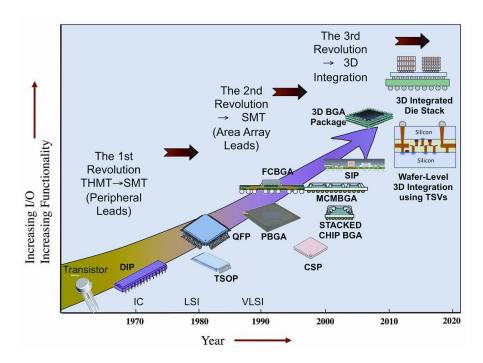

| Figure 1.1                                                                                                                                                                                                                                                                | Figure 1.1 Electronic packaging trend                                                                                                        | 2            |

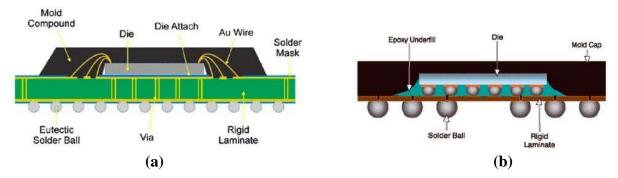

| Figure 1.2                                                                                                                                                                                                                                                                | Typical first level interconnect (a) wire bonding (b) flip-chip package                                                                      | 5            |

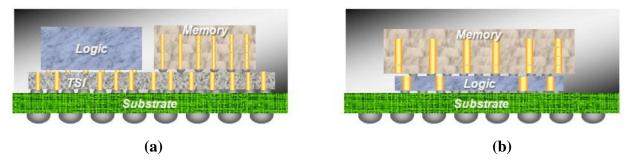

| Figure 1.3                                                                                                                                                                                                                                                                | Schematic illustration of typical (a) 2.5D and (b) 3D IC package                                                                             | 5            |

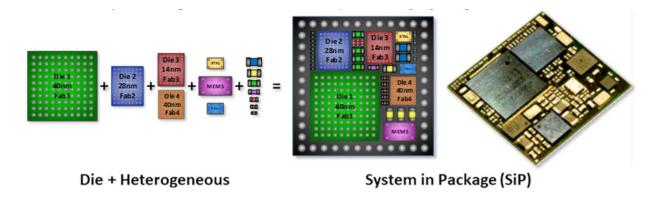

| Figure 1.4                                                                                                                                                                                                                                                                | Heterogeneous integration and system in package (SiP)                                                                                        | 6            |

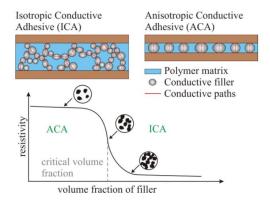

| Figure 1.5                                                                                                                                                                                                                                                                | Electrically conductive adhesive types and effect of filler volume fraction                                                                  | n 8          |

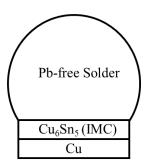

| Figure 1.6                                                                                                                                                                                                                                                                | Illustration of IMC during the soldering process                                                                                             | 8            |

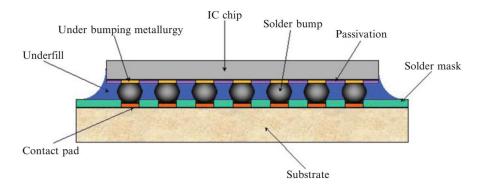

| Figure 1.7                                                                                                                                                                                                                                                                | Schematic configuration of typical flip chip package with underfill                                                                          | 10           |

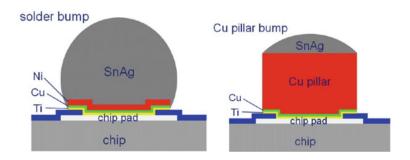

| Figure 1.8 solder cap                                                                                                                                                                                                                                                     | Schematic drawing of a conventional solder bump and a copper pillar w                                                                        | ith<br>11    |

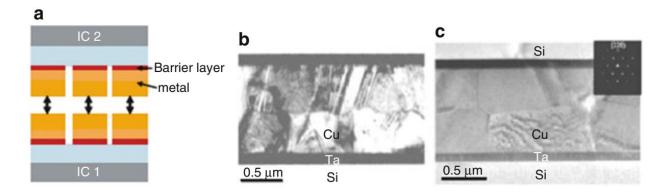

| Figure 1.9<br>Cu bond (c) a                                                                                                                                                                                                                                               | 1.9 (a) IC stacking using Cu-Cu bonding, (b) cross-sectional TEM image of ter annealing (no visible interface)                               | of Cu-<br>12 |

| Figure 1.10                                                                                                                                                                                                                                                               | Working principle of LED                                                                                                                     | 13           |

| Figure 1.11 vertical LED,                                                                                                                                                                                                                                                 | Three common types of high-power LED structure: (a) lateral LED, (b) (c) flip-chip LED                                                       | 14           |

| Figure 1.12<br>Study                                                                                                                                                                                                                                                      | Major causes of electronic failures in U.S.A.F. Avionics Integrity Program                                                                   | 1<br>16      |

| Figure 1.13 (a) Cross section of control BGA after 4400 thermal cycles at High Mean thermal profile (b) Failure mechanism of the package edge solder joints of top WLCSP with details of cracking on RDL side                                                             |                                                                                                                                              |              |

| Figure 1.14                                                                                                                                                                                                                                                               | Environmental reliability stress test flow                                                                                                   | 19           |

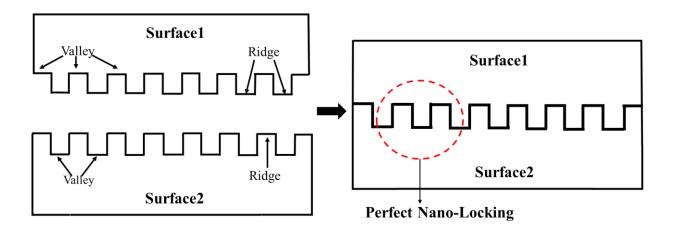

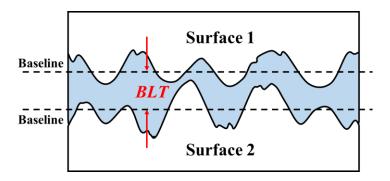

| _                                                                                                                                                                                                                                                                         | chematic illustration of the Nano-Locking (NL) method for chip interconna a perfect locking for two surfaces with exact matching structures. | ection<br>26 |

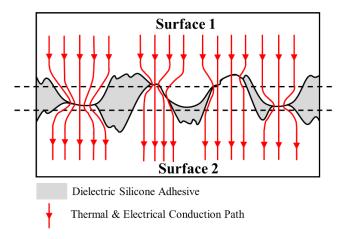

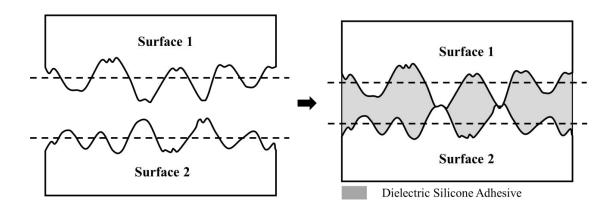

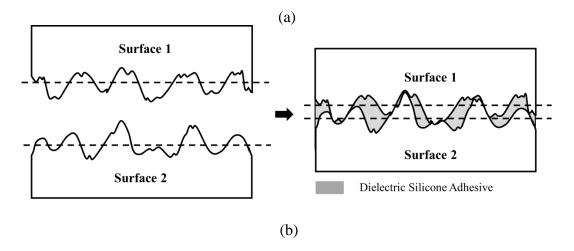

| Figure 2.2 Schematic illustration of the Nano-Locking (NL) method for chip interconnection and bonding: a locking for general interconnecting surfaces with random intrinsic structures: electrical and thermal interconnections are established when the surfaces are in |                                                                                                                                              |              |

| contact, and the interconnection is stabilized and the two surfaces are bonded be adhesive filled in the surface valleys                                                                                                                                                                           | y the<br>26 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2.3 Schematic illustration of the bond-line thickness (BLT): vertical distance between the baseline of the surface roughness on the two bonding surfaces                                                                                                                                    | 27          |

| Figure 2.4 Schematic illustration of the BLT limits: (a) the maximum BLT; (b) the minimum BLT. The maximum BLT is achieved when the two highest ridges on two surfaces are consistent of the minimum BLT is reached when the highest ridge on surface contact with the deepest valley on surface 1 | ontact      |

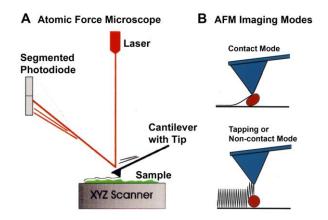

| Figure 2.5 Schematic illustration of the working principle of atomic force microscopy (AFM)                                                                                                                                                                                                        | 7<br>29     |

| Figure 2.6 Definition of the test sample and test area of metallic pads on semiconduct die and substrate for AFM analysis                                                                                                                                                                          | tor<br>30   |

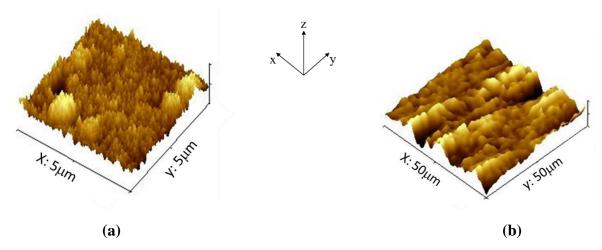

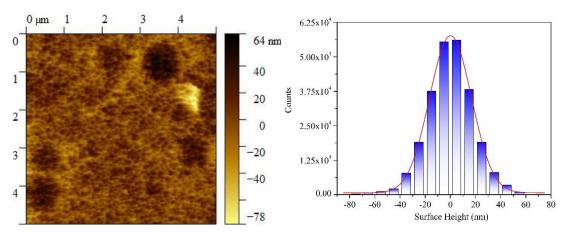

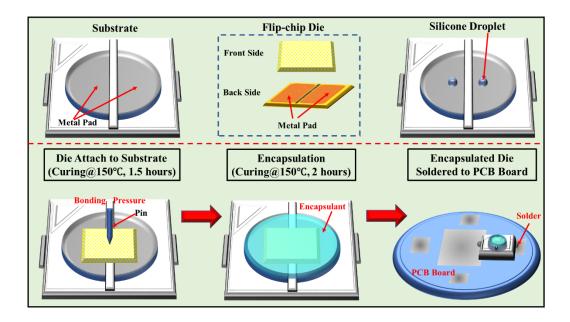

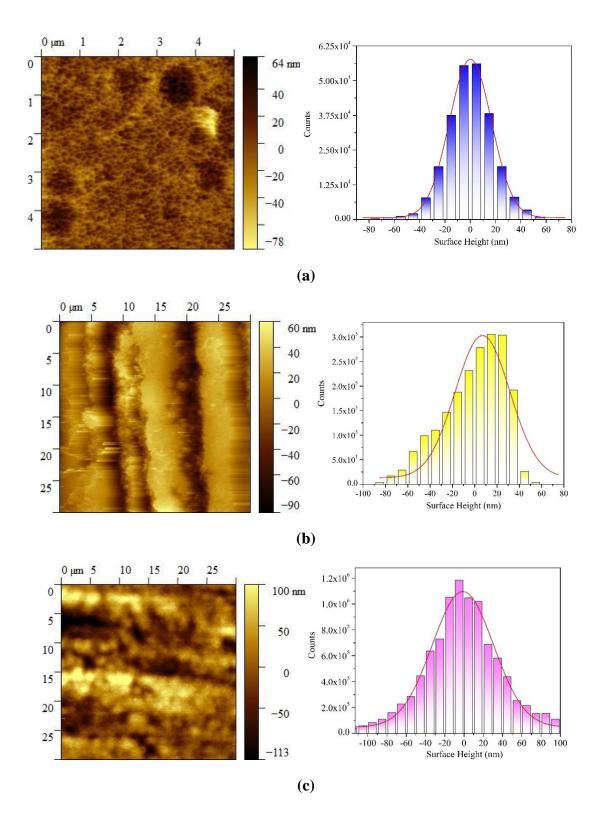

| Figure 2.7 Atomic force microscopy for the topography and height distribution histogof the surface roughness on the semiconductor die metallic pad                                                                                                                                                 | gram<br>31  |

| Figure 2.8 Atomic force microscopy for the topography and height distribution histogof the surface roughness on the package substrate metallic pad                                                                                                                                                 | gram<br>31  |

| Figure 2.9 Chemical formula of silicone-based adhesive (a) DMS-V31 (vinly terminate polymidmethylsiloxane); (b) HMS-301 (25-35% methylhydrosiloxane-dimethylsiloxane copolymer, trimethylsiloxane terminated)                                                                                      |             |

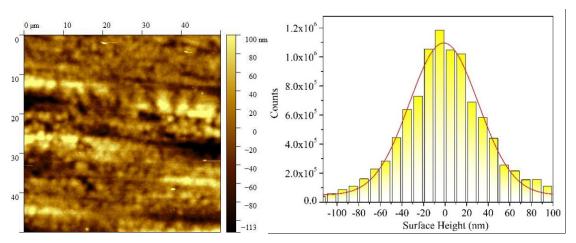

| Figure 2.10 Fabrication of packaging process for flip-chip type high power LED                                                                                                                                                                                                                     | 34          |

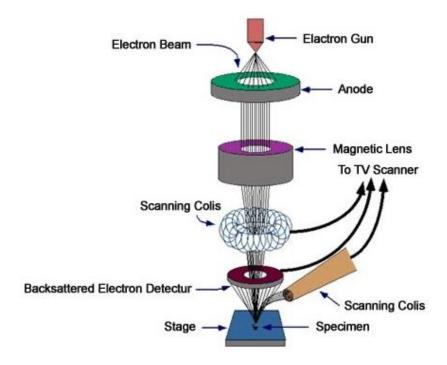

| Figure 2.11 Schematic illustration of measurement principle of SEM                                                                                                                                                                                                                                 | 36          |

| Figure 2.12 Tescan GAIA3 SEM-FIB instrument                                                                                                                                                                                                                                                        | 37          |

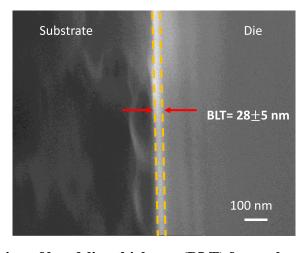

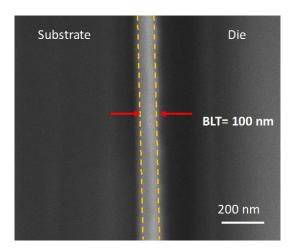

| Figure 2.13 SEM imaging of bond-line thickness (BLT) for packaged devices enabled by NL                                                                                                                                                                                                            | 39          |

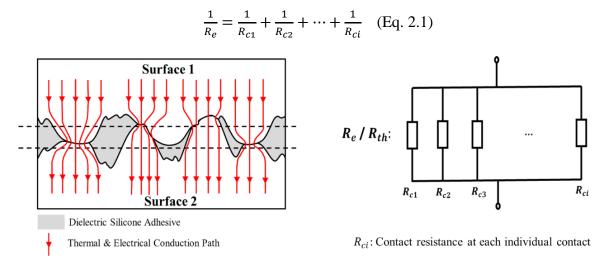

| Figure 2.14 Schematic illustration of electrical and thermal conduction mechanism of bonding method and its equivalent circuits between the two interconnecting surfaces                                                                                                                           | NL<br>40    |

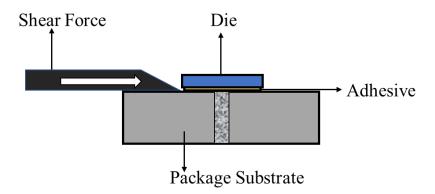

| Figure 2.15 Schematic drawing of experimental set-up for die shear strength measurement                                                                                                                                                                                                            | 41          |

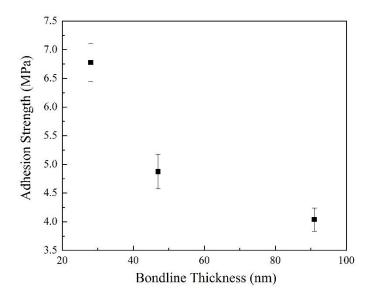

| Figure 2.16 Adhesion strength of the NL bonding method as a function of bond-line thickness                                                                                                                                                                                                        | 42          |

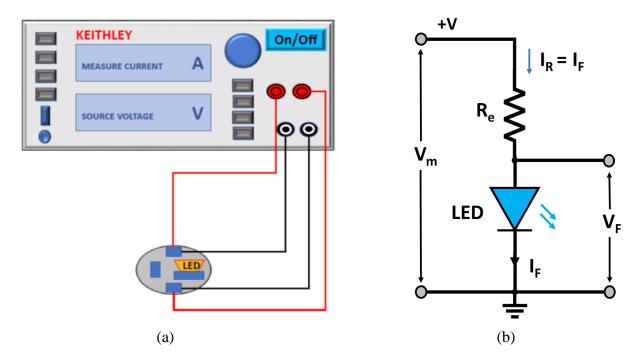

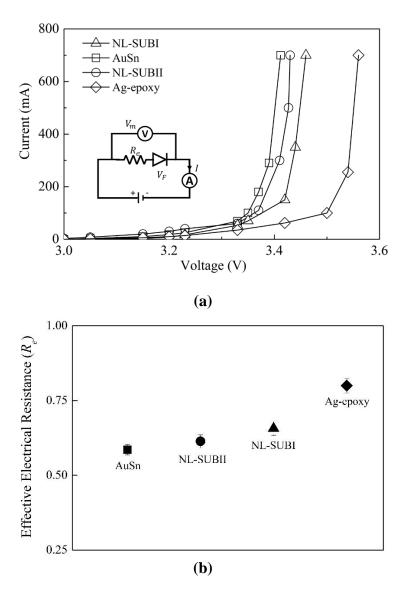

| Equivalent electrical circuit for I-V measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

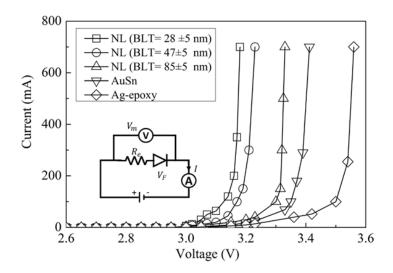

| Figure 3.2 Measurement of current (I) and voltage (V) relationship for the devices mather present NL and conventional die-substrate interconnection and bonding methods open square symbol ( $\square$ ) represents the NL bonding with BLT=28±5 nm, the open triangle symbol represents the NL bonding with BLT=47±5 nm, the open triangle symbol represents the NL bonding with BLT=85±5 nm, the open triangle symbol ( $\triangledown$ ) represent AuSn bonding; the open rhombus symbol ( $\diamondsuit$ ) represents the Ag-epoxy bonding. The curve represents the best I-V fitting                       | The circle $(\triangle)$ as the |

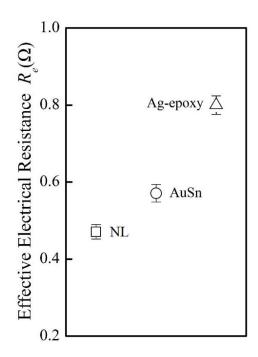

| Figure 3.3 The $R_e$ of different die-substrate bonding and connection methods: the square symbol ( $\square$ ) represents NL bonding with BLT=85±5nm, the open circle symbol represents AuSn bonding with an industrial standard BLT value of 20± 2 $\mu$ m, the triangle symbol ( $\triangle$ ) represents Ag-epoxy bonding with an industrial standard BLT value 25± 2 $\mu$ m                                                                                                                                                                                                                               | ol (°)<br>open                  |

| Figure 3.4 Schematic illustration of how electrical conduction paths are established uninterrupted particle-to-particle contact between the component and the chip catterminal pads in an ICA joint                                                                                                                                                                                                                                                                                                                                                                                                             | -                               |

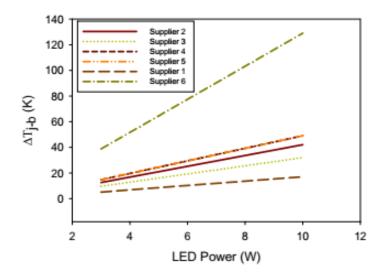

| Figure 3.5 The estimated temperature differences from junction to board of more that W LED. As increasing input power, the die-attach materials become more important                                                                                                                                                                                                                                                                                                                                                                                                                                           | n 1<br>52                       |

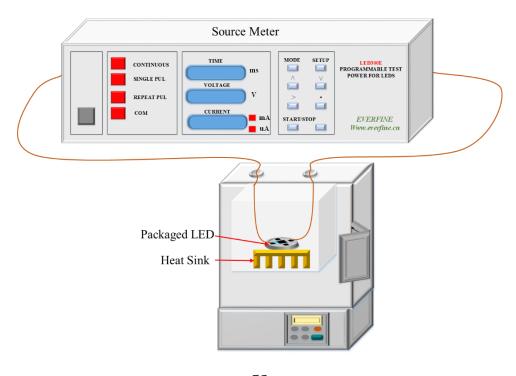

| Figure 3.6 Experimental setup for junction temperature measurement of packaged devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                              |

| Figure 3.7 Flip-chip LED package structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                              |

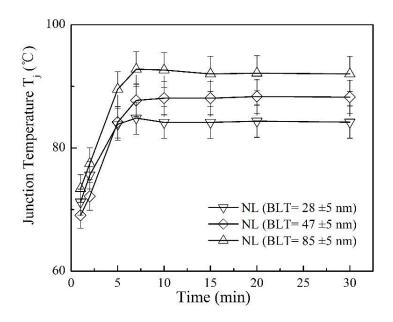

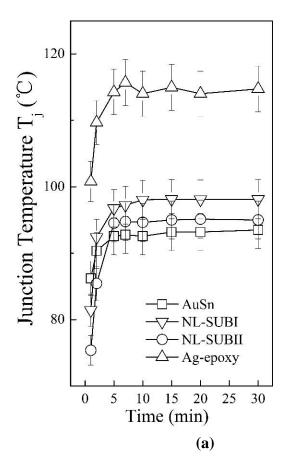

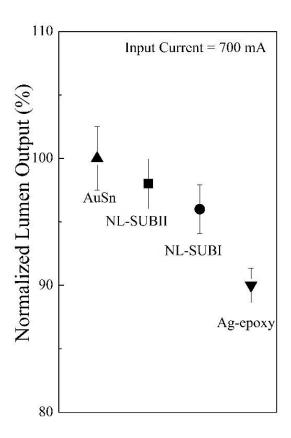

| Figure 3.8 The die junction temperature $(T_j)$ of the devices made by NL bonding approach with different BLTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                              |

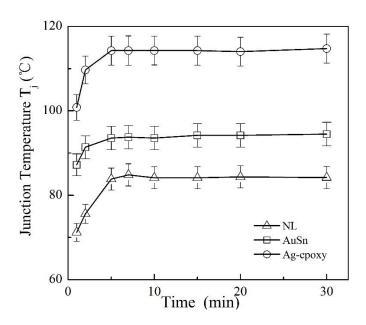

| Figure 3.9 The die junction temperature $(T_j)$ of the devices made by three different substrate bonding methods: the open triangle symbol $(\triangle)$ represents the experiment measurement of $T_j$ for the device made with the NL approach with a BLT of 28±5 nm. open square symbol $(\Box)$ represents $T_j$ data for the device made by the AuSn bonding an industrial standard BLT value of 20± 2 $\mu$ m, the open circle symbol $(\circ)$ represents $T_j$ for the device made with Ag-epoxy bonding with an industrial standard BLT value of 2 $\mu$ m. The solid lines represent the best fitting | ental<br>. The<br>with<br>data  |

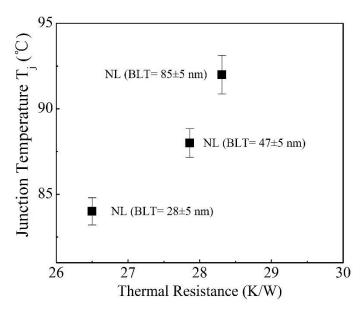

| Figure 3.10 The thermal resistance of $(R_{th})$ of the devices made by NL bonding approach with different BLTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ch<br>56                        |

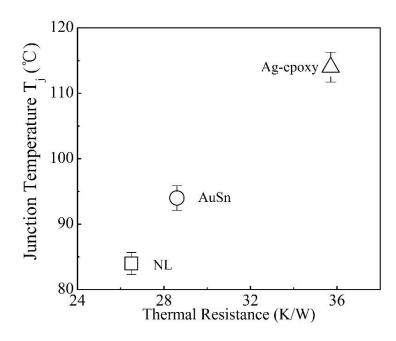

| Figure 3.11 The relationship between $T_j$ and $R_{th}$ : the open square symbol ( $\Box$ ) represent | ents |

|-------------------------------------------------------------------------------------------------------|------|

| NL bonding with BLT=28 $\pm 5$ nm, the open circle symbol ( $\circ$ ) represents AuSn bonding w       | /ith |

| an industrial standard BLT value of 20± 2 $\mu$ m, the open triangle symbol ( $	riangle$ ) represents | s Ag |

| epoxy bonding with an industrial standard BLT value of 25± 2 μm                                       | 57   |

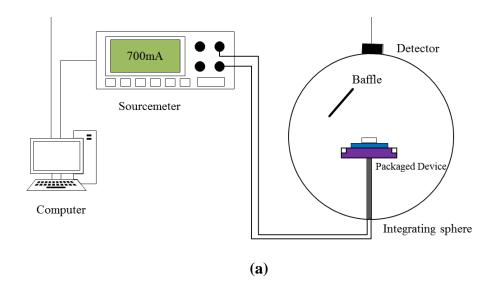

Figure 3.12 (a) Spectral light measurement system for LED lumen output. (b) Integrating sphere photometry 58

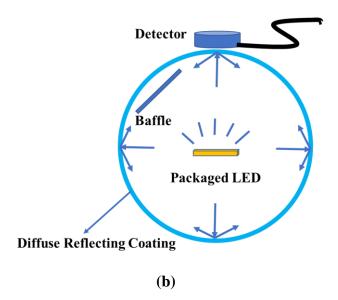

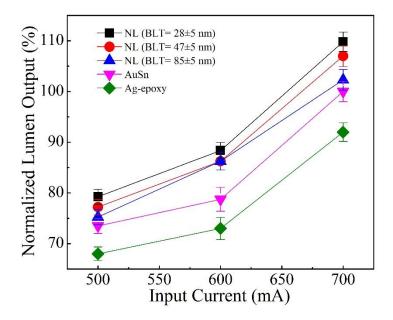

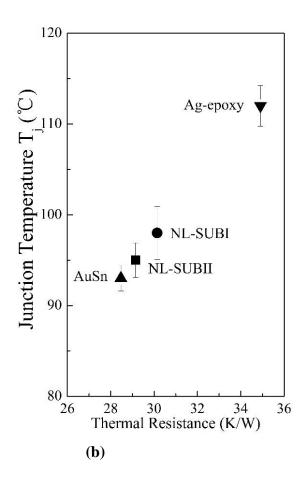

Figure 3.13 Normalized lumen output of the devices made by NL bonding approach with different BLTs

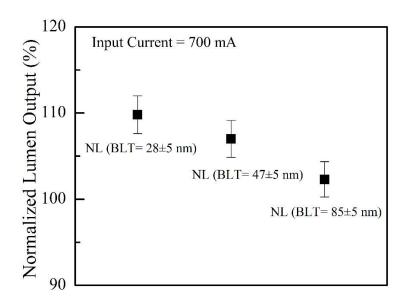

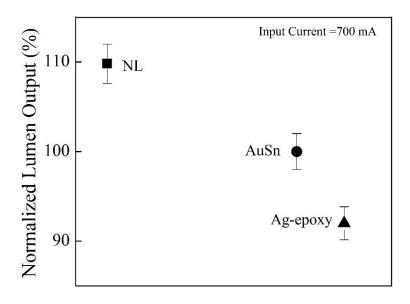

Figure 3.14 Normalized lumen output of the devices made by three different die-substrate bonding methods at an input current of 700 mA: the solid square symbol ( $\blacksquare$ ) represents the NL bonding approach with BLT=28±5 nm, the solid circle symbol ( $\bullet$ ) represents AuSn bonding with an industrial standard BLT value of 20±2  $\mu$ m, the solid triangle symbol ( $\blacktriangle$ ) represents Ag-epoxy bonding with an industrial standard BLT value of 25±2  $\mu$ m 62

Figure 3.15 Changing trend of normalized lumen output of the packaged devices under different input current: the solid square symbol ( $\blacksquare$ ) represents the NL bonding approach with BLT=28±5 nm, the solid circle symbol ( $\blacksquare$ ) represents the NL bonding approach with BLT=47±5 nm, the solid upside triangle symbol ( $\blacksquare$ ) represents the NL bonding approach with BLT=85±5 nm, the solid downside triangle symbol ( $\blacksquare$ ) represents AuSn bonding with an industrial standard BLT value of 20±2  $\mu$ m, the solid rhombus symbol ( $\blacksquare$ ) represents Agepoxy bonding with an industrial standard BLT value of 25±2  $\mu$ m

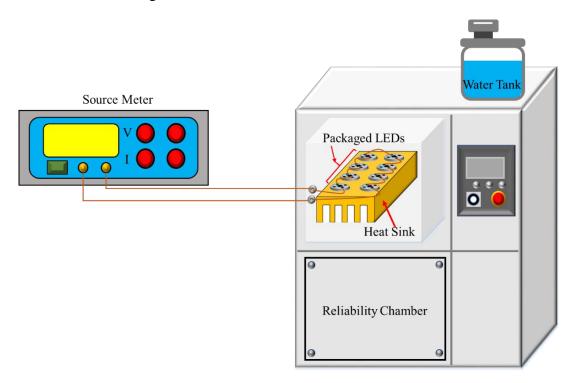

Figure 4.1 Experimental setup for the wet high temperature operation life (WHTOL) reliability test

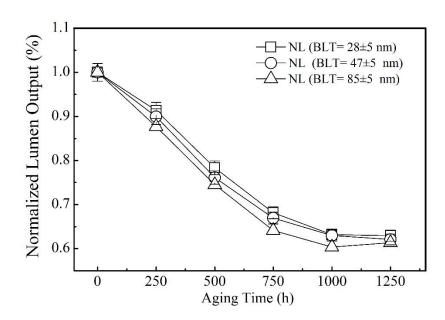

Figure 4.2 Long-term lumen maintenance of the devices enabled by NL bonding with different BLTs as a function of aging time under the stressing condition of an operating current of 700mA, a relative humidity RH=85%, and a high environmental temperature of 85°C: the open square symbol ( $\square$ ) represents the experimental data of NL bonding with BLT=28±5 nm, the open circle symbol ( $\circ$ ) represents the experimental data of NL bonding with BLT=47±5 nm, the open triangle symbol ( $\triangle$ ) represents the experimental data of NL bonding with BLT=85±5 nm. This Wet High Temperature Operating Life (WHTOL) test goes beyond the requirement of the standard JEDEC No.22-A101C while extending the test duration by 25% from 1000 to 1250 hr

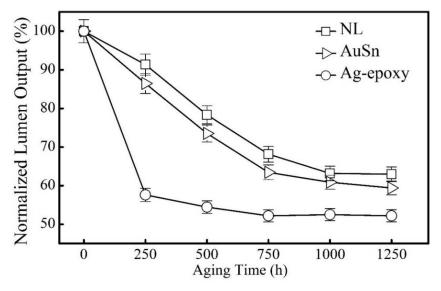

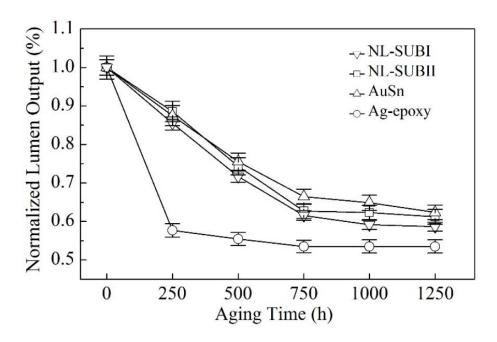

Figure 4.3 Long-term lumen maintenance of the devices with three different die-substrate bonding methods as a function of aging time under the stressing condition of an operating current of 700mA, a relative humidity RH=85%, and a high environmental temperature of

| 85°C: the open square symbol (□) represents the experimental data of NL bonding with BLT=28±5 nm, the open triangle symbol (▷) represents the experimental data of AuSn bonding, the open circle symbol (○) represents the experimental data of Ag-epoxy bonding. This Wet High Temperature Operating Life (WHTOL) test goes beyond the requirement of the standard JEDEC No.22-A101C while extending the test duration by 25% from 1000 to 1250 hr |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

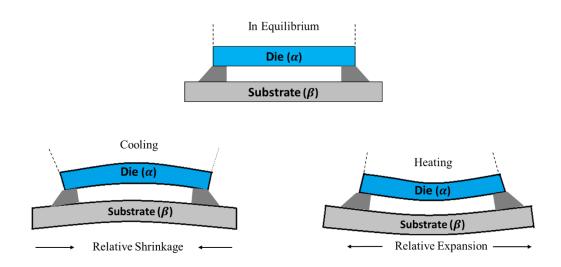

| Figure 4.4 CTE mismatch producing cyclic stress 75                                                                                                                                                                                                                                                                                                                                                                                                  |

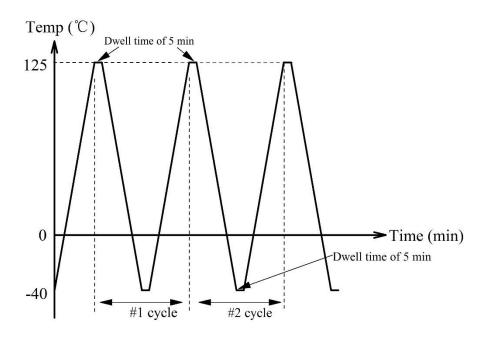

| Figure 4.5 Thermal cycling (TC) profile between -40°C and 125°C 76                                                                                                                                                                                                                                                                                                                                                                                  |

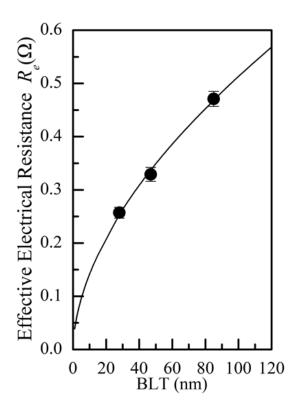

| Figure 5.1 The solid circle symbol ( $\bullet$ ) correspond to the extracted values for $R_e$ in the NL approach, which indicates $R_e$ decreases with decreasing BLT which can be described by $R_e = 0.039(BLT)^{0.56}$ (the solid curve)                                                                                                                                                                                                         |

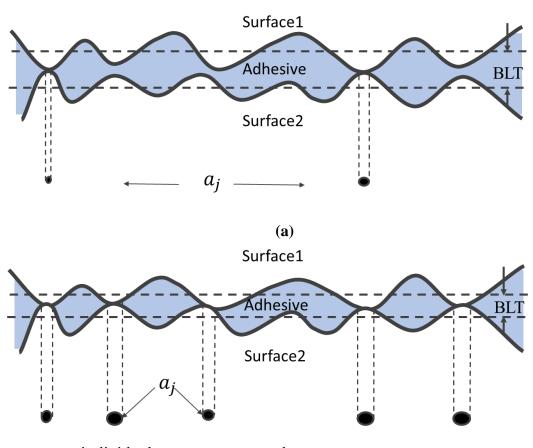

| Figure 5.2 Illustration of contact resistance on the dependence of BLT: thinner BLT leads to larger number of total contacts and larger individual contact area at each contact 82                                                                                                                                                                                                                                                                  |

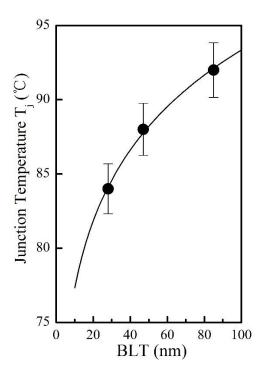

| Figure 5.3 For the devices made by the NL bonding, $T_j$ is found to decrease with the decreasing BLT, which can be described by $T_j$ =64.06( $BLT$ ) <sup>0.082</sup> ( the solid curve), and the solid circle symbol ( $\bullet$ ) represents the experimental data for $T_j$ 83                                                                                                                                                                 |

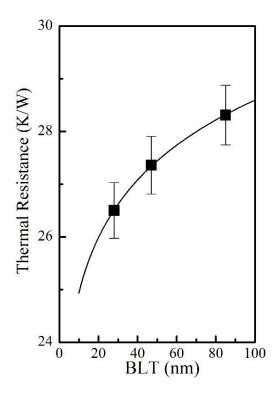

| Figure 5.4 For the devices made by the NL bonding, $R_{th}$ is found to decrease with the decreasing BLT, as described by $R_{th}$ =21.75( $BLT$ ) $^{0.059}$ (the solid curve). The solid square symbol ( $\blacksquare$ ) represents the extracted thermal resistance $R_{th}$ 84                                                                                                                                                                 |

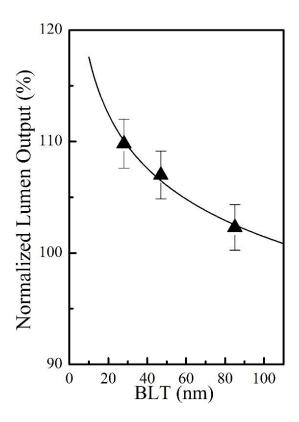

| Figure 5.5 For the devices made by the NL bonding, the normalized lumen output $(I_m)$ is found to be increased with the decreasing BLT, which can be described by $I_m = 1.36 (BLT)^{-0.064}$ (the solid curve), and the solid triangle symbol ( $\blacktriangle$ ) represents the experimental data for normalized lumen output $(I_m)$ 85                                                                                                        |

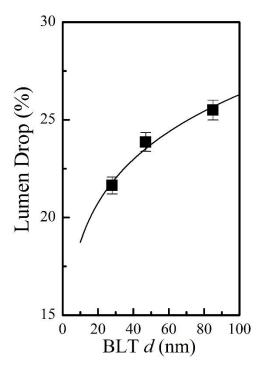

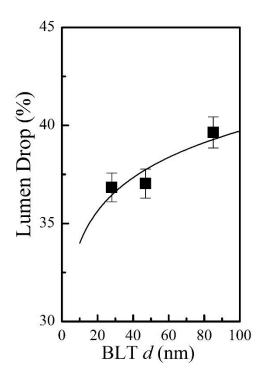

| Figure 5.6 The lumen drop $(I_d)$ at aging time of 500h vs BLT $(d)$ : it follows a power-law relationship $I_d$ =0.13 $(d)^{0.15}$ as presented by the solid line; (c) The lumen drop $(I_d)$ at aging time of 1000h vs BLT(d): it follows a power-law relationship $I_d$ =0.29 $d^{0.07}$ as presented by the solid line                                                                                                                          |

| Figure 6.1 Atomic force microscopy (AFM) for the surface topography and surface roughness distribution (a) the semiconductor die metallic pads; (b) the package substrate-II metallic pad 91                                                                                                                                                                                                                                                        |

| Figure 6.2 SEM/FIB observation of BLT of nano-locking chip bonding approach 92                                                                                                                                                                                                                                                                                                                                                                      |

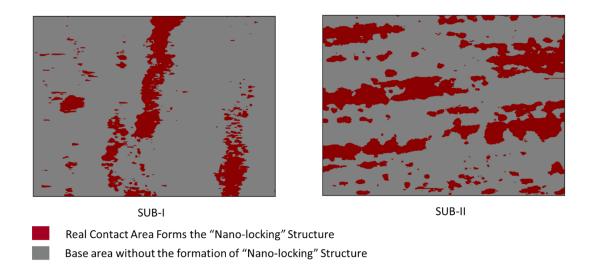

Figure 6.3 Real contact area distribution on the metallic pads of the two different types of package substrates under the same BLT.

Figure 6.4 (a) Measurement of current (I) and voltage (V) relationship for the devices made of the present NL with different substrates and conventional die-substrate interconnection and bonding methods. The open square symbol ( $\square$ ) represents the AuSn bonding; the open circle symbol ( $\circ$ ) represents the NL bonding with substrate type-II; the open triangle symbol ( $\triangle$ ) represents the NL bonding with substrate type-I; the open rhombus symbol ( $\diamond$ ) represents the Ag-epoxy bonding. The solid curve represents the best I-V fitting. (b) The R\_e of packaged devices made by NL bonding with different substrates and different die-substrate interconnection and bonding methods: the solid square symbol ( $\blacksquare$ ) represents AuSn bonding with an industrial standard BLT value of 20± 2  $\mu$ m; the solid circle symbol ( $\blacksquare$ ) represents the NL bonding with substrate type-II; the solid rhombus symbol ( $\spadesuit$ ) represents the Ag-epoxy bonding with an industrial standard BLT value of 25± 2  $\mu$ m 96

Figure 6.5 (a) The die junction temperature  $(T_j)$  of the devices made by NL bonding method with different substrates and two conventional die-substrate bonding methods: the open circle symbol  $(\circ)$  represents  $T_j$  data for the device made by NL bonding with substrate type-II, the open downside triangle symbol  $(\nabla)$  represents  $T_j$  data for the device made by NL bonding with substrate type-I, the open square symbol  $(\square)$  represents  $T_j$  data for the device made by the AuSn bonding with an industrial standard BLT value of  $20 \pm 2 \mu m$ , the open upside triangle symbol  $(\triangle)$  represents Ag-epoxy bonding with an industrial standard BLT value of  $25 \pm 2 \mu m$ . (b) The relationship between  $T_j$  and  $R_{th}$ : the solid circle symbol  $(\blacksquare)$  represents NL bonding with substrate type-II, the solid square symbol  $(\blacksquare)$  represents NL bonding with substrate type-II, the solid upside triangle  $(\blacktriangle)$  represents AuSn bonding with an industrial standard BLT value of  $20 \pm 2 \mu m$ , the solid downside triangle  $(\blacktriangledown)$  represents Ag-epoxy bonding with an industrial standard BLT value of  $20 \pm 2 \mu m$ , the solid downside triangle  $(\blacktriangledown)$  represents

Figure 6.6 Normalized lumen output of the devices made by NL bonding method with different substrates and two conventional die-substrate bonding methods at an input current of 700 mA: the solid circle symbol ( $\blacksquare$ ) represents NL bonding with substrate type-I, the solid square symbol ( $\blacksquare$ ) represents NL bonding with substrate type-II, the solid upside triangle ( $\blacktriangle$ ) represents AuSn bonding with an industrial standard BLT value of 20± 2  $\mu$ m, the solid downside triangle ( $\blacktriangledown$ ) represents Ag-epoxy bonding with an industrial standard BLT value of 25± 2  $\mu$ m

Figure 6.7 Long-term lumen maintenance of the devices made by NL bonding method with different substrates and two conventional die-substrate bonding methods as a function of

aging time under the stressing condition of an operating current of 700mA, a relative humidity RH=85%, and a high environmental temperature of 85°C: the open downside triangle symbol ( $\nabla$ ) represents the experimental data for the device made by NL bonding with substrate type-I, the open square symbol ( $\square$ ) represents the experimental data for the device made by NL bonding with substrate type-II, the open upside triangle symbol ( $\triangle$ ) represents Ag-epoxy bonding with an industrial standard BLT value of 25± 2  $\mu$ m, the open circle symbol ( $\circ$ ) represents the experimental data of Ag-epoxy bonding with an industrial standard BLT value of 20± 2  $\mu$ m. This Wet High Temperature Operating Life (WHTOL) test goes beyond the requirement of the standard JEDEC No.22-A101C while extending the test duration by 25% from 1000 to 1250 hr

## **LIST OF TABLES**

|                          |                                                                           | Page |

|--------------------------|---------------------------------------------------------------------------|------|

| Table 1.1                | Commonly used die-attach materials in electronic packaging                | 9    |

| Table 1.2                | Environmental Tests & Conditions                                          | 19   |

| Table 2.1                | Packaged devices with different BLTs                                      | 34   |

| Table 2.2<br>bonding met | Electrical and thermal properties of different die-substrate hods         | 35   |

| Table 4.1 die-substate   | Thermal cycling results of packaged LEDs with different bonding materials | 77   |

| Table 6.1                | Frequency Percent Distribution of Surface Roughness Heights               | 94   |

#### **ACKNOWLEDGMENTS**

I still remember how excited I was on the day that I got my Ph.D. offer from the University of California, Irvine. That offer changed my life and I came across the whole way over the Pacific Ocean from China to the U.S. and starting to chase my dream. I'm so lucky and with great honor to study and work among some of the most knowledgeable and talented individuals over the past five years. And without the continuous support of these truly amazing mentors and friends, I could not complete my Ph.D. study.

I would like to express my deepest gratitude to my academic advisor and is my committee chair, Professor Frank G. Shi, who has a great passion for research work and a rigorous academic attitude. He offered me the opportunity to work on a very promising project and provided immense insights on how to perform a well-organized research project. Whenever I face any obstacles, Professor Shi will always support me and encourage me to go over those challenges. He spent huge efforts to train me become a qualified researcher and gave me countless suggestions and instructions for my Ph.D. work. We often have brainstorm and discussion together and I'm truly grateful to him. Professor Shi broadened my understanding in the field of electronics packaging and provided me with the knowledge necessary to conclude my Ph.D. studies and provide me suggestions for my future career development. Without Professor Shi's guidance, this study would have not been possible.

I would also like to convey my appreciation to Professor Chin C. Lee, who is the former director of the program of Materials and Manufacturing Technology. He provided the scholarship on behalf of the department and gave me lots of suggestions on course selection at the beginning of my Ph.D. study. I also want to thank Professor Lorenzo Valdevit, who is

the current director of the Materials and Manufacturing Technology for providing me fellowship on behalf of the department during the end of my Ph.D. study.

I would also like to thank my Ph.D. committee members, Professor James Earthman, and Professor Lizhi Sun for their insightful comments on my research at different stages of my Ph.D. journey.

In addition, I would also like to thank my colleagues and friends for their support and kind help. A thank you to my senior colleague, Dr. Yu-Chou Shih, Dr. Youngjun Huo, Dr. Jiun-Pyng You. As my seniors they provided invaluable help and suggestions on my research, from experimental trainings to technical discussions.

I would also like to thank to my UCI friends: Dr. Roozbeh Sheikhi, Dr. Jinfeng Li, Dr. Jiaqi Wu, Jack Ngo, Yuanhan Chen, Xuan Che, Yipin Wu, Jinfeng Li, Dandan Ren, Hong Wei, Tuo Zhou, Yingjie Yang etc.

I'm also appreciative to IMRI staff members, Dr. Jian-Guo Zheng and Dr. Qiyin Lin for teaching me various experimental techniques. I'm also grateful to the administrative staff of Materials and Manufacturing Technology program and department of Chemical and Biomolecular Engineering at university of California Irvine for enabling me to carry out this research project.

Lastly, I am exceptionally grateful to my husband, parents and friends. To my lovely husband, for your love, patience, friendship, and willingness to support and accompany me to go through all the frustrations, all the worries, all the self-doubt, and tears. To my beloved Mum and Dad, your unconditional love and encouragement keep me motivated and chasing my dream during this whole wonderful Ph.D. journey. To my dear friends, thank you all for support and caring.

### **CURRICULUM VITAE**

### Jielin Guo

2009-2013 Bachelor of Science

**Electrical Engineering**

Harbin University of Science and Technology

2013-2016 Master of Science

**Electrical Engineering**

Xi'an Jiaotong University

2016-2021 Doctor of Philosophy in Engineering

Materials and Manufacturing Technology

University of California, Irvine

2019.1-2020.6 Packaging Engineer Internship at Skyworks Solutions Inc. Part-time

2020.6-2020.9 Packaging R &D Engineer Internship at Intel Corporation. Full-time

#### **PUBLICATIONS**

- 1. Jielin Guo, Yu-Chou Shih, Frank G. Shi, "Electrical Interconnection and Bonding by Nano-Locking." Nanomaterials, (2021, accepted)

- 2. Jielin Guo, Yu-Chou Shih, Roozbeh Sheikhi, Jiun Pyng You, Frank G. Shi, "Semiconductor Chip Electrical Interconnection and Bonding by Nano-Locking.", Nanomaterials, (2021, under review)

#### ABSTRACT OF THE DISSERTATION

Semiconductor Chip Electrical Interconnection and Bonding by Nano-Locking

By

**Iielin** Guo

Doctor of Philosophy in Engineering

Materials and Manufacturing Technology

University of California, Irvine, 2021

Professor Frank G. Shi, Chair

Nowadays, the relentless needs for increasing functionality and speed of ubiquitous electronic and optoelectronic devices with reduced cost, size and weight call for novel on-chip and off-chip interconnect technologies. Thus, in addition to the continuing overall push for an ever shrinking pitch size of off-chip interconnections, there are compelling reasons to seek an alternative chip bonding approach enabling simultaneous mechanical, thermal and electrical interconnections with a much reduced vertical dimension than what can be achieved by the current mainstream bump and bumpless methods.

This dissertation explored a new die-attach method used for die-substrate electrical interconnection without requiring a prior time-consuming and expensive surface nanoscopic planarization and without requiring any intermediate conductive material. A chip bonding method with a concept of "nano-locking" (NL) is proposed: The new method takes advantage of the intrinsic nanoscopic surface roughness on the interconnecting surfaces: the two surfaces are locked together for electrical interconnection and bonding with a conventional die bonder, and the connection is stabilized by a dielectric adhesive filled into nanoscale valleys on the interconnecting surfaces.

This "nano-locking" (NL) method for chip interconnection and bonding is demonstrated by its successful application for the attachment of high-power GaN based semiconductor dies to its device substrate.

In Chapter3, the electrical, thermal and optical performances of devices enabled by the present NL bonding are evaluated. The resulting bond-line thickness of devices enable by NL bonding approach achieved is shown to be as low as 30 nm, several hundred times thinner than those achieved using mainstream bonding methods, resulting in a lower overall device thermal resistance, and a reduced electrical resistance, and thus an improved overall device performance. In Chapter4, the wet high temperature operating life test and thermal cycling test are performed to evaluate the reliability of the packaged devices enabled by the NL bonding method and compared with the conventional Ag-epoxy and AuSn bonding approach. The experimental results help demonstrate the fact that the NL bonding approach helps reduce the risk of interfacial delamination during bonding operation and the chances of commonly observed failure caused by interfacial delamination and the mechanical breakdown can be significantly reduced without adding the conductive metallic fillers.

Chapter5 and Chapter6 focused on the study on the influence of bond-line thickness (BLT) and surface morphology on the device performance and reliability. The performances and reliability of the devices enabled by the NL bonding method follows a power law relationship with the different BLT and different density of surface height distribution and leads to different value of electrical and thermal resistance.

The present work opens a new direction for the scalable, reliable and simple nanoscale off-chip electrical interconnection and bonding for nano- and micro-electrical devices. In addition, the

present method applies to the bonding of any surfaces with intrinsic or engineered surface nanoscopic structures as well.

# Chapter1

# **Introduction and Background**

Nowadays, the relentless needs for increasing functionality and speed of ubiquitous electronic and optoelectronic devices with reduced cost, size and weight call for novel on-chip and off-chip interconnect technologies. Although significant innovations in design and process technologies are ongoing, to continue the drive to the next nodes, Moore's Law economics are coming to an end and some key performance metrics at advanced nodes are plateauing. It is much difficult to enhance the performance of a chip-to-package electrical bonding by size scaling, which often suffers from electrical and reliability issues [1]. System-on-chips including chiplets, enabled by 2.5D and 3D integration of dies from separate or the same wafers onto a single chip, represents a new paradigm for advantages beyond Moore's law [2]. This new paradigm is essential to the further development of innovative electrical interconnection technologies for die-to-die, die-to-wafer, die-to-interposer, die-to-substrate or board, die-to-redistribution layer, and wafer-to-wafer, interpose-to-substrate interconnections [3]. The semiconductor packaging technology progression from dual in line (DIP) to surface mount technology (SMT) and then developed to area array packages such as ball grid array (BGA) to achieve higher I/O density as shown in Fig. 1.1. For off-chip electrical interconnections, bump and bumpless methods are two mainstream ones. In bump-based interconnection with thermocompression or thermosonic bonding, which has a relatively low throughput due to the long process time, two interconnecting metallic surfaces are bonded together using electrically conductive bumps made of conductive adhesives such as solders, Cu bumps, or other conductive materials. The most advanced mainstream bump is made of copper pillars with the smallest interconnect pitch achieved being 40 μm, i.e., a 25 μm Cu bump with 15 μm spacing. It becomes a serious challenge to further shrink the Cu bump pitch: although a 20 µm pitch is possible from a lithography standpoint, the difficulty lies in other process steps including the strict surface nanoscale flatness requirement [4].

Figure 1.1 Electronic packaging trend. Source: Electronics Cooling [5]

The bumpless method eliminates the need for intermediate conductive bump and the warpage or delamination issue associated with the bumps and die stacking with a pitch down to 2  $\mu$ m or lower becomes possible. Achieving a good bumpless Cu-to-Cu bonding requires precise control over the nanoscale topography of the interconnecting surfaces which thus must be well planarized by using chemical mechanical polishing to reduce the respective surface roughness below 0.1 nm, and in some cases, the surfaces must also be plasma activated in an ultra-high vacuum of  $10^{-4} \sim 10^{-7}$  Pa, before eventually undergoing a low temperature annealing around  $300^{\circ}$ C [6].

Although the interconnection pitch has a paramount significance for enhancing the integrated density of silicon dies, it is noted that the overall purpose of various integration schemes is to reduce the device power consumption and to increase the device speed at a lower cost. Thus, in addition to

interconnection pitch, the vertical thickness of the interconnection is also critical since it contributes to the overall thermal and electrical resistance of the resulting devices. For example, with a 3D die stack, the potential hot spot within the middle of the stack could be a challenging thermal management and cost issue, which contribute to its much slower commercial adoption than interposer-based 2.5D integration that has less thermal related issues, even though the 3D IC design and architecture have been explored for several decades [7].

The significance of the vertical interconnecting dimension or bond-line thickness (BLT) is even more evident in the case of die-to-substrate bonding in power devices based on wide band gap (WBG) SiC and GaN, which are being explored as another route to extend Moore's law and to replace silicon for many needed emerging devices and applications under high power, high temperature, high frequency, high radiation and other harsh working conditions [8-9]. However, the apparent potential of WBG semiconductors cannot be fully realized until a more advanced die bonding with much lower thermal and electrical resistance can be established, although many bump-based bonding methods including nano-silver sintering have been explored for decades [10].

Thus, in addition to the continuing overall push for an ever shrinking pitch size of off-chip interconnections, there are compelling reasons to seek an alternative chip bonding approach that enabling simultaneous mechanical, thermal and electrical interconnections with a much reduced vertical dimension than what can be achieved by the current mainstream bump and bumpless methods.

### 1.1 Overview of Microelectronic Packaging

An integration of many circuits or components on a single chip is defined as an integrated circuit (IC). Packaging is the bridge that interconnects the ICs and other components into a system-level

board to form electronic products [11]. IC packaging has three important parameters: the amount of I/O which determines the pitch of the IC package as well as the wiring needs at the system level, the size of the IC which affects the reliability of the IC to package connection and the power which affects the heat dissipation and properties of IC and system level packaging.

The electronic packaging has following four main functions: (1) signal distribution; (2) power distribution, involving electromagnetic, structural, and material aspects; (3) heat dissipation (thermal management); (4) protection (mechanical, chemical, electromagnetic) of components and interconnections. These enables the IC package to protect, power, and cool the microelectronic device and to provide an electrical and mechanical connection between the chip and the outside world.

The package interconnects may be classified to die-to-die interconnects, die-to-package interconnects, also known as first level interconnect (FLI), package-to-board interconnect, also known as the second level interconnect (SLI). In this study, the focus is on the first-level packaging that the die is bonded to the substrate. The bonding can take place with a conductive or non-conductive adhesive layer. Electrical interconnection is made possible through a variety of materials and techniques such as wire bonds, Cu pillars, solder bumps, eutectic solder adhesives or conductive epoxy-based adhesives. Two types of first-level interconnection dominate the industry: 1) wire bonding and (2) flip-chip attachment. The wire bonding consists of ball bonds and wedge bonds. The flip-chip attachment technology is used to improve the high integrated density and shorten the signal travel distance, the die is flipped over and facing directly down to the substrate and without using of bond wire. In order to enhance the reliability of flip-chip technology, epoxy based underfill are applied to redistribute the thermo-mechanical stress caused by coefficient of thermal expansion (CTE) mismatch between the die and substrate [12]. After die bonding process, the encapsulant will be applied as the molding cap to protect the die from environmental effects. Three types of molding

are involved: compression molding, transfer molding and injection molding. Typical first level interconnect wire bonding and flip-chip packaging technologies are shown in Fig.1.2.

The recent semiconductor industry is embracing multi-chip package (MCP), integrates a number of ICs in a single packaging structure. It is done either by multi-chip modules (MCMs) in the planar fashion or by 3D stacked-chip packaging referred to as system-in-package (SiP) which incorporates ICs stacked vertically. The advanced 2.5D and 3D integration that can stack different functional components vertically in a single package is very promising technology to overcome the physical, technological, and economic limitations that encountered in planar ICs, extending Moore's law and enabling "More than Moore" applications. Typical 2.5D and 3D IC package are shown in Fig.1.3.

Figure 1.2 Typical first level interconnect (a) wire bonding (b) flip-chip package.

Source: Amkor

Figure 1.3 Schematic illustration of typical (a) 2.5D and (b) 3D IC package.

Source: ASE/SPIL

The 3D integration is classified in three main categories:1) stacking of packages (or substrates); 2) stacking of embedded dies (without TSVs); 3) 3D TSV technology in high volume manufacturing [13,14]. Generally, 3D integration schemes rely on traditional interconnect methods such as wire bonding and flip chip to achieve vertical stacks [15]. The key technologies in 3D integration are wafer thinning and dicing, chip/wafer stacking, bonding, through-silicon via (TSV) and its associated underfill materials. Through-silicon via (TSV) is a vertical electrical interconnection (via) that passes completely through a silicon wafer or die that the reduced vertical interconnect length and substantially high integrated density. In addition, the TSVs enable reduced latency, lower capacitance and inductance and permit higher speed communications which form higher numbers of interconnections and lower power level communication links between circuits [16].

To continue Moore's Law, the heterogeneous integration is proposed to build large systems out of smaller functions [17]. Heterogeneous integration refers to the integration of separately manufactured components into a higher-level assembly (System in Package, SiP) which provides enhanced functionality, smaller size, lower latency, lighter weight and lower cost [18]. In heterogenous integration, components such as dies with different feature size can be integrated into a single package as shown in Fig.1.4. 3D heterogeneous integration includes the following three main categories: 1) 3D System-on-Chip (3D-SoC); 2) 3D Wafer-level Packaging (3D-WLP); 3) 3D System-in-Package (3D-SiP) [19].

Figure 1.4 Heterogeneous integration and system in package (SiP). Source: ASE

The primary driver for advanced packaging technologies is the need for increased interconnect densities to support heterogenous integration and deliver increasing bandwidth. Key challenges will continue to be in fine pitch sort, thermal management, power delivery and reliability for high volume manufacturing.

### 1.2 Die-Attach Materials in Semiconductor Package

Die-attach is the process of attaching the die to the support structure (die cavity or die pad) of the semiconductor package and provide the electrical interconnection between the die and substrate. The two key functions of die attach materials are to ensure the heat dissipation and mechanical fixation of the die on substrate. The attach materials used in the package play an important role in degerming the overall performance, reliability and lifetime of the semiconductor devices.

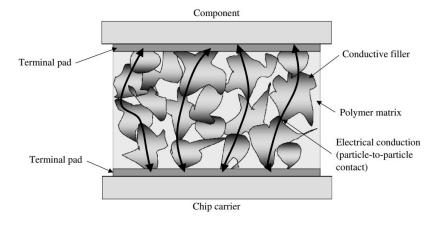

The two commonly used die-attach materials include electrically conductive adhesives (ECAs) and eutectic alloy solders. The ECAs are consisted of a polymeric binder matrices and conductive metallic fillers. The conductive fillers provide the electrical conduction and the polymetric matrices provide the physical and mechanical properties. There are two types of ECAs: 1) isotropically conductive adhesives (ICAs) which are conductive equally in all directions and 2) anisotropically conductive adhesives (ACAs) which are only conductive in one direction, typically along the z-axis [20]. Figure 1.5 is the schematic drawing of ICA and ACA. For ICAs, they have been proposed as an alternative to tin/lead solders in surface mount technology, flip chip, and other applications [21]. For ACAs, the directional conductivity is achieved by using a relatively low volume loading of conductive filler (5-20 volume percent) which enables prevents conductivity in the x-y plane of adhesives.

Figure 1.5 Electrically conductive adhesive types and effect of filler volume fraction [22].

For the lead-free interconnect materials, in soldering process, the molten solder reacts to a base metal to ignite the bonding. The bonding action is initiated by intermetallic compound (IMC) formation, which is a chemical reaction [23]. Take Sn-based Pb-free solder on copper as an example. During the soldering process, the solder melts and reacts with copper to form Cu<sub>6</sub>Sn<sub>5</sub> intermetallic compound and link the solder and cupper together, also known as wetting action, on the interface as shown in Fig.1.6. The IMC formation occurs on all known soldering systems and the soldering process can't be successful without it. The key requirement for soldering is to remove or convert the oxides. The table 1.1 summarize some commonly used die-attach material.

Figure 1.6 Illustration of IMC during the soldering process.

Table 1.1 Commonly used die-attach materials in electronic packaging

| Die-attach material              | Remark                                                                                               |

|----------------------------------|------------------------------------------------------------------------------------------------------|

| Electrically conductive adhesive | Pros: high conductivity; reduced costs through reduction in                                          |

| (ECA)                            | number of processing steps; low curing temperatures; low thermal stresses; better fatigue resistance |

| [Ag-epoxy]                       | Cons: higher electrical and thermal resistance compared with                                         |

|                                  | solders; not compatible for high temperature electronics                                             |

| Eutectic solder paste            | Pros: high thermal conductivity and excellent                                                        |

| [Au80Sn20]                       | mechanical properties;                                                                               |

| [/10051120]                      | Cons: high fabrication temperature                                                                   |

| Lead free solder                 | Pros: high melting temperature                                                                       |

| [SnAgCu]                         | Cons: formation of intermetallic compound and high                                                   |

| [Silrigett]                      | fabrication temperature                                                                              |

| Sintered nano-silver             | Pros: high thermal and electrical conductivity                                                       |

|                                  | Cons: expensive and excessive voiding                                                                |

| Non-conductive adhesive (NCA)    | Pros: Avoid short circuits; ease of processing; cost-                                                |

| [anovy]                          | effectiveness                                                                                        |

| [epoxy]                          | Cons: No direct electrical interconnection                                                           |

### 1.3 Flip-chip Interconnection Technology

Flip-chip technology was first invented by IBM in 1961 and it is an interconnect method where the semiconductor IC is manufactured such that the electrical terminals can be connected in a face down or flipped manner to the package substrate [24]. The schematic drawing of a flip-chip package is shown in Fig. 1.7. Flip-chip assembly becomes a mainstream packaging interconnect technology within the recent decades in response to the need for a relatively large number of highly reliable input/output connections in semiconductor devices. Several types of flip-chip interconnects being used today: solder bumps, Cu pillar bumps, solder pastes, electrically conductive adhesives, sintering nano-silver, Cu-Cu bonding etc.

Figure 1.7 Schematic configuration of typical flip chip package with underfill [25].

Pb-free solders such as SnCu, SnAg, and SnAgCu are used in flip-chip technology. The solder bumping includes a series of steps: 1) the incoming wafers with open via to process; 2) the under bump metallization (UBM) is applied by plating; 3) a photoresist is deposited and patterned on the wafer over the device pads for bumping; 4) the solder metallurgy is then plated to deposit the appropriate solder composition on the chip pads; 5) the photoresist is stripped from the wafer and the UBM metallization is then removed; 6) the solder bumps are then reflowed to form characteristic truncated sphere shapes [26].

Cu pillar is introduced as an alternative to the conventional solder bumps for first level flip-chip interconnections [27]. The Cu pillar bump is an emerging technology for high performance packaging since it offers fine pitch capabilities. Cu pillar is fabricated over a variety of spacing on a Cu-seed layer. A solder cap can be optionally plated on top of Cu pillar and subsequently reflowed form a solder bump or cap. Figure 1.8 illustrates the schematic drawing of solder bump and Cu pillar bump with solder cap.

The anisotropic conductive adhesives are employed for electrical interconnection in flip-chip technology. By controlling the particle volume fraction in the adhesive below the percolation, the insulation in x-y plane is ensured. The conductive particles used are typically solid metal or metal

plated polymer spheres. During the bonding process, it is essential and important to remain precise alignment, electrical contact, parallelism and uniform pressure. There are several requirements for the selection of the adhesive materials. The coefficient of thermal expansion of the particles should be matched to the adhesive. Besides, the glass transition temperature, adhesion strength, modulus of the adhesive and its resistance to moisture are all important to maintain processing capability and reliability.

Figure 1.8 Schematic drawing of a conventional solder bump and a copper pillar with solder cap [28].

Metal to metal solid state diffusion bonding of Cu-Cu and Au-Au has been widely used in IC stacking. The advantages of using metal to metal bonding are the formation of a non-melting microjoint during the sequential stacking processes which enables good heat transfer and reliable mechanical support. Cu-Cu bonding is achieved by thermo compression under bonding pressure with high temperature. The cleanliness of surface before bonding is very important which are influenced by the surface oxide, contamination, hardness and surface roughness in achieving successful bonding. The annealing step using  $N_2$  or  $N_2$ -H<sub>2</sub> gas is essential to get higher bonding strength by allowing Cu interdiffusion and grain growth. Figure 1.9 shows the example of Cu-Cu bonding technology.

Figure 1.9 (a) IC stacking using Cu-Cu bonding, (b) cross-sectional TEM image of Cu-Cu bond (c) after annealing (no visible interface) [29].

As the physical feature size continues to shrink according to Moore's law, the flip-chip technology has steadily advanced to accommodate the interconnection requirements by decreasing bump size and pitch as well as increasing the number of interconnecting bumps. Conventional underfill is applied to reduce the CTE mismatch between the die and substrate. Epoxy resin mixed with inorganic fillers are often used as typical underfill material by flowing into the gap between the die and substrate.

# **1.4** Light Emitting Diode (LED)

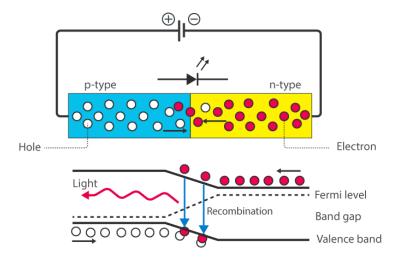

Light-emitting diode (LED) is a semiconductor light source that emits a narrow spectrum of light when the electric current flows through it. The recombination of electrons and electron holes in a semiconductor produces light. The working principle of LED is shown in Fig.1.10. As shown in the Fig.1.10, the n-type region has a high electron concentration and p-type region has a high hole concentration, electrons diffuse from n-type side to p-type side. Similarly, the holes flow by diffusion from p-type side to n-type side. Resulting in an electron field at the junction and forming the depletion region which allows electrical current pass through the junction in only one direction. It is widely

applied for outdoor lighting, automotive headlamps, traffic signals, camera flashes etc. For mini- and micro-LEDs are used for the advanced display technology. According to the peak wavelength of emitted photos, modern LEDs can be classified as visible LEDs, ultraviolet LEDs, and infrared LEDs [30]. The dominant wavelength of visible LEDs ranges from 400 to 760 nm.

Figure 1.10 Working principle of LED. Source: BYJU'S

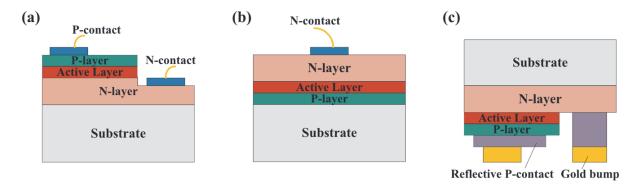

Based on the different structures of GaN based junction configuration, LEDs can be classified as lateral LEDs, flip chip LEDs and vertical LEDs. Figure 1.11 shows these three-types of chip structure. The conventional lateral type of LED consists of sapphire substrate, GaN buffer layer, n-GaN layer, p-GaN layer, electrodes and active layer. Inside the active layer multi-quantum well (MQW) lead to electron-hole combination and light emission. GaN-based LED is the most popular LED which is grown on the sapphire (Al<sub>2</sub>O<sub>3</sub>). The light efficiency of lateral structure is not high, function needs high forward voltage, and heat dissipation in the chip is poor due to the low thermal conductivity of sapphire substrate.

Figure 1.11 Three common types of high-power LED structure: (a) lateral LED, (b) vertical LED, (c) flip-chip LED [31].

The LEDs with vertical structure have been introduced recently to address the aforementioned shortcomings. In the vertical design, the electrodes are placed on both the top and bottom of LED chips. Vertical LEDs could grow on thermal/electrically conductive substrate such as Si, SiC and metal alloys. Compared to the conventional lateral LEDs, the vertical LEDs possess uniform current spreading, smaller thermal resistance and series electrical resistance.

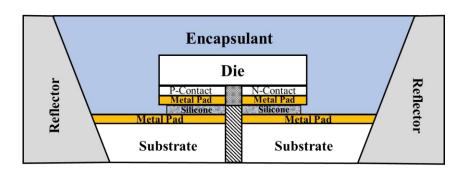

The third type of LED structure is the flip-chip, in this configuration LED dies are flipped over and facing down bonded onto the substrate by metal bump or a uniform bonding layer. In the flip-chip design, the sapphire layer with low thermal conductivity is not within the heat dissipation path and the generated heat can flow downward through the thinner epitaxial material, solder/bonding later and substrate; accordingly, thermal performance of this structure is considerably improved, and thus high-power operation can be achieved with this configuration. A drawback in the manufacturing and packaging process of these structures is the precision alignment needed for bonding metals pads onto the substrate.

The LED light extraction efficiency is greatly influenced by the packaging materials used. Ideally, all the electron-hole pairs should be combined, and the input power should be converted 100% into

optical power. However, the only 70%~85% of electrical power is converted into heat generation. The increase in junction temperature of LED chips will also result in reduction of output power, forward voltage and mean time of failure, additionally shifting of the output wavelength can occur [32].

The electrical interconnection between LED die and package substrate mainly includes wire bonding and flip chip bonding. In wire bonding, most LED's failures are induced by the break-down of ultra-thin gold wire. Furthermore, with the progress of LED industry towards high power, high density and low cost, flip chip bonding has attracted more attentions and the interconnection between LED die and package substrate improve the heat dissipation.

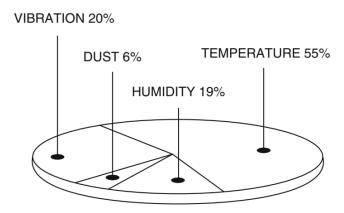

# 1.5 Thermal Management in Semiconductor Packaging: Role of Dieattach Material

The electrical energy supplied to electronic devices will ultimately transform into heat dissipation and accompanied by a temperature rise at the heat source followed by the transport of heat to regions of lower temperature within and outside of the electronic package. For the inside of the package, the heat flux flows through the process of thermal conduction in the solid material that making up the package. When the heat reaches the external surfaces of the package, it usually transfers to a cooling fluid via a thermal convection process. The temperature within the semiconductor package is supposed to continue rising until the rate of heat removal from the package is equal to the rate of heat generation. However, the resulting temperatures would be too high in most cases and become the major failure for the electronic devices as shown in Fig.1.12.

The high packaging density leads to increasing heat flux levels at both the chip and module package. There are three fundamental mechanisms of heat transport from the generation source to the external environment: thermal conduction, convection and radiation. The task of maintaining

relatively low device and package temperature while keep supporting the increased heat fluxes has become one of the most challenges facing today. The die-attach material is the bottleneck for effective heat dissipation among the packaged device.

Figure 1.12 Major causes of electronic failures in U.S.A.F. Avionics Integrity Program Study [33].

Locally high heat fluxes can result large local temperature increases which is often called as hot spots. The thermal design objectives for the packaged devices includes the followings. The temperature of all components needs to be maintained within specific functional limits. Besides, a cooling system needs to be designed to meet the overall system reliability. Thermal interface materials (TIMs) are used to bond the heat spreader with the back side of the chip package. The goal of TIM is to mechanically couple the back side of the chip to the heat spreader while also provide heat conduction. Another important attribute of TIM is its coefficient of thermal expansion, because it acts as the interlayer between a chip and a substrate with significantly different CTEs, the CTE of TIM should be matched with two other bonding surfaces. Studies have shown that 60% of the thermal resistance of a system is in TIMs [34]. TIM thermal resistance  $R_{TIM} = \frac{BLT}{R_{TIM}} + R_{c1} + R_{c2}$ , where BLT

is the bond line thickness,  $k_{TIM}$  is the thermal conductivity of the TIM material,  $R_{c1}$  and  $R_{C2}$  are the thermal contact resistance between the TIM and the bonding surface.

### 1.6 Reliability for Chip Interconnection and Bonding

The reliability of chip interconnection and bonding is highly dependent on the properties of the constituent components and the interfaces formed between the chip and package substrate. Chip-package interconnection can cause chip cracking, solder bump cracking, package substrate trace cracking, and delamination of underfill encapsulation for the flip chip assembly.

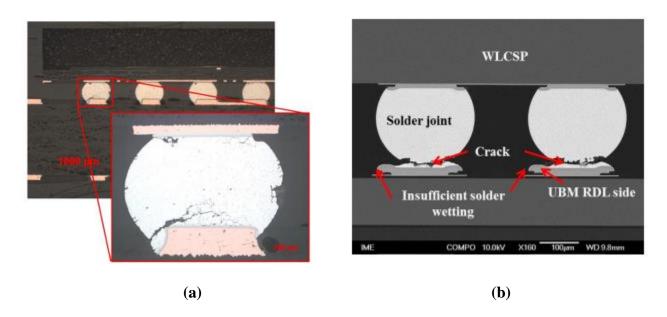

For eutectic AuSn bonding, the primary reliability issues arise from defects introduced during processing (voids, irregular phase formation, weak interfaces due to insufficient barrier metals, etc.) that act as crack initiation sites [35]. The failure modes of the interconnection include delamination, solder ball fatigue/ball crack due to the poor adhesion at interfaces between die and package substrate. Or crack formation and propagation within the under-bump metallization, intermetallic compound, or solder interconnect as descript in [36-38]. In addition, there also exists Cu pad peeling off problem and crack happened to Cu trace at the corner of the package of top wafer level chip scale packaging (WLCSP) and cracks happened to solder joints on back redistribution layer (RDL) side. Figure 1.13 shows the failure mode in solder balls.

For electrically conductive adhesives, the delamination caused by poor adhesion which occurs with both ICAs and ACAs can weaken the mechanical strength of the interconnection. Under high humidity bias environment, moisture can penetrate through the package and the water will degrade the polymers by reacting with them by producing hydroxyl and carbonyl end groups [39]. The silver flakes in ECA are prone to oxidation and can cause problems for adhesive interconnections. In addition, it has been observed that when the ECA interconnection is thermally cycled over its lass transition temperature, the silver flakes may start to segregate. This leads to open circuit as the

particles move away from the other pad. Besides, other impact factors such as air bubbles within an ACA interconnection may retain moisture diffusing and cause short circuits.

Figure 1.13 (a) Cross section of control BGA after 4400 thermal cycles at High Mean thermal profile [40]. (b) Failure mechanism of the package edge solder joints of top WLCSP with details of cracking on RDL side [41].

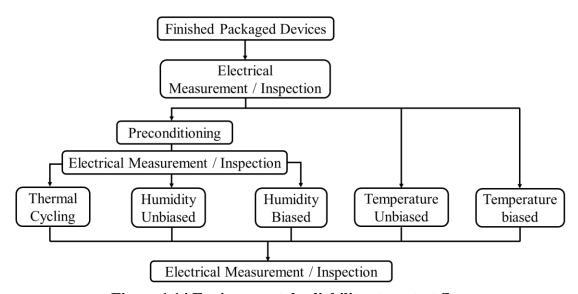

The reliability of the second level interconnection and bonding can be evaluated by a number of different methods, including wet high temperature operating life test (WHTOL), thermal cycling (TC), thermal shock (TS), highly accelerated temperature and humidity stress test (HAST), high temperature storage test (HTSL) etc. The environmental tests and conditions are summarized and shown in Table 1.2.

**Table 1.2 Environmental Tests & Conditions**

| <b>Environmental Stress Test</b> | Abbr. | Specification | <b>Stress Conditions</b> | Requirements    |

|----------------------------------|-------|---------------|--------------------------|-----------------|