## UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Acceleration of Streaming Applications on FPGAs from High Level Constructs

Permalink https://escholarship.org/uc/item/2v24n2wd

**Author** Mitra, Abhishek

Publication Date 2008

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Acceleration of Streaming Applications on FPGAs from High Level Constructs

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

by

Abhishek Mitra

December 2008

Dissertation Committee: Dr. Walid Najjar, Chairperson Dr. Laxmi Bhuyan Dr. Vassilis Tsotras

Copyright by Abhishek Mitra 2008 The Dissertation of Abhishek Mitra is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgements

PhD. is an interesting journey, chock full of twists, turns, crossroads, and unchartered territories, and I would like to profusely thank my advisor Prof. Walid Najjar for guiding me through and for ensuring my reaching of the final destination. I am also extremely grateful to Prof. Laxmi Bhuyan for his able guidance, help and encouragement. I am also thankful to Prof. Vasillis Tsotras for his guidance during the last leg of my research. Finally I am thankful to Prof. Satish Tripathi for providing me an opportunity to study at UC Riverside.

Over the course of last five years I have had the honor of working with excellent colleagues, to whom I am grateful for their constructive criticisms and suggestions. I would like to thank my colleagues (Anirban Banerjee, John Cortes, Jason Villarreal, Petko Bakalov, Marcos Vieira, David Sheldon, Edward Fernandez, Scott Sirowy, Joon Lee, Thomas Repantis, Jingnan Yao, and Roger Moussali).

I am grateful and thankful to my parents Anjusree Mitra and Vishwajit Mitra and my sister Ahana Mitra for their constant encouragement. Moreover I am extremely thankful to Poulomi Dasgupta. She was a real catalyst whenever the going got slow or things didnt work out that well. I am grateful to my best friend Dr. Karuppiah Ramkumar for his constant encouragement.

Due thanks go to Terri, Amy, Madie, Vanoohi from CSE Department and Kelly and Deja from IEC for helping me out with administrative tasks.

My classmates from college Kumar Kartikeya, Ashish Gupta, Nitin Agarwal, Subhek Garg, Sampan Arora, Sheetendu M. Mani and Abhay P. Singh were always there with a helping hand, and I would like to thank them for their help and motivation.

Finally I would also like to thank my current and past room mates Shalendra Chhabra, Varun Kohli, Arinder Arora and Anirban Banerjee for all their help outside of the school.

#### ABSTRACT OF THE DISSERTATION

#### Acceleration of Streaming Applications on FPGAs from High Level Constructs

by

Abhishek Mitra

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, December 2008 Dr. Walid Najjar, Chairperson

Field Programmable Gate Arrays (FPGA) based Reconfigurable Computing hardware are programmed with specialized Hardware Description Language (HDL). FPGAs are increasingly being made available as co-processors on high-performance computation systems. The generation of HDL from high-level software languages is way too complex for a human developer to handle in a reasonable amount of time due to incompatibilities in the execution paradigm between a traditional CPU and on an FPGA. This error prone process manifests itself as the main impediment to a wider use of reconfigurable platforms in high-performance computing. Compilation frameworks are thus a valuable tool for translating traditional highlevel software constructs to HDL for implementation on FPGAs.

This dissertation details how we leverage FPGAs for accelerating PERL Compatible Regular Expressions (PCRE), SNORT Intrusion Detection System (IDS), Common Processing Functions, and XML Filtering, by compiling high-level software language to HDL.

In this dissertation, we detail the implementation of a tool that translates PCRE code into hardware that is mapped to an FPGA. Our compiler generates VHDL code corresponding to the opcodes generated from regular expressions. We have tuned our hardware implementation to utilize an NFA based regular expression engine using greedy quantifiers in much the same way as the software based PCRE engine does.

The SNORT IDS system, incorporates the software based PCRE engine for regular expression matching on the payload. We benchmark the performance of regular expression based rules from SNORT IDS using software only execution on a multi-processor system. We demonstrate the case when 30% or more number of network packets trigger regular expression matching, the software based IDS cannot maintain 10 Gbps throughout, and thus requires hardware acceleration.

Using our PCRE to HDL compilation system, we implement regular expressions from the SNORT ruleset on to the FPGA. These rulesets are organized into one of 16 banks on the FPGA and all operate in parallel. We have implemented more than two hundred PCRE engines based on a plethora of SNORT IDS regular expression rules. These were mapped to the Xilinx Virtex-4 LX200 FPGA on the SGI RASC RC 100 Blade connected to the SGI ALTIX 4700 supercomputing system as a testbed. We obtain an interface throughput of 12.9 GBits/s and a speedup of 353X over software based PCRE execution. We also show that it is possible to scale down the processing related power consumption of an IDS by two orders of magnitude using an FPGA . In this dissertation we describe software tools as well as an IDS architecture that leverages reprogrammability of FPGA hardware. Our software tools for Configurable System on a Chip (CSoCs) generates the communication interface between the software running on the CPU and a tightly coupled IP core based co-processing system. Our tool generates hardware wrappers for the IP Cores that makes them look like a C function invocation in the source code. We also use our tool to support partial reconfiguration: the same wrapper is used for a multitude of IP Cores and the user selects the core to be invoked in the program.

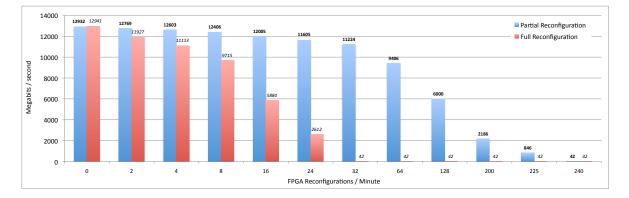

We also demonstrate an adaptable regular expression based IDS using Virtex-4 LX 200 FPGAs that have been floor-planned for partial reconfiguration. Our novel design allows partial reprogramming across 16 banks of regular expression rule-sets. We implement 448 different regular expressions on two FPGAs and perform multiple partial and full reconfigurations. We measure the throughout of the integrated Field Programmable Gate Array (FPGA) and multiprocessor SGI Altix system with varying number of reconfigurations per minute. The adaptive IDS can provide better than 10 Gbps throughput even with 32 partial reconfigurations per minute.

In this dissertation we demonstrate a four step approach that converts user profiles expressed as XPath queries into HDL, suitable for implementation on FPGA. We convert XPaths to PCRE, cluster them by their common prefixes, compile the PCRE to HDL and finally synthesize and implement them on FPGA. This hardware is usable for XML filtering in pub-sub applications. Our benchmarks reveal orders of magnitude improvement in running time while running XML filtering on FPGA, when compared to the state of the art software based XML filtering systems.

Finally, in this dissertation we demonstrate a FPGA based implementation of Prüfer sequence generation hardware for streaming XML document. We match the stream with several Prüfer sequence blocks obtained from twig queries.

# Contents

| Li | ist of Tables xv |         |                                                                | XV |

|----|------------------|---------|----------------------------------------------------------------|----|

| Li | ist of Figures x |         |                                                                |    |

| 1  | Intro            | oductio | n                                                              | 1  |

|    | 1.1              | FPGAs   | s for Code Acceleration                                        | 2  |

|    | 1.2              | Regula  | ar Expression to HDL                                           | 6  |

|    | 1.3              | FPGA    | Reprogrammability                                              | 8  |

|    | 1.4              | XML I   | Filtering on FPGA                                              | 10 |

|    | 1.5              | Contril | butions                                                        | 12 |

|    |                  | 1.5.1   | Compiling PCRE to FPGA and accelerating SNORT IDS              | 12 |

|    |                  | 1.5.2   | Dynamic Co-Processor Interface Automation                      | 15 |

|    |                  | 1.5.3   | Adaptive Hardware/Software Regular Expression Based IDS        | 16 |

|    |                  | 1.5.4   | Boosting XML filtering with a scalable FPGA-based architecture | 18 |

|    |                  |         |                                                                |    |

#### 2 Related Work

|   | 2.1 | Netwo   | ork Intrusion Detection Systems                   | 21 |

|---|-----|---------|---------------------------------------------------|----|

|   |     | 2.1.1   | IDS engines with String Matching                  | 22 |

|   |     | 2.1.2   | IDS engines with Regular Expression Matching      | 24 |

|   | 2.2 | Interfa | cing IP cores on FPGA                             | 28 |

|   | 2.3 | Partial | Reconfiguration on FPGA                           | 28 |

|   | 2.4 | XML     | Filtering                                         | 34 |

|   |     | 2.4.1   | Software Based Filtering                          | 34 |

|   |     | 2.4.2   | Hardware Based Filtering                          | 36 |

| 2 | C   | •1•     |                                                   | 20 |

| 3 | Con | ipiling | PCRE to FPGA via opcodes and accelerating SNORT   | 38 |

|   | 3.1 | Regula  | ar Expressions, IDS and FPGA Acceleration         | 38 |

|   |     | 3.1.1   | PCRE                                              | 39 |

|   |     | 3.1.2   | SNORT IDS and PCRE                                | 39 |

|   |     | 3.1.3   | Accelerating PCRE on FPGA                         | 40 |

|   |     | 3.1.4   | Finite Automaton on FPGA                          | 42 |

|   | 3.2 | SNOR    | T IDS                                             | 42 |

|   |     | 3.2.1   | PCRE rules in SNORT                               | 43 |

|   | 3.3 | Comp    | iling PERL Compatible Regular Expressions to FPGA | 46 |

|   |     | 3.3.1   | PCRE Opcodes                                      | 48 |

|   |     | 3.3.2   | PCRE Opcode Frequencies in SNORT Rules            | 49 |

|   | 3.4 | Comp    | ilation Flow                                      | 50 |

|   |                    | 3.4.1                                               | Compilation Overview                                                                                                                                                                                                        | 52                                                                                             |

|---|--------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |                    | 3.4.2                                               | Common Prefix Optimization                                                                                                                                                                                                  | 54                                                                                             |

|   |                    | 3.4.3                                               | Hardware Implementation of PCRE Opcodes                                                                                                                                                                                     | 54                                                                                             |

|   |                    | 3.4.4                                               | NFA Implementation on FPGA                                                                                                                                                                                                  | 65                                                                                             |

|   | 3.5                | Experi                                              | mental Results                                                                                                                                                                                                              | 69                                                                                             |

|   |                    | 3.5.1                                               | Software only performance with multi-cpu load balancing                                                                                                                                                                     | 70                                                                                             |

|   |                    | 3.5.2                                               | Hardware Benchmark and Comparison with Single Threaded Soft-                                                                                                                                                                |                                                                                                |

|   |                    |                                                     | ware Execution                                                                                                                                                                                                              | 75                                                                                             |

|   |                    | 3.5.3                                               | Single Processor Power Consumption Analysis                                                                                                                                                                                 | 80                                                                                             |

|   | 3.6                | Conclu                                              | sion                                                                                                                                                                                                                        | 82                                                                                             |

|   |                    |                                                     |                                                                                                                                                                                                                             |                                                                                                |

| 4 | Part               | ial Reco                                            | onfiguration on FPGA                                                                                                                                                                                                        | 84                                                                                             |

| 4 | <b>Part</b><br>4.1 |                                                     | onfiguration on FPGA                                                                                                                                                                                                        |                                                                                                |

| 4 |                    | Dynam                                               |                                                                                                                                                                                                                             | 85                                                                                             |

| 4 | 4.1                | Dynam                                               | ic Co-Processor Interface Automation                                                                                                                                                                                        | 85<br>88                                                                                       |

| 4 | 4.1                | Dynam<br>System                                     | and Co-Processor Interface Automation                                                                                                                                                                                       | 85<br>88<br>88                                                                                 |

| 4 | 4.1                | Dynam<br>System<br>4.2.1                            | and Co-Processor Interface Automation                                                                                                                                                                                       | 85<br>88<br>88<br>89                                                                           |

| 4 | 4.1                | Dynam<br>System<br>4.2.1<br>4.2.2                   | <ul> <li>and Co-Processor Interface Automation</li></ul>                                                                                                                                                                    | 85<br>88<br>88<br>89<br>90                                                                     |

| 4 | 4.1                | Dynam<br>System<br>4.2.1<br>4.2.2<br>4.2.3          | aic Co-Processor Interface Automation                                                                                                                                                                                       | 85<br>88<br>88<br>89<br>90                                                                     |

| 4 | 4.1                | Dynam<br>System<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4 | An Overview for IP Core Wrapper Generation and Partial Reconfiguration         The CSoC platform         APU (Auxiliary Processing Unit) on Virtex-4 FX         IP Cores         ROCCC Overview         Interface Synthesis | <ul> <li>85</li> <li>88</li> <li>88</li> <li>89</li> <li>90</li> <li>92</li> <li>93</li> </ul> |

|   |     | 4.3.1   | The FPGA Architecture                                | . 104 |

|---|-----|---------|------------------------------------------------------|-------|

|   |     | 4.3.2   | Xilinx Partial Reconfiguration Flow                  | . 104 |

|   |     | 4.3.3   | The Hardware/Software Integrated Test System         | . 105 |

|   |     | 4.3.4   | Hardware Performance                                 | . 107 |

|   |     | 4.3.5   | Hardware/Software Performance with Reconfiguration   | . 109 |

|   | 4.4 | Conclu  | usion                                                | . 111 |

| 5 | Boo | sting X | ML filtering with a scalable FPGA-based architecture | 113   |

|   | 5.1 | XML     | Pub-sub                                              | . 113 |

|   |     | 5.1.1   | Using FPGA for XML Filtering                         | . 116 |

|   | 5.2 | Comp    | ilation System Overview                              | . 119 |

|   |     | 5.2.1   | XPath Expressions                                    | . 119 |

|   |     | 5.2.2   | XPath on FPGA                                        | . 120 |

|   |     | 5.2.3   | Dictionary Replacement                               | . 121 |

|   |     | 5.2.4   | XPath to Stack-enhanced Regular Expressions          | . 122 |

|   |     | 5.2.5   | Common Prefix Optimization                           | . 125 |

|   |     | 5.2.6   | Area Efficient Character Decoder Hardware            | . 126 |

|   |     | 5.2.7   | Regular Expression to VHDL compilation               | . 127 |

|   |     | 5.2.8   | FPGA Implementation                                  | . 128 |

|   | 5.3 | Twig I  | Profiles on FPGAs                                    | . 130 |

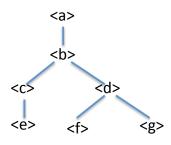

|   |     | 5.3.1   | Overview of Prüfer Sequences                         | . 131 |

|   |     | 5.3.2    | FPGA implementation of Prüfer subsequence matching | 133 |

|---|-----|----------|----------------------------------------------------|-----|

|   | 5.4 | Experi   | mental Evaluation                                  | 136 |

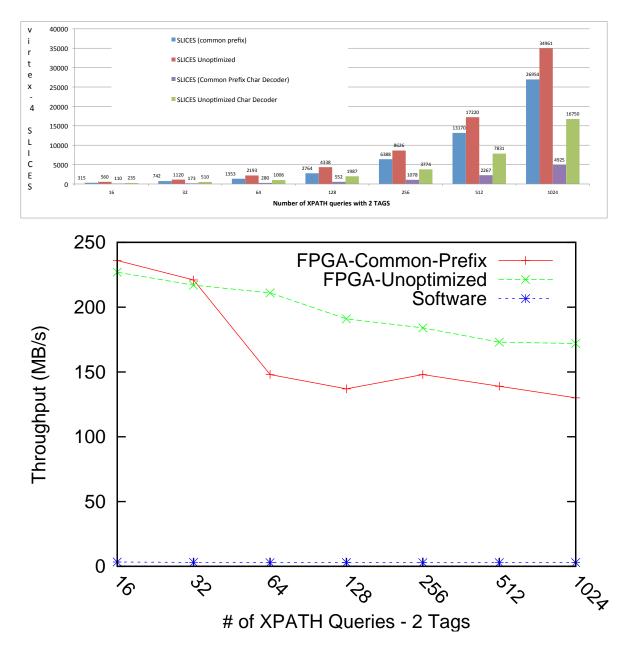

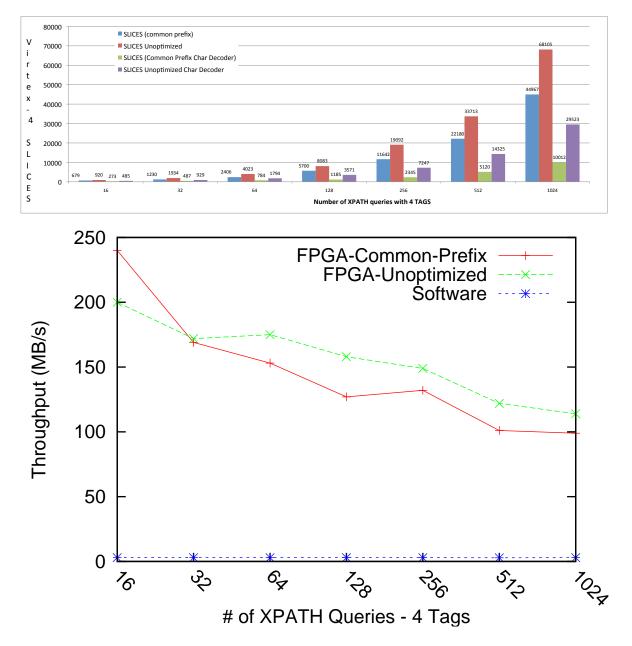

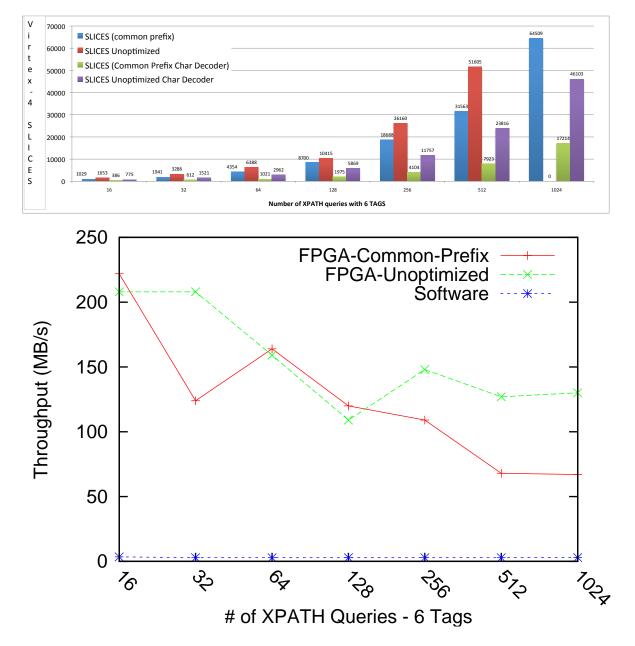

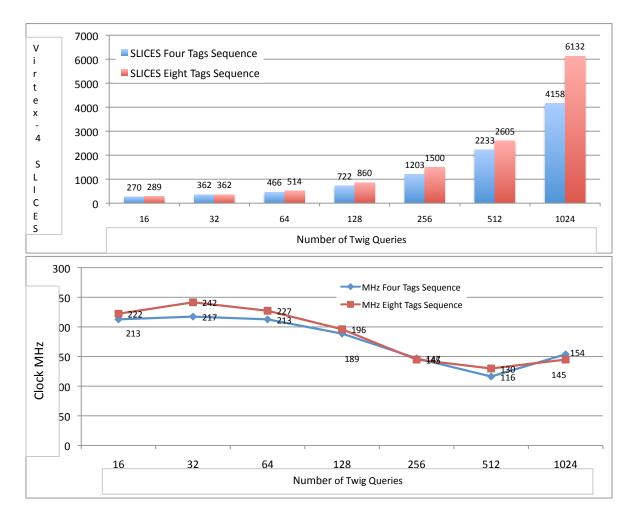

|   |     | 5.4.1    | Performance and Speedup                            | 142 |

|   | 5.5 | Conclu   | sion                                               | 143 |

|   |     |          |                                                    |     |

| 6 | Con | clusions |                                                    | 145 |

|   | 6.1 | PCRE     | to FPGA compiler                                   | 145 |

|   | 6.2 | Accele   | rating regular expression of SNORT IDS             | 146 |

|   | 6.3 | Dynam    | nic Co-Processors on FPGA                          | 147 |

|   | 6.4 | Adapti   | ve Hardware-Software Regular Expressions based IDS | 148 |

|   | 6.5 | Scalab   | le Architecture for XML Filtering on FPGA          | 149 |

|   |     |          |                                                    |     |

### Bibliography

# **List of Tables**

| 3.1 | Example Rules in SNORT DB 2.4                                            | 45  |

|-----|--------------------------------------------------------------------------|-----|

| 3.2 | Format of a typical PCRE Rule in SNORT IDS with the optional modifiers   | 45  |

| 3.3 | Example snippets from SNORT Rules highlighting the use of PCRE operators | 46  |

| 3.4 | Occurences of important PCRE operators in our target SNORT DB 2.4        | 48  |

| 3.5 | Simple Quantifiers Occurrence Table                                      | 59  |

| 3.6 | Ranged Quantifiers Occurrence Table                                      | 60  |

| 3.7 | Unbounded Quantifiers Occurrence Table                                   | 61  |

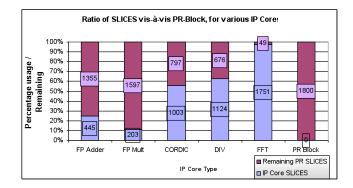

| 4.1 | Area Covered by the Dynamically instantiated IP Cores                    | 100 |

| 4.2 | The Area Covered by IP Wrappers and Wrapped IP Cores.                    | 101 |

| 5.1 | PCRE operators used for implementing XPath profiles on FPGA              | 122 |

# **List of Figures**

| 1.1 | Demonstration of the throughput of a CPU and FPGA: A Highway Analogy.     |    |

|-----|---------------------------------------------------------------------------|----|

|     | An FPGA with a ten times slower clock rate can offer 10X the throughput   |    |

|     | of a dual core CPU by implementing two hundred parallel data paths on the |    |

|     | fabric.                                                                   | 3  |

| 3.1 | A Finite Automata Implemented on FPGA using LUTs                          | 43 |

| 3.2 | SNORT IDS and PCRE Engine usage on a software only Implementation.        |    |

|     | pcre_compile function compiles the regular expression while pcre _execute |    |

|     | function runs the engine of the payload                                   | 45 |

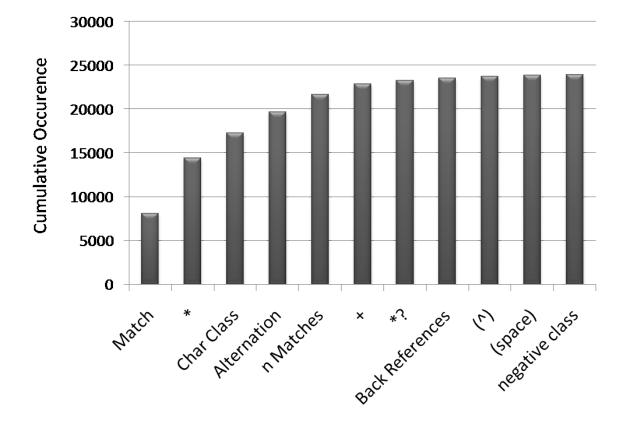

| 3.3 | Frequency Distirbution of PCRE opcodes in SNORT DB 2.4. The most fre-     |    |

|     | quently occurring opcode is the character-match opcode                    | 50 |

| 3.4 | Cumulative Distirbution of PCRE OPCODES in SNORT DB 2.4. The five         |    |

|     | OPCODES viz. Match, star, Character Class, Alternation and constrained    |    |

|     | repetition make up for the most frequently occurring cases of OPCODES     | 51 |

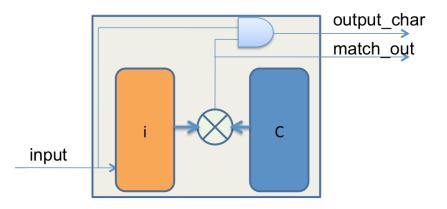

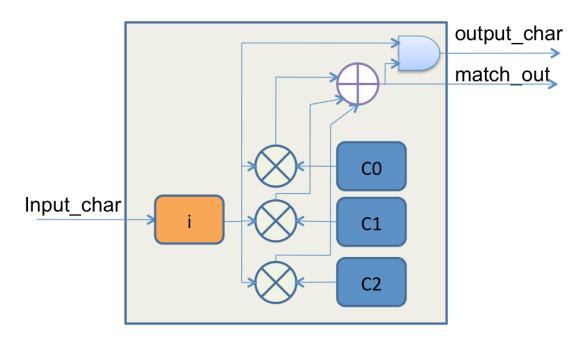

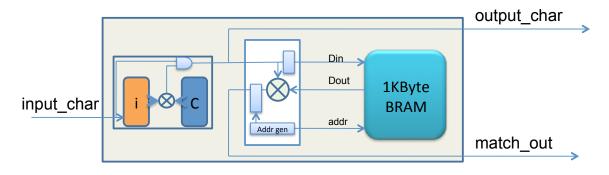

| 3.5  | The Character(s) Match Opcode. The input ( $i$ register) is compared with the |    |

|------|-------------------------------------------------------------------------------|----|

|      | data in the ROM and the output (match_out) is triggered high in case of a     |    |

|      | match                                                                         | 55 |

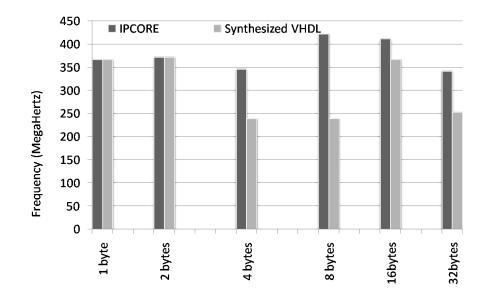

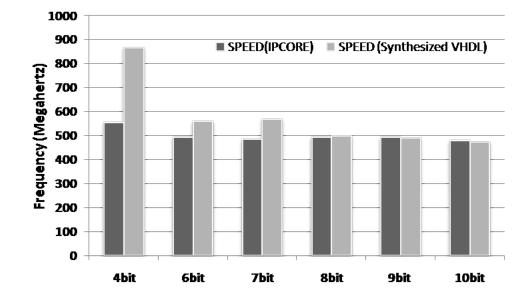

| 3.6  | Implementation Speed in (MHz) of the character-match opcode versus char-      |    |

|      | acter size sets for the two implementation types. Implementing using IP       |    |

|      | Core provides a faster clock speed, as compared to the synthesized design     |    |

|      | for match sizes greater than 2 Bytes                                          | 56 |

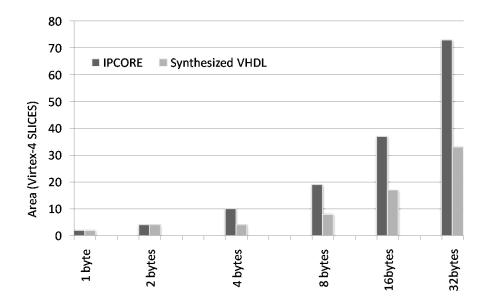

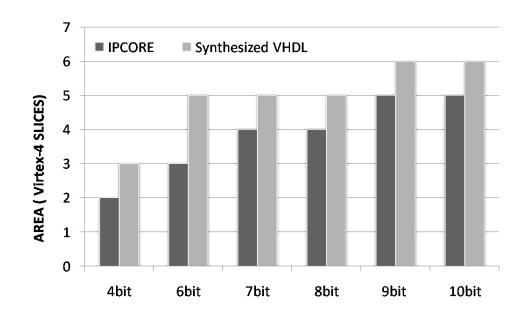

| 3.7  | Implementation area in FPGA slices of the character-match opcode versus       |    |

|      | character size sets for the two implementation types. The area of the opcode  |    |

|      | block increases linearly with increasing match size. Moreover the synthe-     |    |

|      | sized hardware is more area efficient as compared to the IP Core based block  |    |

|      | for a given match size                                                        | 56 |

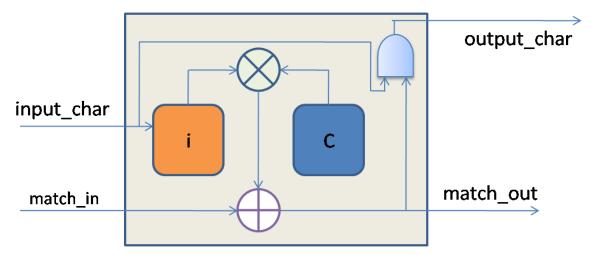

| 3.8  | The Character Class Match Opcode.                                             | 57 |

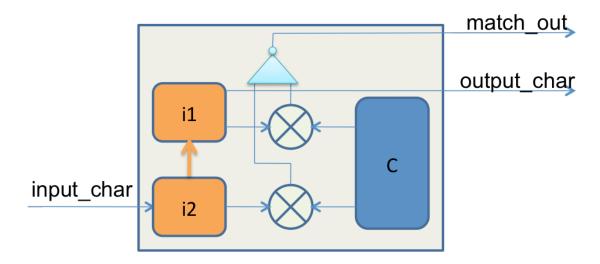

| 3.9  | The * repetition Match Opcode.                                                | 57 |

| 3.10 | The + repetition Match Opcode                                                 | 58 |

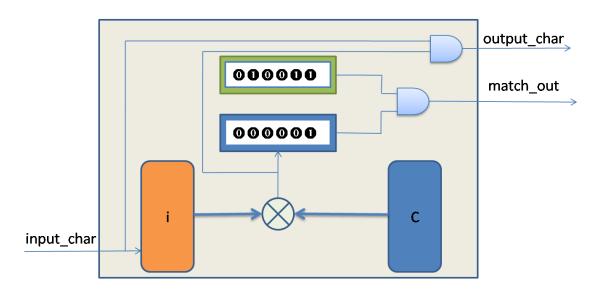

| 3.11 | The quantifier Match Opcode.                                                  | 59 |

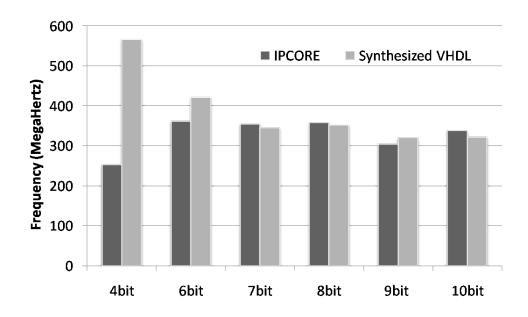

| 3.12 | Speed of unrestricted counters in (MHz) with increasing count size and the    |    |

|      | two implementation types. For counts until 8 bit the synthesized counters are |    |

|      | faster, while for 9 and 10 bit counters, the IP Core is slightly faster       | 61 |

| 3.13 | Speed of restricted counters in (MHz) with increasing sizes and the two im- |    |

|------|-----------------------------------------------------------------------------|----|

|      | plementation types. The 4 bit and 6 bit restricted counters are faster when |    |

|      | synthesized while the performance of the synthesized and IP core is compa-  |    |

|      | rable for higher count sizes                                                | 62 |

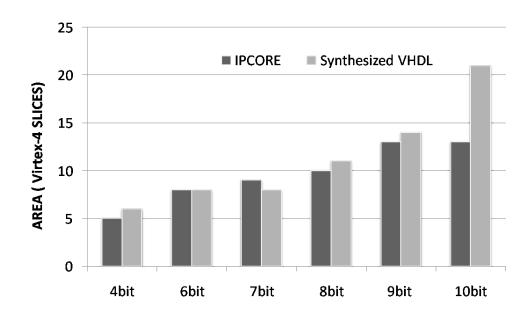

3.14 Variation of Area of un-restricted counters on FPGA with increasing count size and the two implementation types. The area of the counters implemented using IP Core is lesser when compared to the area of synthesized counters. . 63

| 3.15 | Variation of Area of counters with restricted count on FPGA with increasing    |    |

|------|--------------------------------------------------------------------------------|----|

|      | count size and the two implementation types. Restricting the count i.e. count- |    |

|      | ing before the maximum range of the counter, imposes substantial penalty on    |    |

|      | the size of the counter which results in more than doubling the area of counts |    |

|      | up to 8 bit and almost triples the area for the 9 and 10 bit counters          | 64 |

| 3.16 | The backreference Opcode                                                       | 65 |

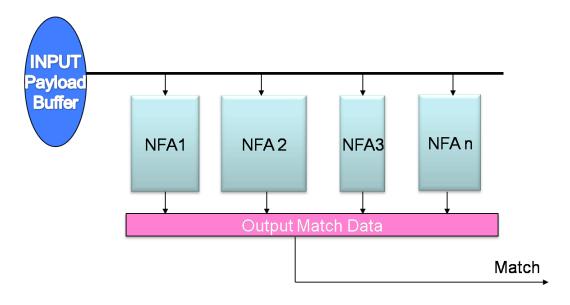

| 3.17 | Multiple NFA engines executing in parallel on a FPGA                           | 66 |

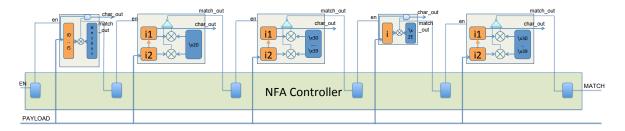

| 3.18 | The NFA derived from the SNORT Rule 'NetBus\s+\d+\x2E\d+'. This                |    |

|      | NFA occupies 71 slices and can run at 331MHz. The NFA controller im-           |    |

|      | plements flip-flops to enable subsequent stages in the NFA and generates the   |    |

|      | match output at the final flop. The NFA controller occupies 2 slices in this   |    |

|      | regular expression.                                                            | 66 |

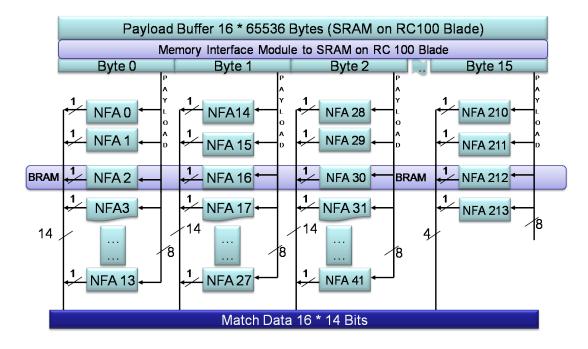

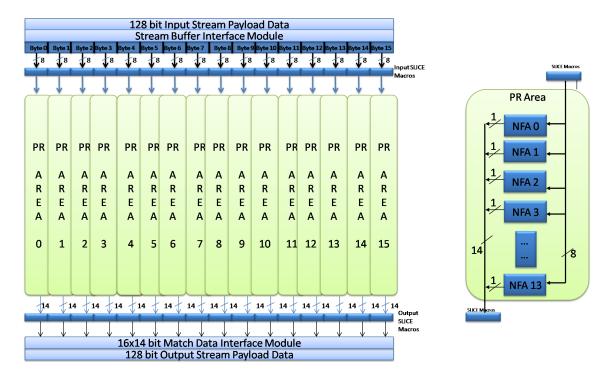

| 3.19 | Architecture of parallel PCRE Engines on Virtex-4 LX 200 FPGA. Each of        |    |

|------|-------------------------------------------------------------------------------|----|

|      | the sixteen byte-wide bank obtains a character from the Memory Interface      |    |

|      | Module and sends them to the 14 NFA engines on that bank. The BRAM is         |    |

|      | utilized by NFAs implementing the back reference opcode                       | 67 |

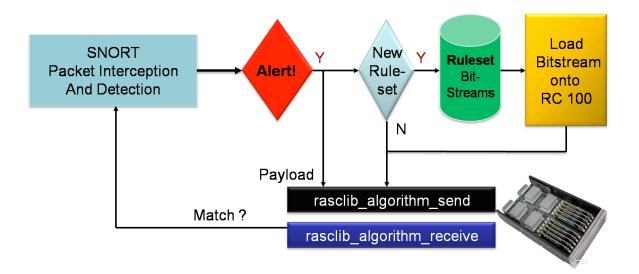

| 3.20 | Overall system using SNORT IDS and PCRE Engines on FPGA                       | 69 |

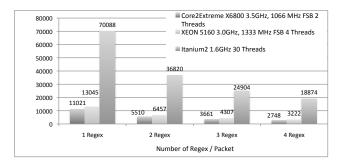

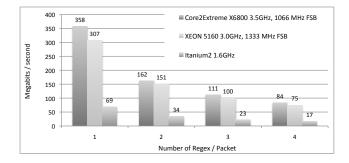

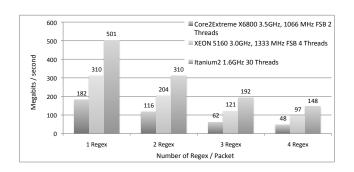

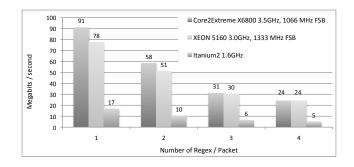

| 3.21 | Comparison of system throughput with varying number of regular expression     |    |

|      | rules executing per TCP payload. The results are shown for software based     |    |

|      | execution in presence of minimal malicious activity in the network payload    |    |

|      | dump                                                                          | 71 |

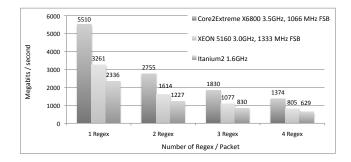

| 3.22 | Comparison of system throughput per processor thread with varying number      |    |

|      | of regular expression rules executing per TCP payload. The results are shown  |    |

|      | for software based execution in presence of minimal malicious activity in the |    |

|      | tcp payload dump                                                              | 72 |

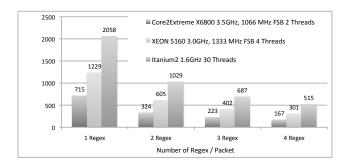

| 3.23 | Comparison of system throughput with varying number of regular expression     |    |

|      | rules executing per TCP payload. The results are shown for software based     |    |

|      | execution in presence of moderate amounts of malicious activity in the tcp    |    |

|      | payload dump                                                                  | 73 |

| 3.24 | Comparison of system throughput per processor thread with varying number      |    |

|      | of regular expression rules executing per TCP payload. The results are shown  |    |

|      | for software based execution in presence of moderate amounts of malicious     |    |

|      | activity in the tcp payload dump                                              | 73 |

| 3.25        | Comparison of system throughput with varying number of regular expression      |    |

|-------------|--------------------------------------------------------------------------------|----|

|             | rules executing per TCP payload. The results are shown for software based      |    |

|             | execution in presence of high amounts of malicious activity in the tcp payload |    |

|             | dump                                                                           | 73 |

| 3.26        | Comparison of system throughput per processor thread with varying num-         |    |

|             | ber of regular expression rules executing per TCP payload. The results are     |    |

|             | shown for software based execution in presence of high amounts of malicious    |    |

|             | activity in the tcp payload dump                                               | 74 |

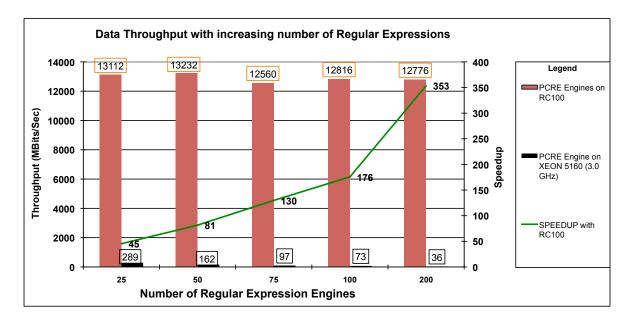

| 3.27        | Throughput of the PCRE engines on the SGI RASC RC100 Blade as func-            |    |

|             | tion of the number of regular expressions. The speedup is in comparison to     |    |

|             | software execution on a 3.0 GHz Xeon. The throuput improvement is 353x         |    |

|             | using 200 regular expressions.                                                 | 77 |

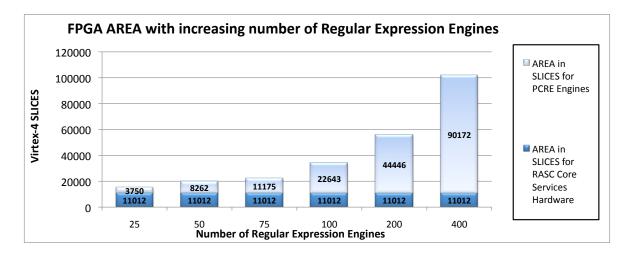

| 3.28        | Area (in slices) occupied by PCRE engines on the Virtex-4 FPGA on SGI          |    |

|             | RASC RC100 Blade. The lower dark section is the fixed area cost dedicated      |    |

|             | to the RASC Core services on the FPGA (11,012 slices)                          | 79 |

| 3.29        | Picture of the RASC RC100 Blade usable on the SGI Altix 4700                   | 81 |

| 4.1         | System Architecture of the dynamic co-processor system on FPGA                 | 89 |

| 4.2         | An example Floating Point IP Core, demonstrating the I/O interface             |    |

| 4.3         | ROCCC system overview                                                          |    |

| 4.4         | The C function call to the co-processor and the #pragma directive              |    |

| 4.5         | Data flow using FSL from the Virtex-4 APU to the static wrapper                |    |

| <b>+</b> .J | Data now using FSD noin the vintex-4 AFO to the static wrapper                 | 74 |

| 4.6  | Data flow using FSL from the Virtex-4 APU to the static wrapper 95             |

|------|--------------------------------------------------------------------------------|

| 4.7  | A compiler generated dynamic wrapper for CORDIC engine                         |

| 4.8  | The Partial Reconfiguration Module Generation Flowchart for FPGA 97            |

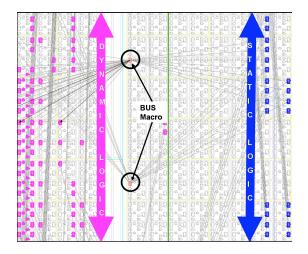

| 4.9  | SLICE macros placed on the Dynamic / Static logic boundary 98                  |

| 4.10 | SLICE usage for various IP Cores, and PR Block occupancy                       |

| 4.11 | Architecture of the Sixteen Partial Reconfigurable Area blocks on the Virtex-  |

|      | 4 LX 200 FPGA. Each PR block consists of fourteen NFA engines. A PR            |

|      | Block, expanded on the right hand side of the figure, obtains one byte payload |

|      | data through the SLICE Macro each clock cycle and outputs 14-bit match         |

|      | data on completion of a match                                                  |

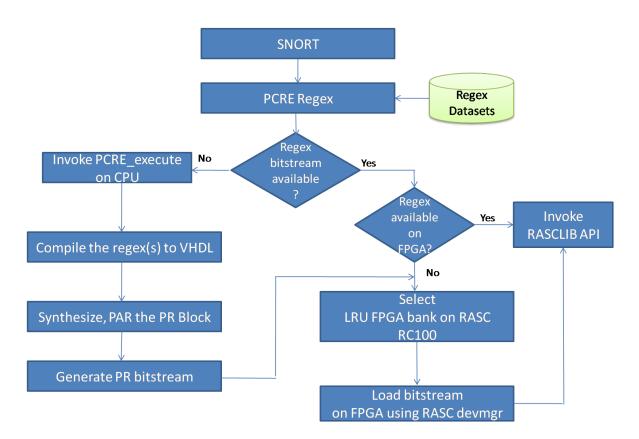

| 4.12 | Using regular expression engines with an integrated FPGA hardware and          |

|      | multiprocessor software flow                                                   |

| 4.13 | System Throughput with increasing number of FPGA reconfigurations / minute.    |

|      | During the FPGA reconfiguration, the software based PCRE engines are uti-      |

|      | lized. Data is plotted for both partial one bank reconfiguration and complete  |

|      | FPGA reconfiguration                                                           |

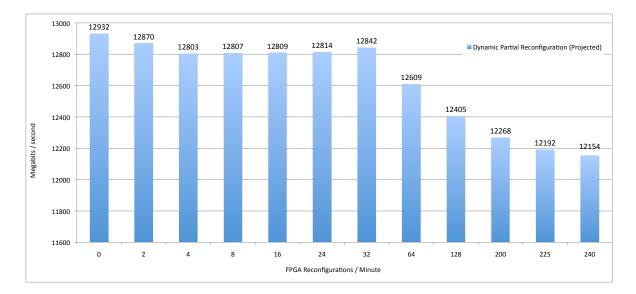

| 4.14 | Projected System throughput with increasing numbers of DPR per minute.         |

|      | With DPR, only the regexes corresponding to the NFA bank being repro-          |

|      | grammed need to be run in software                                             |

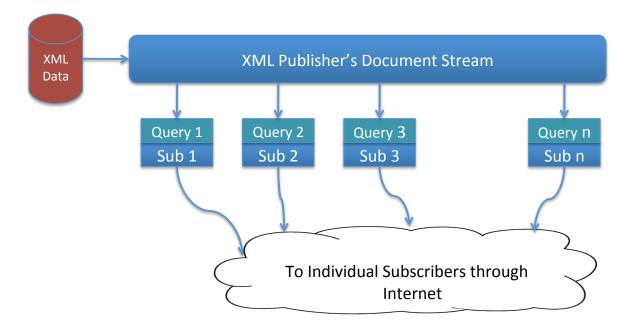

| 5.1  | An XML Publish Subscribe System. A published XML document stream is            |

|      | parsed and filtered through multiple subscriber profiles                       |

| 5.2  | An example XML tree                                                                                   |

|------|-------------------------------------------------------------------------------------------------------|

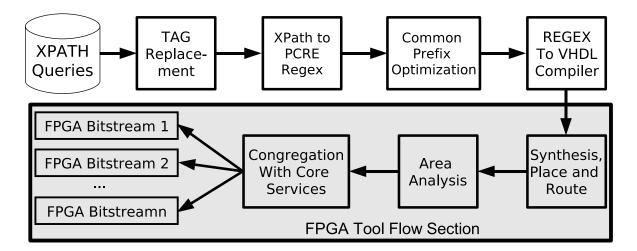

| 5.3  | Compilation Flow of XPath expressions to FPGAs. The XPATH profiles go                                 |

|      | through a four step compilation process to generate the HDL. The lower gray                           |

|      | section denotes the hardware flow for converting HDL to a bitstream for the                           |

|      | FPGA                                                                                                  |

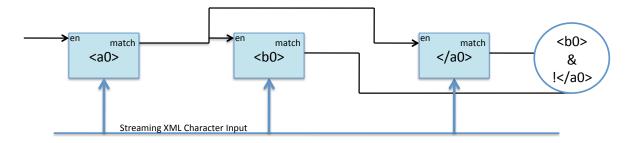

| 5.4  | The block diagram for XPath $\langle a0 \rangle //\langle b0 \rangle$ , showing the implementation of |

|      | the ancestor-descendant axis                                                                          |

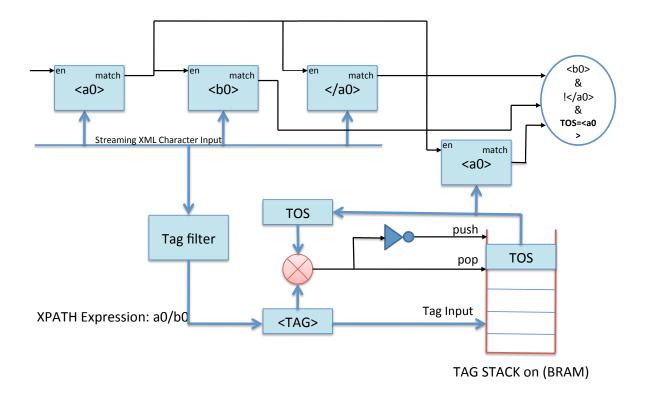

| 5.5  | The block diagram for XPath $\langle a0 \rangle / \langle b0 \rangle$ , showing the implementation of |

|      | the parent-child axis. The additional hardware includes the tag filter, stack                         |

|      | and TOS match blocks                                                                                  |

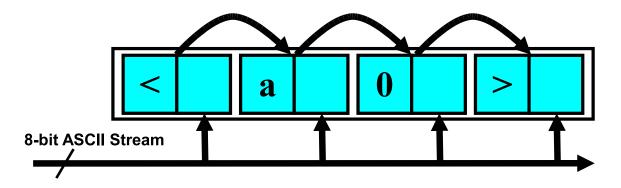

| 5.6  | Block diagram of the Character Match Hardware Block for a tag $\langle a0 \rangle$ . The              |

|      | hardware is a 8-bit x 4 comparator block                                                              |

| 5.7  | Block diagram of the Character Pre-Decoder Hardware Block for a tag $< a0 >$ .                        |

|      | The hardware is a 1-bit x 4 comparator block                                                          |

| 5.8  | An example FPGA organization denoting the input / output data path with                               |

|      | sixteen XPath expressions                                                                             |

| 5.9  | XML document, Tree and Prufer sequence representation                                                 |

| 5.10 | The block diagram for twig matching hardware. This block generates Prüfer                             |

|      | sequence of the XML tags from a streaming document and matches it with                                |

|      | Prüfer sequences of the queries in twig form. This figure is an example of                            |

|      | the query a0[b0]/c0                                                                                   |

## Chapter 1

# Introduction

Stream data processing and inspection involves executing a set of pre-defined processing steps on the streamed sequence of data. Examples of network oriented stream content processing applications include IDS (Intrusion Detection Systems), XML (eXtensible Markup Language) data filtering, video transcoding, image compression, etc. Due to the nature of stream content processing, it involves very low storage overhead during the actual processing step. Moreover stream data processing is highly parallelizable because a stream can be processed across multiple independent engine threads. In fact multiple streams can be processed by multiple parallel threads, all independent of each other. Such kind of applications are amenable for hardware acceleration using silicon devices such as FPGA (Field Programmable Gate Array), ASICs (Application Specific Integrated Circuit) and GP-GPUs (General Purpose Graphics Processing Unit) [127].

### **1.1 FPGAs for Code Acceleration**

FPGA based reconfigurable computing systems are being commonly used to speed up CPU (Central Processing Unit) intensive applications. FPGAs allow speedup of slow sequential software by efficient hardware implementation. Streaming applications are highly suitable for speedup on FPGAs, because the required processing steps can be implemented efficiently as a datapath on the FPGA. Moreover a datapath implemented on FPGAs alleviate the inefficiencies of Von Neumann computing paradigm, by trimming down load store and branch instructions from the traditional CPU datapath.

Modern FPGA devices benefit from Moores' Law, latest silicon processes and feature size. FPGAs provide immense amounts of programmable logic blocks which can be exploited for implementing parallel datapaths from CPU intensive algorithms. Another important advantage of FPGA with respect to other available acceleration devices is its reconfigurablity. FPGAs are programmable hardware devices, and various innovative and custom digital circuits can be implemented on them. FPGAs can be also be reprogrammed to obtain a multitude of hardware capabilities, at different times, as required by the implementation scenario. One drawback of an FPGA when compared to an ASIC or a CPU is its low clock speed, usually an order slower than the highest performing CPUs. Nevertheless, FPGAs can more than make up for the slow clock rate by implementing several parallel datapaths.

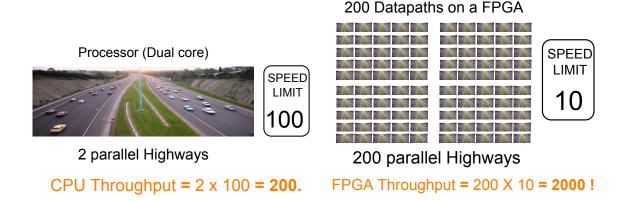

Figure 1.1 demonstrates a simple explanation of how an FPGA, compares to a dual core CPU operating at ten times the clock rate of the FPGA. A datapath could be analogous to a highway and the traffic on the highway is analogous to data moving on the datapath and the speed limit is analogous to the clock speed of the device. A dual core CPU implements two parallel data path at a clock rate of 100 units. The datapath could be two threads of regular expression matching engines. On an FPGA, several of these engines can be optimized and implemented. Each engine operates in parallel, running at a clock rate of 10 units. If we measure the overall throughput of both the approaches, it can be ascertained that the FPGA provides ten times the throughput than what is provided by the CPU.

Figure 1.1: Demonstration of the throughput of a CPU and FPGA: A Highway Analogy. An FPGA with a ten times slower clock rate can offer 10X the throughput of a dual core CPU by implementing two hundred parallel data paths on the fabric.

FPGAs are increasingly being made available as co-processors on high-performance computation systems. In one kind of configuration, the FPGAs are available in blades, which are directly plugged into the backplane of a server. The SGI RASC Blade [4] available on SGI Altix 4700 [151] shared memory computing system is one such example. The available maximum data throughput for this blade is 6.4 GBytes/s. In other kinds of implementations, FPGAs are usually packaged in modules, which are dropped in CPU sockets on server

motherboards. Examples include bridged FSB-FPGA [123] on Intel Xeon platforms, Quickpath interconnect [191] on new Intel platforms and Hypertransport [12] interfaced FPGA on AMD Opteron platforms. One of the first systems of this kind is the Cray XD-1 supercomputer [1]. The Intel FSB FPGA architecture provides upwards of 8.5GBytes/s throughput. The Xtremedata [5] XD1000 coprocessor device [210] using a single channel 8-bit Hypertransport provides 0.5 GBytes/s throughput.

High density FPGAs such as Xilinx Virtex-4LX 200 [195], Virtex-5 LX [207] and Altera Stratix II EP2S80F [9] containing millions of logic gates, abundant high speed dual port memory hardware ALU blocks on current feature sized silicon fabric (90nm, 65nm, 40nm) have been used in these accelerator systems. Modern FPGAs also integrate a (hard or soft) processor core, with the reconfigurable fabric. These FPGAs provide multiple specialized I/O transceivers [206] [10] which can operate from 600Mbps to 6 Gbps. The acceleration architecture involves streaming input data from a host processor to the FPGA, which is then processed by the various hardware datapaths, with the eventual streaming out of the results back to the host processor. The host processor is relegated to the simple task of setting up DMA based data transfer from memory to the FPGA, thus resulting in very high throughputs [10] [206]. A typical FPGA based application acceleration scenario includes profiling / inspecting the software code to ascertain the slowest executing program components. These program components are transformed to equivalent HDL (Hardware Description Languages) for implementation on FPGA. The HDL code is synthesized and implemented on FPGA. Simulation after Place and Route can provide an accurate representation of the theoretical speedup, provided by the FPGA. Various application from a wide range of domain have been successfully accelerated on FPGAs. The application domain for utilizing FPGA based code acceleration include computer databases [209], regular expressions [116] [162], molecular dynamics [186] [185], image and signal processing [73] [117] [115], bio-infomatics [55][44], option pricing models [211], signature detection, [168], etc.

The transformation from a high level language description to HDL is a very challenging task, due to incompatibilities in the execution paradigm between a traditional CPU and on an FPGA. Architectural limitations on an FPGA based accelerator includes lack of pointer based memory addressing, lack of dynamic memory allocation, limited stack size, lack of an ISA (Instruction Set Architecture) and absence of cached memory access. Thus, to accelerate a program written in high level language on FPGA the above mentioned limitations have to be factored in before conversion to HDL. As an example, pointers need to be converted to array accesses in C loop nests and regular expression that demand nesting on a stack need to be simplified. Manual translation from high level programming language to HDL has been used in the past, but it quickly manifests itself as an impediment to a wider use and is prone to errors. Compilation frameworks thus are a valuable tool for translating traditional high level description languages to FPGA.

## **1.2 Regular Expression to HDL**

An example of a widely used inspection and parsing application is regular expression. In regular expression matching process, the input stream is inspected for the existence of one or more member strings of a given regular expression. Regular expressions are usually implemented as one of DFA or NFA in software based systems. DFA implementation is unsuitable for hardware due to the state space explosion of implementing a DFA, and the accompanying memory requirements. NFA based implementations try to mimic parallelism on software based execution by using a stack. Since the software can evaluate only one transition at a given time, a stack based implementation can store the other transitions for future evaluation at a later time. On the other hand FPGA provides inherent hardware based parallelism, which allows an automata to evaluate more than one state transition at the same time. Therefore NFA based implementations are extremely suitable on FPGAs. One area which has seen a rapid growth in use of regular expressions is Intrusion Detection System (IDS). Increase in malicious activities using computer networks as a medium, has also resulted in an increased deployment of IDS that scan and intercept network packets containing signatures of such activities. SNORT IDS, one the most popular open source IDS uses PERL compatible regular expressions (PCRE) for its regular expression based rules. Network payload data are streamed to a PCRE engine and is tested with a regular expression deemed suitable by SNORT. The NFA based regular expression model used by PCRE imposes a high demand on the computation power needed to execute regular expression matches. With current network data links approaching 10 Gbps and higher, software based regular expression engines working on network payloads are unable to cope up with the link throughput while looking for malicious signatures within network packets, especially during an active attack. Thus a FPGA based implementation of regular expression rules can result in speeding up of an IDS. More so, since a network payload is frequently tested on more than one regular expression rule, an FPGA based accelerator can parallelize the regular expression matching, by testing the payload through the required rules simultaneously.

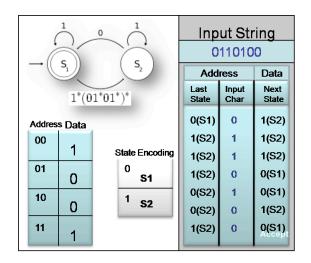

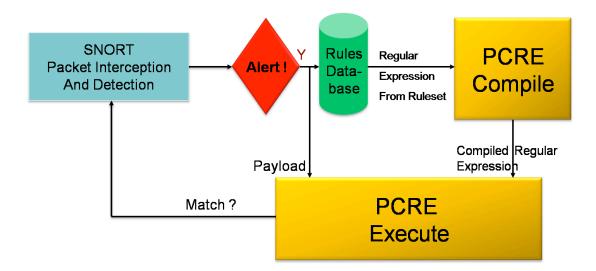

Our compilation tool converts a PCRE to HDL via PCRE opcodes. This tool solves a very important limitation towards implementation of PCRE on FPGA. This tools uses the front end parser of the PCRE compiler which produces opcodes based on the regular expression operands which are in turn obtained from a regular expression. In the original software implementation, these opcodes are executed by a software based PCRE engine running on a processor. In order to accelerate PCRE, our tool allows us to implement the opcodes on a FPGA based PCRE engine. The current implementation of the tool operates within the limitations of FPGA hardware and does not currently support regular expression operations that could require nesting / recursion. Our tool compiles the PCRE opcodes obtained from a regular expression and creates HDL code for each of them. Our compilation tool then integrates the hardware opcode blocks with a NFA controller which is then implemented on a FPGA. Moreover multiple regular expression rules are connected to the same input data stream, allowing a network payload to be tested against multiple rules at the same time. Multiple input data streams can also be matched in parallel banks on suitable FPGA hardware that supports multiple input streams, for example SGI RASC Blade.

In a load balanced software implementation of SNORT, multiple IDS processes generate multiple network payload test requests, which are processed by multiple instances of PCRE engines in parallel. We solve the problem of accelerating such systems by implementing multiple banks of regular expressions, with each regular expression bank catering to one of the IDS process. With a 128-bit wide input data bus (available on SGI RASC Blade), a single FPGA can cater to sixteen 8-bit input payload threads. Additional FPGAs can implement many more regular expression banks or can replicate the banks, as deemed necessary.

## 1.3 FPGA Reprogrammability

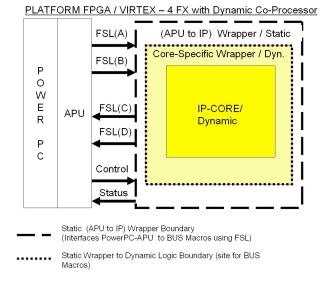

Unlike ASICs and hard silicon devices, FPGAs allow reprogrammability of the hardware. This powerful feature increases the versatility of FPGAs, and increases the number of applications that can be accelerated. FPGA based accelerators typically utilize a fixed width input / output data interface. The accelerator hardware block connects to this interface and thus is able to send / receive data from the host processor. Interfacing the available library of accelerator blocks to the FPGA interface is a time-consuming and tedious task which almost always, needs to be taken care of manually. The system designer is left with the task of interfacing each and every accelerator blocks, (usually available as IP cores) to the data interface. In order to solve this problem, we have developed a tool that automatically generates the communication interface between the data interface and a tightly coupled IP core based

accelerator (co-processor) system on a CSoC (Configurable Systems on a Chip) i.e. Virtex-4 FX FPGA. It generates hardware wrappers for the IP core that makes the hardware look like a C function invocation in the host processor source code. Thus a 'C' function call in the host processor can change the functionality of the FPGA base co-processor by reprograming the required bitstream. The SGI RASC library uses a similar mechanism by which an API call can reprogram the Virtex-4 LX 200 FPGA on the blade with a new bitstream.

Partial reconfiguration on the FPGA makes it possible to create a system that allows reconfiguration of pre-assigned parts of the FPGA without affecting the static parts, or inducing a system-wide reset. It is a very powerful tool to overcome the area limitation of a single FPGA platform across multiple applications. The system designer is usually left with the task of generating the interface between static and dynamic regions of the FPGA as required for partial reconfiguration. We extend the aforementioned interface generation tool to support partial reconfiguration, by generating an interface wrapper that delineates the static and dynamic regions on the FPGA. This feature is useful on CSoCs that implement basic hardware peripherals along with a co-processor on the same reconfigurable fabric.

Another application for utilizing partial reconfiguration on an FPGA are situations that demand quick adaptability. Software defined cognitive radios have used this functionality for a while to adapt the hardware towards external changes in the air interface.

There is a limitation to the number of regular expressions that can be implemented on an FPGA. Fast changing network activity scenario, can lead to the IDS selecting among different rulesets in a short period of time. Reconfiguration of the FPGA with the type of intrusion

detection engines required at the moment enables adaptability to change with network conditions. Partial reprogrammability of the FPGA can be used to cater to such dynamic situations, when only few rulesets of regular expression rules changes over short intervals of time. IDS that employ these FPGA can maintain execution through software threads during the brief moment, when the FPGA is being reconfigured Moreover an IDS with two or more FPGAs can maintain execution on the other FPGA(s) while one of them is either partially or fully reconfigured with a different set of regular expression engines. In order to implement an adaptable IDS that allows a single bank of regular expression to be re-programmed keeping the other banks intact, we have added modularity to our aforementioned regular expression architecture. With our modular architecture, regular expression banks can be quickly swapped in order to adapt to changing networks scenarios.

### **1.4 XML Filtering on FPGA**

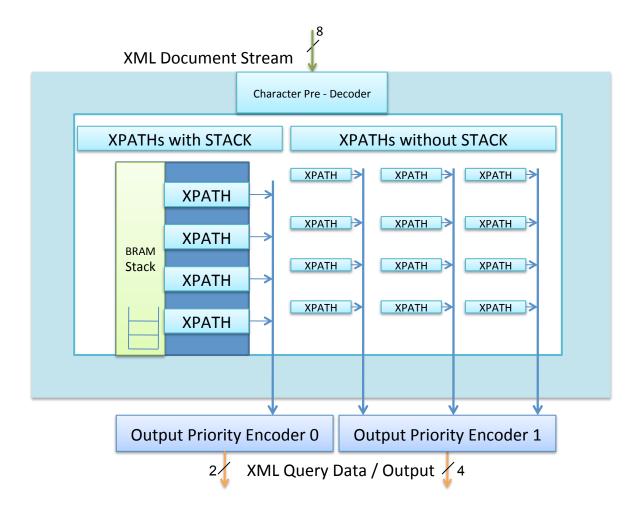

Streaming XML filtering is being used abundantly for publish/subscribe applications (or simply pub-sub). In pub-sub, the message transmission on the internet is guided by the message content, rather than its destination IP address. Selective deliverance of parts of XML documents, is obtained by filtering the document through multiple filters described in high level language such as XPath. In pub-sub systems, each individual subscriber interest is described by an XPath expression. XPath expressions consists of a sequence of XML tags and the relationship between the tags are expressed as axes. XPath infers a a tree based navigation over an XML document, and involves a parent-child axis and ancestor-descendant axis. XPath profiles can be easily converted to PCRE. The XML tags are converted to character match blocks, while the axes define the regular expression sequence. We have used a conversion process to convert XPaths to PCRE. Thereafter we have employed our PCRE to HDL compiler to implement XPath profiles on hardware. The only other addition required would be a XML tag STACK to verify a parent-child axis. Pub-sub involves streaming the same document across multiple XPath profiles, and thus all the subscriber profiles can execute in parallel on a FPGA. Moreover XPath profiles share commonality in their prefix, and hence are optimized to share the common prefix and reduce the area occupied on FPGAs.

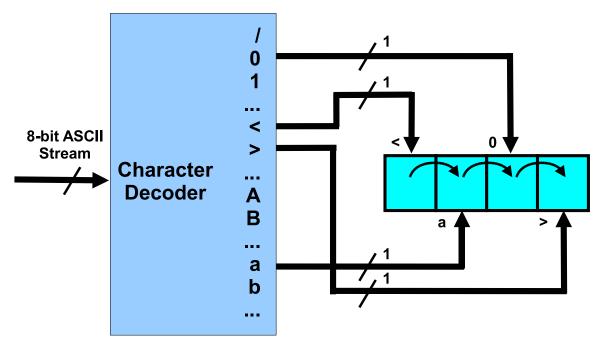

Implementing XPath profiles on FPGAs mainly involves implementing character matching blocks to identify XML tags in the input document stream. The character matching hardware block compares sequences of characters from the input stream to a given sequence that define an XML tag. The implemented character matching blocks for the XML tags consist of many redundant blocks, the prime examples being the open tag '<', close tag '>', and end tag '/' characters. It is possible to simplify the design with a 8-bit stream ASCII decoder. This decoder can be used to decode the 8-bit XML data input into one of each 256 1-bit output per clock cycle. Identifying an XML tag in the input stream would thus involve a simple controller, one that checks for a given sequence of 1-bit decoder symbols. Due to this simplification, the XML filter design using a ASCII decoder is area efficient and it runs at a higher clock rate when compared to the design using character match blocks.

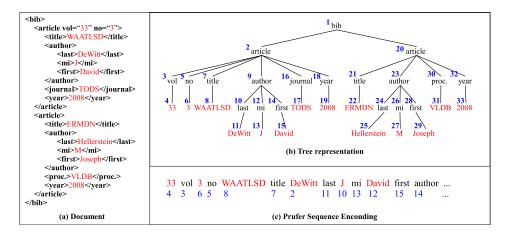

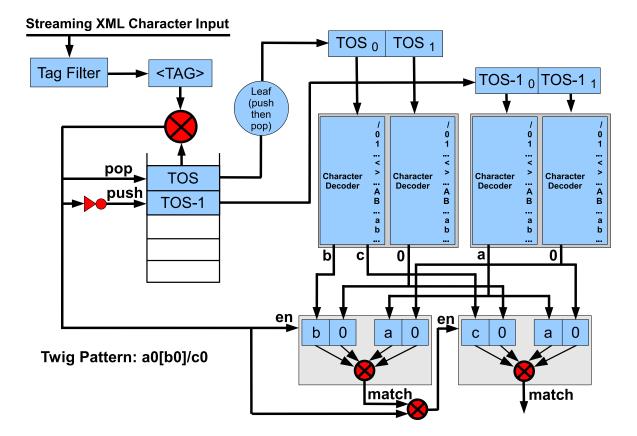

XML queries are also formed from twig structures, which include multiple path queries

in a single query. Such queries can be converted to a sequence of tags / tree nodes also known as a Prüfer sequence. An XML document is also converted to its Prüfer sequence. Thus the problem of matching a twig query would now involve matching the given Prüfer sub-sequence of the twig with the Prüfer sequence of the document.

## **1.5** Contributions

#### **1.5.1** Compiling PCRE to FPGA and accelerating SNORT IDS

We present a novel method to compile PCRE Operation Codes (opcodes) directly to VHDL for parallel implementation on FPGA hardware. We implement the PCRE regular expressions from the SNORT IDS using a two stage translation process. In the first stage, the SNORT IDS rulesets are compiled using the PCRE compiler to generate PCRE opcodes. In the second stage the PCRE opcodes are translated to VHDL hardware blocks suitable for implementation on FPGA and connected together using a NFA based control logic. Our system maintains the execution semantics of the software based regular expression engine on the FPGA hardware, thus ensuring compatibility with the SNORT IDS ruleset. The interface throughput suffices for wire-speed payload scanning of even the fastest available ethernet interfaces. Our design is a compile once, NFA based design, with re-compilation necessary only for new and updated rules. We obtain more than 350X speedup with our FPGA based regular expression engine architecture when compared to a baseline state of the art CPU, the Intel Xeon 5160. Our design can sustain a throughput of 12.9 Gbps. The specific contributions include:

- Compilation of PCRE opcode to hardware. We modified the PCRE compiler v6.7 by adding an opcode dump module to the PCRE compilation library. We then process the generated opcodes and related operands using successive compilation steps and convert them to VHDL blocks. The VHDL opcode blocks are tied together in an NFA and are synthesized and implemented on the FPGA.

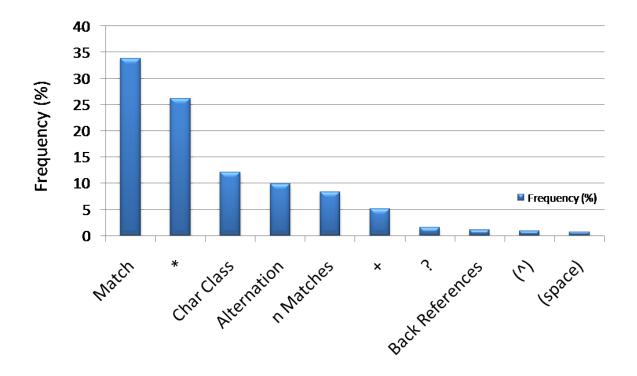

- Quantitative Evaluation of PCRE opcodes. We investigate the frequency of the opcodes which make up regular expression rules in SNORT DB2.4 using the modified version of the PCRE compiler. We have removed the NETBIOS rules from the database since it is suggested by the security community [54] that this ruleset be disabled because the rules may generate a lot of false positives, and these rules are not pertinent to Internet based traffic. We have ascertained, using the results, that the character match is the most prominent opcode ( 34%) followed by the Kleene closure operator '\*' ( 26%). Our design is currently limited to the frequently occurring opcodes in SNORT DB. Moreover due to hardware limitations, we concentrate on regular expressions that do not involve backtracking.

- Implementation Details of the PCRE opcodes. We discuss detailed FPGA based implementation of important PCRE opcodes. We compare two important implementation paradigms i.e. utilizing IP core based opcode generation and secondly by synthesizing the opcodes from VHDL code. We provide data on the variation of area and speed of

important opcodes generated using the two paradigms. We provide additional details with respect to quantifier opcodes. We provide data on the size of counters required to deal with the specific range of counts that occur after the compilation of SNORT rules. We also document the variation of FPGA area with increasing number of regular expressions.

- Implementation of SNORT Regular Expression Rules on FPGA Platform. We have designed an FPGA based regular expression IDS with clock speed of 155MHz and 128bit payload I/O per clock cycle. It is possible to run regular expression based IDS on the Virtex-4 LX 200 FPGA at a maximum sustained throughputs of 19.84 Gbps. We obtain more than 350X speedup with our FPGA based regular expression engine architecture when compared to a baseline state of the art CPU viz. the Intel Xeon 5160 and our design can sustain a throughput of 12.9 Gbps on the SGI RASC Blade.

- Detailed Benchmark of a Load Balanced IDS with Regular Expression. We conduct detailed benchmark of software based regular expression IDS, under various network scenarios, using three different multiprocessor systems. We demonstrate, with a first of a kind comprehensive experiment, that, even on a thirty core Distributed Shared Memory (DSM) system, a software based IDS using regular expression, can reduce the network throughput from 10 Gbps to nearly 150 Mbps when the amount of malicious activity increases in the network. We demonstrate the case when 30% or more number of network packets trigger regular expression matching, the software based IDS cannot

maintain 10 Gbps throughout, and thus requires hardware acceleration.

• Comparative Evaluation of CPU and FPGAs. Multi-CPU load balanced IDS approach[63] entails huge cost in terms of the hardware infrastructure, with the cost of components like memory, motherboards, disk drives and also power consumption and cooling costs adding up. We provide an analysis into the projected performance of a FPGA vis-a-vis a high end dual core processor while executing regular expression matches, and in this dissertation, we estimate the power savings enabled by the use of FPGAs in such designs.

#### **1.5.2 Dynamic Co-Processor Interface Automation**

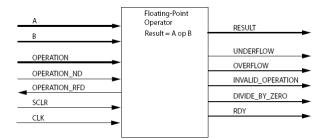

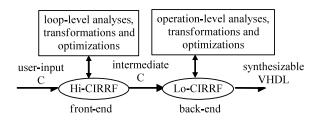

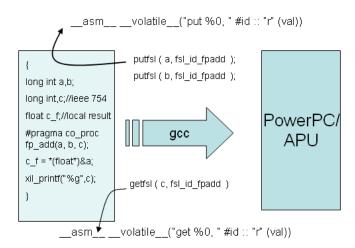

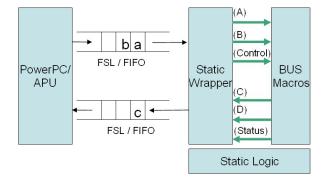

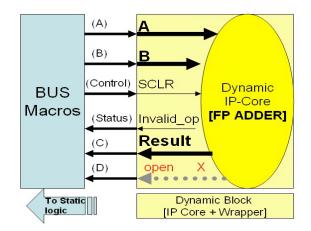

In this dissertation. we describe a software tool for automatically generating the communication interface between the software running on the CPU and a tightly coupled IP core based co-processing system on the Virtex-4 FX FPGA. We use the software tool to extend our compiler for FPGA-based reconfigurable systems, ROCCC [72] which leverages the huge wealth of IP cores by allowing the user to import these cores into the software source code. Our tool generates hardware wrappers for the core that makes it look like a C function invocation in the source code. Using this tool, the compiler automatically generates a wrapper structure that would hide the timing and stateful nature of the IP Cores and makes each available to the C language compiler, as an un-timed side-effect free function call.

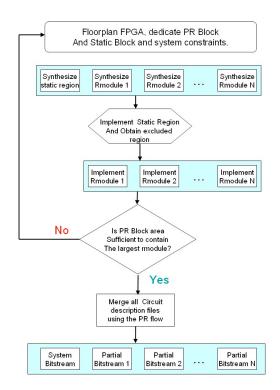

We extend this tool to support partial reconfiguration: the same static wrapper is used for multiple cores and the user selects a given core to be invoked in the 'C' program. We support

run-time reconfiguration by automating the generation of the interface between static and dynamic regions of the FPGA. The user can switch between multiple functional units by calling the appropriate C function in the code, thus entailing the use of the same hardware wrapper for multiple IP Cores. Utilizing our software tool along with the ROCCC infrastructure we have been able to automatically configure multiple IP-cores on the fabric viz. FP (Floating point) Adder, FP Multiplier, Integer divider CORDIC engine and an FFT engine.

Moreover using partial reconfiguration we have been able to overcome the area limitation of a single FPGA platform (Virtex-4 FX12), using five different IP Cores. We have allocated a region of 1800 slices for the co-processor, thus resulting in a reduction in the floor area by 2656 slices due to partial reconfiguration. Moreover the area dedicated for the hardware wrapper is no more than 14 slices, quite miniscule, when compared to the actual IP Core area.

#### **1.5.3** Adaptive Hardware/Software Regular Expression Based IDS

FPGAs can be reprogrammed to change it's functionality. This allows reconfiguration of the FPGA with the type of the intrusion detection engines required at the moment i.e. adaptability to the current network conditions. Additionally Xilinx FPGAs and some custom developed FPGAs [161] also support partial reconfiguration flow, so that a part of the FPGA could be reconfigured. This reduces the hardware re-programming time, when only a part of the FPGA needs to be modified. IDS that employ these FPGA can maintain execution through software threads while the FPGA is reconfigured during the brief moment. Moreover an IDS with two or more FPGAs can maintain execution on the other FPGAs while one of them is either partially or fully reconfigured with a different set of regular expression engines. An FPGA system supporting partial reconfiguration can respond to new types of network attack much faster than FPGA systems that only support full reconfiguration.

With our proof of concept hardware system, our novel design allows partial reprogramming across 16 banks of regular expression rule-sets can successfully maintain throughput at 10 Gbps scale even under a range of partial and full reconfiguration scenarios running on a proof-of-concept platform. We use our PCRE to HDL compiler to compile regular expression based rules to VHDL. Similar rules are grouped together in banks of rule-sets. We implement our adaptive IDS on a Virtex-4 LX 200 FPGA that has been floor-planned for partial reconfiguration across 16 banks of regular expression rule-sets.

We have also benchmarked our proof of concept FPGA accelerated regular expression based IDS test-bed using a thirty-two core SGI Altix 4700 supercomputer with a RASC Blade consisting of two FPGAs. We implement 448 different regular expressions in 32 modular rule-sets, on the two FPGAs. Such an architecture is a first of a kind demonstration of an adaptable hardware/software regular expression based IDS. We show that by utilizing our architecture, it is possible to avert concerted attacks and also to adapt towards changing network activities, by performing multiple partial and full reconfigurations. We measure the throughout of the integrated Field Programmable Gate Array (FPGA) and multiprocessor SGI Altix system with varying number of reconfigurations per minute. The maximum sustainable throughput of our design is 19.84 Gbps per FPGA. Our adaptive IDS can provide better than 10 Gbps throughput even with 32 partial reconfigurations per minute. Our system can also sustain 10 Gbps throughput with four full-reconfigurations per minute. Our IDS design can be extended to similar FPGA accelerated multi-processor system.

#### **1.5.4** Boosting XML filtering with a scalable FPGA-based architecture

The growing amount of XML encoded data exchanged over the Internet increases the importance of XML based publish/subscribe (pub-sub) and content based routing systems. The input in such systems typically consists of a stream of XML documents and a set of user subscriptions expressed as XML queries. The pub-sub system then filters the published documents and passes them to the subscribers.

Pub-sub systems are characterized by very high input XML data rates and therefore the processing time is critical. Given the high volumes of messages and profiles, the filtering process becomes a critical performance requirement for pub-sub systems. Since pub-sub XML filtering involves multiple parallel queries processed over a single document data-stream, it is possible to utilize FPGAs for improving the filtering performance. Each query can be implemented on the FPGA unit as a hardware datapath circuit and with appropriate optimizations it is possible to fit thousands of queries on a single FPGA chip. This results in accelerated query processing and leads to substantial savings in general purpose computation infrastructure, and thus reducing the amount of power required by the infrastructure.

We utilize a four step approach that converts user profiles expressed as XPath queries into hardware description language, suitable for implementation on FPGA. The first step involves conversion of an XPath query to PERL compatible regular expressions. The regular expressions are clustered by their common prefixes in order to produce more compact representation on the board and are then translated to VHDL using our "PCRE to VHDL" compiler. Moreover, in order to support parent-child relationships, we introduce the use of stacks and modify the regular expression hardware to use them. The highly optimized VHDL code is then deployed on the Virtex-4 LX 200 FPGA on SGI RASC Blade. The stream of documents is forwarded to the RASC Blade where it is processed with high degree of parallelism. Our experimental evaluation reveals that this architecture achieves orders of magnitude improvement in the terms of running time compared to the state of the art software based XML filtering systems.

We investigated the XPath filter architecture and came to the conclusion that most of the FPGA area was being used by XML tag match blocks, which in turn consist of 8-bit character match blocks. In order to further improve the area efficiency of the XPath hardware we incorporated a stream ASCII decoder, which would decode the incoming XML stream at the input and produce 256 1-bit outputs. The character decoder hardware block simplifies the design of the XML tag match blocks by replacing a 8-bit character match comparator with a 1-bit comparator. Moreover using multiple 1-bit data lines instead of routing the 8-bit input stream over the FPGA, reduces the routing overhead, which in turn leads to a design with faster clock speed. The average area improvement by using a character decoder at the input over distributed character matching blocks is 1.5X while the clock speed improvement is 2.5X. We have also with described our hardware implementation of streaming Prüfer sequence conversion of an XML document. We also describe how we can execute twig pattern matching using the generated Prüfer sequence. Our hardware can accurately match parent-child relationship in the twig patterns.

# Chapter 2

# **Related Work**

In this chapter we describe related work with respect to implementation of efficient IDS systems using string and regular expression based approaches. We also discuss various hardware based approaches for accelerating string and regular expression matching. We also discuss software based load balanced IDS systems, and hardware based approaches to accelerate SNORT IDS.

# 2.1 Network Intrusion Detection Systems

Network Intrusion Detection Systems originated as software string matchers which worked with the NIC drivers and LIBPCAP [184] to filter malicious packets from the ingress / egress links on a location. Very soon the throughput of the software based NIDS began to dwindle, mainly due to the serial execution approach on a Processor. Moreover executing Regular Expression engine in addition warranted a hardware oriented approach to deal with ever increasing number of rules which a network payload goes through.

#### 2.1.1 IDS engines with String Matching

Initial versions of SNORT started with string based pattern matching on a ruleset comprising of string matches. These string matching algorithms are continuously being optimized for Software execution, on newer processors. A very important algorithm for state based string matching is the Aho Corasick [6] method. Worst case performance improvement over Aho Corasick was improved with [179] by Tuck, Sherwood, et al, by utilizing path-compression on the Aho Corasick algorithm. Commentz - Walter [51] and Wu [193], propose similar string matching algorithms which preprocess the data structure.

Various improved versions of string matching algorithms are implemented on a variety of Hardware such as FPGA and ASICs. Since hardware execution provides orders of magnitude improvement over software execution of string matching algorithms, thus it is imperative to utilize optimized hardware for current multi GBits/s rate network interfaces. FPGAs provide the dual benefits of fast optimized hardware execution along with great flexiblity to compile and re-program the hardware quickly and efficiently. The use of parallel bloom filter [35] architecture on FPGA has been introduced by [58]. [168] have documented a method to compile C code of bloom filter based text scanners to VHDL and achieve high throughput (18 Gbps) on Virtex II FPGA. [175] and [88] detail on a high throughout design of the Aho-Corasick engine for string matching based IDS on Application specific silicon by converting the Aho Corasick algorithm into multiple binary state machines. Also known as

the bit-split optimization for string matching this optimized engine is documented in detail in [174]. [163], detail a CAM-based pattern matcher FPGA design that additionally predecodes characters. [164] also target Virtex-2 FPGA with a fine grained pipelined string matching hardware to achieve 10Gbps throughput. [47] detail out a silicon to implement a hardware based string matching coprocessor for SNORT IDS that runs at 7 Gbps. Their ASIC design provides a high performance platform for pattern matching. [16][15] demonstrate an FPGA implementation of the Knuth-Morris-Pratt algorithm for string matching suitable for IDS applications at 2.4Gbps. Area constraints on string matching hardware on FPGAs have been solved in [213] by utilizing bit-level hardware sharing CAM. The authors also mention on the performance and space efficiency of many other approaches towards efficient high speed hardware implementation of string matching which are proposed in an 2.88Gbps FPGA based hardware in [48], and in an 2Gbps FPGA based hardware in [68]. Novel hardware oriented methods namely Hash Boyer Moore algorithm implemented on Intel IXP network processors with a throughput in close vicinity of 2Gbps have been researched by [125]. A programmable systolic array based FPGA implementation of Knuth-Morris-Pratt string matching by [18] provides 2.4Gbps throughput for use as an IDS. [49] have developed a Platform FGPA based embedded intrusion detection system that includes the network packet decoder as well as the SNORT rules based IDS on a single platform FPGA chip.

#### 2.1.2 IDS engines with Regular Expression Matching

Research initiatives over the past decade have resulted in optimized Regular Expression engines in software as well as hardware which result in fast execution, in order to keep up with increasing data rates of network interfaces.

Song, et al. [160] have also identified the core problem with NIDS, that the throughput reduces drastically while processing malicious packets. Software optimizations have been proposed to mainly target the 1Gbps throughput barrier on general purpose processors. [212] suggest optimizing techniques on DFAs generated from regular expressions to reduce their execution times and achieve 50 to 700 times speedup. But their method also asks for rewriting of the SNORT rulesets, which may not be supported by the community due to their adherence to PCRE standards. [95] have demonstrated graph theoretic algorithm to generate D2FA from DFA by combining multiple transitions in order to reduce the memory requirements of DFAs by more than 95%. Their design enhances Cisco network appliance by reducing embedded memory requirements. [94] have categorized three deficiencies viz. Insomnia, Amnesia and Acalculia, in DFA based execution paradigm and have proposed relevant mechanisms to deal with such problems. Networked cluster based approach for load balancing NIDS has been well documented in [183], [189] and [190]. Katashita et al. [91] explore the potential of porting SNORT rule-set 2.3 using a space efficient NFA hardware on FPGAs and suggest a theoretical maximum throughput of 10 Gbps on a Virtex2-8000 with 64bit datapath. DFA based regular expression engines have been targeted towards FPGAs mainly for parallel execution on smaller FPGAs by Moscola et al. in[122] and Lockwood et al. in[104][103]. The authors

utilize the JLex library to generate description of regular expressions from SpamAssassin rules.

Hardware oriented state of the art architectures utilize FPGAs, ASICs as well as GPG-PUs. Tarari Inc. [182] have demonstrated a 6.2 Gbps using a state of the art GPU, to power a malware scanning acceleration engine. FPGAs have been utilized on various IDS architectures, due to their ability to execute parallel regular expression based scanning engines, and the possibility to compile regular expression based rules to hardware, thus leading to immense flexibility vis-a-vis hardware generation and modifications. Compilation of regular expressions to hardware circuits were proposed more than two decades ago in a seminal work by [66]. Regular expressions can be implemented on a given hardware by utilizing two paradigms which are DFA and NFA. DFA entails faster execution, by sacrificing the space requirements, which could exponentially blow up, while NFAs entails  $O(n^2)$  space requirements but by processing one character at a time. With the advent of FPGAs with several hundred megahertz clock rates, and high speed I/O interface to the host processors, it has been made possible to speed up NFAs on FGPAs. It is also possible to enable parallel matching paths using NFAs on FPGA. Current research on NFAs used for regular expression Matching have resulted in optimization of speed and area on FPGAs. Sidhu, Prasanna provide a highly detailed work on implementing and optimizing NFAs for use on FPGAs [154]. In fact they propose a fast algorithm that generates the NFA on the FPGA hardware, rather than compiling it from software. Generation of several regular expression operators including single character match, alternation, concatenation, and Kleene closure have been detailed in this work. [169] improves the FGPA based NFA / Regular Expression model by implementing very fast partial character decoders on the hardware. [120] implement a combined pipelined character grid string matching as described in [15] combined with NFA based regular expression matching. [84] proposed optimized space usage of NFAs via common prefix sharing, as well as a design philosophy built on [154] by including some additional regular expression operators i.e. '?', '.', and '[]'. Their design involves a pipelined broadcast tree for ensuring maximum throughput. [43] develop new hardware structures to implement FSM based regular expression engine. On their actual hardware test they obtain a 4Gbps sustained throughput on a 133MHz Virtex-II FPGA. [101] propose various optimization methods including prefix infix and postfix sharing of regular expressions on an older version of the SNORT ruleset. Overall their methods bring about 20% reduction in on chip area, but its effect on clock speed is not discussed. [177] propose utilizing Block RAM resources on the FPGA for storing LUT data, and hence free up LUT resources on the chip. It results in a savings of 26% power compared to LUT based implementation of control logic for Finite State Machines. [32] touch upon a VHDL generation scheme of NFAs from SNORT ruleset. They utilize extensive size optimization on NFAs including prefix sharing, Character Class Sharing and Static Pattern sharing. Their design results in a throughout of 2Gbps on a Virtex-4 FPGA, which suffice for 1GbE or slower network connections. [162] describe three building blocks that optimize constrained repetitions in regular expressions. They utilized their VHDL based hardware blocks to generate overall area efficient IDS systems on FPGA. The maximum throughput corresponding to their improved design is 3.2Gbps on a Virtex-4