# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Design Considerations of Graphene FETs for RF Applications

#### **Permalink**

https://escholarship.org/uc/item/2rk2j7rb

#### **Author**

Lee, Kangmu Min

### **Publication Date**

2016

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# **Design Considerations of Graphene FETs for RF Applications**

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Nanoscale Devices and Systems)

by

Kangmu Min Lee

### Committee in charge:

Professor Peter Asbeck, Chair Professor Prabhakar Bandaru Professor Gert Cauwenbergh Professor Yuan Taur Professor Paul Yu

| The dissertation of Kangmu Min Lee is approved, and it is |       |            |       |      |     |             |    |

|-----------------------------------------------------------|-------|------------|-------|------|-----|-------------|----|

| acceptable                                                | in    | quality    | and   | form | for | publication | on |

| microfilm a                                               | and o | electronic | ally: |      |     |             |    |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             | _  |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             | _  |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             | _  |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            |       |      |     |             |    |

|                                                           |       |            | Cha   | air  |     |             |    |

University of California, San Diego

2016

# **Dedication**

This dissertation is dedicated to my family.

# **Table of Contents**

| Signature Pa    | geiii                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------|

| Dedication      | iv                                                                                                         |

| Table of Con    | itentsv                                                                                                    |

| List of Figure  | esviii                                                                                                     |

| List of Table   | sxiv                                                                                                       |

| Acknowledg      | ements xv                                                                                                  |

| Vita            | xvii                                                                                                       |

| Abstract of the | he Dissertation xx                                                                                         |

| Chapter 1       | Introduction11.1. Graphene Strucuture and Electrical Properties31.2. Material Preparation of Graphene5     |

|                 | 1.3. Graphene Field Effect Transistor(GFET)81.4. Research Summary131.5. Thesis Overview151.6. References17 |

| Chapter 2       | Physics of Junctions of Graphene Devices                                                                   |

|                 | <ul> <li>2.2. Theory and Simulations: Graphene FET and p-n Junction</li></ul>                              |

|                 | 2.4. Summary: Graphene p-n Junction                                                                        |

|                 | 2.6. Doping on graphene by metal contact and the Charge Transfer Region                                    |

|           |       | 2.6.1. Effective Doping on Graphene by Workfunction Diff  |         |

|-----------|-------|-----------------------------------------------------------|---------|

|           |       | of Contact                                                |         |

|           |       | 2.6.2. Lateral Charge Transfer Region Formation           |         |

|           | 2.7.  | Two-Dimensional Simulation of CTR                         |         |

|           |       | 2.7.1. Theory and Simulation Method                       |         |

|           |       | 2.7.2. Device Parameters Influencing CTR Lengths          | 41      |

|           | 2.8.  | Impact of CTR on Device Characteristics                   |         |

|           |       | 2.8.1. Contact Resistance Measurement: Transfer Length M  |         |

|           |       | 2.8.2. Formation of p-n Junction due to Metal-Graphene Ef |         |

|           |       | Doping Effect                                             |         |

|           |       | 2.8.3. CTR of Highly Scaled Devices and                   |         |

|           |       | Ratio                                                     |         |

|           | 2.9.  |                                                           | Contact |

|           | 2.10. | References                                                |         |

|           |       |                                                           |         |

| Chapter 3 |       | erical Study of Inhomogeneity Effects on Hall Measureme   |         |

|           | 1     | nene Films                                                |         |

|           | 3.1.  | Introduction                                              |         |

|           | 3.2.  | Sample Structure                                          |         |

|           | 3.3.  | Ambipolar Hall Equations                                  |         |

|           | 3.4.  | Nonuniformity Model                                       |         |

|           | 3.5.  | Simulation of local $n(x,y)$ and $p(x,y)$ distributions   |         |

|           | 3.6.  | Two dimensional current distribution calculation          |         |

|           | 3.7.  | Potential and charge distribution                         |         |

|           | 3.8.  | Simulation of Hall Mobility                               |         |

|           | 3.9.  | Assesment of Hall Measurement of inhomogeneous graphe     |         |

|           | 3.10. | Minimum conductivity and Dirac point shift                |         |

|           | 3.11. | Epitaxial Graphene on SiC Substrates                      |         |

|           | 3.12. |                                                           |         |

|           | 3.13. | References                                                | 89      |

| Chapter 4 | Analy | vsis of Heat Dissipation of Epitaxial Graphene Device     | ces on  |

| Chapter . | •     | on or from prospersor or promote comprising               |         |

|           | 4.1.  | Introduction                                              |         |

|           | 4.2.  | Simulation Method                                         |         |

|           | 4.3.  | Simulation Results                                        |         |

|           | 1.51  | 4.3.1. Substrate and Interface Thermal Resistances        |         |

|           |       | 4.3.2. Lateral Heat Spreading                             |         |

|           | 4.4.  | Device Fabrication and Measurement Method                 |         |

|           | 4.5.  | Analysis on Pulsed I-V Measurement Results                |         |

|           | 4.6.  | Conclusions                                               |         |

|           | 4.6.  | References .                                              |         |

|           |       |                                                           | + + 4   |

| Chapter 5 | R.F. Circuit Applications of Graphene FETs: Zero-Biased R.F.                         | . Power  |  |  |  |

|-----------|--------------------------------------------------------------------------------------|----------|--|--|--|

|           | Detector and Resistive Mixer                                                         |          |  |  |  |

|           | 5.1. Introduction                                                                    | 116      |  |  |  |

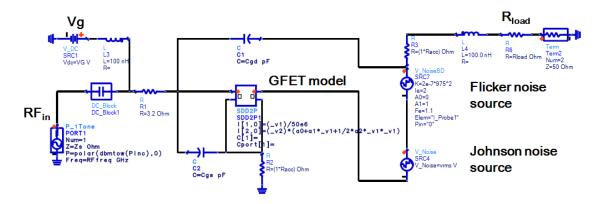

|           | 5.2. Graphene FET models for circuit simulation                                      | 118      |  |  |  |

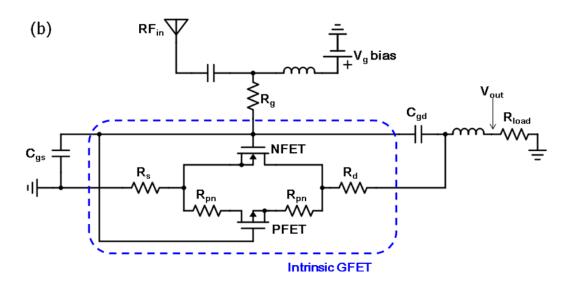

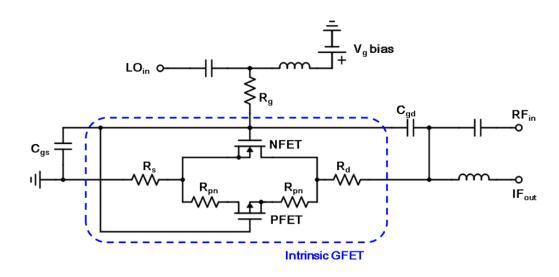

|           | 5.2.1. Compact model: Back to back connected FETs(BBC                                | CF) 118  |  |  |  |

|           | 5.2.2. Abstract model                                                                |          |  |  |  |

|           | 5.3. Graphene FET-Based RF to millimeter-wave detector                               |          |  |  |  |

|           | 5.3.1. Detector operation and simulation setup                                       |          |  |  |  |

|           | 5.3.2. Intrinsic device parameters related to the sensit                             | ivity of |  |  |  |

|           | detector                                                                             | 129      |  |  |  |

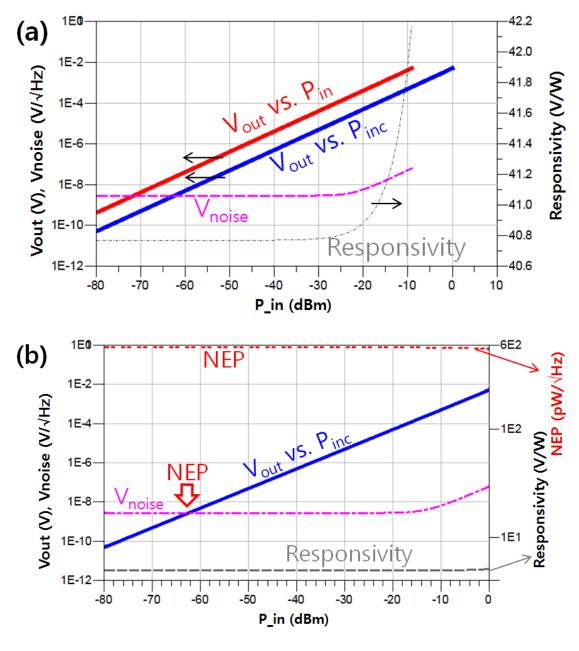

|           | 5.4. Optimization of GFET based r.f. power detector                                  | 131      |  |  |  |

|           | 5.4.1. Power Incident and Noise Considerations                                       | 131      |  |  |  |

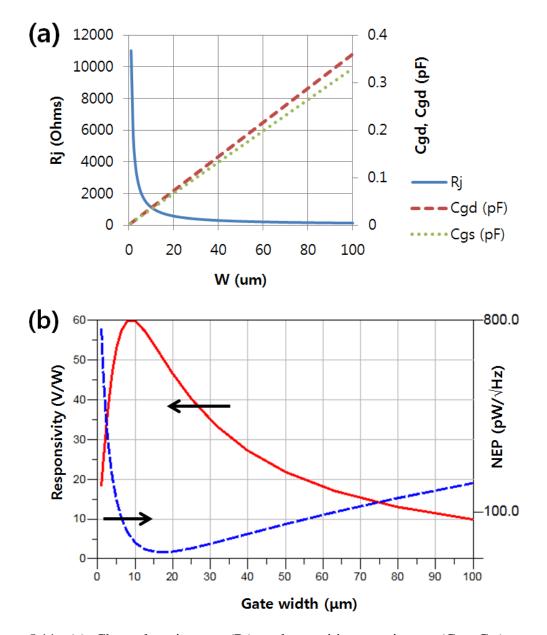

|           | 5.4.2. Optimum Size of the Device: Effective Channel Wi                              | dth 135  |  |  |  |

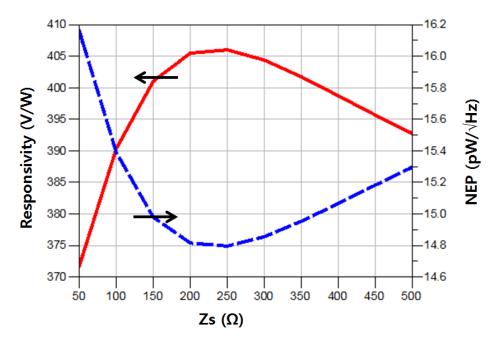

|           | 5.4.3. Extrinsic Parameters: Z <sub>s</sub> , C <sub>pad</sub> and R <sub>load</sub> | 137      |  |  |  |

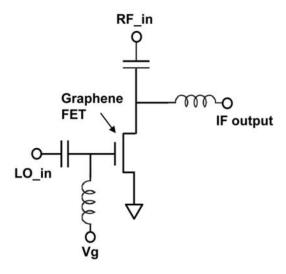

|           | 5.5. Zero-Bias Linear Resistive Mixers                                               | 140      |  |  |  |

|           | 5.5.1. GFET resistive mixer operation                                                | 141      |  |  |  |

|           | 5.5.2. Linear region of GFET near zero bias                                          | 142      |  |  |  |

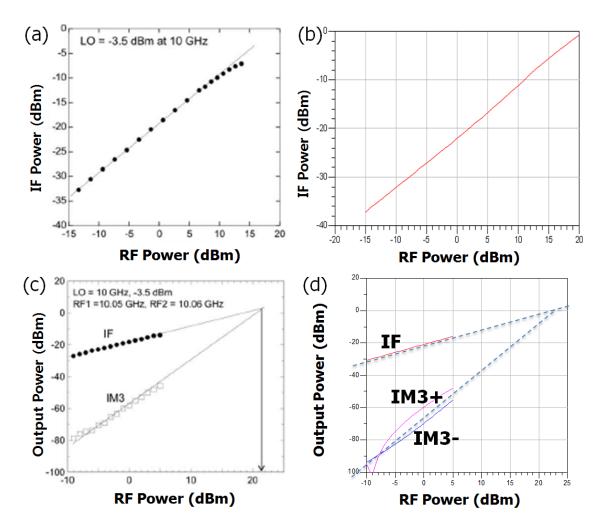

|           | 5.5.3. Mixer Simulation and impact of device parameters.                             | 143      |  |  |  |

|           | 5.6. Conclusions                                                                     | 148      |  |  |  |

|           | 4.6. References                                                                      | 148      |  |  |  |

|           |                                                                                      |          |  |  |  |

| Chapter 6 | Conclusion                                                                           | 151      |  |  |  |

# **List of Figures**

| Figure 1.1. Atomic structure of graphene. Carbon atoms arranged two dimensionally in honeycomb structure                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. E-k dispersion relation of graphene forms a cone shape near Dirac point 4                                                                                                                                                                                                             |

| Figure 1.3. (a) Hall bar fabrication with exfoliated graphene (b) CVD graphene transfer on flexible substrate (c) AFM image of epitaxial graphene shows terraces of SiC surface (inset) TEM image of graphene coverage over SiC terrace                                                           |

| Figuer 1.4. (a) Representative structure of epitaxial graphene FET (b) SEM image of 2-finger GFET                                                                                                                                                                                                 |

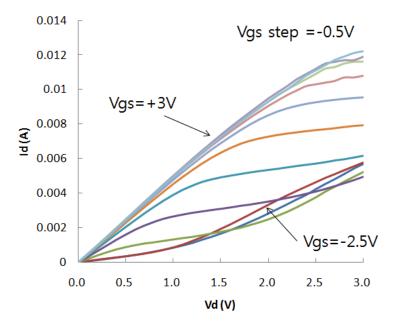

| Figure 1.5. Id-Vd curves of GFET with different Vgs                                                                                                                                                                                                                                               |

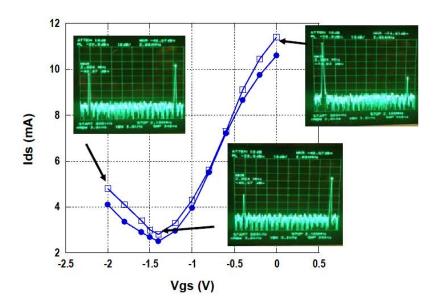

| Figure 1.6. Graphene FET's Id-Vgs curve shows ambipolar, v-shape curve with minimum current at Vgs=VDirac. Mixer output spectra is also shown, which benefitted from quadratic current increase of GFET                                                                                           |

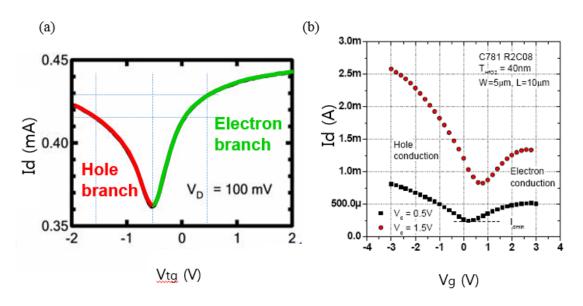

| Figure 2.1. Asymmetry in the drain current transfer characteristics reported in literatures. (a) Graphene FET with n-type channel (effectively doped). $V_{Dirac}$ is below 0V and electron branch shows higher current level than hole branch. (b) $I_d$ - $V_g$ of p-doped graphene channel FET |

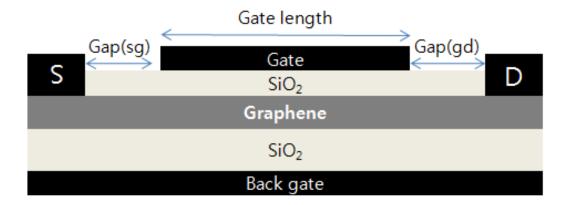

| Figure 2.2. (a) Schematic of the simulated device structure. The gate length is $1.5\mu m$ , and the length of each gap is $0.3um$ . $T_{ox}$ is $10nm$                                                                                                                                           |

| Figure 2.3. Schematic band alignments versus Fermi energy for intrinsic, n-type and p-type channel graphene FET                                                                                                                                                                                   |

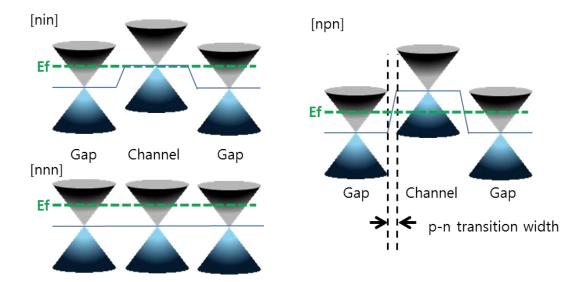

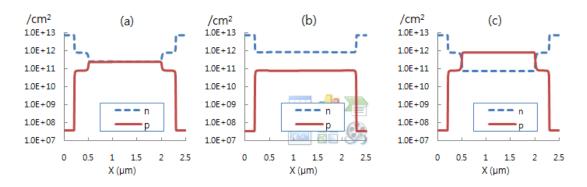

| Figure 2.4. Simulated carrier distribution of graphene FETs. (a) nin structure (b) nnn structure (c) npn structure. Contacts are assumed to be n-type                                                                                                                                             |

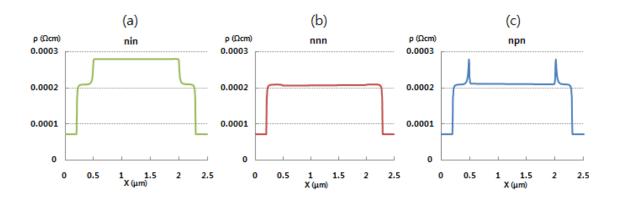

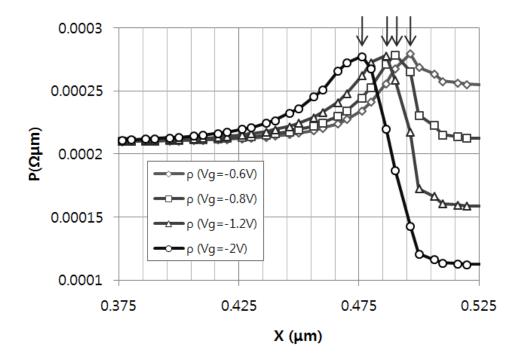

| Figure 2.5. $\rho$ versus channel position. (a) nin structure ( $V_{tg}=V_{Dirac}$ ), the channel is intrinsic and shows high resistivity (b) nnn structure ( $V_{tg}>V_{Dirac}$ ), the channel is n-type (c) npn structure ( $V_{tg}). Resistivity peak is at the p-n junction$                  |

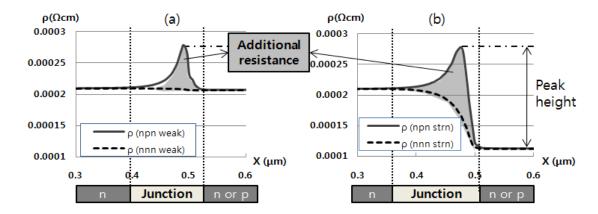

| Figure 2.6. The additional resistance from the resistivity curve. (a) Additional resistance of p-n junction is the integrated area between resistivity of nnn and npn. (b) Increased peak height and integrated area when larger $V_{tg}$ applied to the top gate                                 |

| Figure 2.7. The maximum resistivity peak shifts with $V_{tg}$ change. Larger $V_{tg}$ pushes the position of the peak far from the gate edge                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

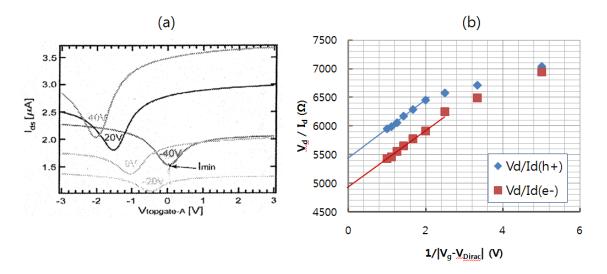

| Figure 2.8. (a) A measured example of drain current transfer characteristics. (b) Extracting $\Delta R$ from $V_d/I_d$ vs. $1/ V_{tg}-V_{Dirac} $ plot.                                                                                                                                                         |

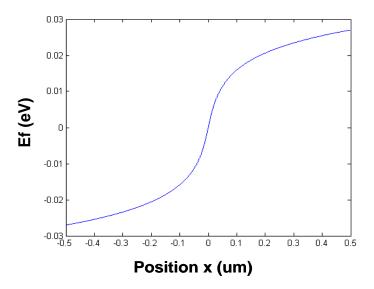

| Figure 2.9. Calculated spatial variation of carrier quasi-fermi level across the p-n junction                                                                                                                                                                                                                   |

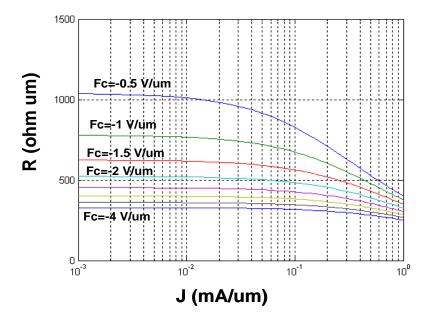

| Figure 2.10. p-n junction resistance calculated from analytical model vs junction current, for different values of electric field $F_c$ .                                                                                                                                                                       |

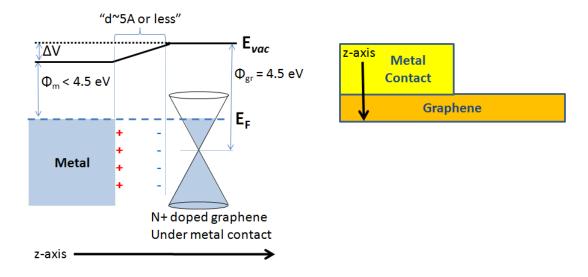

| Figure 2.11. Charge transfer occurs between graphene and metal contact as a result of work function difference and small density of states of graphene                                                                                                                                                          |

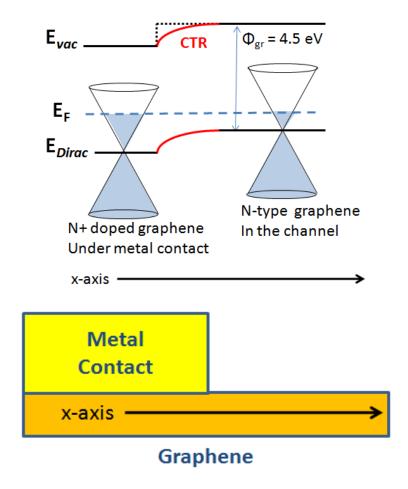

| Figure 2.12. Lateral Charge transfer region formation at high-doped graphene and low-doped graphene junction. Potential and carrier density gradually change to equilibrium states.                                                                                                                             |

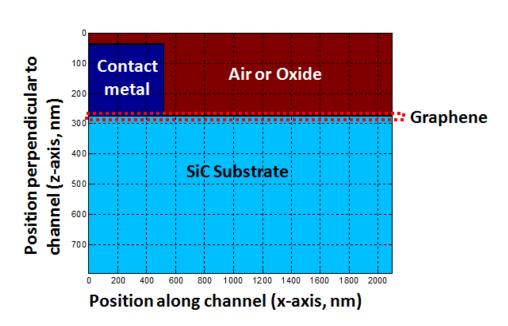

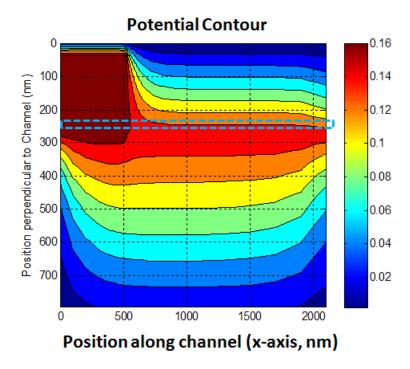

| Figure 2.13. (a) Metal-graphene structure simulated by 2-D Poisson solver. (b) Representative potential distribution. Graphene area is indicated by blue dashed box 39                                                                                                                                          |

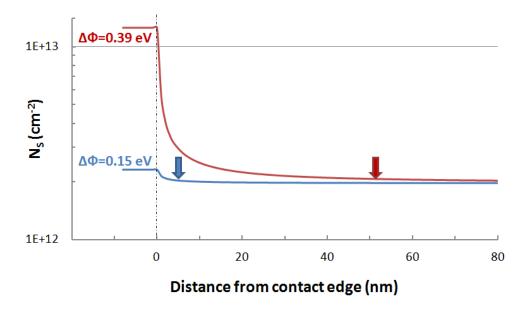

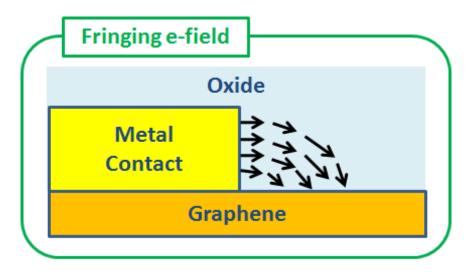

| Figure 2.14. Representative graphene sheet charge density vs distance near the metal contact for unbiased, $N_s=2 \cdot 10^{12}$ cm <sup>-2</sup> , and $\Delta \Phi=0.34$ eV. Arrows are indicating the end point of CTR with emphasis on the impact on sheet resistance                                       |

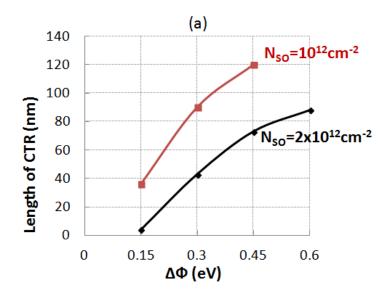

| Figure 2.15. (a) Computed dependence of CTR length on Metal-graphene workfunction difference $\Delta\Phi$ = $\Phi_G$ - $\Phi_M$ ( $T_{metal}$ =20 nm, $\epsilon_{ox}$ =3.9). (b) CTR length dependency on sheet charge density of graphene ( $T_{metal}$ =20 nm, $\epsilon_{ox}$ =3.9)                          |

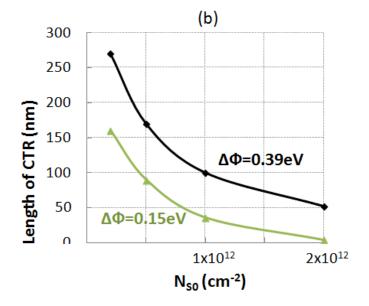

| Figure 2.16. Influence of fringing electric field on graphene electrostatics and charge transfer region                                                                                                                                                                                                         |

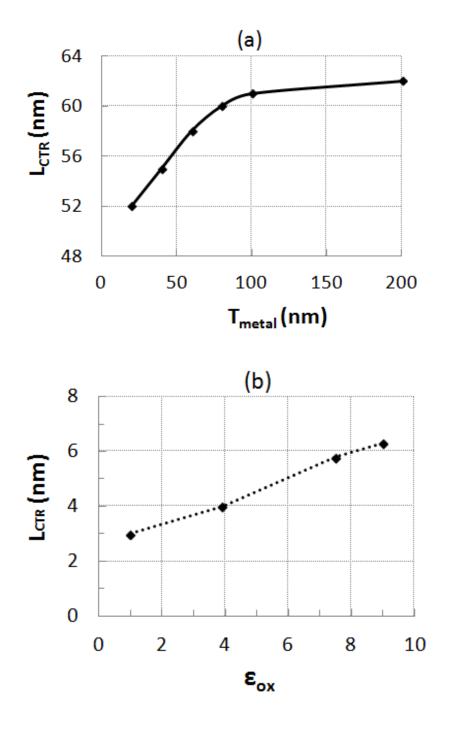

| Figure 2.17. (a) Computed dependence of CTR length on metal thickness ( $\Delta\Phi$ =0.34eV, N <sub>SO</sub> =2•10 <sup>12</sup> cm <sup>-2</sup> ). (b) CTR length vs. top oxide dielectric constant ( $\Delta\Phi$ =0.15eV, T <sub>metal</sub> =20nm, N <sub>SO</sub> =2•10 <sup>12</sup> cm <sup>-2</sup> ) |

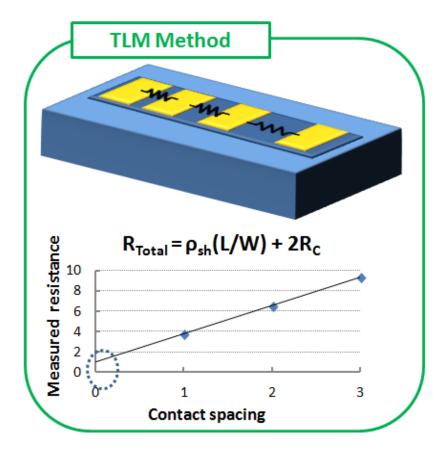

| Figure 2.18. Schematic of TLM method and typical measured result of total resistance vs. contact spacing curve. Contact resistance $R_{\rm c}$ will be half of the y-intercept value 46                                                                                                                         |

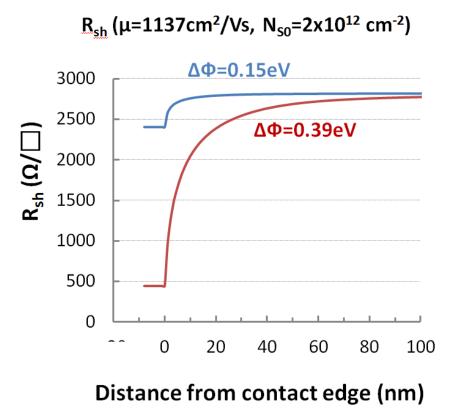

| Figure 2.19. Representative graphene sheet resistance vs distance near the metal contact for unbiased, $N_s$ =2e12cm <sup>-2</sup> , and $\Delta\Phi$ =0.15, 0.34eV                                                                                                                                             |

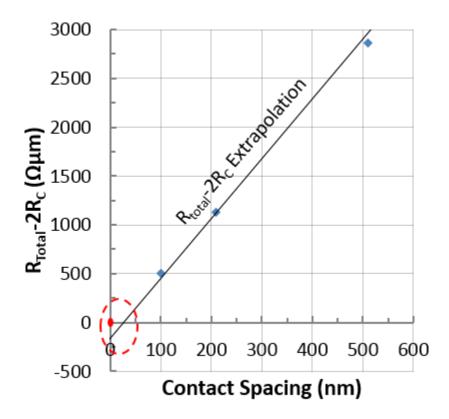

| Figure 2.20. Simulated dependence of measured resistance [R <sub>Total</sub> -2•R <sub>c</sub> ] vs. TLM contact spacing, showing negative intercept                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

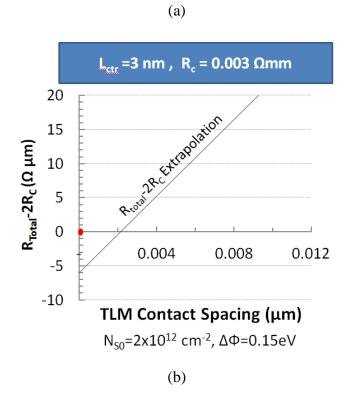

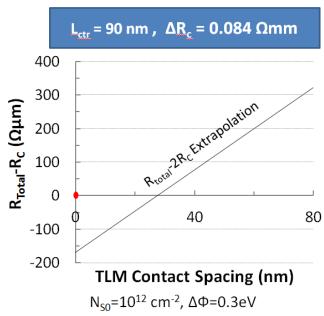

| Figure 2.21 Simulated TLM measurement in terms of [ $R_{Total}$ -2• $R_c$ ] vs. TLM contact spacing, for cases of (a) $\Delta\Phi$ =0.15eV on $N_{S0}$ =2•10 <sup>12</sup> cm <sup>-2</sup> , (b) $\Delta\Phi$ =0.3eV on $N_{S0}$ =2•10 <sup>12</sup> cm <sup>-2</sup> .                                                               |

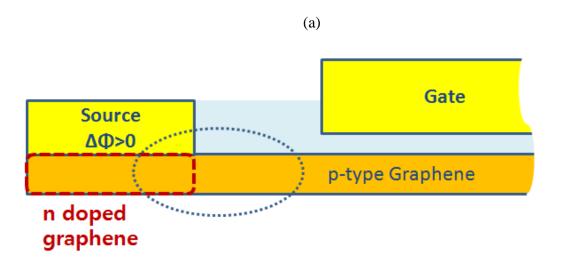

| Figure 2.22. (a) A schematic device structure of n-type doping on p-type graphene film.                                                                                                                                                                                                                                                |

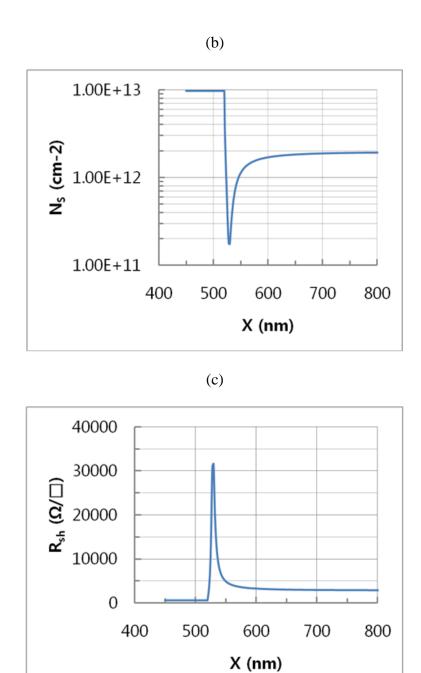

| Figure 2.22. (b) Simulated sheet charge density profile for case of n-type contact and p-type channel. (c) p-n junction shows carrier depletion which causes higher resistivity. 51                                                                                                                                                    |

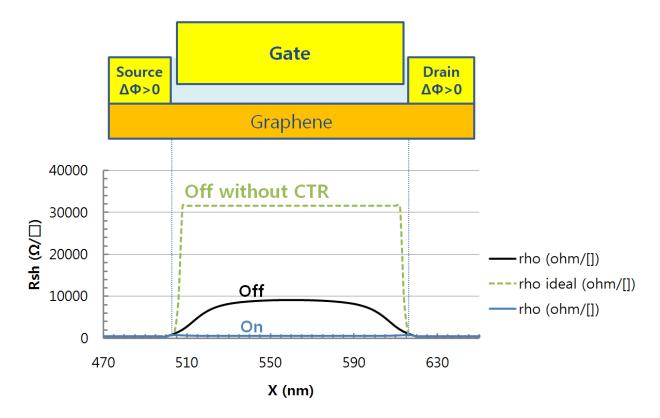

| Figure 2.23. A schematic of self-aligned graphene FET with channel length of 100 nm and R <sub>sh</sub> of on, off, off without CTR cases.                                                                                                                                                                                             |

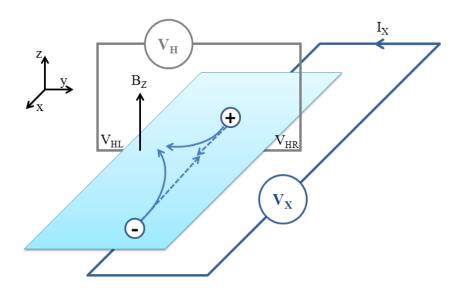

| Figure 3.1. Schematic diagram of Hall measurement. Motions of both holes and electrons are indicated                                                                                                                                                                                                                                   |

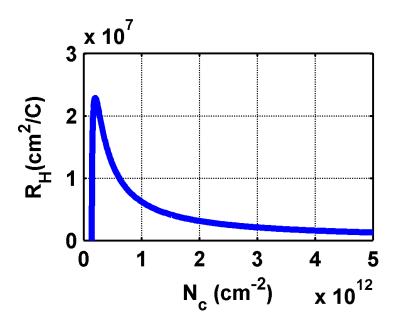

| Figure 3.2. R <sub>H</sub> vs N <sub>c</sub> using ambipolar formula. R <sub>H</sub> vanishes near Dirac point where n~p.                                                                                                                                                                                                              |

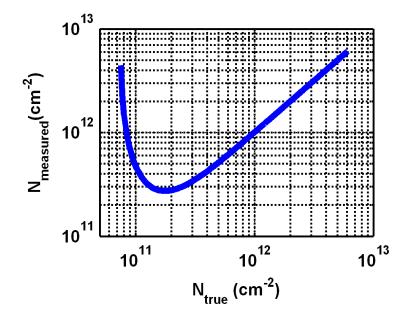

| Figure 3.3. Relation between the extracted carrier density from single carrier Hall measurement (N <sub>measured</sub> ) of graphene and carrier density from ambipolar Hall equation (N <sub>true</sub> ). Single carrier Hall equation overestimates the number of carriers near the Dirac pint.                                     |

| Figure 3.4. The generation and smoothing of inhomogeneous doping profile 65                                                                                                                                                                                                                                                            |

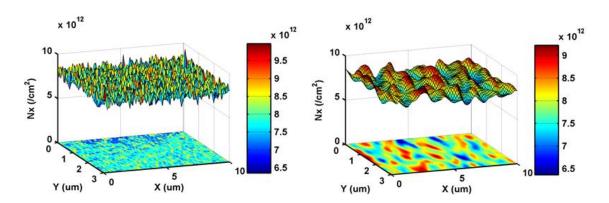

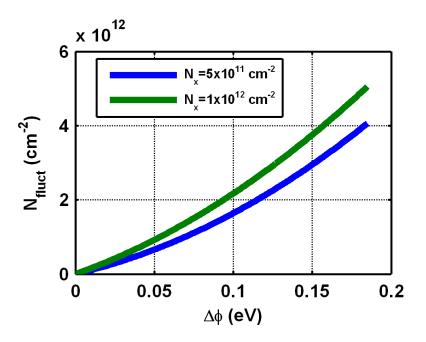

| Figure 3.5. Variation in local electrostatic potential ( $\Delta \phi$ ) vs. local effective doping fluctuation ( $\Delta N_{fluct}$ ) from average doping level $N_x$ of $5\cdot 10^{11}$ and $5\cdot 10^{12}$ cm <sup>-2</sup>                                                                                                       |

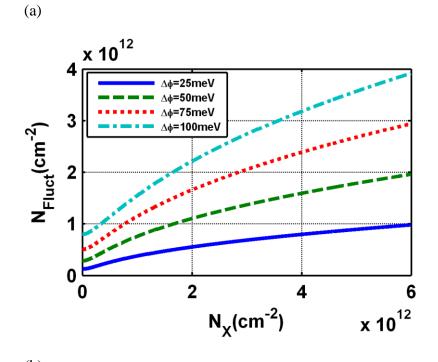

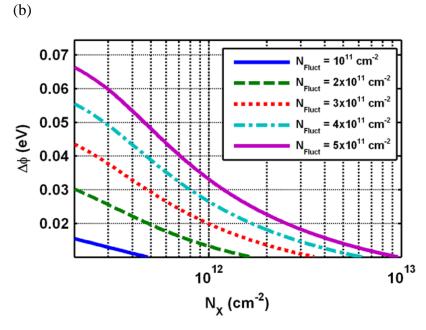

| Figure 3.6. (a) Standard deviation of carrier density $(N_{fluct})$ vs. average doping density $(N_x)$ of graphene film, when the standard deviation of potential fluctuation $(\Delta \phi)$ is fixed as 25, 50, 75 and 100 meV. (b) Standard deviation of potential fluctuation $(\Delta \phi)$ vs. average doping density $(N_x)$ . |

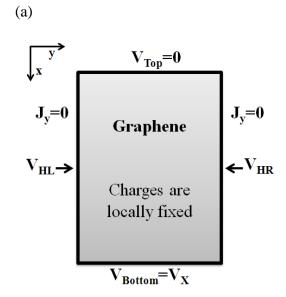

| Figure 3.7. (a) Simulated device structure with boundary conditions. (b) Randomly generated inhomogeneous charge density distribution. (c) Electrical potential contour of non-uniform graphene Hall measurement sample. (d) Electrical potential contour of uniform graphene Hall measurement sample                                  |

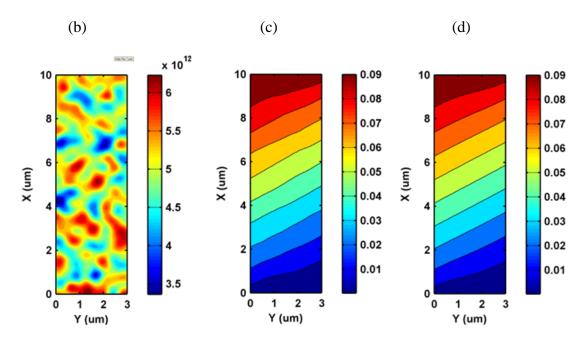

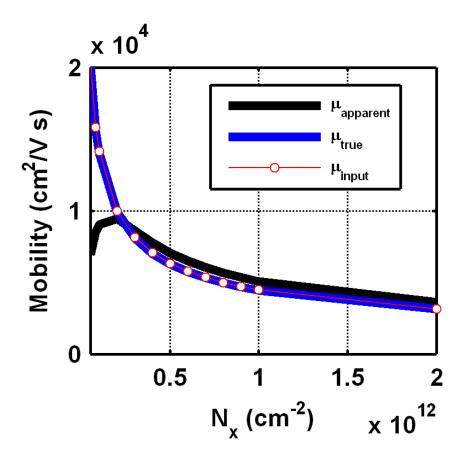

| Figure 3.8. Comparison of simulated Hall mobility ( $\mu_{apparent}$ ) vs. input mobility value in the simulation ( $\mu_{input}$ ) and corrected mobility value ( $\mu_{true}$ ). Simulated Hall sample is uniform film without any local inhomogeneity ( $N_{fluct}$ =0)                                                             |

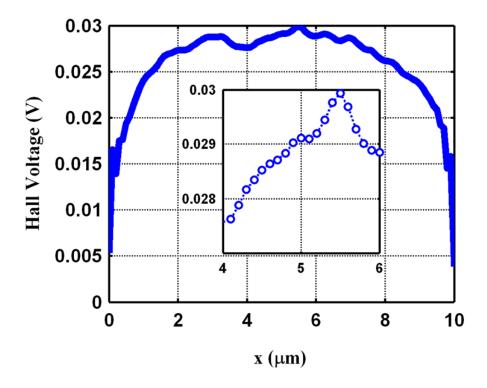

| Figure 3.9. Simulated Hall voltage along the x-axis (longitudinal current flowing direction) when $N_x=3\cdot 10^{12}$ cm <sup>-2</sup> and $N_{fluct}=5\cdot 10^{11}$ cm <sup>-2</sup> . Inset: Zoom-in image of Hall voltage for mid area of the Hall bar.                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

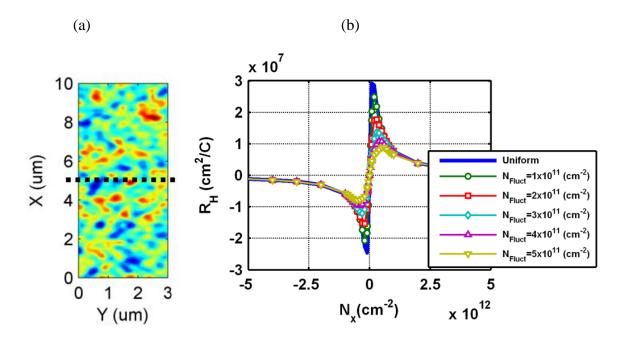

| Figure 3.10. Inhomogeneous graphene Hall measurement simulation. (a) Effective doping distribution of inhomogeneous graphene. (b) Hall coefficient vs. gate voltage. 77                                                                                                                                                                                                                                                 |

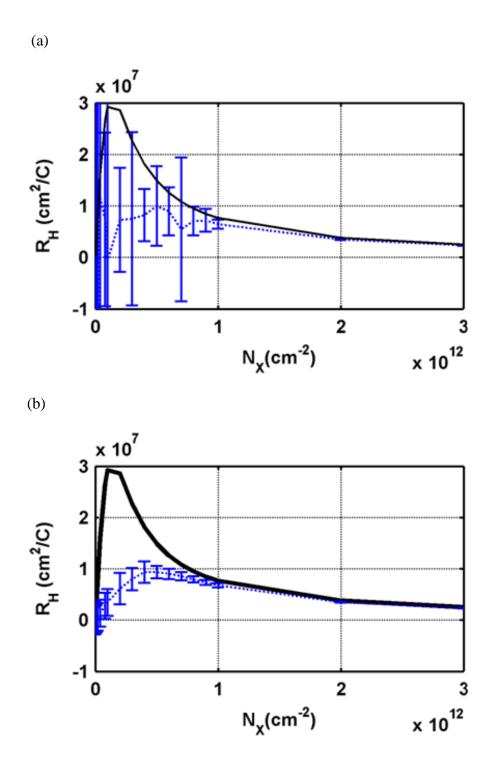

| Figure 3.11. Hall coefficient vs $N_x$ . Solid line (black) indicates the uniform graphene sample case. (a) Hall coefficient vs $N_x$ when the size of filter size is 200 nm. (b) 500 nm. (c) 1 $\mu$ m. (d) $N_{measured}$ vs. $N_x$ .                                                                                                                                                                                 |

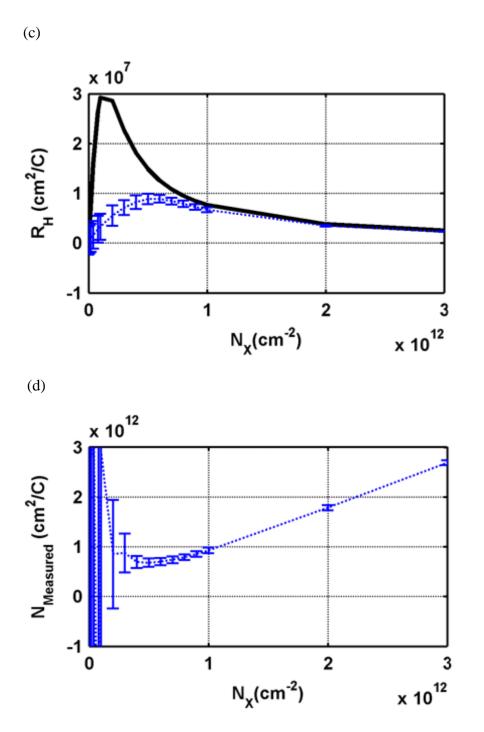

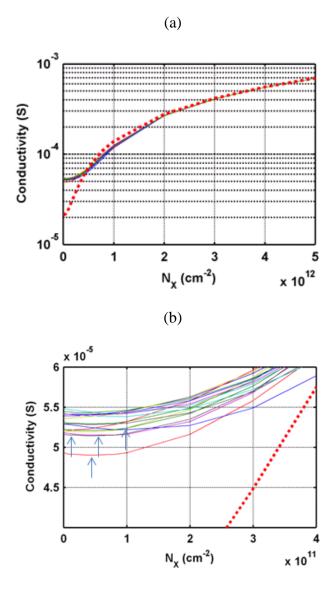

| Figure 3.12. (a) Conductivity curves from multiple simulations of inhomogeneous doping distribution. (b) Zoomed-in conductivity near Dirac point; the Dirac point is shifted and the minimum conductivity also varies.                                                                                                                                                                                                  |

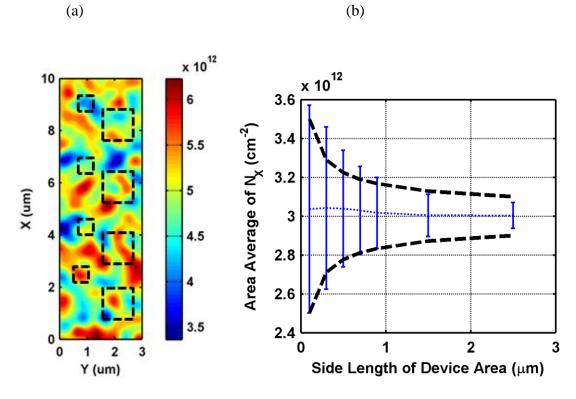

| Figure 3.13. (a) Device area defined on inhomogeneous graphene (b) Distribution of average $N_x$ (blue dot) and standard deviation (error bars) vs. device size, for 100 devices.                                                                                                                                                                                                                                       |

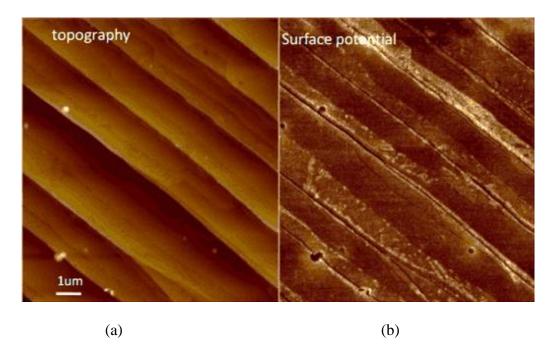

| Figure 3.14. (a) Atomic force microscope image of topography of steps on epitaxial graphene on SiC. (b) Surface potential of epitaxial graphene on SiC substrate 86                                                                                                                                                                                                                                                     |

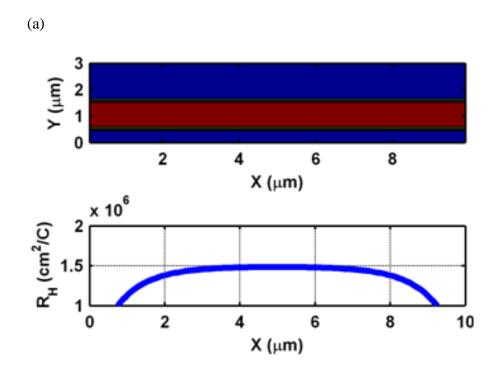

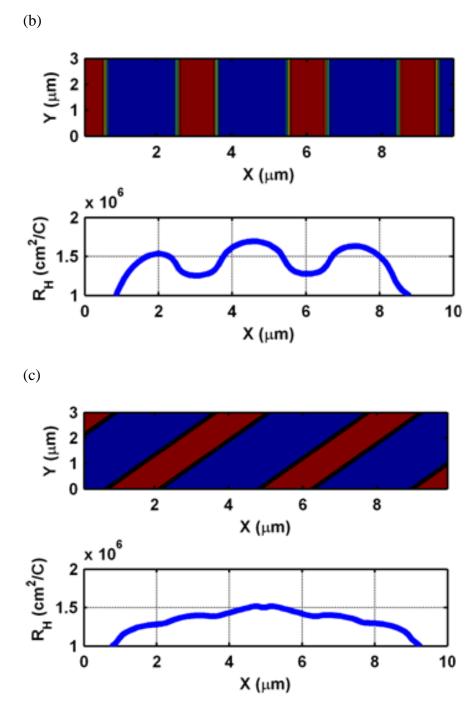

| Figure 3.15. Various orientations of terraces and associated graphene regions of edge area (Red) in the simulation and their impact on the Hall coefficient. (a) 0 degree orientation. (b) 90 degree orientation (c) 45 degree orientation                                                                                                                                                                              |

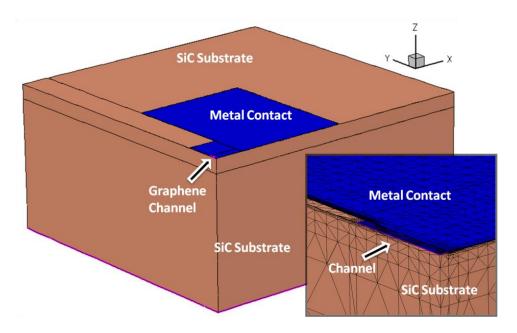

| Figure 4.1. Simulated device structure; a quarter of graphene resistor on SiC substrate. (inset) Zoom-in image of the device with mesh grid                                                                                                                                                                                                                                                                             |

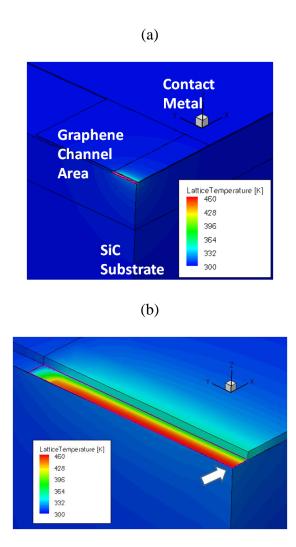

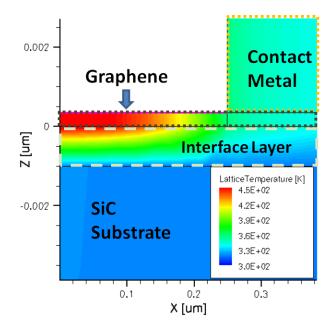

| Figure 4.2. (a) 3-D simulated lattice temperature of graphene resistor. A quarter of the device is shown here. (b) Zoom-in figure of (a) which shows cooling effect from the metal contact and side edge of the channel. Hottest point is indicated by white arrow. (c) Cut-area picture at the middle of the channel.                                                                                                  |

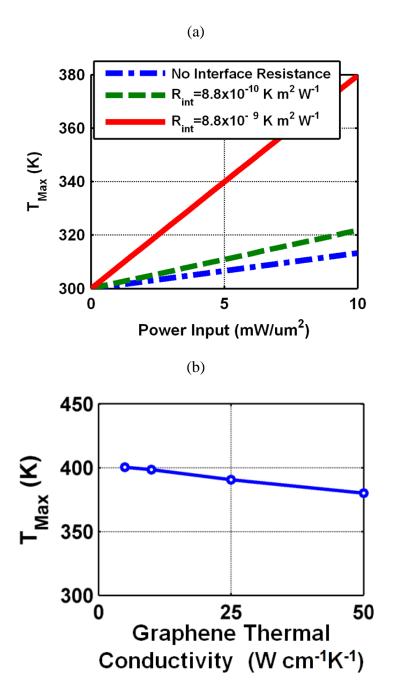

| Figure 4.3. (a) Simulated junction temperature ( $T_{Max}$ ) with graphene-substrate interface resistance variation. Assumed graphene thermal conductivity is 50 Wcm <sup>-1</sup> K <sup>-1</sup> (b) Simulated junction temperature with various graphene thermal conductivities assumed. $10 \text{mW}/\mu\text{m}^2$ of input power was applied for $R_{int}=8.8\cdot10^{-9}$ K m <sup>2</sup> W <sup>-1</sup> case |

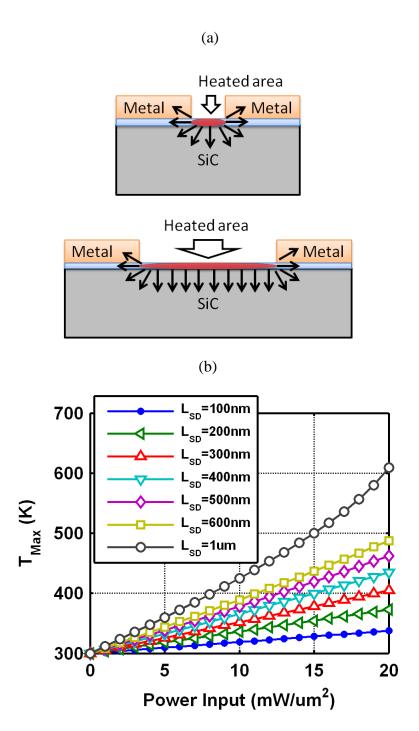

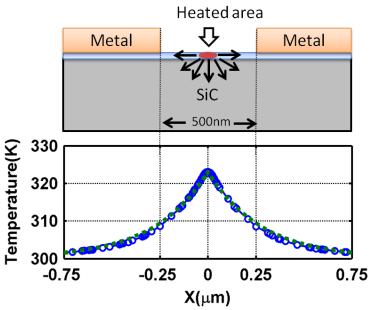

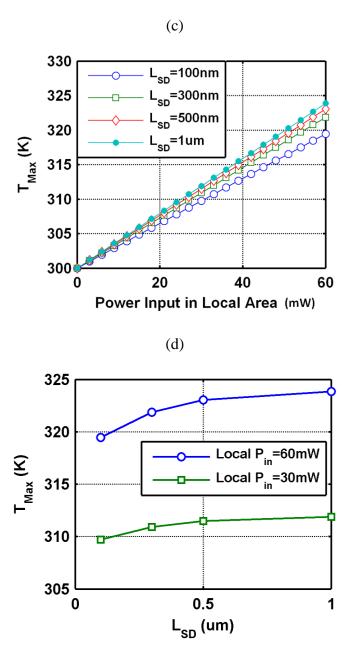

| Figure 4.4. (a) Schematic of channel length varying thermal simulation with uniform power input over channel area (cut along x-z plane of 3-D simulation). Arrows indicate heat dissipation paths. (b) Simulated $T_{Max}$ for various $L_{SD}$ .                                                                                                                                                                       |

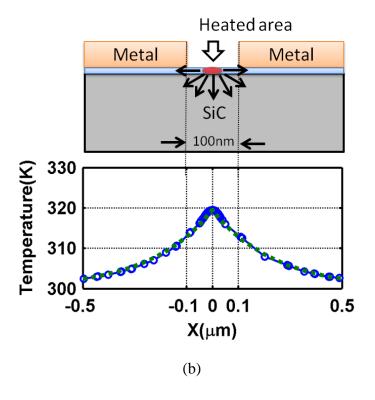

| Figure 4.5. (a, b) Schematic of channel length varying thermal simulation with local heating (cut along x-z plane of 3-D simulation). (c) Simulated $T_{Max}$ vs. $P_{in}$ for various $L_{SD}$ , when local heating is applied to a 50nm width strip in the middle of the channel. (d) Simulated $T_{Max}$ vs. $L_{SD}$                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

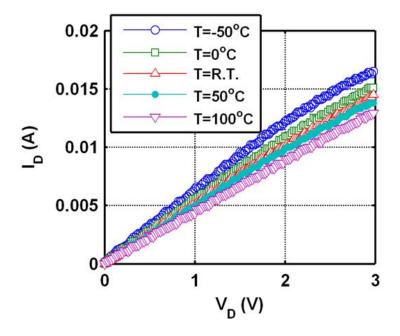

| Figure 4.6. Measured pulsed I-V at various temperatures, with pulse length of 200 ns                                                                                                                                                                                                                                                                       |

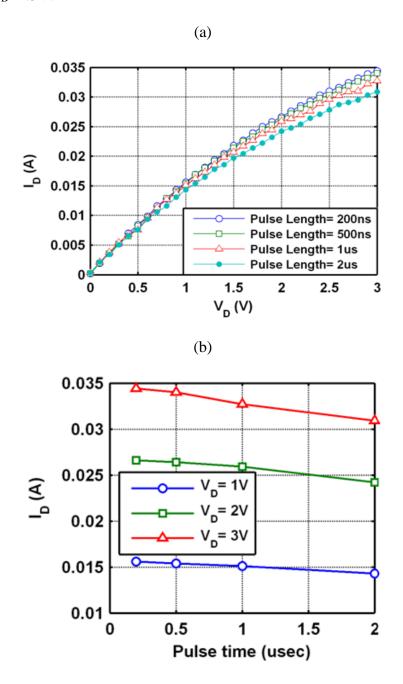

| Figure 4.7. (a) Measured pulsed I-V characteristics with variable pulse durations. (b) $I_D$ vs. pulse duration for various $V_D$ values                                                                                                                                                                                                                   |

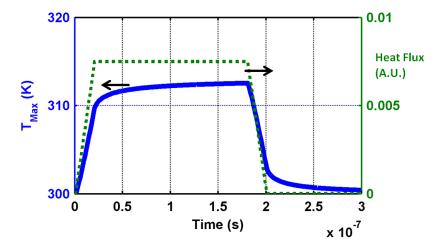

| Figure 4.8. Transient simulation with 20 ns pulse rise time                                                                                                                                                                                                                                                                                                |

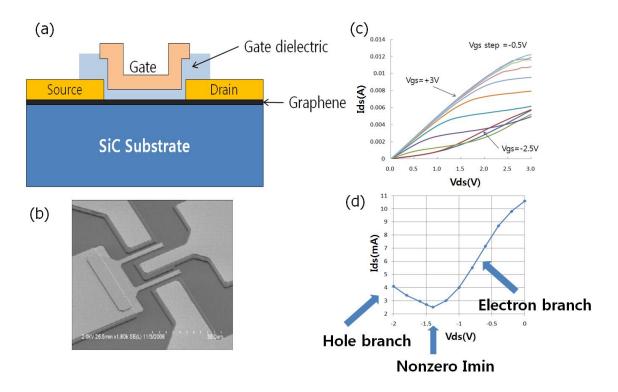

| Figure 5.1 (a) Schematic of graphene FET structure based on epitaxial graphene on SiC substrate (vertical cut) (b) SEM image of r.f. Graphene FET with two gate fingers (c) Representative $I_d$ - $V_d$ curve of graphene FET. Width is 6 $\mu$ m, channel length is 3 $\mu$ m. (d) Representative $I_d$ - $V_g$ curve of GFET.                           |

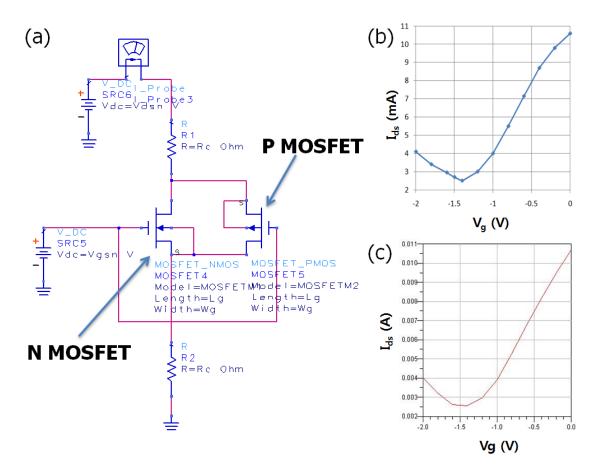

| Figure 5.2. (a) Compact model of GFET for circuit level simulations as appeared in ADS simulation. N MOSFET and P MOSFET are connected back-to-back to describe the ambipolar behavior of GFET. (b) $I_d$ - $V_g$ measurement result of GFET [9] (c) Fitted $I_d$ - $V_g$ curve with GFET compact model                                                    |

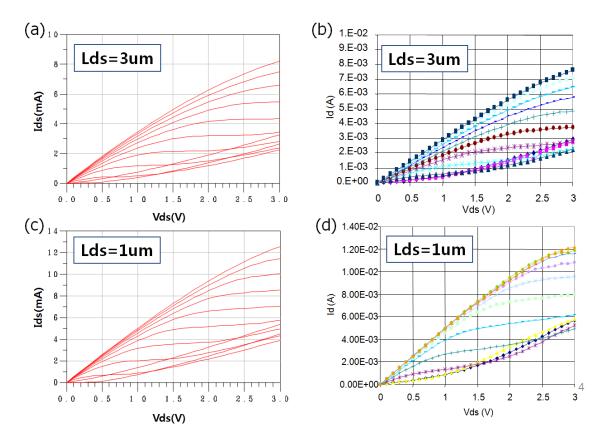

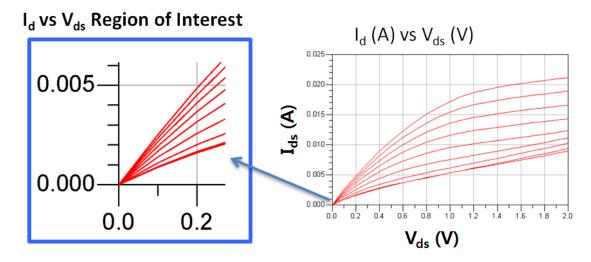

| Figure 5.3. (a) Simulated $I_d$ - $V_d$ curves for GFET with $L_{ds}$ = 3 $\mu m$ (b) $I_d$ - $V_d$ measurement result of GFET with $L_{sd}$ = 3 $\mu m$ (c) Simulated $I_d$ - $V_d$ curves for GFET with $L_{ds}$ = 1 $\mu m$ (b) $I_d$ - $V_d$ measurement result of GFET with $L_{sd}$ = 1 $\mu m$ . Measurement results: courtesy of HRL Laboratories. |

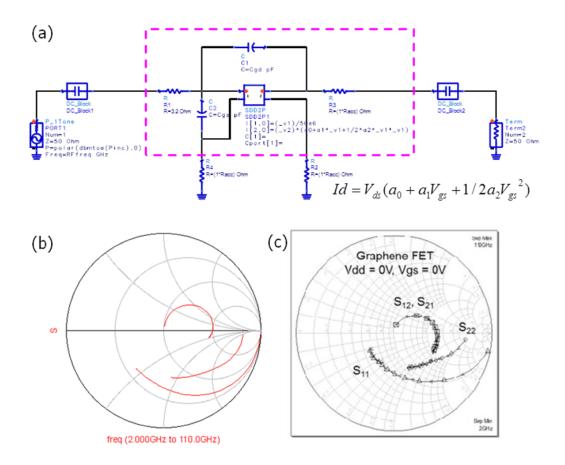

| Figure 5.4 (a) Circuit diagram using abstracted model with parasitic elements as a 2-terminal box device, which uses $V_g$ and $V_d$ as input and calculated $I_d$ from the abstracted model for output. (b) s-parameter simulation result using the abstracted model of GFET (c) measurement s-parameter of GFET.                                         |

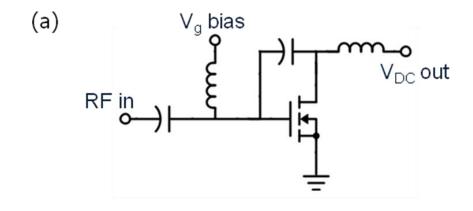

| Figure 5.5. (a) Schematic of power detector system (b) A circuit diagram of the power detector with full model of GFET including parasitic elements                                                                                                                                                                                                        |

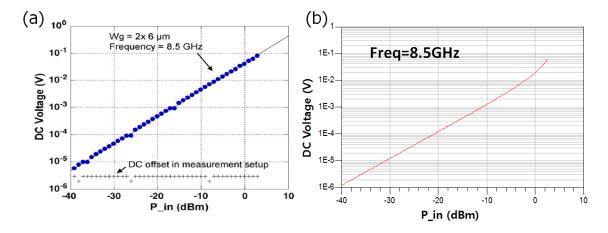

| Figure 5.6. Input power (P <sub>in</sub> ) vs. output voltage (V <sub>out</sub> ) plot of GFET power detector (a) measurement result (b) simulated result                                                                                                                                                                                                  |

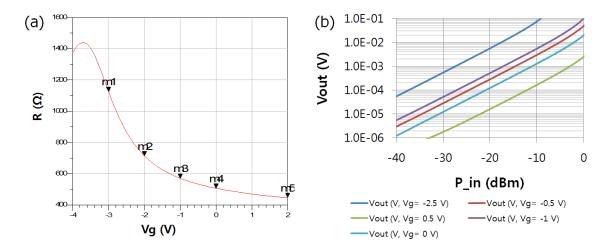

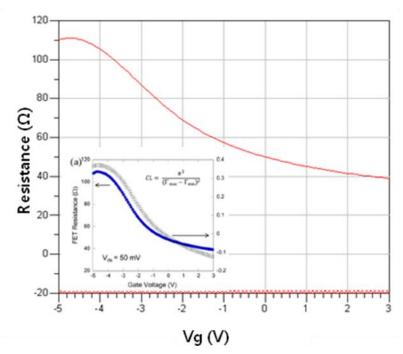

| Figure 5.7. (a) R vs $V_g$ plot of GFET. (b) $V_{out}$ vs. $P_{in}$ plot with $V_g$ variation                                                                                                                                                                                                                                                              |

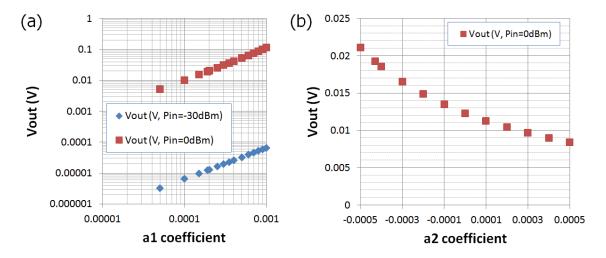

| Figure 5.8. (a) Output voltage variation with a <sub>1</sub> coefficient at P <sub>in</sub> =0 and -30 dBm. (b) Output voltage variation with a <sub>2</sub> coefficient                                                                                                                                                                                   |

| Figure 5.9. Schematic of power detector with noise source                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.10. (a) Representative $V_{out}$ vs. $P_{in}$ plot with comparison of incident power ( $P_{inc}$ ) versus delivered power ( $P_{in}$ ). (b) Simulated $V_{out}$ vs. incident power ( $P_{inc}$ ) of unbiased graphene FET based power detector                                                 |

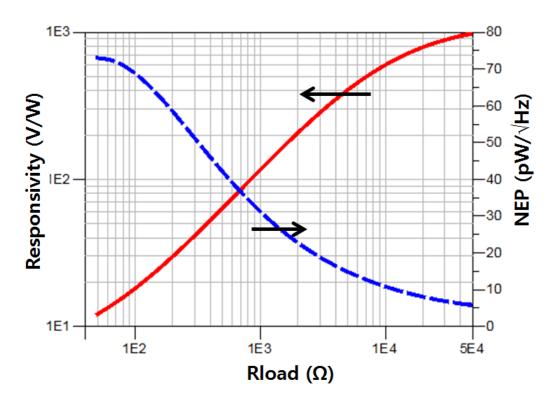

| Figure 5.11. (a) Channel resistance $(R_j)$ and parasitic capacitance $(C_{gs},\ C_{gd})$ versus effective device width at Vg=-2.5V. (b) Responsivity and NEP vs. device channel width. Larger width will increase the Cpara, while lowering the channel resistance 136                                 |

| Figure 5.12. Responsivity and NEP versus input impendance (Z <sub>s</sub> )                                                                                                                                                                                                                             |

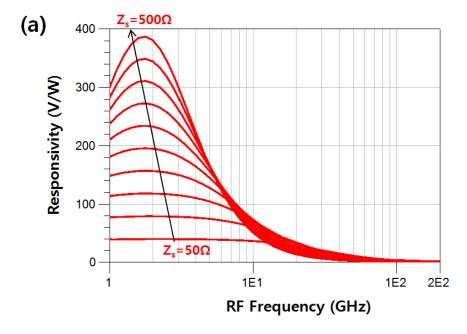

| Figure 5.13 (a) Frequency response of responsivity of power detector when $Z_s$ is varying from 50 to 500 $\Omega$ . (b) NEP vs. r.f. frequency when $Z_s$ is varying                                                                                                                                   |

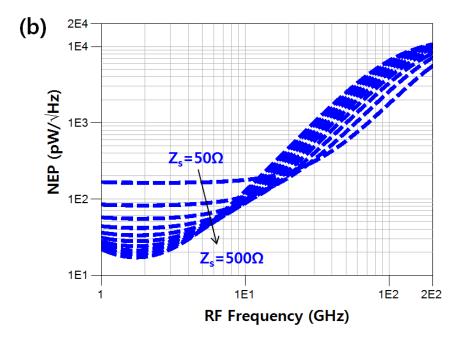

| Figure 5.14. Responsivity and NEP for various R <sub>load</sub> at 8.5 GHz                                                                                                                                                                                                                              |

| Figure 5.15. Schematic of resistive FET mixer, where the LO signal is applied to the gate (gate-pumped). The IF output signal is measured at the drain                                                                                                                                                  |

| Figure 5.16. Simulated $I_{ds}$ - $V_{ds}$ curves of GFET with varying gate bias. (inset) zoom-in: region of interest near $V_{ds}$ = 0 V                                                                                                                                                               |

| Figure 5.17. Schematic of resistive GFET mixer with bact-to-back-connected FET device model                                                                                                                                                                                                             |

| Figure 5.18. Simulated GFET resistance as a function of gate voltage. (inset) Measured GFET resistance vs. Vg and reflection coefficient                                                                                                                                                                |

| Figure 5.19. (a) Measured IF power versus r.f. input power of GFET at 10 GHz (b) Simulated IF power vs. r.f. input power at 10 GHz (c) Measured two-tone test result of a GFET at 10 GHz (d) Simulated two-tone test of GFET at 10 GHz. The gate width was $2*12\mu m$ , gate length was $0.25~\mu m$ . |

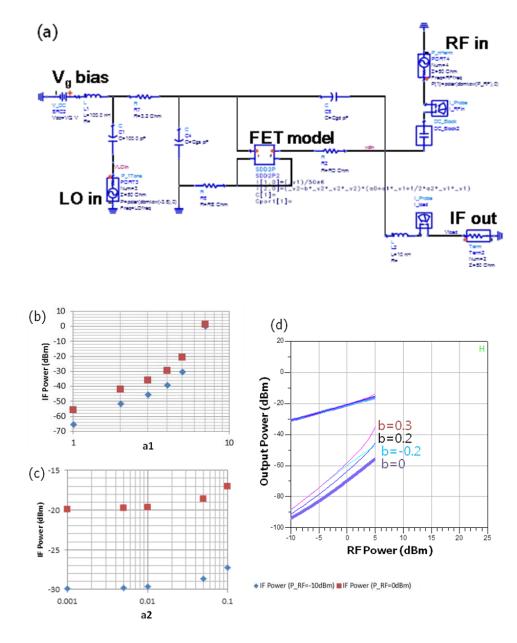

| Figure 5.20. (a) A schematic of the linear mixer as used in the ADS simulation. (b) IF power respect to a <sub>1</sub> parameter variation (c) IF power versus a <sub>2</sub> parameter (d) Output power vs. r.f. power when b parameter varies                                                         |

# **List of Tables**

Table 5.1. Device parameters for GFET compact model based on BSIM3 model  $\dots$  119

## Acknowledgements

First and foremost, I would like to thank my PhD advisor, Dr. Peter Asbeck, who has continuously inspired me with his passion and wisdom. I've been fortunate to start and finish my PhD journey with his guidance and support. Indeed, it was a previlege to have opportunities to work together and learn from him a lot. I would like to express my gratitude to my committee members, Dr. Yuan Taur, Dr. Paul Yu, Dr. Prab Bandaru and Dr. Gert Cauwenbergs. I appreciate their interests and thoughtful comments and advices on my research. Through all years of the study in UCSD, I've learned so much from all professors I've met in classes and interacted with regarding various research projects.

I must thank my colleagues in our lab, HSDG. I was lucky to have so knowlegable, smart and warm-hearted group members around me to share tough times and fun moments. New friends I've met in San Diego formed my graduate student life more endurable and fruitful. I'm thankful for having them as my classmates, neighborhoods, soccer team mates, and most of all, the family. I also would like to thank my childhood friends who also faced and experienced similar challenges in their own graduate studies in the states. Although we could only gather a few times over years, the friendship gave me a great comfort and strength that I cannot appreciate enough.

I would like to acknowledge members of HRL Laboratories who are my current colleagues, especially Dr. Jeong-Sun Moon for the opportunity of graphene studies. His generous support and guidance really helped me to walk through my PhD study. I would

also thank Dr. James Li for his support and motivating me to move to the next chapter of my career.

I would like to express my deepest gratitude to my parents and sister for their unlimited, selfless love. I couldn't have finished this journey without them. I'm also really happy and feeling so productive to have my lovely twins, Jaina and Henry, who are priceless additions to my life. I'm not sure if they are supporting me or just trying to give me more hard times, though. Finally, I'm really greatful for my wife, Hyemin, who is the best friend, partner and companion of my life. Her love, patience, and support allowed me to make all things possible.

It has been a long, but a fun ride. May the force be with us all.

Chapter 2 or portion thereof has been published in MRS Proceedings (2010 MRS Spring Meeting), May 2010, K. Lee, L. Wang, P. Asbeck and J. Moon, and in International Semiconductor Device Research Symposium (ISDRS), Dec. 2011, K. M. Lee, A. Ohoka, P.M. Asbeck. The dissertation author was the primary investigator and author of both papers.

Chapter 3, in full, is a reprint of the material as it appeared in *Solid State Electronics* 2014, K. Lee, J.S. Moon, T. Oh, S. Kim, P. Asbeck and P. M. Asbeck. The dissertation author was the primary investigator and author of this paper.

Chapter 4 in full, is a reprint of the material as it appeared in *Solid State Electronics* 2014, K. Lee and P. M. Asbeck. The dissertation author was the primary investigator and author of this paper.

### Vita

| February, 2006 | Bachelor of Science in Materials Science and Engineering<br>Seoul National University, Seoul, Korea                                                     |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| February, 2008 | Master of Science in Nano Science and Technology<br>Interdiciplinary Program for Nano Science and Technology<br>Seoul National University, Seoul, Korea |

| 2008-2014      | Graduate Student Researcher Department of Electrical and Computer Engineering University of California, San Diego                                       |

| June, 2016     | Doctor of Philosophy in Electrical Engineering<br>University of California, San Diego                                                                   |

### **Journal Publications**

- P. M. Asbeck, <u>K. Lee</u> and J. Min, "Projected Performance of Heterostructure Tunneling FETs in Low Power Microwave and mm-Wave Applications," in IEEE Journal of the Electron Devices Society, vol. 3, no. 3, pp. 122-134, May 2015

- <u>K. Lee</u>, P. Asbeck, "Numerical study of inhomogeneity effects on Hall measurements of graphene films," Solid-State Electronics, Volume 106, April 2015, Pages 34-43, ISSN 0038-1101

- <u>K. Lee</u>, J.S. Moon, T. Oh, S. Kim, P. Asbeck, "Analysis of heat dissipation of epitaxial graphene devices on SiC," Solid-State Electronics, Volume 101, November 2014, Pages 44-49, ISSN 0038-1101

- S. Gu, H. Katayose, K. Nomoto, T. Nakamura, A. Ohoka, <u>K. Lee</u>, W. Lu and P. M. Asbeck, "High transconductance ion-implanted GaN MISFETs using atomic layer deposited high-k dielectrics," physica status solidi (c), Vol. 10, Issue 5, pages 820–823, May 2013

- J. S. Moon, H. -C. Seo, M. Antcliffe, D. Le, C. McGuire, A. Schmitz, L. O. Nyakiti, D. K. Gaskill, P. M. Campbell, **K.-M. Lee**, and P. Asbek, "Graphene FETs for Zero-Bias

- Linear Resistive FET Mixers," IEEE Electron Device Letters, Vol. 34, No. 3, March 2013

- J.S. Moon, H.-C.Seo, M. Antcliffe, S. Lin, C. McGuire, C. D. Le, L.O. Nyakiti, D.K. Gaskill, P, M. Campbell, <u>K.-M. Lee</u>, P.Asbeck, "Graphene FET-Based Zero-Bias RF to Millimeter-Wave Detection," IEEE Electron Device Letters, Oct. 2012

- J.S. Moon, M. Antcliffe, H.C. Seo, D. Curtis, S. Lin, A. Schmitz, L. Milosavljevic, A. A. Kiselev, R. S. Ross, D. K. Gaskill, P. M. Campbell, R.C. Fitch, **K.-M. Lee**, P. Asbeck, "Ultra-low resistance ohmic contacts in graphene field effect transistor," Applied Physics Letters, May 2012

- J.S. Moon , M. Antcliffe, H.C. Seo, S.C. Lin, A. Schmitz, L. Milosavljevic, K. McCalla, D. Wong, D.K. Gaskill, P.M. Campbell, **K.-M. Lee**, P. Asbeck, "Graphene review: An emerging RF technology", Silicon Monolithic Integrated Circuits in RF Systems (SiRF), 2012 IEEE 12th Topical Meeting on, On page(s): 199 202

- J.S. Moon , M. Antcliffe, H.C. Seo, S.C. Lin, A. Schmitz, L. Milosavljevic, K. McCalla, D. Wong, D.K. Gaskill, P.M. Campbell, <u>K.-M. Lee</u>, P. Asbeck, "Graphene transistors for RF applications: Opportunities and challenges," in Int. Semiconductor Device Research Symposium (ISDRS), Dec. 2011

- J.S. Moon, D. Curtis, D. Zehnder, S. Kim, D. K. Gaskill, G.G. Jernigan, R.L. Myers-Ward, C.R. Eddy, P.M. Campbell, <u>K.M. Lee</u>, P. Asbeck, "Low-Phase-Noise Graphene FETs in Ambipolar RF Applications," IEEE Electron Device Letters, March 2011

- W Chen, W. V. Chen, <u>K Lee</u>, SS Lau and T. F. Kuech, "High Quality InP Layers Transferred by Cleavage Plane Assisted Ion-Cutting," Electrochem. Solid-State Lett.2010 volume 13, issue 8, H268-H270, May 2010

## **Conference Proceedings**

- <u>K. Lee</u> and P. Asbeck, "Analysis of Heat Dissipation of Epitaxial Graphene Devices on SiC," in International Semiconductor Device Research Symposium (ISDRS), 2013

- J. S. Moon et al., "Graphene review: An emerging RF technology," Silicon Monolithic Integrated Circuits in RF Systems (SiRF), 2012 IEEE 12th Topical Meeting on, Santa Clara, CA, 2012, pp. 199-202.

- K. M. Lee, A. Ohoka, P.M. Asbeck, "Charge transfer region at the edge of metal

contacts on graphene and its impact on contact resistance measurement," in International Semiconductor Device Research Symposium (ISDRS), Dec. 2011, Nominated: Best Student Paper

- <u>K. Lee</u>, L. Wang, P. Asbeck and J. Moon, "Analysis of Resistance Asymmetry Due to p-n Junctions in Graphene FETs," in MRS Proceedings (2010 MRS Spring Meeting) / Vol.1259 / 2010

- P. Asbeck, <u>K. Lee</u> and J. Moon, "Graphene: Status and prospects as a microwave material," in IEEE 12th Annual Wireless and Microwave Technology Conference (WAMICON), April 2011

#### ABSTRACT OF THE DISSERTATION

## **Design Considerations of Graphene FETs for RF Applications**

by

### Kangmu Min Lee

Doctor of Philosophy in Electrical Engineering (Nanoscale Devices and Systems)

University of California, San Diego, 2016

Professor Peter Asbeck, Chair

This dissertation discusses various physical aspects of graphene electronic devices, particularly FETs, of importance for high frequency (RF, microwave and mmwave) applications. Device physics of graphene junctions and contact junctions are considered. Inhomogeneity effects, heat dissipation and graphene FET compact modeling including unique nonlinearity mechanisms are discussed.

The first part of the dissertation discusses device physics of graphene. The importance of its unique band structure, high carrier mobilities, and maximum current handling are highlighted for RF applications. Graphene junctions are discussed in detail, including p-n junctions and graphene-to-metal junctions. It is shown that graphene p-n

junctions provide additional resistance at the transition region within representative FETs due to depletion of carriers, which results in asymmetric ambipolar Id-Vg curves. It is also shown that a charge transfer region is formed at metal-graphene edges, which produces errors in the customary contact resistance measurement and analysis. Both junction effects are controlled by carrier density of the film, fringe electric field, and bias conditions.

Inhomogeneous graphene films are modeled in detail to describe the formation of electron-hole puddles, and their impact on Hall mobility measurements. Inhomogeneity is more significant with larger amplitude of random charge fluctuation and the size of puddles. It is shown that measured Hall mobility can be degraded by more than 8 % due to inhomogeneity, compared with ideally uniform films with the same average carrier density.

Thermal properties of graphene FETs must also be understood in relation to their performance and reliability. Heat dissipation of graphene devices has been analyzed with 3-D thermal simulations. The significance of interface thermal resistance, device design for quick heat release, and contact metal use for lateral heat spreading is described. Simulation and experimental results showed that pulses as short as 200 ns can still heat up graphene devices due to their small heat capacity.

Finally, graphene device models are developed in two forms: a SPICE-like compact model for straightforward usage in circuit simulators, and a more abstract analytic model for investigation of the impact of device parameters on circuit performance. Both device models are used to explore the performance of graphene-

based FETs in zero bias r.f. power detector and resistive linear mixer applications. Parasitic elements such as parasitic capacitances, gate and series resistances are included for realistic circuit simulation, and the role of these components on the circuit performance is investigated. Graphene-based zero-biased power detectors showed sensitivity comparable to those using CMOS and InP HEMT-based technologies. Simulated noise equivalent power (NEP) was estimated to be as low as 10 pW/Hz0.5 for a passive r.f. power detector, thanks to the suppression of flicker noise. The mixer also exhibited linearity comparable to state-of-the-art, with input third-order intercept point (IIP3) estimated at about 22 dBm. Simulation results describe the experimental results well. The impact of different device design parameters are investigated by simulation in order to optimize performance.

# **Chapter 1**

## Introduction

Since the first experimental realization of graphene by Geim and Novoselov [1], the research activities on graphene have grown explosively over the last decade [2, 3]. Numerous researchers explored this novel material which has unique electrical [4, 5], photonic [6, 7], mechanical [8] characteristics. Graphene showed the highest room temperature mobility [4, 9, 10], for both holes and electrons. It is transparent, flexible, and has very high strength. Among many possible applications, r.f. applications could have a significant benefit from utilization of graphene [11].

Traditionally, better performance of FETs has been achieved by scaling down the gate length. In order to maintain the electrostatic channel control and to suppress short

channel effect, the vertical dimensions of the gate dielectric and channel should be scaled down as well [12]. The vertical scaling down has been a major challenge because it generates problems such as the degradation of mobility due to surface scattering, deterioration of electrostatic control over the channel, and gate leakages through the thin oxide layers. However, graphene is already an extremely scaled down channel layer – one atom thick. One can control the characteristics of graphene FET channel via electrical field modulation, forming both n- and p-channel and changing the polarity. Graphene also showed excellent room temperature mobility for both electrons and holes. Graphene FET already demonstrated high cutoff frequencies [13-17], thanks to its large carrier velocity and ability to stand high current flow. The large optical phonon energy of graphene also helps to reduce the scattering and maintain the high mobility of carriers [18-20]. The planar structure of the material enables to have compatible process with various technologies including CMOS. More over, graphene is transparent and flexible, which would be possible to serve as a platform of flexible electronic devices.

In this chapter, a brief overview is provided to review advantages of graphene for high frequency FETs, material preparation methods, and opportunities and challenges towards graphene based high speed microwave transistors. The objective of this thesis is then described, and the research results are summarized. The chapter ends with a brief description of the remaining chapters.

### 1.1. Graphene Structure and Electrical Properties

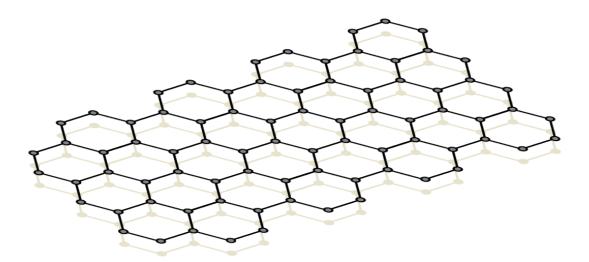

Graphene is a single atom thick sheet of carbon atoms hexagonally arranged to honeycomb structure (Figure 1.1). Physically it is equivalent to single layer detached from graphite single crystal. Interlayer bonding force is relatively weaker than intralayer bond, therefore it is possible to peel off graphene layers from the bulk graphite. Often the exfoliation results more than a single layer, which is known as bilayer, trilayer, and multi-layer graphene.

Figure 1.1. Atomic structure of graphene. Carbon atoms arranged two dimensionally in honeycomb structure

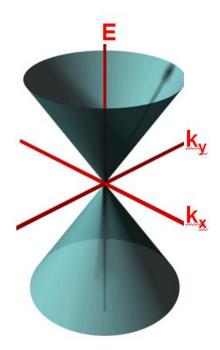

Within the layer, carbon atoms are tightly bonded with sp2 bonding, and additional electrons are forming orbital perpendicular to the plane which contributes to form conduction and valence bands [21]. Graphene has a unique E-k relation:  $E=\hbar \cdot v_D \cdot k$ , where  $v_D$  is the Dirac velocity  $8 \cdot 10^7$  cm/s. As displayed in Figure 1.2, graphene energy

band forms a mirrored cone structure with zero bandgap.  $E_c$  and  $E_v$  meeting at the charge neutrality point, also known as the Dirac point. Fermi energy will reside at the Dirac point when the graphene is at intrinsic condition. Thermally activated finite minimum charge density is in the order of  $\sim 1 \cdot 10^{11}$  cm<sup>-2</sup> at room temperature. According to the linear E-k relation, the density of states of band reduces near at the Dirac point, and quickly increases as the Fermi energy pushed away from  $E_{Dirac}$ .

Figure 1.2. E-k dispersion relation of graphene forms a cone shape near Dirac point

Graphene's unique linear E-k dispersion also allows very high speed for both electrons and holes. Dirac velocity  $v_D$  is the maximum, however average velocity of carriers with field will be reduced in the presence of scattering induced by defects [22],

fixed charges [23, 24], acoustic [18] and optical phonons [18, 19]. Mobility of graphene carrier is affected by carrier density as well, where the intrinsic, minimum carrier density state will result maximum mobility [25]. The optical phonon energy of graphene is very high (180 meV) [20], because of graphenes light mass and strong bonds. Large optical phonon energy suppresses optical phonon scattering and enhances the carrier mobility. However, optical phonon scattering from gate dielectric limits the mobility of graphene channel of FETs. Therefore, highest mobility was measured from suspended graphene structures where graphene is standing alone without any interface with dielectric or substrate.

### 1.2. Material Preparation of Graphene

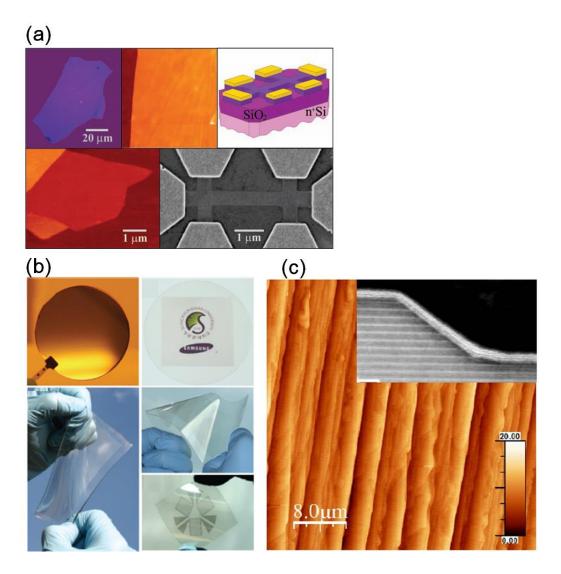

The first seperation of graphene layer was demonstrated by peeling off flakes from graphite crystal using Scotch tape [1]. Exfoliated flakes are mechanically transferred on to 300 nm-thick SiO<sub>2</sub> layer on Si substrate which is widely used, because the graphene flake is visible on this particular substrate, displayed in figure 1.3 (a) [1]. It is possible to distinguish the number of layers of the graphene flake with optical microscope. Since the method doesn't require high cost equipment, most of graphene devices were fabricated on exfoliated graphene flakes at the beginning of graphene research boom. Highest mobility of carriers of graphene was measured on suspended device of exfoliated graphene flake which is a single crystal and has an excelent uniformity of thickness withing short distance (~µm). However, despite its high quality, the exfoliated graphene has a critical weakness; lack of scalability.

Chemical vapor deposition (CVD) emerged as a popular method of graphene growth since the size of graphene film is only limited by the size of metal foil, which serves as a film growth surface. Carbon film is deposited on copper [26] or nickel [27] films, and C atoms arranges in honeycomb structure with grain boundaries. The size of graphene grain is affected by the size of the grain of metal foils, growth temperature. CVD film of graphene can be transferred to various substrates by wet-transfer [28], dry-transfer [29]. Large area of graphene (continuous roll of 10 inches width film) fabrication and transfer was demonstrated using thermal detach adhesion [30]. Since the CVD graphene often need to be transferred to target substrate, non-negligible probability of contamination exists during the process. Several electronic devices have been reported that used CVD graphene as channel material, however, large area graphene films showed it is more suitable for transparent, flexible electrode material when it is used as multi-layer graphene.

Figure 1.3. (a) Hall bar fabrication with exfoliated graphene [1] (b) CVD graphene transfer on flexible substrate [28] (c) AFM image of epitaxial graphene shows terraces of SiC surface (inset) TEM image of graphene coverage over SiC terrace [31]

Epitaxial graphene has been an attractive candidate for high speed graphene transistor applications, because of its excellent film quality and no need of transfer to other substrate. The film is grown on SiC substrate by sublimation of Si atoms of the top surface by annealing at >1000°C under vacuum or Ar environment [31, 32]. Carbon atoms remain at the surface and rearrange to form a graphene film. C-terminated faces

tend to form a multi layer graphene, while it is easier to control the number of carbon sheet layers from single to few layers on Si-terminated SiC surface. Epitaxial graphene shows n-type doped characteristics due to background doping effect from the substrate and interface [32]. Figure 1.3 (c) shows TEM image of epitaxial graphene over the terrace of SiC substrate, where graphene has an excellent coverage over steps and terraces of SiC surface.

The film quality of graphene is typically measured by means of atomic force mictroscopy (AFM) and Raman spectroscopy. AFM measurement shows grain sizes up to micron scale [33, 34] and steps of epitaxial graphene due to the topography of SiC substrate [31]. Raman spectroscopy can distinguish the number of layers [35, 36] by investigating the height and width 'g peak', which is a signal according to graphene. Quality of graphene film can be estimated by 'd peak' which typically shows the defects of the film. After years of intensive R&D efforts, the quality and reproducibility of large area graphene film has been improved significantly. The degree of control of material characteristics over wafer scale is comparable to conventional semiconductor materials [37-39]

### **1.3.** Graphene Field Effect Transistors (GFET)

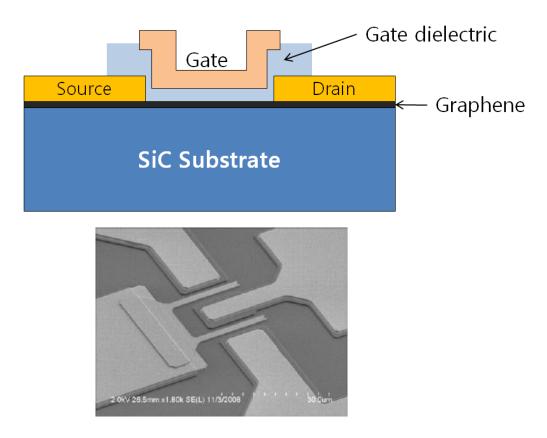

A representative top-gated graphene FET structure on semi-insulating SiC substrate is shown in Figure 1.4 (a) [11]. The graphene FET channel area is defined by  $O_2$  plasma etch. Source and drain electrodes, gate dielectric, and gate metal stack processes follows. Figure 1.4 (b) shows a SEM image of fabricated r.f. GFET on SiC substrate. Ohmic contacts showed resistance as low as  $0.2 \Omega \cdot mm$  [40]. devices are also similar

structure, except using the substrate of SiO<sub>2</sub> on bulk Si [13, 41]. When the Si substrate is low resistivity substrate, it can act as a global bottom gate. In fact, many of initial device fabrication have used global back gate to control the transferred graphene flake devices without top gate.

Figuer 1.4. (a) Representative structure of epitaxial graphene FET (b) SEM image of 2-finger GFET [11]

Various types of gate dielectrics have been utilized for graphene surface, which have been a challenging task due to lack of dangling bonds on the surface of graphene [42]. Prototype transferred graphene used thick oxide as a gate dielectric. Building an embedded gate structure under high-k material then transferring graphene film on top was

another way to avoid this problem [43]. Spontaneous oxidization of few nanometer of Al film or graphene surface functionalization by grafting diazonium salt [44] are a few example of providing an initial seed layer for subsequent ALD deposition for conventional device process steps.

Doping the graphene film is also a difficult challenge. There have been several methods reported such as replacing carbon atoms with nitrogen atoms [45], add organic layer to provide charge transfer [46]. However, it is still difficult to obtain high quality graphene (without degrading mobility) after these doping methods. Transferred graphene FETs can use the global back gate to provide desired charge density level of the region between gate and source/drain. Ungated gap region is series resistance along the channel of the FET, which degrades the performance [14, 15]. Epitaxial graphene is known to have n-type film which has ~10<sup>12</sup> cm<sup>-2</sup> of charge density [11, 31], relatively relieves the need of additional doping, however, it would be desired to have self aligned structure best performance.

Figure 1.5. Id-Vd curves of GFET with different Vgs

A long channel graphene FET  $I_d$ - $V_d$  characteristics are displayed in figure 1.5. Current level is modulated with gate bias, however, current flows even when  $V_g < V_{th}$  (or  $V_{Dirac}$ ). It is due to graphene's zero bandgap nature which makes the pinch off difficult, especially under large  $V_{ds}$ . When  $V_{ds}$  increases the current shows a saturation behavior, then increases again because hole channel is introduced near drain instead of pinch-off region of conventional FETs. A model with the Gradual Channel Approximation describes the I-V characteristics.

$$I = \mu \frac{W}{L} C_{eff} \left[ \frac{1}{2} (V_g - V_t)^2 + \frac{1}{2} (V_d - V_g + V_t)^2 \right]$$

where I is drain current when  $\mu$  is effective mobility, W and L are width and length of the channel, respectively.  $C_{eff}$  is effective gate capacitance,  $V_d$  is drain bias,  $V_g$  is gate bias, and  $V_t$  is threshold voltage also known as Dirac point. Figure 1.6 displays  $I_d$ - $V_g$  characteristic of graphene FET is a V-shaped ambipolar curve, with minimum current conduction point at  $V_g$ = $V_{Dirac}$ . Where  $V_g$ > $V_{Dirac}$ , the channel is filled with electrons (electron branch), while it becomes hole channel when  $V_g$ < $V_{Dirac}$  (hole branch). Near at Dirac point, it also offers unique features such as quadratic variation of current with gate voltage.

Figure 1.6. Graphene FET's Id-Vgs curve shows ambipolar, v-shape curve with minimum current at Vgs=VDirac. Mixer output spectra is also shown, which benefitted from quadratic current increase of GFET [47]

Graphene also could handle a very high on current, up to values of >3mA/um, limited by dielectric strength [17], thermal breakdown [48]. Excellent confinement barriers surrounding graphene channel also affects the efficient current flow, which is

much improved compared with conventional FETs. The number of carriers can increase if the gate dielectric is thinner and also hold large electric field. Better thermal design can increase the  $I_{max}$  by lower the junction temperature from Joule self heating.

Graphene offers new opportunities for a high frequency FETs because of its high carrier mobility, planar structure with excellent scaling properties, limited scattering and a simple modulation of electron and hole channels.

#### 1.4. Research Summary

Motivated by unconventional experimental results and mismatches between test data and theory on epitaxial graphene devices, several simulation and modeling approaches have been employed to illuminate the details of several building-blockcomponents required to build graphene-based device systems. A starting point for the research is the set of graphene material properties such as uniformity of the charge density, and junctions of graphene-contact metal, and between p- and n-type graphene. Joule-self heating is heavily involved in current saturation and breakdown of GFETs, therefore the thermal behavior of graphene device is investigated with 3-D thermal simulations. After reviewing the characteristics of elements of GFETs, device models are introduced in two forms: a SPICE-like compact model; and an abstract analytic model. Circuit simulations with these device models are demonstrated for GFET based power detector and resistive mixer applications. Key results of this dissertation are summarized here:

- Techniques to perform a classical approach with physically based TCAD simulator for electrostatics of graphene p-n junction. Numerical estimation of spatial resistivity based on carrier distribution and carrier density dependent mobility of electrons and holes, which matches the experimental results and provides a simple understanding of origin of asymmetrical I<sub>d</sub>-V<sub>g</sub> curves.

- Modeling of lateral charge spread from the metal contact by employing a twodimensional Poisson solver, to find out relations of charge density and metal work function which causes unintentional lateral doping and errors on contact resistance measurements.

- Modeling techniques of inhomogeneous graphene film which describes the

physical consequences of randomly distributed charges, so-called electron hole

puddles, on Hall measurements, Dirac point estimation, and overall device-todevice uniformity on wafer scale.

- Application of a three-dimensional thermal simulation to investigate the junction temperature of graphene devices. Investigated the heat dissipation behavior with focus on device dimensions, structure, and interface thermal resistances.

Comparison with experimental results shows the saturation behavior of I-V of graphene device is partially due to Joule self-heating.

- Establishment of a SPICE based compact model to describe the ambipolar conduction of GFETs to explore circuit applications in straightforward manner.

The model shows a good fit with experimental results with only a few device parameter adjustments.

- Development of an abstract analytic model of GFET with Taylor expansion to investigate the impact of device parameters on circuit performance, such as nonlinearity.

- Demonstration of GFET circuit simulation utilizing compact and abstract models,

for description of power detector and mixer applications. Investigation on impact

of device parameters on circuit performances for optimization.

#### 1. 5. Thesis overview

This thesis presents an analysis of various aspects of graphene behaviors and device physics, of importance for applications of graphene in high frequency electronics. Electrical characteristics at graphene p-n junctions and metal-graphene contact edges, graphene film uniformity and its impact on mobility measurements, Joule self-heating and heat dissipation are described and analyzed. The thesis also covers compact device modeling of graphene FETs for circuit simulations and discusses implications for r.f. applications

In Chapter 2 the local resistance of graphene devices around p-n junctions and graphene-metal edges are described. p-n junction resistance causes additional series

resistance and asymmetry of V-shaped ambipolar Id-Vg current between hole and electron current. Metal edges can form several types of junctions and impacts the accuracy of TLM measurement for contact resistance. These experimentally observed effects are analyzed with two dimensional devices simulations and Poisson solver. Classical approach shows characteristics of graphene p-n junctions and its impact on ambipolar current asymmetry. Effective graphene doping from metal and charge transfer region will be discussed, focusing on contact resistance measurement.

Chapter 3 introduces a two-dimensional inhomogeneous graphene model for calculation of electric charges and fields with or without magnetic fields. In the model, dopants are distributed randomly to emulate the so-called electron-hole puddle. Various device parameters such as puddle size, charge density deviation and channel sizes are investigated to provide potentials and limits of uniformity for practical graphene devices.

Chapter 4 presents analysis on thermal behavior of graphene resistors on silicon carbide substrates, using three dimensional heat simulations. Several device parameters such as interface thermal resistance, channel width, and contact spacing are investigated for vertical and lateral heat spread characteristics. For comparison, pulsed I-V measurement is employed with various pulse lengths and environment temperature. Effective thermal resistance of the system and Joule heating during a short pulse will be discussed.

Chapter 5 explores the potential performance of radio frequency (r.f.) graphene FETs (GFET). A compact model is developed with SPICE models and also an analytic model was used for analyze the relation of device parameters with circuit performances.

Zero biased power detector and resistive linear mixers are investigated and optimized with circuit simulations including parasitic componenets.

Chapter 6 summarizes the thesis and briefly mentions future works.

#### 1.6. References

- [1] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva and A. A. Firsov, "Electric field effect in atomically thin carbon films," Science, vol. 306, Oct. 2004, no. 5696, pp. 666-669, doi: 10.1126/science.1102896

- [2] F. Schwierz, "Graphene transistors," Nature Nanotech., vol. 5, May 2010, pp. 487–496, doi:10.1038/nnano.2010.89

- [3] A. K. Geim, "Graphene: status and prospects," Science, vol. 324, June 2009, pp. 1530-1534, doi: 10.1126/science.1158877\

- [4] S. V. Morozov, K. S. Novoselov, M. I. atsnelson, F. Schedin, D. C. Elias, J. A. Jaszczak, and A. K. Geim, "Giant Intrinsic Carrier Mobilities in Graphene and Its Bilayer," Phys. Rev. Lett., vol. 100, Jan. 2008, pp. 160602, doi: 10.1103/PhysRevLett.100.016602

- [5] K. S. Novoselov, A. K. Geim, S. Morozov, D. Jiang, M. Katsnelson, I. Grigorieva, S. Dubonos, and A. Firsov, "Two-Dimensional Gas of Massless Dirac Fermions in Graphene," Nature, vol. 438, Nov. 2005, pp. 197-200, doi: 10.1038/nature04233

- [6] H. Wang, Q. Wang, K.-G. Zhou, and H.-L. Zhang, "Graphene in Light: Design, Synthesis and Applications of Photo-active Graphene and Graphene-Like Materials." Small 9, no. 8, 2013, pp. 1266-1283

- [7] S. Seo, M. Min, S.M. Lee, and H. Lee, "Photo-switchable molecular monolayer anchored between highly transparent and flexible graphene electrodes," Nature communications, 4, 2013, p.1920

- [8] C. Lee, X. Wei, J. W. Kysar, J. Hone, "Measurement of the Elastic Properties and Intrinsic Strength of Monolayer Graphene," Science 18 Jul. 2008, Vol. 321, Issue 5887, pp. 385-388, DOI: 10.1126/science.1157996

- [9] K. I. Bolotin, K.J. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P. Kim and H.L. Stormer, "Ultrahigh electron mobility in suspended graphene," Solid State Comm. vol. 146, June 2008, pp. 351-355, doi:10.1016/j.ssc.2008.02.024

- [10] Y. Zhang, Y.-W. Tan, H. L. Stormer & P. Kim, "Experimental observation of the quantum Hall effect and Berry's phase in graphene," Nature, vol. 438, Nov. 2005, pp. 201-204, doi:10.1038/nature04235

- [11] J. S. Moon, D. Curtis, M. Hu, D. Wong, C. McGuire, P.M. Campbell, G. Jernigan, J.L. Tedesco, B. VanMil, R. Myers-Ward and C. Eddy Jr, "Epitaxial-Graphene RF Field-Effect Transistors on Si-Face 6H-SiC Substrates," IEEE Elec. Dev. Lett., vol. 30, pp. 650-652, doi: 10.1109/LED.2009.2020699

- [12] D. J. Frank, Y. Taur, and H. -S. P. Wong, "Generalized Scale Length for Two-Dimensional Effects in MOSFET's," IEEE Elec. Dev. Lett., vol. 19, Oct. 1998, pp. 385-387, doi: 10.1109/55.720194

- [13] Max C. Lemme, Tim J. Echtermeyer, Matthias Baus, and Heinrich Kurz, "A Graphene Field-Effect Device," IEEE ELEC. DEV. LETT., VOL. 28, APRIL 2007, pp. 282-284, doi: 10.1109/LED.2007.891668

- [14] D. B. Farmera, Y.-M. Lin and Ph. Avouris, "Graphene field-effect transistors with self-aligned gates," Appl. Phys. Lett. vol. 97, July 2010, pp. 013103/1-013103/3, doi:10.1063/1.3459972

- [15] L. Liao, Y.C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K.L. Wang, Y. Huang, and X. Duan, "High-speed graphene transistors with a self-aligned nanowire gate," Nature, vol. 467, Sep. 2010, pp. 305–308, doi: 10.1038/nature09405

- [16] J. S. Moon, D. Curtis, S. Bui, T. Marshall, D. Wheeler, I. Valles, S. Kim, E. Wang, X. Weng and M. Fanton, "Top-Gated Graphene Field-Effect Transistors Using Graphene on Si (111) Wafers," IEEE Elec. Dev. Lett., vol. 31, Nov. 2010, pp. 1193-1195, doi: 10.1109/LED.2010.2065792

- [17] Y.M. Lin, C. Dimitrakopoulos, K.A. Jenkins, D.B. Farmer, H.Y. Chiu, A. Grill, and P. Avouris, "100-GHz transistors from wafer-scale epitaxial graphene," Science, 327(5966), 2010, pp.662-662

- [18] R. S. Shishir and D. K. Ferry, "Intrinsic mobility in graphene," J. Phys.: Condens. Matter vol. 21, June 2009, pp. 232204/1-232204/4, doi: 10.1088/0953-8984/21/23/232204

- [19] J. Yan, Y. Zhang, P. Kim and A. Pinczuk, "Electric Field Effect Tuning of Electron-Phonon Coupling in Graphene," Phys. Rev. Lett. vol. 98, Apr. 2007, pp. 166802/1-166802/4, doi: 10.1103/PhysRevLett.98.166802

- [20] A. Konar, T. Fang and D. Jena, "Effect of high-k gate dielectrics on charge transport in graphene-based field effect transistors," Phys. Rev. B, vol. 82, Sep. 2010, pp. 115452/1-115452/7, doi: 10.1103/PhysRevB.82.115452

- [21] A. K. Geim and K. S. Novoselov, "The rise of graphene," Nature Mat.erials, vol. 6, Mar. 2007, pp. 183-191, doi: 10.1038/nmat1849

- [22] G. M. Rutter, J. N. Crain, N. P. Guisinger, T. Li, P. N. First, and J. A. Stroscio, "Scattering and Interference in Epitaxial Graphene," Science. vol. 317, July 2007, pp. 219-222, doi: 10.1126/science.1142882

- [23] M.I. Katsnelson and A.K. Geim, "Electron scattering on microscopic corrugations in graphene," Phil. Trans. R. Soc. A, vol. 366, Jan. 2008, pp.195-204, doi: 10.1098/rsta.2007.2157

- [24] C. Jang, S. Adam, J.-H. Chen, E. D. Williams, S. Das Sarma, and M. S. Fuhrer, "Tuning the Effective Fine Structure Constant in Graphene: Opposing Effects of Dielectric Screening on Short-and Long-Range Potential Scattering," Phys. Rev. Lett. vol.101, Oct. 2008, pp.146805/1-146805/4, doi: 10.1103/PhysRevLett.101.146805

- [25] Y. Zhang, Y.-W. Tan, H. L. Stormer and P. Kim, "Experimental observation of the quantum Hall effect and Berry's phase in graphene," Nature, vol. 438, Nov. 2005, pp. 201-204, doi:10.1038/nature04235

- [26] X. Li, W.Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, and S.K. Banerjee., "Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils," Science, vol. 324, June 2009, pp. 1312-1314, doi: 10.1126/science.1171245

- [27] A. Reina, X. Jia, J. Ho, D. Nezich, H. Son, V. Bulovic, M. S. Dresselhaus and J. Kong, "Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition," Nano Lett., vol. 9, Dec. 2008, pp. 30–35, doi: 10.1021/nl801827v

- [28] Y. Lee, S. Bae, H. Jang, S. Jang, S. E. Zhu, S. H. Sim, Y.I. Song, B. H. Hong, J. H. Ahn, "Wafer-scale synthesis and transfer of graphene films," Nano letters, 10(2), Jan 2010, pp. 490-493

- [29] J. D. Caldwell, T.J. Anderson, J.C. Culbertson, G.G. Jernigan, K.D. Hobart, F.J. Kub, M.J. Tadjer, J.L. Tedesco, J.K. Hite, M.A. Mastro, and R.L. Myers-Ward, "Technique for the Dry Transfer of Epitaxial Graphene onto Arbitrary Substrates," ACS Nano, Jan. 2010, 4 (2), pp 1108–1114, DOI: 10.1021/nn901585p

- [30] S. Bae, H. Kim, Y. Lee, X. Xu, J.S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H.R. Kim, Y.I. Song, and Y.J. Kim, "Roll-to-roll production of 30-inch graphene films for transparent electrodes," Nature nanotechnology, Aug. 2010, *5*(8), pp.574-578

- [31] D.K. Gaskill, G. Jernigan, P. Campbell, J.L. Tedesco, J. Culbertson, B. VanMil, R.L. Myers-Ward, C. Eddy, J. Moon, D. Curtis, and M. Hu, "Epitaxial Graphene Growth on SiC Wafers," ECS Trans., vol. 19, May 2009, pp. 117-124, doi: 10.1149/1.3119535

- [32] C. Berger, Z. Song, T. Li, X. Li, A.Y. Ogbazghi, R. Feng, Z. Dai, A.N. Marchenkov, E.H. Conrad, P.N. First, and W.A. De Heer, "Ultrathin Epitaxial Graphite: 2D Electron Gas Properties and a Route toward Graphene-based Nanoelectronics," J. Phys. Chem. B, vol. 108, Dec. 2004, pp. 19912-19916, doi: 10.1021/jp040650f

- [33] P. Y. Huang, C.S. Ruiz-Vargas, A.M. van der Zande, W.S. Whitney, M.P. Levendorf, J.W. Kevek, S. Garg, J.S. Alden, C.J. Hustedt, Y. Zhu, and J. Park, "Grains and grain boundaries in single-layer graphene atomic patchwork quilts," Nature 469, Jan. 2011, pp. 389–392, doi:10.1038/nature09718

- [34] P. Nemes-Incze, K.J. Yoo, L. Tapasztó, G. Dobrik, J. Lábár, Z.E. Horváth, C. Hwang, and L.P. Biró, "Revealing the grain structure of graphene grown by chemical vapor deposition," Appl. Phy. Lett., Jul. 2011 1;99(2):023104

- [35] A. C. Ferrari, J.C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscanec, D. Jiang, K.S. Novoselov, S. Roth, and A.K. Geim, "Raman Spectrum of Graphene and Graphene Layers," Phys. Rev. Lett., vol. 97, Oct. 2006, pp.187401/1-187401/4, doi: 10.1103/PhysRevLett.97.187401

- [36] A. Gupta, G. Chen, P. Joshi, S. Tadigadapa and P. C. Eklund, "Raman scattering from high-frequency phonons in supported n-graphene layer films," Nano Lett., vol. 6, Nov. 2006, pp. 2667-2673, doi: 10.1021/nl061420a

- [37] J. S. Moon, D. Curtis, M. Hu, D. Wong, P. M. Campbell, G. Jernigan, J. Tedesco, B. VanMil, R. Myers-Ward, C. Eddy, D. K. Gaskill, J. Robinson, M. Fanton, P. Asbeck, "Development toward Wafer-Scale Graphene RF Electronics," ECS Trans., vol. 19, May 2009, pp. 35-40, doi: 10.1149/1.3119525

- [38] Y.-M. Lin, C. Dimitrakopoulos, K.A. Jenkins, D.B. Farmer, H.Y. Chiu, A. Grill, and P. Avouris, "100-GHz Transistors from Wafer-Scale Epitaxial Graphene," Science, vol. 327, Feb. 2010, p. 662, doi: 10.1126/science.1184289

- [39] K. Kim, "From the future Si technology perspective: Challenges and opportunities," IEEE Intl. Elec. Dev. Meeting (IEDM 2010), Dec. 2010, pp. 1.1.1 1.1.9, doi: 10.1109/IEDM.2010.5703274

- [40] J.S. Moon, M. Antcliffe, H.C. Seo, D. Curtis, S. Lin, A. Schmitz, I. Milosavljevic, A.A. Kiselev, R.S. Ross, D.K. Gaskill, and P.M/ Campbell, "Ultra-low resistance ohmic contacts in graphene field effect transistors," Appl. Phys. Lett. 100(20), 2012, p.203512

- [41] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L. Shepard, "Current saturation in zero-bandgap, top-gated graphene field-effect transistors," Nat. Nanotechnol., vol. 3, Nov. 2008, pp. 654–659, doi: 10.1038/nnano.2008.268