# UC Santa Barbara

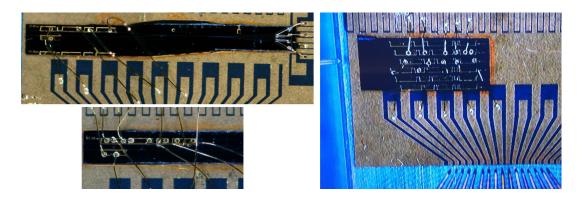

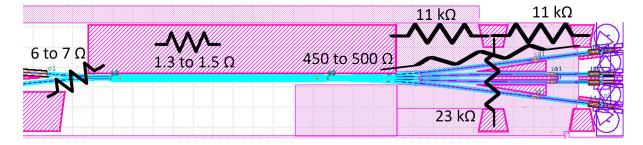

**UC Santa Barbara Electronic Theses and Dissertations**

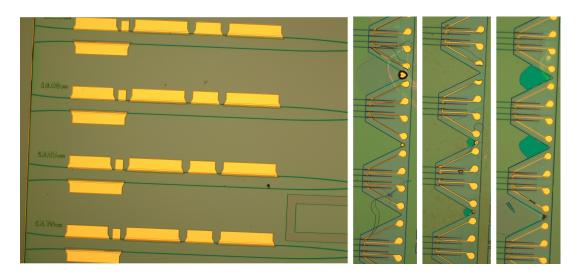

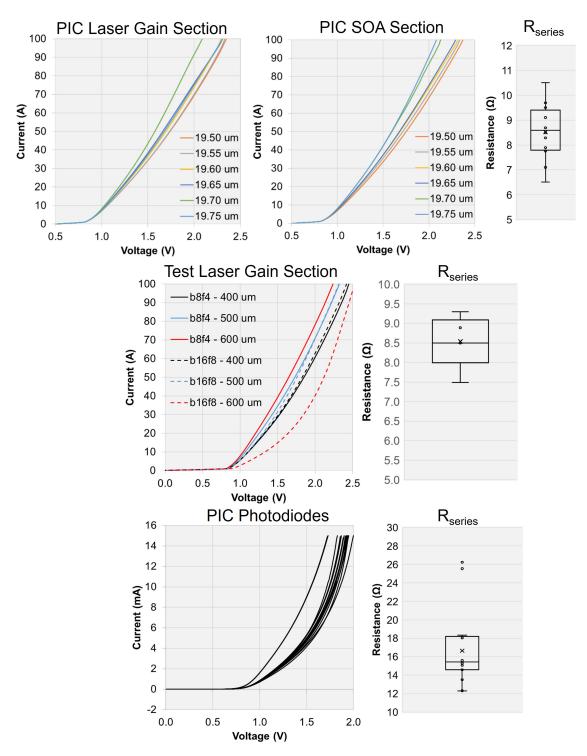

### Title

Coherent Receivers for O-band, Short Reach Optical Links

### Permalink

https://escholarship.org/uc/item/2r8441j3

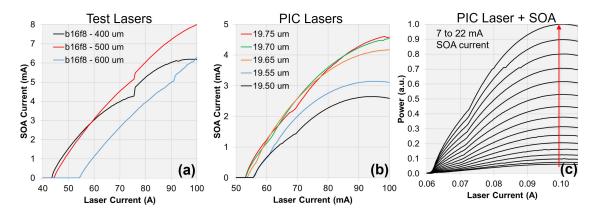

### Author

Misak, Stephen Michael

# **Publication Date**

2024

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

# Coherent Receivers for O-band, Short Reach Optical Links

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

Stephen Misak

Committee in charge:

Professor Clint Schow, Co-chair Professor Larry Coldren, Co-chair Professor James Buckwalter Professor Adel Saleh

December 2024

The Dissertation of Stephen Misak is approved.

Professor James Buckwalter

Professor Adel Saleh

Professor Larry Coldren, Committee Co-chair

Professor Clint Schow, Committee Co-chair

December 2024

Coherent Receivers for O-band, Short Reach Optical Links

Copyright  $\bigcirc 2024$

$\mathbf{b}\mathbf{y}$

Stephen Misak

Dedicated to my Mom and Dad for their love, patience, and support

#### Acknowledgements

I am grateful for the years of support and advice I have received from my advisor Clint Schow and from Larry Coldren. They provided invaluable guidance with difficult problems and encouragement to keep moving forward.

I want to acknowledge Jim Buckwalter, Adel Saleh, Jonathan Klamkin, and their students for their contributions to the INTREPID project. For all of their help and for sharing good times over the years, I am thankful for Takako Hirokawa, Yujie Xia, Steven Estrella, Aaron Maharry, Hector Andrade, Aaron Wissing, Xinhong Du, Junqian Liu, Viviana Arrunategui-Norvick, Ghazal Movaghar, and Evan Chansky. We have struggled together in the lab, but we have also laughed together outside of work at game and movie nights. I want to thank Yujie for the time we spent together working on the first generation InP receiver. It was a lot of hard work, but we were able to overcome the challenges in the end. I am also grateful to Xinhong for his technical and moral support during my time in the cleanroom and for our weekend badminton matches. I am glad to have Aaron M as a friend and former roommate. We have shared many good memories since we both joined Clint's group in 2017. Thanks to David Plant, Jinsong Zhang, Zixian Wei, and the rest of the Plant group for all their work at McGill on the coherent link measurements and for the fun time we had together during our visit to Montreal.

Thanks to Takako for getting me involved in the Photonics Society at UCSB. I have enjoyed organizing and taking part in events where students have been able to learn and network professionals from academia and industry. The seminars, outreach events, beach BBQs, quantum industry showcases, and banquets were all exciting. I am proud to have contributed to the UCSB photonics community and happy to see the continued efforts by the current officers and members. I am glad to have spent time with Michael Nickerson, Michael Choquer, Caroline Reilly, Jiawei Wang, Kaikai Liu, Emily Trageser, Andrei Isichenko as officers. I am confident that the Photonics Society is in good hands to continue its mission of "developing a local and regional network of students and professionals for the purposes of engaging the community through photonics education and providing opportunities for career development."

Thanks to the UCSB Nanofab staff for keeping the cleanroom operational while advising me with my processing. Special thanks to Biljana Stamenic, Demis John, and Brian Thibeault for their exceptional help when I was starting Gen. 1 InP and for their thoughtful responses to all my questions. Thanks to Bill Mitchell for his help with e-beam lithography. Thanks to Alethia Butler-Nalin for all of her wirebonding work. Thanks to Mario Milicevic and Maxlinear for their support on the Keystone DSP. Thanks to V. V. Kumar, C. Kretzschmar, K. Giewont, T. Hirokawa, and K. Dezfulian at GlobalFoundries for their support with RX PIC design and fabrication. Thanks to R. Nagarajan and L. Qin and their teams at Marvell for driver and TIA support.

Thanks to Intel Silicon Photonics and Intel Labs for assistance with design of the SG-DBR lasers and coherent TX/RX PICs and to Intel F11X for fabrication of all the PICs. Special thanks to the many great people who helped with questions and other work while at Intel, including: Ansheng Liu, Giovanni Gilardi, Matthew Sysak, Ranjeet Kumar, Richard Jones, Sean Liao, John Heck, Md. Mahbub Satter, Dina Unadkat, Hari Mahalingam, David Patel, Nutan Gautam, Olufemi Dosunmu, Meer Sakib, Duanni Huang, Karan Mehta, Mengyuan Huang, Keija Li, Thomas Pham, Boris Vulovic, Lobna Kamyab, Siamak Amiralizadeh, and Yuliya Akulova. I am grateful that I had the opportunity to meet you in person and learn from all of you.

The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency Energy (ARPA-E), U.S. Department of Energy, under Award Number DE-AR0000848. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

### Curriculum Vitæ Stephen Misak

### Education

| 2024 | Ph.D. in Electrical and Computer Engineering, University of California, Santa Barbara.                                                               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara.                                                                |

| 2017 | B.S. in Engineering Physics, Optical Engineering Minor, Semicon-<br>ductor Materials and Devices Certificate, Rose-Hulman Institute of<br>Technology |

### Publications

S. Misak, A. Wissing, J. Liu, V. Arrunategui-Norvick, A. Maharry, H. Andrade, M. Milicevic, E. Chansky, G. Movaghar, X. Du, G. Gilardi, R. Kumar, G. Su, A. Liu, Y. Akulova, J. F. Buckwalter, A. A. M. Saleh, L. Coldren, and Clint L. Schow, "Mixed domain coherent link with electrically reconfigurable IMDD and coherent modes for O-band data center applications," Opt. Express 32, 38550-38559 (2024). doi: 10.1364/OE.532184

S. Misak, A. Wissing, J. Zhang, Z. Wei et al. "400 Gbps/ $\lambda$  DP-16QAM O-band Link with SiP TX and RX PICs using only Heterogeneously Integrated Lasers and SOAs for Optical Gain," in 2024 Optical Fiber Communications Conference and Exhibition (OFC), Mar. 2024, pp. 1–3.

S. Misak et al. "Heterogeneously Integrated O-band SG-DBR Lasers for Short Reach Analog Coherent Links," in OSA Advanced Photonics Congress 2021 (2021), paper JTh3A.1, Jul. 2021, p. JTh3A.1. doi: 10.1364/IPRSN.2021.JTh3A.1

S. Misak, J. Beil, R. Swertfeger, and P. Leisher. "Investigating the Modal Dependencies of Beam Quality - Via Spectrally-resolved Imaging of the Mode Structure in Diode Lasers." Proceedings of the 5th International Conference on Photonics, Optics and Laser Technology – PHOTOPTICS (2017), ISBN 978-989-758-223-3; ISSN 2184-4364, SciTePress, pages 245-251. doi: 10.5220/0006152702450251

S. Misak, D. Dugmore, K. Middleton, E. Hale, K. Farner, K. Choquette, and P. Leisher. "Spectrally resolved imaging of the transverse modes in multimode VCSELs." In Vertical-Cavity Surface-Emitting Lasers XIX (Vol. 9381, pp. 156-162). SPIE. (2015, March) doi: 10.1117/12.2076629

J. Zhang, Z. Wei, S. Misak, A. Wissing et al. "First Demonstration of 200-G Coherent PON at O-band with Heterogeneously-Integrated SiP Tx and Rx with Lasers," in 2024 Optical Fiber Communications Conference and Exhibition (OFC), Mar. 2024, pp. 1–3.

A. Maharry, H. Andrade, S. Misak, J. Liu, Y. Xia, A. Wissing, G. Movaghar, V. Arrunategui-Norvick, E. D. Chansky, X. Du, A. A. M. Saleh, J. F. Buckwalter, L. Coldren, and C. L. Schow, "Integrated SOAs enable energy-efficient intra-data center coherent links," Opt. Express 31 (May, 2023) 17480–17493. doi: 10.1364/OE.486407

J. Liu, A. Maharry, A. Wissing, H. Andrade, S. Misak, G. Gilardi, S. Liao, A. Liu, Y. Akulova, L. Coldren, J. Buckwalter, C. Schow. "First O-band silicon coherent transmitter with integrated hybrid tunable laser and SOAs," Proc. SPIE 12426, Silicon Photonics XVIII, 124260A (13 March 2023). doi: 10.1117/12.2668010

A. Maharry et al., "First Demonstration of an O-Band Coherent Link for Intra-Data Center Applications," in Journal of Lightwave Technology, doi: 10.1109/JLT.2023.3290487.

A. Maharry, J. Liu, S. Misak, H. Andrade, L. A. Valenzuela, G. Gilardi, S. Liao, A. Liu, Y. Akulova, L. Coldren, J. F. Buckwalter, and C. L. Schow. "First Demonstration of an O-Band Coherent Link for Intra-Data Center Applications," in European Conference on Optical Communication (ECOC) 2022, J. Leuthold, C. Harder, B. Offrein, and H. Limberger, eds., Technical Digest Series (Optica Publishing Group, 2022), paper Mo4F.4.

T. Hirokawa et al. "Analog Coherent Detection for Energy Efficient Intra-Data Center Links at 200 Gbps Per Wavelength," in Journal of Lightwave Technology, vol. 39, no. 2, pp. 520-531, 15 Jan.15, 2021, doi: 10.1109/JLT.2020.3029788

J. Beil, L. Shimomoto, R. Swertfeger, S. Misak, J. Campbell, J. Thomas, D. Renner, M. Mashanovitch, P. Leisher, R. Liptak. "Improvements to tapered semiconductor MOPA laser design and testing," Proc. SPIE 10514, High-Power Diode Laser Technology XVI, 105140U (19 February 2018). doi: 10.1117/12.2289933

J. Beil, R. Swertfeger, S. Misak, Z. Gao, K. Choquette, and P. Leisher. "Semiconductor Laser Beam Quality Metrics for Free-Space Optical Communications." Proceedings of the 5th International Conference on Photonics, Optics and Laser Technology – PHO-TOPTICS (2017), ISBN 978-989-758-223-3; ISSN 2184-4364, SciTePress, pages 196-201. doi: 10.5220/0006122601960201

R. Swertfeger, J. Beil, S. Misak, J. Thomas, J. Campbell, D. Renner, M. Mashanovitch, and P. Leisher. "Direct Observation of the 2D Gain Profile in High Power Tapered Semiconductor Optical Amplifiers." Proceedings of the 5th International Conference on Photonics, Optics and Laser Technology – PHOTOPTICS (2017), ISBN 978-989-758-223-3; ISSN 2184-4364, SciTePress, pages 114-121. doi: 10.5220/0006187301140121

T. Balz, A. Bernal, W. Kline, J. Livingston, S. Misak. "Finding a Passion and Making It Happen: A Program's Approach to Promoting Entrepreneurship, Making, and Innovation through Hands-On Projects that Benefit Society." 2017 ASEE Annual Conference & Exposition, Columbus, Ohio. (2017, June) doi: 10.18260/1-2-28356

R. Swertfeger, J. Beil, S. Misak, J. Thomas, J. Campbell, D. Renner, M. Mashanovitch, and P. Leisher. "Direct Observation of the 2D Gain Profile in High Power Tapered Semiconductor Optical Amplifiers." In Proceedings of the 5th International Conference on Photonics, Optics and Laser Technology - PHOTOPTICS, ISBN 978-989-758-223-3; ISSN 2184-4364, SciTePress, pages 114-121. (2017) DOI: 10.5220/0006187301140121

G. Brodnik, S. Misak, D. Dugmore, E. Hale, K. Middleton, and P. Leisher. "Real-time spectrally-resolved imaging of the transverse modes in broad area diode lasers," 2015 11th Conference on Lasers and Electro-Optics Pacific Rim (CLEO-PR), Busan, Korea (South), 2015, pp. 1-2, doi: 10.1109/CLEOPR.2015.7376072

#### Abstract

Coherent Receivers for O-band, Short Reach Optical Links

by

#### Stephen Misak

High bandwidth optical links are required to support the continual increases in the demand for high-resolution video, high-performance computing, machine learning, cloud computing, the Internet of Things (IoT), 5G networks, and other applications. In particular, the bandwidth requirements for short reach inter- and intra-data center optical links are reaching the capability limits of the industry standard intensity modulation, direct detection (IMDD) links. Coherent modulation, while more complex for a single optical link, can operate at higher data rates and spectral efficiency by encoding multiple bits per symbol. The high sensitivity of coherent links also enables data centers to replace electrical switches with optical switches, reducing overall power consumption and hardware cost. O-band coherent receivers (RX) on indium phosphide (InP) and silicon photonics (SiP) platforms will be discussed in this dissertation. These receivers were designed for compatibility with an analog coherent link architecture using an optical phase-locked loop, but they can also be used in a traditional coherent link. Tradeoffs in design, performance, and manufacturability between material platforms will be discussed. The design, fabrication, and measurements from two generations of InP O-band coherent RX PICs will be described. Two generations of O-band coherent RX PICs fabricated using Intel's SiP process (with and without integrated lasers) and a dual-mode coherent RX using Global Foundries 45SPCLO will also be shown. A sampled-grating distributed Bragg reflector (SG-DBR) laser designed for O-band coherent RXs using Intel's SiP process will be presented. To demonstrate the RX PICs, they are packaged with high-speed electronic integrate circuits (EICs) and measured with multiple coherent modulation formats using digital signal processing (DSP) or analog electronics for data recovery. Architectures using reduced DSP or analog electronics both show promise for energy efficient, short reach coherent links.

# Contents

| Cı           | urriculum Vitae                                                 |  | vii       |  |

|--------------|-----------------------------------------------------------------|--|-----------|--|

| $\mathbf{A}$ | bstract                                                         |  | x         |  |

| 1            | Introduction                                                    |  |           |  |

|              | 1.1 Brief History of Optical Communications                     |  | 1         |  |

|              | 1.2 Data Center Scaling and INTREPID                            |  |           |  |

|              | 1.3 Preview of Dissertation                                     |  |           |  |

| <b>2</b>     | PIC Design for Coherent Communication                           |  | 13        |  |

|              | 2.1 Basics of Coherent Optical Communications                   |  |           |  |

|              | 2.2 Material and Integration Platforms                          |  | 19        |  |

|              | 2.3 Photonic Component Design                                   |  | 24        |  |

| 3            | Generation 1 InP O-band Coherent Receiver                       |  | <b>54</b> |  |

|              | 3.1 Gen. 1 PIC Design                                           |  | 55        |  |

|              | 3.2 Gen. 1 PIC Fabrication                                      |  | 69        |  |

|              | 3.3 Gen. 1 PIC Characterization                                 |  | 89        |  |

|              | 3.4 Gen. 1 Receiver Assemblies                                  |  | 97        |  |

| <b>4</b>     | Generation 2 InP O-band Coherent Receiver                       |  | 105       |  |

|              | 4.1 Gen. 2 InP PIC Design                                       |  | 105       |  |

|              | 4.2 Gen. 2 InP PIC Fabrication                                  |  | 110       |  |

|              | 4.3 Gen. 2 InP RX - Device Testing                              |  | 138       |  |

|              | 4.4 InP PIC Processing Challenges, Lessons, and Recommendations |  | 143       |  |

| <b>5</b>     | Silicon Based PICs for O-band Coherent Links                    |  | 147       |  |

|              | 5.1 Heterogeneous III-V on Si based tunable lasers              |  | 148       |  |

|              | 5.2 IQ Traveling Wave Modulator                                 |  | 153       |  |

|              | 5.3 Coherent Receivers                                          |  | 155       |  |

| 6            | Short Reach O-band Coherent Link Demonstrations |                                            | 160        |  |

|--------------|-------------------------------------------------|--------------------------------------------|------------|--|

|              | 6.1                                             | Integrated Laser Intradyne Coherent Link   | 161        |  |

|              | 6.2                                             | Reconfigurable Mixed Domain Coherent Link  | 168        |  |

| 7            | Con                                             | clusion                                    | 178        |  |

|              | 7.1                                             | Outlook on Data Centers and Coherent Links | 178        |  |

|              | 7.2                                             | Summary of Work                            | 185        |  |

|              | 7.3                                             | Future Work                                | 186        |  |

| $\mathbf{A}$ | MA                                              | TLAB Code                                  | 188        |  |

|              | A.1                                             | MMI Transmittance                          | 188        |  |

| в            | InP                                             | Process Flows                              | 192        |  |

|              | B.1                                             | Generation 1 InP RX Process                | 192        |  |

|              | B.2                                             | Generation 2 InP RX Process                | 192        |  |

| Bi           | bliog                                           | raphy                                      | <b>212</b> |  |

# Chapter 1

# Introduction

### **1.1** Brief History of Optical Communications

While light has been used for millennia to transmit signals via fire, smoke, or mirrors, the development of modern optical links began soon after Charles Townes and Arthur Schawlow published the proof of concept paper for the laser, and Theodore Maiman built the first working laser in 1960 [1]. The laser initiated the development of free-space optical links, but commercialization of long distance optical communication through glass fibers was not feasible due to excessive optical loss. Several groups separately raced to reduce the optical loss. The first long distance links in the late 1970s used Corning glass fiber with losses of 3 dB/km and Bell Laboratories GaAs semiconductor lasers at 850 nm to transmit data with repeaters every 10 km [2]. The modern 0.2 dB/km at 1.55  $\mu$ m was attained in 1979 by a Japanese group through refinement of the fiber preform growth process to reduce imperfections [3]. Another major improvement to the growth process reduced the impact of the SiOH impurities, which lead to the so-called OH or "water peak," bringing the loss down from multiple dB/km to around 0.3 dB/km [2, 4]. There have been some groups who have made slight reductions to fiber loss, but 0.3 to 0.2 dB/km from 1310 to 1550 nm remain the standard values to this day.

Introduction of opto-electronic integrated circuits (OEIC) for communications began with advances in photolithography technology and the analysis of dielectric waveguides [5]. GaAs lasers at 850 nm with silicon detectors were employed in the first generation of optical communication systems, but systems transitioned to InP at wavelengths centered around 1310 and 1550 nm for lower dispersion and reduced fiber loss in the 1980s. The first coherent receivers on InP with an integrated laser, a  $2 \times 2$  coupler, and photodiodes were made at NTT and Bell labs in 1989, publishing their work within the same month [6, 7]. Photonic integrated circuits (PIC) became a common term in the 1990s [8] with continued work on InP. Communication systems were struggling to improve the span between signal regeneration in the 1980s. Coherent communication offered benefits in spectral efficiency (SE) and sensitivity to improve the reach, but the invention of the erbium doped fiber amplifier (EDFA) provided a simpler method of increasing reach. Research on coherent communications was largely put on hold from 1990 to 2004 with advances in EDFA technology, fiber dispersion compensation, wavelength division multiplexing (WDM), forward error correction (FEC), and differential quadrature phase shift keying (DQPSK). The broad gain spectrum of the EDFA supported many WDM channels. From 1996 to 2007, research results on overall fiber capacity grew from 1 Tb/s to 25 Tb/s, with 11 Tb/s and 25 Tb/s hero demonstrations including 273 and 160 WDM channels. Commercial systems followed this trend with lag time of several years, introducing 1 Tb/s systems in the early 2000s, right around time that the telecommunications bubble burst [4, 9].

Research into coherent coherent communication systems expanded a few years after the telecommunications bubble as WDM systems filled the EDFA gain spectrum. Coherent systems offered higher SE, better receiver sensitivity, and access to the optical field in digital form for signal processing. CMOS digital-to-analog converters (DACs) for transmitters and analog-to-digital converters (ADCs) for receivers had improved enough to enable signal processing for correction of chromatic dispersion, polarization-mode dispersion, and other fiber nonlinear effects at 10 Gbaud [9]. Nortel and Alcatel-Lucent brought coherent transceivers to market at 10 and 28 Gbaud in 2008 and 2009. Over the next few years, coherent gained dominance in long-haul networks, and metro networks started using 100 Gb/s coherent systems following the 100 Gb/s Ethernet standard.

Today, coherent has entered the data center interconnect (DCI) market with the 400G modules following the OIF 400ZR standard for point to point links up to 120 km. The deployment of 400G modules has grown since the standards were published in 2020. In October 2024, OIF finalized the 800ZR standard, and Acacia/Cisco already demonstrated 800G modules at OFC2024. As bandwidth continues to scale, especially in data center applications, it is likely that the benefits of coherent will lead to transceivers with a target reach below 2 km for data center campus and intra-data center interconnects, possibly in the 1.6 or 3.2 Tb/s transceiver generations [10]. The next section will discuss some of the driving forces for short reach coherent links and potential packaging form factors.

# 1.2 Data Center Scaling and INTREPID

As the demands for internet traffic and machine learning continue to drive data center scaling [11, 12, 13], there has been a substantial amount of research and development led by both industry and academia to devise feasible solutions to the future bandwidth and power consumption requirements. Improvements to the intra-data center network will have a significant impact on efficiency and power consumption with >70% of the zetabytes (10<sup>21</sup>) of data center traffic sent between servers in the same location. In future data centers acting as artificial intelligence (AI) clusters, the server rack bandwidth and power consumption requirements are expected to be 10 times larger than traditional data center at >100 Tbps and >100 kW [13]. Pluggable 10/25/100G intensity-modulation directdetection (IMDD) transceiver connections to Ethernet switch ports comprise a large part of the current data center transceiver market, but 400G and 800G solutions are expected to grow over the next few years [13]. Optical links for 400G and 800G transceivers are using 53/56 Gbaud PAM4 modulation with channels on parallel fibers for data center reach (DR) up to 500m. Wavelength division multiplexed channels for fiber reach (FR) up to 2 km and long reach (LR) up to 10 km are also common for hyper-scale data centers. Transceivers using 106 Gbaud PAM4 for 1.6T interconnects been developed by Accelink (with Cisco), Coherent, Innolight, and Eoptolink for DR applications. The switches connecting the data center racks have been operating with 12.8 and 25.6 Tb bandwidth, but 51.2 Tb switches have recently entered the market with NVIDIA, Marvell, Broadcom, and Cisco offering competing chips for leaf/spine switches [14]. Future scaling to 102.4 Tb switches is currently in development.

While 1.6T transceivers have been shown up to 2 km, coherent transceivers are capable of longer reaches or increased link budget while also providing more spectral efficiency. In recent years, coherent communication for short reach, O-band data center links has gained support as a solution to address data center scaling [15, 16, 17]. To demonstrate the capabilities of coherent for improving link budget and reducing power consumption, the INTelligent Reduction of Energy through Photonic Integration for Datacenters (IN-TREPID) [18] project was started in 2017 as part of the ENergy-efficient Light-wave Integrated Technology Enabling Networks that Enhance Datacenters (ENLITENED) [19, 20] program funded by the Advanced Research Projects Agency - Energy (ARPA-E). The ENLITENED program was created in response to the rising power consumption of data centers in the USA. Estimated at 2.5% of total power in 2017, demand for data center services continues to rise with the fraction currently at >4% and expected to reach 6% by 2026 [21].

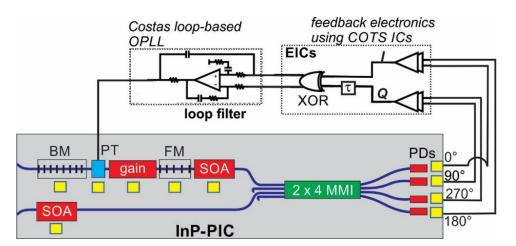

The INTREPID project planned to demonstrate transceiver components and new link architectures for improving the bandwidth, cost, latency, and power consumption of data centers. Increasing the energy efficiency of individual links is one method for energy reduction. This can be achieved by low power vertical-cavity surface emitting laser (VCSEL) optical links at moderate bandwidth and short reach links within a server rack or within a row of racks. Coherent optical links with high bandwidth and moderate power can also reduce power consumption and offer >2 km length. Coherent optical links with reduced power were the main focus with some work on VCSEL links [22] during early stages of the INTREPID project. Coherent links at O-band (1260 - 1360 nm) minimize chromatic dispersion, and analog electronics used in place of application specific integrated circuits (ASICs) for digital signal processing (DSP) enable significant power savings. A proof of concept demonstration for low power coherent links with integrated InP photonics using an optical phase-locked loop (OPLL) was made by Mingzhi Lu, Eli Bloch, Hyun-chul Park, and other collaborators in 2012, led by Larry Coldren and Mark Rodwell [23, 24, 25, 26]. Their work builds on a long series of improvements to OPLLs since the first free-space demonstration in 1965 and the first integrated InP photonic demonstration in 2009 [27, 28]. Expanding on their work and the analysis done by Joe Kahn, Anujit Shastri and Jose Perin in [15], a major target of INTREPID was to construct O-band coherent PICs capable of 200 Gbps/ $\lambda$  that can be paired with analog OPLL circuitry to replace the carrier recovery functions of DSP for power savings [29].

#### **1.2.1** Integrated Circuit Efficiency Optimization

A significant fraction of the power (>50%) for IMDD and coherent links come from the DSP, ADC, and DAC circuits [30, 31], so improving these circuits is a clear path to increasing energy efficiency. Replacing DSP circuits with analog electronics for an OPLL forms the basis of the "analog coherent" link design proposed as part of the INTREPID project, but additional power can be saved by using QPSK modulation with limiting electronics which can achieve efficiency of <1 pJ/bit [32] compared to ADCs which can consume between 4 and 12 pJ/bit [30]. The efficiency of ADCs has also been improving with smaller process nodes edging closer to 1 pJ/bit [33]. Prototype circuits for analog phase recovery have been made on 130 nm BiCMOS SiGe [34] and 130 nm SiGe HBT [35] node with 400 mW (10 pJ/bit at 40 Gb/s) and 200 mW (2 pJ/bit at 100 Gb/s) power consumption, and further improvements are possible with smaller process nodes. A direct comparison to DSP chips optimized for short reach coherent is not possible at this time, but analysis indicates that power consumption for short reach coherent DSP is close to 1.6 times PAM4 DSP [36]. Using advanced process nodes, PAM4 DSP chips consume approximately 5 pJ/bit [37], so the equivalent coherent DSP would be close to 8 pJ/bit. This indicates that analog electronics replacements for DSP using advanced process nodes can potentially save several pJ/bit.

### **1.2.2** Packaging Considerations

In addition to the power savings from the design of a single optical link, the packaging interface between the optical links and the server is another area for improvement. Pluggable transceivers suffer from channel loss of the high speed electrical signal travelling through the PCB channel from the pluggable to the server ASIC. Due to packaging constraints on electrical interconnect density using ball grid arrays (BGA) or land grid arrays (LGA) with  $\sim$ 1 mm pitch, the bandwidth density of the interconnects between the PIC and the electronic integrated circuits (EICs) is also limited. Co-packaged optics (CPO) is also part of the INTREPID project's vision for future data centers to overcome these limitations [38]. Using flip chip bonding of the PIC and EIC onto a silicon interposer (2.5D integration), enables the use of finer C4 pitch (~  $130\mu m$ ) which increases the connection density by a factor of ~60. The short connection length between PIC and EIC through the interposer also reduces the electrical losses which can lead to a  $10\times$  improvement in the energy efficiency [38]. The advantages of CPO have lead several companies to develop the technology [39].

Ranovus has been developing their optical engine with PICs from GlobalFoundries (GF) Fotonix process. They have been partnering with multiple companies to develop 3 generations of CPO products using 100Gbps PAM4 [40, 41]. Intel demonstrated a 12.8T switch with LGA and soldered connections [42]. Broadcom have 25.6T CPO switches in production with deployments in Tencent's network, and have shown 51.2T CPO switches with 50% power savings and lower cost compared to pluggable solutions [43, 44, 45]. Marvell showed 2.5D heterogeneous integration of drivers and TIAs that are flip chip bonded to a silicon photonics (SiP) chip that is connected to an multi-layer organic substrate through C4 bumps. This 2.5D light engine was integrated into an LGA package as part of optical module which was tested in a full system demonstration with Marvell's Teralynx 7 switch [46]. Cisco has developed 3.2 Tbps light engines based on SiP FR4 optical modules [47], and demonstrated them at OFC 2023 inside of a 25.6T switch [48]. IBM worked with Finisar (now part of Coherent Corp.) on the Multi-wavelength Optical Transceivers Integrated on Node (MOTION) project (also part of ENLITENED) to develop CPO based on VCSELs for low cost and high radix links [49, 50]. Rain Tree Photonics recently demonstrated a 1.6 Tbps (224 Gbps/ $\lambda$ ) optical engine for CPO based on fan-out wafer level packaging [51] at OFC 2024. NVIDIA has published an analysis of CPO discussing its feasibility and benefits [52], and they have also made a SiP light engine using GlobalFoundries Fotonix process [53]. TSMC also announced that it is working with Broadcom and NVIDIA to develop SiP for CPO [54].

While the power savings and density benefits of CPO solutions are clear, there are

a number of technical challenges that must be addressed from the device to module level. Starting at the device level, many pluggable transceivers use SiP Mach-Zehnder modulators (MZM), which consumer a significant amount of area due to their relatively large  $V_{\pi}$ , limiting the ability to improve the bandwidth density. Shrinking the modulators comes with the trade-off of higher voltage swing requirements to achieve the same optical modulation amplitude. These challenges can be addressed with co-design of the driving electronics and modulator, but the material properties of silicon will always limit the efficiency. Ring modulators offer very compact devices and enable dense wavelength division multiplexed (DWDM) link architectures, but they require wavelength locking feedback loops and more complex signal pre-distortion to compensate for their non-linear response [55]. Careful design is required to enable low DWDM crosstalk, though analysis by NVIDIA has shown that the concept is feasible [52]. Electro-absorption modulators (EAMs) integrated on Si also offer compact solution with good modulation efficiency, but fabrication is challenging. There have been some successful demonstrations of high speed EAMs integrated via micro-transfer printing and wafer bonding [56, 57, 58].

The increased component density also leads to challenges with thermal management where copper heat spreaders and cold plates with liquid cooling will likely be required [55, 52, 59], though Broadcom showed its CPO solution with air cooling [44]. Maintaining acceptable temperatures below 100°C for the high power density from the EICs with enough thermal isolation to keep the PICs below ~80°C will require more separation between the EIC and the PICs or efficient cooling solutions. Thermal expansion can also lead to issues with mechanical bowing, which will create fiber misalignment. To address thermal and reliability concerns, external lasers are often proposed for CPO to maintain efficiency and enable replacement in case of laser failure.

Broadening out to the module and system level, reliability and serviceability are major concerns since tight integration of the optical modules makes replacement of one module difficult if not impossible depending on the mounting and cooling design. There has been some progress on creating standards for CPO, with the Optical Internetworking Forum (OIF) publishing an implementation agreement (IA) for 3.2T CPO modules [60]. The IA and past demonstrations have shown integration of optical modules using high speed sockets, making replacement possible, but servicing for one module would likely take the entire switch systems offline, especially if liquid cooling solutions like the one in [59] are used.

The manufacturing cost and complexity are also major challenges with packaging and test are major contributors. The large fiber count of single mode fiber (SMF) and polarization maintaining fiber (PMF) adds cost and the fiber alignment process is also time consuming and expensive. V-groove alignment structures offer some improvement, but there are still issues with epoxy curing time and yield [59]. Issues with assembly have a large impact on yield and cost, since they typically occur at the final stage of assembly. Intel has recently shown a micro-optic glass bridge based using a periscope, which can be added earlier in the assembly process for better yield [61].

The efforts from Cisco, Broadcom, Intel, NVIDIA, and other companies show that the technical challenges can be overcome. Increases in production volume will likely lead to lower costs, but the timeline to more broad adoption and profitability of CPO solutions remains to be seen.

### 1.2.3 Optical Switching

Expanding out to the view of the data center as a whole, changes in the network architecture can have a much larger impact compared to individual links. Optical switching is a path to significant power savings and cost reduction compared to traditional electrical switching. Optical switches can be implemented with free-space beam steering using arrays of micro-electro-mechanical system (MEMS) mirrors or liquid crystal pixels, with bulk gratings or planar arrayed waveguide gratings (AWG), with integrated photonics using a network of  $2 \times 2$  switch cells, or with a combination of multiple methods. There are trade-offs with size, cost, port count scaling, wavelength selectivity, polarization dependency, switching speed, cross-talk, routing flexibility, and insertion loss for different solutions. The cost and power reduction of optical switching was recently demonstrated by Google. They reported a reduction of 30% in capital expenditure and 41% in power by changing from a Clos to a direct-connect topology using custom MEMS based optical circuit switches (OCS) for dynamic topology reconfiguration [62]. Optical switches provide lower latency and enable software defined data center network reconfigurability, which can be used for fast expansion with minimal interruption and optimization of job performance [63]. Reconfigurable optical switch networks can be leveraged to improve data center task execution through optimization of resource allocation in disaggregated data center networks [64]. Since optical switches do not perform any signal conversion, they are also transparent to the modulation format and bit rate. These benefits are valuable in cloud service and machine learning data center networks. Product development has been on the rise with Calient, Accelink, DiCon, and Agiltron offering MEMS optical switches; Polatis offering free-space piezo-electric beam steering optical switches; and Coherent demonstrating switches with liquid crystal technology. A newer start-up, Drut Technologies, has also developed optical switches along with interface cards and management software for a full system solution. High switch radix is key for flattening the data center network to reduce latency, cost, and power consumption [65, 66]. The companies above are offering switches with  $128 \times 128$  to  $576 \times 576$  ports. LightCounting forecasts that OCS sales will increase with a 28% CAGR, reaching over \$500M by 2029 [67].

The current switch products are useful for slow network topology changes with re-

configuration times on the order of several milliseconds; however, this is not ideal for changing workloads. Low latency and better bandwidth utilization can be achieved with faster switching times, using switches based on integrated photonics. While these switches offer faster switching times on the order of 10  $\mu$ s for thermo-optic switches to 10 ns for electro-optics switches, there are significant challenges with achieving low loss and high port count with demonstrations typically exhibiting >10 dB of loss and port count below  $32 \times 32$  [66]. Larger port counts with lower loss are possible with low loss materials like thin film lithium niobate [68]. More development is needed before integrated photonics switches are ready to compete with existing free space optical switches.

In all cases, some insertion loss is inevitable, and link budgets are highly constrained for data center applications. Google was forced to implement new DSP and FEC techniques to overcome the additional losses [63]. Coherent links provide an advantage compared to IMDD with higher receiver sensitivity which enables much larger link budgets to incorporate optical switching [38]. The transparency of optical switches to modulation format also aids in reducing the barrier to implementing coherent transceivers. While DSP requirements remain a barrier for coherent to enter into intra-data center markets, there are efforts to simplify the coherent architecture for reduced DSP [69, 70] and improve the efficiency of coherent DSP [71]. In Section 6.2, I will also show a coherent link demonstration using low speed analog optical signal processing with commercial PAM4 DSP, showing that coherent communications can be implemented with minimal changes to existing protocols while unlocking larger link budgets for optical switching.

### **1.3** Preview of Dissertation

With an understanding of the benefits that coherent links can provide to address data center scaling challenges, this dissertation will discuss the different material platforms and component design details which comprise the overall PIC design in Chapter 2. My work on a single polarization coherent receiver, designed for analog coherent with an OPLL, using an InP offset quantum well (QW) platform will be discussed in Chapter 3. Building on knowledge from the first InP receiver fabrication, Chapter 4 will provide an overview of a second generation InP receiver and lessons learned from the process. To examine the capabilities of silicon photonics platforms for coherent transceivers, Chapter 5 will review O-band integrated lasers and coherent receivers fabricated by Intel's platform and a coherent receiver made using GlobalFoundries 45SPCLO (Fotonix). The receiver PICs will be tested in short reach links to demonstrate their performance in Chapter 6. The dissertation will conclude with an outlook on coherent for data centers and future work.

# Chapter 2

# PIC Design for Coherent Communication

As discussed in Section 1.1, InP was used for fabricating the first coherent TX and RX PICs. While InP is still the platform of choice for long-haul coherent communication, silicon on insulator (SOI) and thin film lithium niobate (TFLN) on silicon platforms also offer good performance and manufacturability at high volume. This chapter provides an overview of coherent optical communications in Section 2.1, provides a comparison of material platforms to understand their benefits and limitations for coherent transmitter and receiver PICs in Section 2.2, and discusses the design details for the main photonic components in Section 2.3.

# 2.1 Basics of Coherent Optical Communications

Electromagnetic fields have multiple properties - amplitude, phase, frequency, and polarization. For optical communications, data is encoded onto the amplitude and phase of the electric field. To maintain a constant frequency, a continuous wave (CW) laser is used as the source of the field. IMDD only uses the amplitude of the field while coherent modulation uses amplitude and phase. The electric field can be expressed as shown in Eqn. 2.1.

$$E_{sig} = E_0(t)e^{(i\omega_{sig}t + \theta_{sig})} \tag{2.1}$$

To modulate the amplitude and phase of  $E_{sig}$ , a nested MZM structure is typically used with a static 90° phase shift between the two MZMs, leading to in-phase and quadrature channels which form the overall IQ modulator (IQM). For PIC based IQMs, TE polarization is maintained on chip, but dual polarization (DP) data output can be achieved by integrating a polarization beam rotator and combiner (PBC) right before the output of the TX with a corresponding polarization beam splitter (PBS) at the RX input. When the signal fields pass through the optical fiber, imperfections in the fiber geometry and material properties lead to rotation of the the polarization state. To correctly recover the transmitted data, corrections must be applied either to the optical signal, using a polarization controller (PC), or to the electrical signal from the photodetectors, using PC digital signal processing (DSP) algorithms. At the receiver,  $E_{sig}$  must interfere with another electric field to demodulate the data encoded in the phase. This is required because the photodetectors which are used to convert the optical signal back to an electrical signal are only sensitive, with a responsivity  $R_{PD}$  in A/W, to the power of the field, given by  $|E^2|$ . The interfering field is provided by a second laser (often called a local oscillator) or by a parallel reference path from the original TX laser. To transform the phase modulation into amplitude modulation, a 90° optical hybrid structure is used for each polarization. The structure has inputs for the signal and reference, and it has 4 outputs (2 differential pairs) for the I and Q data [72]. Each output port has a sinusoidal transmission which depends on the relative phase between the signal and reference fields. The sinusoidal output port transmission curves are each shifted by a multiple of 90°, giving the hybrid its name. The balance in power between the differential pairs and the accuracy of the phase dependent transmission are key to recovering the transmitted data. More details on the 90° hybrid will be discussed in Section 2.3.3. In the ideal case, the output fields are expressed as shown in Eqn. 2.2 - 2.5, where the differential I and Q output pairs are  $E_{out1}$ ,  $E_{out2}$  and  $E_{out3}$ ,  $E_{out4}$ .

$$E_{out1} = \frac{1}{2}(E_{sig} + E_{ref})$$

(2.2)

$$E_{out2} = \frac{1}{2}(E_{sig} - E_{ref})$$

(2.3)

$$E_{out3} = \frac{1}{2}(E_{sig} + iE_{ref})$$

(2.4)

$$E_{out4} = \frac{1}{2} (E_{sig} - iE_{ref})$$

(2.5)

The photocurrent which is digitally processed to recover the data depends on the power of the fields. For a more sensitive receiver, the power of the reference field can be increased, boosting the photocurrent after the signal and reference interfere in the 90° hybrid. The photocurrent from the I and Q pairs are given by Eqn. 2.6 - 2.8, which show that the current scales with the square root of reference power  $P_{ref}$  times the signal power  $P_{sig}$ . This is another advantage of coherent modulation over IMDD.

$$I_I(t) = I_{out1}(t) - I_{out2}(t) = R_{PD}\sqrt{P_{sig}P_{ref}}\cos(\theta_{sig}(t) - \theta_{ref}(t))$$

(2.6)

$$I_Q(t) = I_{out3}(t) - I_{out4}(t) = R_{PD}\sqrt{P_{sig}P_{ref}}sin(\theta_{sig}(t) - \theta_{ref}(t))$$

(2.7)

$$I_{tot}(t) = I_I(t) + iI_Q(t) = R_{PD}\sqrt{P_{sig}P_{ref}}e^{i[\theta_{sig}(t) - \theta_{ref}(t)]}$$

(2.8)

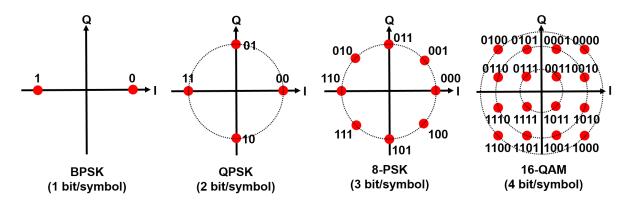

With the ability to modulate the phase and amplitude, a 2D constellation of points can be constructed which decodes the position in IQ space into a sequence of bits. Each position is referred to as a symbol where  $log_2(n)$  of the number of positions determines the number

Figure 2.1: Example constellations are shown for coherent modulation formats with increasing bits/symbol.

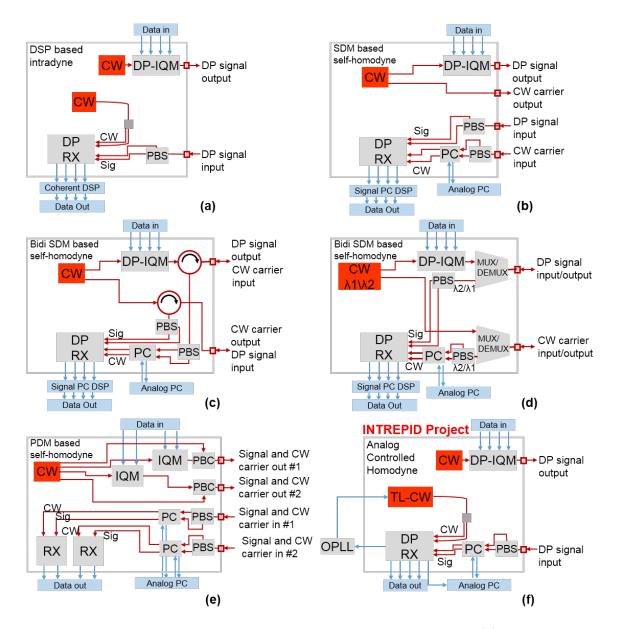

of bits which is encoded in each symbol. Figure 2.1 shows four example constellations – binary, quadrature, 8 phase shift keying (PSK), and 16 quadrature amplitude modulation (QAM). To minimize the probability of bit errors, the encoding typically follows a rule where there is only one bit difference adjacent symbols. All coherent transceivers require a CW laser, IQM, and receiver, but there are multiple different potential architectures. Figure 2.2 shows block diagrams for 6 different architectures with equal total bit rates. Traditionally, a coherent transceiver includes separate TX and RX lasers, as shown in Fig. 2.2(a) which are kept at the same wavelength within a few GHz. To adjust for the frequency offset, compensate for polarization rotation, and recover the phase, a complex set of DSP algorithms are implemented on a custom circuit. This works well for long haul coherent transmission, but it is costly and uses a large amount of power. For shorter reaches, self-homodyne and analog controlled homodyne techniques do not rely on the complex coherent DSP. All self-homodyne approaches use a single source laser for the signal output and the carrier reference output. This removes the need for frequency offset compensation, but polarization and phase recovery are still required. For the approaches where the signal and carrier are on parallel fibers for spatial division multiplexing, as shown in Fig. 2.2(b) - (d), the fiber path lengths must be closely matched to avoid issues

Figure 2.2: Block diagram examples of coherent transceivers using (a) traditional intradyne with DSP, (b) self-homodyne with parallel fiber SDM, (c) circulator based bidirectional SDM self-homodyne, (d) wavelength filter based bidirectional SDM selfhomodyne, (e) analog PC based PDM self-homodyne, and (f) OPLL based homodyne architectures show several approaches for achieving data transmission on 4 lanes.

with phase recovery. Reducing the fiber count helps with packaging cost and reliability, so bidirectional (Bidi) architectures have been proposed using wavelength MUX/DEMUX filters with different transmit and receive wavelengths or using optical circulators. These optical elements add complexity and cost to the transceiver, since they are frequently implemented as micro-optic elements, between the PIC and the fiber output from the module. To avoid fiber induced power fading of the carrier between the two received polarizations, a PC is introduced to maintain a constant power split. The polarization recovery for the signal is still handled via DSP algorithms.

A polarization division multiplexing (PDM) approach enables ideal path length matching for simplified phase recovery, but four fibers are required to acheive the same total bit rate as the other architectures. With PDM, the signal and CW carrier are sent on orthogonal polarizations. An analog PC can be made on the PIC for polarization recovery with low cost and moderate complexity. With this architecture, the use of specialized DSP is eliminated, so it is compatible with systems using standard IMDD transceivers. While the physical implementation of the analog PC is relatively simple, tracking the input polarization when there are disturbances to the fiber and avoiding resets of the PC tuning elements are major design challenges. A prototype version of this architecture will be discussed in Section 6.2.

Using an OPLL, mentioned in Section 1.2, the frequency and phase recovery DSP is replaced by an analog feedback circuit. An analog PC is used for polarization recover of the signal. This has the potential to reduce power consumption, and it also compatible with systems using standard IMDD transceivers. This architecture was the focus of the INTREPID project. It sought to develop novel O-band PICs with tunable lasers (TL) and integrated PC and to make novel EICs for the OPLL. While this architecture provides excellent performance in terms of spectral efficiency, power consumption, and compatibility with IMDD systems, it also presents the largest challenge for integration and analog control. Section 3.1, 4.1, and 5.3 discuss multiple RX PIC designs intended for integration with an OPLL.

These six examples provide an overview of the different design choices and major building blocks for coherent transceivers, but there are numerous other design decisions which determine the performance of the individual building blocks and the overall system. The material platform used for each building block is one of the first major decisions when designing a transceiver module. This will be discussed in more detail in Section 2.2. The overall performance of the transceiver depends on multiple performance metrics from each of the building blocks. High laser power and low linewidth are optimal. Modulators are designed for high extinction ratio (ER), low  $\pi$  phase shift voltage  $(V_{\pi})$ , high optical and electro-optical bandwidth, low insertion loss (IL), and compact size. Coherent receivers must also have high bandwidth, low noise floor, low IL, low phase error, and compact size. The combined performance of all the elements determines the maximum bit rate and the bit error rate (BER) sensitivity to receiver input power and signal to noise ratio (SNR). More details on the laser, modulator, 90°-hybrid, and photodetectors will be discussed in Sections 2.3.1, 2.3.2, 2.3.3, and 2.3.4, respectively. More comprehensive details on the building blocks and different system considerations for coherent optical links can be found in [4, 10, 73, 74, 75, 76], among other books.

## 2.2 Material and Integration Platforms

The first coherent PICs were made using InP, and it remains the primary material platform for long haul coherent PICs. While III-V materials on InP substrates have excellent material properties for both modulation and photodetection, silicon on insulator and thin film lithium niobate (TFLN) offer advantages in scalability and integration. While Coherent Inc. recently expanded to 6 inch InP wafers [77], silicon and TFLN are able to utilize larger 8 to 12 inch Si wafers. With advanced integration techniques, it is possible to combine the advantages of each platform together. Integration of III-V material on silicon has been a major area of research and development for the last decade with continual improvements in different integration techniques. More integration of SiP with InP may happen with Infinera entering the data center market and gaining access to more SiP technology since they were acquired by Nokia [78, 79]. The following sections will provide a comparison of the capabilities and performance of the main material platforms.

### 2.2.1 Indium Phosphide (InP)

InP is the most mature of the optical communications material platforms with decades of research and development from universities and companies, including AOI, Coherent, Infinera, Lumentum, Neophotonics, NTT, Sumitomo, and many others. InP, and related III-V compounds, have a direct bandgap and strong electro-optical effects, making them ideal for lasers, modulators, and detectors. With advancements in metal-organic chemical vapor deposition (MOCVD) and other fabrication processes, there is large amount of flexibility when optimizing the epitaxial layers and PIC process flow. There are several PIC integration platforms with varying design and processing complexity. Offset QW, dual QW, asymmetric twin waveguide, QW intermixing, butt joint growth, and selective area growth are several popular platforms [80, 81]. While this complexity can make designs more challenging, the changes to the epitaxy and process enable integration of active and passive devices with minimal performance penalties.

For data- and telecommunications wavelengths, InP based lasers are a necessity. Monolithic InP has been the dominant platform for O-band and C-band lasers for decades. In the last 10 years, there has been significant development of heterogeneous and hybrid lasers [82, 83, 84, 85, 86]. These still use InP based epitaxial layers for the gain material, but the laser cavity is formed by integrating the epitaxy with an SOI platform. There are multiple methods for achieving this integration which will be discussed in Section 2.3.1.

InP based modulators benefit from the Franz-Keldysh, quantum-confined Stark, and free-carrier absorption effects for the amplitude and phase of input laser light. These effects enable efficient and high speed modulation, but they do not have a linear relationship with driving voltage. These effects lead to chirp and distortions in the transmitted data, with more pronounced effects at higher drive swing [87]. At OFC 2024, NTT presented a >100 GHz InP-based modulator with  $V_p i = 1.5V$  for beyond 200 Gbaud modulation using a specialized n-i-p-n structure and carefully designed capacitively-loaded travelingwave electrodes (CL-TWE) that are 3.6 mm long [88]. This is one of best modulators in any platform in terms of BW and modulation efficiency, with only some novel plasmonic or Si-organic-hybrid modulators having higher bandwidth. While laser and modulator performance on InP is excellent, passives often have higher losses and lower fabrication yield. The material properties of InP typically lead to higher insertion losses compared to Si, and the process control for InP etching is more challenging, leading to more dimensional variation. These challenges have made it difficult to realize fabrication tolerant polarization rotators and splitters on InP with recent research showing some progress [89, 90, 91]. Another major argument against InP is the difficulty with scaling to high volume. While wafer sizes and yield have increased over the years, InP fabrication is still more expensive than Si and not as well equipped to meet the large demand for transceivers to connect AI clusters and data centers. For high volume, integration of InP on Si is the popular solution, but there are several integration methods (hybrid, heterogeneous, monolithic) with trade-offs in fabrication complexity, cost, and integration density [92].

### 2.2.2 Silicon on Insulator (SOI)

Silicon photonics (siP) has matured and expanded rapidly over the past 15 years with manufacturing dominated by foundries (e.g. AIM Photoncis, AMF, CEA-Leti, Cornerstone, Global Foundries, IHP, Imec, SkyWater, Tower, TSMC, etc.) offering silicon photonics processes while a only few other private companies (e.g. Intel, Skorpios) operate their own fabrication facilities. With high development and operating costs, most companies design SiP products while using a foundry for fabrication. The development of SiP modulators began in the late 1980s with the analysis by Soref and Bennett [93] which found that the refractive index could be modulated via the free carrier plasma effect. Initial work to produce low loss passive components and high speed modulators was aided by the existing silicon CMOS ecosystem and the years of Si fabrication development. With continual development in the SiP ecosystem, typical SiP foundry offerings include a variety of passive components, high speed pn modulators, thermal phase tuners, and Ge PDs on 300 mm wafers [94, 95]. Silicon has advantages in wafer size, waveguide loss, component density, production cost, and integration with CMOS electronics. Si nitride (SiN) waveguides are also offered by several foundries, providing even lower losses compared to standard SOI [96, 97]. As mentioned previously, the primary gap in silicon photonics is the lack of integrated gain. This is an active area of development with heterogeneous integration demonstrated by Intel, Tower, and Nexus Photonics, and Skorpios [98, 99, 100, 101]. Other laser integration methods are also in development and will be discussed more in Section 2.3.1. Relative to InP, modulation efficiency and bandwidth are also lower for pn junction based Si modulators, but this deficiency can also be resolved with heterogeneous integration [102, 103]. Advanced modulators using III-V EAMs [104, 57], Si-organic hybrid (SOH) [105], barium titanate (BTO) [106], lithium tantalate (LTO) [107], plasmonic-organic-hybrid (POH) [108], and thin film lithium niobate (TFLN) [109] have all been demonstrated. Table 2.2.4 provides a performance comparison between the different modulator materials. Of the multiple modulator materials, TFLN on SOI is the most mature.

#### 2.2.3 Thin Film Lithium Niobate (TFLN)

Bulk lithium niobate has been a high performance modulation material for decades, but TFLN modulators using a lithium niobate on insulator (LNOI) platform have only been developing over the last decade. Several companies - including Hyperlight, Fujitsu, Liobate, and Eoptolink - have been refining the fabrication and design of TFLN modulators. Lithium niobate is an advantageous modulator material because it has low loss, high bandwidth, and linear modulation via the Pockel's effect. Using Si 6" to 8" substrates, TFLN also benefits from large volume manufacturing. Modulators with >100 GHz BW have been demonstrated by multiple groups and companies [31, 110]. For integration density, TFLN not the best material because it has a lower modulation efficiency compared to InP, leading to longer modulator lengths. New designs have been proposed to improve the modulation efficiency using thick co-planar waveguide electrodes [111]. Continued development has been reducing fabrication difficulties, but there are material quality and etching challenges where more reliability and yield data is still needed. The TFLN platform also lacks lasers and photodiodes, but there have been successful research demonstrations of heterogeneous III-V wafer bonding to add these elements [112, 113].

#### 2.2.4 Modulator and Photodetector Comparison

Competition between platforms for share of the booming data center and AI market will continue to drive innovation in modulator and photodetector designs. Unless pure InP modulator costs can match the next generation of SiP, it is likely that Si MZMs will continue to grow in popularity. In the next 5 to 10 years, foundries and transceiver vendors may introduce products using novel modulator materials on SOI to keep up with the BW scaling. Table 2.2.4 provides a comparison between pure InP, pure SOI, and heterogeneous modulators. The table covers several designs and materials, but there are many other designs not included. For photodetectors, InGaAs on InP and Ge on Si have both demonstrated excellent performance. Since Ge on Si PDs have gained maturity on SiP, there is not a major incentive for foundries that already use Ge to develop integration processes for high speed InGaAs PDs on Si, but micro-transfer printing them to a low loss passive platform is being explored by Ligentec [114, 115]. In addition to Table 2.2.4, BW vs responsivity comparisons of III-V PDs can be found in [116, 117]. A tabular comparison of several metrics for WG PDs can be found in [118, 119, 120].

## 2.3 Photonic Component Design

As discussed in Section 2.1, the laser, modulator, 90°-hybrid, and photodiodes are the main components that are critical to the overall design of PICs for coherent communications. This section will cover the design considerations for each of these components.

#### 2.3.1 Integrated Laser

The advantages of miniaturization, improved optical coupling, higher manufacturing volume, and electronic control provide the foundation for the development of integrated lasers, and the diverse set of applications powered by these lasers (e.g. transceivers, LIDAR, quantum computing, chemical sensing, optical coherence tomography, etc.) has driven their continued growth and advancement.

The first integrated lasers were made with a monolithic integration platform where the laser and PIC were fabricated on the same wafer. Initially, the wafer material platforms

| Material/<br>Platform | Design       | $\lambda$ (nm) | 3,6 dB<br>EO BW<br>(GHz) | $V_{pi}$ (V) | $\begin{array}{c} V_{pi}L\\ (\text{V-cm}) \end{array}$ | ER<br>(dB) | Length<br>(mm) | Ref.  |

|-----------------------|--------------|----------------|--------------------------|--------------|--------------------------------------------------------|------------|----------------|-------|

| InP                   | CL-<br>TWMZM | C-band         | >67, -                   | 1.5          | 0.54                                                   | >10        | 3.6            | [121] |

| InP                   | CL-<br>TWMZM | C-band         | >100, 110                | 1.5          | 0.54                                                   | >25        | 3.6            | [88]  |

| InP                   | TWMZM        | C-band         | 54, > 65                 | 2            | 0.55                                                   | 25         | 4              | [122] |

| InP                   | TWMZM        | C-band         | 110, -                   | 3.4          | $0.7{\pm}0.4$                                          | 15.3       | 1              | [123] |

| InP                   | EAM          | O-band         | 85,  90                  | —            | _                                                      | 3          | 0.075          | [124] |

| InP                   | TWEAM        | C-band         | >100, -                  | —            | _                                                      | >20        | 0.18           | [125] |

| SOI                   | TWMZM        | C-band         | 44, 62                   | 8            | 1.6                                                    | >25        | 2              | [126] |

| SOI                   | CL-<br>TWMZM | C-band         | 61, 78                   | 8            | 3.2                                                    | _          | 4              | [127] |

| SOI                   | MRM          | O-band         | 77, 81                   | $<\!\!1.5$   | 0.5                                                    | 3.8        | 0.012          | [128] |

| SOI                   | slow-light   | $1550 \pm 4$   | 110, >120                | $78^{1}$     | 0.96                                                   | 3          | 0.124          | [129] |

| InP/SOI               | EAM          | O-band         | 60,67                    | _            | _                                                      | —          | —              | [57]  |

| Ge/SOI                | EAM          | L-band         | 100, >110                | —            | —                                                      | 2.3        | 0.02           | [130] |

| SOH/SOI               | MZM          | O-band         | 100, -                   | 0.92         | 0.046                                                  | 20         | 0.5            | [105] |

| BTO/SiN               | MZM          | C-band         | 110, -                   | 6.4          | 0.0096                                                 | 13.3       | 0.015          | [106] |

| LTO/SOI               | TWMZM        | C-band         | 110, -                   | 4.8          | 2.88                                                   | _          | 6              | [107] |

| POH/SOI               | MRTM         | C-band         | 176, -                   | 1.67         | 0.015                                                  | 12         | 0.028          | [108] |

| TFLN/SOI              | TWMZM        | O-band         | 70, >100                 | 1.7          | 3.06                                                   | 20         | 18             | [109] |

| TFLN/SOI              | TWMZM        | C-band         | 110, >125                | 1            | 2.3                                                    | 35         | 23             | [131] |

| TFLN/SOI              |              | O-band         | 110, >125                | 4.37         | 2.36                                                   |            | 5.4            | [110] |

| TFLN/SOI              | TWMZM        | C-band         | 110, >125                | 5.78         | 3.12                                                   |            | 5.4            | [110] |

Table 2.1: Modulator performance comparison

<sup>1</sup> slow-light phase efficiency is very nonlinear

EAM: electro-absorption mod., CL-TW: capacitively-loaded traveling-wave MRM: micro-ring mod., SOH: Si-organic hybrid, BTO: barium titanate LTO: lithium tantalate, POH: plasmonic-organic-hybrid, RTM: racetrack mod.

| Material/  | Dogign | $R_{ext}$       | λ      | OE BW | I <sub>dark</sub> | RF $P_{sat}$ | Ref.  |

|------------|--------|-----------------|--------|-------|-------------------|--------------|-------|

| Platform   | Design | (A/W)           | (nm)   | (GHz) | (nA)              | (dBm)        | nei.  |

| InGaAs/InP | PIN    | 0.5             | C-band | 120   | _                 | _            | [132] |

| InGaAs/InP | PIN    | 0.4             | C-band | 145   | <40               | -10          | [133] |

| InGaAs/InP | MUTC   | 0.5             | C-band | 119   | 1.5               | -1.2         | [118] |

| InGaAs/InP | MUTC   | 0.31            | C-band | 165   | < 0.1             | -1.7         | [116] |

| InGaAs/InP | MUTC   | 0.24            | C-band | 220   | < 0.1             | -1.8         | [116] |

| Ge/Si      | PIN    | $0.78 - 1.05^*$ | C-band | 67    | < 6.4             | _            | [134] |

| Ge/Si      | PIN    | $0.74^{*}$      | 1550   | 67    | <4                | _            | [135] |

| Ge/Si      | PIN    | $0.89^{*}$      | C-band | 80    | <10               | _            | [136] |

| Ge/Si      | PIN    | $0.95^{*}$      | 1550   | 103   | <7                | _            | [137] |

| Ge/Si      | PIN    | 0.2             | C-band | 240   | <100              |              | [119] |

Table 2.2: Photodetector performance comparison

$R_{int}$  vs  $R_{ext}$  not made clear

were limited to the direct bandgap semiconductors (e.g. GaAs, InP, InGaAsP, InAlGaAs, InP) which are required for laser gain. Innovations in fabrication and packaging have led to new integration techniques which can be grouped into hybrid, heterogeneous, and monolithic methods.

Hybrid integration involves packaging a complete laser gain chip with an separate PIC through flip-chip bonding, butt-joint edge coupling, or photonic wire bonding [138, 139, 85]. With flip chip-bonding, devices can be screened before integration to increase yield. The bonding process uses solder bumps to connect a completed III-V device, such as a InP based laser or photodetector, to a separate substrate with metalized pads. While this is a mature process, it is still challenging to achieve low (<2 dB) coupling loss, and it is less flexible with the size and arrange of the chips compared to other integration methods. While the self-alignment of the solder bumps via surface tension, aids in optical alignment, mechanical stops are required for required for reliable low coupling loss, adding complexity to the packaging. The optical coupling with flip-chip bonding may use butt coupling, grating coupling, or a 45° etched mirror [85]. While the position accuracy requirements for grating and mirror coupling are lower due to the larger beam diameter, the best case coupling losses are also higher, and grating couplers limit the spectral bandwidth. Other designs may use butt coupling without flip chip bonding by precisely aligning the waveguides at the edges of the chips. In all cases, it is important to design the mode size and shape to closely match between the two chips for optimal coupling, which often requires the use of spot size converters. Photonic wire bonding may be used to act as a spot size converter and to remove the precise alignment requirements for optical coupling. A 3D polymer waveguide is aligned to both chips and written lithographically, resulting in low coupling loss. This method is advantageous for relaxing chip placement tolerances, but the relatively long write times for the polymer waveguides make it less suitable for high volume applications.

Heterogeneous integration involves bonding two separate wafers (or smaller dies to wafers) together and completing the fabrication process to define the active and passive devices together on the bonded wafers. With this method, only moderate precision is required for placement before bonding, and precise waveguide alignment is achieved using lithographic pattern alignment and etching on the bonded wafers. With evanescent coupling tapers, low losses can be achieved; passive devices can be more flexibly routed in the bonding area; and a large number of active devices can be defined simultaneously during the post-bond fabrication steps. To maintain a strong bond, the surface preparation and interface material properties are critical. Heterogeneous integration began by using thin polymer layers for their tolerance imperfections in surface preparation, temperature stability, chemical resistance, and low cost [139]. The low thermal conductivity of polymers hinders active device performance, which motivated the development of direct bonding. Though more stringent surface preparation and flatness are required for a reliable bond, direct bonding utilizes the intermolecular forces between two pristine surfaces for integration without an interfacial adhesion layer. This process-which involves plasma surface treatment followed by compression bonding, and high temperature annealing-was pioneered by the Bower's group at UCSB [82]. While mechanical strain and thermal expansion are concerns, a variety of III-V materials have been successfully bonded, and the process has been commercialized by Intel, resulting in highly reliable lasers which can be manufactured at high volume [83, 140, 98].

Micro-transfer printing (MTP) shares characteristics with hybrid and heterogeneous integration. In many demonstrations, completed devices from one substrate are bonded to another with precise alignment required, similar to hybrid integration. It is possible to transfer partial devices and to continue processing after transfer printing, similar to heterogeneous integration. The transfer printing process uses a elastomeric stamp, typically PolyDiMethylSiloxane (PDMS), to adhere to a membrane device on a donor substrate and break thin tethers to lift it away. The stamp is positioned precisely over the receiving substrate and the device is carefully pressed into place. More details regarding the design of the donor membrane device and the transfer printing process can be found in [138, 85, 141, 142]. This technique provides flexibility in PIC design since small devices can be placed individually, and multiple donor substrates with different materials can be integrated together on one receiving substrate. Less material is wasted in the transfer process since, unlike heterogeneous wafer bonding, a substrate removal is not required, which leads to material cost savings. While the process has been commercialized successfully by X-Celeprint for micro-LEDs, photovoltaic cells, and other semiconductor devices, more process development is needed to enable high volume production of integrated lasers using micro-transfer printed III-V material. Recent laser demonstrations have shown good progress, but achieving low loss coupling for high laser power remains a challenge [143, 144, 145]. For companies already utilizing heterogeneous wafer bonding, switching to MTP for bonding blank membrane coupons rather than larger wafer chips may enable material cost savings with only small changes to existing processes.

Monolithic integration (or direct epitaxial growth) on silicon offers excellent scalabil-

ity, low cost, and dense integration by directly growing the laser gain material on large silicon wafers. This approach faces several technical challenges to achieve high quality III-V material due to the mismatch between the lattice constant, thermal expansion coefficient, and polarity of III-V materials compared to silicon. These differences can create threading and misfit dislocations, antiphase boundaries, and thermal cracking [146]. Techniques using offset cut Si substrates, buffer layers [147, 148], defect trapping and filter layers, v-groove patterned substrates [149], GaP-on-Si templates [150, 151], and lateral aspect ratio trapping growth have all been investigated as methods of reducing defect generation and propagation [138, 139, 146]. Much of the work on direct epitaxial growth has focused on quantum dot (QD) active material because its increased tolerance to defects, and its improved performance compared to quantum well material from its delta function density of states. While the methods above have been successfully employed, with many research demonstrations of high power QD lasers grown on Si, low loss coupling to Si or SiN waveguides remains a challenge. Most solutions are incompatible with the evanescent coupling currently used in heterogeneous wafer bonded lasers, and but coupling losses need to be improved [148, 150, 152]. For high volume production of cleaved or etched facet lasers on large Si wafers, direct epitaxial growth has clear advantages and commercialization seems feasible in the near future. Integration of directly grown III-V elements into more complex PICs will require more development, but current research work shows promise.

Shifting back to the basics of laser design, regardless of the integration technology, all diode laser designs follow the same principles for calculating device performance. The primary equations governing the laser design are as follows [153]–

$$R = r_1 r_2 \tag{2.9}$$

Lasers need mirrors to form a cavity where in Eqn. 2.9, R is the mean mirror reflection coefficient and  $r_1 \& r_2$  are the field reflection coefficients of mirrors 1 & 2.

$$\alpha_m = \frac{1}{L} ln\left(\frac{1}{R}\right) \tag{2.10}$$

In Eqn. 2.10,  $\alpha_{\rm m}$  is the mirror loss which is defined per unit length based on the total cavity length, L.

$$\Gamma g = \langle \alpha_i \rangle + \alpha_m = \frac{1}{v_q \tau_p} \tag{2.11}$$

In steady state, Eqn. 2.11 shows the laser gain is equal to the loss where  $\Gamma$  is the confinement factor, g is the modal gain,  $\langle \alpha_i \rangle$  is the average internal loss,  $v_g$  is photon group velocity, and  $\tau_p$  is the photon lifetime.

$$\eta_d = \frac{\eta_i \alpha_m}{\langle \alpha_i \rangle + \alpha_m} \tag{2.12}$$

The laser differential efficiency  $\eta_d$  is calculated using Eqn. 2.12 where the carrier injection efficiency  $\eta_i$  is multiplied by the mirror loss divided by the total loss.

$$N_{th} = N_{tr} e^{(\langle \alpha_i \rangle + \alpha_m) / \Gamma g_{0N}} \tag{2.13}$$

As shown in Eqn. 2.13, there is an exponential relationship between  $N_{th}$  and  $N_{tr}$ , the threshold and transparency carrier densities, where  $g_{0N}$  is the gain coefficient.

$$P_0 = \eta_d \frac{h\nu}{q} (I - I_{th})$$

(2.14)

Above the threshold current  $I_{th}$ , neglecting nonlinear effects, the laser optical output power  $P_0$ , is linearly related to the electrical current I by the differential efficiency and the photon energy  $h\nu$  generated per electron charge q that recombines, where h is Planck's constant and  $\nu$  is the laser frequency in Eqn. 2.14.

$$MSR = \frac{F_1(\lambda_0)\alpha_m(\lambda_0)[\alpha_i + \alpha_m(\lambda_1) - \Gamma g(\lambda_1)]}{F_1(\lambda_1)\alpha_m(\lambda_1)[\alpha_i + \alpha_m(\lambda_0) - \Gamma g(\lambda_0)]}$$

(2.15)

For single mode lasers, the mode suppression ratio (MSR) is defined by 2.15 where  $\lambda_1$ and  $\lambda_0$  are the wavelengths of the two competing modes and  $F_1$  is the fraction power emitted from one side of the laser. Competing modes are often adjacent cavity modes spaced apart by  $\Delta \lambda_{mode}$  based on the cavity length L and the optical group index  $\overline{n_g}$ using Eqn. 2.16.

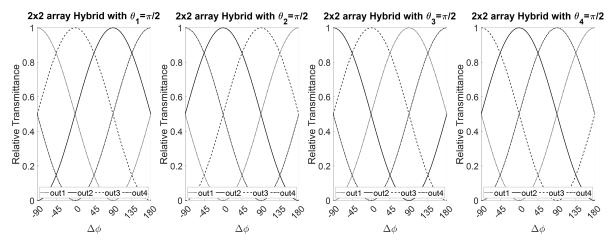

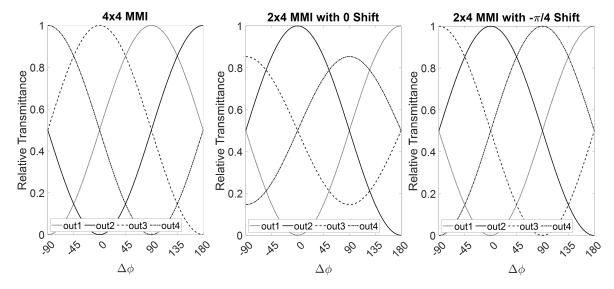

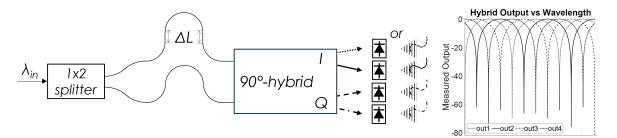

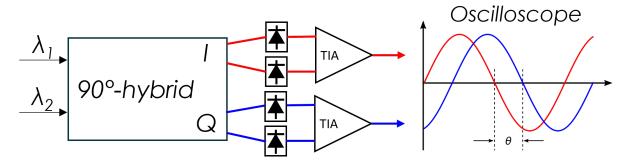

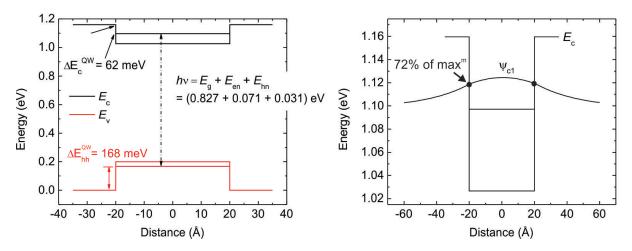

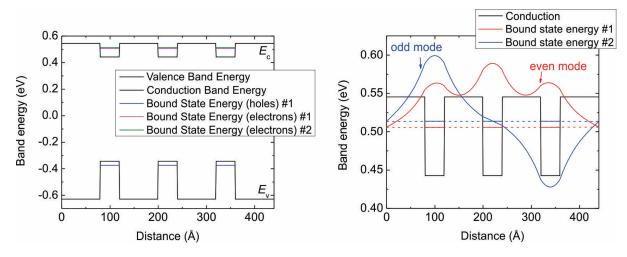

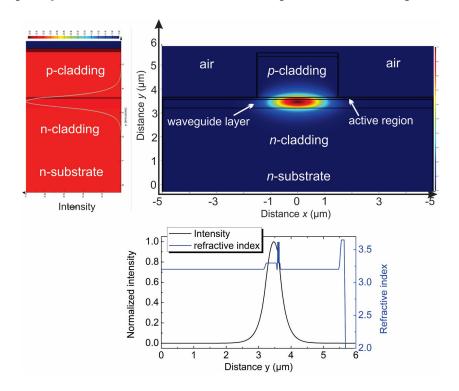

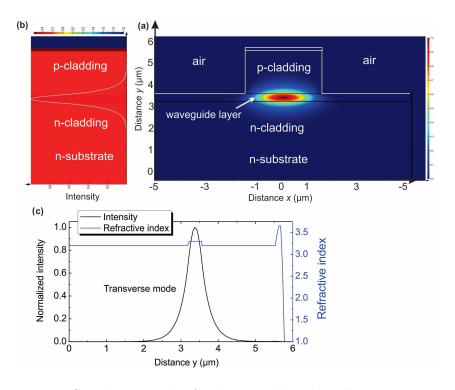

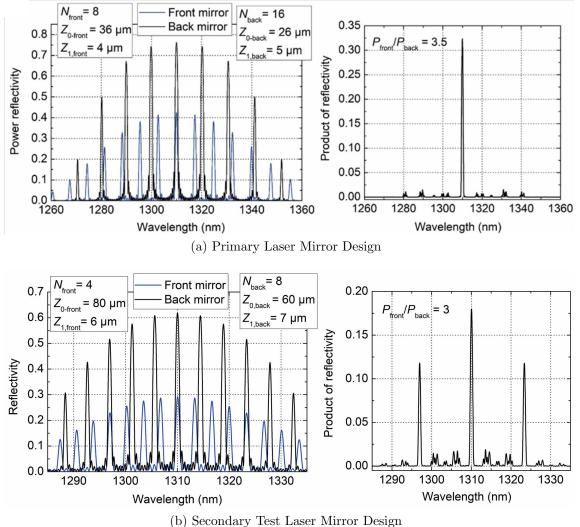

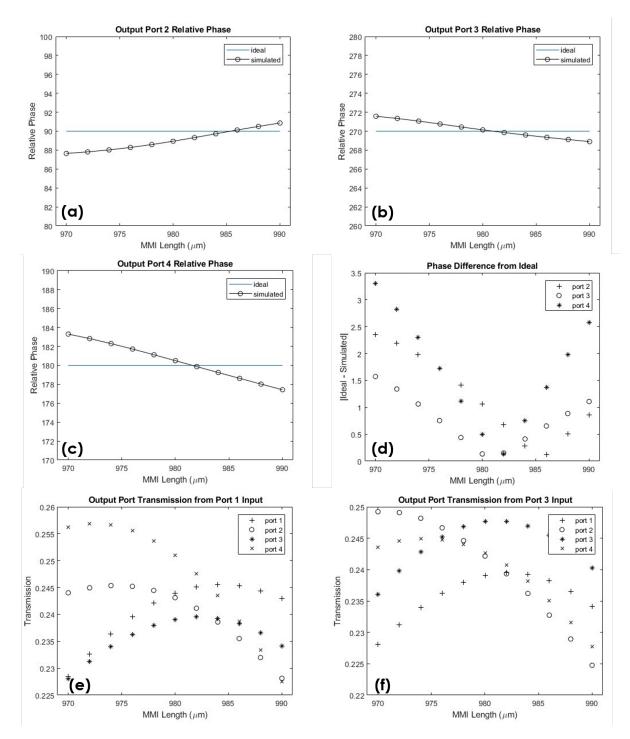

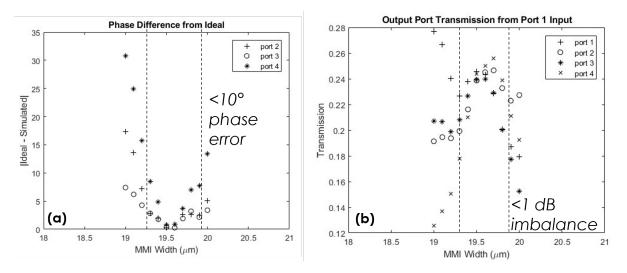

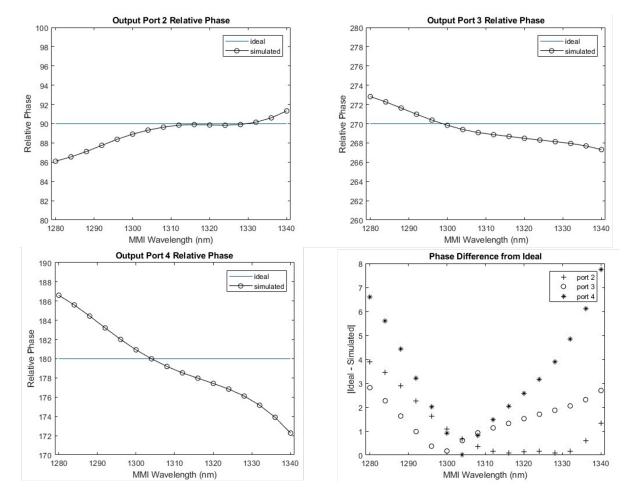

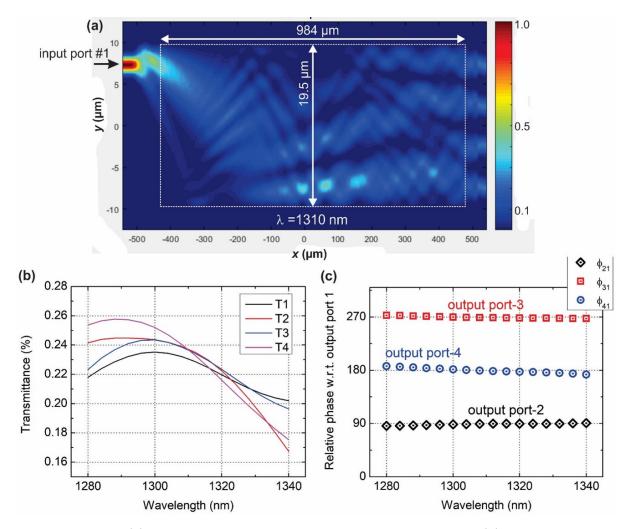

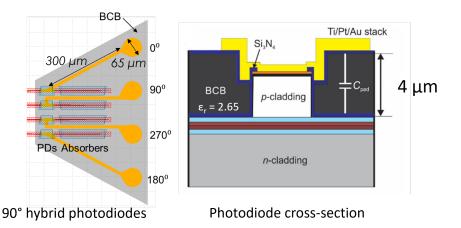

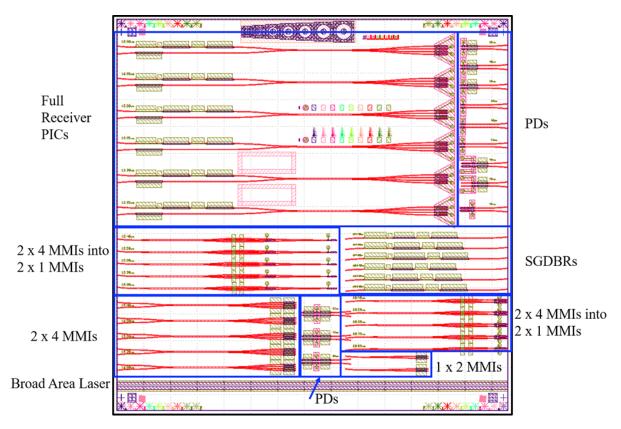

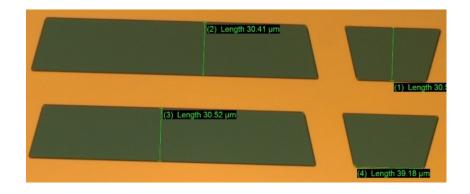

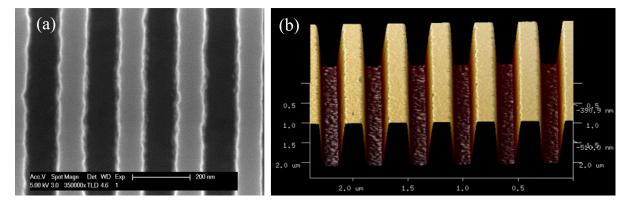

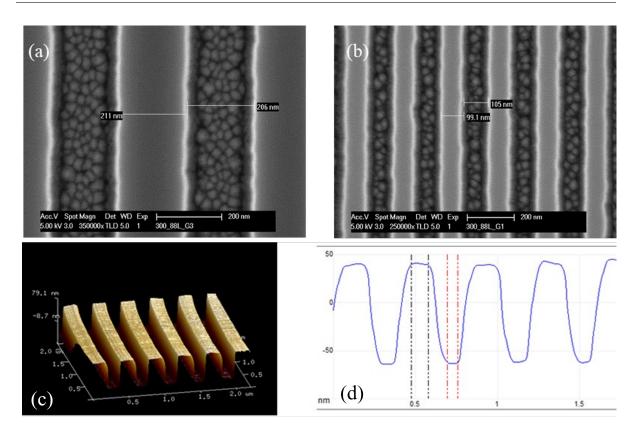

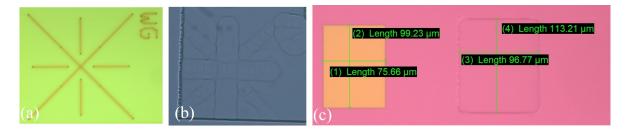

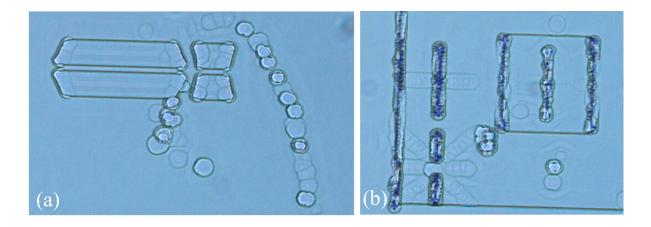

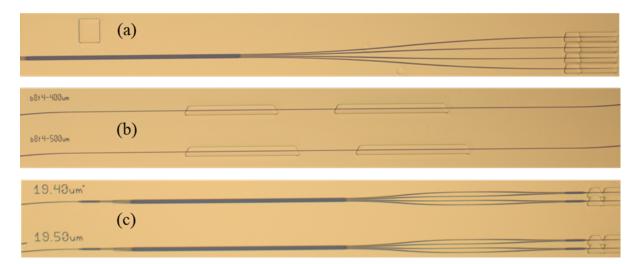

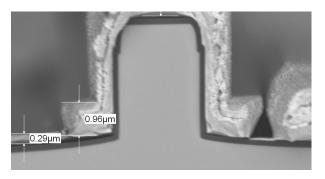

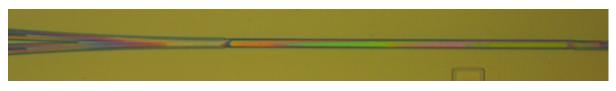

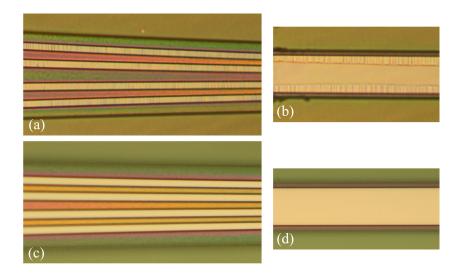

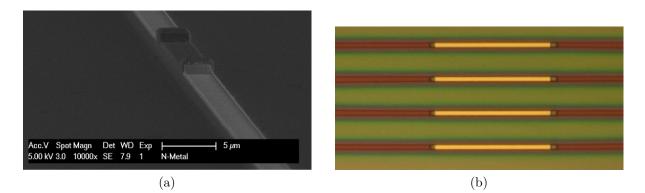

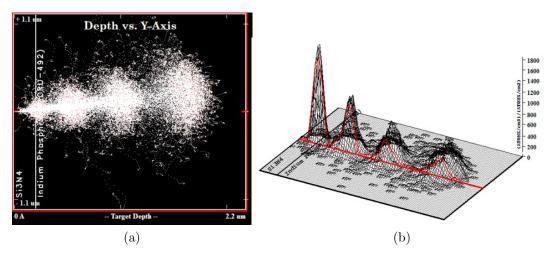

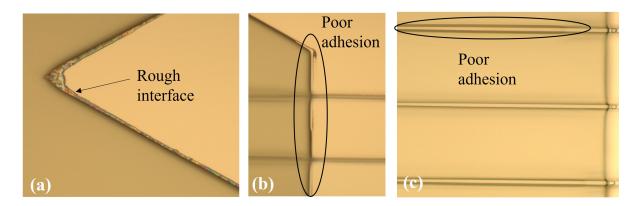

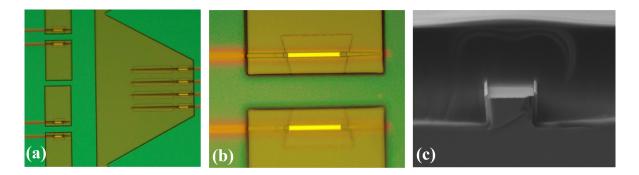

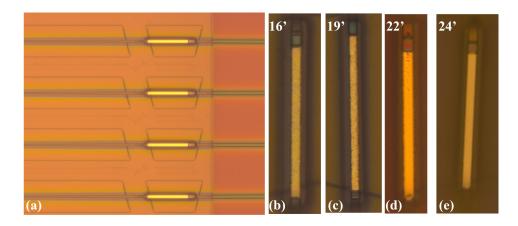

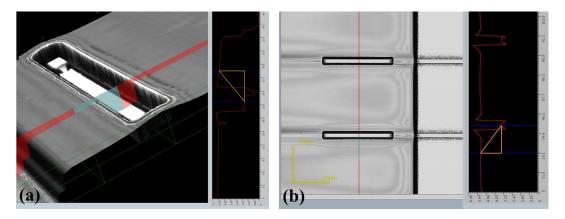

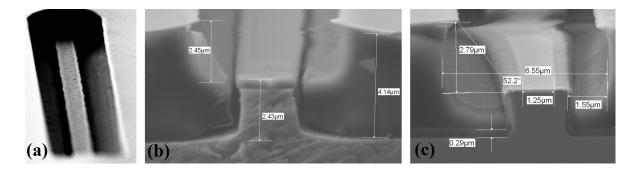

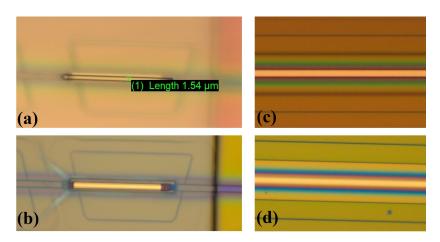

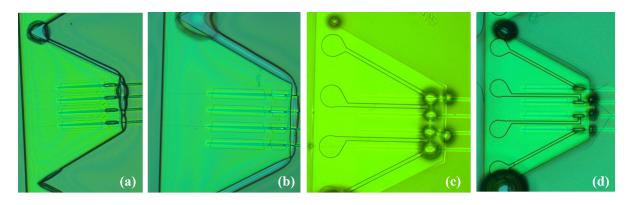

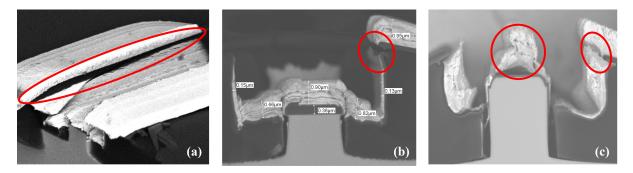

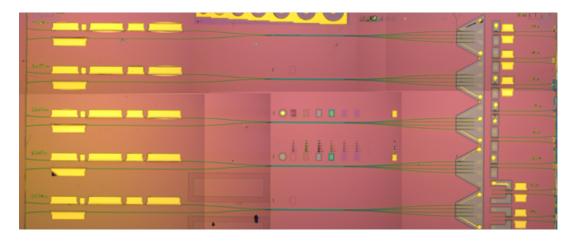

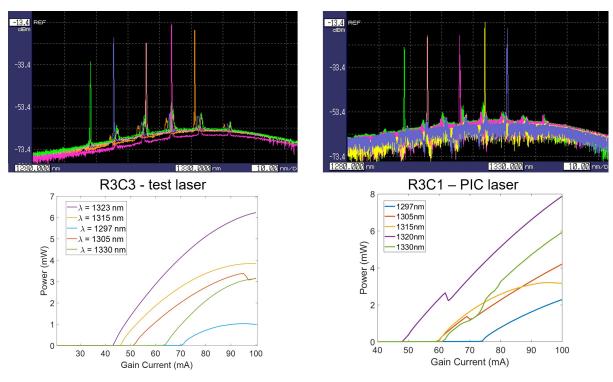

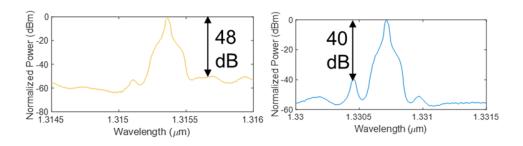

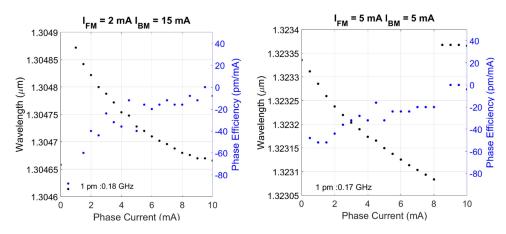

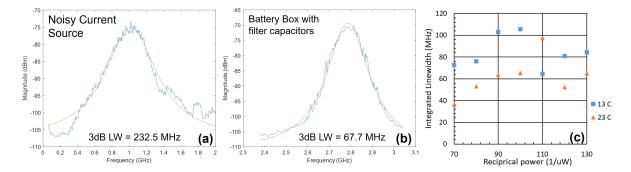

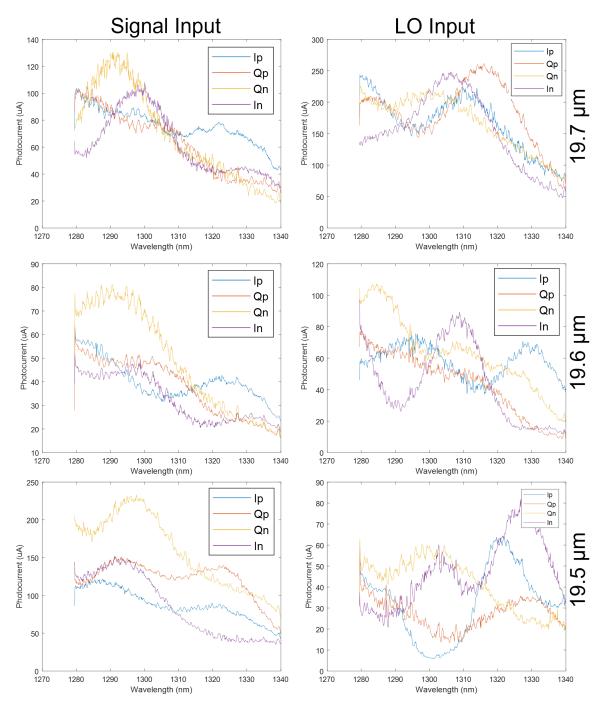

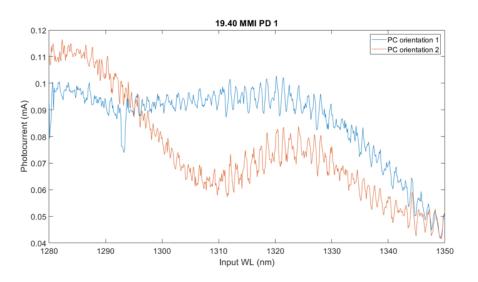

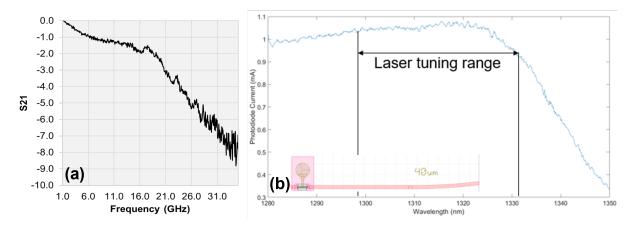

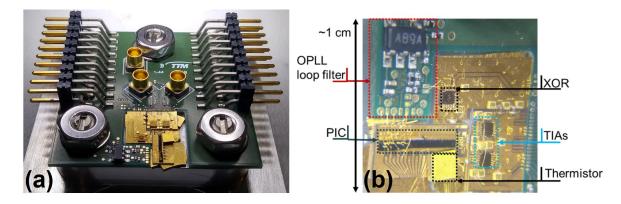

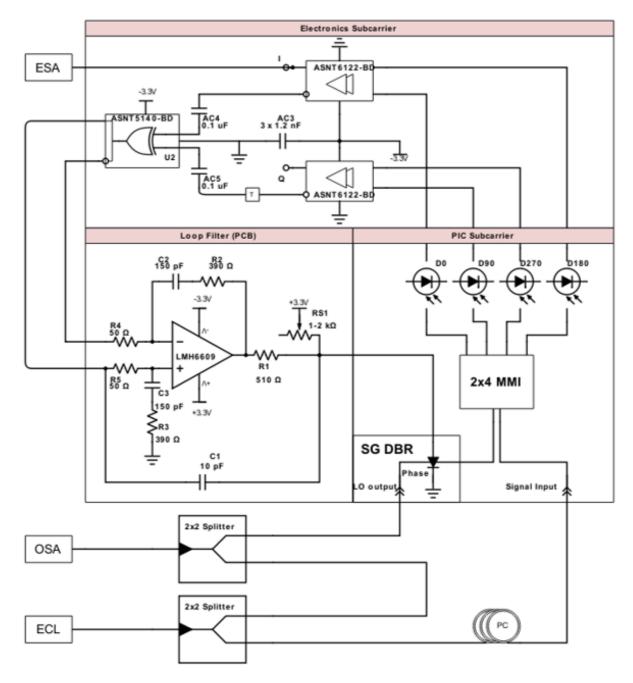

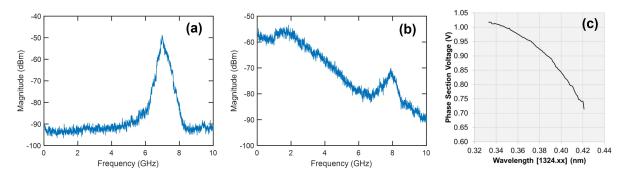

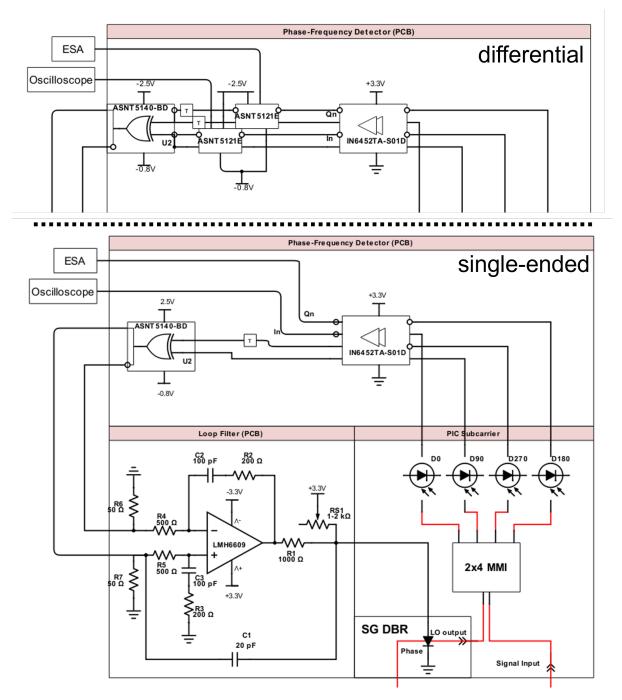

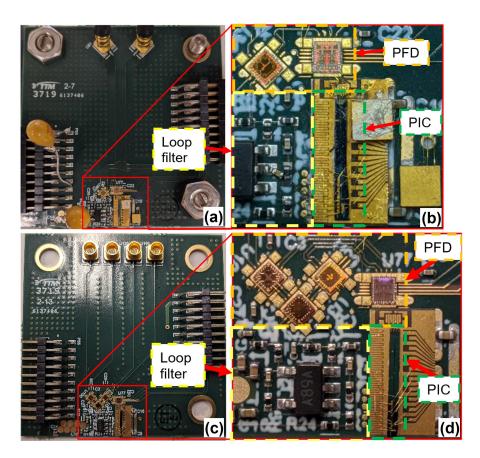

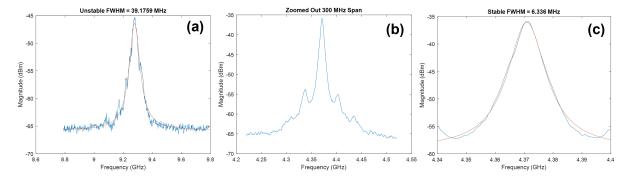

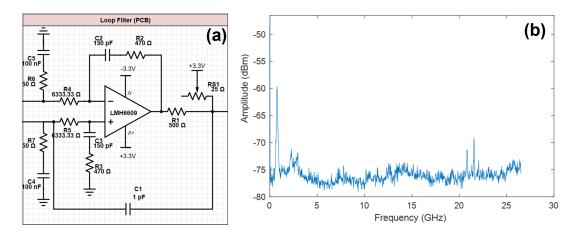

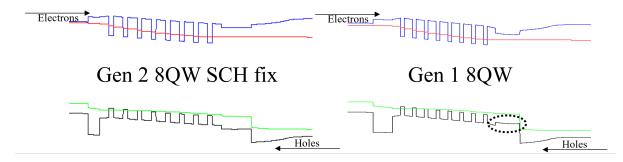

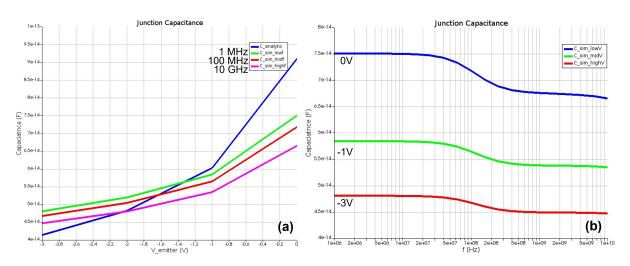

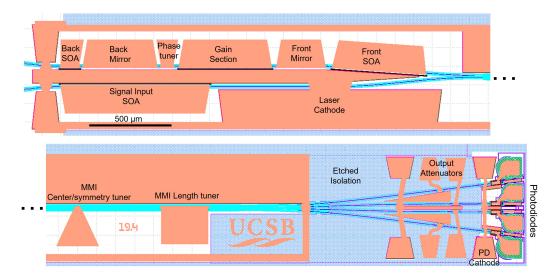

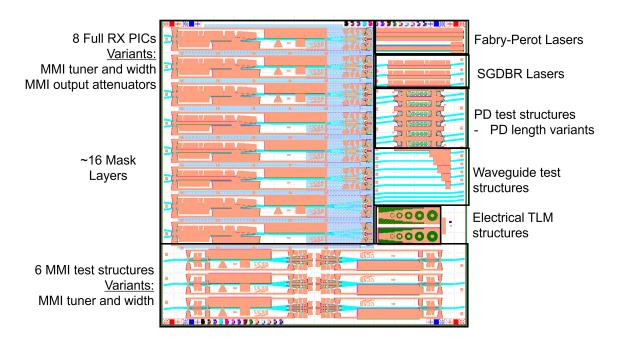

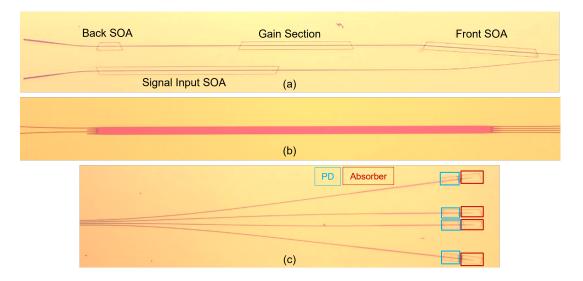

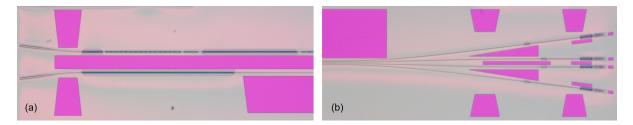

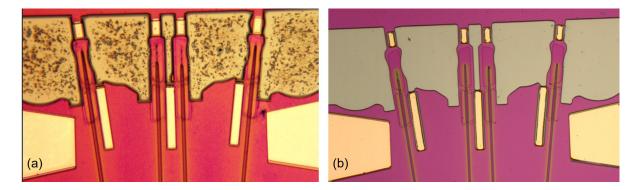

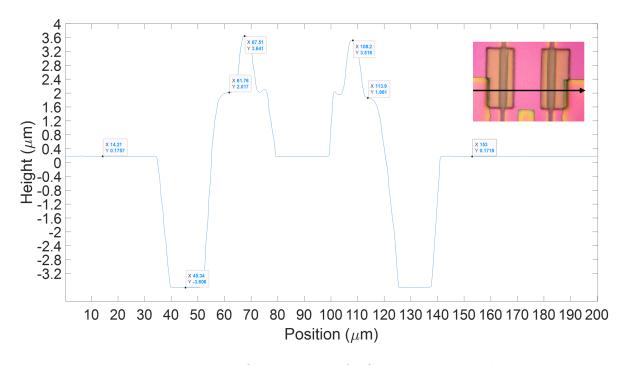

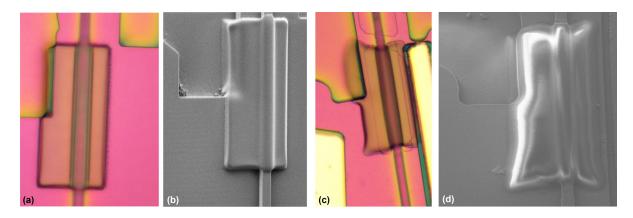

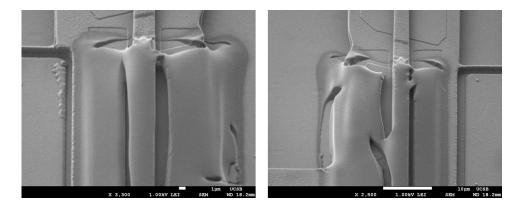

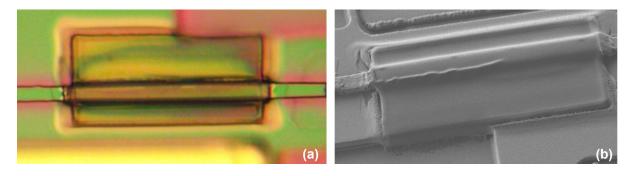

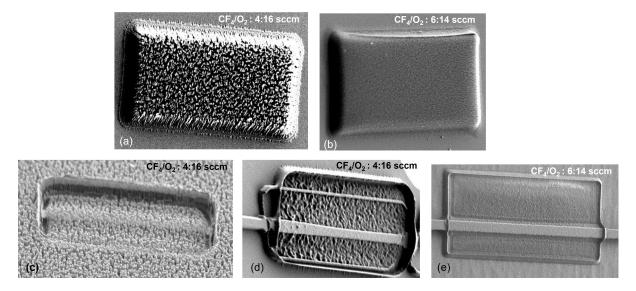

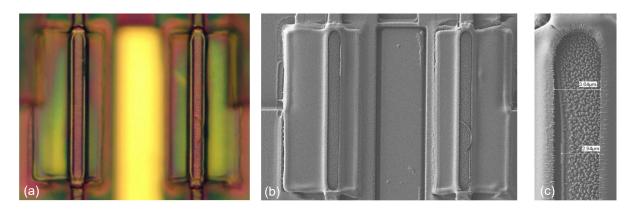

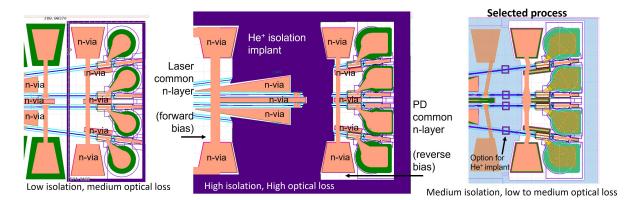

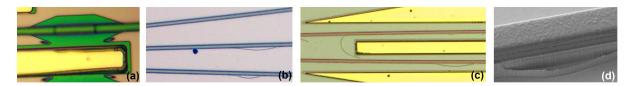

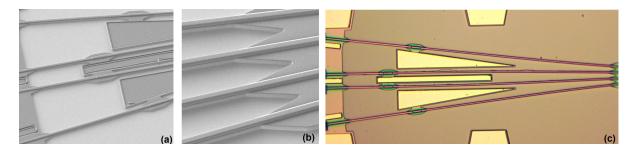

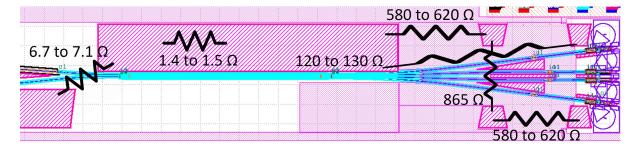

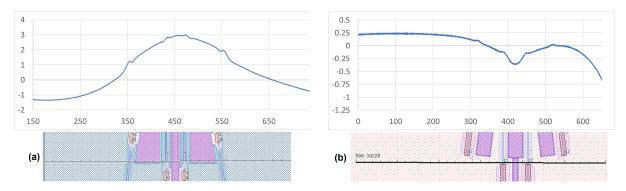

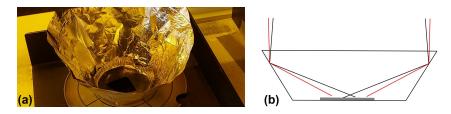

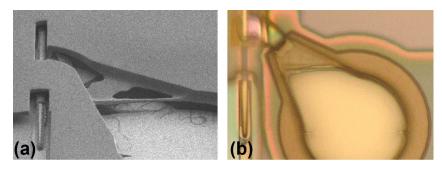

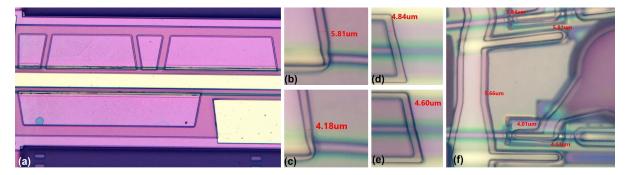

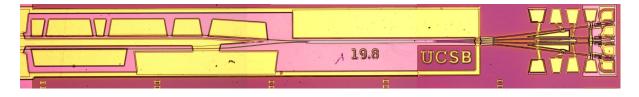

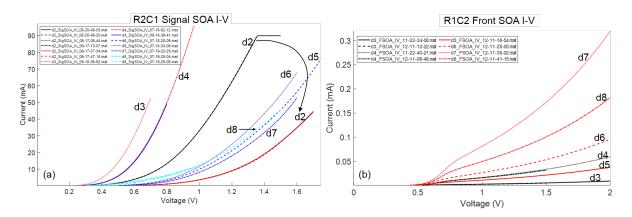

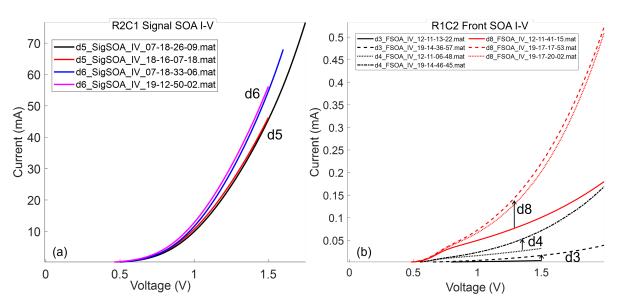

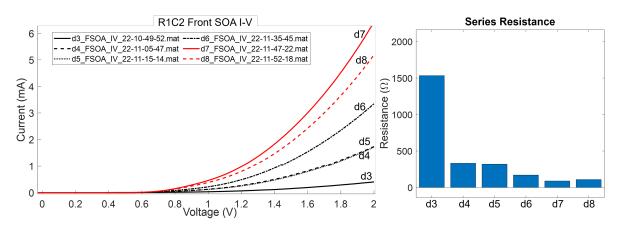

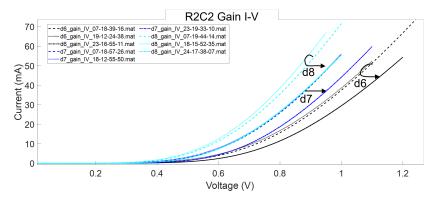

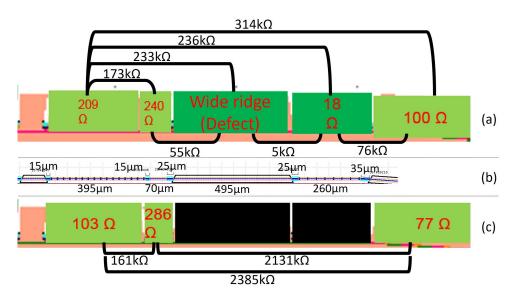

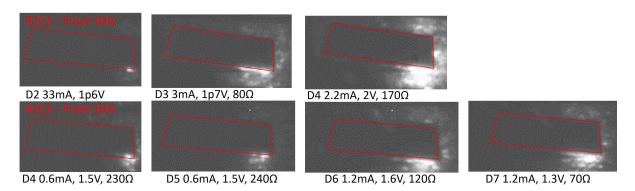

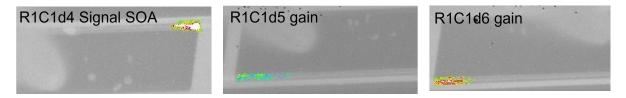

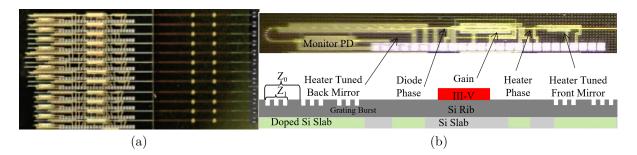

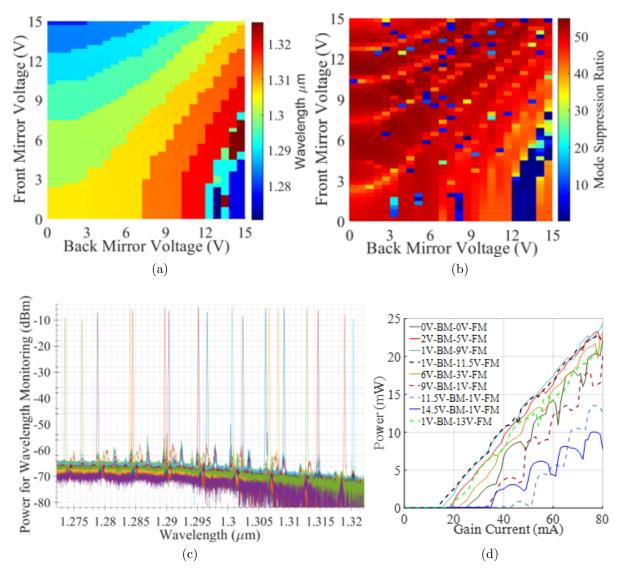

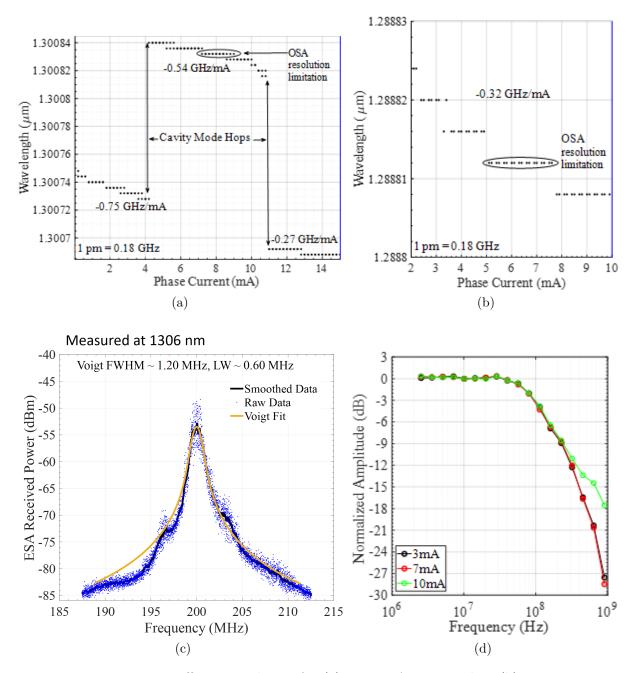

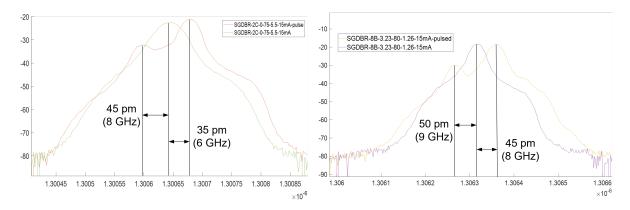

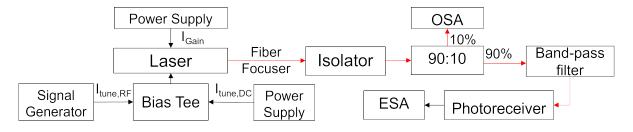

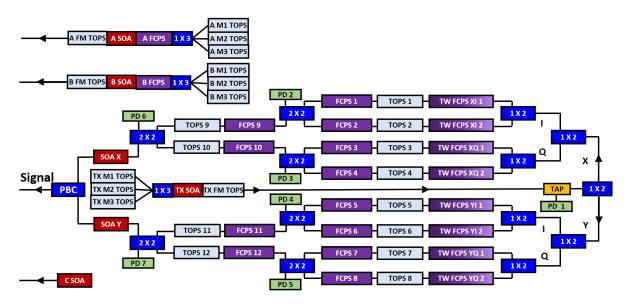

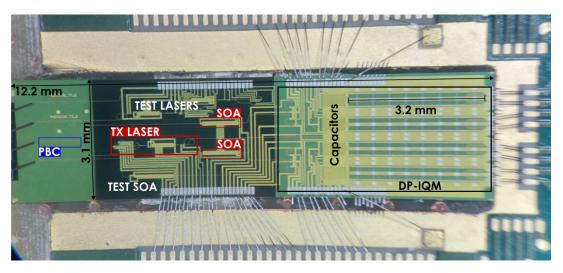

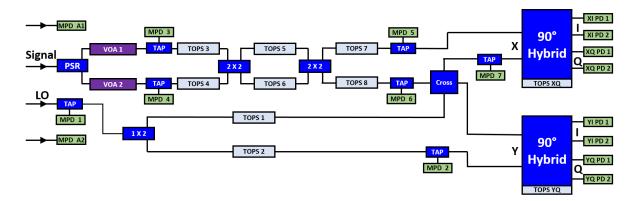

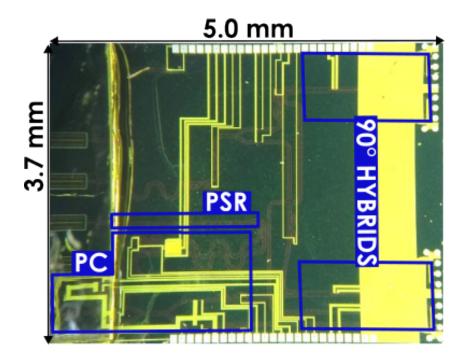

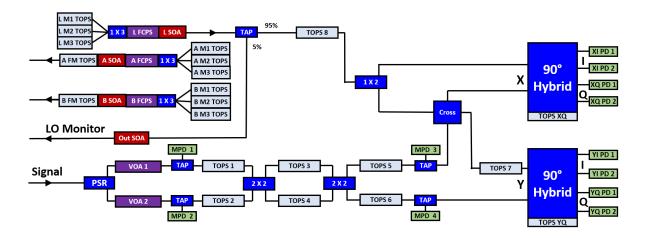

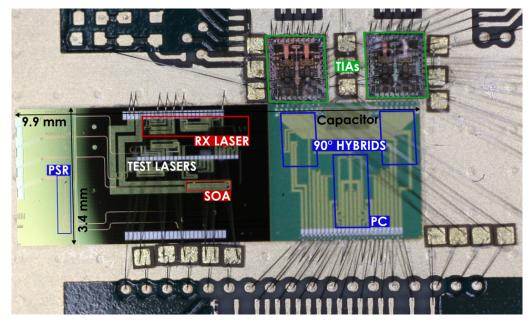

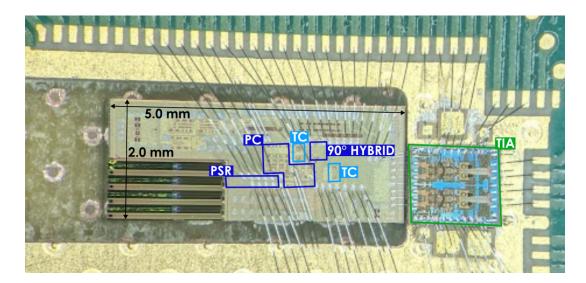

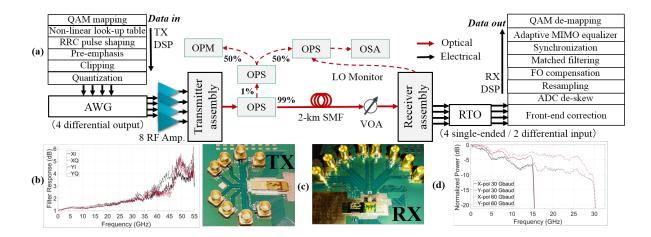

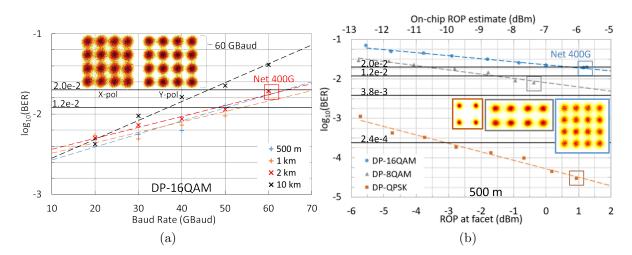

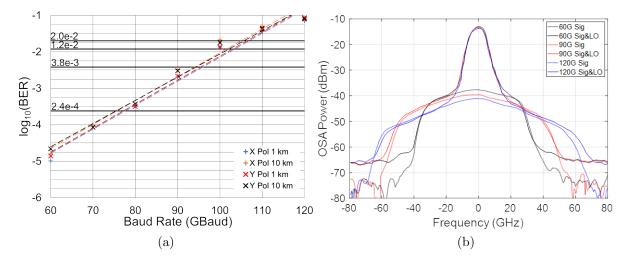

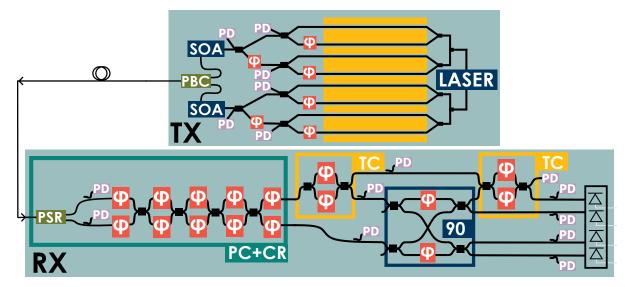

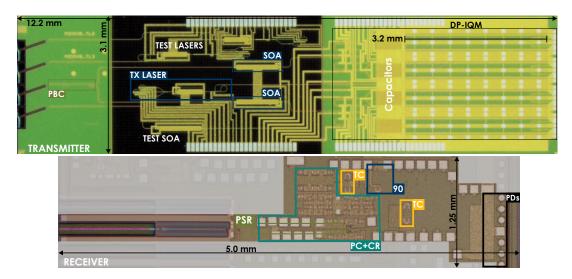

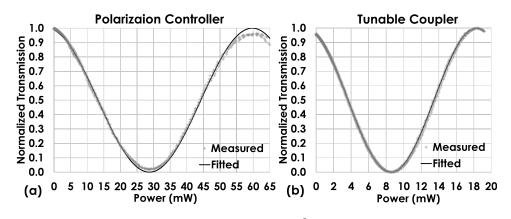

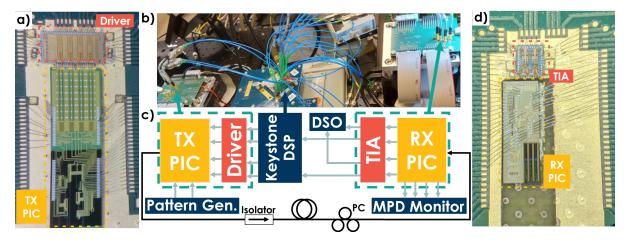

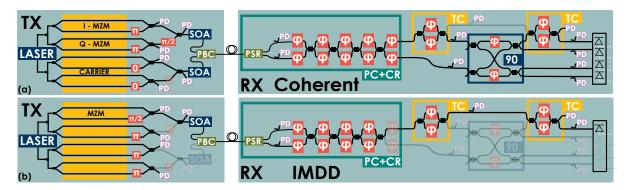

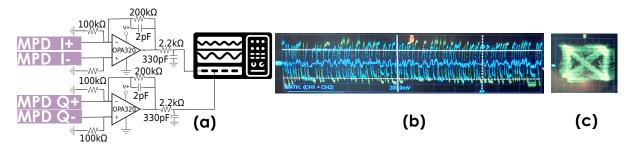

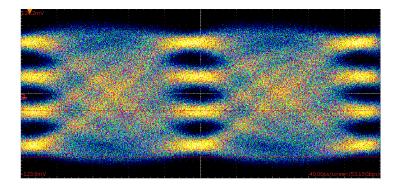

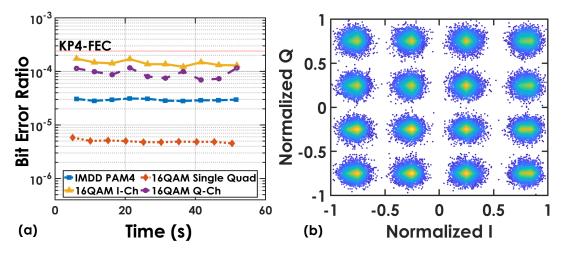

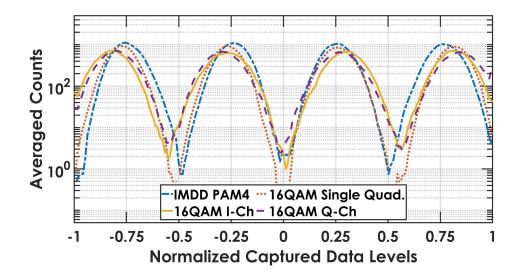

$$\Delta\lambda_{mode} = \frac{\lambda^2}{2\overline{n_g}L} \tag{2.16}$$