## **UC Davis**

#### **UC Davis Electronic Theses and Dissertations**

#### **Title**

High-Performance Wideband Power Amplifiers for 6G and Optical Communications

#### **Permalink**

https://escholarship.org/uc/item/2ks6r4b1

#### **Author**

Nguyen, Nguyen

#### **Publication Date**

2021

Peer reviewed|Thesis/dissertation

#### High-Performance Wideband Power Amplifiers for 6G and Optical Communications

By

#### NGUYEN LE KHOI NGUYEN

#### **DISSERTATION**

Submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

**Electrical and Computer Engineering**

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**DAVIS**

Approved:

Anh-Vu Pham, Chair

Omeed Momeni

Rajeevan Amirtharajah

Committee in Charge

2021

# ${\bf Abstract}$

Given how much of our current technology relies on the use of wireless sensors, improving communications technology directly benefits consumer products (smartphones, tablets, mobile devices of all kinds), healthcare (mobile monitoring devices, life-saving implants). Therefore, much higher communication speed, lower latency, and cheaper solutions are highly demanding as the technology is moving to the sixth generation (6G). The frequency band from 70 to 100 GHz and 125 to 160 GHz are currently the main focus band for the next generation of wireless communication.

Different from wireless communication systems, optical communication involves the transfer of information using light rather than radio frequencies (RF). This method of data transportations has many advantages over standard telecommunications methods, such as improved bandwidth, speed, and power. Optical communication devices have applications in data connectivity (such as cloud storage), transportation networks, CATV systems, submarines, and defense technology. Indeed, as communication technology continues to advance, optical networking devices are becoming a much sought-after commodity.

One of the most critical components in wireless communication and optical communication systems is the wideband power amplifiers (PA). Various semiconductor processes have been investigated to support the development of PA for 6G and optical communications systems. By far, Indium Phosphide (InP) and Silicon Germanium (SiGe) process have been proven to be great candidates for the development of the future system thanks to their superior performance in terms of cut-off frequencies. In addition, Indium Phosphide has a significantly higher output power and, therefore, is favorable for high power applications at high frequencies. However, as the operating frequencies emerge into the mm-W region, gain, linearity, and output power degrade rapidly, making the PA highly inefficient and unrealizable.

In this dissertation, several original techniques are proposed and implemented to distributed amplifiers and wideband amplifiers. These techniques are applied to demonstrate high-performance power amplifiers up to 160 GHz, potentially enabling the future realization of 6G and the next generation of optical communications. The original techniques are listed as follows:

- 1. A new bandpass distributed amplifier (DA) using a wideband gain-boosting technique is introduced. A novel feedback network with a series inductor and a shunt capacitor is employed. The traditional theory has suggested that a series inductor only enhances narrowband gain, and a shunt capacitor decreases upper-frequency capacities. However, the combination of these components can obtain a wideband gain enhancement. The proposed amplifier achieves the record gain boosting over the wide bandwidth ever reported.

- 2. A wideband linearization technique for distributed amplifiers achieves the highest linearization bandwidth. The technique utilizes an auxiliary transistor that generates distortion components, which are the opposite sign of those generated by the main amplifier. The proposed prototype demonstrates the widest linearization bandwidth.

- 3. A 160 GHz DA with bandwidth improvement using 3-D interdigital capacitors and a 150 GHz using metal-insulator-metal (MIM) capacitors are designed in an InP process. This work demonstrates for the first time that 3-D interdigital capacitors can be used to improve input matching conditions and bandwidth of a distributed amplifier.

- 4. A linear wideband differential optical driver amplifier in a SiGe process for the next generation of optical communication systems is demonstrated. This is the first time a triplestacked hetero junction bipolar transistor (HBT) with an emitter degeneration network is employed for optical drivers.

### Acknowledgments

First of all, I would like to express my sincerest gratitude toward my Ph.D. advisor, Professor Anh-Vu Pham, for his guidance, support, and encouragement from the very first day until the end of my graduate study. None of this work could have been done without his outstanding supervision and valuable advice.

I would like to thank the rest of my committee members, Professor Omeed Momeni, Professor Rajeevan Amirtharajah, for their time and guidance. In addition, I also thank Professor Jane Gu, Professor Xiaoguang Liu, and Professor Vivek Srinivasan for their support in my Qualifying Exam.

I am deeply grateful to Mr. Wayne Kennan, Dr. Novak Farrington, and Dr. Alexander Stameroff for their support and valuable comments on my research. I also thank Keysight Technologies, MACOM Technology Solutions, the Vietnam Education Foundation (VEF), and the IEEE MTT-S Graduate Fellowship for supporting my Ph.D. work.

Special thanks to my close friends for the enjoyable time we had, Dr. Thuy Nguyen, Dr. Reinhard Gentz, Stephen Imbach, Sam Wagner, and Can Cui.

I would like to thank my colleagues from the Microwave Microsystems Laboratory (MML), Dr. Duy P. Nguyen, Dr. Chi Pham, Dr. Matthew Clements, Dr. Manish Mamidanna, Dr. Mohammad Darwish, Dr. Tuan-Anh Vu, Natalie Killeen, Phat Nguyen, Juan Romero, Stephen Pancrazio, Ahmad Alkasimi, and my colleagues from the department, Li Zhang, Jingjun Chen, Hao Wang, Xuan Ding, and Hai Yu. So many great ideas, breakthroughs, and solutions were generated from our countless discussions.

My greatest appreciation goes to my family for their unconditional love and trust. My parents are always by my side since the day I was born, Mrs. Nghi Le and Mr. Binh Nguyen. Thanks to my older sister and my nephew, who are always cheerful.

# **Table of Contents**

| Abstract                                                                    | ii                  |

|-----------------------------------------------------------------------------|---------------------|

| Chapter 1. Introduction of 6G and Optical Communication Applications        | 1                   |

| 1.1 The sixth-generation (6G) and Optical Communications                    | 1                   |

| 1.2 Distributed Amplifiers                                                  | 2                   |

| 1.3 Dissertation Organization                                               | 4                   |

| 1.4 Reference                                                               | 5                   |

| Chapter 2. A Wideband Gain Enhancement Technique for Distributed Amplifiers | 6                   |

| 2.1 The Proposed Feedback Gain Cell                                         | 8                   |

| 2.2 Bandpass Cut-off Frequencies and Transmission Zero                      | 12                  |

| 2.3 The DA with the Proposed Feedback Technique                             | 16                  |

| 2.4 Circuit design and implementation                                       | 18                  |

| 2.4.1 The Inductive Feedback Network                                        | 18                  |

| 2.4.2 The Band-pass Gain Enhanced Distributed Amplifier                     | 20                  |

| 2.5 Measurement results                                                     | 23                  |

| 2.5.1 Small-signal Measurements                                             | 23                  |

| 2.5.2 Large-signal Measurements                                             | 26                  |

| 2.6 Conclusion                                                              | 29                  |

| 2.7 Reference                                                               | 29                  |

| Chapter 3. A Wideband Highly Linear Distributed Amplifier Using Intermodu   | lation Cancellation |

| Technique for Stacked-HBT Cells                                             | 33                  |

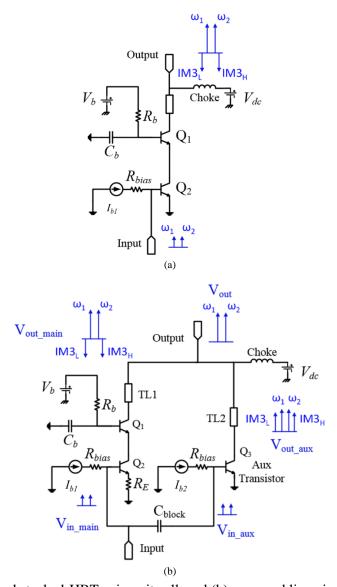

| 3.1 Proposed Linearization Technique                                        | 35                  |

| 3.1.2 Proposed wideband linearization technique                                   | 35  |

|-----------------------------------------------------------------------------------|-----|

| 3.2 Linearized Gain Unit Cell                                                     | 39  |

| 3.3 Distributed Amplifier Design                                                  | 44  |

| 3.4 Experimental Results                                                          | 48  |

| 3.5 Conclusion                                                                    | 55  |

| 3.6 Reference                                                                     | 56  |

| Chapter 4. 160 GHz Wideband, High Output Power Distributed Amplifiers             | 60  |

| 4.1 Proposed 3-D Interdigital Capacitor Distributed amplifier                     | 61  |

| 4.2.1 Circuit Design                                                              | 61  |

| 4.2.2 Experimental Results                                                        | 66  |

| 4.2.3 Conclusion                                                                  | 68  |

| 4.2.4 Reference                                                                   | 69  |

| 4.2 A Double-stacked HBT 1-150 GHz Distributed Amplifier                          | 70  |

| 4.2.1 Circuit Design                                                              | 70  |

| 4.2.2 Experimental Results                                                        | 72  |

| 4.2.3 Conclusion                                                                  | 75  |

| 4.2.4 Reference                                                                   | 75  |

| Chapter 5. A Wideband SiGe Power Amplifier Using Modified Triple Stacked-HBT Cell | 77  |

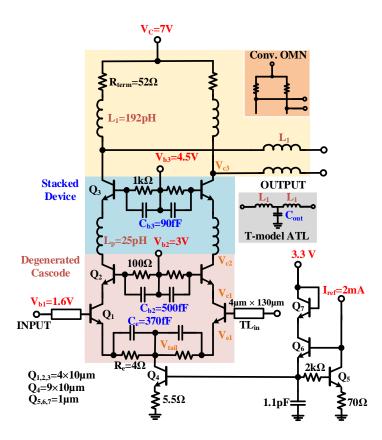

| 5.1 Circuit Design and Implementation                                             | 79  |

| 5.2 Experimental Results                                                          | 82  |

| 5.2 Conclusion                                                                    | 9.1 |

| 5.4       | Reference      | 5 |

|-----------|----------------|---|

|           |                |   |

| Chapter 6 | 5. Conclusions | 7 |

# List of Figures Chapter 1

| Fig. 2.12. Complete schematic diagram of the nine-stage feedback DA                                                    |

|------------------------------------------------------------------------------------------------------------------------|

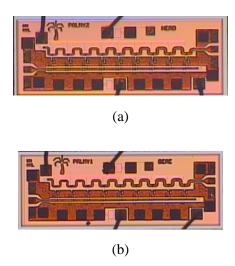

| Fig. 2.13. Chip photograph of (a) proposed inductive feedback bandpass DA, and (b) conventional low-                   |

| pass DA. Both chips have a size of 1.6 mm x 0.6 mm                                                                     |

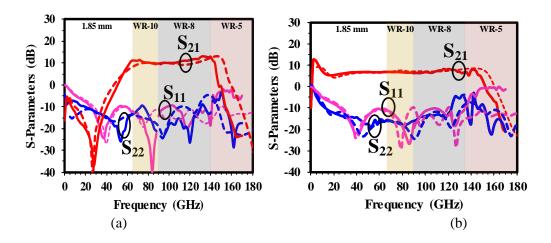

| Fig. 2.14. Measured (solid) and simulated (dashed) S-parameters of (a) the proposed feedback DA and (b)                |

| the conventional low-pass DA                                                                                           |

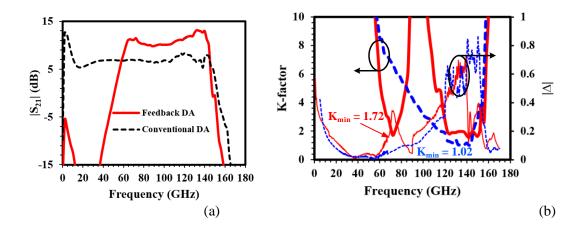

| Fig. 2.15. Comparison between feedback DA and conventional DA for (a) measured gain, $S_{21}$ , and (b)                |

| measured stability factors $k$ and $\Delta$ . The solid red line is the proposed feedback DA, and the dashed blue      |

| line is the conventional DA                                                                                            |

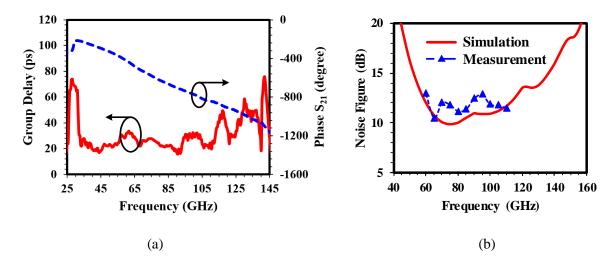

| Fig. 2.16. (a) Measured group delay (ps) and relative phase (degree) of S <sub>21</sub> , and (b) noise figure of the  |

| feedback DA                                                                                                            |

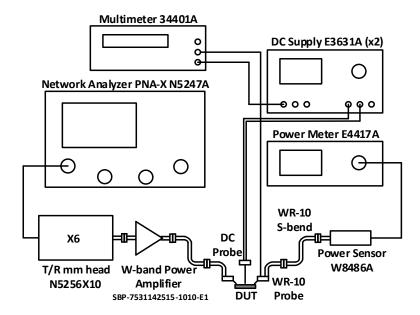

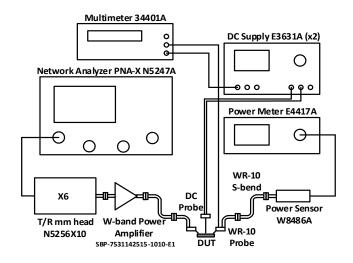

| Fig. 2.17. W-band power measurement test setup                                                                         |

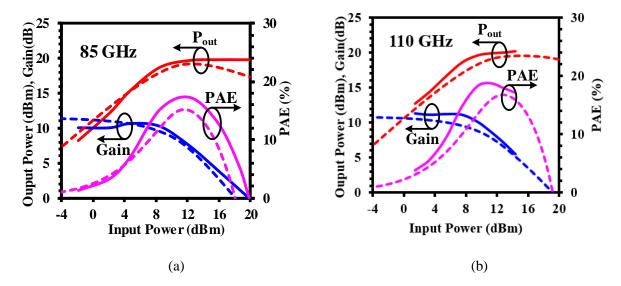

| Fig. 2.18. Measured and simulated output power, gain, and PAE of the proposed feedback DA at (a) 85                    |

| GHz, and (b) 110 GHz. The solid line and dashed line are measurement and simulation, respectively 27                   |

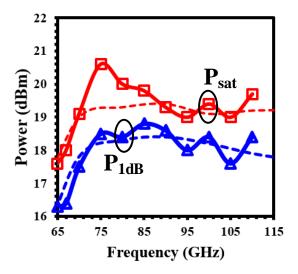

| Fig. 2.19. $P_{sat}$ and $P_{IdB}$ over the frequency of the feedback DA. The solid line and dashed line are           |

| measurement and simulation, respectively                                                                               |

|                                                                                                                        |

| Chapter 3                                                                                                              |

| Fig. 3.1. (a) Conventional stacked-HBT gain unit cell, and (b) proposed linearized gain unit cell36                    |

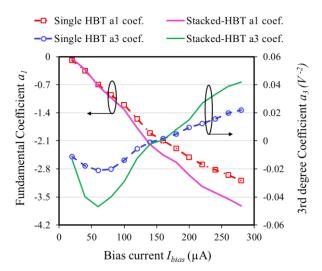

| Fig. 3.2. Fundamental and 3 <sup>rd</sup> degree coefficients of the single common-emitter HBT and stacked-HBT gain    |

| unit cell40                                                                                                            |

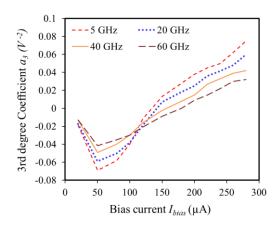

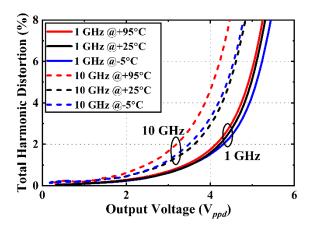

| Fig. 3.3. Third degree coefficient $a_3$ at frequencies: 5, 20, 40, 60 GHz40                                           |

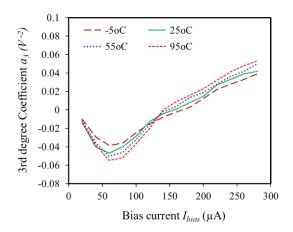

| Fig. 3.4. Third degree coefficient $a_3$ at temperature: -5, 25, 55, 95°C                                              |

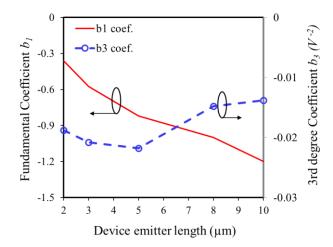

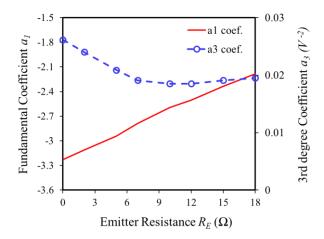

| Fig. 3.5. Fundamental and $3^{rd}$ degree coefficients of the auxiliary device $Q_3$ at $I_{bias} = 100 \mu\text{A}42$ |

| Fig. 3.6. Fundamental and 3 <sup>rd</sup> degree coefficients of the main stacked-HBT cell with emitter degeneration   |

| <i>R<sub>E</sub></i>                                                                                                   |

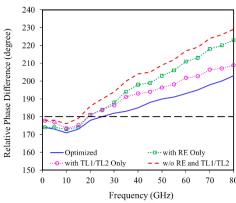

| Fig. 3.7. Simulated relative phase difference between the fundamental and 3 <sup>rd</sup> IM3 with emitted        |

|-------------------------------------------------------------------------------------------------------------------|

| degeneration $R_E$ . 43                                                                                           |

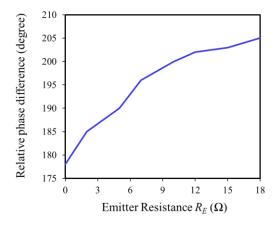

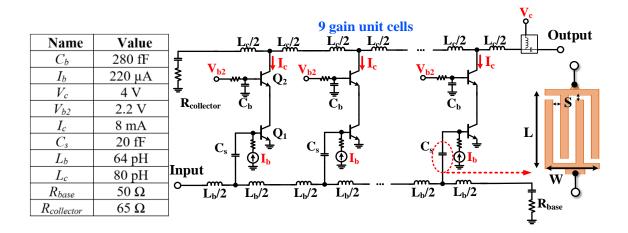

| Fig. 3.8. Schematic diagram of the proposed distributed amplifier.                                                |

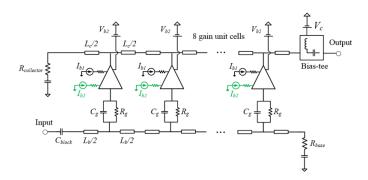

| Fig. 3.9. Simulated amplitude (a) and phase (b) of the fundamental components and 3 <sup>rd</sup> order           |

| intermodulation products at the output of the main and auxiliary paths under two-tone excitation44                |

| Fig. 3.10. Relative phase difference between the main IM3 and auxiliary IM3 signals versus frequency              |

| under the impact of TL1/TL2 and R <sub>E</sub>                                                                    |

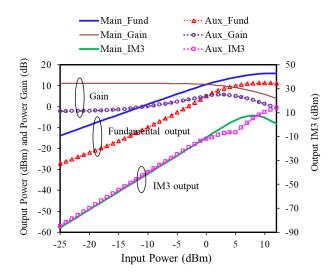

| Fig. 3. 11. Fundamental and IM3 amplitude as a function of input power at 40 GHz                                  |

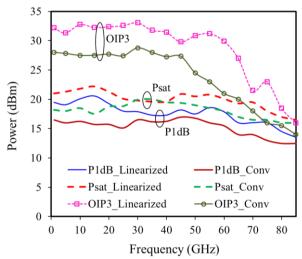

| Fig. 3. 12. Simulated $P_{1dB}$ and OIP3 of the linearized DA and conventional DA over frequency48                |

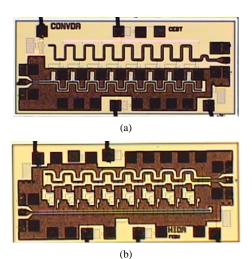

| Fig. 3. 13. Chip photograph of (a) conventional stacked-HBT DA, and (b) proposed linearized DA49                  |

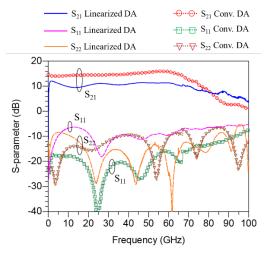

| Fig. 3.14. Measured S-parameter of the conventional DA and proposed linearized DA                                 |

| Fig. 3.15. Measured phase and group delay                                                                         |

| Fig. 3.16. (a) Measured output power and gain at continuous wave (CW) 20 GHz, and (b) dc power                    |

| dissipation and PAE versus output power of the conventional DA and proposed linearized DA51                       |

| Fig. 3.17. Measured relative IM3 components of the conventional DA and linearized DA at 20 GHz using              |

| two-tone excitation with 10 MHz tone spacing.                                                                     |

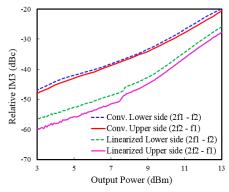

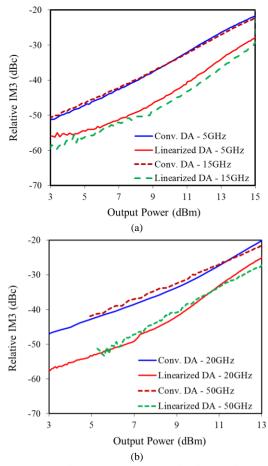

| Fig. 3.18. Measured relative IM3 using two-tone excitation with 10 MHz tone spacing of the conventional           |

| DA and proposed linearized DA: (a) center frequency 5 GHz and 15 GHz, and (b) center frequency 20 GHz             |

| and 50 GHz                                                                                                        |

| Fig. 3.19. Measured $P_{IdB}$ , $P_{sat}$ , and $OIP3$ as a function of frequency (at room temperature, nominal   |

| condition)53                                                                                                      |

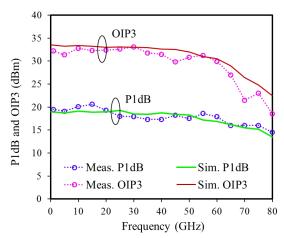

| Fig. 3.20. Measured versus simulated $P_{1dB}$ and $OIP3$ of the proposed linearized DA                           |

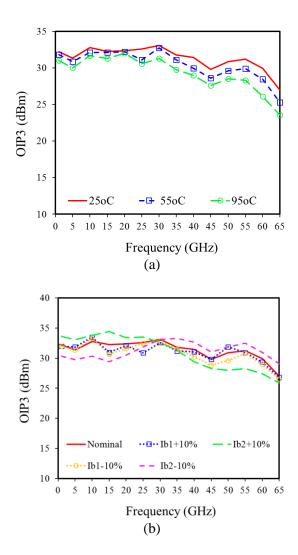

| Fig. 3.21. Measured <i>OIP3</i> of the linearized DA at (a) different backside temperature and (b) different bias |

| variants55                                                                                                        |

## Chapter 4

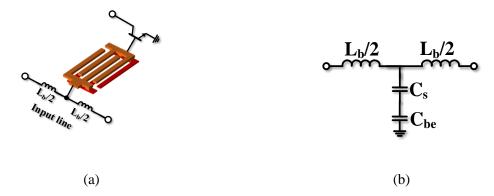

| Fig. 4.1.1. Schematic diagram of the proposed interdigital capacitors distributed amplifier61                                    |

|----------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.1.2. (a) Proposed 3-D interdigital capacitor, and (b) approximated equivalent T-model of a one-                           |

| section input transmission line                                                                                                  |

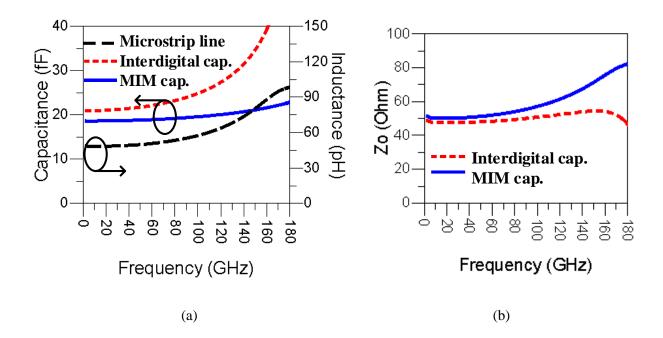

| Fig. 4.1.3. Simulated (a) Capacitance and inductance of the proposed 3-D interdigital capacitor, MIM                             |

| capacitor, and a microstrip line inductor. (b) Characteristic impedance two nine-section T-model                                 |

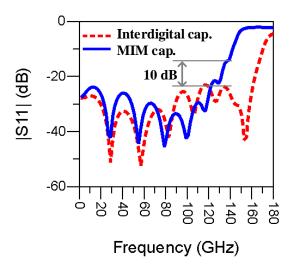

| transmission lines                                                                                                               |

| Fig. 4.1.4. Input return loss of the nine-section transmission lines using different capacitors                                  |

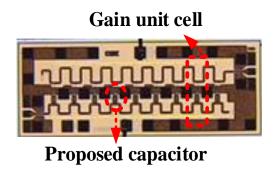

| Fig. 4.1.5. Microphotograph of the proposed 3-D interdigital capacitor distributed amplifier (1.6 mm $\times$                    |

| 0.8 mm, including all pads)64                                                                                                    |

| Fig. 4.1.6. Measured and simulated small-signal S-parameters                                                                     |

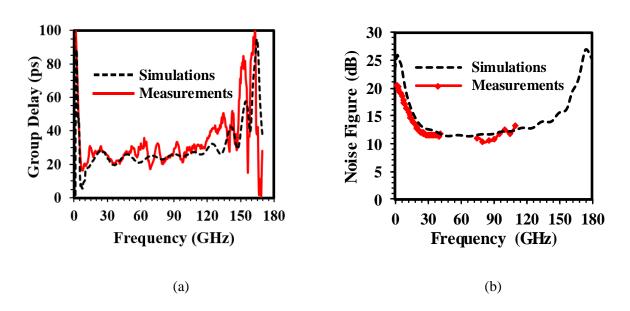

| Fig. 4.1.7. Measured and simulated (a) group delay (ps), and (b) noise figure (dB) of the proposed DA. 65                        |

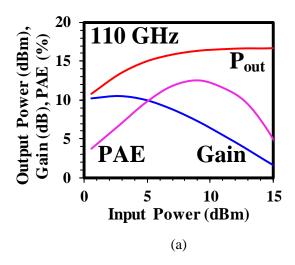

| Fig. 4.1.8. (a) Measured large-signal measurement at 110 GHz, and (b) measured saturated output power                            |

| P <sub>sat</sub> and 1-dB compression power P <sub>1dB</sub>                                                                     |

|                                                                                                                                  |

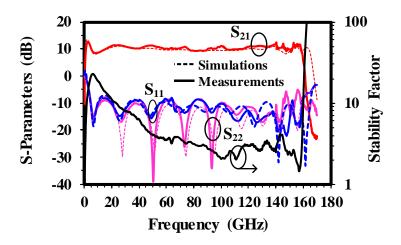

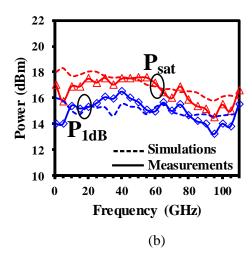

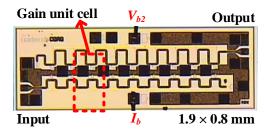

| Fig. 4.2.1 (a) Schematic diagram of the double-stacked distributed amplifier and (b) layout realization of                       |

| the parallel/series input coupling capacitor $C_s$                                                                               |

| Fig. 4.2.2. Die photograph of the nine-stage double-stacked distributed amplifier (1.9 mm $\times$ 0.8 mm                        |

| including all pads)                                                                                                              |

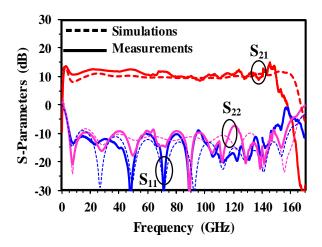

| Fig. 4.2.3. Measured and simulated small-signal S-parameters                                                                     |

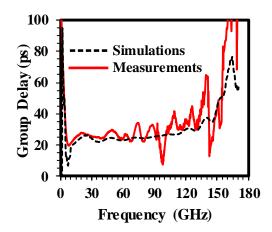

| Fig. 4.2.4. Measured and simulated group delay (ps) of the proposed DA                                                           |

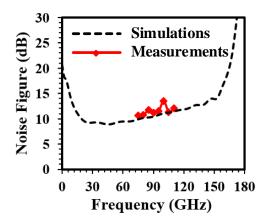

| Fig. 4.2.5. Measured and simulated noise figure (dB) of the proposed DA                                                          |

| Fig. 4.2.6. W-band power measurement test setup                                                                                  |

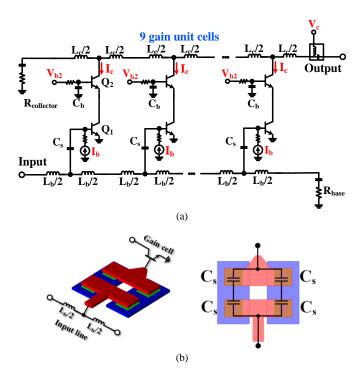

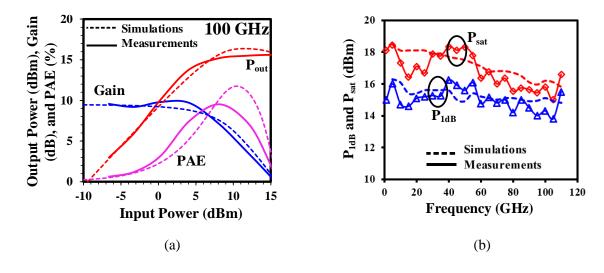

| Fig. 4.2.7. Measured and simulated of (a) $P_{out}$ , gain, and $PAE$ at 100 GHz and (b) $P_{sat}$ , $P_{1dB}$ , and $PAE_{max}$ |

| over frequencies                                                                                                                 |

| Chapter 5                                                                                                                        |

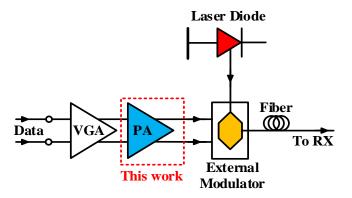

| Fig. 5.1. Block diagram of a typical optical transmitter                                                                         |

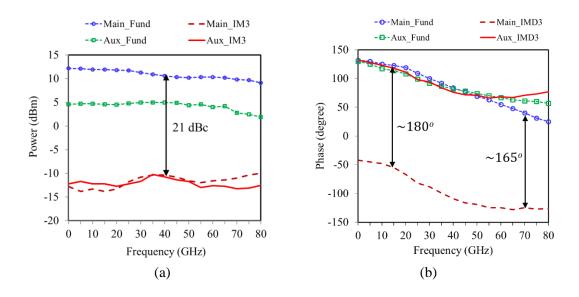

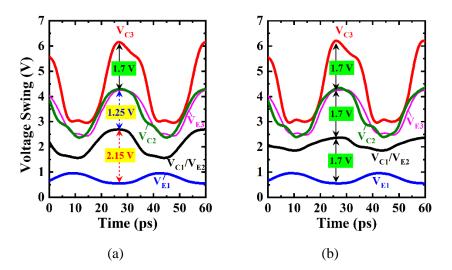

| Fig. 5.2. Circuit diagram of the proposed amplifier                                              | 78         |

|--------------------------------------------------------------------------------------------------|------------|

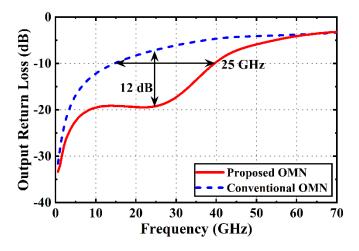

| Fig. 5.3. Simulated voltage swings of (a) the conventional triple-stacked, and (b) the proposed  | d modified |

| stacked topology at 30 GHz.                                                                      | 80         |

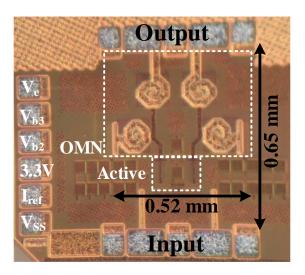

| Fig. 5.4. Simulated output return loss using the proposed output matching network (OMN           | N) and the |

| conventional approach.                                                                           | 80         |

| Fig. 5.5. Microphotograph of the amplifier. The core amplifier size is 0.52×0.65 mm <sup>2</sup> | 81         |

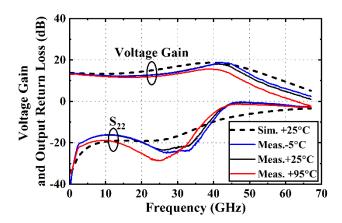

| Fig. 5.6. Measured voltage gain and output return loss over temperature.                         | 82         |

| Fig. 5.7. Measured large-signal performance of the proposed power amplifier.                     | 82         |

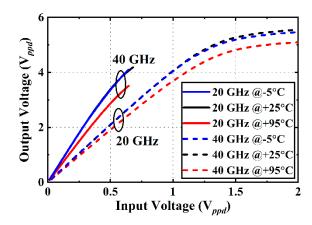

| Fig. 5.8. Measured differential output voltage swing of the proposed power amplifier with        | the swep   |

| differential input voltage                                                                       | 83         |

# **List of Tables**

### Chapter 2

| Table 2.1. Design Parameters of The Proposed Feedback DA         | 22 |

|------------------------------------------------------------------|----|

| Table 2.2. Comparison to State-of-The-Art Wideband Amplifiers    | 28 |

| Chapter 3                                                        |    |

| Table 3.1. Design Parameters Of The Two Amplifiers               | 46 |

| Table 3.2. Comparison to Other State-of-The-Art Das              | 56 |

| Chapter 4                                                        |    |

| Table 4.1. Comparison to State-of-The-Art Distributed Amplifiers | 68 |

| Table 4.2. Design Parameters and Biasing Condition               | 70 |

| Table 4.3. Comparison to State-of-The-Art DAs                    | 75 |

| Chapter 5                                                        |    |

| Table 5.1. Comparison to State-of-The-Art Modulator Drivers      | 84 |

#### **Curriculum Vitae**

#### **EDUCATION**

2021 Ph.D. in Electrical and Computer Engineering from University of California, Davis, CA, USA 2019 M.Sc. in Electrical and Computer Engineering from University of California, Davis, CA, USA 2016 B.Eng. in Electrical Engineering and Information Technology from Vietnamese-German University, Binh Duong, Vietnam 2016 B.Eng. in Electrical Engineering and Information Technology from Frankfurt University of Applied Sciences, Frankfurt, Hesse, Germany **HONORS AND AWARDS** 2021 UC Davis Dissertation Writing Fellowship 2020 IEEE Asia-Pacific Microwave Conference best regular paper in Microwaves 2020 IEEE MTT-S Graduate Fellowship 2016 Vietnam Education Foundation Ph.D. Fellowship PROFESSIONAL EXPERIENCE MMIC Design Internship, MACOM Technology Solutions, Santa Clara, CA, 2019 **USA** 2018 MMIC Design Internship, MACOM Technology Solutions, Santa Clara, CA, **USA** PROFESSIONAL SERVICES **Journals Reviewer** Journals: IEEE Transaction on Microwave and Techniques, IEEE Microwave Wireless Components Letters, IEEE Access, IET Microwaves, Antennas and Propagation **Conferences Reviewer** IEEE MWCAS, ISCAS, APCCAS **Conference Organization** 2020 IEEE Asia-Pacific Conference on Circuits and Systems (APCCAS) Session Chair

#### **PUBLICATIONS**

#### **Journals**

- [1] N. L. K. Nguyen, B. T. Nguyen, T. Omonri, D. P. Nguyen, R. Moroney, S. D'Agostino, W. Kennan, and A. Pham, "A Wideband SiGe Power Amplifier Using Modified Triple Stacked-HBT Cell," in *IEEE Microwave and Wireless Components Letters*, vol. 31, no. 1, pp. 52-55, Jan. 2021

- [2] N. L. K. Nguyen, N. S. Killeen, D. P. Nguyen, A. N. Stameroff and A. -V. Pham, "A Wideband Gain-Enhancement Technique for Distributed Amplifiers," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 9, pp. 3697-3708, Sept. 2020

- [3] N. L. K. Nguyen, D. P. Nguyen, A. N. Stameroff and A. Pham, "A 1–160-GHz InP Distributed Amplifier Using 3-D Interdigital Capacitors," in *IEEE Microwave and Wireless Components Letters*, vol. 30, no. 5, pp. 492-495, May 2020

- [4] D. P. Nguyen, N. L. K. Nguyen, A. N. Stameroff, V. Camarchia, M. Pirola and A. Pham, "A Wideband Highly Linear Distributed Amplifier Using Intermodulation Cancellation Technique for Stacked-HBT Cell," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 7, pp. 2984-2997, July 2020

#### Conference

- [5] N. L. K. Nguyen, D. P. Nguyen, A. Stameroff and A. Pham, "A High Output Power 1 150 GHz Distributed Power Amplifier in InP HBT Technology," 2020 IEEE Asia-Pacific Microwave Conference (APMC), Hong Kong, Hong Kong, 2020

- [6] D. P. Nguyen, X. Tran, P. T. Nguyen, N. L. K. Nguyen and A. Pham, "High Gain High Efficiency Doherty Amplifiers with Optimized Driver Stages," 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 2019

- [7] D. P. Nguyen, X. -T. Tran, N. L. K. Nguyen, P. T. Nguyen and A. Pham, "A Wideband High Efficiency Ka-Band MMIC Power Amplifier for 5G Wireless Communications," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019

- [8] D. P. Nguyen, N. L. K. Nguyen, A. N. Stameroff and A. Pham, "A Highly Linear InP Distributed Amplifier Using Ultra-wideband Intermodulation Feedforward Linearization," 2018 IEEE/MTT-S International Microwave Symposium - IMS, Philadelphia, PA, USA, 2018

#### **Under Review**

- [9] **N. L. K. Nguyen**, *et al.*, "A 150 GHz, 17.8 dBm and 110 GHz, 24.5 dBm Output Power Distributed Amplifier in InP Process", under review, in *IEEE Transactions on Microwave Theory and Techniques*.

- [10] **N. L. K. Nguyen**, et al., "A 1 220 GHz High Isolation Amplifier in InP Process for 6G Applications", to be submitted, in *IEEE Microwave and Wireless Components Letters*.

- [11] **N. L. K. Nguyen**, *et al.*, "A DC-75 GHz High Gain InP HBT Distributed Amplifier Using Pseudo Tapered Output Line", to be submitted.

# Chapter 1. Introduction of 6G and Optical Communication Applications

#### 1.1 The sixth-generation (6G) and Optical Communications

The need for improved communications is spurred by the increase in mobile traffic as developments in artificial intelligence (AI), and the Internet of Everything (IoE) proliferate. In 2017, global mobile data traffic was at 11.51 exabytes per month. In 2020, it reached 40.77 exabytes per month and is set to be 77.49 exabytes per month by 2022 [1]. Nowadays, the fifth generation (5G) of wireless communication has been introduced to the public with the expectation of greatly improve user experiences. Moreover, 5G communication is unable to accommodate the most leading-edge advances in automation and AI technology.

Given how much of our current technology relies on the use of wireless sensors, improving communications technology directly benefits consumer products (smartphones, tablets, mobile devices of all kinds), healthcare (mobile monitoring devices, life-saving implants), and defense (more powerful radios in ground vehicles, aircraft, and for soldiers). In 2019, the global smartphone market had a value of \$714.96 billion USD. Further, the United States is investing heavily in patient monitoring devices (with market size of \$4.4 billion USD in 2016, set to reach \$6 billion USD by 2023) and defense (current spending is \$934 billion USD) [2].

Therefore, much higher communication speed, lower latency, and cheaper solutions are highly demanding as the technology is moving to the sixth generation (6G). The millimeter-wave region is attractive to researchers due to the fact that smaller wavelength such as visible light, which is highly susceptible to the ambient environment, or radiative wavelengths such as X-ray, which are harmful to human and, therefore, infeasible to be used at a wireless communication method [3]. As a result, the frequency band from 70 to 100 GHz and 125 to 160 GHz are the main focus band for the next generation

of wireless communication. In fact, several research groups have demonstrated the feasibility of a wireless communication system at 150 GHz [4].

Different from wireless communication systems, optical communication involves the transfer of information using light rather than radio frequencies (RF). This has many advantages over standard telecommunications methods, such as improved bandwidth, speed, and power. Optical communication devices have applications in data connectivity (such as cloud storage), transportation networks, CATV systems, submarines, and defense technology. Indeed, as communication technology continues to advance, optical networking devices are becoming a much sought-after commodity, commanding \$16.9 billion in total market value. Moreover, it is estimated that the United States must invest anywhere from \$130-\$150 billion in optical fiber communication to keep up with the competition [5].

One of the most critical components in both wireless communication and optical communication systems is the power amplifiers (PA). In a typical transceiver architecture, the PA is the most power-hungry component in the chain. Furthermore, highly advanced systems such as multiple-input-multiple-output (MIMO) require a large number of power amplifiers on the transmitter side. As a result, high-performance PAs over a very wide bandwidth is crucial to the implementation of the systems. Several specifications such as high gain, high linearity, high output power, and high efficiency over a very wide bandwidth are desirable in many applications.

#### 1.2 Distributed Amplifiers

The wideband matching performance of passive matching networks is limited by the Bode-Fano bandwidth limitation and is impractical to achieve a fractional bandwidth near 200% [6]. The Bode-Fano equation does, however, indicate that the bandwidth of an amplifier can be extensively increased if the output capacitance of the amplifier can be reduced. The reduction of the effective input and output capacitance of a gain block is essentially the underlying basis of distributed amplifiers (DAs).

The distributed amplifier, which is also named traveling-wave amplifiers, was originally invented by Ginzton in 1948 [7]. The very first DA was presented in vacuum tube technology in the 1950s, which had the gain of 11dB in a bandwidth of 100Hz-300MHz with a 15W output power [8]. The first monolithic integrated circuit (MMIC) DA was implemented in 1982 by Ayasli in a Gallium Arsenide (GaAs) metal-semiconductor field-effect transistor (MESFET) process [9]. The first MMIC DA was accommodated with a  $50\Omega$  input and output system and achieved 9dB gain from 1-13GHz bandwidth. Ever since, the distributed amplifiers have been implemented in various technologies such as complementary metal-oxide-semiconductor (CMOS), Gallium Nitride (GaN), Silicon Germanium (SiGe), and Indium Phosphide (InP), etc. These technologies provide different benefits from bandwidth, power, noise, and production cost.

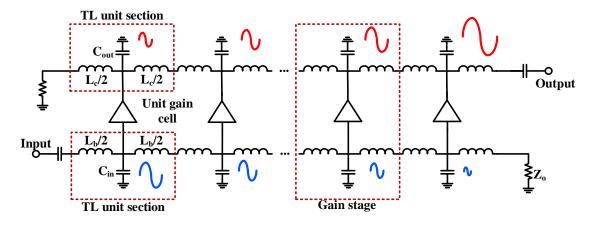

Fig. 1.1 Conceptual presentation of an N-stage DA

Fig 1.1 shows an N-stage conceptual distributed amplifier, where  $L_b$ ,  $L_c$ ,  $C_{in}$  and  $C_{out}$  are the baseline inductor, collector-line inductor, effective input capacitance and effective output capacitance of the gain cell, respectively. The base-line inductors and the effective input capacitance of the gain cell form an input artificial transmission line. The collector-line inductors and the effective output capacitance of the gain cell create an output artificial transmission line. This is the key idea of the distributed amplification. The inductances are chosen in such a way that the characteristic impedance of the lossless input and output artificial transmission lines are equal to  $Z_0$  to achieve a good return loss. The values of  $L_b$  and  $L_c$ , therefore, can be computed by

$$Z_{0,b} = Z_{0,c} = Z_0 = \sqrt{\frac{L_b}{C_{in}}} = \sqrt{\frac{L_c}{C_{out}}}.$$

(1.1)

Furthermore, the phase synchronization between the input and the output lines should be satisfied to achieve gain flatness over frequency. This relation can be expressed as

$$\tau_b = \tau_c = \sqrt{L_b C_{in}} = \sqrt{(L_c C_{out})} \tag{1.2}$$

If we assume each of the gain cell contributes an transconductance of  $g_m$ , and the load of each gain cell is identical, then the voltage gain of the DA can be derived as

$$A_{\nu} = \frac{1}{2}N \cdot g_m \cdot Z_0 \tag{1.3}$$

where N is the number of stages and  $Z_0$  is the characteristic impedance of the lines. The wave propagates to the input line, gets amplified by the gain cell. The input wave is terminated at the end of the line. At the output, the wave propagates in two directions, namely forward and reverse. The forward direction provides the same phase path for each of the gain cells. Therefore, the signal is added up and propagates to the output. In the reverse direction, the signal is out of phase and is terminated with the characteristic impedance. There is a trade-off between the gain bandwidth of the DA.

#### 1.3 Dissertation Organization

Background motivations, global and the U.S. statistics on communications, concept and basic theory on distributed amplifiers are introduced in Chapter 1.

Chapter 2 presents a novel wideband gain boosting technique for distributed amplifiers. In this chapter, a detailed analysis, design, and characterizations of two DA prototypes in an Indium Phosphide (InP) process are discussed. The proposed technique illustrates the highest gain enhancement over the widest bandwidth from (60 to 145 GHz) ever reported.

Chapter 3 introduces a novel wideband linearization technique for DAs using a feed-forward technique. The chapter covers the analysis, design, and characterization of two prototypes in InP. The proposed technique demonstrates the highest linearization bandwidth (dc to 90 GHz) ever reported.

Chapter 4 focuses on the design and demonstration of high-performance DAs from 1 to 160 GHz in InP. This chapter presents two prototypes with the implementation of double-stacked HBT gain cell and interdigital capacitors for bandwidth enhancement.

Chapter 5 presents the design of a new wideband triple-stacked HBT power amplifier in Silicon Germanium (SiGe). The driver amplifier design is suitable for the next generation of optical communication systems.

Chapter 6 concludes the dissertation with notable remarks.

#### 1.4 Reference

- [1] J. Clement, "Global mobile data traffic 2022," Statista, 28-Feb-2020. [Online]. Available: https://www.statista.com/statistics/271405/global-mobile-data-traffic-forecast/. [Accessed: 21-May-2021]. [2] https://www.statista.com/topics/2711/us-smartphone-market/

- [3] T. S. Rappaport, Y. Xing, O. Kanhere, S. Ju, A. Alkhateeb, G. C. Trichopoulos, A. Madanayake, S. Mandal, "Wireless Communications and Applications Above 100 GHz: Opportunities and Challenges for 6G and Beyond (Invited)," IEEE ACCESS, Vol. 7, No. 7, June 2019

- [4] "NEC successfully demonstrates 10Gbps outdoor transmission in the 150GHz-band," NEC. [Online]. Available: https://www.nec.com/en/press/202003/global\_20200304\_01.html. [Accessed: 21-May-2021].

- [5] Dan Littmann "Deep fiber: The next internet battleground: Deloitte US," *Deloitte United States*, 03-May-2021. [Online]. Available:

- https://www2.deloitte.com/us/en/pages/consulting/articles/communications-infrastructure-upgrade-deep-fiber-imperative.html. [Accessed: 21-May-2021].

- [6] C. F. Campbell, "Evolution of the Nonuniform Distributed Power Amplifier: A Distinguished Microwave Lecture," in IEEE Microwave Magazine, vol. 20, no. 1, pp. 18-27, Jan. 2019.

- [7] E. L. Ginzton, W. R. Hewlett, J. H. Jasberg, and J. D. Noe, "Distributed amplification," Proc. IRE, vol. 36, no. 8, pp. 956–969, Aug. 1948.

- [8] A. P. Copson, "A distributed power amplifier," Elect. Eng., vol. 69, no. 10, pp. 893–898, Oct. 1950

- [9] Y. Ayasli, R. L. Mozzi, J. L. Vorhaus, L. D. Reynolds, and R. A. Pucel, "A monolithic GaAs 1-13-GHz travelling-wave amplifier," IEEE Trans. Microwave Theory Tech., vol. MTT-30, pp. 976–981, July 1982.

# Chapter 2. A Wideband Gain Enhancement Technique for Distributed Amplifiers

Wideband, high gain, high output power, and low power consumption are the prominent figures of merit for high data rate communication systems, high-resolution radars, and instrumentation applications [1]. When frequency emerges to the millimeter-wave (mmW) and sub-millimeter-wave regions, maintaining high gain and output power becomes challenging due to increased transmission line losses, unwanted couplings, and parasitic elements [2], [3]. Gain is further degraded when a transistor operates near the transition frequency ( $f_T$ ) for a given process. Distributed amplifiers (DAs) have been proven to offer ultra-wideband performance but still suffer from gain-bandwidth (GBW) trade-offs [1].

Different techniques have been reported to enhance the DA gain, including cascaded gain stages [3]-[8], cascaded multi- and single-stage [9]-[11], and matrix DAs [12], [13]. However, the results come along with larger chip sizes and higher dc consumption. These techniques also increase the gain in a multiplicative amplification, thereby degrading stability. Cascaded amplifiers also reduce the bandwidth performance depending on the number of cascaded stages and passive losses. Furthermore, mismatches between the stages introduce mid-band ripples and worsen the group delay of the amplifier.

Techniques to enhance the gain-bandwidth product of the DA have also been reported. A widely used technique is to employ peaking inductors at the inter-stage nodes [5], [7], [8], [11], [14]. The gain peaking approach is simple and easy to implement, although the overall gain flatness and stability are sensitive to temperature variations and model accuracy. The coupled drain-line inductors [15], [16], coupled gate-line inductors [15]-[18], and the negative resistance loss compensation have been proposed to extend DA bandwidth [19]-[21]. In addition, several feedback techniques have already been employed in a DA structure to improve performance. The resistive-source-degeneration technique is used in [22]-[24], which provides negative feedback to improve the bandwidth at the expense of the amplifier's gain. A DA with an internal feedback loop introduced in [25] uses an internal path to direct the signal back through the DA for

re-amplification. Another form of feedback is a direct coupling between the input and output line, such as the gate-drain transformer feedback technique [26], [27], or by using capacitive feedback [28]. In [28], a capacitor is connected from the output to the input line to inject power and compensate for the loss from the input line at high frequency. However, direct feedback from output to input could reduce the stability of the circuit. The aforementioned techniques are inherently gain boosting techniques at high frequencies, while the gain at low frequencies remains unchanged.

Besides the conventional low-pass structure, distributed amplifiers can be implemented in a bandpass configuration. The conventional bandpass DA is implemented using bandpass transmission line structures instead of low-pass ones. Several methods have been introduced, such as adding series capacitors on the transmission line [29], or connecting shunt-series LC networks at either or both of the input and output line [28], [30]-[32]. The benefit of using a shunt inductor in a T-section model of a transmission line is to slightly increase the maximum operating frequency. However, the trade-off is the degradation of the lower frequency edge performance, and GBW is significantly reduced. Recently, a bandpass Silicon Germanium (SiGe) distributed amplifier using cascode HBT cells and a supply-scaling technique to achieve high power and efficiency has also been introduced [33].

In this chapter, we present a new bandpass distributed amplifier using an inductive feedback technique to uniformly enhance the gain for the entire passband while maintaining the upper cut-off frequency. The original contributions of our work include:

- The introduction of a new bandpass topology for DAs that preserves the GBW compared to the conventional low-pass structure.

- 2) A comprehensive analysis is presented showing how the proposed inductive feedback enhances the DA gain for the entire bandwidth. Notably, the introduction of peaking poles at lower and upperfrequency edges of the bandpass amplifier.

- 3) The designed DA achieves the highest reported gain boosting over a very wide bandwidth.

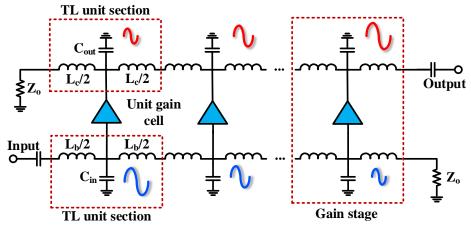

Fig. 2.1. Conceptual presentation of an N-stage low-pass DA.

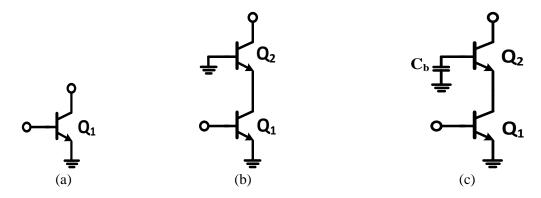

Fig. 2.2. Typical unit gain cells using HBTs: (a) common emitter, (b) cascode topology, (c) stacked-HBTs with a base capacitor  $C_b$ .

To validate the proposed technique, a 60 - 145 GHz bandpass DA is designed and fabricated in an Indium Phosphide (InP) Heterojunction Bipolar Transistor (HBT) process. The prototype exhibits a measured average small-signal gain of 10.5 dB, a 3-dB bandwidth from 60 - 145 GHz, and a maximum saturation power ( $P_{sat}$ ) of 20.9 dBm with the corresponding 1 dB compression power ( $P_{1dB}$ ) of 18.5 dBm at 75 GHz. The feedback DA has a 4-dB gain improvement spanning from 64 to 142 GHz compared to its counterpart conventional DA.

#### 2.1 The Proposed Feedback Gain Cell

Fig. 2.1 shows a conceptual N-stage distributed amplifier, where  $L_b$ ,  $L_c$ ,  $C_{in}$ , and  $C_{out}$  are the base-line inductor, collector-line inductor, and effective input and output capacitances of an ideal gain cell,

respectively. Fig. 2.2 illustrates common implementations of the unit gain cell of Fig. 2.1 using HBT devices, including a common emitter transistor, a cascode structure, and double-stacked HBTs. Compared to a single common emitter device, a cascode and double-stacked HBTs can provide a lower output conductance. This low output conductance of the cascode/stacked structure minimizes the loss of the output artificial transmission line [34]-[36]. The base capacitor  $C_b$  in Fig. 2.2(c) provides a finite impedance that allows for a small voltage swing at the base of the transistor  $Q_2$ . Hence, the voltage swing between the collector and the emitter of  $Q_2$  is reduced at high frequencies and is below the breakdown voltage [24], [37], [38].

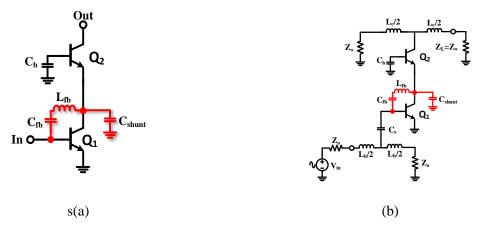

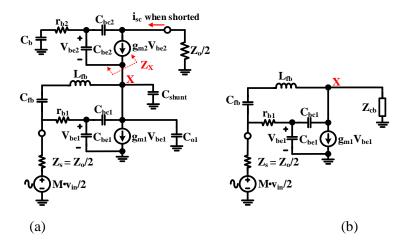

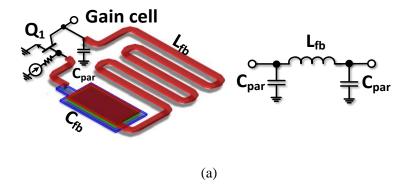

We propose a wideband gain enhancement technique for a DA, which provides a high roll-off bandpass structure by using an inductive feedback network applied to Fig. 2.2(c), as shown in Fig. 2.3(a). The proposed technique introduces a feedback inductor  $L_{fb}$  and a shunt capacitor  $C_{shunt}$  at the collector of the common emitter transistor in the stacked-HBT gain cell configuration. The feedback inductor  $L_{fb}$  introduces gain peaking at the low-frequency edge while the shunt capacitor  $C_{shunt}$  boosts up the gain at the high-frequency edge. The feedback capacitance  $C_{fb}$  acts as a dc block from the collector to the base of transistor  $Q_I$  to prevent shorting out the HBT.

Fig. 2.3(b) shows a single-stage DA employing the proposed gain cell in Fig. 3(a) in addition to a commonly used series input capacitor  $C_s$  to obtain a high bandwidth. In general, the feedback network has an insignificant impact on the overall input capacitance of the gain cell for most of the passband. The input capacitance of the feedback gain cell is then approximately equal to  $C_{be1}$ . The coupling capacitor  $C_s$  factors the gain of the DA by the capacitive division ratio, M, defined as  $M = C_s/(C_s + C_{be1})$  [39]. In order to maximize the bandwidth, the ratio M can be much smaller than one. Although stacked-FETs have been scrutinized and reported [37], [38], [40], a DA using inductive feedback stacked-HBTs has not been examined before. By constructing a Thevenin equivalent at the input, the input voltage source is factored by M/2. The output network is simplified into  $Z_0/2$ . The schematic in Fig. 2.3(b) can be presented by a small-signal circuit in Fig. 4(a). The voltage gain of the single-stage DA can be calculated as

Fig. 2.3. (a) The proposed bandpass inductive feedback gain cell, and (b) a single-stage DA using the proposed gain cell.

Fig. 2.4. (a) Simplified small-signal model of the single-stage DA for gain calculation (dc bias is omitted for simplicity) and (b) simplified the load at node X of the transistor Q1.

$$A_{stage,fb} = |G_{M,eff} \cdot \frac{Z_0}{2}| \tag{2.1}$$

where  $G_{M,eff}$  and  $Z_0$  are the effective transconductance and the characteristic impedance of the transmission lines, respectively. The effective transconductance,  $G_{M,eff}$ , can be derived when the output is shorted and the short-circuit output current,  $i_{sc}$ , is calculated, as illustrated in Fig. 2.4(a). The effective transconductance  $G_{M,eff}$  is then

$$G_{M,eff} = \frac{i_{sc}}{Mv_{in}/2} = \frac{i_{sc}}{v_X} \cdot \frac{v_X}{Mv_{in}/2} = G_{M2} \cdot A_{v1,fb}$$

(2.2)

where  $G_{M2}$  is the transconductance of transistor  $Q_2$ , and  $A_{v1,fb}$  is the gain of the common emitter transistor  $Q_1$  with the feedback network. The transconductance  $G_{M2}$  is given by

$$G_{M2} = \frac{g_{m2}C_b + sC_{bc2}(C_{be2} + g_{m2}r_{b2}C_b)}{(C_b + C_{be2}) + sC_{be2}C_br_{b2}}$$

(2.3)

with s as the complex frequency variable in Laplace transform. Assuming that  $C_{fb}$  is an ideal dc block  $(C_{fb} = \infty fF)$ , the gain  $A_{v1,fb}$  can be deduced in (2.4) at the bottom of the page, where  $Z_x$  is the impedance looking into the emitter terminal of transistor  $Q_2$ , as shown in Fig. 2.4(a).  $Z_{cb}$  is the equivalent load seen by common emitter transistor  $Q_1$  at node X. In other words,  $Z_{cb}$  is equivalent to  $Z_x$  in parallel with  $C_{o1}$  and  $C_{shunt}$  as shown in Fig. 2.4(b). The impedances  $Z_x$  and  $Z_{cb}$  are frequency-dependent and given by

$$Z_{x} \approx \frac{(C_{b} + C_{be2}) + s \cdot r_{b2}C_{b}C_{be2}}{(g_{m2} + sC_{be2})(C_{b} + s \cdot r_{b2}C_{b}C_{bc2})}$$

(2.5)

$$Z_{cb} = Z_x || \frac{1}{s(C_{ca} + C_{chyrat})}.$$

(2.6)

Although the impedance  $Z_x$  and  $Z_{cb}$  vary with frequency; they are not a strong function of frequency. The poles and zeroes in (2.5) and (2.6) locate at very high frequencies and, therefore, are non-dominant factors.

From (2.1)-(2.6), the simplified voltage gain of a DA stage employing the proposed feedback topology is given by (2.7), neglecting the higher-order products of the capacitances. Note that the coefficient M is valid for most of the passband. By letting  $L_{fb} \to \infty$  and  $C_{shunt} \to 0$ , the voltage gain of a conventional double-stacked HBT single-stage DA is shown in (2.8). The significant differences between the proposed feedback technique in (2.7) and the conventional structure in (2.8) can be observed as follows:

- 1. Since  $L_{fb}C_{bc1}$  is much smaller than  $g_{m1}L_{fb}$ , the dominant zero in (2.7) of the proposed feedback DA is now introduced at  $-1/(g_{m1}L_{fb})$ , which indicates a bandpass structure. Likewise, the zero of the conventional DA is at  $g_{m1}/C_{bc1}$  in (2.8). Clearly, inductor  $L_{fb}$  neutralizes feedback capacitor  $C_{bc1}$  in the proposed design.

- 2. The lower frequency pole of the conventional DA at  $-1/(C_{be1}Z_s)$  in (2.8) moves up and interacts with the feedback inductor  $L_{fb}$  forming a dominant conjugate pole pair, which results in gain peaking at the lower bandpass frequency edge.

- 3. The high-frequency pole at  $-1/((C_{bc1} + C_{o1})Z_x)$  in (2.8) is shifted to a lower frequency by  $C_{shunt}$ , which also interacts with  $L_{fb}$  and the inductive interconnection line between the two transistors. This coupling effect leads to gain improvement at high frequency.

As a result, the proposed feedback technique provides a bandpass characteristic with a gain enhancement for the entire passband. In the following subsections, the bandpass cut-off frequencies are derived and validated. In addition, (2.7) and (2.8) are verified with simulations.

#### 2.2 Bandpass Cut-off Frequencies and Transmission Zero

The lower cut-off frequency of the feedback structure is determined by the peaking frequency between feedback inductor  $L_{fb}$  and input capacitance  $C_{be1}$  of transistor  $Q_I$ , as described in point 2 in the previous subsection. The exact peaking frequency is complicated to quantify because of various coupling

$$A_{v1,fb} \approx \frac{M \cdot \left(-s^2 L_{fb} C_{bc1} + g_{m1} L_{fb} s + 1\right) \cdot Z_x}{2\left(s^2 C_{be1} L_{fb} Z_s + s\left(L_{fb} + C_{be1} Z_s r_{b1} + C_{be1} Z_s Z_{cb}\right) + Z_s\right) (1 + s\left(C_{o1} + C_{bc1} + C_{shunt}\right) Z_x)}$$

(2.4)

$A_{stage,fb} \approx$

$$A_{stage,fb} \approx \frac{M \cdot [g_{m2}C_b + sC_{bc2}(C_{be2} + g_{m2}r_{b2}C_b)](-s^2L_{fb}C_{bc1} + g_{m1}L_{fb}s + 1)}{2(g_{m2} + sC_{be2})(C_b + sr_{b2}C_bC_{bc2})(s^2C_{be1}L_{fb}Z_s + s(L_{fb} + C_{be1}Z_sr_{b1} + C_{be1}Z_sZ_{cb}) + Z_s)(1 + s(C_{o1} + C_{bc1} + C_{shunt}(2.7))} \cdot \frac{Z_o}{2}$$

$$A_{stage,conv} = \frac{M \cdot [g_{m2}C_b + sC_{bc2}(C_{be2} + g_{m2}r_{b2}C_b)](g_{m1} - sC_{bc1})}{2(g_{m2} + sC_{be2})(C_b + sr_{b2}C_bC_{bc2})(1 + sC_{be1}Z_s)(1 + s(C_{bc1} + C_{o1})Z_x)} \cdot \frac{Z_o}{2}$$

(2.8)

factors. However, an elegant expression of the low frequency,  $f_{low}$ , at which the peaking occurs, can be derived from the Miller theorem for  $L_{fb}$  as

$$f_{low} = \frac{1}{2\pi \sqrt{\frac{L_{fb}}{1 + |A_{v1}|} C_{be1}}}$$

(2.9)

where  $A_{v1}$  is the low-frequency voltage gain from the base to the collector of transistor  $Q_I$  without the feedback inductor. The peaking magnitude depends on the damping term  $(L_{fb} + C_{be1}Z_sr_{b1} + C_{be1}Z_sZ_{cb})$  in (2.7), as well as the resistive loss of  $L_{fb}$ . The upper cut-off frequency,  $f_{high}$ , is limited by the process capability. The proposed inductive feedback technique also improves the gain at the high frequency of the passband.

The gain peaking mechanism at the upper band is similar to the peaking inductor technique [5], [7], [8], [11], [18], [24]. If  $C_{shunt}$  is too big, the pole described in point 3 above will become dominant, thereby reducing the upper cut-off frequency. The values of  $C_b$  and  $C_{shunt}$  will determine the impedance looking into the base of the transistor  $Q_2$ . Therefore, the two design parameters need to be chosen carefully from (7) and verified by simulations to ensure both gain enhancement and unconditional stability. Furthermore,  $C_{shunt}$  shifts the pole in (7) to lower frequency and, at the same time, interacts with the feedback inductor, which might cause degradation in the stability of the feedback DA compared to the conventional DA. A transmission zero can be achieved at the series resonant frequency of  $C_{fb}$  and  $C_{fb}$ .

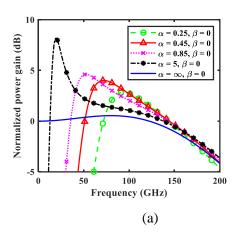

Fig. 2.5 shows the normalized gain of single-stage DA from (2.7) and (2.8) with different values of  $L_{fb}$  and  $C_{shunt}$ , in which  $\alpha$  and  $\beta$  are normalized feedback parameters. The parameter  $\alpha$  is defined as the ratio of  $L_{fb}$  in pH over  $C_{be1}$  in fF or  $\alpha = L_{fb}/C_{be1}$ . The dimensionless parameter  $\beta$  is the capacitance ratio,  $\beta = C_{shunt}/C_{o1}$ . The calculation is based on the extracted small-signal parameters from the InP transistor model. The ideal calculated analytical results do not consider the resistive losses of the DA transmission lines, and losses contributed by the devices, nor losses from the feedback inductor itself.

Fig. 2.5. Normalized voltage gain using analytical equation calculations (7), (8): (a) varying  $\alpha$  with  $\beta = 0$ , and (b) varying  $\alpha$  with  $\beta = 3$ , where  $\alpha = L_{fb}/C_{be1}$  and  $\beta = C_{shunt}/C_{o1}$ .

Fig. 2.5(a) shows the behavior of the gain under the effect of  $L_{fb}$  alone, that is  $\alpha > 0$  and  $\beta = 0$ . The conventional low-pass topology can be modeled by  $\alpha = \infty$  and  $\beta = 0$ . The smaller the inductance, the lower gain enhancement there would be since the inductor behaves as a low impedance circuit. By adding both the feedback inductor  $L_{fb}$  and the shunt capacitor  $C_{shunt}$ , the gain of the DA can be improved over the entire passband, as shown in Fig. 2.5(b). An overlay of  $\alpha = 0.45$  and  $\beta = 0$  is shown in Fig. 2.5(b) to highlight the effect of  $L_{fb}$  and  $C_{shunt}$  to the DA's gain.

The value of  $C_{shunt}$  should be large enough to achieve uniform gain enhancement while maintaining the maximum operating frequency. From Fig. 2.5(a), it demonstrates that high peaking can be achieved with large  $\alpha$  or  $L_{fb}$ . However, to maintain the gain flatness over the bandwidth, larger  $\alpha$  or  $L_{fb}$  requires increasing  $C_{shunt}$  or  $\beta$ . At the same time, large  $C_{shunt}$  or  $\beta$  will decrease the higher cut-off frequency of the DA. Therefore, optimal  $\alpha$  and  $\beta$  can be chosen to maximize the bandwidth while simultaneously obtaining gain flatness.

Fig. 2.6. (a) Simulation of the maximum available gain of a unit gain cell and (b) simulation and analytical solutions (7), (8) of  $S_{21}$  of a six-stage DA with and without feedback. The feedback network is  $L_{fb}$ = 140 pH,  $C_{shunt}$ = 20 fF, and  $C_{fb}$  = 0.2 pF.

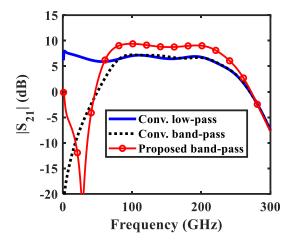

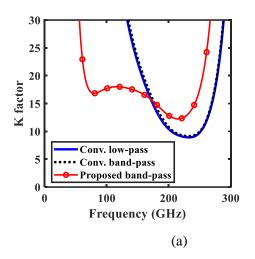

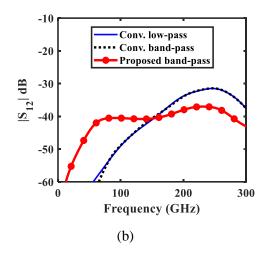

Fig. 2.7.  $S_{21}$  simulation of three six-stage DAs in a conventional low-pass, conventional bandpass with shunt inductors at input and output line, and the proposed bandpass structure.

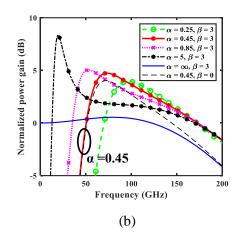

#### 2.3 The DA with the Proposed Feedback Technique

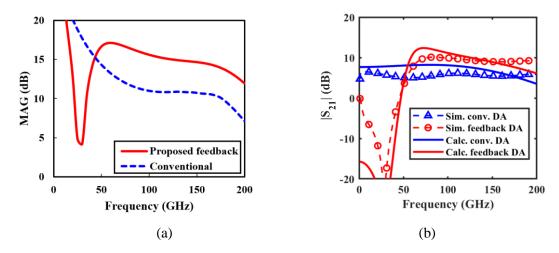

By neglecting all the losses due to the input and output transmission lines, the ideal total voltage gain of an N-stage DA exploiting the proposed technique can be calculated by factoring N into (2.7). Fig. 2.6(a) illustrates the simulated maximum available gain (MAG) of a unit gain cell with and without the feedback network. Uniform gain enhancement of approximately 5 dB can be observed in our design frequency band from 60 to 150 GHz. Fig. 2.6(b) compares the calculated power gain based on (2.7) and (2.8) in a 50  $\Omega$  system and the simulated  $S_{2I}$  using the actual transistor model and lumped components of a six-stage DA (N = 6) with and without the proposed feedback technique.

The series input capacitor to the gain stage,  $C_s$ , is chosen to be 20 fF. Inductances  $L_b$  and  $L_c$  provide the characteristic impedance and phase synchronization. The feedback capacitor,  $C_{fb}$ , is valued at 0.2 pF. The value of  $L_{fb}$  =140 pH is calculated using (9) to peak at 70 GHz as the lower edge of W-band, and the value of  $C_{shunt}$  = 20 fF is chosen to achieve a flat gain response without sacrificing the upper cut-off frequency. A good agreement is obtained between the simulation and the analytical solution as described by (2.7) and (2.8) as shown in Fig. 2.6(b). The difference in magnitude is due to the uncaptured losses from multiple stages and devices.

Fig. 2.8. (a) Stability factor, and (b) reverse isolation  $S_{12}$  of the six-stage conventional low-pass, conventional bandpass, and the proposed feedback DA.

Fig. 2.7 shows the  $S_{21}$  simulations of the conventional low-pass DA, conventional bandpass DA with shunt inductors at the input and output, and the proposed six-stage DA using the gain cell in Fig. 2.3. The simulations indicate that the feedback DA provides gain improvement for the entire passband. Previously in section 2.1,  $C_{fb}$  is assumed to be infinite and acts as a dc block. However, in practice, the value of  $C_{fb}$  can determine a transmission zero at the resonant frequency between  $C_{fb}$  and  $L_{fb}$ , as shown in Fig. 2.7. The presence of a zero will increase the roll-off of  $S_{21}$  at the low-frequency edge. In addition,  $C_{fb}$  will affect the peaking frequency and magnitude.

Fig. 2.8(a) shows the simulation of the stability factor of the conventional low-pass, conventional bandpass, and the feedback bandpass DAs. The proposed feedback technique introduces a negative feedback path, which is a stabilizer for the DA at high frequency compared to its counterparts. Fig. 2.8(b) presents the simulated reverse isolation  $S_{12}$  of the three amplifiers. As predicted, the reverse isolation of the feedback DA shows improvements compared to the conventional designs. The conventional low-pass and bandpass structures share similarities in Fig. 2.8(a) and (b) since the active components are identical, and the input/output transmission line remains the same characteristic impedance.

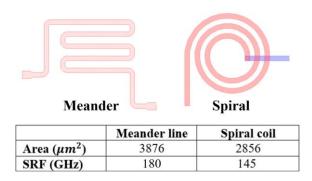

Fig. 2.9. Comparison between a meander line and a spiral inductor for the inductance of 150 pH.

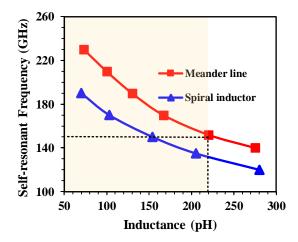

Fig. 2.10. Simulated self-resonant frequency of the meander line and the spiral inductor with respect to the inductance.

#### 2.4 Circuit design and implementation

#### 2.4.1 The Inductive Feedback Network

In this subsection, we present the study and design of the feedback network to maximize the peaking amplitude while preserving the upper cut-off frequency. In particular, the feedback inductor is realized with a meander transmission line for a high self-resonant frequency (SRF) given layout constraints. The shunt capacitor,  $C_{shunt}$ , is absorbed into the feedback inductor parasitic, avoiding an additional Metal-Insulator-Metal (MIM) capacitor. The inductors are simulated in an InP process using the Keysight Advanced Design System (ADS) Momentum Electromagnetic (EM) full-wave simulator. Test structures and customized calibration kits are fabricated to compare with the simulated results. The EM simulation

setups, including port excitation configurations, meshing, and convergence conditions, are validated with the measurement of different test structures.

Fig. 2.9 shows the comparison of two typical implementations of an inductor using a meander transmission line and a spiral coil for the same inductance of 150 pH. The most important aspect of the feedback inductor for this extremely wideband application is the self-resonant frequency (SRF). If this frequency falls within the band of interest, the benefits of the feedback network will be eradicated. Fig. 2.10 shows the simulated SRF with respect to the inductance of the meander line inductor and the spiral inductor. The higher self-resonant frequency in a broad range of inductance makes the meander line inductor more suitable for our wideband implementations.

In this application, the passband extends up to 150 GHz; hence, according to Fig. 2.10 in the shaded area, the maximum allowable inductance from the meander line is approximately 220 pH. This range allows some flexibility in designing the feedback inductor. To achieve gain boosting at 70 GHz, the calculated inductance using (2.9) gives a value of 100 pH with  $C_{fb} = \infty$  fF. However, due to the size limitation and layout consideration, the feedback capacitor  $C_{fb}$  is selected to be 200 fF, which requires the inductance to be adjusted to 140 pH to achieve the same peaking frequency. The transmission zero is predicted by the resonant frequency of  $L_{fb}$  and  $C_{fb}$  at 30 GHz.

The shunt capacitance,  $C_{shunt}$ , is found to be approximately 20 fF to achieve a flat gain while maintaining the required upper frequency. This small capacitance can be absorbed to the feedback inductor's parasitic capacitance  $C_{par}$  in the  $\pi$ -model, as shown in Fig. 2.11(a). Fig. 2.11(b) illustrates the fabricated test structure of the feedback inductor-capacitor network with two Ground-Signal-Ground (GSG) probe pads and 50  $\Omega$  feed lines for characterization. The calculated and extracted parameters from the measurement at 70 GHz are shown in Fig. 2.11(b). Since the layout of the feedback inductor is compact, the proposed technique is useful to improve the amplifier gain performance.

#### 2.4.2 The Band-pass Gain Enhanced Distributed Amplifier

**De-embedded ports**

| Parameters  | Calculated    | Measurement   |

|-------------|---------------|---------------|

| $L_{fb}$    | 140 <i>pH</i> | 190 <i>pH</i> |

| $C_{fb}$    | 200 <i>fF</i> | 272 <i>fF</i> |

| $C_{shunt}$ | 20 <i>fF</i>  | 24 <i>fF</i>  |

(b)

Fig. 2.11. (a) Feedback network layout and inductor pi-model and (b) inductor-capacitor feedback network test structure and extracted data compared to theoretical calculations.

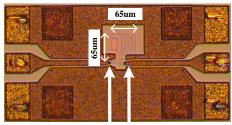

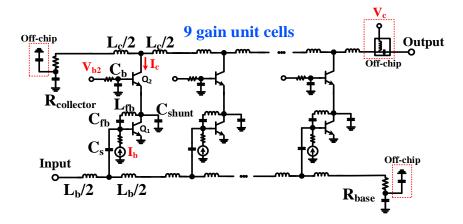

To verify the concept, two distributed amplifiers are designed and fabricated in an InP HBT process [14], [24], [41], [42]. This process offers a transition frequency  $f_T$  of 290 GHz and a maximum frequency  $f_{max}$  of 390 GHz. The first prototype is the conventional DA with the coupling ratio optimized to achieve the maximum bandwidth while maintaining good input and output matching conditions. The second prototype is the first prototype with the proposed inductive feedback network added. The complete schematic diagram of the feedback DA is shown in Fig. 2.12. Both DAs employ nine stages to meet the gain requirement. Based on our simulations, adding more stages after the 9<sup>th</sup> gain cell does not provide gain enhancement due to losses of the artificial transmission lines.

Fig. 2.12. Complete schematic diagram of the nine-stage feedback DA.

Fig. 2.13. Chip photograph of (a) proposed inductive feedback bandpass DA and (b) conventional low-pass DA. Both chips have a size of 1.6 mm x 0.6 mm.

Each gain unit cell employs a stacked-HBT configuration in which both the common-emitter transistor and the common-base transistor have 10- $\mu$ m emitter length. The stacked-HBT structure not only increases the voltage swing but also helps reduce the input parasitic capacitance due to the Miller effect [37] and the output conductance of the gain cell to minimize the loss of the output line [34]-[36]. Therefore, the DA can achieve higher output power and gain-bandwidth product as compared to the conventional single common emitter transistor topology. Fig. 2.13 presents the chip photos of the fabricated prototypes. Both amplifiers have a chip size of  $1.6 \times 0.6 \text{ mm}^2$ , including all pads. The bases of the two transistors are

Table 2.1. Design Parameters of The Proposed Feedback DA

| Design parameters      | Feedback DA     |                                     |

|------------------------|-----------------|-------------------------------------|

| Gain unit cell         | Topology        | Feedback stacked-HBT                |

| Gain unit cen          | $C_b$           | 128 fF                              |

| Emitter length         | $L_e$           | $10  \mu m$ (both $Q_1$ and $Q_2$ ) |

|                        | $I_b$           | 250 μΑ                              |

| Bias conditions        | $C_b$ $L_e$     | 4 V                                 |

| Dias conditions        | $V_{b2}$        | 1.8 V                               |

|                        | $I_c$           | 12.3 mA                             |

| Input series capacitor | $C_s$           | 20 fF                               |

| Inductances            | $L_b$           | 38 pH                               |

| Inductances            | $L_c$           | 77 pH                               |

| Terminations           | $R_{base}$      | 65 Ω                                |

| Terminations           | $R_{collector}$ | 55 Ω                                |

|                        | ¥               | 190 pH                              |

| Feedback network       | $C_{fb}$        | 272 fF                              |

|                        | $C_{shunt}$     | 24 fF                               |

biased through a 1 k $\Omega$  resistor. The circuit operates at 4 V collector supply,  $V_c$ , and 12.3 mA collector current,  $I_c$ , each cell at the small signal condition. The common emitter device,  $Q_1$ , is biased in class A with a base current of  $I_b$ = 250  $\mu$ A per gain cell.

The feedback network is carefully designed, as described in the previous subsection. The interconnection length between the two devices is minimized to reduce any peaking effects other than those from our proposed network. Collector inductors,  $L_c$ , are realized using microstrip lines. The base inductors,  $L_b$ , are implemented using a coplanar waveguide structure to reduce losses and create a better grounding for the devices. All the passive components are fully simulated using the Keysight ADS Momentum.

In our proposed design, the input and output planar transmission lines are tapered to improve output power and efficiency. In particular, the width of the output microstrip line is 10 µm at the first stage and gradually increases to 17 µm at the output port. The input coplanar waveguide width decreases from 15 µm at the input port to 8 µm toward the termination. Thanks to a low-loss dielectric substrate offered by InP processes [43], [44], the simulated conductor loss of the proposed output microstrip line is about 0.15 dB/mm at 110 GHz. Not only the low output conductance provided by the InP HBT device [45] and the feedback stacked-HBT configuration, but the low conductor loss of the InP microstrip lines also contribute to the low loss per stage of the output artificial transmission lines [36].

Our simulated loss per distributed gain stage of the output transmission line is approximately 0.07 dB/stage at 110 GHz. The low loss per stage of the output line allows for the power from each stage to arrive at the load with minimal attenuations. Furthermore, the tapered output line maximizes the output signal traveling toward the output load, therefore, increases the output power. Compared to an identical DA with a uniform output microstrip line, the simulated output power using the proposed tapered line increases by 17 %.

Based on the output line loss per stage and the tapered line discussed above [36], the total output power can be estimated by superposing the power arrives at the load contributed by each stage after subtracting the loss on the signal path. The calculated output power for the proposed DA is approximately 98.8 mW at 110 GHz. With a dissipated power of 442 mW, the power added efficiency is in the order of 17.8 %. Overall, the low output conductance HBT device, the stacked-HBT configuration with the feedback network, the low-loss microstrip line, and the tapered output transmission lines help the proposed DA achieving high power and efficiency while maintaining good input and output matching conditions.

In our proposed design, the values of the two termination resistors are determined as 55  $\Omega$  and 65  $\Omega$  for the collector line and the base line, respectively. The termination networks, which include the resistors  $R_{collector}$  and  $R_{base}$  in series with a small capacitor, are designed on-chip to achieve good input and output return losses, as well as a flat gain response over a wide frequency range up to 180 GHz. Each network is bond-wired to a 700 pF off-chip shunt bypass capacitor to eliminate any low-frequency signals. The collector of the DA is biased through an external bias-tee. Both input and output are connected to 100  $\mu$ m pitch GSG probe pads. The design parameters of the feedback DA are listed in Table 2.1. The conventional DA has an identical set of parameters with the feedback network in Fig. 2.11(a) removed for comparison.

#### 2.5 Measurement results

#### 2.5.1 Small-signal Measurements

Fig. 2.14. Measured (solid) and simulated (dashed) S-parameters of (a) the proposed feedback DA and (b) the conventional low-pass DA.

Fig. 2.15. Comparison between feedback DA and conventional DA for (a) measured gain,  $S_{21}$ , and (b) measured stability factors k and  $|\Delta|$ . The solid red line is the proposed feedback DA, and the dashed blue line is the conventional DA.

Fig. 2.14(a) and 2.14(b) present the frequency response of the proposed feedback and the conventional DA, respectively. The dashed and solid lines are simulated and measured results, respectively. The small-signal measurements are conducted in different frequency bands: 0 - 67 GHz (1.85 mm coaxial cable), 67 - 90 GHz (WR-10 waveguide), 90 - 140 GHz (WR-8 waveguide), and 140 - 170 GHz (WR-5

Fig. 2.16. (a) Measured group delay (ps) and relative phase (degree) of  $S_{21}$ , and (b) noise figure of the feedback DA.

waveguide) using the PNA-X network analyzer and appropriate frequency extenders. The gain discontinuities are less than 0.7 dB at 90 GHz and 1 dB at 140 GHz for both DAs.

The proposed gain boosting feedback DA exhibits an average gain of 10.5 dB with a positive gain slope. The 3-dB bandwidth extends from 60 GHz up to 145 GHz, making the gain-bandwidth product of 285 GHz. The DA achieves input and output return loss better than -10 dB up to 110 GHz. The transmission zero appears at 27 GHz. The conventional DA demonstrates a 6.5 dB average gain with a 3-dB bandwidth from 15 to 148 GHz. The input and output return loss maintain below -10 dB up to 120 GHz. The measurements correlate well with the simulated results for both DAs. Due to the large device size and a wide bandwidth close to  $f_T$ , our conventional DA has lower gain. Therefore, the feedback network is developed to enhance the gain while still achieving high output power and high-frequency operation.

Fig. 2.15(a) illustrates the measured gain  $S_{2I}$  of the feedback DA and the conventional low-pass DA. An average gain improvement of 4 dB is achieved in the feedback DA compared to the conventional DA from 64 to 142 GHz. Both distributed amplifiers consume 440 mW. Fig. 2.15(b) exhibits the measured stability factors k and  $|\Delta|$  of the DAs up to 180 GHz. Both DAs fulfill the Rollet proviso and exhibit k > 1 and  $|\Delta| < 1$  at all frequencies. Therefore, both DAs are unconditionally stable. It is noteworthy that the k-

Fig. 2.17. W-band power measurement test setup.

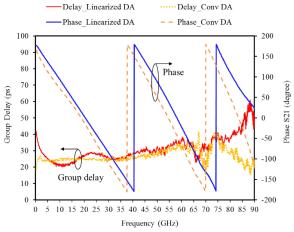

factor of the feedback DA is larger than that of the conventional DA at above 80 GHz. Fig. 2.16(a) depicts the measured group delay in pico-second (ps) and the relative phase of  $S_{21}$  (degree) of the feedback DA. The proposed feedback DA achieves a linear phase with respect to frequency up to 145 GHz with a maximum deviation of  $\pm$  20 ps within the passband.

The noise measurement is performed at V-band  $(60-70 \, \mathrm{GHz})$  and W-band  $(75-110 \, \mathrm{GHz})$  by adapting the direct method [28]. The device under test (DUT) is terminated at the input. The output noise contributed by the DUT is observed using a spectrum analyzer. The noise figure of the feedback DA is then extracted after the overall system loss is calibrated out. Fig. 2.16(b) illustrates the simulated and measured noise figure of the feedback DA. The minimum noise figure achievable is 10.5 dB at 65 GHz.

### 2.5.2 Large-signal Measurements

Fig. 2.17 illustrates the measurement setup for the W-band power sweep. In this approach, a W-band signal is generated using a PNA-X network analyzer and multiplied by a WR-10 frequency extender from Keysight Technologies. The signal is amplified by a commercially available connectorized waveguide

Fig. 2.18. Measured and simulated output power, gain, and PAE of the proposed feedback DA at (a) 85 GHz, and (b) 110 GHz. The solid line and dashed line are measurement and simulation, respectively.

Fig. 2.19.  $P_{sat}$  and  $P_{IdB}$  over the frequency of the feedback DA. The solid line and dashed lines are measurement and simulation, respectively.

W-band power amplifier from SAGE Millimeter. The input signal to the WR-10 S-bend is calibrated using the WR-10 power sensor Agilent W8486A and the power meter Keysight E4417A EPM-P. The loss of the probe and S-bend combination is then de-embedded using data from the thru-measurement of the back-to-back configuration. The input and output power from the DUT can be obtained. The dc current is recorded

Table 2.2. Comparison to State-of-The-Art Wideband Amplifiers

| Reference       | Technology | Gain (dB) | BW<br>(GHz) | $f_T/f_{max}$ (GHz) | $P_{sat}(dBm)^*$ | PAE (%)     | $\frac{P_{dc}}{\left(mW\right)^{**}}$ | Die size (mm²) |

|-----------------|------------|-----------|-------------|---------------------|------------------|-------------|---------------------------------------|----------------|

| [46]            | InP        | 20.7      | 71-95       | 400/700             | 21.2@81GHz       | 40@81GHz    | 433                                   | 0.47           |

| [46]            | InP        | 17.8      | 96-122      | 400/700             | 20.2@110GHz      | 22.5@110GHz | 442                                   | 0.38           |

| [47]            | InP        | 10        | 38-220      | 375/650             | 9.2 @77GHz       | 5@77GHz     | 105                                   | 0.33           |

| [48]            | InP        | 10        | 40-185      | 360/400             | 10 @160GHz       | -           | 96                                    | 1.36           |

| [49]            | InP        | 12        | 31-130      | 360/400             | 11.5<br>@110GHz  | 8@110GHz    | 129                                   | 0.6            |

| [50]            | InP        | 10        | 40-105      | 270/750             | 12@96GHz         | 43@93GHz    | 43                                    | 0.73           |

| [3]             | SiGe       | 20        | 10-170      | 270/450             | 13.5<br>@135GHz  | -           | 560                                   | 0.91           |

| [28]            | SiGe       | 14.5      | 52-142      | -/210               | 1.6 @75GHz       | -           | 103                                   | 0.45           |

| [51]            | SiGe       | 8.5       | dc-135      | 230/300             | 11 @20GHz        | -           | 99                                    | 0.36           |

| [33]            | SiGe       | 12        | 14-105      | 300/-               | 17 @50GHz        | 12.6@50GHz  | 297                                   | 1.51           |

| [40]            | SOI        | 16        | 1.5-103     | 290/250             | 22@15GHz         | 19.5@15GHz  | 890                                   | 0.33           |

| [52]            | SOI        | 13        | 10-82       | 280/270             | 17.2@50GHz       | 17.4@50GHz  | 182                                   | 0.8            |

| [52]            | SOI        | 12.6      | 11-83       | 280/270             | 17.5@50GHz       | 20.2@50GHz  | 182                                   | 0.8            |

| [53]            | GaAs       | 11        | dc-110      | 380/500             | 11 @75GHz        | -           | 425                                   | 1.69           |

| Conventional DA | InP        | 6.5       | 15-148      | 290/390             | 19.5 @20GHz      | 20.1@20GHz  | 440                                   | 0.96           |

| Feedback DA     |            | 10.5      | 60-145      |                     | 20.9 @75GHz      | 19.2@110GHz | 440                                   | 0.96           |

<sup>\*</sup>Maximum reported saturated output power\*\* Small-signal condition

through the high-precision dc supply Agilent 34401A. The large-signal measurement setup is validated by measuring a commercial power amplifier and comparing it with the provided datasheet, which shows consistency across W-band.

Fig. 2.18 presents the large-signal measurement of the proposed feedback DA. The measured and simulated results at 85 GHz, and 110 GHz are shown in Fig. 2.18(a) and (b), respectively. At 85 GHz, the DA attains a saturated power ( $P_{sat}$ ) of 19.8 dBm, a 1-dB compression output power ( $P_{1dB}$ ) of 18.8 dBm, and a maximum power added efficiency (PAE) of 17.3 %. At 110 GHz, the  $P_{sat}$ ,  $P_{1dB}$ , and maximum PAE are 20.2 dBm, 18.6 dBm, and 19.2 %, respectively. The measured results at these frequencies are slightly higher than the simulated ones. This effect might be caused by the conservative modeling of the device.

The input power is driven up to 20 dBm without damaging the device. The output signal of the DA at high input power is observed with the spectrum analyzer. There are no indications of parametric instability.

The measured and simulated 1-dB compression output power,  $P_{IdB}$ , and the saturated power,  $P_{sat}$ , over the frequencies are provided in Fig. 2.19. The maximum achievable  $P_{sat}$  is 20.9 dBm at 75 GHz with the corresponding  $P_{IdB}$  of 18.5 dBm. The minimum  $P_{sat}$  in W-band is 19 dBm, which is coherent with state-of-the-art InP technologies that can offer at W-band and above [46], [54]. Table 2.2 summarizes the performance of state-of-the-art wideband amplifiers in the same frequency range.

#### 2.6 Conclusion