## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Compositional Design of Analog Systems Using Contracts

#### **Permalink**

https://escholarship.org/uc/item/2jj6j47f

#### **Author**

Sun, Xuening

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

#### **Compositional Design of Analog Systems Using Contracts**

by

### Xuening Sun

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Electrical Engineeing and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Alberto Sangiovanni-Vincentelli, Chair Professor Jan Rabaey Professor David Brillinger

Spring 2011

## **Compositional Design of Analog Systems Using Contracts**

Copyright 2011 by Xuening Sun

#### **Abstract**

Compositional Design of Analog Systems Using Contracts

by

#### Xuening Sun

Doctor of Philosophy in Electrical Engineeing and Computer Sciences

University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

This work addresses the problem of assembling analog integrated systems out of pre-designed IP components. Efficient system-level design is increasingly relying on hierarchical design-space exploration, as well as compositional methods, to shorten time-to-market, leverage design re-use, and achieve optimal performances. However, in analog electronic systems, circuit behaviors are so tightly dependent on their interface conditions that accurate system performance estimations based on characterizations of individual stand-alone circuits is a hard task. Since there is no general solution to this problem, analog system integration has traditionally used *ad-hoc* solutions heavily dependent on designers' experience and detailed knowledge of the target application.

A system composition method is proposed that build upon the *analog platform-based design* (APBD) methodology by exploiting assume-guarantee reasoning, *contracts*, to enforce *correct-by-construction* system-level composition. Contracts intuitively capture the thought process of a designer, who aims at *guaranteeing* circuit performance only under specific *assumptions* (e.g. interface loading or dynamic range). Contracts can be broadly classified into two categories: *horizontal* contracts between components of the same abstraction level and *vertical* contracts between a system at level l+1 and the components that make up the system from level l. Horizontal contracts can be used to ensure that correct component behavior by constraining the external environment settings to be within the assumed range. Vertical contracts capture assumptions that system-level designers introduce by leveraging knowledge about the system architecture, which is not available at the component-level. *Contracts* can be naturally incorporated into the APBD design flow to ensure accurate design space explorations and correct design implementations.

The methodology is applied to several case studies to demonstrate the value of our approach. First, an ultra-wide band receiver front-end is composed using horizontal contracts to preserve the correct behavior of pre-designed IP components in composition and to allow design decisions to be reliably made at a higher abstraction level, both key factors to improve designer productivity. In another case study for composition of an analog feedback systems, the Sallen-Key cell, I show the application of both horizontal and vertical contracts so that the performance of a composition of circuit blocks not only preserves component behavior, but also satisfies system specifications

and requirements. Finally, the methodology is applied to the complete design study of the UWB receiver chain for the Intelligent Tire System to demonstrate hierarchical design space exploration using analog contracts. The study shows that given a library of components, an optimized system can be quickly realized through hierarchical construction of subsystems and propagation of contracts. The works featured are seminal to further advancements in bridging the gap between system-level and circuit-level design in the analog/mixed-signal domain.

To my supporting family and friends.

## **Contents**

| Acknowledgements  1 Introduction 1.1 Trends and Challenges 1.2 Thesis Contributions and Organization  2 Background 2.1 Design Tools 2.2 Analog Platform-based Design 2.3 Contract-based Design 3 Analog Composition Using Contracts 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                | Contents  List of Figures |            |                                                                                                              |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|--------------------------------------------------------------------------------------------------------------|--|

| Acknowledgements  1 Introduction 1.1 Trends and Challenges 1.2 Thesis Contributions and Organization  2 Background 2.1 Design Tools 2.2 Analog Platform-based Design 2.3 Contract-based Design 3 Analog Composition Using Contracts 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                |                           |            |                                                                                                              |  |

| 1 Introduction 1.1 Trends and Challenges 1.2 Thesis Contributions and Organization  2 Background 2.1 Design Tools 2.2 Analog Platform-based Design 2.3 Contract-based Design  3 Analog Composition Using Contracts 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts | Li                        | st of T    | Tables vi                                                                                                    |  |

| 1.1 Trends and Challenges 1.2 Thesis Contributions and Organization  2 Background 2.1 Design Tools 2.2 Analog Platform-based Design 2.3 Contract-based Design  3 Analog Composition Using Contracts 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                                                | A                         | know       | vledgements                                                                                                  |  |

| 2.1 Design Tools 2.2 Analog Platform-based Design 2.3 Contract-based Design  3 Analog Composition Using Contracts 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                                                                                                                                  | 1                         | 1.1        | oduction       2         Trends and Challenges       3         Thesis Contributions and Organization       3 |  |

| 3.1 Analog Contracts 3.1.1 Composition 3.1.2 Properties of Composition 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                                                                                                                                                                                                                                                      | 2                         | 2.1<br>2.2 | kground  Design Tools  Analog Platform-based Design  Contract-based Design  13                               |  |

| 3.2 Case Study 3.2.1 UWB RF Components 3.2.2 Contracts 3.2.3 Composition and Optimization 3.3 Results  4 Vertical Propagation of Contracts 4.1 Contract Propagation 4.1.1 Design Flow 4.1.2 Vertical Contracts                                                                                                                                                                                                                                                                                                                           | 3                         |            | Analog Contracts       15         3.1.1 Composition       19                                                 |  |

| 4.1 Contract Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |            | Case Study       23         3.2.1       UWB RF Components       24         3.2.2       Contracts       24    |  |

| 4 L 3 Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                         |            | Contract Propagation                                                                                         |  |

|          | ••• |

|----------|-----|

| CONTENTS | 11  |

| CONTENTS | 11  |

|          |     |

|    |        | 4.1.4    | System Optimization                             | 38 |

|----|--------|----------|-------------------------------------------------|----|

|    | 4.2    | Case S   | tudy                                            | 39 |

|    |        | 4.2.1    | Analog Feedback Systems                         | 39 |

|    |        | 4.2.2    | Sallen-Key Bi-quadratic Cell Composition        |    |

|    |        | 4.2.3    | Component Characterization                      |    |

|    |        | 4.2.4    | Vertical Assumptions                            |    |

|    | 4.3    | Results  | s                                               |    |

| 5  | App    | lication | : UWB Receiver for Intelligent-Tire-System      | 51 |

|    | 5.1    |          | gent Tires                                      | 52 |

|    |        | 5.1.1    | Background: Automotive Safety Systems           |    |

|    |        | 5.1.2    | Intelligent-Tire-System                         |    |

|    | 5.2    | UWB      | Communication System Planning and Specification |    |

|    |        | 5.2.1    | UWB Communication                               |    |

|    |        | 5.2.2    | Tire UWB Channel                                |    |

|    |        | 5.2.3    | Signal Transmission                             |    |

|    | 5.3    | System   | n Construction                                  |    |

|    |        | 5.3.1    | Receiver Specifications                         | 66 |

|    |        | 5.3.2    | Receiver Architecture                           |    |

|    |        | 5.3.3    | Subsystem Construction                          |    |

|    |        | 5.3.4    | System Exploration                              | 81 |

|    | 5.4    | Results  | s                                               | 83 |

| 6  | Con    | clusion  |                                                 | 91 |

|    | 6.1    | Future   | Recommendations                                 | 92 |

| Bi | bliogr | aphy     |                                                 | 95 |

| Bi | bliogr | aphy     |                                                 | 95 |

# **List of Figures**

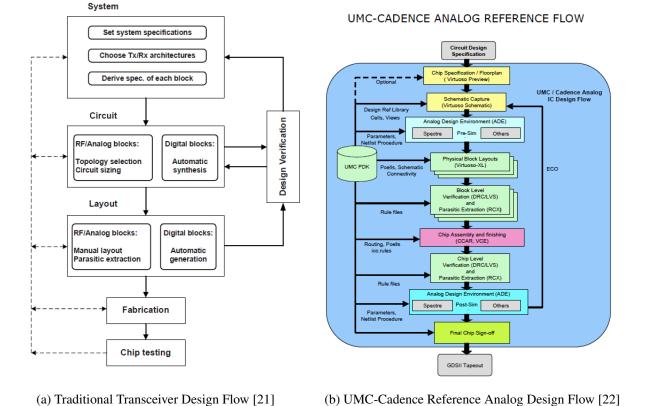

| 2.1 | Reference State-of-the-Art Analog Design Flows                                                                                                                                                                                                                                               | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

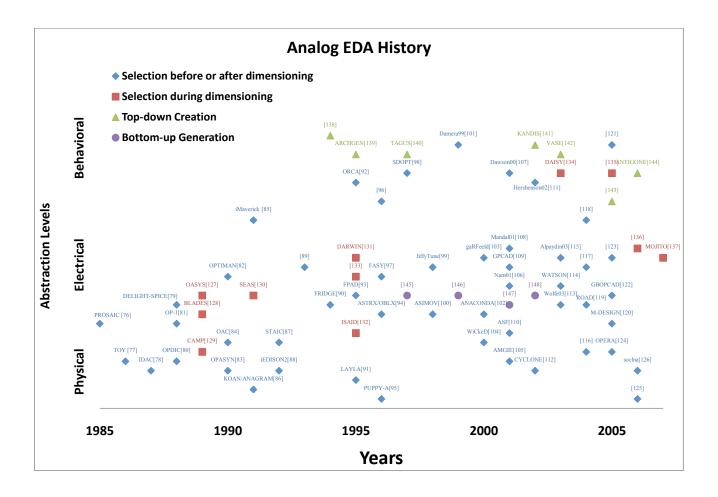

| 2.2 | Review of analog EDA work in the past quarter-century by G. Gielen [1]                                                                                                                                                                                                                       | 9  |

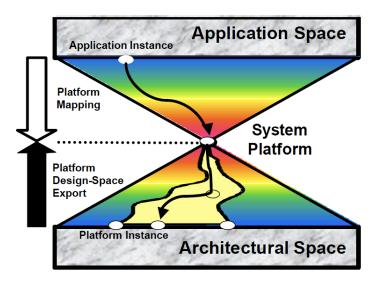

| 2.3 | Each platform stack of PBD features a meeting-in-the-middle of system constraints                                                                                                                                                                                                            |    |

|     | and performance characterizations                                                                                                                                                                                                                                                            | 11 |

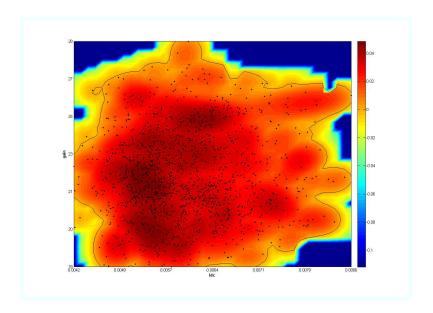

| 2.4 | SVM classifiers help separate feasible and infeasible performance spaces of a com-                                                                                                                                                                                                           |    |

|     | ponent                                                                                                                                                                                                                                                                                       | 12 |

| 2.5 | Platform abstraction process                                                                                                                                                                                                                                                                 | 12 |

| 3.1 | A compose B on shared variables $\lambda$                                                                                                                                                                                                                                                    | 18 |

| 3.2 | Projections of the contracts of $A$ and $B$ onto assumptions and performance guarantees of the shared variables $\lambda$ during composition. Composition can only occur between design instances that simultaneously satisfy assumptions of both compositions of the shared variables $A$ . | 10 |

| 2.2 | nents involved, which is confined to the <i>compatible regions</i> $\mathcal{G}''_{\mathcal{A}}$ and $\mathcal{G}''_{\mathcal{B}}$                                                                                                                                                           | 19 |

| 3.3 | Composition Associativity                                                                                                                                                                                                                                                                    | 22 |

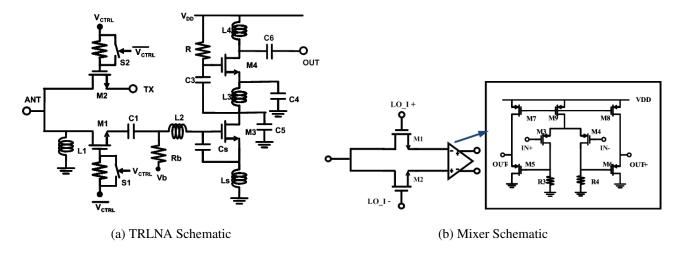

| 3.4 | Circuit Schematic                                                                                                                                                                                                                                                                            |    |

| 3.5 | Circuit Characterization Testbench                                                                                                                                                                                                                                                           | 26 |

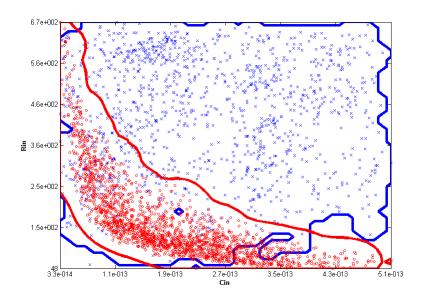

| 3.6 | Intersection of TRLNA RC loading assumptions (blue) and mixer input RC per-                                                                                                                                                                                                                  | •  |

|     | formances (red)                                                                                                                                                                                                                                                                              | 28 |

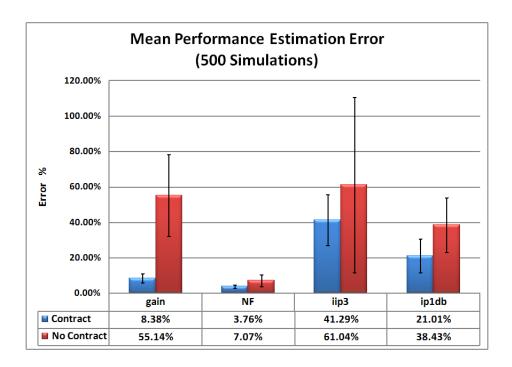

| 3.7 | Contract-based composition yielded lower average estimation error for all performances, as well as a lower standard deviation, as represented by the error bars                                                                                                                              | 31 |

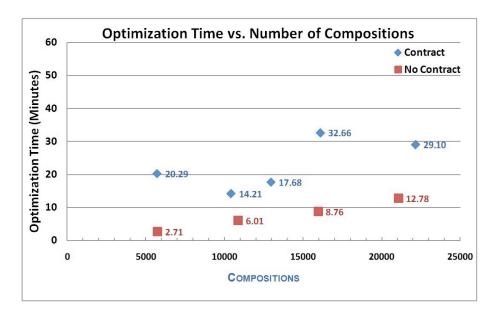

| 3.8 | Optimization runtime comparison for composition with and without contracts                                                                                                                                                                                                                   | 32 |

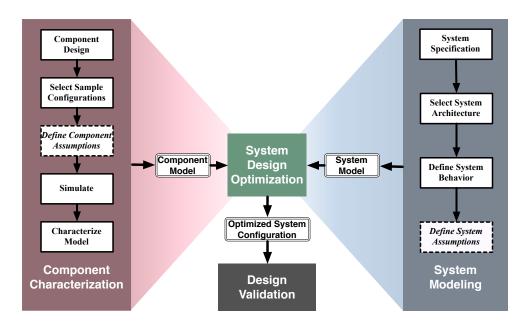

| 4.1 | APBD Design Flow                                                                                                                                                                                                                                                                             |    |

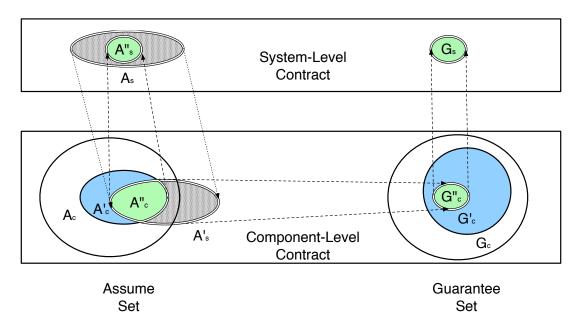

| 4.2 | Vertical Propagation of System-level Contracts                                                                                                                                                                                                                                               |    |

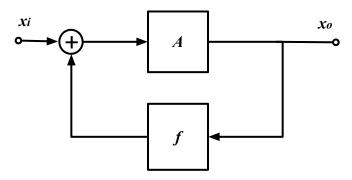

| 4.3 | Ideal Feedback System                                                                                                                                                                                                                                                                        | 40 |

| 4.4 | Real Analog Feedback System                                                                                                                                                                                                                                                                  | 40 |

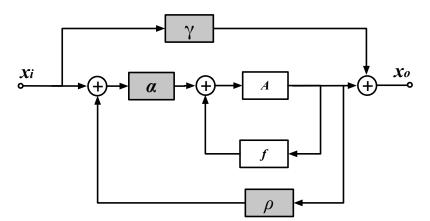

| 4.5 | Shunt-shunt two-port feedback composition                                                                                                                                                                                                                                                    | 41 |

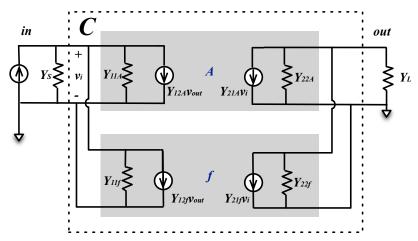

| 4.6 | UWB Direct-conversion receiver system                                                                                                                                                                                                                                                        | 42 |

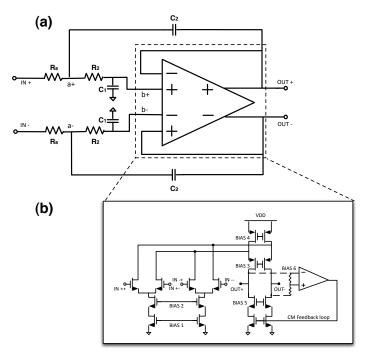

| 4.7 | (a) Differential Ultra-wideband Sallen-Key Low-pass Filter System (b) Differential                                                                                                                                                                                                           |    |

|     | difference amplifier (DDA) transistor-level schematic                                                                                                                                                                                                                                        | 43 |

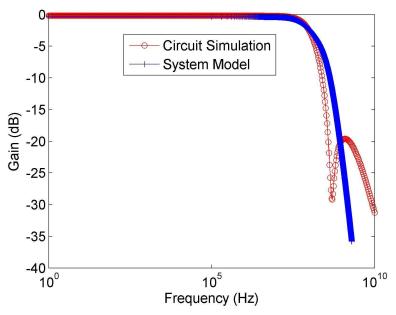

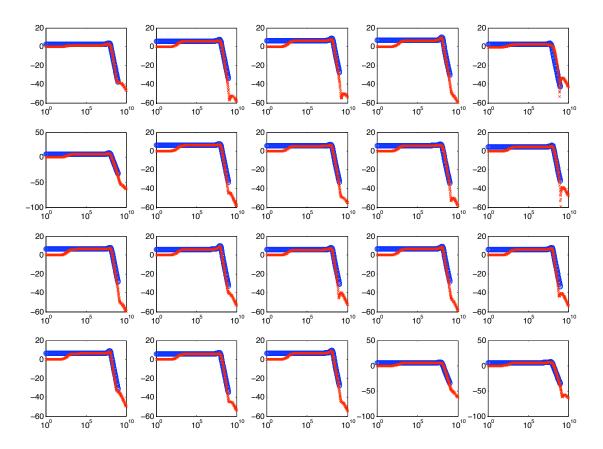

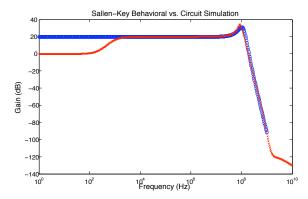

| 4.8 | Comparison of System Model vs. Circuit Simulation for Sallen-Key Filter                                                                                                                                                                                                                      | 48 |

LIST OF FIGURES v

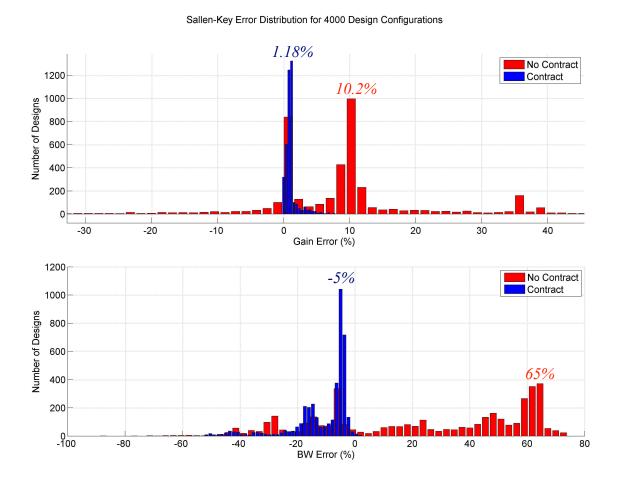

| 4.9  | Error histogram distribution comparing system model to circuit simulation on 4000 contract-based configurations vs 4000 no-contract configurations                     | 49 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

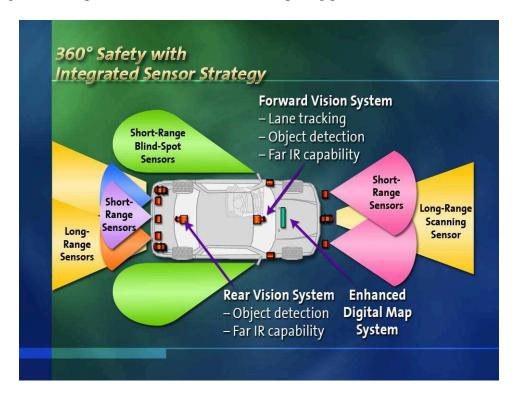

| 5.1  | 360 degree Integrated Safety                                                                                                                                           | 52 |

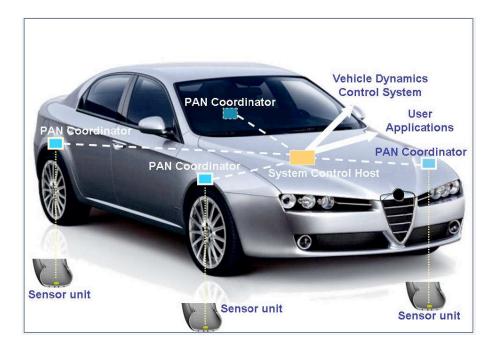

| 5.2  | System architecture                                                                                                                                                    |    |

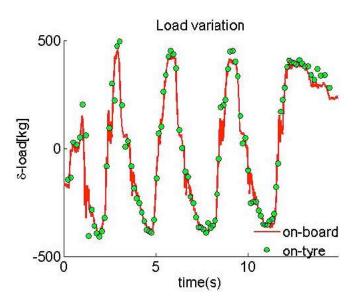

| 5.3  | Load transfer during multiple acceleration-deceleration maneuvers. Circles represent the estimated load transfer with the intelligent tire system while the solid line |    |

|      | is the traditional load estimation method based upon sensors on vehicle                                                                                                |    |

| 5.4  | Anatomy of a tire                                                                                                                                                      |    |

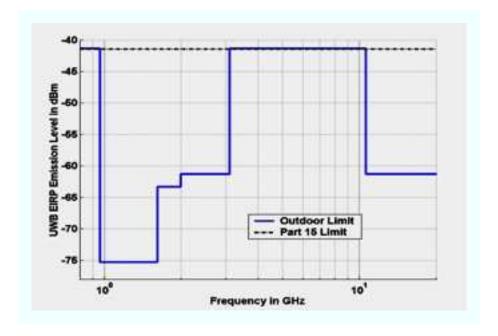

| 5.5  | FCC spectrum mask for UWB signals                                                                                                                                      |    |

| 5.6  | Channel measurement setup                                                                                                                                              |    |

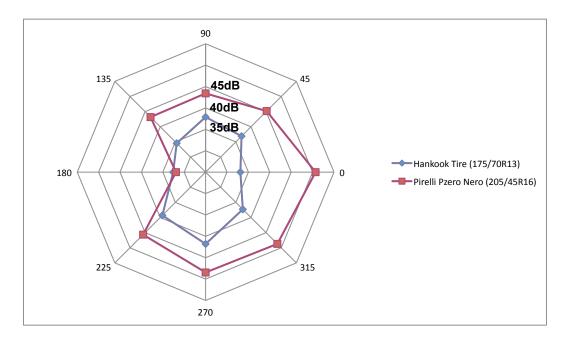

| 5.7  | $\alpha$ for Hankook (blue) and Pirelli (red)                                                                                                                          |    |

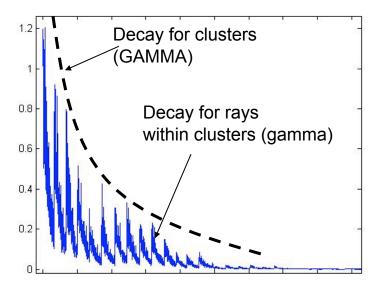

| 5.8  | SV-Model cluster and ray decay                                                                                                                                         | 60 |

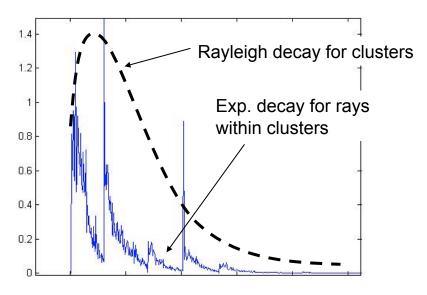

| 5.9  | Rayleigh SV UWB channel model                                                                                                                                          | 61 |

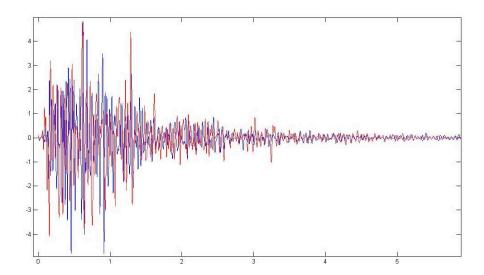

| 5.10 | Impulse response of SV-R model (red) compared to the measured data (blue). The                                                                                         |    |

|      | x-axis is in 10 ns                                                                                                                                                     | 62 |

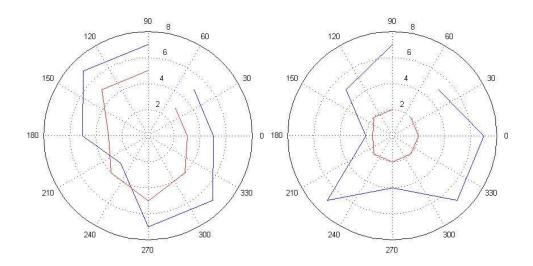

| 5.11 | $\gamma_c$ (outer, blue) and $\gamma_r$ (inner, red) for Hankook (left) and Pirelli (right) in ns                                                                      | 63 |

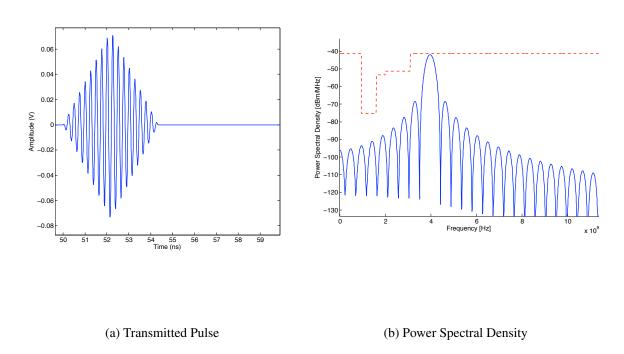

| 5.12 | (a) Triangular sinusoidal pulse with a pulse width of 4.35ns; (b) PSD of transmitted                                                                                   |    |

|      | signal with 500MHz 10-dB bandwidth                                                                                                                                     | 64 |

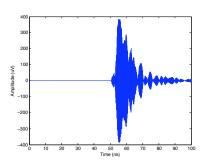

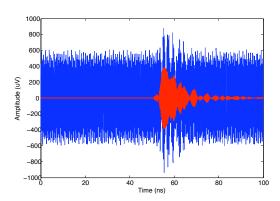

| 5.13 | Received Signal: (a) with attenuation and multipath only; (b) with added narrow-                                                                                       |    |

|      | band interference, with desired signal in red                                                                                                                          | 65 |

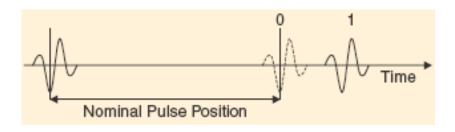

| 5.14 | Binary pulse-position-modulation                                                                                                                                       | 65 |

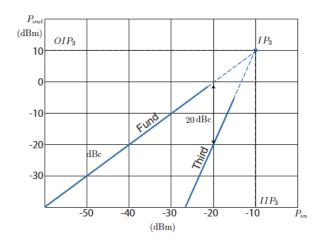

| 5.15 | Third-order Intermodulation with IM3 of 20 dBc at $P_{in}$ of -20 dBm                                                                                                  | 67 |

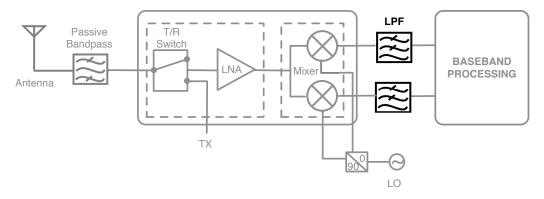

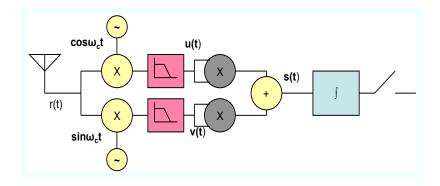

| 5.16 | Direct-conversion energy-detection at base-band receiver for UWB detection                                                                                             | 69 |

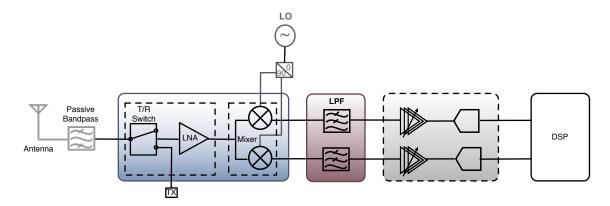

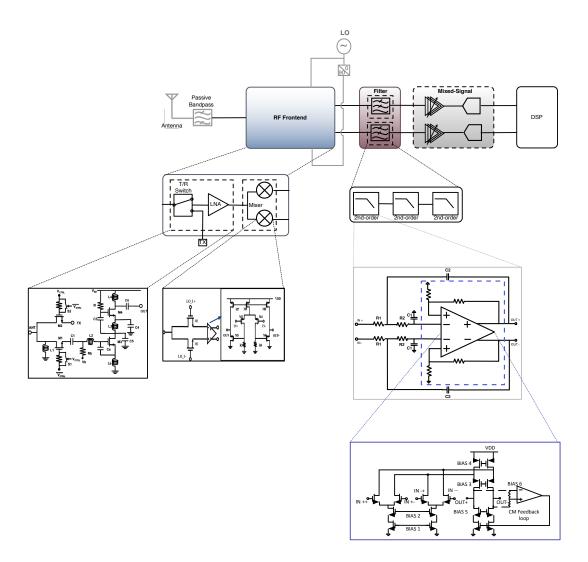

| 5.17 | ITS Receiver Architecture                                                                                                                                              | 69 |

| 5.18 | ITS Receiver Hierarchy                                                                                                                                                 | 71 |

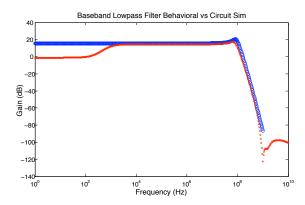

| 5.19 | Comparison of Sallen-Key behavioral model (Blue) and SPICE simulation (Red)                                                                                            |    |

|      | with different designs                                                                                                                                                 | 74 |

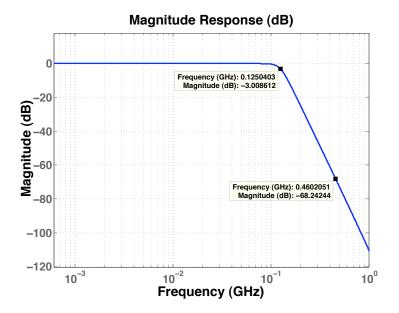

| 5.20 | Comparison of Sallen-Key behavioral model (Blue) and SPICE simulation (Red)                                                                                            |    |

|      | for single design instance                                                                                                                                             | 75 |

| 5.21 | Base-band Filter Mask                                                                                                                                                  | 76 |

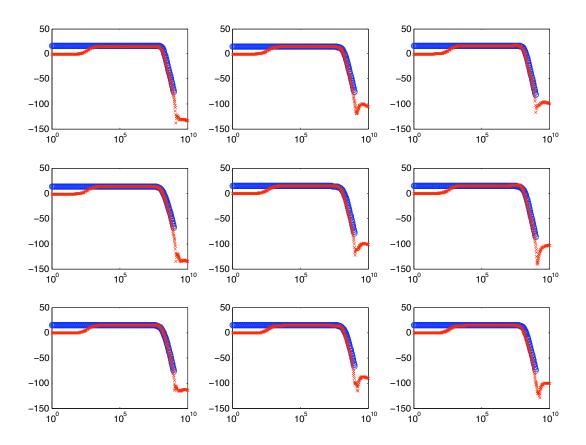

| 5.22 | Comparison of LPF behavioral model (Blue) and SPICE simulation (Red) with                                                                                              |    |

|      | different designs                                                                                                                                                      | 78 |

| 5.23 | Comparison of LPF behavioral model (Blue) and SPICE simulation (Red) for sin-                                                                                          |    |

|      | gle design instance                                                                                                                                                    | 79 |

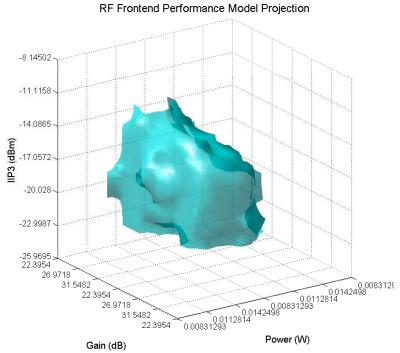

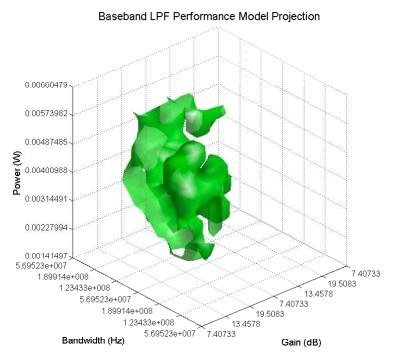

| 5.24 | Projection of RF Front-end AP Component Model                                                                                                                          | 80 |

|      | Projection of LPF AP Component Model                                                                                                                                   | 80 |

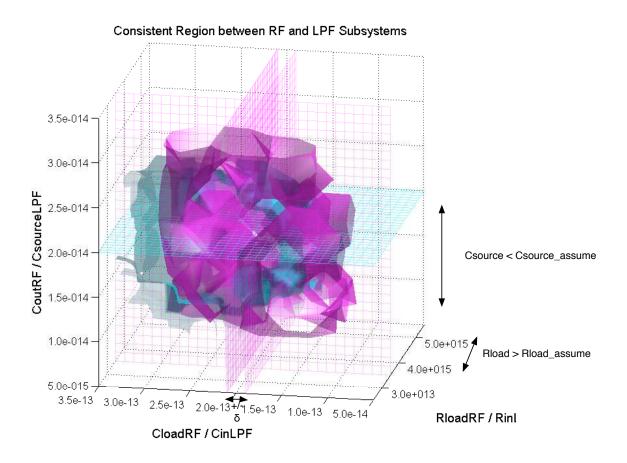

|      | Combined Projections of RF (magenta) and LPF (cyan) AP models onto interface                                                                                           |    |

|      | variables to show potential compatible regions                                                                                                                         | 82 |

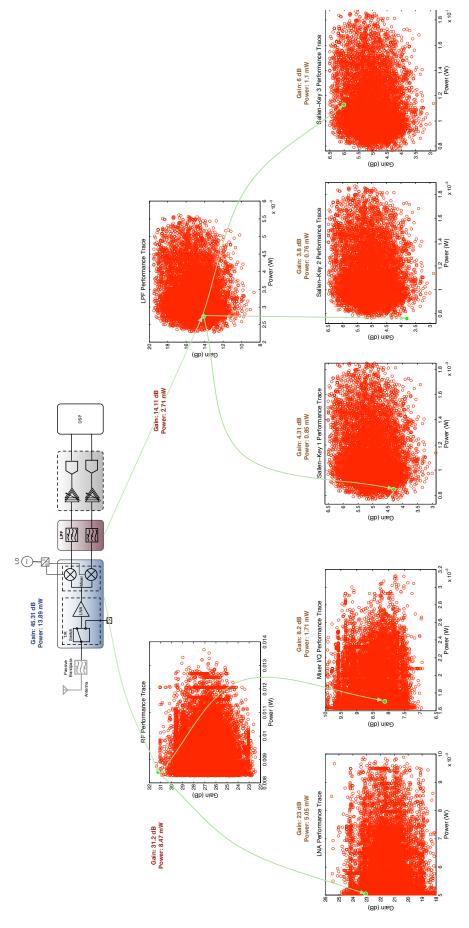

| 5.27 | Optimization Trace for Min Power (projected onto Gain and Power dimensions)                                                                                            |    |

LIST OF FIGURES vi

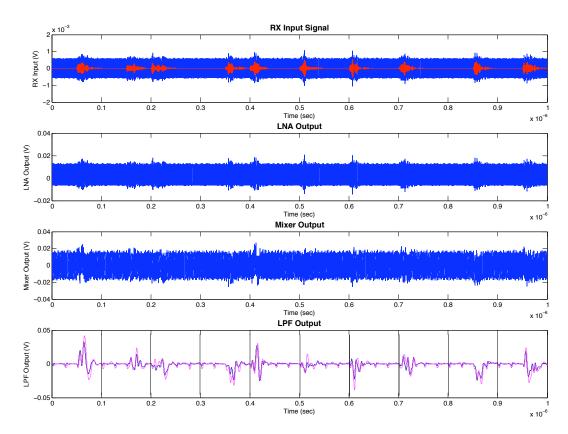

| 5.28 | Time-domain plots of signal propagation (with NBI) in Receiver, compared against   |    |

|------|------------------------------------------------------------------------------------|----|

|      | transient simulations in SPICE. (blue) Total Signal (red) Desired Signal (magenta) |    |

|      | SPICE simulation output                                                            | 88 |

# **List of Tables**

| 3.1  | Elements of performance vectors $\zeta_{TRLNA}$ and $\zeta_{Mixer}$              | 27 |

|------|----------------------------------------------------------------------------------|----|

| 3.2  | Optimization and simulation results                                              |    |

| 3.3  | Optimization results for different cost functions                                | 31 |

| 4.1  | Types of Assumptions                                                             | 36 |

| 4.2  | Models and assumptions for two-port feedback configurations                      | 42 |

| 4.3  | Characterized DDA Performances                                                   | 44 |

| 4.4  | Two-port Y-parameters of Sallen-Key filter                                       | 45 |

| 4.5  | Sallen-Key system-level non-ideal path assumptions                               | 46 |

| 4.6  | Sallen-Key system-level non-ideal component assumptions                          | 46 |

| 4.7  | DDA loading assumptions                                                          | 46 |

| 4.8  | Summary of Optimization Results                                                  | 47 |

| 5.1  | Narrow-band interference signals for ITS                                         | 63 |

| 5.2  | Receiver Specifications                                                          | 68 |

| 5.3  | Characterized performance of LNA and Mixer                                       | 72 |

| 5.4  | Characterized performance of 2nd-order Sallen-Key Lowpass Filter Cell            | 73 |

| 5.5  | Required Q and Bandwidth for Low-pass Filter Subsystem                           | 77 |

| 5.6  | Characterized performance of RF Frontend Subsystem                               | 79 |

| 5.7  | Characterized performance of LPF Subsystem                                       | 79 |

| 5.8  | Optimization results for various objectives                                      | 83 |

| 5.9  | System prediction error of optimization results compared with circuit simulation |    |

|      | results using mapped circuit configurations                                      | 84 |

| 5.10 | Implication for VGA design and channel NF                                        | 84 |

| 5.11 | Receiver environment assumptions during optimization                             | 84 |

|      | Average and variance of accuracy for system performance estimation over 1000     |    |

|      | different design configurations                                                  | 85 |

| 5.13 | Optimization Results for Various Objectives                                      | 89 |

|      | Comparison of Receiver Performance with Literature.                              |    |

#### Acknowledgments

First and foremost, I thank God, my Lord and Savior, Jesus Christ. I'm certainly not the most devout or religious of followers and have questioned more than my fair share of traditional preaching. But I know that without Him, none of this would be possible. I am grateful.

The past six years have been a significant and unforgettable experience in my life that will always be treasured. The journey hasn't always been smooth, but the challenges along the way became great memories and transformed a naive engineering student into a researcher and a true knowledge seeker. This experience would not have been possible without the support of those around me.

I would like to thank my research advisor and mentor Professor Alberto Sangiovanni-Vincentelli for his guidance and support all these years. He is a true visionary with a wealth of experience. His short and to-the-point comments are always insightful and have pointed me to the right direction time-and-time again. His energy and enthusiasm for research and innovation have been and will continue to be an inspiration for my own career path. It has been a real pleasure to work with him, and I will always value the advice and encouragements that he has given to me these years.

I've also had the pleasure to work with Professor Jan Rabaey throughout the years as part of the Pirelli CyberTyre project. In addition to being on my qualifying exam and dissertation committee, he also instructed me in one of the first circuits classes that I took at Berkeley. His knowledge of low-power circuits, wireless communications, and embedded systems has helped tremendously throughout this work. His drive to explore the unknown and challenge the impossible have inspired me to always look beyond the horizon, an attitude that I will remain with me always. I also have had the pleasure of being hooded by him during commencement.

In addition, I must express my deepest appreciation to Professor Elad Alon for being on my qualifying exam committee and Professor David Brillinger for being on both my qualifying exam and dissertation committee. Both of them have offered their valuable time and advice to help me clarify my research direction, despite extremely busy schedules. I'm always impressed by Elad's quick wit and breadth of knowledge, and every conversation with him spawns new thoughts. David was also my professor for Time-Series Analysis, where I learned many things that proved to be beneficial, beyond just my research domain. I'd also like to express my gratitude to all the faculty members that have impacted my life at Berkeley. Professor Kurt Keutzer, who was my temporary advisor during my first semester at Berkeley, along with Professor Sanjit Seshia were the instructors who introduced me to computer-aided design. In particular, Kurt's vast industry knowledge and Socratic teaching style not only opened my eyes to new things academically, but challenged me personally to become a more proactive person. Sanjit, despite being extremely busy, always showed interest in my work and offered his own views and experiences to help me explore my own path, even though he was not my research advisor. For this, I have and always will appreciate the conversations with him. I thank Professor Andreas Kuehlmann introduced me to logic synthesis, as well as reinforced my programming skills in the process. I can say that EE219B was honestly the most challenging class I had at UC Berkeley, and also the most memorable. I thank Professor Kris Pister, who reinforced my analog circuit knowledge in EE140, as well as introduced me to the world of wireless sensor networks in EE290Q. His broad industry and application experiences were very helpful to me during the Pirelli project. I also would like to express my appreciation to Professor Laurent El Ghoui for his class in Convex Optimization, which helped me reinforce and expand my understanding of mathematical programming and optimization techniques.

Certainly, spending six years anywhere would not be possible without the support of friends and colleagues, and it's especially true at Berkeley. Their talent and drive are truly inspires me to better myself everyday. I'm sure I'll cross paths with many of them during my career. First, I'd like to acknowledge those that worked closely with me on this research project, in chronological order: Fernando Di Bernardinis, although we weren't able to meet, his work established the fundamentals of analog platform-based design, which deeply impacted this work; Yanmei Li, who taught me everything about APBD and became a good friend along the way; James Wu, whose work ethic and experience really supported a major part of the RF platform building stage of this work; Pierluigi Nuzzo, whose knowledge of circuits and mathematics both helped in shaping the theory formulation of this work; and Alberto Puggelli, who helped built the base-band platform for this project and whose energy and inquisitiveness helped refine many key assumptions in this work. In addition, the members of albertogroup have been tremendously helpful along the way through stimulating discussions and meetings. Abhijit Davare and Qi Zhu were the first group members that I interacted with in the group and have given me many encouragements these years to push through the hurdles. Alvise Bonivento, who was simultaneously my office mate, friend, and project mentor offered many valuable advice for the young naive me as a first year grad student. Other members in the group that I've had the pleasure of working with include Luca Carloni, Douglas Densmore, John Finn, Carlo Fischione, Liangpeng Guo, Sameer Iyengar, Chungwei Lin, Kelvin Lwin, Mehdi Maasoumi, Mark McKelvin, Trevor Meyerowitz, Mohammad Mozumdar, Alessandro Pinto, Marco Sgroi, Gerald Wang, Guang Yang, Yang Yang, Haibo Zeng, Wei Zheng. All of whom helped to shape my growth both academically and personally. I'd also like to express my appreciation for all other members of the DOP Center, including, but not limited to: Professor Robert Brayton, Professor Edward Lee, Professor Jaijeet Roychowdury, Christopher Brooks, Alan Mishchenko, Stavros Tripakis, Bryan Brady, Bryan Catanzaro, Donald Chai, Jike Chong, Sungmin Cho, Chenjie Gu, Dan Holcomb, Nathan Kitchen, Animesh Kumar, Chao-yue Lai, Wenchao Li, Ben Lickly, Jiang Long, Bradley Miller, William Plishker, Sayak Ray, Baruch Sterin, RIchard Su, Tobias Welp, Lynn Tao-Ning Wang, Jaesoek Yang, and Jia Zou.

Furthermore, I spent quite a bit of time at Berkeley Wireless Research Center (BWRC) and must acknowledge many individuals that made my stay there enjoyable and offered a helping hand when needed. I've learned from each of them. These include many from Professor Jan Rabaey's group such as David Chen, Stanley Chen, Simone Gambini, Ping-chen Huang, Tsung-te Liu, Michael Mark, Rikky Muller, Jesse Richmond, and Nathan Pletcher. Others include, but again not limited to: Shaoyi Cheng, Yida Duan, Pulkit Grover, Cristian Marcu, Vinayak Nagpal, Vincent Ng, Ji-Hoon Park, Kun Qian, and Seng Oon Toh.

In addition to the faculty members for UC Berkeley, I must also acknowledge industry partners who have also been very helpful. The experiences and mentorship I received from working

with them are invaluable for my future success. These include, but not limited to: Hugo Andrade, Sayf Alalusi, Giorgio Audisio, Vito Avantaggiati, Sinem Ergen, Thomas Koo, Seungjun Lee, Marco Sabatini, Marco Sgroi, and Antonio Travali. This work was supported in part by the MARCO-sponsored Gigascale System Research Center (GSRC), Berkeley Wireless Research Center (BWRC) at UC Berkeley, and a grant from Pirelli Tyres S.p.A.

In addition to classes and interactions with professors in the EECS department, I found myself spending much of my time at the Haas School of Business, which deeply changed my career views. I've always been interested in entrepreneurship and have received valuable insights from my own advisor, as well as other professors in the EECS department such as Professor Kurt Keutzer, Kris Pister, David Culler, Randy Katz, and Seth Sanders. But it wasn't until I started going to Haas and getting involved with the Management of Technology program did I really understand what is involved in really building a business. Here I'd like to especially thank Professor Drew Isaacs for his teachings and personal mentorship. His insight into opportunity recognition, network building, and time and relationship management have been extremely valuable. He also gave me one of the most valuable opportunities here at Berkeley, which is to be involved in the Mayfield Fellows Program. Through this program, not only was I able to become deeply connected with the entrepreneur and VC community in Silicon Valley, I also gained valuable execution experience by working closely with the executive teams of Sierra Solar Power and Pixim Inc. I was able to meet my mentor, David Ladd, from Mayfield Fund, who's experience as both entrepreneur and VC gave me an inside view at what it takes and what it means to be an entrepreneur. But by far, the most valuable asset gained from the Mayfield Fellow experience is meeting other fellows from different backgrounds, but shared my enthusiasm in creating value through building new startups. I have no doubt that these relationship will continue to develop into life-long friendships. I'd like to acknowledge my 2010 Fellows: Buzz Bonneau, Adithya Jayachandran, Bryan Mao, Ann McEvoy, Hannah Murnen, Satish Polisetti, Becky Rutherford, and Matt Zilli. Furthermore, Jike Chong and David Chen were instrumental in pushing me to apply for this program. I'd like to also especially acknowledge Dekong Zeng, a fellow EECS PhD and entrepreneur, who became a good friend and now a business partner. I believe together, we can overcome many hurdles in our business careers, as we have throughout our PhD career.

I also want to give a special thanks to all the staff members of the UC Berkeley EECS department, who has always gone far and beyond their responsibilities to help me in times of need. Most importantly, they include Rosita Alvarez-Croft, Jo Bullock, Mark Davis, Jessica Gamble, Ruth Gjerde, Dana Jantz, Gladys Khoury, and Ellen Lenzi.

Last, but definitely not least, my friends and family have been extremely supportive of my academic pursuits. For this Id like to thank them. Without their support, graduate school would have been a much worse experience. Although there are too many to list here, I'd like to especially mention my grandparents, three of whom are no longer with with us, but all of whom have deeply impacted me. They all come from very humble roots with very little education and real notion of exactly what a Ph.D. is. Nonetheless, they've always been supportive and encouraging, and have taught me two very important lessons that has helped me achieve everything that I have: 1) growth comes from pushing beyond the limits, 2) always finish what you start. Without their loving

support, I would not be the person that I am today. For this, I am grateful.

## **Chapter 1**

## Introduction

Electronic systems are an integral part of modern society. The global semiconductor market in 2010 reached an astonishing \$300.3 Billion, after a 31.5% post-recession growth from 2009. [2] Indeed, industry demands remain strong, and as the pace of innovation continues to accelerate, semiconductor technology is pushed beyond the realm of computing and becomes pervasively applied across all industry sectors. In the energy sector, smart-meters pave the way for the next generation of efficient power distribution, load-balancing, and demand-response. [3] In transportations, micro-sensors help monitor and manage congested traffic. [4] In the automotive industry, X-by-wire systems have replaced traditionally mechanical control to improve handling, safety, and ergonomics for the driver. [5] In healthcare, brain-machine interfaces may, one day, enable paraplegic patients to walk again. [6] And in the military space, unmanned vehicles and robotics can replace humans in reconnaissance missions exploring uninhabitable terrain or dangerous unknown habitats through use of complex electro-mechanical sensor systems. [7]

The deep immersion of electronic systems is driven by a combination of innovations in sensor/actuator technology, shrinking devices, system integration, packaging, wireless communication, and embedded software. One key technology component is the set of analog, mixed-signal, and RF (AMS/RF) systems that lie at the interfaces, bridging the physical world with the digital processing cores. Without these systems, such rich physical interactions and novel applications would not be possible. However, the development process for AMS/RF systems still heavily relies on manual efforts in transistor-level design and physical layout and is one of the main bottlenecks in the design and implementation of new electronic applications.

## 1.1 Trends and Challenges

The development of the electronics industry over the past half-century have been largely fueled by advancements in digital CMOS technology and guided by Moore's Law. [8] Innovations from the electronic design automation (EDA) industry have allowed digital designers to handle the exponential increase in system design complexity by raising the level of abstraction from transistor-level to gate-level, register-transfer-level (RTL), and most recently, electronic-system-level (ESL). [9] Unfortunately, EDA counterparts for analog and mixed-signal systems have remained elusive, and systems still primarily rely on manual design and integration efforts.

As new applications become more complex, heterogeneous, and deeply immersed into the physical world, the lack of tools and design methods to effectively address the increasing design complexity of AMS/RF systems becomes a major hindrance. Traditionally stand-alone AMS/RF blocks, such as PLL or transceiver front-ends, are increasingly being integrated onto the same chips as the digital processing cores in order to minimize fabrication costs and to improve performances. As of 2009, 90% of all systems-on-chip (SoC) contain analog circuitry and take up 20% of the physical area.[10] And according to industry estimates, between 50-70% of SoC respins are due AMS issues, each of which incur an extra \$5-10 million to the non-recurring-engineering (NRE) cost and six- to eight-week delay in product delivery. [11, 12] AMS issues are not only concerns for SoC designers, but also for historically digital-dominated microprocessor and graphic processor companies such as Intel and nVidia. As pointed out by Intel Fellow, Greg Taylor, at the 2010 VLSI Conference, more than 20 different types of analog components (ranging from I/O buses and clock generator to thermal sensors, power management units, and fuse control) exist on each Intel microprocessor for technology nodes at 90nm and below, with the number rapidly increasing for each new process generation.[13] Along with the increasing number of required AMS/RF components, the market demand for high-performance low-resource applications have further constrained these components to meet very stringent performance requirements, such as ultra-low-power, high dynamic-range, low-cost, or high-yield. However, AMS/RF designers are also severely constrained by the physical limitations of the underlying devices. Specifically, the desire to integrate AMS/RF functionalities onto the digital core introduces many complex physical-level issues such as voltage scaling, lower signal-to-noise-ratio, signal interference, and device mismatch.

Despite the increasing demand and complexity of AMS/RF systems, designer productivity in this domain have remained unchanged, relying mostly on manual design efforts. The need for new EDA tools and design methods is clear. Thus far, industry and academic efforts have mostly focused on automation of *circuit-level* design and *physical-level* layout; however, commercial adoption have been extremely limited. According to the 2010 Gartner Hype Report[14], analog automated synthesis and optimization tools introduced thus far have been under industry expectation. They are either not powerful enough to produce reliable designs that meet the demanding requirements of industrial applications or are too restrictive/complicated to use to foster mass adoption. The main reasons for the lack of adoption by design community can be broadly attributed to three types:

- 1. Limitation in scope of use: when the tool or method is only valid for specific types of topology, application, or technology. Either not generally applicable or lose significant accuracy or performance when wrongly applied. Rule-based systems are especially prone to this.

- 2. Loss of design insight: when the tool or method maps the design problem onto internal variables that are insignificant or incomprehensible to the designer, where designers lose valuable design insight and cannot understand or modify the output of the tool. Optimization tools that rely on numerical methods for manipulation and optimization are prone to this, which causes designer doubt when combined with lack of accuracy or generality from above.

- 3. More effort, minor gain: when the tool or method is significantly different from traditional electronic design training and tool flow used by the designer, significant retraining is required. However, when combine with the effects of 1 and 2, many designers and companies consider the return on investment for retraining to be of little or even negative value.

Instead of attempting to automate the low-level design processes, a compositional design methodology at the system-level can more efficiently overcome the complexity of modern AMS/RF integrated systems, without dramatically disrupting the current design practices of AMS/RF circuit designers, allowing smooth industry adoption. Specifically, a compositional design flow leverages design reuse, enables early-stage validation of design decisions, and reduces the number of design iterations, which minimizes overall NRE costs. Furthermore, as we reach the end of Moore's Law, the industry is transitioning to the "More than Moore" paradigm, which relies on innovative system integration and optimization techniques to meet performance demands. [15] Design methodologies that make decisions at the system-level would allow global tradeoffs to be evaluated among various system components, rather than focusing on localize optimizations of single components, achieving a greater degree of freedom during design space exploration.

However, integration and reuse of AMS/RF components at the system-level is non-trivial. In fact, analog intellectual-property (IP) components offered by most companies today are hard IP blocks, in GDS II format, where the physical sizing and placement of the transistors in the component are already pre-determined to a fixed parameter. Thus, the components are not configurable, and are very hard to reuse in most cases. Even in cases where these IP blocks can be used, their performances differ depending on different system environments and requires multiple design iterations between the IP vendors and the system architects to meet the system requirements. The problem stems from the fact that the functionality and performance of an analog component is closely tied to the physics of the underlying devices. Not only are they a function of the internal design parameters, such as transistor sizings and voltage biasing, but also a function of the interface conditions at the input and output ports. Even in the simple case of two cascaded analog circuits, performances of the composition cannot be generally obtained by directly cascading behavioral and performance models of the stand-alone components, since the behavior of the loading block substantially affects that of the driver. The problem of interface conditions during integration, under which hierarchical system compositions are legal, has not been rigorously addressed and mostly relies on the experience and manual efforts of the circuit designer. However, to overcome the increasing complexity of modern AMS/RF design, a formalized approach must be introduced to enable fast and accurate performance estimation and validation of integrated AMS/RF systems based on pre-characterized component blocks. Furthermore, configurability of the component blocks must be retained at the system-level to ensure a high degree of flexibility during design space exploration, so that the optimal system can be reached to meet the demanding requirements of modern electronic applications.

### 1.2 Thesis Contributions and Organization

This dissertation introduces a compositional design methodology, which leverages the analog platform-based design (APBD) flow introduced in [16, 17] and assume-guarantee reasoning to guarantee correct system construction. The main contributions include:

- The definition of AMS/RF contracts for component composition and a set of necessary and sufficient conditions for composition compatibility, under which the functions and performances of the composed AMS/RF components in the integrated system are guaranteed to behave the same as those obtained from stand-alone characterization, within a specified error margin;

- A *design flow* for leveraging contracts in system construction using the APBD methodology is introduced;

- Application of the design flow for a *cascade* composition of a low-noise-amplifier with an integrated transmit/receive switch (TRLNA) and a down-converting mixer (MIXER) for UWB receiver applications;

- Application of the design flow for the *feedback* composition of an bi-quadratic low-pass Sallen-Key filter cell (SKCELL), consisting of a feed-forward differential-difference-amplifier (DDA) and a feedback second-order passive resistor-capacitor (RC) filter network;

- Application of the design flow for the specification, composition, and multi-level designspace exploration of the UWB receiver system for the Intelligent Tire application, consisting of subsystems (UWB RF-frontend and low-pass filter) constructed using previously characterized circuit components, to demonstrate hierarchical design refinement and application.

This dissertation is organized into six chapters. Chapter 2 provides the related background works for this dissertation, including an overview of the state-of-the-art analog EDA tools and methods, introduction to the the platform-based design framework, and history on the use of contracts for verification and design in other domains. In Chapter 3, contracts for analog composition will be formally defined, and incorporated into the APBD paradigm. The methodology is applied to the design and integration of an RF system, composed of a TR switch, LNA, and Mixer. In

Chapter 4, a detailed study on the propagation of contracts across different abstraction layers is studied. Specifically, the concept of vertical contracts is discussed. Both horizontal and vertical contracts are demonstrated through a case study on the composition of an analog feedback network, the Sallen-Key bi-quadratic cell. In Chapter 5, a complete application of the design flow is demonstrated through the construction of the UWB receiver chain in the Intelligent Tire System, demonstrating multi-level hierarchical design exploration and composition. In Chapter 6, a summary and recommendations for future research directions is discussed.

## **Chapter 2**

## **Background**

Despite more than 25 years of active research and development in AMS EDA techniques and methods, analog design is still very much a knowledge-intensive and handcrafted process that require expert designers, supported only by a handful of commercial SPICE simulation tools and interactive transistor and layout-level design entry software. As illustrated in Figures 2.1a and 2.1b, modern analog design processes are mostly top-down, where each component is customly designed, optimized and verified locally based on a set system specifications and assumptions. There are many drawbacks to this approach:

- Difficult system-level tradeoffs and exploration: Components are individually designed based

on pre-determined specifications. Since there is very little information about the physical

performances of the components at the system-level, it is very difficult to fully explore the

entire design space at the system-level and accurately perform tradeoffs among the performances of different components.

- Multiple design iterations among various design stages: Since specifications are determined

with very little information of the available resources and performance feasibility of the components, considerable portion of the design cycle is devoted to iterating between specification

engineering and design refinement at each stage of the design cycle.

- Difficult to simulate and validate the system pre-silicon: Since the abstraction of design is stagnated at the transistor-level, fully validating the system via pre-silicon simulation is extremely time consuming. Although there have been efforts [18, 19, 20] on abstracting mixed-signal simulation into a higher level of abstract, adoption have been slow.

Figure 2.1: Reference State-of-the-Art Analog Design Flows

## 2.1 Design Tools

Majority of research efforts in analog EDA have been focused on automating specific stages in the traditional design flow, such as topology selection, circuit sizing, or automatic layout. In [1], a very comprehensive review of the major works in analog EDA over the past 25 years was presented, which is also illustrated in Figure 2.2. Here, the reviewed works were categorized into three abstraction levels: Physical, Electrical, Behavioral. Another way of interpreting this categorization is based on the tasks performed at each abstraction level, which can be drawn directly from Figure 2.1a, specifically:

- 1. Behavioral: Functional Partition, Architecture Selection, and Specification Derivation.

- 2. Electrical: Circuit Topology Selection and Sizing

- 3. Physical: Layout, Routing, and Parasitic Extraction

**Figure 2.2**: Review of analog EDA work in the past quarter-century by G. Gielen [1].

The design exploration strategies were classified into four types:

- Architecture Selection before or after dimensioning

- Select topology or architecture first, then optimize paramters in selection, OR

- Select multiple topologies or architectures, and optimize each of them. Select the best one.

- Selection during dimensioning

- Design is incrementally modified based on a starting parameterized template, until optimal design is reached

#### • Top-down creation

Starting with a high-level description, the system is translated into internal representations and mapped onto basic architecture components. Components are then optimized, integrated, and validated.

#### • Bottom-up generation

Starting with a set of seed component, systems are modified, composed, and rearranged to meet given design specifications.,

Commercially, as observed in Figure 2.1b, the state-of-the-art analog design flow from [22] remains a heavily manual process. Recently, the use of parameterizable cells (PCells), which are pre-designed circuit or layout templates that may be parameterized, have been introduced to reduce designer effort and promote design reuse. However, the use of PCells in industry is still mostly limited to minor components and generally used only at the transistor and layout levels. Furthermore, PCells are only design templates and do not carry any information for circuit or system performance. They still need to be properly sized, simulated, and validated. Current commercially available PCell sizing tools include Cadence NeoCircuit and NeoCELL [23], which came out of research from CMU for stochastic simulation-based circuit sizing [24], as well as Titan ADX [25], which came out of research from Stanford for circuit sizing through geometric programming [26].

While many research works in analog EDA are quite powerful, their applicability and scope of use were limited, which prevented mass adoption of these tools in the designer community. Tools that leveraged the strategies of *selection before*, *during*, *or after dimensioning* require an initial set of template designs and rules which may not be widely available and must be created by designers from scratch, often in the context of the new tool, which are unfamiliar to designers. Tools that use the *top-down creation* strategy are generally limited to the technology-independent behavioral and macro-model levels, while the *bottom-up generation* tools were restricted to the electrical circuit level. There exists a clear gap between the system behavioral level and the electrical circuit level in analog design, which prevents the level of abstraction for AMS design from moving beyond the transistor level. Thus, many system-level issues discussed in Chapter 1 cannot be properly addressed within the current design flow. To address this gap in design, analog platform-based design (APBD) [16] was introduced as a recursive meet-in-the-middle design framework that can be applied to all levels of abstraction.

## 2.2 Analog Platform-based Design

Analog Platform-based Design (APBD) is a design methodology proposed in recent years [27, 21, 16, 28, 17, 29, 30] that adopts the platform-based design (PBD) paradigm [31, 32] into the analog domain. Fundamentally, platform-based design identifies design as a *meeting-in-the-middle* process (Figure 2.3), where successive top-down refinements of high-level specifications across

design layers are mapped onto bottom-up abstractions of potential implementations. The layers in design are supported by a set of *platforms*, which is a collection of abstracted views of low-level components and a set of composition rules. This library-based approach makes PBD is naturally amenable to design reuse.

The multi-view approach to design allows the problem to be partitioned and orthogonalized into concerns at various levels of abstraction and can incorporate all four types of design exploration strategy described in Section 2.1, while closing the gap between abstraction levels through appropriate mapping. Defining the proper levels of abstraction depends on the target application. Since PBD is a recursive process that can applied across many application levels [33, 34, 35, 36, 37, 38], it's not restricted to any single application, design-flow, or set of tools.

**Figure 2.3**: Each platform stack of PBD features a meeting-in-the-middle of system constraints and performance characterizations.

In APBD, each component is characterized by a behavioral model that represents the functionality of the component and a performance model that represent a set of feasible performances of the component and abstracts away unnecessary details. Through the use of machine learning techniques [28], continuous circuit-level performance feasibility regions can be extrapolated from a set of discrete transistor-level electrical simulation simulation samples. An *m*-dimensional support-vector machine is used as a classifier to tightly estimate the feasible performance space of interest for a circuit block (Figure 2.4), where *m* is the number of performance parameters for the circuit.

**Figure 2.4**: SVM classifiers help separate feasible and infeasible performance spaces of a component.

Figure 2.5: Platform abstraction process.

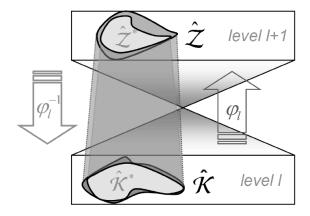

A design is obtained by composing components of the platform into a platform instance, as shown in Figure 2.5, where the outputs of level l ( $\kappa$ ) are used as configurations to obtain system performances at level l+1 ( $\zeta$ ). In this framework, new designs can be assembled quickly from a library of pre-designed and pre-characterized components, giving the highest priority to design reuse, correct assembly of components, and an efficient flow from specification to implementation.

Since design decisions are made at the system level, APBD can locate globally optimal design solutions by evaluating system tradeoff across all components, instead of just using locally optimized designs of each individual component. In addition, platforms permits hierarchical design space exploration, which progressively reduce the number of design variables and separate design concerns.

However, the problem of defining correct composition rules for components of a platform library has not been rigorously addressed. Correct composition guarantees implementation feasibility and performance estimation accuracy. Indeed, performances of analog components are strongly dependent on interfaces with other components and loading conditions. In previous APBD case studies, the interface conditions were hand-tuned and fixed to constants during performance characterization. In [16] the introduction of ad-hoc interconnection blocks is suggested to accurately model interface effects in analog circuits. However, the provided guidelines can be hardly generalized, basically consisting in case-by-case topology-related heuristics which require non negligible effort for the designer to build the models. To formulate a more rigorous composition approach, this work proposes the use of contract-based compositional reasoning.

### 2.3 Contract-based Design

Contracts are fundamentally rooted in compositional assume-guarantee reasoning: if given a set of defined assumptions, a component or model can provide or guarantee a set of outputs, then the assume/guarantee sets form contracts. The essence of contracts is divide-and-conquer, where assume-guarantee (AG) reasoning reduces design and verification complexity by decomposing system-level tasks into manageable subproblems at the component-level under a set of assumptions. System properties are inferred or proved based on component properties that are guaranteed under the given assumptions. The first formal use of AG reasoning can be traced to [39], which leveraged assume-guarantee relations on input and output message traces of individual processes to prove correctness of the overall constructed communication network. In [40], a similar logic style is applied to infer system properties for concurrent software programs. In [41, 42, 43], contracts are applied to reduced complexity in formal verification of large systems, which would otherwise be intractable. More recently, contracts have been extended into the design digital and software systems, where component models are either inherently embedded or annotated with contracts and enforced during design such that the constructed system is *correct-by-construction*. In [44, 45], assumption/guarantee is used to model the interfaces of components, which can be used to support incremental refinement of systems and independent implementability.

The core of contract-based design (CBD) [46, 47] is a set of assume-guarantee relationships between the environment (e.g. interfaces) and the component (e.g. performances). In [47], a meta-theory of of contracts is presented which define the basic properties of contracts, including consistency and compatibility. In addition, contracts are casted both horizontally and vertically, depending on the source of the contract assumptions and abstraction level of the guaranteeing

components. During composition, a legal connection must satisfy the assumptions of all components involved to guarantee the correct system behavior. However, thus far, application of contracts have resided in the digital domain with discrete components that, in general, have a fixed number of static input/output requirements (e.g. legal states or timing constraint) and guarantees. In this dissertation, I apply the meta-theory of contracts from [47] to the analog domain to construct systems based on component composition, where assumption conditions (e.g. load impedance, input voltage level) are continuously variable within a specified range.

Unlike digital components, analog component models must capture a wide and continuous range of assumption values in order to provide rich models that can be used for multiple applications and system environments. Composition is only allowed if the contract assumptions of all interconnected components are simultaneously satisfied. In fact, assume-guarantee relationships have always been intuitively used by analog designers. However, in most cases, only a few fixed interface assumptions are considered in an ad-hoc manner and are rarely captured into an executable model. Within APBD, *validity laws* need to be defined for a component to be useful. However, thus far, *validity laws* have been defined on an ad-hoc basis that can hardly be applied to a general design flow. In contrast, contracts allow rigorous definitions and analysis of the validity of compositions. By considering a wide continuous range of assumptions, contracts allow each component to be reused in multiple application domains since it provides a rich feasibility space that the system designer can explore.

## **Chapter 3**

## **Analog Composition Using Contracts**

Efficient system design increasingly relies on hierarchical design-space exploration and compositional methods to shorten time-to-market, leverage design reuse, and minimize design costs. However, the hierarchical approach tend to lose in accuracy when propagating information across design levels. Consequently, component reuse and system integration are very difficult tasks in all domains: digital, analog, software, and hardware. Integration of analog components is even more cumbersome because circuit performances and behaviors are not only functions of internal design parameters, such as transistor sizings and voltage biasing, but also functions of the external environment, such as interface loading or common-mode input voltage. Even in the simple case of two analog circuits in cascade, performances of the composition cannot be generally obtained by directly cascading behavioral and performance models of the stand-alone components, since the behavior of the loading block substantially affects that of the driver, and vice versa. This tight coupling of circuit behaviors and their environment make component-reuse and performance estimation of the composite system an extremely hard task. Currently, there exists no general solution to this problem, so analog system integration commonly rely on *ad-hoc* solutions, heavily dependent on the designers' experiences and insights at both the circuit and the system levels.

### 3.1 Analog Contracts

As discussed in Chapter 2, Analog Platform-based Design (APBD) is a natural framework to adopt to promote design reuse. However, there lacks a mechanism to ensure the validity of composition. I build upon the APBD methodology by exploiting *contracts* to enforce *correct-by-construction* system composition. Contracts intuitively capture the thought process of a designer, who aims at *guaranteeing* circuit performance only under specific *assumptions* (e.g. loading and dynamic

range). By formally incorporating contracts into the design flow, this approach allows the detection and correct composition of compatible components in a given library, which ensures that the design decisions made at the system-level, based on a global objective, account for the compositional compatibility of the underlying components. Let's first begin by defining the *Analog Platforms*, which is used to represent components at all levels of abstraction in APBD.

#### **Definition 1** An Analog Platform (AP) consists of:

- a set of input variables  $u \in \mathcal{U}$ , a set of output (and performance) variables  $y \in \mathcal{Y}$ , a set of internal variables  $x \in \mathcal{X}$  (including state variables), a set of configuration parameters  $\kappa \in \mathcal{K}$ :

- a behavioral model  $\mathcal{F}(u, y, x, \kappa) = 0$ , which implicitly represents the behavior of the component; in general,  $\mathcal{F}(.) = 0$  is a set of integro- differential equations uniquely determining y and x given u and  $\kappa$ ;

- a performance feasibility model:

$$\mathcal{P}(y,x) = 1 \Leftrightarrow \exists \kappa, u, (y,x) = \phi_y(\kappa, u) \tag{3.1}$$

Let  $\phi_y(\kappa, u)$  denote the map that computes the performance y corresponding to particular values of u and  $\kappa$  by solving the behavioral model. The feasible performance set is then the set described by the relation (3.1).  $\mathcal{P}(y, x)$  is an indicator function denoting the feasible performance space of the component.  $\phi_y$  maybe be either a functional or electrical simulator such as Simulink® [48] or SPICE [49].

• a set of assumptions:  $A(u, y, x, \kappa, \delta) \leq 0$ , which is a set of constraints on the variables of the AP for which both behavioral and performance models are guaranteed to be valid within a set of tolerable margins  $\delta \in \mathcal{D}$ .

Here, we replace *validity rules* in the original definition of AP from [16] with a set of *assumptions*, which is more aligned with the use of contracts. Assumptions of an AP may either be *static* or *dynamic*. Static assumptions are uniquely singular conditions on a set of AP variables, and generally denotes conditions (e.g. supply voltage) that do not change and must be satisfied for the AP to be instantiated, such as:

$$V_{DD} = 1.5V$$

$$V_{SS} = 0V$$

$$L_{min} = 0.18\mu m$$

Dynamic assumptions refer to conditions (e.g. loading impedance) that varies depending on the system architecture or external environments. Dynamic assumptions specifies a range of values for the assumed variable for which the AP may be used, such as:

$$R_{source} = r \quad \forall \ r \in [100, 10000]\Omega$$

In this example,  $R_{source}$  is assumed to be variable within a continuous range between 100 and 10000  $\Omega$ ; however, dynamic assumptions may also be variable within a discrete set, such as in variable-mode components. Since dynamic assumptions are variable, the guaranteed performance of the AP should be able to vary with the assumption. For example, an amplifier may provide a gain of 10 dB if the loading impedance is 1000  $\Omega$  or a gain of 15 dB if the loading is 5000  $\Omega$ . The AP should capture both the varying range of the loading assumption, as well as the corresponding set of gain performances. Clearly, static assumptions are a special case of dynamic assumptions, and the decision for which variables to statically assume versus dynamically assume depends on the component designer and the degree of freedom allowed for the external user of the component. Dynamic assumptions allow greater flexibility for the system environment in which an AP component can be instantiated, which promotes component reuse. A completely staticallyassumed component is essentially hard IP components with no flexibility, whereas a completely dynamically-assumed component is configurable, but would require more efforts during characterization to guarantee accurate model outputs. An AP model is valid when all static assumptions are satisfied, and for dynamic assumptions, there exists a value for the assumed variables that lies within the assumed range, while still satisfying the performance feasibility model of the AP. A valid AP guarantees that its behavioral and performance models correspond to the actual circuit implementation within a tolerance dictated by  $\delta$ .

Given a set of AP components at level l, systems can be composed and represented as APs at level l+1, which themselves are components for a higher-level. *Contracts* ensure component validity during composition and are defined as follows.

**Definition 2** The contract C for an AP component is a set of assume/guarantee tuples  $\{c_i = (a_i^{\delta}, g_i) : i = 1, ..., N\}$  where for each i,

- 1.  $a_i^{\delta}$  is the set of vectors for the assumed variables of the AP,  $(u,y,x,\kappa) \in \mathcal{U} \times \mathcal{Y} \times \mathcal{X} \times \mathcal{K}$ , that satisfies all assumption conditions described in  $\mathcal{A}$  of the AP within the margins  $\delta$ .

- 2.  $g_i$  is the set of all  $(y,x) \in \mathcal{Y} \times \mathcal{X}$ , such that  $a_i^{\delta} \models \mathcal{A} \Longrightarrow \mathcal{P}(g_i) = 1$ , that is, if  $a_i^{\delta}$  satisfies  $\mathcal{A}$ , then  $g_i$  is contained in the AP performance feasibility model. Clearly,  $g_i$  can be also computed by directly executing the behavioral model under the condition dictated by  $a_i^{\delta}$  if  $a_i^{\delta} \models \mathcal{A}$ .

The role of the contract is to identify the correct performance regions guaranteed by each component during composition. As different assumptions are realized during composition, corresponding component performance guarantees are utilized to configure the system to meet the given specifications. This ensures that for various system configurations, the AP models correctly represent the true behavior of the circuit within the system environment. In particular, only *compatible* components can be composed to construct a higher level AP. More formally,

**Definition 3** Two AP components A and B, with contracts  $C_A$  and  $C_B$ , are compatible, i.e.  $A \bowtie B$ , iff there exists ports  $p_A \in \mathcal{U}_A \cup \mathcal{Y}_A$ ,  $p_B \in \mathcal{U}_B \cup \mathcal{Y}_B$ , and contract tuples  $(a_A, g_A) \in C_A$  and  $(a_B, g_B) \in C_B$  such that

$$\mathscr{P}_{p_A}(a_A) \cap \mathscr{P}_{p_B}(g_B) \neq \emptyset$$

and  $\mathscr{P}_{p_B}(a_B) \cap \mathscr{P}_{p_A}(g_A) \neq \emptyset$

where  $\mathscr{P}_p(S)$  is the (orthogonal) projection of the set S onto the subspace of the variables related to port p.

Informally, two AP components are compatible if there exists a set of values for the variables on the shared ports that satisfy the assumptions of *both* components and obeys their behavioral and performance feasibility models. Two AP components are then *composable*, i.e. either the composition  $A \otimes B$  or  $B \otimes A$  forms a valid AP, when  $A \bowtie B$  holds. There are no restrictions for the ports  $p_A$  and  $p_B$  in Definition 3 to be output and input ports, respectively.

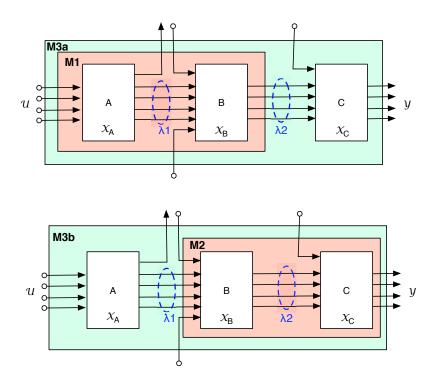

**Figure 3.1**: A compose B on shared variables  $\lambda$ .