# **UCLA**

## **UCLA Electronic Theses and Dissertations**

### **Title**

Design and Verification of a Closed-loop-ready High-channel-count Neuromodulation Unit

### **Permalink**

https://escholarship.org/uc/item/2hb7h78b

### **Author**

Hokhikyan, Vahagn

## **Publication Date**

2017

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

## Los Angeles

Design and Verification of a Closed-loop-ready

High-channel-count Neuromodulation Unit

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Biomedical Engineering

by

Vahagn Hokhikyan

© Copyright by

Vahagn Hokhikyan

#### ABSTRACT OF THE DISSERTATION

Design and Verification of a Closed-loop-ready

High-channel-count Neuromodulation Unit

by

### Vahagn Hokhikyan

Doctor of Philosophy in Biomedical Engineering

University of California, Los Angeles, 2017

Professor Dejan Marković, Chair

According to a report by the World Health Organization (WHO), neuropsychiatric disorders affect about one billion people worldwide[1] and are the leading cause of disability in the U.S.[2]. To address this global epidemic, neuroscientific initiatives are being developed globally[3].

Deep brain stimulation (DBS) has been successful alternate treatment modality for some neuropsychiatric disorders (Parkinson's disease, essential tremor, dystonia, and obsessive-compulsive disorder) when traditional treatment options failed (resection, medication, and psychotherapy). According to one long term study targeting Parkinson's disease, patients' motor function and daily activity-scores improve about 50% while off medication and receiving only DBS therapy[4]. This therapy is delivered through large electrodes in the form of fixed-frequency rectangular stimulation pulses in an always-on, open-loop fashion - ignoring the disease state, medication status, or side effects.

In this work, we present a more advanced neural implant which, while being backward compatible with traditional DBS therapy, 1) is capable of sensing neural signals while delivering stimulation, 2) has high-channel-count, and 3) can generate non-rectangular stimulation waveforms. These key features are enabled by our custom-designed neural sensing and stimulation integrated circuits (ICs), which along with a few passive components, a miniature printed circuit board, and our user-friendly graphical interface comprise a capable neuromodulation system.

Our sensing IC's ability to capture neural signals and stimulation artifacts without saturation at implant-level power is unique. Sampled local field potential (LFP) signals can be used to close the knowledge gap about the disease biomarkers and be fed into closed-loop algorithms for automatic tuning of stimulation parameters based on the disease state. The resulting autonomy will reduce or eliminate the need for periodic clinical visits for re-adjusting stimulation parameters to ameliorate neural network's habituation effects.

Our high-channel-count stimulation IC, when paired with high-density probes, will substantially increase the spatial resolution of DBS, which can improve the therapeutic index and potentially result in lower power consumption for achieving the same therapeutic benefits[5]. Also, the ability of our stimulation IC to generate custom, non-rectangular waveforms can lead to increased implant battery life, as some non-rectangular waveforms seem to be more energy efficient[6],[7].

We believe that the proposed system has the potential to improve the quality of patient care and to further our understanding of neuropsychiatric disorders, and we hope that it will soon find an increased use in various clinical and research environments. The dissertation of Vahagn Hokhikyan is approved.

James Bisley

Nader Pouratian

Nanthia Suthana

Dejan Marković, Committee Chair

University of California, Los Angeles

2017

To the Architect of the Universe,

Who put me in a wonderful world and gave me the curiosity to explore it.

# TABLE OF CONTENTS

| 1 | Introdu | ction                                                           | 1  |

|---|---------|-----------------------------------------------------------------|----|

|   | 1.1 Org | ganization of This Dissertation                                 | 2  |

| 2 | System  | Design                                                          | 4  |

|   | 2.1 The | e Neuromodulation Unit                                          | 4  |

|   | 2.1.1   | Nontraditional System Architecture                              | 4  |

|   | 2.1.2   | Advantages of the Proposed System Architecture                  | 7  |

|   | 2.1.3   | Alternate System Topologies Utilizing Our NMU                   | 9  |

|   | 2.1.4   | Advantages of the Proposed NMU Electronics                      | 10 |

|   | 2.1.4.  | 1 High-Channel-Count                                            | 12 |

|   | 2.1.4.  | 2 Non-Rectangular Waveforms                                     | 12 |

|   | 2.1.4.  | 3 Simultaneous Sensing and Stimulation                          | 14 |

|   | 2.1.5   | NMU Physical Dimensions                                         | 15 |

|   | 2.1.6   | NMU PCB Design                                                  | 17 |

|   | 2.1.7   | Using Three Wires for Communicating with Two SPI Slaves         | 18 |

|   | 2.1.7.  | 1 Absence of SPI SSEL Signal and Recovery from Partial Packets  | 20 |

|   | 2.2 The | e High-Dynamic-Range Sensing IC                                 | 21 |

|   | 2.2.1   | Challenge of Capturing Neural Signals and Stimulation Artifacts | 21 |

| 2.2.2   | Our Sensing Front-End Architecture                                   | 23 |

|---------|----------------------------------------------------------------------|----|

| 2.2.3   | Challenges of Using VCO ADCs for High-Resolution Applications        | 25 |

| 2.2.4   | Previously Used Methods for VCO ADC Nonlinearity Correction (NLC)    | 26 |

| 2.2.5   | The Proposed NLC Approach – Foreground Calibration Using a Polynomi  | al |

| Comput  | tation Engine2                                                       | 27 |

| 2.2.5.  | 1 Engine Order and Hardware Implementation                           | 27 |

| 2.2.5.  | 2 Engine Order Revisited                                             | 29 |

| 2.2.5.  | 3 Coefficient Sharing Between Channels                               | 32 |

| 2.2.6   | Low-Power Optimizations                                              | 33 |

| 2.2.6.  | 1 Technology Selection                                               | 34 |

| 2.2.6.  | 2 Interleaving                                                       | 35 |

| 2.2.6.  | 3 Clock Domain Partitioning and Clock Gating                         | 36 |

| 2.2.6.  | 4 Comparison with State-of-the-art                                   | 10 |

| 2.2.7   | Support for "Blanking" & Identification of "Blanked" Samples         | 12 |

| 2.2.8   | Decimation Block for Data Reduction                                  | 12 |

| 2.2.9   | IC Micrographs4                                                      | 14 |

| 2.3 Sti | mulation IC4                                                         | 15 |

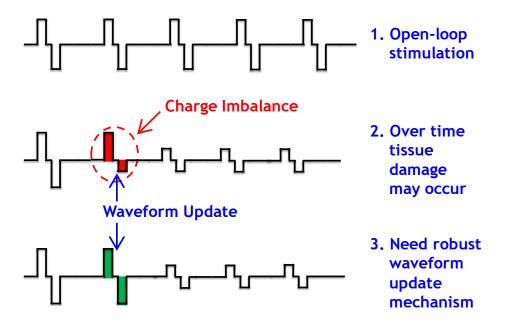

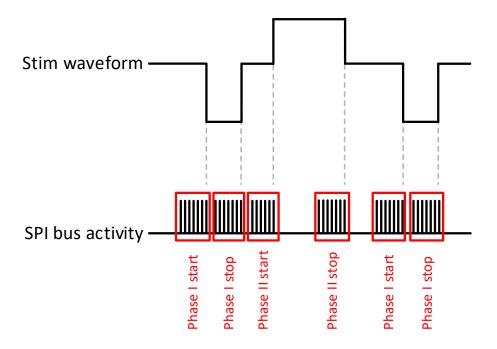

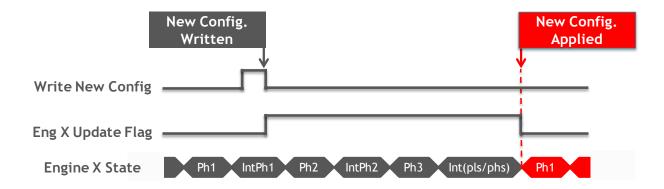

| 2.3.1   | Stimulation Parameter Update Considerations for Closed-Loop Implants | 15 |

|   | 2.3.2   | Safe Waveform Parameter Updates in Commercial Off-the-Shelf Stimulation | on ICs47 |

|---|---------|-------------------------------------------------------------------------|----------|

|   | 2.3.2.  | 1 Intan Technologies RHS2116 Stimulator/Amplifier                       | 47       |

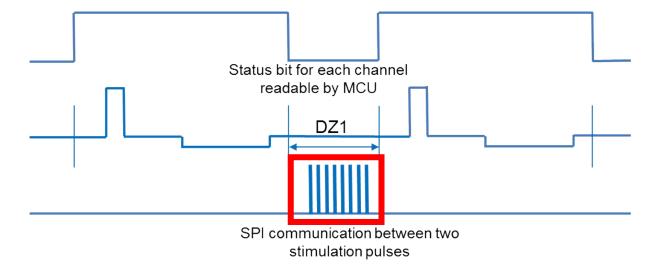

|   | 2.3.2.  | 2 Cactus Semiconductor CSI021                                           | 49       |

|   | 2.3.3   | The Proposed Safe Waveform Parameter Update Mechanism                   | 50       |

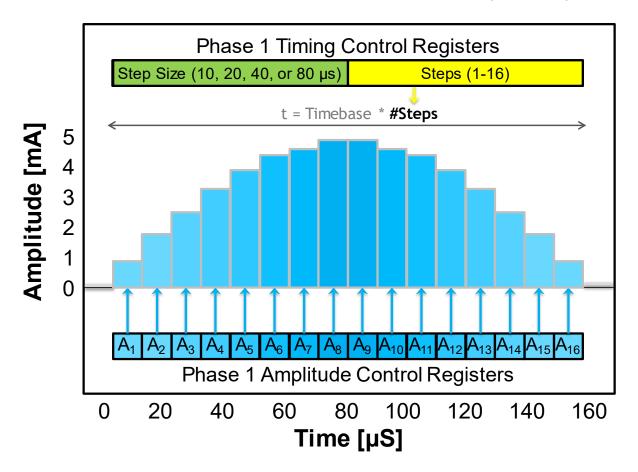

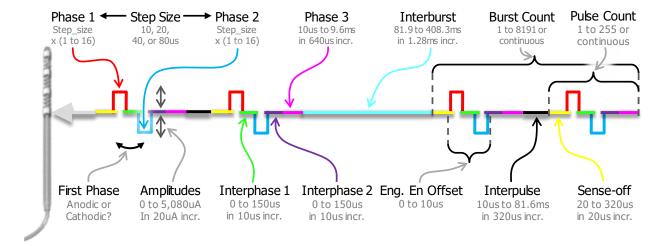

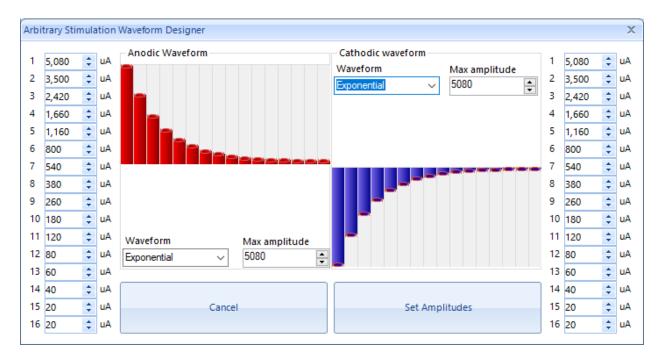

|   | 2.3.4   | Non-Rectangular Waveform Generation                                     | 51       |

|   | 2.3.5   | Stimulation Waveform Programmability                                    | 53       |

|   | 2.3.6   | Patient Safety Features Built into the IC Communication Protocol        | 55       |

|   | 2.3.7   | Sensing Switch-Matrix Control and Support for "Blanked" Sensing         | 57       |

|   | 2.3.8   | IC Micrographs and Low-Power Optimizations                              | 58       |

| 3 | System  | Verification                                                            | 60       |

|   | 3.1 Per | formance Tests                                                          | 60       |

|   | 3.1.1   | VCO ADC Dynamic-Range and Linearity                                     | 60       |

|   | 3.1.2   | VCO Linear-range Stability Over Operational Temperature Range           | 62       |

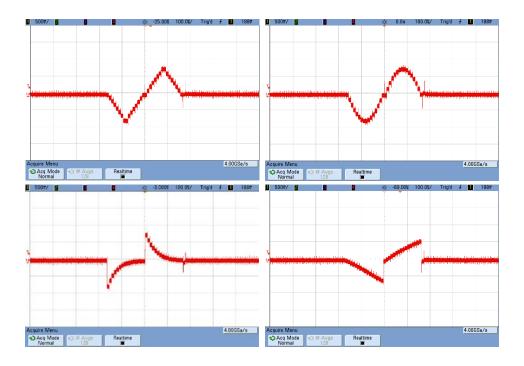

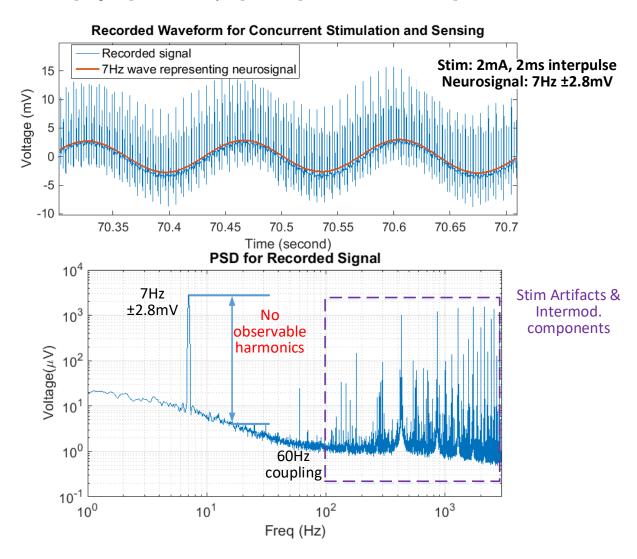

|   | 3.1.3   | Concurrent Stimulation and Sensing Test                                 | 64       |

|   | 3.2 Vei | rification Platform                                                     | 67       |

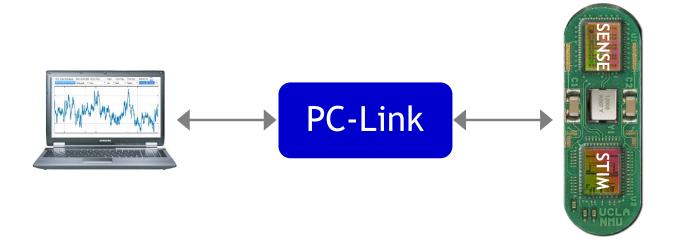

|   | 3.2.1   | PC-link Dongle                                                          | 68       |

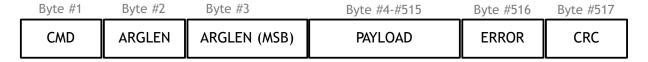

|   | 3.2.1.  | 1 PC to PC-link Communication Packet Structure                          | 68       |

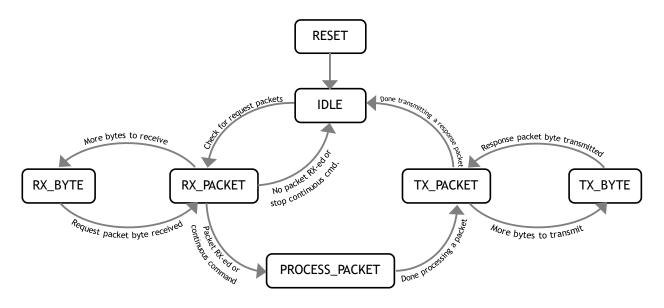

|   | 3.2.1.  | 2 Firmware                                                              | 69       |

|     | 3.2.2      | Custom PC GUI                             | 70 |

|-----|------------|-------------------------------------------|----|

|     | 3.2.2.1    | Synchronization With PC-link              | 71 |

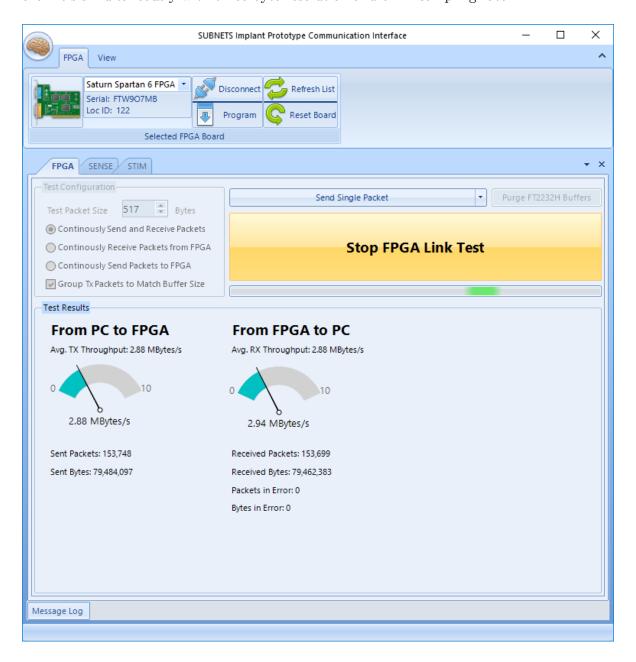

|     | 3.2.2.2    | PC-link Verification Screen               | 72 |

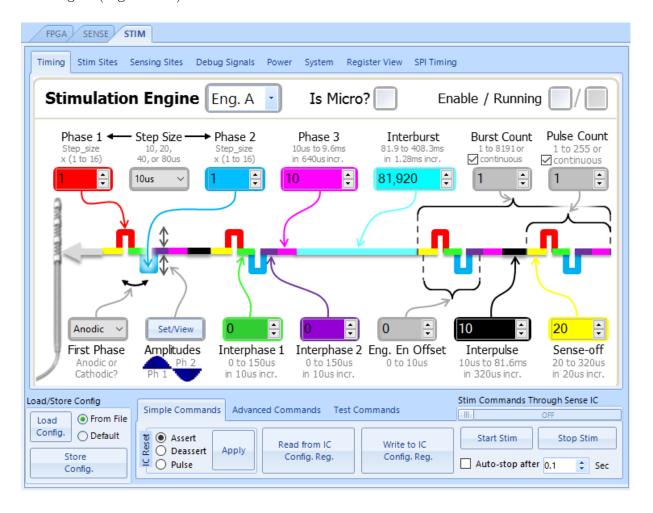

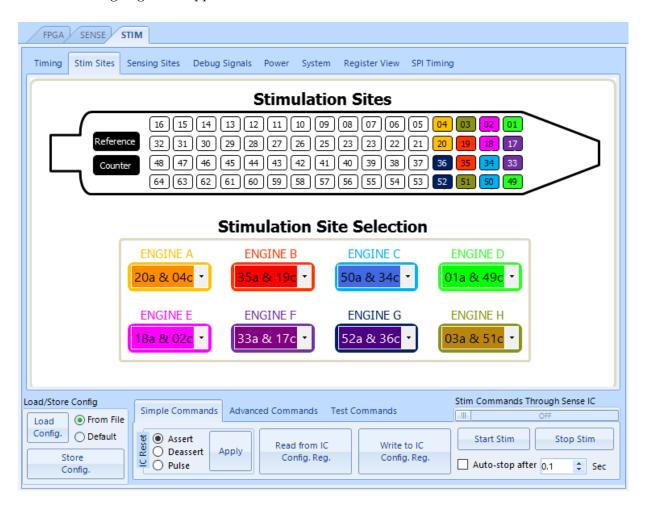

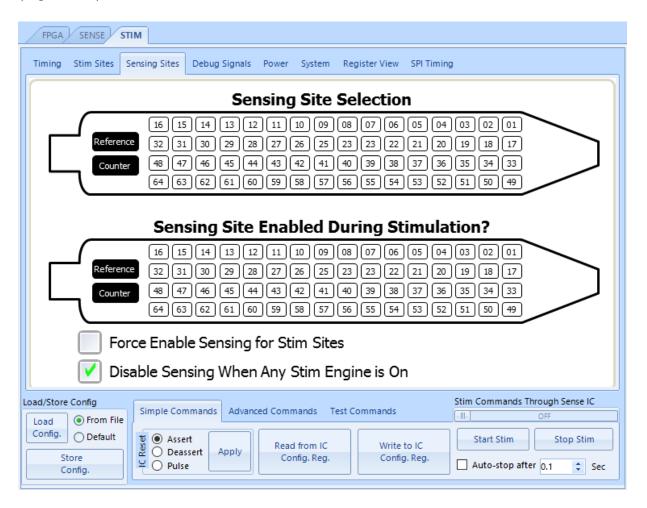

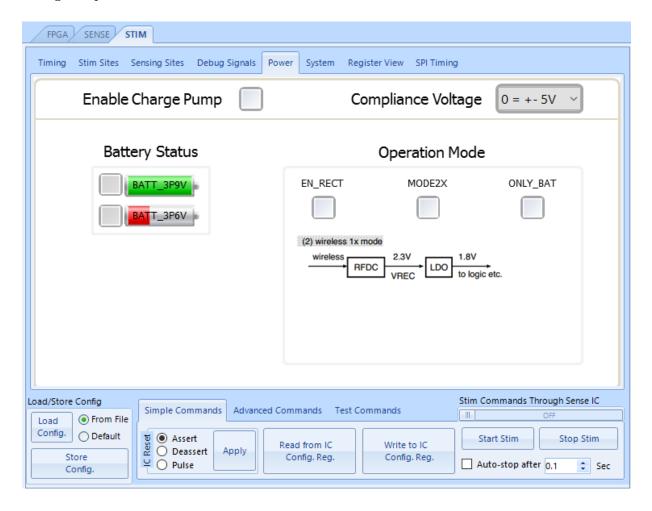

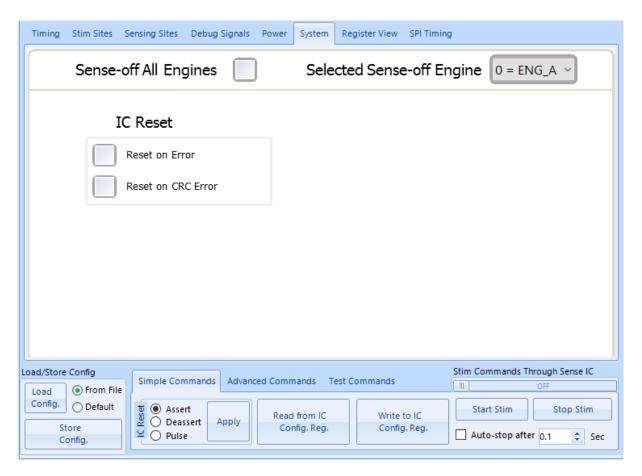

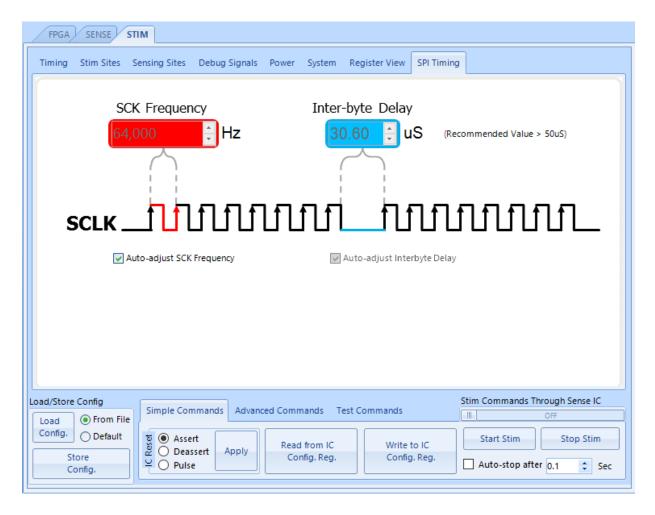

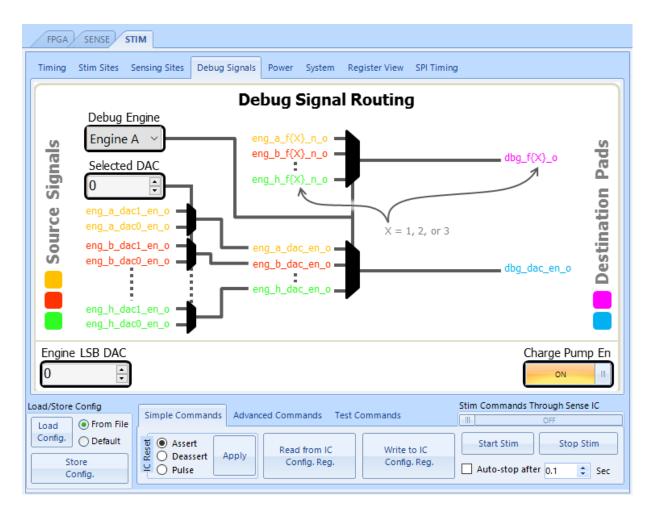

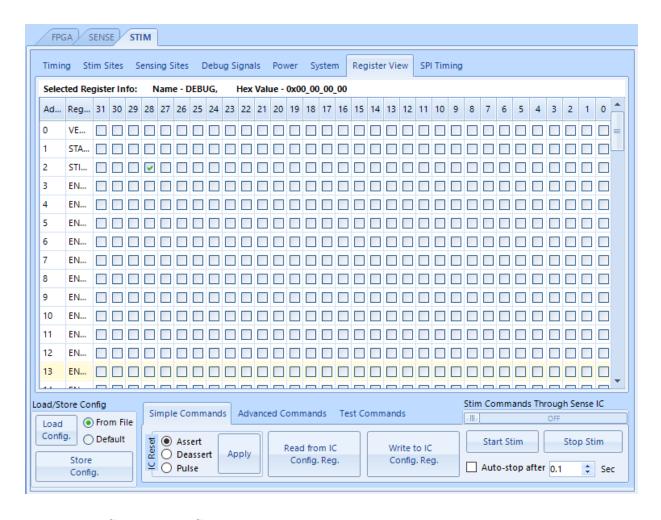

|     | 3.2.2.3    | The Stimulation IC Control Screen         | 74 |

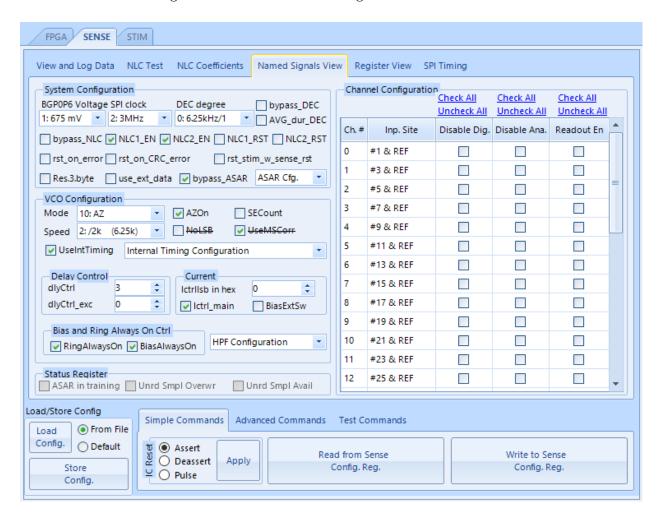

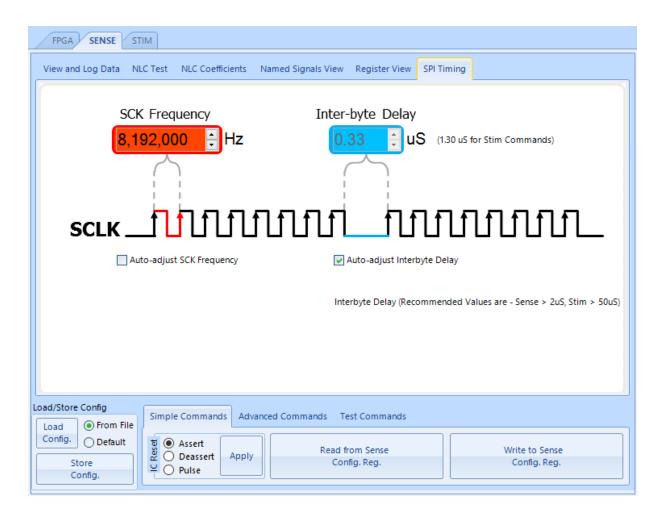

|     | 3.2.2.4    | The Sensing IC Control and Readout Screen | 82 |

| 4   | Conclusion | n                                         | 90 |

| 4   | 1 Sumn     | nary of Research Contributions            | 91 |

| 4   | 2 Futui    | re Work                                   | 94 |

| Ref | erences    |                                           | 96 |

# LIST OF FIGURES

| Figure 2.1 Traditional DBS IPG and probe implantation scheme (Medtronic Activa PC+S               |

|---------------------------------------------------------------------------------------------------|

| shown)5                                                                                           |

| Figure 2.2 Neuropace RNS responsive neuromodulation system and its implantation scheme[11]        |

| 6                                                                                                 |

| Figure 2.3 The proposed DBS system and its implantation scheme (left). Smart lead assembly        |

| (right)                                                                                           |

| Figure 2.4 Alternate system topology utilizing the proposed NMU                                   |

| Figure 2.5 Constant-voltage and constant-current rectangular stimulation pulses used in current   |

| DBS systems                                                                                       |

| Figure 2.6 Illustration of "blanked" neural sensing                                               |

| Figure 2.7 The top and bottom sides of v1 and v2 of the proposed NMU PCB assembly 16              |

| Figure 2.8 The NMU v1 PCB layers. Displayed from the top (#1) to bottom (#8) 17                   |

| Figure 2.9 SPI master connected to two SPI slaves. For avoiding contention, SSEL1 and SSEL2       |

| lines decide which slave drives the MISO line                                                     |

| Figure 2.10 Our scheme of controlling two (2) SPI slaves (sensing IC & stimulation IC) using only |

| three (3) wires                                                                                   |

| Figure 2.11 SPI communication controller processing the STIM_SELECT tokens (blue) 20              |

| Figure 2.12 Frequency and amplitude of the neural signals of interest                             |

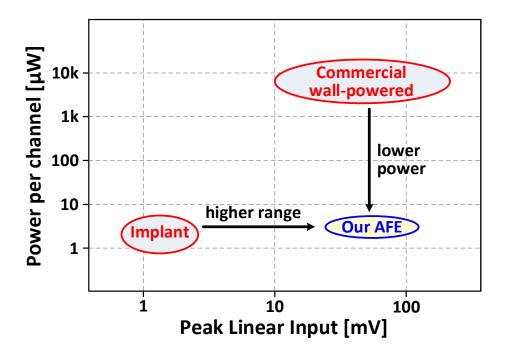

| Figure 2.13 Power and dynamic range tradeoff of a sensing front-end                               |

| Figure 2.14 Conventional sensing AFE vs. VCO-based AFE.                                           |

| Figure 2.15 Schematic of a VCO-based ADC used in our system                                       |

|---------------------------------------------------------------------------------------------------|

| Figure 2.16 Simulated voltage-to-frequency tuning curve of a VCO-ADC                              |

| Figure 2.17 Finding reverse frequency-voltage mapping of VCO ADC                                  |

| Figure 2.18 NLC engine architecture. Source-ready-in (srdyi) and source-ready-out (srdyo) signals |

| specify whether the input and the output of the NLC block are valid                               |

| Figure 2.19 Dividing the NLC curve into four sections                                             |

| Figure 2.20 Polynomial fitting performance of four-section NLC engine when utilizing different    |

| number of sections                                                                                |

| Figure 2.21 Polynomial fitting performance of NLC engine when varying the polynomial order.       |

| 31                                                                                                |

| Figure 2.22 Resulting SNR losses when ch0 NLC coefficients are applied across all other channels. |

|                                                                                                   |

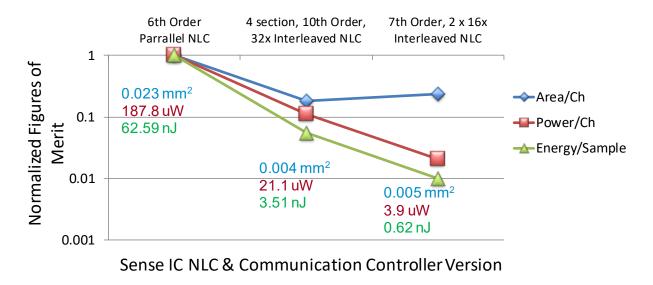

| Figure 2.23 Parallel implementation vs. data-stream interleaving architecture                     |

| Figure 2.24 Area and power of parallel, 16x interleaved, and 32x interleaved NLC engine designs.  |

|                                                                                                   |

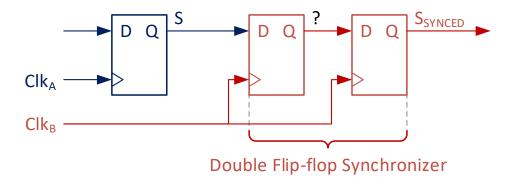

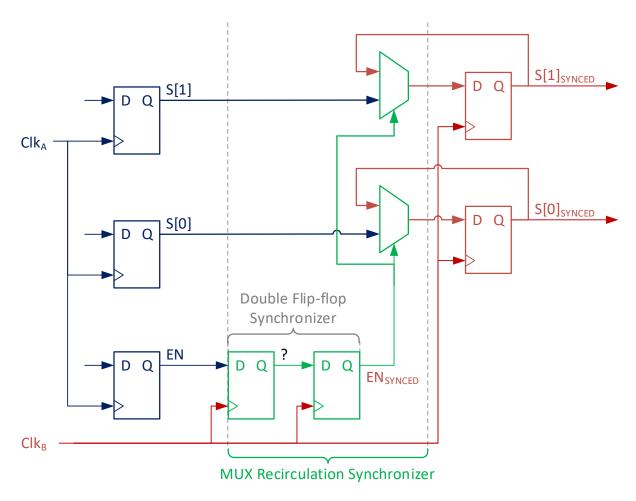

| Figure 2.25 Double flip-flop synchronizer                                                         |

| Figure 2.26 Architecture of the MUX recirculation synchronizer                                    |

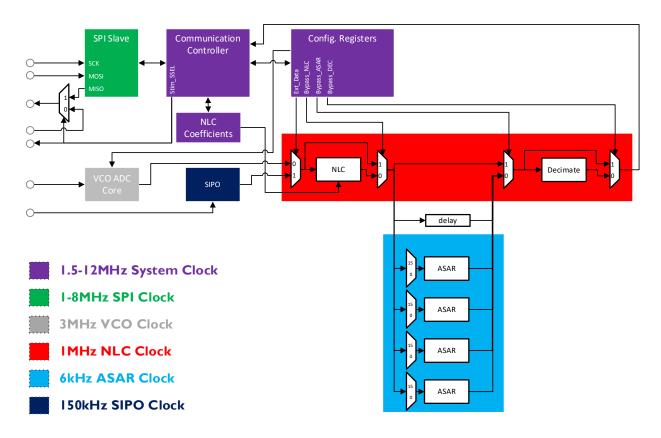

| Figure 2.27 Clock domain partitioning of sensing IC's digital subsystem                           |

| Figure 2.28 Sensing IC power consumption after clock domain partitioning and clock gating $40$    |

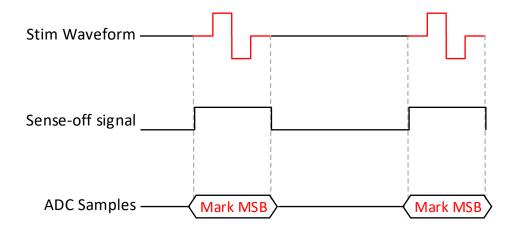

| Figure 2.29 Marking ADC samples based on a trigger signal (sense-off)                             |

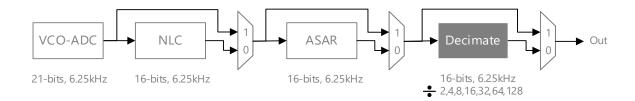

| Figure 2.30 Decimation block in the sensing IC signal chain                                       |

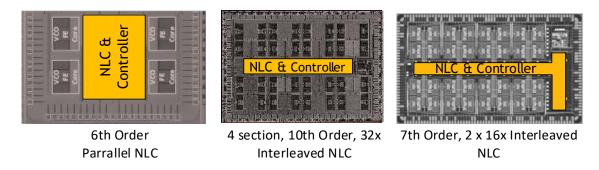

| Figure 2.31 IC micrographs of sensing IC v1, v2, and v3 (left to right). NLC and other digital     |

|----------------------------------------------------------------------------------------------------|

| blocks highlighted in orange                                                                       |

| Figure 2.32 Possibility of creating charge-imbalanced stimulation waveforms during frequent        |

| stimulation parameter updates                                                                      |

| Figure 2.33 Serial update of stimulation parameters                                                |

| Figure 2.34 Stimulation waveform generation with RHS2116                                           |

| Figure 2.35 Safe parameter update sequence in CSI021                                               |

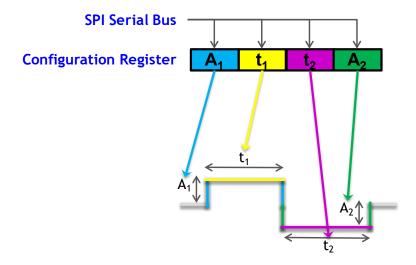

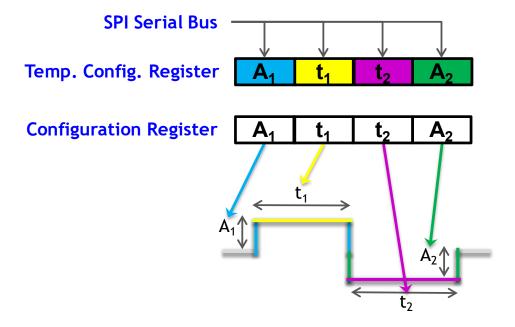

| Figure 2.36 Stimulation IC double-buffered configuration register illustration 50                  |

| Figure 2.37 Temporary-to-configuration register transfer mechanism                                 |

| Figure 2.38 Generation of a custom, non-rectangular pulse. The amplitude is modified based on      |

| stored values at each time-step spanning the pulse. The time-step resolution is also programmable. |

|                                                                                                    |

| Figure 2.39 Examples of custom, non-rectangular waveforms generated by our stimulation IC. 53      |

| Figure 2.40 Stimulation waveform programmability                                                   |

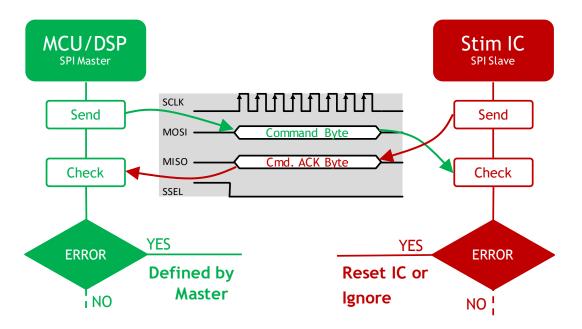

| Figure 2.41 Bidirectional error detection enabled by command, argument, and acknowledgment         |

| bytes checks                                                                                       |

| Figure 2.42 Packet structure for register write command. Data bytes are followed by two CRC        |

| bytes                                                                                              |

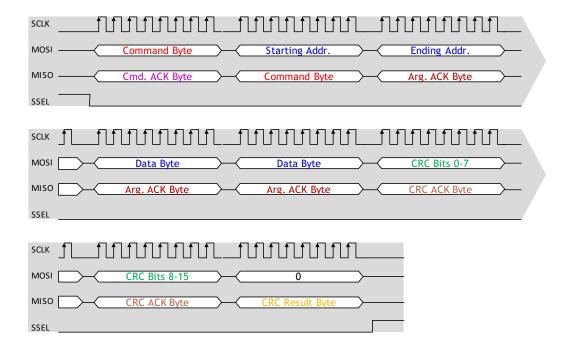

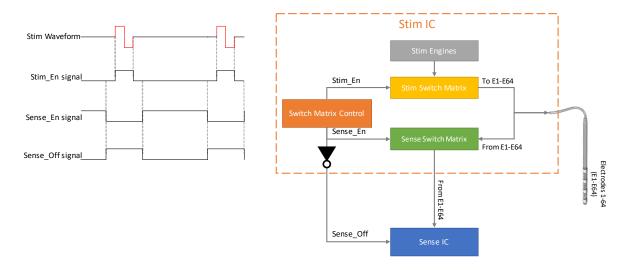

| Figure 2.43 Sensing and stimulation switch-matrices integrated into the stimulation IC 58          |

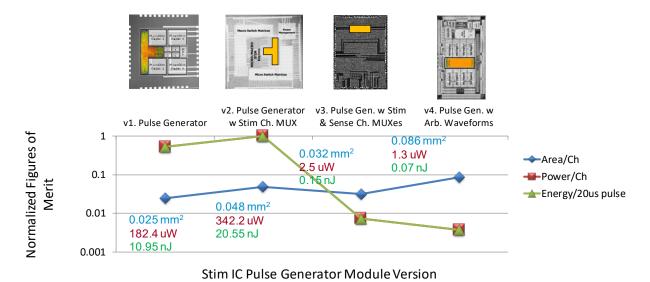

| Figure 2.44 Micrographs of stimulation IC v1, v2, v3, and v4 (top-left to top-right) along w     | /ith |

|--------------------------------------------------------------------------------------------------|------|

| their power and area figures (bottom chart). Digital subsystem is highlighted in orange, the ana | ılog |

| blocks in black-and-white are designed by Dejan Rozgic.                                          | . 59 |

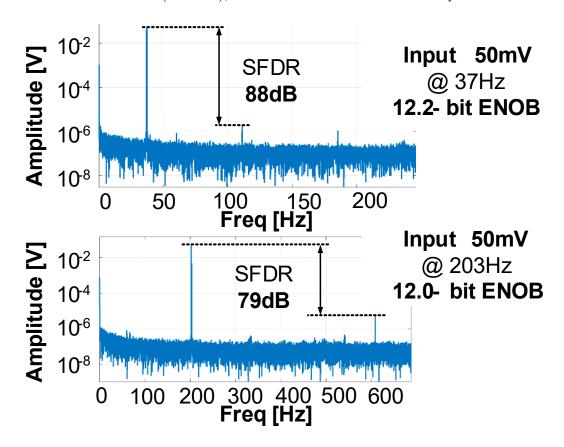

| Figure 3.1 Single-tone test for linearity                                                        | . 61 |

| Figure 3.2 Two-tone test for linearity.                                                          | . 62 |

| Figure 3.3 Temperature stability test setup                                                      | . 63 |

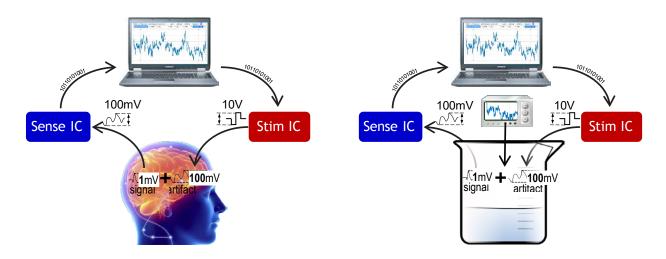

| Figure 3.4 Illustration of in-vivo (A) and In-vitro (B) functional verification setups           | . 64 |

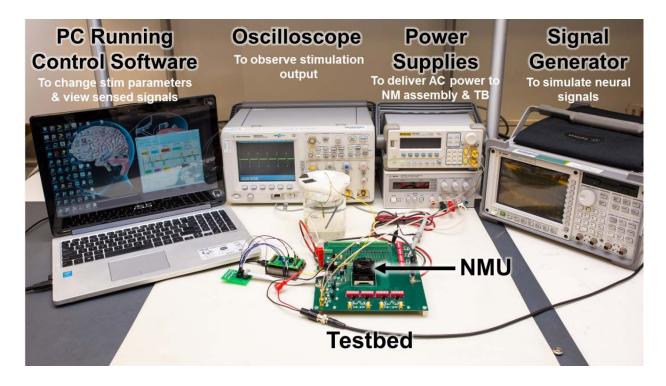

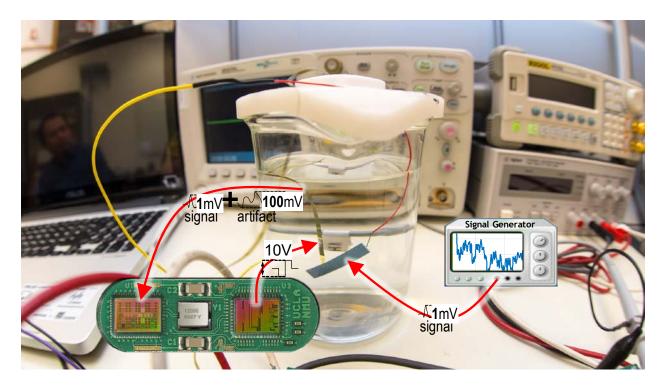

| Figure 3.5 Concurrent sensing and stimulation test setup.                                        | . 65 |

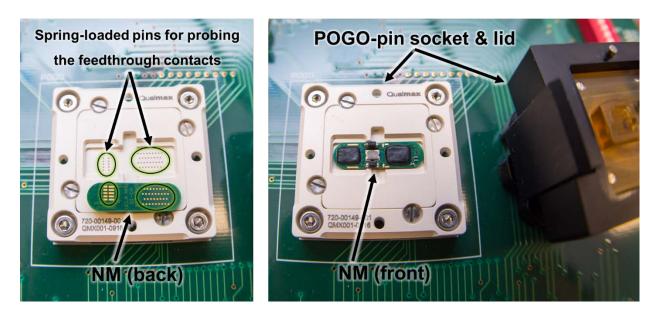

| Figure 3.6 Spring-loaded test socket housing the NMU.                                            | . 65 |

| Figure 3.7 Saline beaker containing the neural lead as well as the electrode injecting mimicle   | kec  |

| neural signals                                                                                   | . 66 |

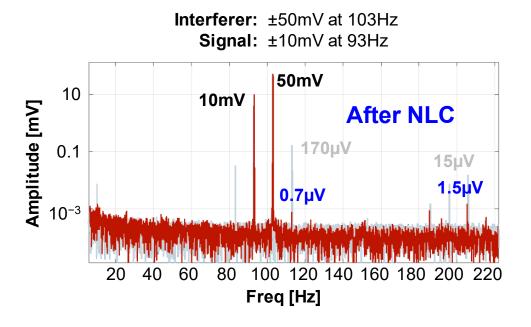

| Figure 3.8 Sensing in the presence of large interferers such as stimulation artifacts            | . 67 |

| Figure 3.9 PC-link dongle for PC to NMU communication.                                           | . 68 |

| Figure 3.10 PC to PC-link variable-length communication packet structure                         | . 69 |

| Figure 3.11 Simplified state machine diagram of the PC-link firmware                             | . 70 |

| Figure 3.12 The PC-link verification screen of the GUI                                           | . 73 |

| Figure 3.13 Stimulation timing configuration screen                                              | . 74 |

| Figure 3.14 Stimulation amplitude configuration screen.                                          | . 75 |

| Figure 3.15 Stimulation switch-matrix configurator.                                              | . 76 |

| Figure 3.16 Sensing site selection screen.                                                       | . 77 |

| Figure 3.17 Stimulation IC power management configuration screen.                                | . 78 |

| Figure 3.18 Stimulation IC system configuration screen                             | 79 |

|------------------------------------------------------------------------------------|----|

| Figure 3.19 Stimulation IC SPI timing configuration screen                         | 80 |

| Figure 3.20 Stimulation IC debug signal selection screen.                          | 81 |

| Figure 3.21 Stimulation IC register view.                                          | 82 |

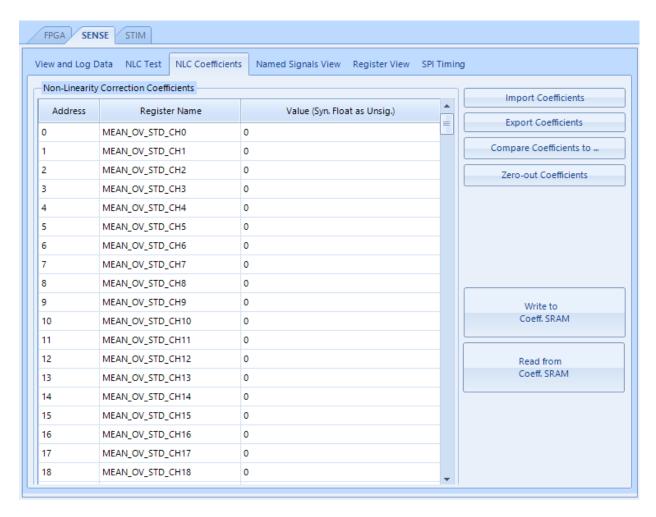

| Figure 3.22 Sensing IC NLC coefficient configuration screen                        | 83 |

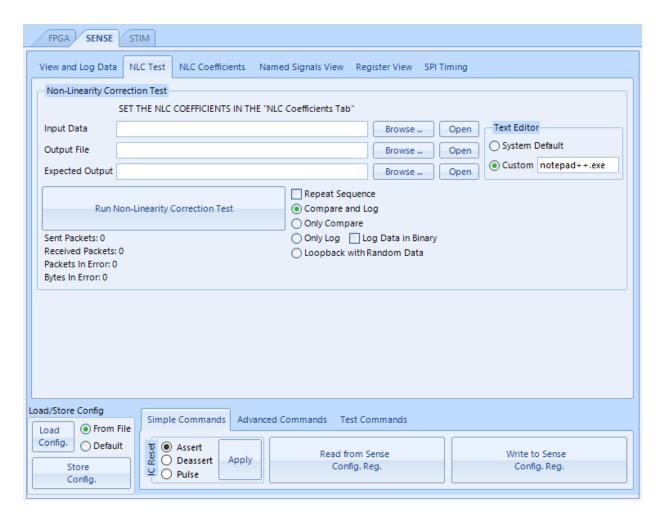

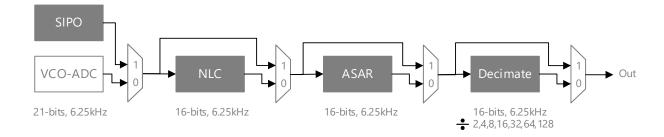

| Figure 3.23 Sensing IC screen for testing the NLC, ASAR, and decimation DSP blocks | 84 |

| Figure 3.24 Bypassing VCO-ADC for testing NLC, ASAR, and decimation DSP blocks     | 84 |

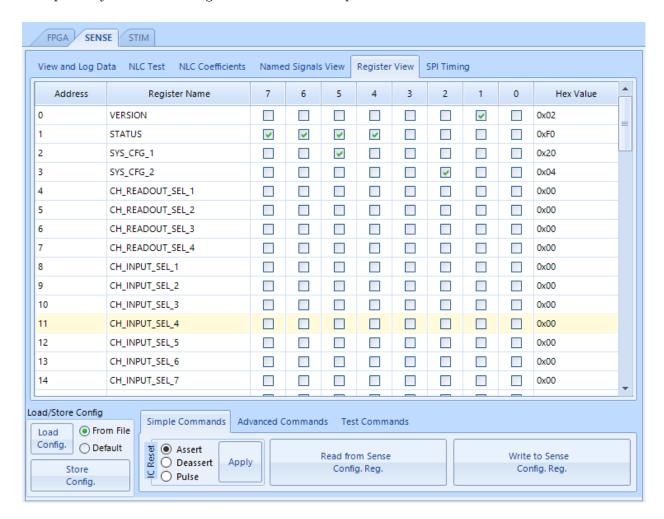

| Figure 3.25 Sensing IC register view screen.                                       | 85 |

| Figure 3.26 Sensing IC named-signals view screen.                                  | 86 |

| Figure 3.27 Sensing IC screen for viewing and logging ADC samples                  | 87 |

| Figure 3.28 Sense IC SPI timing configuration screen.                              | 89 |

# LIST OF TABLES

| Table 2.1 The proposed system's implantation scheme compared to traditional DBS and                       |

|-----------------------------------------------------------------------------------------------------------|

| Neuropace RNS implantation schemes. Cells highlighted in blue denote the qualitative advantage            |

| of a system for a given category8                                                                         |

| Table 2.2 Proposed NMU electronics compared to that of currently available commercial closed-             |

| loop neurostimulators. Cells highlighted in blue denote the qualitative or quantitative advantage         |

| of a system for a given category. *The proposed system has eight (8) independent stimulation              |

| engines, which can be mapped to 64 electrodes by modifying stimulation IC configuration register.         |

|                                                                                                           |

| Table 2.3 Proposed NMU electronics compared to academic closed-loop neurostimulators. Cells               |

| highlighted in blue denote the qualitative or quantitative advantage of a system for a given              |

| category                                                                                                  |

| Table 2.4 Power consumption of sensing IC v1 digital blocks operating at 12.288MHz and                    |

| fabricated with the TSMC45GP process. Cells highlighted in blue and red denote the main power             |

| consumption source and the main power component respectively                                              |

| Table 2.5 Power consumption of sensing IC v1 digital blocks synthesized at 12.288MHz for the              |

| TSMC40LP process. Note the total power of the entire design is $434\mu\mathrm{W},$ which is substantially |

| less (42.5%) than in the design fabricated with the TSMC45GP process                                      |

| Table 2.6 Comparison of our VCO-based sensing front-end with state-of-the-art biosignal front-            |

| ends. Cells highlighted in blue denote the linear input range allowing recording of LFP signals in        |

| the presence of large interferers and the price we pay in terms of power to achieve it                    |

| Table 2.7 Effective sampling rate after decimation                    | 43 |

|-----------------------------------------------------------------------|----|

| Table 2.8 Stimulation waveform programmability                        | 54 |

| Table 3.1 VCO ADC linearity drift over 0°C to +60°C temperature range | 63 |

#### ACKNOWLEDGMENTS

Many names come to mind that were directly or indirectly involved in supporting the work leading to this dissertation over the last few years. I am grateful to Divine Providence for placing me at UCLA, in Parallel Data Architectures Group led by Prof. Dejan Marković right at the time when the group had a growing interest in advancing the neuroengineering field. This also happened to be the time when the U.S. government deemed important to unlock "the mystery of the three pounds of matter that sits between our ears" [8] and announced the BRAIN initiative. The timing and the environment could not have been better for realizing the vision outlined in my university entrance application - designing autonomous implantable medical devices.

I am grateful to Prof. Dejan Marković for taking me under his wings during all these years, for providing me with guidance and financial support, and for giving me the freedom and the unique opportunity to participate in eight mixed signal IC designs. I am indebted to him for the digital circuit design and optimization knowledge that he imparted to me through his two classes – EE216A (Design of VLSI Circuits and Systems) and EE216B (VLSI Signal Processing). If it was not for his encouragement, on occasion or two, I could have quitted the Ph.D. program, and looking back I am thankful that he held me back.

I would like to thank Dr. Nader Pouratian, Dr. James Bisley, and Dr. Nanthia Suthana for their time and effort in serving on my Ph.D. committee and evaluating this work.

At Parallel Architectures Group, I was surrounded by much smarter people, who besides offering their fellowship, helped me in various aspects of this work. Dr. Vaibhav Karkare familiarized me with the digital ASIC flow and allowed me to design the packetization engine and

the wireless transceiver controller for the first version of the neural sensing IC. This neural sensing front end underwent three more iterations. Later, other system level blocks were added for system usability. Wenlong Jiang improved the VCO ADC core design, Sina Basir Kazeruni designed the adaptive stimulation artifact rejection (ASAR) DSP block, Hariprasad Chandrakumar designed the power-on-reset (POR) and crystal oscillator circuits. He also co-designed the low dropout voltage regulators with Weiyu Leng. Our visiting scholars Pinwen Su and Yinghua Hu helped me with the design documentation and testing of the nonlinearity correction (NLC) block. I would like to thank my colleague Dejan Rozgic for entrusting me with the design of digital infrastructure for the neural stimulator IC. For the last revision of this IC, we are grateful to our visiting scholar Dr. Ippei Akita who helped Dejan Rozgic with the analog circuit design. I would also like to thank Sam Barclay for designing NMU test PCB and Wenhao Yu for designing the second version of the NMU PCB.

Our collaborators from Lawrence Livermore National Laboratories helped us with the design and fabrication of the neural probes and implant encapsulation packages. I would like to specifically mention Sat Pannu, Kedar Shah, Vanessa Tolosa, Angela Tooker, Timir Baran Datta-Chaudhuri, and Razi-Ul Muhammad Haque for their contributions to this effort.

I would like to thank our group's administrative assistant – Kyle Jung, for being the person behind the scenes for many of us. To support us, the students, he went an extra mile beyond his responsibilities and many times we learned about those instances after the fact and from others.

Although my family was not directly involved in this work, they did their share of heavy lifting. My parents Albert and Svetik were my main encouragers and supporters for pursuing a

Ph.D. degree before I got married. My engineering bent is probably mostly due to my father, who programmed the first-generation computers that occupied an entire room and took me to his workplace on several occasions. Although an engineer herself, my mother wanted me to become a medical doctor. I hope that a biomedical engineering degree is a good compromise for both of them.

I have two feelings when thinking about my wife and three children during my Ph.D. student years – guilt and gratitude. My wife Anait had to put-off her graduate school plans, spent many lonely evenings when I was in the lab, double her parenting efforts, and among all these circumstances encourage me (thank you, sweetheart! I couldn't have done this without you). Our little wonders – Arpi, Emma, and Albert, never knew how many times they pulled me out of despair just by running up to me and hugging me when I came home at night (love you, my little ones!).

This work was funded by two of the DARPA BRAIN initiative programs – restoring active memory (RAM) and Systems-Based Neurotechnology for Emerging Therapies (SUBNETS)[9]. The views, opinions, and findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

### VITA

1997-2001 Management, Armenian State University of Economics, Yerevan, Armenia

2004-2008 B.S., Computer Engineering, California State University, Northridge, U.S.A

2008-2010 M.S., Electrical Engineering, California State University, Northridge, U.S.A

2011-2017 Ph.D. Candidate, Biomedical Engineering, University of California, Los Angeles, U.S.A

### **PUBLICATIONS**

W. Jiang, V. Hokhikyan, H. Chandrakumar, V. Karkare, and D. Marković, "A 50mVp Linear Input-range, VCO-based Neural Recording Front-end with Digital Nonlinearity Correction," in Proc. IEEE Int. Solid-State Circuits Conference (ISSCC'16), Feb. 2016, pp. 484-485.

W. Jiang, V. Hokhikyan, H. Chandrakumar, V. Karkare and D. Marković, "A ±50-mV Linear-Input-Range VCO-Based Neural-Recording Front-End with Digital Nonlinearity Correction," in IEEE Journal of Solid-State Circuits (JSSCC'17), vol. 52, no. 1, pp. 173-184, Jan. 2017.

D. Rozgic, V. Hokhikyan, W. Jiang, S. Basir-Kazeruni, H. Chandrakumar, W. Leng, D. Marković, (in press) "A True Full-Duplex 32-Channel 0.135cm<sup>3</sup> Neural Interface," in 2017 IEEE Biomedical Circuits and Systems Conference (BioCAS'17).

#### CERTIFICATIONS

Dec. 2011 Professional Engineer (PE) in Electrical Engineering, License E 19873, by State of California Board for Professional Engineers, Land Surveyors, and Geologists

# 1 Introduction

Many neuropsychiatric disorders do not have cures but are rather chronically managed by different treatment modalities during the patients' lifespan. Neuromodulation – a process of regulating neuronal populations through electrical stimuli is one of these treatment modalities and is chronically applied through deep brain stimulation (DBS) implants. These implants have come a long way since their introduction in 1960's. They are currently FDA approved to treat Parkinson's disease, essential tremor, and dystonia and are being studied for treating a host of other neurological disorders (Tourette syndrome, chronic pain, depression, obsessive-compulsive disorder, epilepsy, Alzheimer's disease, etc. [10]). However, the hardware delivering DBS has not changed substantially during these years. Standard DBS probes (Medtronic DBS 3387/3389) have four (4) large ring-shaped stimulation sites which result in pea-size or larger activation volumes. In most cases, only one of these sites is being utilized delivering fixed-frequency rectangular constant-voltage or constant-current stimulation pulses. This stimulation paradigm is applied in always-on, open-loop fashion, ignoring the disease state, medication status, or side effects. Constant application of same stimulation pulses to a neural target activates the habituation of that network and, as a result, the stimulation settings become less effective over time. This habituation effect is usually addressed by occasional clinical visits to re-adjust the stimulation parameters. This re-adjusting process is a little more complex for some neurological disorders due to the long response times. In the case of dystonia, it often takes weeks to observe the effectiveness of stimulation parameters and is thus a tedious process for both - the patient and the clinician. On the other hand, while the open-loop stimulation paradigm improves patients' quality of life in

most cases, it may cause side effects. Hallucinations, manic responses, low mood, anger, and even suicidal thoughts are some of the side effects of DBS. Thus, sending continuous electrical impulses without any mechanism to detect the effectiveness of therapy may be detrimental to patient's mental and physical well-being. The two main reasons why stimulation is not applied automatically based on the disease state are 1) the lack of sensing capability in implantable pulse generators (IPG), and 2) the knowledge gap about the disease biomarkers, where the latter is mostly due to the former. On the stimulation side, recent studies conducted to test the effectiveness of higher density probes (eight sites vs. four) show that the increase in spatial resolution can improve the therapeutic index and potentially result in lower power consumption for achieving the same therapeutic benefits[5]. The status quo of the traditional rectangular stimulation waveforms is also being challenged - some non-rectangular waveforms seem to be more energy efficient [6], [7]. Taking all these recent developments into account, in this work we present a more advanced neural implant which, while being backward compatible with traditional DBS therapy, 1) is capable of sensing neural signals while delivering stimulation for providing feedback to closed-loop algorithms, 2) has high-channel-count for increased spatial resolution, and 3) can deliver custom, non-rectangular stimulation waveforms for improved energy efficiency.

# 1.1 Organization of This Dissertation

Chapter two presents the system-level design of our closed-loop ready high-channel-count neuromodulation unit. In Section 2.1 the non-traditional system architecture of the implant is discussed, and its advantages over traditional neural implant architectures are presented. Section 2.2 describes the design of our VCO-based neural sensing IC and our solution for increasing its

dynamic range for capturing both neural signals and stimulation artifacts. Section 2.3 presents our stimulation IC paying attention to special considerations pertaining to closed-loop neurostimulators such as patient safety and waveform parameter updates. Non-rectangular waveform generation mechanism is also discussed. Chapter three focuses on the verification of the designed closed-loop ready high-channel-count neuromodulation unit. Section 3.1 presents the NMU performance tests while Section 3.2 describes the hardware, firmware, and software designed for the NMU verification.

# 2 System Design

As discussed in Chapter 1, currently available neuromodulation systems improve the quality of patient care. However, there are still areas where the introduction of a closed-loop, high-channel-count system could make a significant impact. This chapter presents the design of a neuromodulation system, which we believe addresses the current shortcomings of DBS. Although the main focus of this work is the electronics, system architecture and implantation schemes are briefly reviewed to justify the need for miniaturization of the electronics.

### 2.1 The Neuromodulation Unit

The proposed neuromodulation unit (NMU) houses our custom designed high-dynamic-range sensing front-end and stimulation ICs. The design of these components will be discussed in more detail in Sections 2.2 and 2.3. This section focuses on system-level design features, and how they compare to those of the existing closed-loop DBS systems.

#### 2.1.1 Nontraditional System Architecture

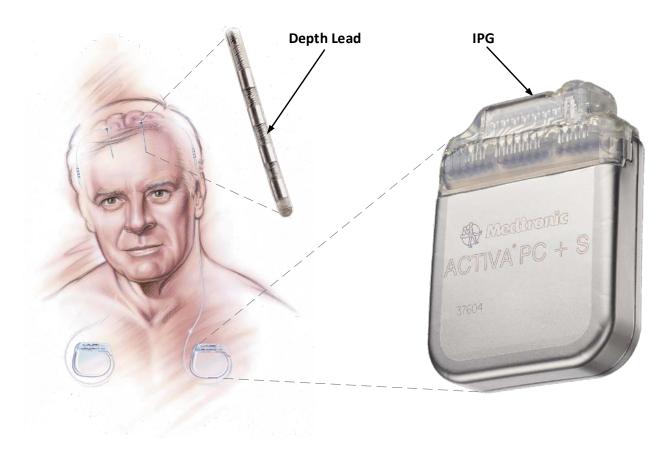

Traditional DBS implants consist of an IPG attached to a neural probe. After a small hole is drilled into the skull (burr hole), the neural probe is inserted through this hole to the neural target using stereotactic surgical techniques. The other end of the neural probe is routed under the skin to the upper chest area, where it connects to the implanted IPG (Figure 2.1). If more than one neural targets need to be stimulated, another pair of an IPG and a neural probe is implanted. This implantation scheme has been refined during the last several decades, works for several indications, and results in minimum amount of skull bone removal (burr hole).

Figure 2.1 Traditional DBS IPG and probe implantation scheme (Medtronic Activa PC+S shown).

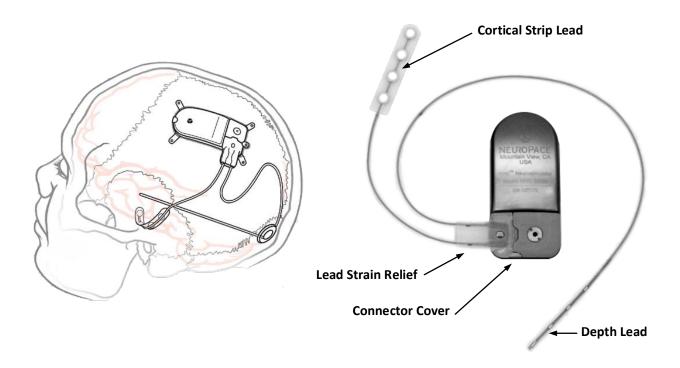

Since the introduction of Neuropace RNS neuromodulation system (November 2013), there is another implantation scheme in use – IPG is directly implanted in the cranium (under the scalp). This system has cortical and depth leads which are implanted in the area of the epileptic seizure focus. The depth lead is implanted through a burr hole using standard neurosurgical techniques. The cortical lead is implanted through craniectomy (removing part of the skull). This implantation scheme is targeted for epilepsy only and requires a significant amount of skull bone removal.

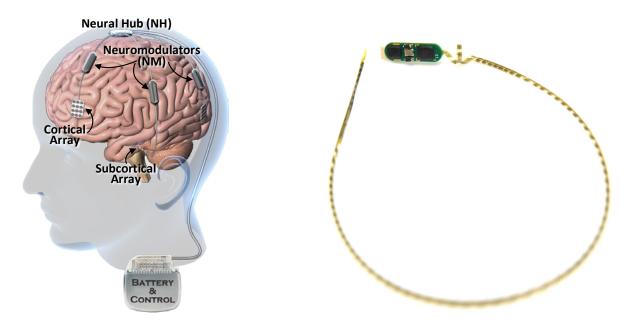

Figure 2.2 Neuropace RNS responsive neuromodulation system and its implantation scheme[11]. The proposed system is modular and has a slightly different implantation scheme. A neuromodulation unit (NMU) is connected to a neural probe and implanted epicranially next to the burr hole. Due to its small footprint, the NMU is affixed to the cranium by making a thin carving rather than removing it completely. The power and communication cable of the NMU is then routed to an aggregator module (AM) - also implanted epicranially using a small amount of cranial carving. If more than one neural targets need to be stimulated or recorded from, another neural probe and NMU pair (smart lead) can be implanted and terminated at the same AM. The cable running from AM to control module (CM) implanted in the chest, contains the power lines as well as the combined data stream from all NMU modules (Figure 2.3).

Figure 2.3 The proposed DBS system and its implantation scheme (left). Smart lead assembly (right).

### 2.1.2 Advantages of the Proposed System Architecture

When comparing our system to traditional DBS and Neuropace RNS implantation schemes in terms of surgical invasiveness, modularity, and proximity of the sensors and drivers to their neural targets, the following observations can be made (summarized in Table 2.1). The proposed implantation scheme becomes surgically less invasive than existing alternatives when three or more brain areas need to be targeted. This modular, distributed architecture allows increasing/decreasing the number of NMU satellites depending on a clinical application without modifying the system design. From the perspective of potential therapeutic effects, the main advantage of our system architecture compared to the DBS implantation scheme is the proximity of sensors and drivers to their neural targets. This advantage is less pronounced when comparing our system with Neuropace RNS since the latter is implanted in the cranium rather than in the chest. For sensing, proximity to the neural target means higher signal-to-noise ratio (SNR) and

for stimulation - lower power losses in cables. Reduced power leads to dissipating less heat inside the surrounding tissue, which according to American Association of Medical Instrumentation (AAMI) should not exceed 1-2°C for implanted medical devices.

Table 2.1 The proposed system's implantation scheme compared to traditional DBS and Neuropace RNS implantation schemes. Cells highlighted in blue denote the qualitative advantage of a system for a given category.

| Implant                                                         | Traditional DBS Implants (Medtronic Activa PC+S or similar)   | Neropace RNS                                                  | This work                                                               |

|-----------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|

| Surgical Invasiveness for One to Two Neural Targets             | Minimal                                                       | Maximal                                                       | Moderate                                                                |

| Surgical<br>Invasiveness for<br>Three or More<br>Neural Targets | Maximal                                                       | Maximal                                                       | Moderate                                                                |

| Modular?                                                        | No, for more neural targets an additional system is required. | No, for more neural targets an additional system is required. | Yes, for more neural targets only an additional smart lead is required. |

| Proximity of Sensors and Drivers to Neural Targets              | Minimal                                                       | Moderate                                                      | Maximal                                                                 |

### 2.1.3 Alternate System Topologies Utilizing Our NMU

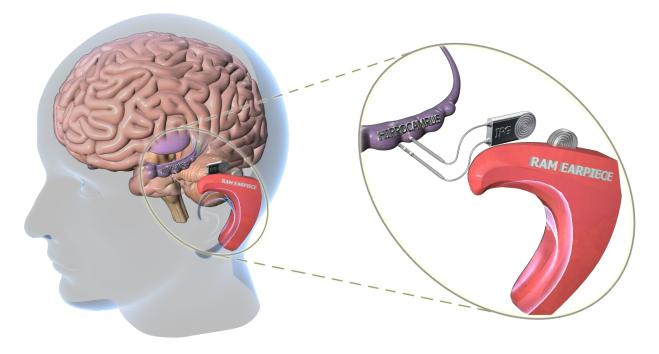

The modular architecture shown in Figure 2.3 can be used for treating many neuropsychiatric disorders. In cases where the stimulation and sensing targets are highly localized, one NMU will suffice for therapy, and alternate system architectures are possible. The system shown in Figure 2.4, for example, resembles cochlear implant architecture. It is conceptualized for short-term memory enhancement application, targets hippocampal region of the brain, and consists of a fully implanted miniature IPG housing NMU assembly along with a near-field wireless data transceiver. Since the power management unit (PMU) residing in the stimulation IC has a mode for receiving wireless inductive power, the addition of a coil is all that is required to break free of an implanted battery requirement and its periodic replacement surgeries. The power and control, in this case, are provided through the external earpiece hidden behind the ear.

Figure 2.4 Alternate system topology utilizing the proposed NMU.

### 2.1.4 Advantages of the Proposed NMU Electronics

When comparing our proposed NMU electronics with that of currently available commercial and academic closed-loop neurostimulators, several features stand out – high-channel-count, ability to generate custom, non-rectangular stimulation waveforms, and ability to sense during stimulation (Table 2.2 and Table 2.3). These features are discussed in Sections 0 - 2.1.4.3 in more detail.

Table 2.2 Proposed NMU electronics compared to that of currently available commercial closed-loop neurostimulators. Cells highlighted in blue denote the qualitative or quantitative advantage of a system for a given category. \*The proposed system has eight (8) independent stimulation engines, which can be mapped to 64 electrodes by modifying stimulation IC configuration register.

| Implant                                         | Medtronic<br>Activa PC+S                                     | Neropace RNS     | This work           |

|-------------------------------------------------|--------------------------------------------------------------|------------------|---------------------|

| No. of Stim. Channels                           | 4                                                            | 8                | 8 x 64*             |

| Output Current (mA)                             | 0-25.5                                                       | 6-11.5           | 0-5.1mA             |

| Compliance Voltage (V)                          | 10.5                                                         | 12               | 10                  |

| Frequency (Hz)                                  | 2-250                                                        | 1-333            | 2.4-16,667          |

| Pulse Width (µs)                                | 60-450                                                       | 40-1000          | 10-1280             |

| Custom, Non-<br>rectangular Stim.<br>Waveforms? | No                                                           | No               | ${f Yes}$           |

| No. of Sensing Channels                         | 4                                                            | 4                | 32                  |

| Simultaneous Sensing During Stimulation?        | Only for certain stimulation site and parameter combinations | No               | ${f Yes}$           |

| Battery Type                                    | Rechargeable                                                 | Non-rechargeable | Rechargeable        |

| Recorded Data<br>Monitoring                     | Wireless                                                     | Wireless         | $\mathbf{Wireless}$ |

Table 2.3 Proposed NMU electronics compared to academic closed-loop neurostimulators. Cells highlighted in blue denote the qualitative or quantitative advantage of a system for a given category.

| Reference    |                                                                                                                | [12]<br>ISSCC'13  | [13]<br>TBioCAS'15       | [14]<br>ISSCC'16           | This work                  |

|--------------|----------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------|----------------------------|

| Application  |                                                                                                                | Cortical          | Cortical                 | Spinal Cord                | Cortical /<br>Sub-cortical |

| Implant Size |                                                                                                                | $>3\mathrm{cm}^3$ | N/A                      | $0.5\mathrm{cm}^3$         | $0.135\mathrm{cm}^3$       |

| Stimulation  | No. Channels / Engines                                                                                         | 8 / 1             | 8 / 1                    | <b>160</b> / <b>40</b>     | 64 / 8                     |

|              | Stim. Mode                                                                                                     | Current           | Voltage                  | Current                    | Current                    |

|              | Custom, Non-<br>rectangular Stim.<br>Waveforms?                                                                | No                | No                       | No                         | Yes                        |

|              | Max. Current / Resolution                                                                                      | 30μA (fixed)      | 0.23mA / 5-bits          | $0.5 \mathrm{mA}$ / 7-bits | 5.1mA / 8-bits             |

|              | $\begin{array}{c} \mathbf{Max.\ Freq\ /} \\ \mathbf{Pulse\text{-}width\ /} \\ \mathbf{Resolution} \end{array}$ | N/A               | 220Hz / 440µs /<br>40 µs | 20kHz / 8ms<br>/ 10 μs     | 20kHz / 1.26ms<br>/ 10μs   |

| Sensing      | No. of Channels                                                                                                | 8                 | 8                        | 16                         | 32                         |

|              | Simultaneous Sensing During Stimulation?                                                                       | No                | No                       | No                         | ${ m Yes}$                 |

|              | $egin{aligned} 	ext{Linear Input} \ 	ext{Range } (	ext{mV}_{	ext{pp}}) \end{aligned}$                          | 10                | 1                        | 36                         | 100                        |

|              | SFDR                                                                                                           | N/A               | N/A                      | N/A                        | 81dB                       |

|              | ENOB (bit)                                                                                                     | 9.57              | 6.5                      | 8.5                        | 12.8                       |

|              | $\begin{array}{c} \textbf{Integrated Noise} \\ \textbf{($\mu$V$_{RMS}$)} \end{array}$                          | 5.23              | 1.97                     | 7.68                       | 4                          |

|              | Area/Ch. (mm <sup>2</sup> )                                                                                    | 0.38              | 0.35                     | N/A                        | 0.12                       |

|              | Signal BW (Hz)                                                                                                 | 1-7k              | 500-3k                   | 1-7k                       | 1-250                      |

#### 2.1.4.1 High-Channel-Count

Standard DBS probes (Medtronic DBS 3387/3389) have four (4) large ring-shaped stimulation sites which result in pea-size or larger activation volumes. Recent studies conducted to test the effectiveness of higher density leads (eight electrodes vs. four) show that the increase in spatial resolution can improve the therapeutic index and potentially result in less power consumption to achieve the same therapeutic benefits[5]. The Medtronic-Sapiens lead is currently the highest density probe in the industry and is being investigated for its therapeutic benefits. It is currently unclear, however, how the Medtronic-Sapiens electrodes are going to be paired and programmed. Neither Medtronic nor its competitors offer an IPG with such high channel count to be used with this probe. Our single NMU electronics can interface with 64-electrode leads, simultaneously sense neural data from 32 channels, and deliver eight (8) independent stimulation waveforms multiplexed to 64 neural sites. As a comparison, the two neurostimulators in the market with sensing capability - Neuropace RNS and Medtronic PC+S, can sense from four (4) channels only[15], and the highest number of stimulation sites in commercial DBS IPGs is 16.

#### 2.1.4.2 Non-Rectangular Waveforms

Currently available DBS IPGs deliver therapy in the form of rectangular shaped pulses (Figure 2.5). There are two approaches to controlling these pulse amplitudes – 1) constant-voltage, and 2) constant-current. Constant-voltage IPGs output fixed voltage during the stimulation, regardless of electrode-tissue impedance changes. If electrode-tissue impedance changes over-time (e.g., scar tissue formation), a constant-voltage pulse will deliver varying levels of current (hence charge) to the neural target. This change will result in a different therapy than initially programmed and

will need to undergo a readjustment by a clinician. Constant-current IPGs will vary the pulse voltage to attain the programmed amount of current up to a maximum value (compliance voltage). The electronics for these IPGs is a little more complex; however, constant charge injection into the neural target is ensured.

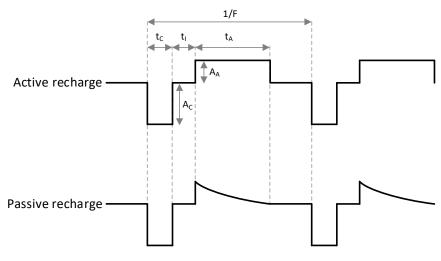

F - Stimulation frequency

t<sub>C</sub> - Duratin of cathodic phase

$t_{l} \quad \text{- Interphase delay} \quad$

$t_{\text{A}}~$  - Duration of anodic phase

$A_C$  - Amplitude of cathodic phase

A<sub>A</sub> - Amplitude of anodic phase

Figure 2.5 Constant-voltage and constant-current rectangular stimulation pulses used in current DBS systems.

Rectangular shaped pulses have become the de-facto standard for neural stimulation since the inception of the neuromodulation field. The reason behind this decision is not the effectiveness of delivered therapy but perhaps has to do with the ease of generating such pulses from the engineering perspective. As a result, the strength-duration curves and charge injection capacities of neural electrodes are defined for rectangular pulses. Recent studies challenged the status quo of the traditional rectangular stimulation waveforms and found that some non-rectangular waveforms seem to be more energy efficient [6], [7]. It is hard to assess additional clinical benefits

of non-rectangular stimulation pulses due to the lack of hardware capable of generating such waveforms. To provide maximum flexibility to the pioneers of the neuromodulation field, our NMU electronics features non-rectangular constant-current biphasic waveform generation with selectable coarseness settings (Figure 2.39). Traditional rectangular stimulation pulses are also supported.

#### 2.1.4.3 Simultaneous Sensing and Stimulation

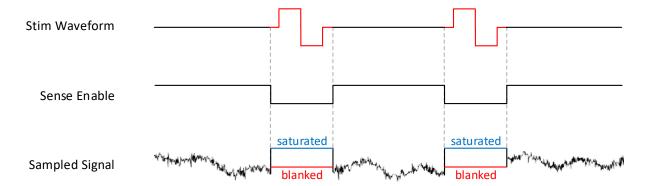

Among currently available DSB implants, only two have neural sensing capability – Neuropace RNS and Medtronic PC+S. Neuropace RNS is an FDA-approved device that targets epilepsy and can record from up to four (4) electrodes simultaneously. Although the electrical specifications of the recording analog front end are not revealed, the user manual talks about the saturation events while sensing and their elimination from processing algorithms by using saturation event detectors[11]. Signal saturation is due to an insufficient dynamic range of the recording analog front end, and can be prevented by disconnecting sensing amplifiers from the signal source - "blanking" (Figure 2.6). "Blanking" of course results in data loss and is probably employed by Neuropace RNS during stimulation based on device functionality illustration[16].

Figure 2.6 Illustration of "blanked" neural sensing.

Medtronic PC+S is an investigational device not yet approved by FDA and is meant to be used for research purposes[17]. This device can simultaneously sense LFP signal from four(4) channels while stimulating[18]. However the caveat is that a specific electrode configuration and stimulation parameters should be used[15].

Our NMU allows simultaneous sensing of LFP signals from 32 channels while stimulating without "blanking" or restrictions on recording sites and stimulation parameters. Since our sensing front end captures neural signals along with stimulation artifacts, it can help to understand probed neural network's dynamics during stimulation. More neuronal populations can be investigated for biomarker content around the implanted probe due to the absence of recording site selection restrictions. Lastly, patient therapy will not need to be compromised due to a limited set of stimulation parameters.

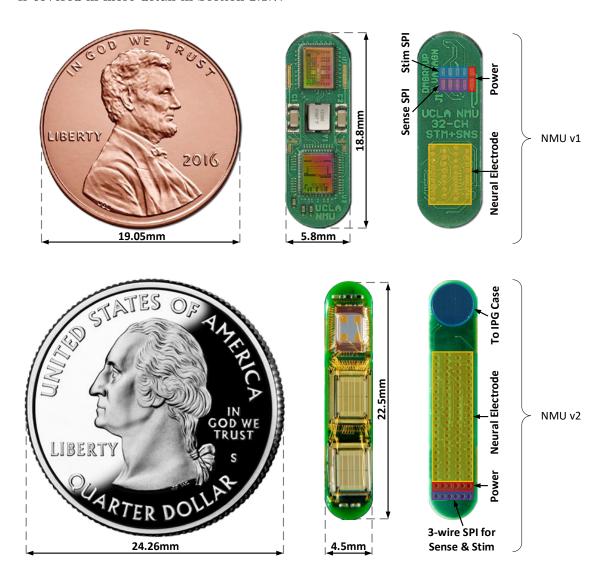

## 2.1.5 NMU Physical Dimensions

Two versions of NMU printed circuit board assemblies (PCBA) were designed (Figure 2.7). The NMU PCBA v1 was assembled with earlier versions of the stimulation and sensing ICs which were designed for 32-electrode neural probes. The NMU PCBA v1 is smaller than a penny (18.8mm x 5.8mm x 1.8mm) and occupies about 135mm<sup>3</sup> of volume. The stimulation and sensing ICs along with only six (6) passive components are placed on the top side of the printed circuit board (PCB), while the bottom side is reserved for power, communication, and neural electrode connections. The 180° phase shifted AC power is delivered through two (2) conductors located near the communication lines. In this version of the NMU PCBA, communication with the sensing and stimulation ICs is achieved through three (3) and four (4) line serial peripheral interfaces (SPI)

respectively. The neural interface consists of 34 pads – 32 for neural targets and two for "common" and "reference" electrodes. The NMU PCBA v2 is smaller than a quarter (22.5mm x 4.5mm x 2mm), and was designed by Wenhao Yu for 64-electrode neural probes. This version shares the same topology as v1 - components on top and implant feedthrough contacts at the bottom. The communication section of the feedthrough differs from that of v1 – stimulation and sensing ICs both share a 3-wire SPI interface instead of using two separate SPI interfaces. This design change is covered in more detail in Section 2.1.7.

Figure 2.7 The top and bottom sides of v1 and v2 of the proposed NMU PCB assembly.

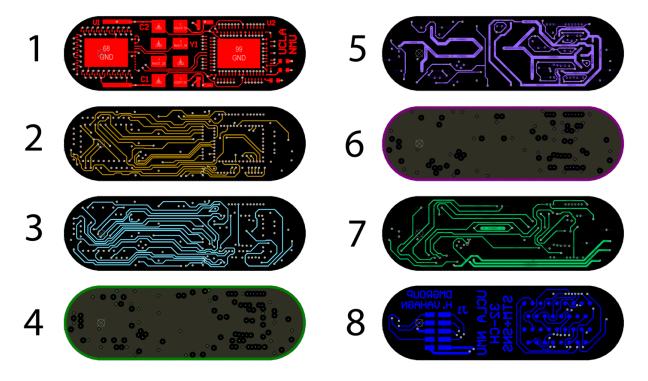

## 2.1.6 NMU PCB Design

The NMU PCB required advanced features for fabrication largely due to very small form-factor and the high number of interconnections between the stimulation IC, sensing IC, and the neural lead feedthrough interface. The eight-layer PCB is 31mil with 3mil minimum spacing, 3mil minimum track width, and uses blind-and-buried vias for routing. The board was surface finished with electroless-nickel-electroless-palladium-immersion-gold (ENEPIG) coating both for ease of sensing and stimulation IC wire-bonding as well as for neural probe attachment process compatibility.

Figure 2.8 The NMU v1 PCB layers. Displayed from the top (#1) to bottom (#8).

When routing two traces close to each other, the current flowing through one trace (aggressor) induces a current in the other trace (victim). This "crosstalk" can cause undesirable effects in the circuitry at the victim node. For this reason, potential aggressor traces were shielded from

surrounding victim traces located on the same layer. Since the AC power signals were high on the list of aggressor traces (5Vpp, 1MHz), they were grouped in one power layer, and besides being isolated from other power traces on that layer, they were also shielded from the layers above and below by two ground planes (Figure 2.8).

## 2.1.7 Using Three Wires for Communicating with Two SPI Slaves

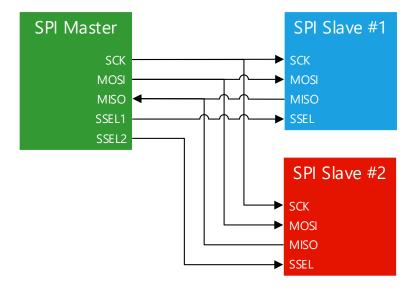

Both sensing and stimulation ICs are implemented as SPI slaves. When only one SPI slave is connected to an SPI master, the minimum number of required physical lines is three (3) – serial clock (SCK), master-out-slave-in (MOSI), master-in-slave-out (MISO). When connecting additional SPI slaves to the system one slave-select (SS) signal should be added for each slave. For a two-slave configuration, this brings the number of needed physical conductors to five (5) (Figure 2.9).

Figure 2.9 SPI master connected to two SPI slaves. For avoiding contention, SSEL1 and SSEL2 lines decide which slave drives the MISO line.

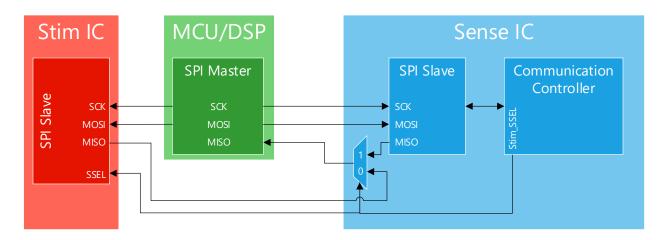

Assuming four (4) NMU assemblies per system, the number of physical conductors running from NMU to the AM module just for digital communication will be 20. This may not seem many, but the feedthrough-interconnect takes significant space on the AM package. To reduce this space and make the AM smaller, while conforming to the regular SPI bus specifications we came up with a new multiplexed bus architecture based on SPI which allows two (2) slave communication only through three (3) wires instead of five. This modification reduced the number of physical conductors running from NMU to AM from 20 down to 12 (Figure 2.10).

Figure 2.10 Our scheme of controlling two (2) SPI slaves (sensing IC & stimulation IC) using only three (3) wires.

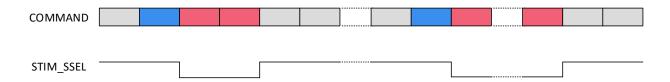

This low-pin-count SPI bus was achieved by the introduction of a small overhead in the communication protocol. In the case of the conventional SPI communication, the asserted SS line tells the slave that it was selected for data exchange. The data from the master is then transferred through the MOSI line, and the slave sends a simultaneous reply on the MISO line. In our case, we assigned the sensing IC to be the communication gateway. The SPI communication controller (SCC) hosted in this IC assumes that as a slave it is always selected and passes the received SPI bytes through its decoding logic. When an SPI packet starts with a STIM SELECT token (0x22),

then the SCC asserts the SS line of the stimulation IC and selects the reply of the stimulation IC (MISO) for routing to the SPI master (MCU located inside the AM) (Figure 2.11). The SCC will also set itself in the pass-through mode and not process the upcoming packet bytes. When the packet does not start with a STIM\_SELECT token, then the SCC assumes the communication is addressed to the sensing IC and processes the following packet bytes.

Figure 2.11 SPI communication controller processing the STIM SELECT tokens (blue).

#### 2.1.7.1 Absence of SPI SSEL Signal and Recovery from Partial Packets

The above-described custom SPI communication protocol works for well-formed packets. This cannot be assumed to be the case all the time, and the corresponding risks need to be mitigated at the SCC level. Let's assume the SPI master starts sending a packet to one of the NMUs, but due to some system malfunction only part of the packet is transmitted, or due to noisy environment extra unintended data bits are shifted into the NMU's receive buffer. Regardless of how the current packet will be processed, the next packet will be out of synchronization between AM and NMU. With a conventional SPI protocol, the SS line takes care of these scenarios by indicating to the internal SPI slave finite state machine (FSM) that it is about to receive the first byte in the packet. This is the reason why many single slave systems will still employ the four-line SPI (adding the SS line), even though they can get away with only three lines. To recover from partial packets, the proposed SCC employs a timeout counter for receiving packet contents.

A 100ms timeout activates after each received packet byte. If all packet bytes are received, the

timeout counter deactivates. However, even if one byte is not received, the timeout event will trigger 100ms after the last byte, and the slave FSM will return to initial state. Before returning to the initial state, the slave FSM can also reset the IC if the RESET\_ON\_ERROR option is set in the configuration register.

## 2.2 The High-Dynamic-Range Sensing IC

Our high-dynamic-range sensing front-end enables the proposed system to concurrently capture both – neural signals of interest and stimulation artifacts. This section outlines why that is challenging for low-power neural sensors required for implants, and presents our solution.

#### 2.2.1 Challenge of Capturing Neural Signals and Stimulation Artifacts

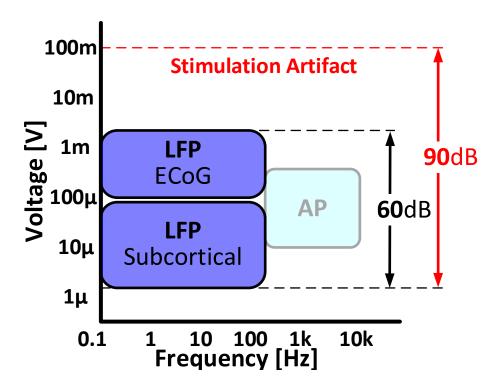

The two types of neural signals that can be accessed through implanted neural probes are local field potentials (LFP) and action potentials (AP) (Figure 2.12). APs are also known as single-units and as the latter name implies contain information about the activity of single (or several) neurons. APs are thus highly localized, and in order to convey information about a specific neural network state, very-high-channel recording is needed followed by a digital signal processing engine for integration. Another factor that makes APs impractical for implanted system usage is the over-time scar tissue formation around the ultra-fine electrodes. The latter dramatically decreases the signal quality of the recordings rendering them useless. LFPs, on the other hand, contain information about the dynamics of large groups of neurons, are recorded from much larger electrodes, and are less prone to the over-time signal degradation. These factors make LFPs a more preferable choice for implanted systems.

Figure 2.12 Frequency and amplitude of the neural signals of interest.

LFPs span a bandwidth of 0.1-100Hz, and an amplitude of 1μV-1mV. Thus, an analog-front-end (AFE) designed to capture LFPs should have a dynamic range of about 60dB. The LFPs are, however, not the only electrical signals present in a DBS implanted brain. The therapeutically injected stimulation pulses can induce up to 100mV signals into the same neural tissue from which neural sensing is performed. This would cause the signal chain to saturate. Until the stimulation artifacts are removed and the AFE recovers from saturation, all the neural signal information will be lost. To avoid this, one could of course design an AFE with sufficient dynamic range to capture both the neural signals and the stimulation artifacts. The challenge is that a typical implant battery can not sustain the amount of power required to operate this circuit. Technological innovation is required to achieve the required dynamic-range while consuming implant-level power (Figure 2.13) - which is exactly what our sensing front-end does.

Figure 2.13 Power and dynamic range tradeoff of a sensing front-end.

## 2.2.2 Our Sensing Front-End Architecture

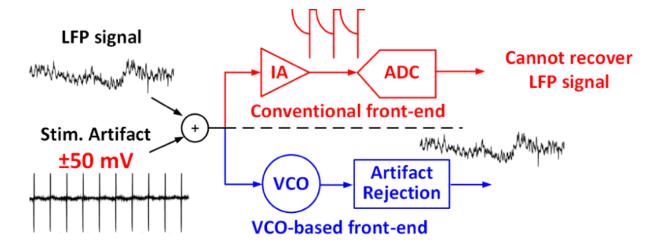

Conventional neural sensing front-ends are optimized for recording neural signals only[19],[20],[21]. Prior to conversion, these AFEs are typically proceeded with a large gain instrumentation amplifier (IA) stage. The IA stage provides a high input impedance and also high input gain, which relaxes the noise requirement - hence power consumption, for the next stages. Inputs that exceed the designed input range will result in signal saturation which can take tens of milliseconds to recover given the large time constants involved in neural recording. This is the main reason why some systems do not even attempt recording while stimulation is on ("blanking"). A solution proposed by Vaibhav Karkare [22] and later improved by Wenlong Jiang [23] is as follows. VCO-based ADCs rely on phase-domain increments of the oscillator output. Since there is no physical bound on the maximum phase of a waveform, the output of a VCO-ADC is not prone to saturation (Figure 2.14).

Figure 2.14 Conventional sensing AFE vs. VCO-based AFE.

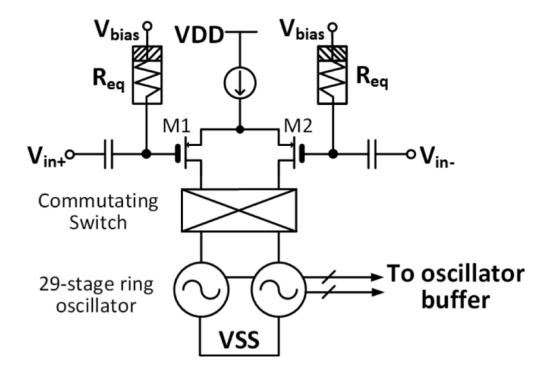

Figure 2.15 shows the high-level schematic of the mentioned VCO-based ADC. The design of this ADC is not going to be discussed in this work, for more details refer to V. Karkare's and W. Jiang's publications[22],[23].

Figure 2.15 Schematic of a VCO-based ADC used in our system.

## 2.2.3 Challenges of Using VCO ADCs for High-Resolution Applications

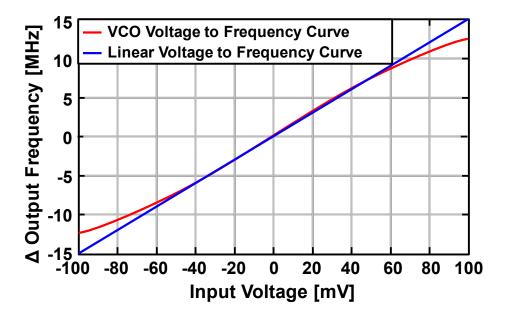

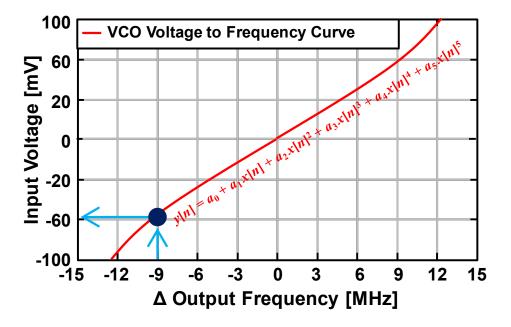

While the selected VCO-ADCs architecture is not prone to saturation, it does not have a linear voltage-to-frequency tuning curve (Figure 2.16). This limits the effective resolution of the VCO ADC to approximately seven (7) bits and makes it unsuitable for simultaneous recording of neural signals and stimulation artifacts. The good news is, however, that this nonlinearity can be corrected post-conversion. In general, two calibration methods can be applied – 1) foreground, and 2) background. For foreground calibration, a mapping function is applied in a feedforward fashion on the conversion results. Background calibration, on the other hand, has a feedback loop which updates the mapping function periodically to ensure mapping function didn't drift over time. Accuracy-wise this method is preferable to foreground calibration however it requires more power and silicon area. Foreground calibration, on the other hand, can be realized with simpler building blocks if mapping drift can be accounted for. The contributors of VCO nonlinearity are 1) the nonlinear voltage-to-frequency relationship, 2) VCO supply voltage variations, 3) temperature and 4) the physical aging of the circuit. Since the voltage-to-frequency relationship is time-invariant, the supply voltage can be easily fixed using a low-dropout (LDO) voltage regulator, and the effects of aging contribute very little to the overall nonlinearity and can be manifested after many years of constant operation, the main remaining contributor of the mapping drift is the operating temperature variation. As an implanted neural implant, the entire electronics is going to be housed inside human body which has a temperature stability of about  $\pm 2^{\circ}$ C. Given a typical VCO temperature sensitivity of 50ppm/C[24], the introduced readout drift of 100ppm will be buried under the noise floor of a 13 effective number of bits (ENOB) ADC. For all the mentioned reasons, the foreground nonlinearity calibration is acceptable for an implantable neural recording system.

Figure 2.16 Simulated voltage-to-frequency tuning curve of a VCO-ADC.

## 2.2.4 Previously Used Methods for VCO ADC Nonlinearity Correction (NLC)

Over time different methods have been proposed to improve the linearity of VCO-based quantizers. In [25] the VCO-based quantizer linearity is improved by placing it inside a continuous time sigma-delta feedback loop. Another approach is using a replica VCO to perform correlation based background calibration [26]. In [27] and [28] a look-up table is used to invert the nonlinearity of the ADC. In a high-channel-count system, however, replica VCOs and look-up tables (LUT) will take a significant area. For example, our 32-channel ADC with a raw resolution of 21-bits and expected output resolution of 15-bits will require a memory with 32 x 2<sup>21</sup> locations and 15bits of word length. Assuming 0.124µm<sup>2</sup> [29] for 6T SRAM cell area, 124.8mm<sup>2</sup> silicon area will be

needed, which is prohibitively large. For comparison, each VCO ADC core takes only  $0.12 \mathrm{mm}^2$  silicon area.

# 2.2.5 The Proposed NLC Approach – Foreground Calibration Using a Polynomial Computation Engine

Provided that the VCO-ADC maintains monotonicity in its transfer function, this nonlinearity can be corrected by learning and inverting the VCO tuning curve. A nonlinear function such as a polynomial can be mapped to this inverted tuning curve (Figure 2.17). Using this foreground calibration approach, we will need to store only the polynomial coefficients; however, we need to calculate polynomial function value for each ADC sample.

Figure 2.17 Finding reverse frequency-voltage mapping of VCO ADC.

## 2.2.5.1 Engine Order and Hardware Implementation

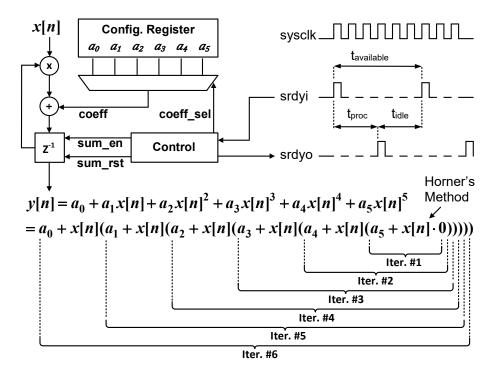

The hardware complexity of this calibration technique depends on the polynomial order. Since the VCO distortions are dominated by third and fifth order nonlinearities: a fifth-order polynomial should be sufficient to correct for them. The general form of our fifth-order polynomial is the following:

$$y[n] = a_0 + a_1 x[n] + a_2 x[n]^2 + a_3 x[n]^3 + a_4 x[n]^4 + a_5 x[n]^5$$

where x[n] is the NLC input sample,  $a_0 - a_5$  are the polynomial coefficients, and y[n] is the NLC output. For better accuracy, we use single-precision floating-point operations to compute the polynomial. A straight-forward implementation would require too many floating-point multipliers that take up significant area even in an advanced technology node. Noticing that the sampling rate of the quantizer is very low, a tradeoff of execution time and area can be made in our favor by adopting Horner's method, which allows iterative computation of a polynomial using a single multiplier-accumulator (MAC) kernel. With Horner's method, our polynomial can be rewritten as

$$y[n] = a_0 + x[n](a_1 + x[n](a_2 + x[n](a_3 + x[n](a_4 + x[n](a_5 + x[n] \cdot 0)))))$$

Thus, y[n] can be computed starting with the innermost MAC operation  $a_5 + x[n] \cdot 0$ , then expanded outward until the whole polynomial is computed. The schematic representation of the implementation is shown in Figure 2.18. When the quantizer output is ready, the raw sample x[n] is sent to the NLC engine and the input valid signal is asserted for one clock cycle. The engine then starts the first iteration, where it multiplies the input sample x[n] with the accumulator register content (which is initialized to 0), adds the fifth-order coefficient  $a_5$  to it, and stores the result back into the accumulator register. In the second iteration, the input x[n] is multiplied with accumulator register content (which is now nonzero); the fourth-order coefficient  $a_4$  is added, and the result is stored into the accumulator register again. This process continues until the whole

polynomial y[n] is computed. After the last (sixth) iteration is complete, the output valid signal is asserted to indicate that the nonlinearity corrected sample is now ready. This iterative polynomial solution with only one MAC kernel reduces the NLC area to be much smaller than the classical LUT approach.

Figure 2.18 NLC engine architecture. Source-ready-in (srdyi) and source-ready-out (srdyo) signals specify whether the input and the output of the NLC block are valid.

## 2.2.5.2 Engine Order Revisited

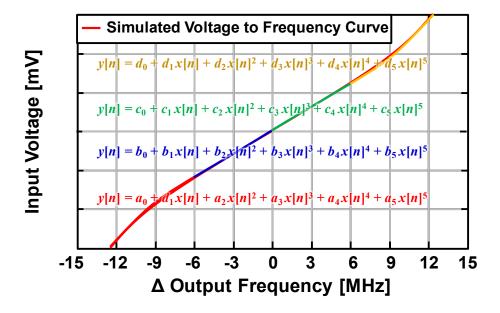

The NLC block for the first version of the sensing IC was designed as a 6<sup>th</sup> order polynomial engine. This was due to the 3<sup>rd</sup> and 5<sup>th</sup> order nonlinearities being dominant terms for VCO distortions. For the next IC iteration among other improvements, we also increased the polynomial order to make sure it was not the limiting factor for the ADC linearity. This was because the IC design CAD tool simulations would show much higher nonlinear distortions at the output of the VCO ADC than the expected 5<sup>th</sup> order terms. The redesigned polynomial engine split the input

range of the VCO ADC into four (4) sections, each one having a  $10^{\rm th}$  order polynomial engine (Figure 2.19).

Figure 2.19 Dividing the NLC curve into four sections.

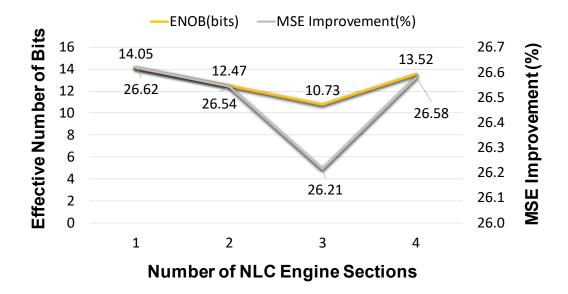

Two different metrics were used to evaluate the fitting performance of the new engine – 1) mean square error (MSE), and 2) ENOB extracted from the fast Fourier transform plots. For the first test, we set out to find out whether dividing the nonlinearity curve into a different number of sections (up to four) results into fitting improvements. Since this engine takes four different polynomial coefficients, we can effectively make one, two, or three section engines by setting some section coefficients to be equal to each other. The measurement results revealed that one-section calibration had the best ENOB and MSE performance (Figure 2.20). This result is a little surprising. If the one-section engine is sufficient for the fitting, the two, three, and four sections should perform as well and not worse than one-section since they provide more degrees of freedom for the fitting. Practically, however, the degraded results for the two, three, and four section tests were due to the curvature mismatch at the section division points.

Figure 2.20 Polynomial fitting performance of four-section NLC engine when utilizing different number of sections.

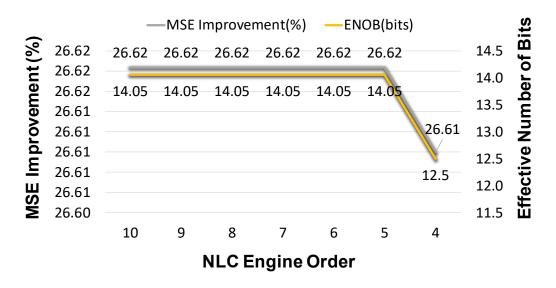

By fixing the section number to one, the next performed test was to identify the required polynomial order for the engine. The same ADC data was applied to a one-section engine, however, in each case, the polynomial fitting function was constrained by a different degree of freedom. The measurement results showed that the fitting performance plateaus sharply after 5<sup>th</sup> order (Figure 2.21). This is consistent with our original analysis.

Figure 2.21 Polynomial fitting performance of NLC engine when varying the polynomial order.

## 2.2.5.3 Coefficient Sharing Between Channels

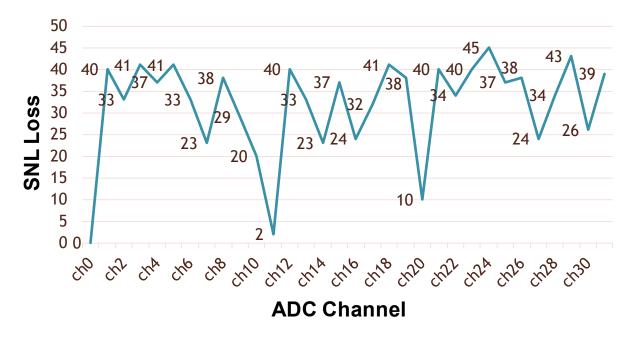

The NLC engine was implemented with a separate coefficient set for each channel. As previously mentioned in Section 2.2.3, the VCO ADC voltage-to-frequency nonlinearity sources are the silicon process, the supply voltage, and the operating temperature. Since the supply voltage and operating temperature are well regulated and the same across all channels, the only source of cross-channel variability remains the silicon manufacturing process. If the on-chip process variations were insignificant, we could use a single coefficient set across all ADC channels. For a 32-channel system, this would mean 32x reduction in coefficient memory size. Since this variability can not be simulated or analytically derived, we empirically measured it on fabricated ICs by applying the coefficients derived for one channel across all the other channels. We can see from Figure 2.22 that coefficient sharing among channels can result in up to 45dB SNR losses. For this reason, we kept the original arrangement of allocating separate coefficients for each channel.

Figure 2.22 Resulting SNR losses when ch0 NLC coefficients are applied across all other channels.

## 2.2.6 Low-Power Optimizations

Before starting the low power optimizations, power consumption sources of the initial design need to be understood. Table 2.4 shows the power consumption of various digital blocks for the sensing IC including the four (4) NLC engines. About 86% of the power consumption is due to the NLC cores, and 60% of this is due to the leakage component. Thus, reduction of the leakage power of the NLC engines will be the main target for the power optimizations. Main contributors of the leakage power are the area of the design, transistor threshold voltage, and the supply voltage. Since threshold voltage is fixed for the digital standard cells provided by the foundry, proper library selection is key in leakage reduction. Area and the supply voltage have a linear relationship to leakage power, however, lowering the supply voltage also requires additional voltage-translation circuitry (hence power) for interfacing the voltage-scaled block to the rest of the system.

Table 2.4 Power consumption of sensing IC v1 digital blocks operating at 12.288MHz and fabricated with the TSMC45GP process. Cells highlighted in blue and red denote the main power consumption source and the main power component respectively.

| Design<br>Block | Switching<br>Power | Internal<br>Power  | Leakage<br>Power | Total Power (µW) | %     |

|-----------------|--------------------|--------------------|------------------|------------------|-------|

| Name            | $(\mu W)$          | $(\mu \mathrm{W})$ | $(\mu W)$        | (1 **)           |       |

| VCO timer       | 0.428              | 1.33               | 8.06             | 9.83             | 1.3   |

| PISO            | 0.236              | 0.936              | 2.62             | 3.79             | 0.5   |

| SIPO            | 0.346              | 1.7                | 3.55             | 5.59             | 0.7   |

| Config. reg.    | 14.8               | 44.1               | 28               | 86.9             | 11.5  |

| 4 NLC cores     | 20.67              | 215.9              | 412              | 648              | 85.8  |

| Entire design   | 36.7               | 264                | 455              | 755              | 100.0 |

| %               | 4.9                | 35.0               | 60.3             | 100.0            |       |

#### 2.2.6.1 Technology Selection

The initial version of the sensing IC (v1) was fabricated with TSMC40GP fabrication process—where TSMC is the name of the foundry (Taiwan Semiconductor Manufacturing Company), 40 denotes the technology node (40nm) and GP means general-purpose transistors were used. GP device processes are meant for high-performance applications such as CPUs, GPUs, or FPGAs hence their power/delay curve is skewed towards lower delays at the expense of added power. This process was used for the v1 of sensing IC due to availability rather than suitability. This process inherently has higher leakage compared to low-power (LP) process of the same 40nm node due to thinner gate oxide layer. Since high throughput (lower-delay) is not needed in our design, just by porting the v1 design to this process would result in 97.6% less leakage power and reduce the total power consumption by 42.5% (Table 2.5).

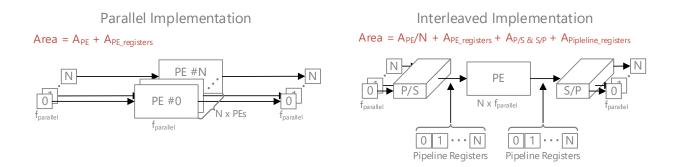

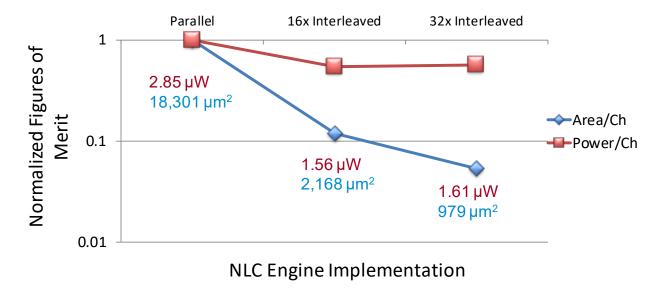

Table 2.5 Power consumption of sensing IC v1 digital blocks synthesized at 12.288MHz for the TSMC40LP process. Note the total power of the entire design is 434µW, which is substantially less (42.5%) than in the design fabricated with the TSMC45GP process.