# **UC Santa Cruz**

**UC Santa Cruz Electronic Theses and Dissertations**

## Title

ANALYSIS AND APPLICATION OF INDUCTANCE IN CLOCK DISTRIBUTION NETWORKS

**Permalink** https://escholarship.org/uc/item/2gs042hr

**Author** Hu, Xuchu

Publication Date 2012

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

## ANALYSIS AND APPLICATION OF INDUCTANCE IN CLOCK DISTRIBUTION NETWORKS

A dissertation submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

## COMPUTER ENGINEERING

by

### Xuchu Hu

March 2012

The Dissertation of Xuchu Hu is approved:

Professor Matthew R. Guthaus, Chair

Professor Jose Renau

Dr. Chin Ngai Sze

Dean Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by

Xuchu Hu

2012

# **Table of Contents**

| List of Figures |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |  |

|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Li              | ist of [ | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | viii |  |

| A               | bstrac   | et in the second s | ix   |  |

| A               | cknow    | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xi   |  |

| 1               | Intr     | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1    |  |

|                 | 1.1      | Thesis Contributions and Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3    |  |

| 2               | Cloc     | ck Distribution Network Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5    |  |

|                 | 2.1      | Clock Network Design Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5    |  |

|                 | 2.2      | Clock Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6    |  |

|                 | 2.3      | Analytical Models in CDN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8    |  |

| 3               | Cloc     | ck Distribution Using Inductance: Resonant Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12   |  |

|                 | 3.1      | Types of Resonant Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13   |  |

|                 |          | 3.1.1 Standing Wave Resonant Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13   |  |

|                 |          | 3.1.2 Rotary Resonant Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14   |  |

|                 |          | 3.1.3 Distributed Inductor-Capacitor (LC) Resonant Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15   |  |

|                 | 3.2      | Theory of LC Resonant Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16   |  |

|                 | 3.3      | Resonant Clock Grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18   |  |

|                 | 3.4      | On-Chip Inductors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19   |  |

|                 | 3.5      | On-Chip Capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21   |  |

| 4               | Rese     | onant Clock Grid Synthesis Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22   |  |

|                 | 4.1      | Resonant Clock Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22   |  |

|                 |          | 4.1.1 Transient Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23   |  |

|                 |          | 4.1.2 AC Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23   |  |

|                 | 4.2      | Challenges in Resonant Clock Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25   |  |

|                 |          | 4.2.1 Resonant Frequency Shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25   |  |

|                 |          | 4.2.2 Signal Attenuation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28   |  |

|                 |          | 4.2.3 Interaction Between Buffers and LC Tanks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29   |  |

|   |     | 4.2.4 On-chip Inductor Overhead                                                   | 29 |

|---|-----|-----------------------------------------------------------------------------------|----|

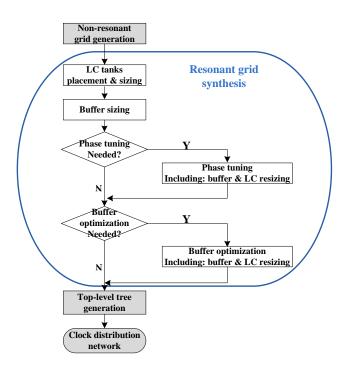

|   | 4.3 | Resonant Clock Grid Synthesis Flow                                                | 31 |

|   |     | 4.3.1 Problem Formulation                                                         | 31 |

|   |     | 4.3.2 Synthesis Flow                                                              | 31 |

| 5 | LC  | Tank Placement and Sizing                                                         | 34 |

|   | 5.1 | Optimal Resonant Clock Grid                                                       | 35 |

|   | 5.2 | LC Tank Placement and Sizing with Continuous Inductors                            | 36 |

|   |     | 5.2.1 LC Tanks Removal                                                            | 36 |

|   |     | 5.2.2 LC Tank Sizing                                                              | 39 |

|   | 5.3 | LC Tanks Placement with Discrete Inductors                                        | 40 |

|   |     | 5.3.1 Resistance ( <i>R</i> ) and Capacitance Mismatch ( $\Delta C$ ) Constraints | 41 |

|   |     | 5.3.2 Discrete LC Tank Placement                                                  | 43 |

|   |     | 5.3.3 Candidate Subset Generation                                                 | 43 |

|   |     | 5.3.4 Candidate Subset Selection                                                  | 45 |

| 6 | Res | onant Clock Buffer Optimization                                                   | 47 |

|   | 6.1 | Non-resonant Clock Grid Buffering                                                 | 47 |

|   | 6.2 | AC-based Buffer Sizing                                                            | 48 |

|   | 6.3 | AC- and Resistance-based Buffer Sizing                                            | 50 |

|   | 6.4 | Resonant Grid Buffer Placement Optimization                                       | 52 |

| 7 | Res | onant Clock Phase Tuning                                                          | 54 |

|   | 7.1 | Dummy Capacitance for Phase Tuning                                                | 55 |

| 8 | -   | erimental Methodology                                                             | 57 |

|   | 8.1 | Technology Setup                                                                  | 57 |

|   | 8.2 | Experiment Design                                                                 | 59 |

|   |     | 8.2.1 Non-resonant Clock Grid Baseline                                            | 59 |

|   |     | 8.2.2 Resonant Clock Grids                                                        | 59 |

|   |     | 8.2.3 Comparison with State-of-the-Art Resonant Clocks                            | 60 |

|   |     | 8.2.4 Comparison with ISPD Clock Synthesis Contest                                | 60 |

| 9 | -   | erimental Results                                                                 | 62 |

|   | 9.1 | Inductor Area                                                                     | 62 |

|   | 9.2 | Resonant Clock Grid with Continuous Inductors                                     | 63 |

|   |     | 9.2.1 Synthesis Flow                                                              | 63 |

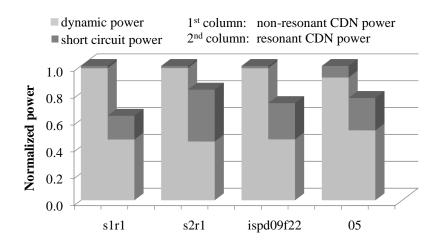

|   |     | 9.2.2 Power                                                                       | 67 |

|   |     | 9.2.3 Skew                                                                        | 68 |

|   |     | 9.2.4 Buffer Size and Area                                                        | 69 |

|   |     | 9.2.5 Inductor Overhead                                                           | 71 |

|   |     | 9.2.6 Capacitor Overhead                                                          | 71 |

|   |     | 9.2.7 Run Time                                                                    | 72 |

|   | 9.3 | Resonant Clock Grid with Discrete Inductors                                       | 72 |

|   |     | 9.3.1 Synthesis Flow                                                              | 72 |

|   |     | 9.3.2 Power                                                                       | 73 |

|     |        | 9.3.3 Skew                                                     | 4 |

|-----|--------|----------------------------------------------------------------|---|

|     |        | 9.3.4 Inductor Overhead                                        | 5 |

|     |        | 9.3.5 Capacitor Overhead                                       | 6 |

|     |        | 9.3.6 Inductor Q factor                                        | 7 |

|     |        | 9.3.7 Run Time                                                 | 7 |

|     | 9.4    | Resonant Grid Transient and AC Analysis                        | 8 |

|     | 9.5    | Comparison with State-of-the-Art Resonant Clocks               | 8 |

|     | 9.6    | Comparison with ISPD Clock Synthesis Contest                   | 0 |

|     | 9.7    | Robustness                                                     | 3 |

|     |        | 9.7.1 Process Variation                                        | 3 |

|     |        | 9.7.2 Inductor Variation                                       | 4 |

| 10  | Prac   | tical Issues with Resonant Clocks 8                            | 5 |

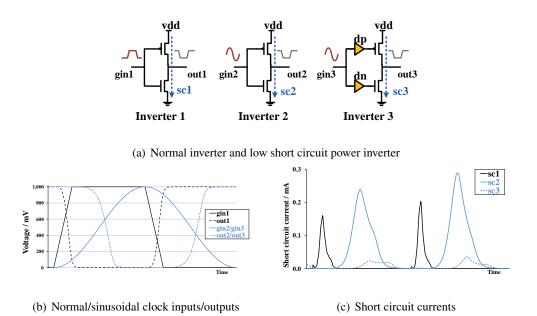

|     | 10.1   | Short Circuit Power of Sinusoidal Resonant Clocks              | 5 |

|     | 10.2   | LC Tank Precharge                                              | 8 |

|     | 10.3   | Frequency Scaling                                              | 9 |

|     | 10.4   | Inductor Library Design                                        | 1 |

| 11  | Cone   | clusions 9                                                     | 3 |

|     | 11.1   | Thesis Contributions                                           | 3 |

|     | 11.2   | Future Work                                                    | 5 |

| Bil | bliogr | aphy 9                                                         | 6 |

| A   | Cloc   | k Tree Optimization for Electromagnetic Compatibility (EMC) 11 | 0 |

|     | A.1    | On-chip Electromagnetic Interference                           | 0 |

|     | A.2    | Problem Statement and Models                                   | 2 |

|     |        | A.2.1 Spectral Analysis of Clock Signal                        | 2 |

|     |        | A.2.2 Radiation Emission                                       | 4 |

|     |        | A.2.3 Problem Statement                                        | 5 |

|     |        | A.2.4 Maximum/Minimum Slew Constraints                         | 5 |

|     |        | A.2.5 Delay and Slew Models                                    | 6 |

|     | A.3    | Clock Tree EMI Optimization Algorithm                          |   |

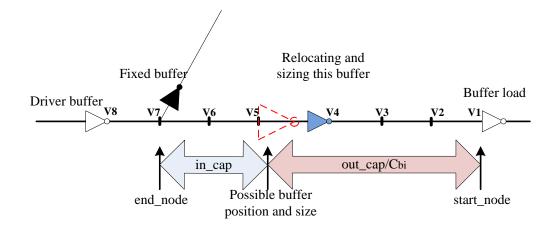

|     |        | A.3.1 Van Ginneken's Dynamic Programming                       | 7 |

|     |        | A.3.2 Top Level Algorithm                                      | 8 |

|     |        | A.3.3 Relocating and Sizing a Critical Path                    |   |

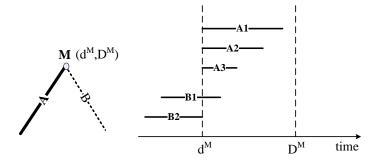

|     |        | A.3.4 Pruning                                                  |   |

|     |        | A.3.5 Infeasible Slew Limits                                   | 3 |

|     | A.4    | Experimental Setup and Results                                 | 4 |

|     |        | A.4.1 Experimental Setup                                       | 4 |

|     |        | A.4.2 Skew and Power                                           | 4 |

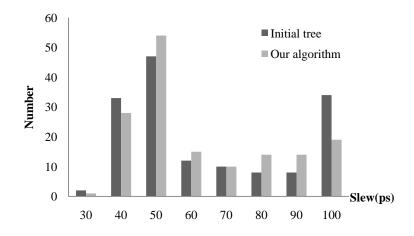

|     |        | A.4.3 Slew Distribution                                        | 5 |

|     |        | A.4.4 Radiation Power                                          | 8 |

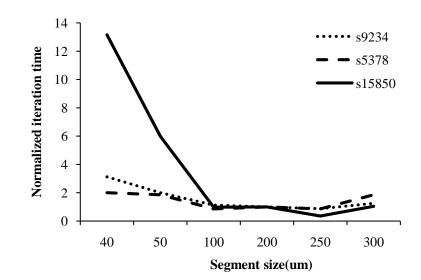

|     |        | A.4.5 Segment Size                                             | 8 |

|     | A.5    | Conclusion                                                     | 9 |

# **List of Figures**

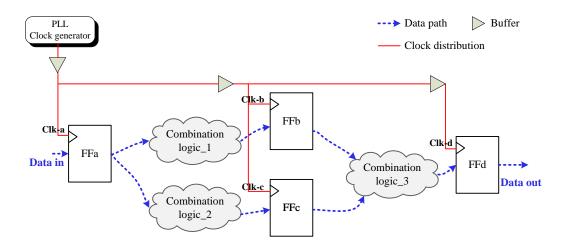

| 2.1 | Combination circuits synchronized by clock signal                            | 6          |

|-----|------------------------------------------------------------------------------|------------|

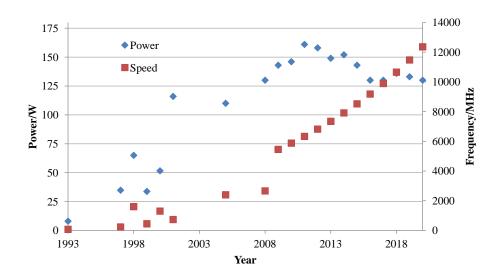

| 2.2 | Power and frequency trend over the years. Data before 2009 is from [57],     |            |

|     | data after 2010 is from ITRS2011 [79]                                        | 7          |

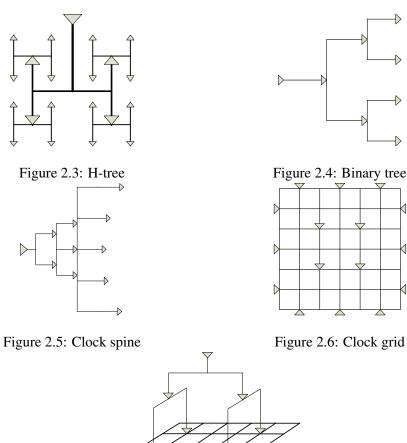

| 2.3 | H-tree                                                                       | 8          |

| 2.4 | Binary tree                                                                  | 8          |

| 2.5 | Clock spine                                                                  | 8          |

| 2.6 | Clock grid                                                                   | 8          |

| 2.7 | Hybrid clock: H-tree driving grid                                            | 8          |

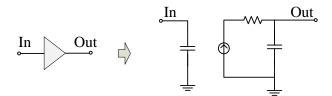

| 2.8 | Buffer RC model                                                              | 9          |

| 2.9 | Wire models                                                                  | 10         |

| 3.1 | Standing-wave clock distribution network [50]                                | 13         |

| 3.2 | Rotary resonant clock [86]                                                   | 14         |

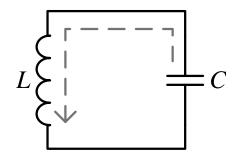

| 3.3 | LC Tank Oscillators                                                          | 16         |

| 3.4 | Energy exchange in LC tank oscillators                                       | 17         |

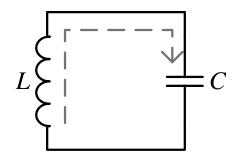

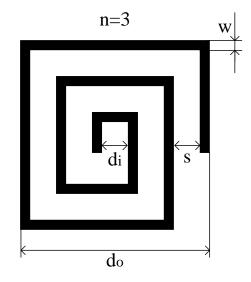

| 3.5 | Structure of a distributed LC resonant clock grid                            | 18         |

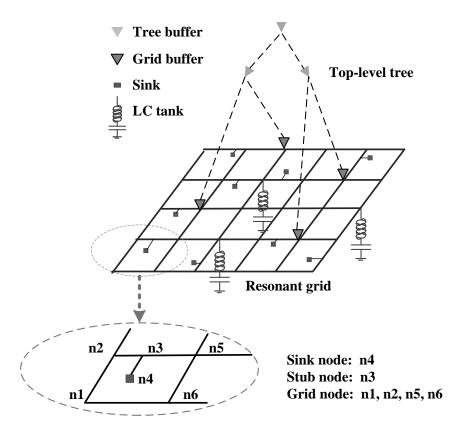

| 3.6 | On-chip square spiral inductor made with normal metal layers                 | 19         |

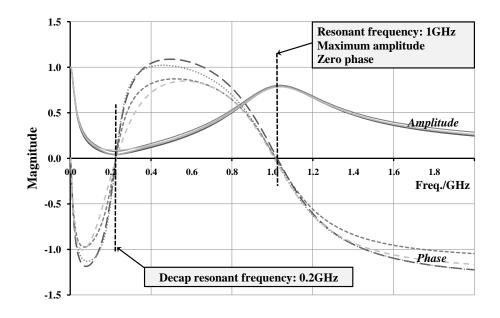

| 4.1 | Amplitude and phase of AC signals                                            | 25         |

| 4.2 | Parasitic resistances and capacitances in LC circuit alter the resonant fre- |            |

|     | quency                                                                       | 26         |

| 4.3 | Current plots in AC analysis of circuit 4.2                                  | 27         |

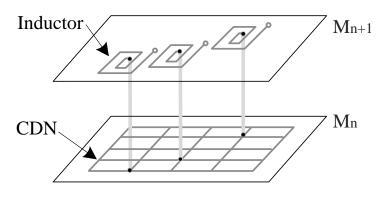

| 4.4 | LC tanks and CDN are implemented in adjacent global metal layers             | 30         |

| 4.5 | Overview of distributed LC resonant grid synthesis methodology               | 32         |

| 5.1 | LC tank removal starts with optimal distributed placement and reduces in-    |            |

|     | ductor area with minimal power loss.                                         | 36         |

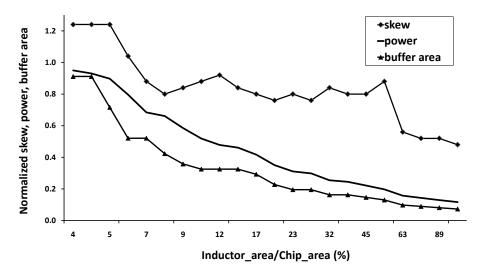

| 9.1 | The relationship between inductor area and clock grid performance, power     |            |

| 0.0 | saving and skew improve with more on-chip inductors.                         | 63         |

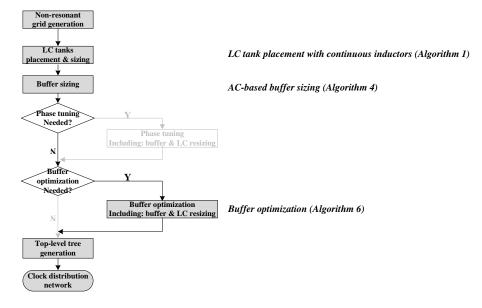

| 9.2 | Resonant clock grid synthesis flow with continuous inductors. Uses Algo-     |            |

|     | rithm 1 for LC tank placement and Algorithm 4 for buffer sizing, phase       | <i>(</i> ) |

|     | tuning is not required in this flow.                                         | 64         |

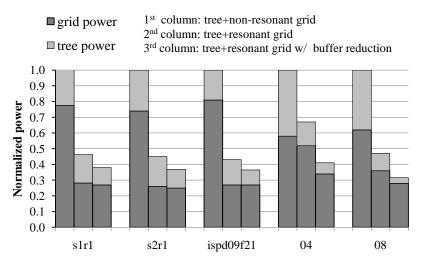

| 9.3  | Representative grid and tree power reductions achieved by resonant clock grids                                                                                                   | 68  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

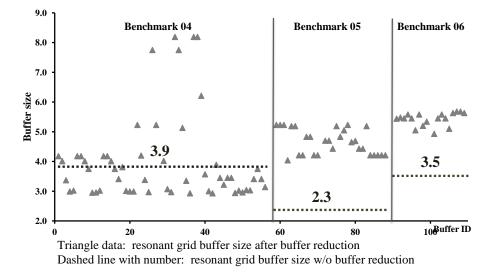

| 9.4  | Buffer reduction can increase or decrease individual buffer sizes, but overall buffer area is reduced.                                                                           | 70  |

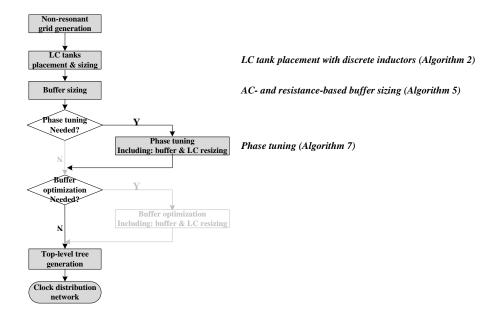

| 9.5  | Resonant clock grid synthesis flow with discrete inductors. Uses Algo-<br>rithm 3 for LC tank placement, Algorithm 5 for buffer sizing and Algo-<br>rithm 7 for phase tuning.    | 73  |

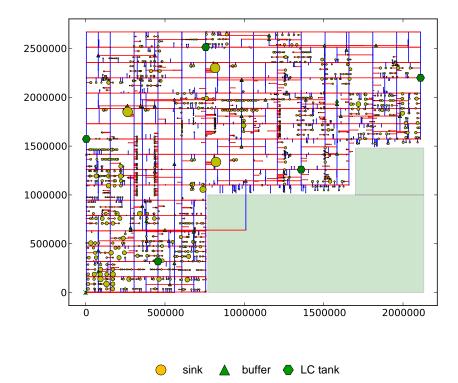

| 9.6  | Clock network with LC tanks (benchmark 04) produced by synthesis flow (Figure 9.5. Dimensions in <i>nm</i> . Buffers, sinks and LC tanks are relatively sized but not to scale.) | 74  |

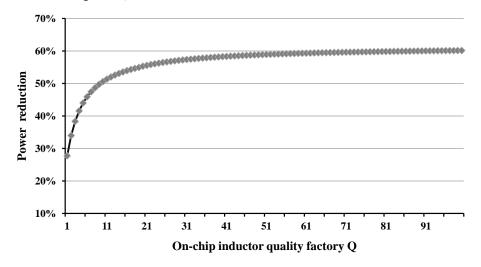

| 9.7  | Significant power gains are obtained even with low-Q on-chip inductors                                                                                                           |     |

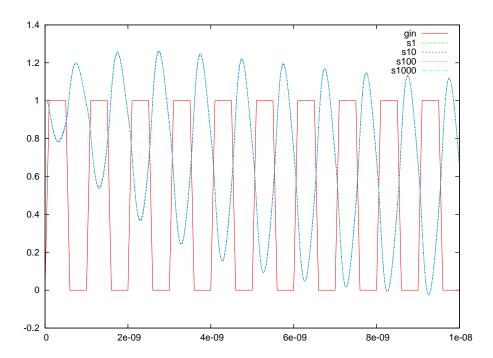

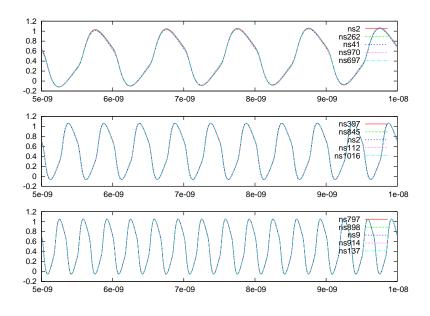

| 9.8  | Resonant clock grid AC analysis                                                                                                                                                  | 79  |

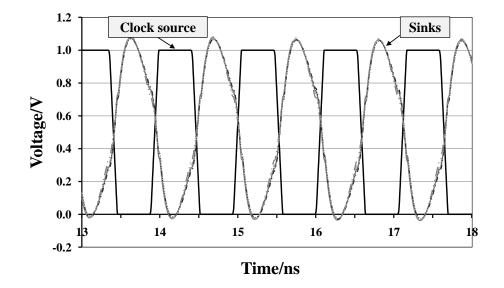

| 9.9  | Resonant clock grid transient analysis                                                                                                                                           | 79  |

| 10.1 |                                                                                                                                                                                  |     |

|      | Dynamic and short circuit power                                                                                                                                                  | 87  |

| 10.4 | pre-charge the initial LC tanks                                                                                                                                                  | 88  |

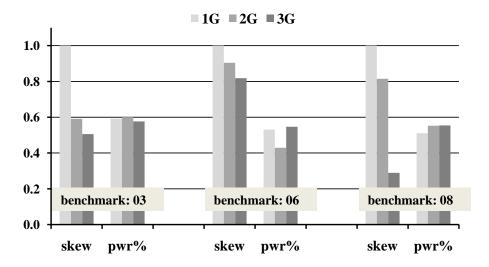

|      | can be successfully synthesized at different frequencies, shown are 1GHz, 2GHz and 3GHz.                                                                                         | 90  |

| 10.5 | Resonant clock power and skew at different frequencies. Skew at 2GHz and 3GHz is normalized to skew at 1GHz.                                                                     |     |

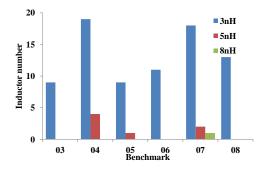

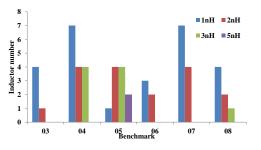

| 10.6 | Inductor usage statistic of resonant clock grid with different inductor li-                                                                                                      | 20  |

|      | brary. The synthesis flow uses fewer inductors with smaller inductor area.                                                                                                       | 91  |

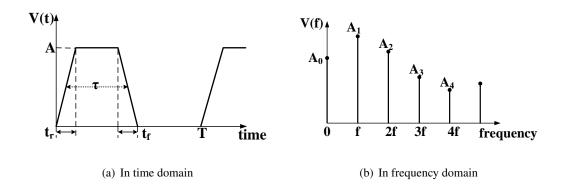

| A.1  | Clock signal in time and frequency domain                                                                                                                                        | 113 |

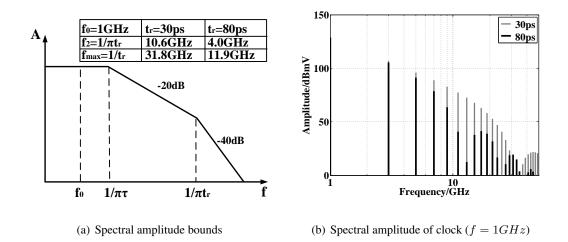

| A.2  | Clock Signal Spectral analysis                                                                                                                                                   |     |

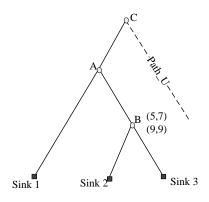

| A.3  | Pruning in dynamic programming of clock tree                                                                                                                                     | 118 |

| A.4  | load_cap and in_cap constraints                                                                                                                                                  |     |

| A.5  | Interval solution pruning based on $D^M/d^M$                                                                                                                                     |     |

| A.6  | Slew distribution of benchmark s15850                                                                                                                                            |     |

| A.7  | Segment size vs iteration run time                                                                                                                                               | 128 |

# **List of Tables**

| 5.1        | Common terms in algorithm                                                                                                                                                                                                                                                                                                   | 42  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.1        | ISPD2009 benchmark simulation results. With 28% one metal layer for on-<br>chip inductors, resonant grid without buffer reduction reduce the average<br>total power by 39.5% and improve the skew by $3.5ps$ . With buffer reduction                                                                                        | (5  |

| 9.2        | (Algorithm 6), power saving is 60.9% while skew slightly increase by 4.8 <i>ps</i> . ISPD2010 benchmark simulation results. With 28% one metal layer for on-<br>chip inductors, resonant grid without buffer reduction reduce the average total power by 48% and increase the skew by 7.6 <i>ps</i> . With buffer reduction | 65  |

|            | (Algorithm 6), power saving is $61\%$ while skew increase by $27.3ps.$                                                                                                                                                                                                                                                      | 66  |

| 9.3        | Experimental results on ISPD 2010 benchmarks show that power is 41% of                                                                                                                                                                                                                                                      |     |

|            | non-resonant power while skew is limited to $17ps$ on average                                                                                                                                                                                                                                                               | 75  |

| 9.4        | Capacitor usage in resonant clock.                                                                                                                                                                                                                                                                                          | 76  |

| 9.5<br>9.6 | Continuous inductor placement/sizing and uniform LC tank placement<br>Comparison of resonant clock generated with Figure 9.5 flow with non-                                                                                                                                                                                 | 80  |

|            | resonant ISPD2010 CDNs [88]                                                                                                                                                                                                                                                                                                 | 82  |

| 9.7        | Resonant clock distributions exhibit decreased worst case skew variation                                                                                                                                                                                                                                                    | 83  |

| 0.0        | (29ps  compared to  32ps) when considering process variations                                                                                                                                                                                                                                                               |     |

| 9.8        | Monte Carlo simulations of inductor variation                                                                                                                                                                                                                                                                               | 84  |

| 10.1       | Inductors and phase tuning capacitance usage with different inductor li-<br>braries. Using smaller inductors reduces on-chip inductor area but needs                                                                                                                                                                        |     |

|            | more capacitance to compensate for the $\Delta C$ mismatch                                                                                                                                                                                                                                                                  | 92  |

| A.1        | Notations                                                                                                                                                                                                                                                                                                                   | 116 |

| A.2        | Benchmark simulation results                                                                                                                                                                                                                                                                                                |     |

|            |                                                                                                                                                                                                                                                                                                                             |     |

#### Abstract

Analysis and Application of Inductance in Clock Distribution Networks

by

#### Xuchu Hu

With better manufacturing technologies, each generation of processors grows smaller, faster, and consumes more power. As microprocessors are operating at multi-GHz speed, power consumption has become a major concern in modern processor design. Especially in portable devices which are battery operated, low power design becomes extreme important.

The on-chip clock distribution network (CDN) consumes in excess of 35% of total chip power and occasionally as much as 70% [61]. Most of this power is due to the dynamic switching of the large number of sequential element clock pins that span the entire chip. Clock distribution using inductance (Resonant clock ) has a potential to reduce the maximum power consumption without degrading the clock network performance. Some previous research works demonstrated power savings by connecting extra inductors to clock network. Compared with clock trees, clock grids are often used in high performance processors which operate at higher frequency and consume more power. Previous resonant works either assume simplified clock network or only consider a small sector of the clock network. Inductance is often used in RF designs. In digital circuits, designers usually try to minimize the inductance effect of long interconnections. So the resonant clock synthesis which is related to both digital and analogy design has not been well studied. In this thesis, a methodology to design low power resonant clock grid is described. The key synthesis procedures involved in resonant clock grid design are discussed. The CDN which has a top-level tree driving a resonant grid shows at least 40% power savings and 53% buffer area reduction while using only 30% of a single metal layer for inductors on average. With more advanced on-chip inductor integration techniques, resonant clock grids hold the potential to save up to 90% of the clock grid power. The automated methods can make these multi-disciplinary clocking techniques practical for use in high-performance ASIC designs. At the end of the thesis, the practical issues of resonant clock will be discussed.

#### Acknowledgments

First of all, I would like to express my deep and sincere gratitude to my advisor, Professor Matthew R. Guthaus, for all his contributions of time, ideas, and funding to make my Ph.D experience productive and stimulating. It is my honor to be his first Ph.D graduate. I appreciate his hands-on help in the initial stage and his encouragement for innovation as a senior Ph.D student. His consistent encouragement and support helped me to complete the Ph.D smoothly. I am also thankful for the excellent example he has provided as an enthusiastic and diligent researcher.

Besides my advisor, I would like to thank the rest of my thesis committee: Professor Jose Renau and Dr. Cliff (Chin Ngai) Sze for their time, dedication and insightful comments.

I thank my fellow labmates in UCSC VLSI-DA group: Seokjoong Kim, Sheldon Logan, Rajsaktish Sankaranarayanan, Marcelo Siero, Walter Condley, Derek Chan and Keven Woo, for both technical discussions and all kinds of fun discussions.

I also wish to thank the graduate advisor and the international student advisor, Carol Mullane and Ally Modzeleski. They are always willing to help and provide helpful suggestions. They helped me with a lot of paperwork and special problems.

I would say without the help of my sincere friends, I could not be able to successfully finish my Ph.D study. I am grateful to my friends, Bin Wu, Xinhua Hu and Jingpei Yang, who took care of my daily life after surgery and helped me go though those tough times.

Last but not the least, I would thank my parents for always being there when I

needed them most, and always considering everything for me. They never complain how far I am away from home and how infrequently I go home to visit them. They deserve far more credit than I can ever give them.

# **Chapter 1**

# Introduction

The integrated circuit (IC) industry has undergone more evolutionary change in the past 50 years than any other industry and has changed the world tremendously. When the first IC was created in 1958 by Jack Kilby, it contained only a few transistors. The latest Intel processor Poulson [62] has been introduced in ISSCC 2011 and contains 3.1 billion transistors. Early integrated circuit is called SSL (small-scale integration), and later developed to MSI (medium-scale integration), LSI (large-scale integration) and VLSI (very large-scale integration). Nowadays, ULSI which stands for "ultra-large-scale integration" is used to describe an IC with more than one million components per chip.

To describe the technical details of a processor, CPU frequency is always the number one spec. CPU frequency is the internal operating frequency of the processor. Generally, the higher frequency is, the faster and the better the processor is. So it is not surprising that the clock design, or to be more precise, the clock distribution network (CDN) in modern chip design is an important aspect, which, to a certain extent, decides how fast the chip can work.

With the sustained and rapid development of IC industry, however, we rarely see processors working over 5GHz as IC designers are facing more challenging power, cooling, and stability problems when targeting for higher clock frequency. This speed threshold is because of the extreme power dissipation of the circuit. According to the CMOS circuit dynamic power consumption equation,

$$P = \alpha C V^2 f; \tag{1.1}$$

the dynamic power is proportional to the circuit capacitance (C), supply voltage (V), clock frequency (f) and switching activity  $(\alpha)$ . Doubling the clock frequency is at the expense of twice power dissipation. The power density of the highly-integrated chip with millions of transistors requires extremely efficient cooling techniques to make the chip reliable.

Clock gating, power gating, dynamic frequency scaling, and dynamic voltage scaling are used at different design abstractions to reduce dynamic power by carefully looking into Equation 1.1 and minimizing each factor. However, the power is usually saved by exploiting inactivity or dynamically adjusting performance. Multi-core processors are considered as a viable solution for keeping clock rates and heat production manageable. Multi-core processors operate at a lower frequency but still achieve the same or even better performance than a single core processor by distributing the tasks to multiple CPU cores. However multi-core still can not break the physical constraints preventing frequency scaling.

The clock frequency f determines the single-thread performance. Because of its high activity and great fanout, the on-chip clock distribution network (CDN) consumes in excess of 35% of total chip power and occasionally as much as 70% [61]. Obviously,

reducing the power of clock network is a great help to control chip power. However, considering process, voltage, and temperature variation issues arised from technical scaling, it is tremendously difficult to design a low power but still robust and stable clock network.

As frequency and power are correlated, only a breakthrough technology could be able to solve the power and frequency problem by breaking this relationship. One possible solution to this problem is resonant clocks which will be investigated in this thesis.

## **1.1** Thesis Contributions and Outline

The on-chip interconnect inductance leads to signal ringing, signal reflection and additional inductive crosstalk under fast slew rates. Inductance in clock wires with high switching activity of clock signals can also cause undesirable effects such as Electromagnetic Interference (EMI) which is a primary concern among many RF designers because unchecked eletromagetic field may interfere with nearby devices. Clock shielding is used to minimize the inductance effect [39]. The EMI reduction in clock network is briefly investigated in Appendix A<sup>1</sup>. On the other hand, research works [18, 32] show that on-chip inductance can be used to improve the performance of high-speed integrated circuits. Inductance improves the signal slew rate, eliminates short-circuit power and reduces the area of the active devices and repeaters inserted to optimize the performance of long interconnects. However, in most recently published clock design works [13, 41, 88], inductance of the CDN is ignored.

Besides the improvement of clock signal slew rate, the application of inducatance has great potential to save power in clock network. This thesis proposes a design automa-

<sup>&</sup>lt;sup>1</sup>This work is not directly related to the inductance application in resonant clock.

tion methodology to synthesis low-power and robustness clock network by utilizing the resonance phenomenon. By adding inductors to clock networks, the power of CDN can be reduced by up to 90% without scracific frequency, or robustness.

This dissertation begins with an overview of clock distribution networks in Chapter 2. The general structures and metrics in CDN design are introduced. In Chapter 3, resonant theory is introduced. With the background of the resonant theory, different types of resonant clocks which utilize resonant phenomenon in clock network to save power are introduced with their advantages and disadvantages. At the end of this chapter, on-chip inductors and on-chip capacitors, are introduced. Chapter 4 is an overview of resonant clock synthesis. The application of small signal analysis (AC analysis) is introduced at the begining of this chapter, which is different from previous transient analysis in CDN design. Special challenging issues in resonant clock design are summaried with a complete synthesis flow to address these problems. Chaper 5, 6 and 7 are the three major procedures in the resonant clock synthesis: LC tank placement/sizing, buffer placement/sizing and phase tuning. Each chapter introduces the methodologies used in each step to synthesis resonant clocks. Chapter 8 summarizes the experimental setup, and experimental design to validate the proposed methods. Chapter 9 includes all the experimental results with different experimental setups followed with conclusions. Chapter 10 raises some practical issues related to application of resonant clock, and provides solutions to these special issues. Finally, Chapter 11 summarizes the work presented in this dissertation and describes potential areas for further studies.

# **Chapter 2**

## **Clock Distribution Network Background**

Normally, an integrated Phase-Lock Loop (PLL) generates the clock signal and the CDN will distribute the clock signal from the PLL to all the registers/flip-flops across the chip. Figure 2.1 is an example to show how the combinational circuits are synchronized by the clock signal which is generated by the PLL. The red solid line in the figure represents the clock from the source to each flip-flop. These flip-flops are often called *clock sinks*. Buffers are inserted in the clock network for delay, slew, and noise optimization.

## 2.1 Clock Network Design Metrics

**Skew**: Skew is defined as the maximum difference among the source to sink delays. In the example in Figure 2.1, the clock skew is the difference between the earliest and latest arrival time in Clk-a, Clk-b, Clk-c and Clk-d. Buffering, symmetric structure, and redundant connections are commonly used methodologies [22, 58, 77] to minimize clock skew. **Power**: While the clock signal has to traverse longer distance with the increasing chip size,

the CDN consumes more power and low-power clock design became an urgent require-

Figure 2.1: Combination circuits synchronized by clock signal

ment. Figure 2.2 shows the processor power and frequency trend over the time. From ITRS roadmap, the maximum power in the future will be limited to 150W. Clock gating is the most commonly used low-power method [10, 11, 49]. Dynamic voltage and frequency scaling (DVFS) [48] and low-voltage swing clocks [97] are also used in low-power clock design.

**Variations**: Another consideration in CDN design is the uncertainty in the CMOS design technologies. Technology scaling has lead to an increase in on-die PVT (process, voltage, temperature) variations which may degrade performance. Many previous works [24–29, 40, 74, 80, 94] discussed the variation problem in clock design.

## 2.2 Clock Structure

There are various clock distribution structures. In a rough classification, CDN structures can be classified into four types: trees, spines, grids and hybrid structures. Fig-

Figure 2.2: Power and frequency trend over the years. Data before 2009 is from [57], data after 2010 is from ITRS2011 [79]

ure 2.3 and Figure 2.4 are tree structures. The symmetric structure of H-tree and binary tree is good for skew and often consume less power. Though H-trees are robust to die-to-die variations, tree structures are very sensitive to variations. The spine structure is a specific implementation of a binary tree. Figure 2.5 is a clock spine structure. The spine structure is simple to implement but there will be residual skew due to asymmetry. A clock grid is formed by a set of vertical and horizontal wires as shown in Figure 2.6. Figure 2.7 is a hybrid structure with a top-level H-tree driving a clock grid.

Clock grid is able to provide low skew and very good robustness to variations because of the redundant connections, so clock grid is often used high-performance designs. However, power consumption is the major concern in clock grid application. Recently, some clock grid optimization methods [30, 59, 88] are proposed to reduce the clock grid power. By removing redundant wires, the total capacitance of the clock grid can be reduced and hence reduce the power. The buffer placement/sizing optimization methods find a more efficient way to utilize buffers to drive the clock grid to reduce the buffer area and short circuit power.

Figure 2.7: Hybrid clock: H-tree driving grid

## 2.3 Analytical Models in CDN

Clock signal generator, clock sink, buffer and wire constitute the clock network. Usually, the clock generator is not included in the clock network synthesis. Therefore, this section will focus on the sink, buffer and interconnect analytical models.

Sink models

Figure 2.8: Buffer RC model

A clock sink is either a flip-flop or a latch. It can also be a buffer in the hierarchical clock network. The clock sink is often modeled as a capacitor with a specific capacitance the same as the flip-flop (or latch, buffer) capacitance seen by the clock network.

#### **Buffer models**

A buffer/inverter is often modeled as a switch-level RC circuit as Figure 2.8 in previous clock network designs [82,87]. The delay of buffer can be calculated according to the buffer size, buffer load and the intrinsic delay. This model is able to estimate the buffer delay very quickly but the accuracy is getting worse while as the interconnect resistance gets more significant. In recent clock synthesis, the BSIM model is more often used in accurate timing analysis.

#### Wire models

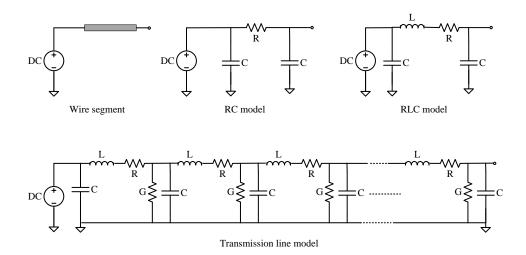

Three wire segment models are often discussed in the CDN analysis: RC model, RLC model and transmission line model as shown in Figure 2.9.

The RC model is a first-order extraction of wire. Usually, a wire segment is replaced by a resistor and two capacitors which is also called  $\pi$ -model. The RC model is simple. When frequency is not very high and wire length is relatively short, RC model is often used.

Figure 2.9: Wire models

However, due to increasing clock speeds, increasing interconnect lengths and decreasing signal rise times, the inductive effects of on-chip interconnects become more significant. The on-chip inductance can cause reflections and overshoots which may cause reliability problems. The on-chip interconnect inductance also effects delay and rise/fall time. There are many research works [34, 36, 37, 43, 44] about the inductance calculation, extraction and modeling.

Transmission line models are the most accurate and closet model. As shown in Figure 2.9, the lossy transmission line model represents a wire with many distributed "lumps" of R, L, and C elements. Because of the cascaded structure, the T-line model often takes much longer time than RC and RLC models. In real designs, if the signal frequency is low compared to the size of the circuit, a reasonable approximation can be used to simplify the circuit for calculation when doing transient analysis [16].

Though unchecked inductance will introduce many uncertainties, the application

of inductance in clock network is a fundamental solution to break the frequency and power relationship as in Equation 1.1 which is an insolvable problem in present low power design. Moreover, this method is more applicable in high frequency designs which often consume more power.

# **Chapter 3**

# Clock Distribution Using Inductance: Resonant Clock

As discussed before, power consumption is a predominant challenge in modern high-performance systems. One way to decrease this dynamic power consumption is with resonant clocking which can circumvent the dynamic power Equation 1.1.

Many previous works related to inductance try to minimize the effect of inductance [35, 42, 43, 60], however, a large amount of power can potentially be saved by using this same inductance in resonant clocks.

In this chapter, the background of resonant theory is introduced. Different types of resonant clocks and their advantages and disadvantages are discussed. Finally, the extra cost of resonant clock will be discussed.

Figure 3.1: Standing-wave clock distribution network [50]

## 3.1 Types of Resonant Clocks

There are various approaches to resonant clocks including standing wave [50], rotary/salphasic [14,71,86], and inductor-capacitor (LC) tank [7,8,21,92,98].

#### 3.1.1 Standing Wave Resonant Clock

A standing wave is a non-traveling vibration formed by the interference of two harmonic waves of the same frequency and amplitude. In standing wave clocks, the phases of all points are the same which is ideal for skew but the maximum amplitude varies with position.

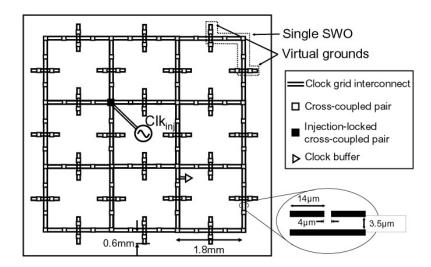

A simple method to generate a standing wave is to send a wave along a transmission line and reflect it back at the end of the transmission line [50]. Figure 3.1 is a standing wave clock distribution network.

The loss of the transmission lines is one of the practical issues of standing wave

Figure 3.2: Rotary resonant clock [86]

clock. The transmission line loss attenuates the amplitude of the waves and hence, introduces a residual traveling wave that leads to clock skew. Distributed trans conductors [5, 19, 86] are introduced to compensate for signal attenuation because of wire loss. Another practical issues of standing wave clock is the varying amplitude. To connect standing wave clock to conventional clock network, specific two-stage clock buffers [45] are required to convert the low-swing standing wave signal to digital level signal.

#### 3.1.2 Rotary Resonant Clock

A rotary clock (shown as in Figure 3.2) is a closed parallel loop formed by an inner and outer transmission line [86]. When a signal is applied to the cross-connected inner and outer loop, the signal could travel on this loop indefinitely if there is no loss. Same as standing wave clock, negative impedance components are needed to overcome the signal attenuation.

Unlike standing wave clocks, the maximum amplitude of all positions in a rotary clock loop are the same while the phase varies with position. The differences between sink

phases bring about extra work in clock timing and synchronization since clock sinks may be attached to different positions on the loop. Though there are two-phase latched logic [86], connecting conventional signal D-latch to the rotary clock loop needs extra work on skew scheduling which makes it inapplicable in practical designs. Up to now, there is no logic synthesis tools supporting the design with different phase clock network.

#### 3.1.3 Distributed Inductor-Capacitor (LC) Resonant Clock

Both standing wave clocks and rotary clocks have severe restrictions on the physical implementation so that the correct phase or amplitude is used. This makes them difficult to apply in practice, because most clock distributions are asymmetric and unbalanced. On the other hand, LC (inductor-capacitor) tank resonant clocks ideally have constant phase and constant magnitude which allows these CDNs to have structure similar to previous non-resonant clocks. Industry has demonstrated several variants of distributed LC resonant clocks on uniform H-trees [7,8] and academia has demonstrated several monolithic LC tank clocks on small, low-speed designs [21,92,98].

LC-based resonant clocks are extensions of conventional clock with the addition of spiral inductors. Therefore, this thesis is focused on the application of inductor in LCbased resonant clocks. In the remainder of this thesis, the term "resonant clock" refers to a distributed LC resonant clock network.

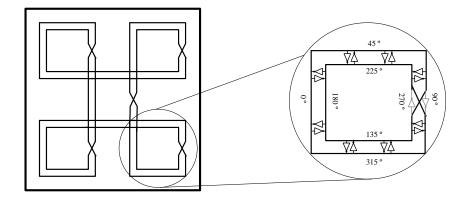

## 3.2 Theory of LC Resonant Oscillators

The admittance of inductance, capacitance, and resistance for Alternating Current (AC) signals are most often represented using complex numbers:  $G_R = 1/R$ ,  $G_L = 1/(j\omega L)$ , and  $G_C = j\omega C$  that depend on the frequency of operation ( $\omega$ ). A parallel or series LC tank has capacitive reactance and inductive reactance exactly equal at one specific frequency which is known as the *resonant frequency*. By equating the inductive and capacitive reactances ( $G_L = G_C$ ), we can obtain the unique resonant frequency as

$$f = \frac{\omega}{2\pi} = \frac{1}{2\pi\sqrt{LC}} \tag{3.1}$$

where L is the inductor size and C is the capacitor size. In a parallel LC tank, this ideally presents infinite impedance, while in a series LC tank this ideally presents zero impedance. This has been used extensively in building high-quality passive filter networks, but it also has enormous potential to lower the power required to drive clock distributions.

(b) LC tank oscillator with decoupling capacitance to positively bias the voltage of capacitor C

Figure 3.3: LC Tank Oscillators

(a) Energy transfer from electric field in capacitor C to magnetic field in inductor L

(b) Energy transfer from magnetic field in inductor L to electric field in capacitor C

Figure 3.4: Energy exchange in LC tank oscillators

When an AC signal such as a clock is applied to these LC tanks, they form a *resonant oscillator*. Resonant oscillators can circumvent the active power in Equation 1.1 by using inductive reactance. In a clock distribution, the wire and sink capacitances form the clock distribution capacitance (C) as shown in Figure 3.3(a), which is parallel to L. The energy in the system is exchanged between an electric field in C and a magnetic field in the inductor (L) as in Figure 3.4(a). The charge stored on the capacitor C is discharged through the inductor L which then induces a current and subsequently the opposite charge on the capacitor in Figure 3.4(b). The voltage across C is maximized when this voltage and the input current are in phase at the resonant frequency. With no parasitic resistances, this will oscillate indefinitely.

A simple LC tank will naturally oscillate between a positive and negative voltage so we must also add an additional decoupling capacitor ( $C_d$ ) to the grounded end of each inductor as shown in Figure 3.3(b) to positively bias the voltage to a compatible CMOS logic range (0 to  $V_{dd}$ ) [7,8]. This additional capacitor, however, creates an additional undesirable parasitic series LC tank. Care must be taken in sizing  $C_d$  to ensure that the series LC tank resonant frequency is distinctly separated from the parallel LC tank resonant frequency or, more formally,

$$\frac{1}{2\pi\sqrt{LC_d}} \ll \frac{1}{2\pi\sqrt{LC}}.$$

(3.2)

## 3.3 Resonant Clock Grid

Figure 3.5: Structure of a distributed LC resonant clock grid

Clock grids are often used for regional clock distribution in high-performance designs due to their robustness to process and environmental variations. A clock grid is formed by a set of vertical and horizontal wires with stubs connecting clock sinks. A top-level tree is often used to drive the grid. A *resonant clock grid* is a clock grid with distributed LC tanks which resonate at the operating frequency attached directly to the grid wires. Figure 3.5 shows a resonant grid with a top-level tree and three such LC tanks. The intersection of grid wires are called *grid nodes*. Clock sinks are connected to grid wires through *stubs*. The intersection nodes of grid wires and stubs are called *stub nodes*. A *node capacitance* is the sum of the capacitance of all wires, sinks and buffers which are adjacent to a node. The grid wire, grid buffer and sink capacitances form the capacitor (C) in Figure 3.3(a) and, as such, the inductors (L) and decoupling capacitors ( $C_d$ ) should be placed/sized according to the capacitance C is distributed throughout a chip which introduces parasitic resistance from the CDN itself. The grid buffers are inserted to compensate for the energy loss of the tanks due to parasitics.

### 3.4 **On-Chip Inductors**

Figure 3.6: On-chip square spiral inductor made with normal metal layers

The on-chip inductors used in LC tank resonant clock grids can be created using normal metal layers, special layers in RF processes, or using free-standing MEMs devices [68]. Multi-layer spiral inductors can also use mutual inductance between adjacent spirals increases the total inductance [12,46]. The total inductance of a n-layer inductor inductor is  $n^2$  of one inductor [99]. These inductors can be planar or 3D. With 3D inductor techniques, inductors can be designed with less area and comparable performance.

Our analysis conservatively assumes that we will be using a common commercial process and that on-chip inductors will be created using single-layer square spiral topologies with ground shields [93] as shown in Figure 3.6. The inductance of inductor has two parts, self and mutual inductance. The total inductance is the sum of self inductance, positive mutual inductance which contributes to increase self magnetic flux, and the negative mutual inductance which reduces the magnetic flux. Mutual inductance between two segments depends on their distance, shape, intersection angle [2] and there are many algorithm and models have been provided to calculate the self and mutual inductance [23, 67].

In the model we use [2], the inductance is

$$L = 0.0002l \left[ ln \frac{2l}{(w+t)} + 0.5 + \frac{w+t}{3l} \right] nH$$

(3.3)

where the n is the number of turns, w is the width of trace, t is the thickness of the metal, l is the length of trace and s is the spacing between turns. Given n, s, w, and  $d_i$  (the inner diameter of the square spiral inductor), the metal area occupied by an inductor is

$$Area = d_o^2 = (d_i + 2n(s+w))^2$$

(3.4)

where  $d_o$  is the outer diameter.

Significant parasitic resistances and capacitances are also associated with an inductor and can alter their efficiency. The quality factor Q of an inductor is the ratio of its reactance to its resistance at a certain frequency

$$Q = \frac{\omega L}{R}.$$

(3.5)

The thick top metal layer with higher conductivity is often used to implemented the inductor to reduce the ohmic losses.

Given modern process dimensions and oxides, it is feasible to create high-Q spiral inductors with densities of  $32 - 40nH/mm^2$  at chip speeds of 1 - 5 GHz [15]. This is the first work to consider actual inductor area based on Equation 3.4 during the distributed LC tank clock synthesis while all previous LC tank resonant clock works have not quantify the inductor overhead in this way. All inductors are created on the single, top-level metal layer and do not obstruct active devices or other routing layers. In later results, the percentage of this metal layer area is used to quantify the overhead consumed by all on-chip inductors. Specialized EM inductor simulation tools such as ASITIC [47] can be used to model the inductors at various accuracies.

## **3.5 On-Chip Capacitors**

The on-chip decoupling capacitors which used in resonant clock are also widely utilized to manage transient power supply noise and are commonly implemented as polysiliconinsulator-polysilicon (PIP), MOS-based or metal-insulator-metal (MIM) capacitors [33].

# **Chapter 4**

## **Resonant Clock Grid Synthesis Overview**

The basic elements in CDN and their analytical models have been introduced in Chapter 2.3. In this chapter, the resonant clock analysis method is introduced which is different from the method used in non-resonant clock design. The inductors in the resonant clock cause special problems which do not exist in non-resonant clock network. All these challenges are summarized in this chapter. At the end of this chapter, a complete resonant clock synthesis flow is provided with each step addressing different challenges.

## 4.1 Resonant Clock Analysis

In clock tree synthesis, Elmore delay is widely used to quickly estimate the timing [17, 38, 76]. In the clock grid synthesis, as there are more components and possibly loops in the circuits, some other methods has been proposed to simplify the massively network to speed the analysis of clock grid. By merging the drivers and reducing model order [81, 89, 90], the massive network size is reduced and fast clock mesh simulation is possible. However, these kinds of fast simulation methods are not applicable to resonant clock grids. If two buffers are merged together as a super driver as in [90], the new super buffer shows different parasitic resistance and capacitance to the LC tanks which changes the resonant behavior. How this change effects the resonant grid is discussed in detail later. Moreover, the buffer driving ability can not be easily estimated by logical effort due to the interaction with the LC tanks. These fast simulation methods used in non-resonant grid analysis are not applicable to resonant grid analysis.

#### 4.1.1 Transient Analysis

A widely used clock network analysis method is transient analysis. At every time point in transient analysis, the time-dependent components, such as capacitors and inductors, are replaced by their equivalent circuit according to their instantaneous I-V characters [56]. At different time points, these I-V relationships change, so the transient analysis has to run many iterations and it is usually very time consuming for large circuits. With detailed calculations at each time point, transient analysis is able to plot any time-domain waveform, like voltage, current and power. Because the clock signal varies with time in a clock cycle, transient analysis is usually used to measure power and to check that the timing related clock metrics, such as skew and slew, are satisfied.

#### 4.1.2 AC Analysis

In the frequency-domain, small signal analysis, or Alternating Current analysis (AC analysis) is used to simulate the circuit at different frequencies. Similar to transient analysis, AC frequency sweep is a small-signal linear analysis. While transient analysis

solves circuit equation at different timing analysis points, AC analysis build the circuit equations at different frequencies and solves the linear equations to simulate the circuit in the frequency-domain. The AC analysis is a linear modified nodal analysis, thus no iteration is necessary and it is much faster than transient analysis.

To consider the frequency effect on the circuit, complex quantities are applied in the AC analysis and non-linear circuit components are replaced by their linear smallsignal models. As introduced in Chapter 3.2, the voltage, current, and RLC in a circuit are represented as complex numbers which include both phase and magnitude information. The clock grid circuit is written as a set of nodal equations which describe all the elements in the circuit. Using the complex admittance values of the CDN wires, sinks and LC tanks, we formulate the resonant grid as a complex linear system

$$GV = I \tag{4.1}$$

where G is the complex admittance matrix of the mesh, I are the mesh buffer driving currents, and V are the (complex) voltages of each sink/node in the grid. The complex voltages V include information about the voltage amplitude and phase of each node in the CDN.

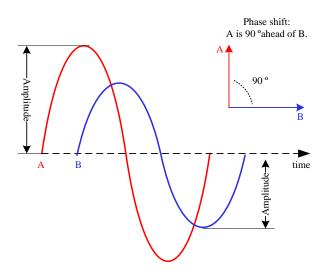

The complex voltage is v = x + jy, where x and y are both real numbers. The amplitude of v is  $\sqrt{x^2 + y^2}$  and the phase of v is  $tan^{-1}(\frac{y}{x})$ . Figure 4.1 shows the amplitude and phase relationship between two AC signals. There is a 90 degree phase between signal A and signal B.

Figure 4.1: Amplitude and phase of AC signals

## 4.2 Challenges in Resonant Clock Synthesis

### 4.2.1 Resonant Frequency Shift

The parasitic resistances and capacitances in the CDN alter the resonant frequency. To demonstrate the frequency shift caused by parasitics, we design a set of circuits and verify their resonant characteristics with AC analysis.

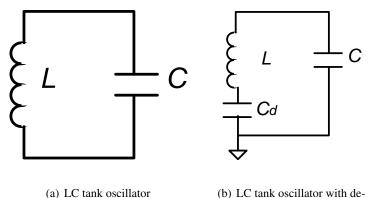

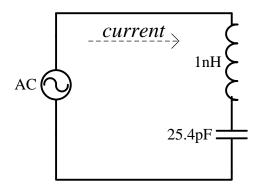

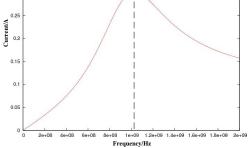

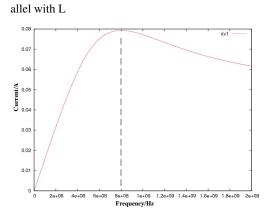

Figure 4.2(a) is an ideal serial LC circuit without parasitic resistance. According to the resonant frequency calculation Equation 3.1, the resonant frequency is about 1GHz. Figure 4.3(a) plots the current of this LC circuit by running AC analysis. The current at the resonant frequency is maximized and because it is an ideal LC tank, the waveform is very sharp showing a very good qualify factor Q which is introduced in Chapter 3.4.

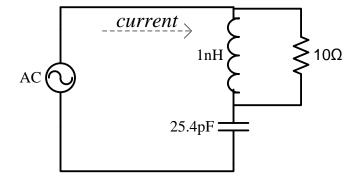

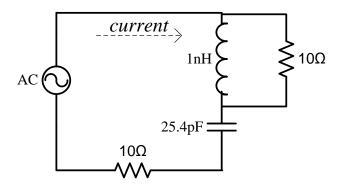

Figure 4.2(b) is the same LC circuit but considering the parasitic resistance of inductor. The  $10\Omega$  resistor is selected to illustrate the parasitic resistance effect. Figure 4.3(b)

(a) Ideal LC resonant circuit

(b) LC resonant circuit with resistance in parallel with L, the parallel

resistance represents the parasitic of inductor L

(c) LC resonant circuit with resistance in parallel with L and resis-

tance in series with R, the series resistance represents the parasitic

of wire

Figure 4.2: Parasitic resistances and capacitances in LC circuit alter the resonant frequency.

(b) AC analysis of LC circuit with resistance in par-

(c) AC analysis of LC circuit with resistance in parallel with L and resistance in serial with R

Figure 4.3: Current plots in AC analysis of circuit 4.2

is the corresponding current plot from AC analysis. The current reaches the maximum value around 1GHz, which means the parallel parasitic resistance of the inductor doesn't change the resonant frequency much. However, the current waveform is very different from Figure 4.3(a). The wave is flatter which means the quality factor Q of this circuit is smaller than the ideal LC circuit.

In Figure 4.2(c), another series resistor is added which represents the interconnect wire resistance or the capacitor parasitic resistance. The AC analysis 4.3(c) clearly shows that the current reaches its maximum at 0.8GHz which means the resonant frequency of this circuit has been shifted to 0.8GHz because of the new serial  $10\Omega$  resistor. The much flatter waveform shows the Q factor of this circuit is even worse.

Though the parallel resistor of inductor in Figure 4.2(b) doesn't significantly change resonant frequency, the serial resistor in Figure 4.2(c) shifts the resonant frequency by 20% even the circuit is as simple as a single LC tank like Figure 4.2. The clock grid structure is much more complex with a huge number of components, loops, parallel and series resistors. The LC tanks placement and sizing should carefully consider this parasitic resistance, otherwise, the final resonant frequency may shift away from the designated clock frequency as in previous hand-made designs [9,21].

#### 4.2.2 Signal Attenuation

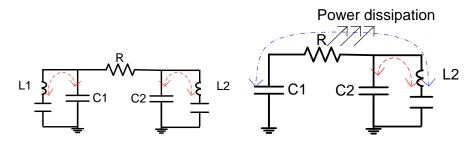

On closer inspection, besides alternating the resonant frequency, the CDN wire resistance also changes the maximum current at resonant frequency. The maximum current of ideal resonant circuit is 23A which is attenuated to 0.3A with one parallel resistor in Figure 4.3(b) and further attenuated to 0.08A with two resistors in Figure 4.3(c). This indicates another negative effect of parasitic to the resonant clock: it attenuates voltage swings at high frequencies. The signal attenuation can also be caused by a driver with high resistance.