## UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Topologies, Modeling, and Control of Hybrid Switched-Capacitor Converters

## Permalink

https://escholarship.org/uc/item/27t9s234

## Author

Das, Ratul

## **Publication Date**

2022

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

Topologies, Modeling, and Control of Hybrid Switched-Capacitor Converters

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

#### Electrical Engineering (Electronic Circuits and Systems)

by

Ratul Das

Committee in charge:

Professor Hanh-Phuc Le, Chair Professor Jan Kleissl Professor Patrick Mercier Professor Chunting Mi Professor Tse Nga Ng

Copyright

Ratul Das, 2022

All rights reserved.

The Dissertation of Ratul Das is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2022

## DEDICATION

This thesis is dedicated to my undergraduate thesis supervisor late Dr. Kazi Mujibur Rahman. He taught me how to think like an engineer.

#### EPIGRAPH

It doesn't matter how beautiful your theory is, it doesn't matter how smart you are. If it doesn't agree with the experiment, it's wrong.

Richard Feynman

The saddest aspect of life right now is that gathers knowledge faster than society gathers wisdom.

Isaac Asimov

The good thing about science is that it's true whether or not you believe in it.

Neil deGrasse Tyson

| Dissertation Approval Page                                                                                                                                                                                                                                                      | iii                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Dedication                                                                                                                                                                                                                                                                      | iv                                     |

| Epigraph                                                                                                                                                                                                                                                                        | v                                      |

| Table of Contents                                                                                                                                                                                                                                                               | vi                                     |

| List of Figures                                                                                                                                                                                                                                                                 | xi                                     |

| List of Tables                                                                                                                                                                                                                                                                  | xix                                    |

| Preface                                                                                                                                                                                                                                                                         | xxi                                    |

| Acknowledgements                                                                                                                                                                                                                                                                | xxii                                   |

| Vita                                                                                                                                                                                                                                                                            | xxix                                   |

| Abstract of the Dissertation                                                                                                                                                                                                                                                    | xxxi                                   |

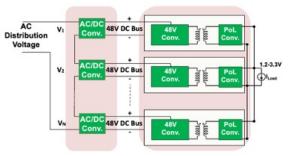

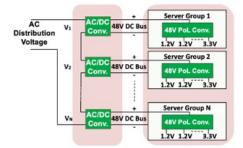

| Chapter 1Introduction1.1Power Delivery Architectures1.2Hybrid Switched-Capacitor Converters1.3Thesis Organization                                                                                                                                                               | 1<br>2<br>6<br>7                       |

| Part I Multi Inductor Hybrid Converter Family                                                                                                                                                                                                                                   | 9                                      |

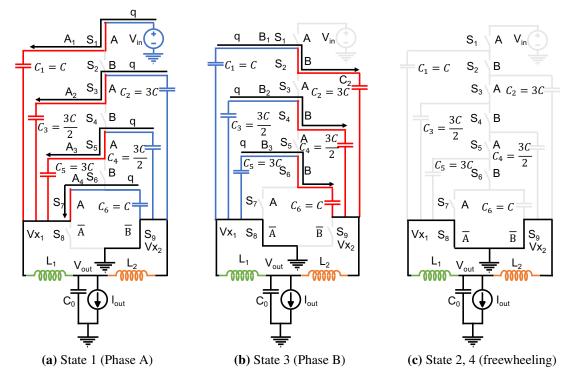

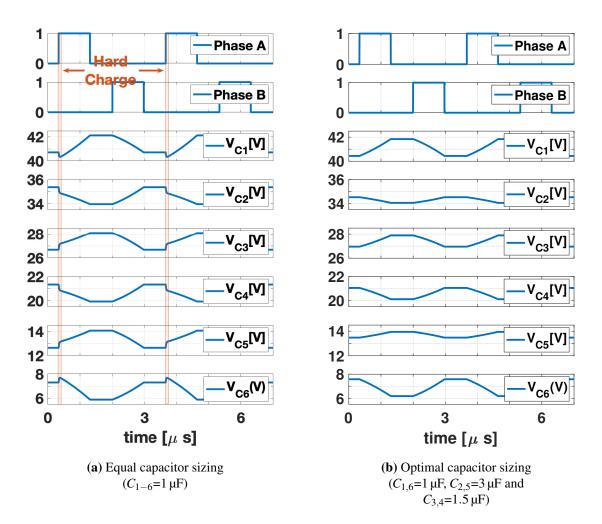

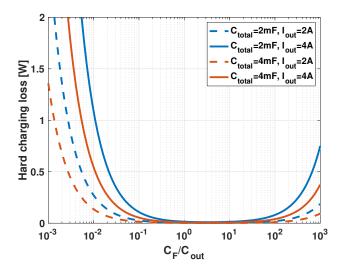

| <ul> <li>Chapter 2 Analysis of Dual-Inductor Hybrid Converters for Extreme Conversion Ratios</li> <li>2.1 Introduction</li> <li>2.2 Operation of DIH Converter</li> <li>2.3 Impacts of Flying Capacitor Values on Their Voltage Ripples and Soft-Charging Capability</li> </ul> | 10<br>10<br>14<br>18                   |

| <ul> <li>2.3.1 Flying Capacitors of the Same Value</li></ul>                                                                                                                                                                                                                    | 20<br>22<br>24<br>24<br>30<br>34<br>35 |

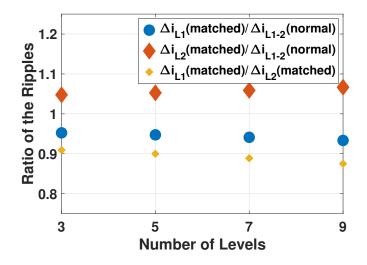

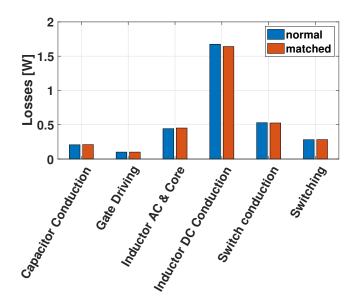

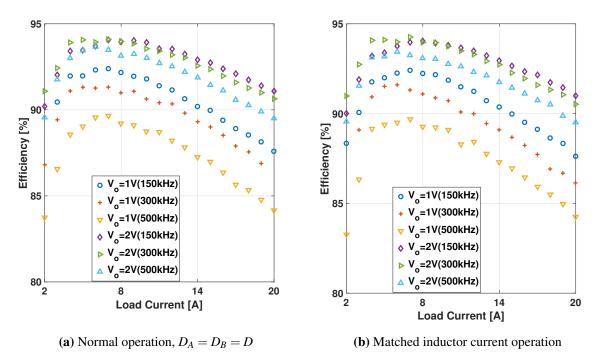

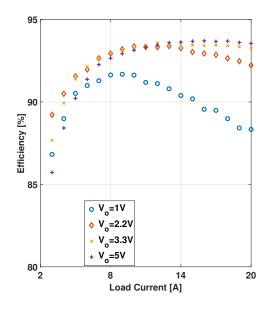

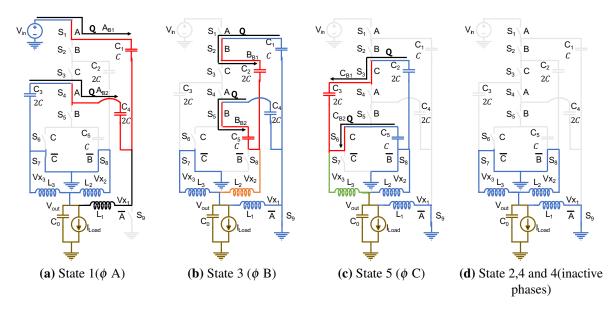

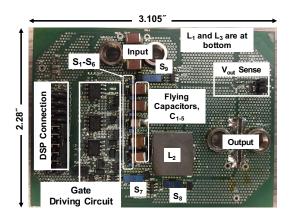

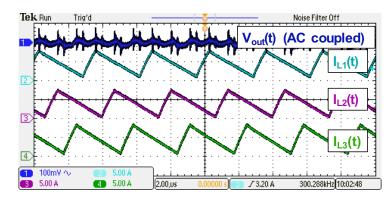

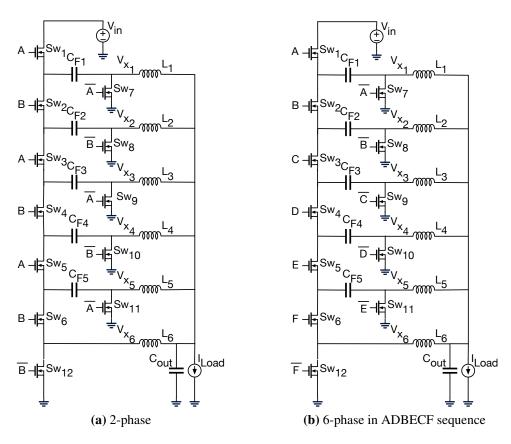

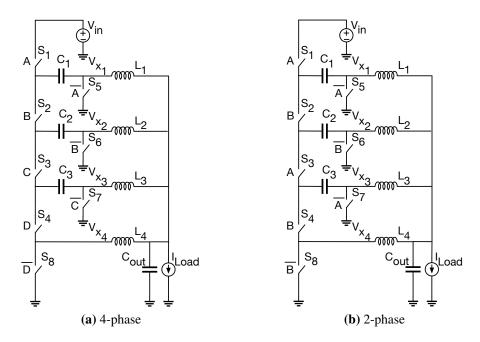

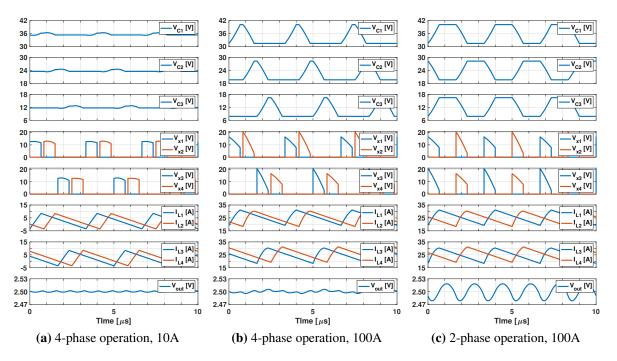

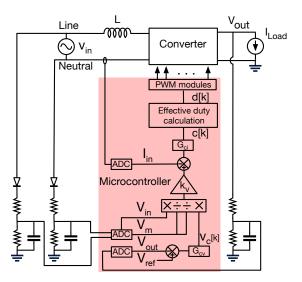

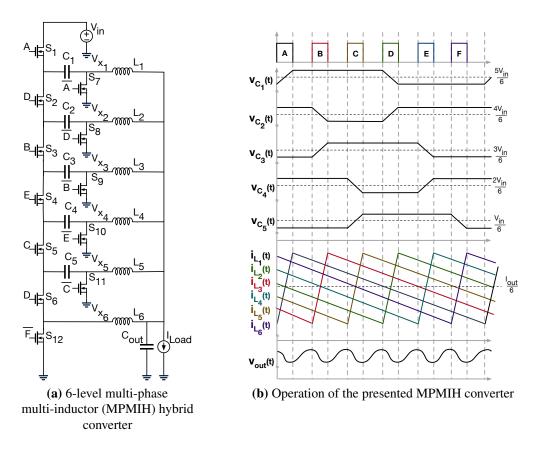

| Chapter 3An 80-W 94.6%-Efficient Multi-Phase Multi-Inductor Hybrid Converter3.1Introduction3.2Operation of the Multi-Phase Multi-inductor Hybrid Converter3.3Soft-Charging Operation and Strategy for Capacitor Sizing                                                          | 37<br>37<br>38<br>41                   |

## TABLE OF CONTENTS

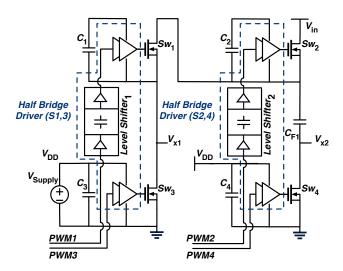

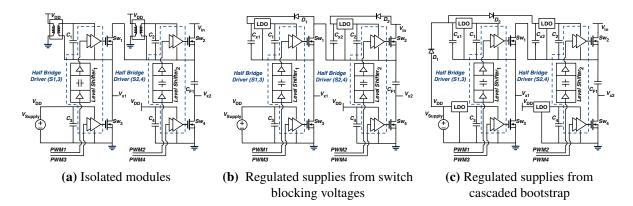

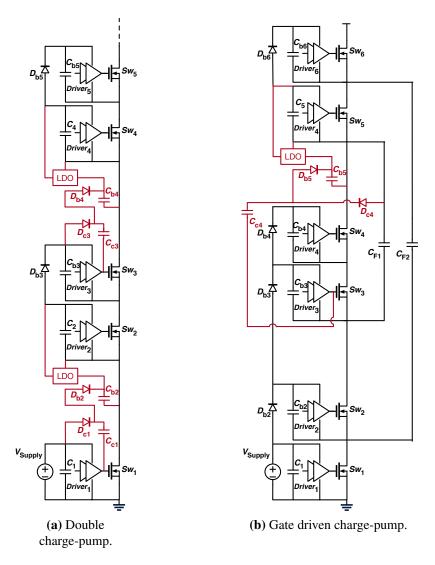

| Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results <th>3.4</th> <th>Experimental Results</th> <th>45</th>                            | 3.4      | Experimental Results                                                         | 45  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------|-----|

| Applications in Data Centers and Telecommunication Systems       47         4.1       Introduction       47         4.2       Operation of the DPMIH Converter       49         4.3       Native Soft-Charging and Analysis of Switching Node Voltages       51         4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid Converter       59         5.2.2       Multi-Inductor Hybrid Converter       62         5.2.3       Multi-Inductor Hybrid Converter       63         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.4       Series Capacitor Buck (SCB) Converter       73         6.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter<                                                                                | 3.5      | Chapter Summary                                                              | 46  |

| Applications in Data Centers and Telecommunication Systems       47         4.1       Introduction       47         4.2       Operation of the DPMIH Converter       49         4.3       Native Soft-Charging and Analysis of Switching Node Voltages       51         4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid Converter       59         5.2.2       Multi-Inductor Hybrid Converter       62         5.2.3       Multi-Inductor Hybrid Converter       63         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.4       Series Capacitor Buck (SCB) Converter       73         6.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter<                                                                                |          |                                                                              |     |

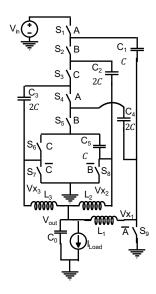

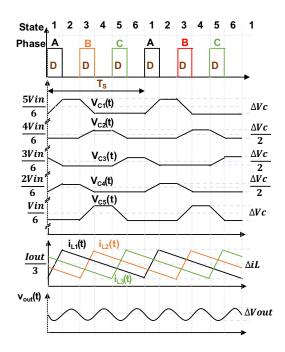

| 4.1       Introduction       47         4.2       Operation of the DPMIH Converter .       49         4.3       Native Soft-Charging and Analysis of Switching Node Voltages       51         4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid Converter       59         5.2.2       Multi-Inductor Hybrid Converter       52         5.2.3       Multi-Inductor Hybrid Converter       52         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2                                                                                                                        | Chapter  |                                                                              |     |

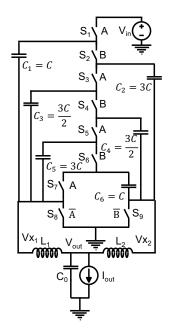

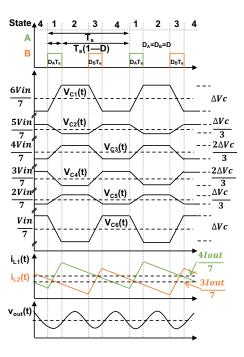

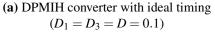

| 4.2       Operation of the DPMIH Converter       49         4.3       Native Soft-Charging and Analysis of Switching Node Voltages       51         4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Inductor Hybrid Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Driveres       75 <t< td=""><td></td><td></td><td></td></t<>                                                                    |          |                                                                              |     |

| 4.3       Native Soft-Charging and Analysis of Switching Node Voltages       51         4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       63         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73       75         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78 <td>4.1</td> <td>Introduction</td> <td>47</td>                                                                 | 4.1      | Introduction                                                                 | 47  |

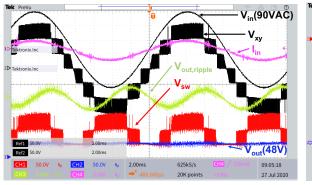

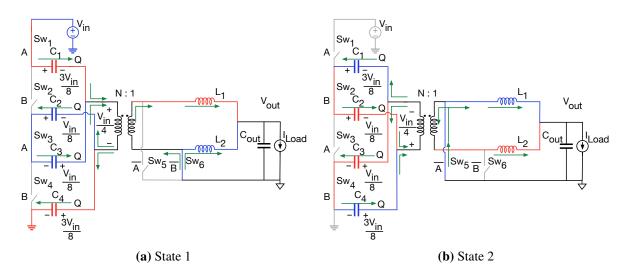

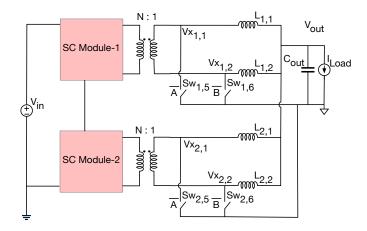

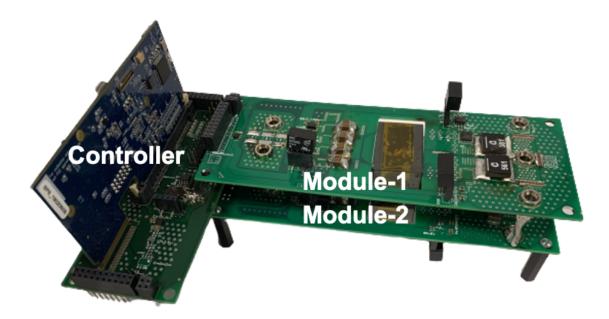

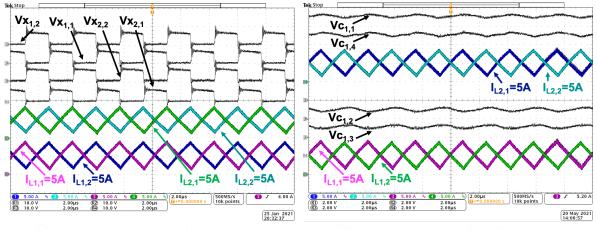

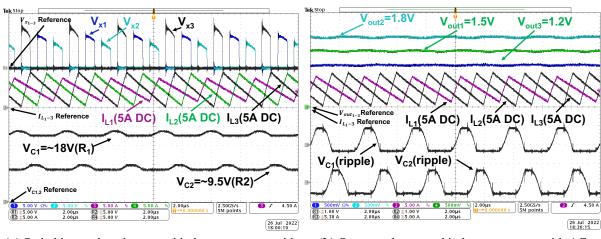

| 4.4       Experimental Results       54         4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       58         5.2.1       Dual Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Newer Rail Generation       78         6.3.1       Use of Isolated Power Modules       78                                                                                                             | 4.2      | Operation of the DPMIH Converter                                             | 49  |

| 4.5       Chapter Summary       55         Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid Converter Family and Synthesis       58         5.2.2       Multi-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79 </td <td>4.3</td> <td>Native Soft-Charging and Analysis of Switching Node Voltages</td> <td>51</td> | 4.3      | Native Soft-Charging and Analysis of Switching Node Voltages                 | 51  |

| Part II       Techniques Related to Multi-Inductor Hybrid Converters       56         Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis       57         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Inductor Hybrid Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       79         6.3.2       Regulated Supplies from Switch Blocking Voltages       79 <td>4.4</td> <td>Experimental Results</td> <td>54</td>                                               | 4.4      | Experimental Results                                                         | 54  |

| Chapter 5       Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Analysis         5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85                                                                                      | 4.5      | Chapter Summary                                                              | 55  |

| ysis575.1Introduction575.2Multi-Inductor Hybrid Converter Family and Synthesis585.2.1Dual Inductor Hybrid (DIH) Converter595.2.2Multi-Phase Dual-Inductor Hybrid (DIH) Converter625.2.3Multi-Inductor Hybrid Converter625.2.4Series Capacitor Buck (SCB) Converter635.2.5Optimal Inductor Hybrid Converter635.3Small Signal Model Based on Averaged Circuit Modeling645.4Chapter Summary71Chapter 6Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                               | Part II  | Techniques Related to Multi-Inductor Hybrid Converters                       | 56  |

| ysis575.1Introduction575.2Multi-Inductor Hybrid Converter Family and Synthesis585.2.1Dual Inductor Hybrid (DIH) Converter595.2.2Multi-Phase Dual-Inductor Hybrid (DIH) Converter625.2.3Multi-Inductor Hybrid Converter625.2.4Series Capacitor Buck (SCB) Converter635.2.5Optimal Inductor Hybrid Converter635.3Small Signal Model Based on Averaged Circuit Modeling645.4Chapter Summary71Chapter 6Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapter  | 5 Multi Inductor Hybrid Converter Family: Synthesis and Small Signal Anal-   |     |

| 5.1       Introduction       57         5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85                                                                                                         | 1        |                                                                              | 57  |

| 5.2       Multi-Inductor Hybrid Converter Family and Synthesis       58         5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       79         6.3.2       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92         Part III       General Analyses of Hybrid Switched-Capacitor Converters       94 </td <td>5.1</td> <td>-</td> <td>57</td>                                                  | 5.1      | -                                                                            | 57  |

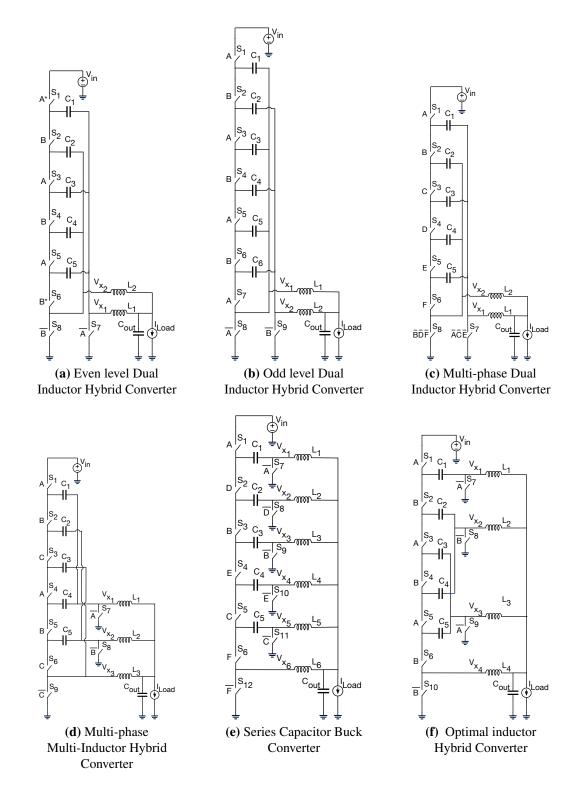

| 5.2.1       Dual Inductor Hybrid (DIH) Converter       59         5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92                                                                                                                       |          |                                                                              |     |

| 5.2.2       Multi-Phase Dual-Inductor Hybrid (DIH) Converter       62         5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92         Part III       General Analyses of Hybrid Switched-Capacitor Converters       94                                                                                                                                                               | 0.2      |                                                                              |     |

| 5.2.3       Multi-Inductor Hybrid Converter       62         5.2.4       Series Capacitor Buck (SCB) Converter       63         5.2.5       Optimal Inductor Hybrid Converter       63         5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       79         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92         Part III       General Analyses of Hybrid Switched-Capacitor Converters       94                                                                                                                                                                                                                                             |          |                                                                              |     |

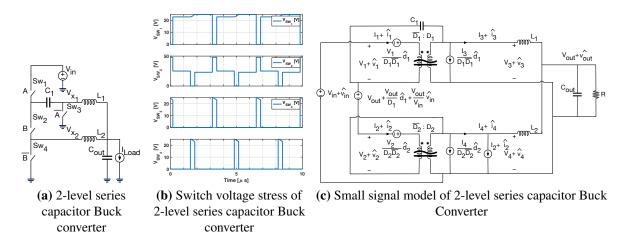

| 5.2.4Series Capacitor Buck (SCB) Converter635.2.5Optimal Inductor Hybrid Converter635.3Small Signal Model Based on Averaged Circuit Modeling645.4Chapter Summary71Chapter 6Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                                                                              |     |

| 5.2.5Optimal Inductor Hybrid Converter635.3Small Signal Model Based on Averaged Circuit Modeling645.4Chapter Summary71Chapter 6Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                              |     |

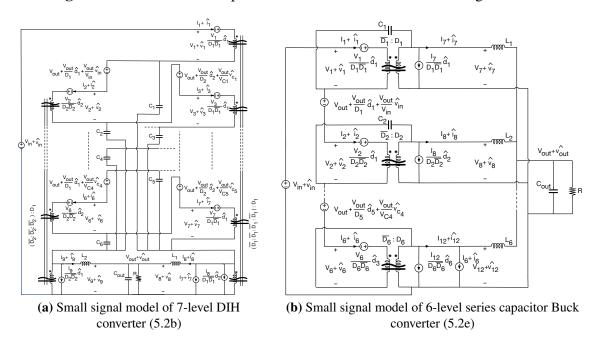

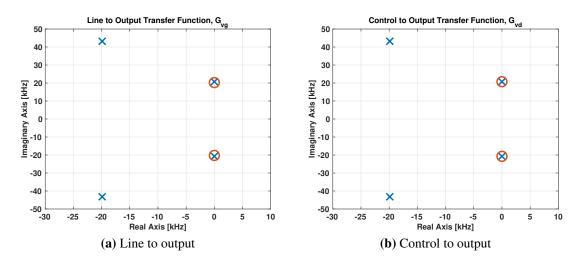

| 5.3       Small Signal Model Based on Averaged Circuit Modeling       64         5.4       Chapter Summary       71         Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92         Part III       General Analyses of Hybrid Switched-Capacitor Converters       94                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 1 /                                                                          |     |

| 5.4Chapter Summary71Chapter 6Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53       | 1 2                                                                          |     |

| Chapter 6       Gate Driver Circuits With Discrete Components For GaN-based Multi-Level<br>Multi-Inductor Hybrid Converter       73         6.1       Introduction       73         6.2       Optimal Use of Half-bridge Drivers       75         6.3       Power Rail Generation       78         6.3.1       Use of Isolated Power Modules       78         6.3.2       Regulated Supplies from Switch Blocking Voltages       79         6.3.3       Regulated Supplies from Cascaded Bootstrap Circuits       80         6.3.4       Discussion on Recently Popular Charge-Pump Methods       82         6.4       Hardware Implementations and Experimental Results       85         6.5       Chapter Summary       92         Part III       General Analyses of Hybrid Switched-Capacitor Converters       94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                                              |     |

| Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.4      |                                                                              | /1  |

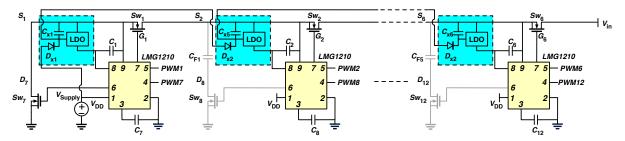

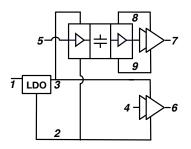

| Multi-Inductor Hybrid Converter736.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Chapter  | 6 Gate Driver Circuits With Discrete Components For GaN-based Multi-Level    |     |

| 6.1Introduction736.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | empter   | 1                                                                            | 73  |

| 6.2Optimal Use of Half-bridge Drivers756.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61       |                                                                              |     |

| 6.3Power Rail Generation786.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                              |     |

| 6.3.1Use of Isolated Power Modules786.3.2Regulated Supplies from Switch Blocking Voltages796.3.3Regulated Supplies from Cascaded Bootstrap Circuits806.3.4Discussion on Recently Popular Charge-Pump Methods826.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                                                              |     |

| 6.3.2 Regulated Supplies from Switch Blocking Voltages796.3.3 Regulated Supplies from Cascaded Bootstrap Circuits806.3.4 Discussion on Recently Popular Charge-Pump Methods826.4 Hardware Implementations and Experimental Results856.5 Chapter Summary92Part III General Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.5      |                                                                              |     |

| 6.3.3 Regulated Supplies from Cascaded Bootstrap Circuits806.3.4 Discussion on Recently Popular Charge-Pump Methods826.4 Hardware Implementations and Experimental Results856.5 Chapter Summary92Part III General Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                              |     |

| 6.3.4 Discussion on Recently Popular Charge-Pump Methods826.4 Hardware Implementations and Experimental Results856.5 Chapter Summary92Part III General Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                                              |     |

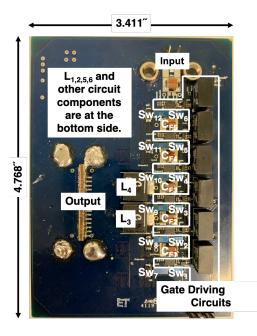

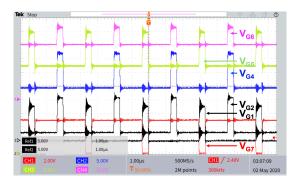

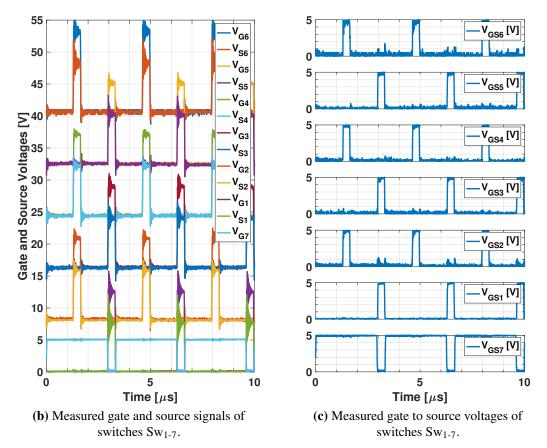

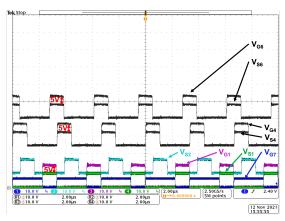

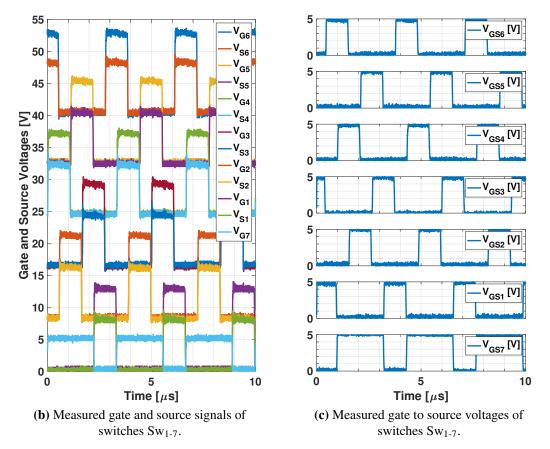

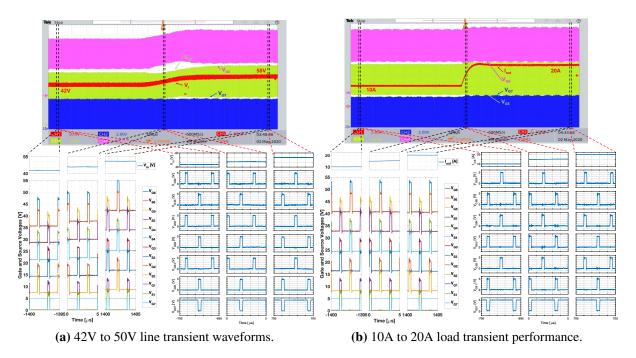

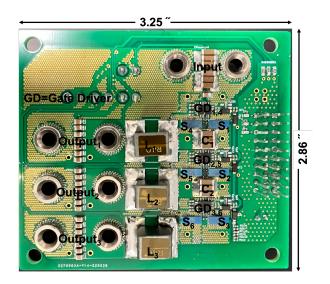

| 6.4Hardware Implementations and Experimental Results856.5Chapter Summary92Part IIIGeneral Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                                              |     |

| 6.5 Chapter Summary92Part III General Analyses of Hybrid Switched-Capacitor Converters94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6 1      |                                                                              |     |

| Part III General Analyses of Hybrid Switched-Capacitor Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                              |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.3      | Chapter Summary                                                              | 92  |

| Chapter 7 Demystifying Capacitor Voltages and Inductor Currents in Hybrid Converters 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Part III | General Analyses of Hybrid Switched-Capacitor Converters                     | 94  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Chapter  | 7 Demystifying Capacitor Voltages and Inductor Currents in Hybrid Converters | 95  |

| 7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.1      |                                                                              | 95  |

| 7.2 Median and Average Values of Component State Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7.2      | Median and Average Values of Component State Variables                       | 97  |

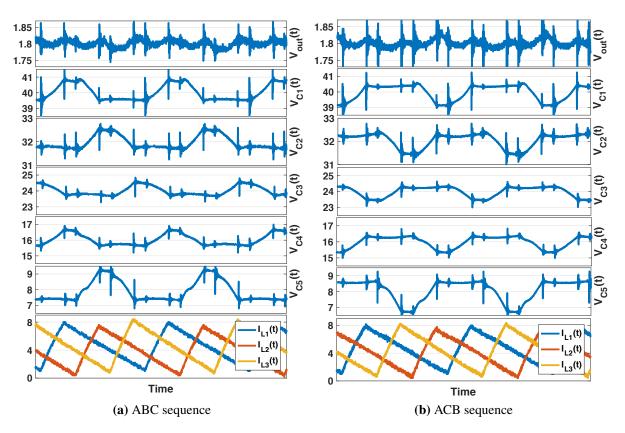

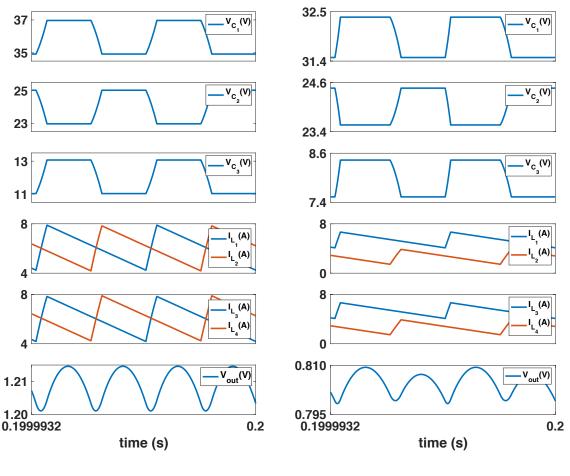

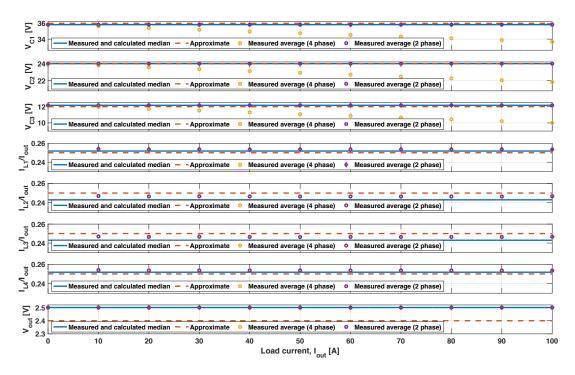

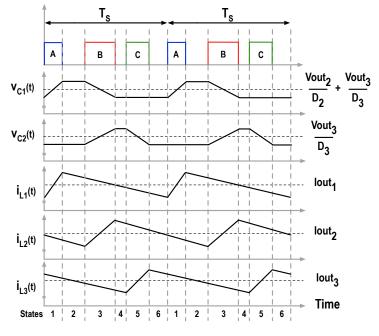

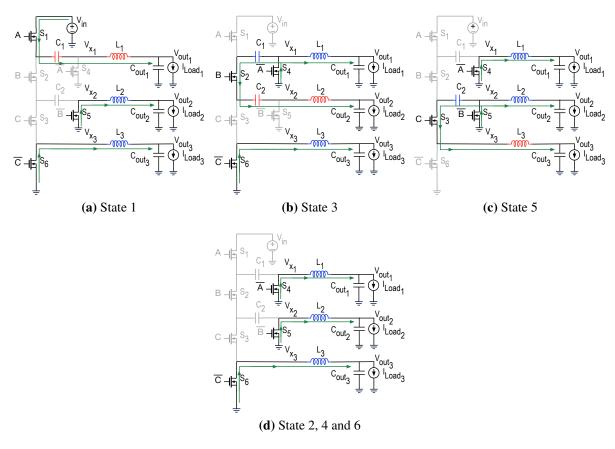

| 7.3 Application to the DPMIH Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.3      |                                                                              | 99  |

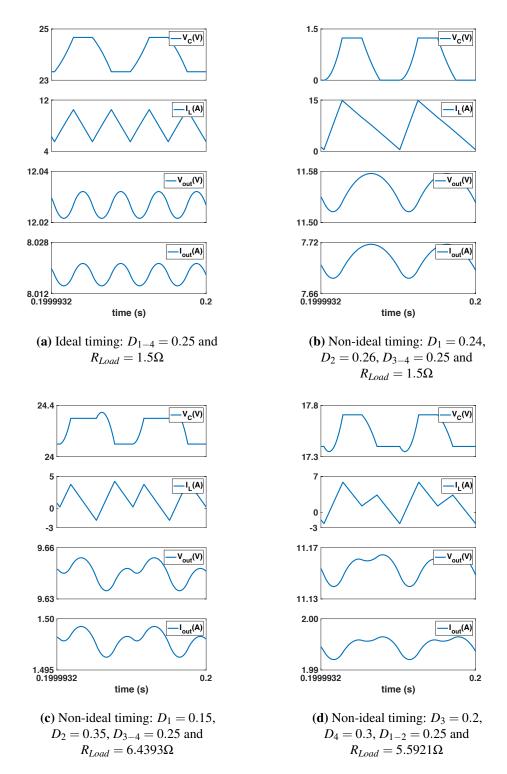

| 7.3.1 Ideal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 7.3.1 Ideal Timing                                                           | 99  |

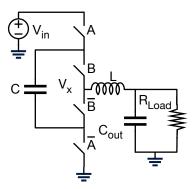

| 7.3.2 Non-Ideal Timing 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 7.3.2 Non-Ideal Timing                                                       | 102 |

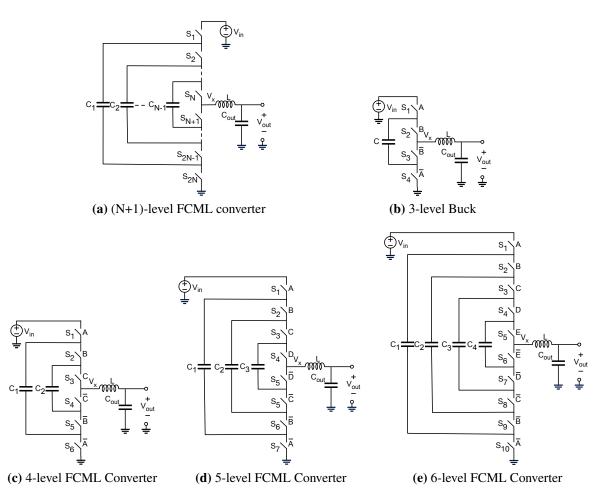

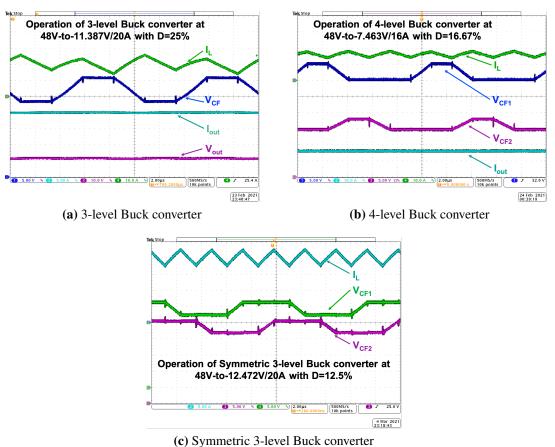

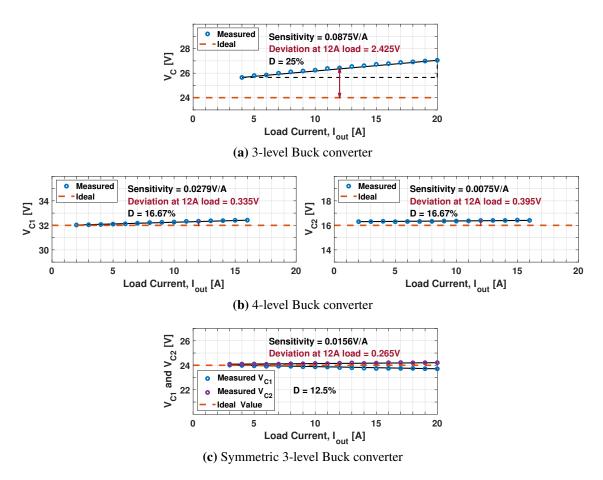

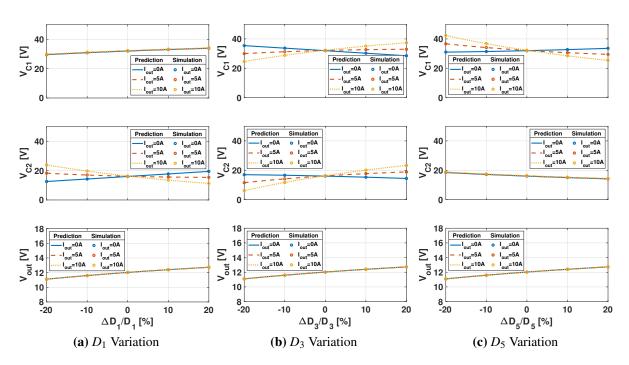

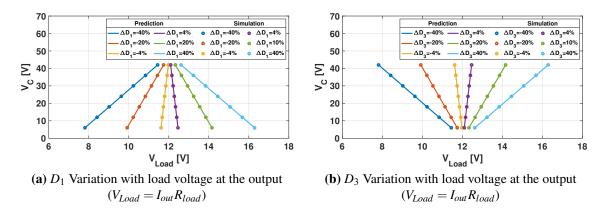

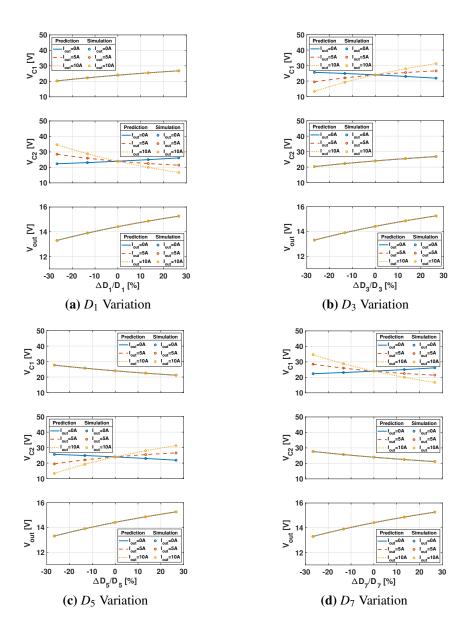

| 7.4       Application to the 3-Level Buck Converter       104         7.4.1       Ideal Timing       105         7.4.2       Non-Ideal Timing       106         7.4.3       Verification       111         7.5       Chapter Summary       111         7.5       Chapter Summary       111         7.5       Chapter Summary       111         7.5       Chapter A Accurate Approach to Calculate and Measure Capacitor Voltage and<br>Inductor Current Levels in Hybrid Converter       113         8.1       Introduction       113         8.2       4-level Multi-Inductor Hybrid Converter       115         8.3       Median and Average Value Analysis       116         8.3.1       Flying Capacitor Voltages       117         8.3.2       Inductor Currents       118         8.3.3       Output Voltage       120         8.4       Chapter Summary       120         Chapter 9       Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inher-<br>ently Balanced Operation Using Symmetric Architecture       122         9.1       Introduction       124         9.3       Application to Multi-Level Converters       126         9.3.1       Inductor Current with Odd Number of Charging Intervals       126                                                                                                                              |           | 7.3.3 Verification                                                           | 104 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------|-----|

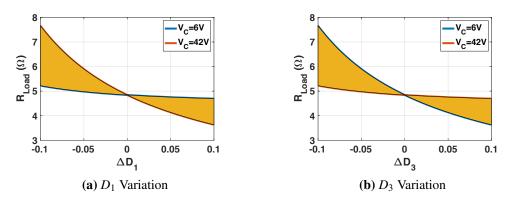

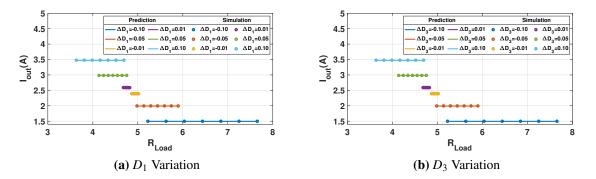

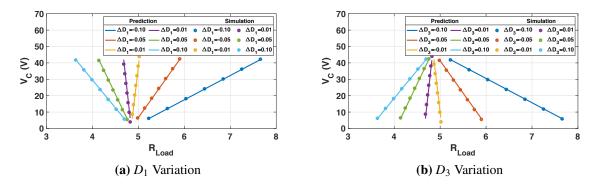

| 7.4.1Ideal Timing1057.4.2Non-Ideal Timing1067.4.3Verification1117.5Chapter Summary111Chapter SAn Accurate Approach to Calculate and Measure Capacitor Voltage and<br>Inductor Current Levels in Hybrid Converters1138.1Introduction1138.24-level Multi-Inductor Hybrid Converter1158.3Median and Average Value Analysis1168.3.1Flying Capacitor Voltages1178.3.2Inductor Currents1188.3.3Output Voltage1208.4Chapter Summary120Chapter 9Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inher-<br>ently Balanced Operation Using Symmetric Architecture1229.1Introduction1229.2Voltage-Charge Relationship1249.3Application to Multi-Level Converters1269.3.2Inductor Current with Odd Number of Charging Intervals1269.3.3Balancing Performance of Other Conventional Hybrid Converters with<br>$V_{out} < \frac{Vm}{V}$ 133Chapter 10General Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues1309.4Multi-phase Symmetric Converter Architecture for Voltage Balancing1309.5Experimental Verifications13410.1Introduction13410.2Analysis of FLying Capacitor Multi-Level Converters For Balancing<br>Issues133133Chapter 11Two-Stage Power Delivery Architecture144<                                                                                                                                                        | 7.4       | Application to the 3-Level Buck Converter                                    | 104 |

| 7.4.2Non-Ideal Timing1067.4.3Verification1117.5Chapter Summary1117.5Chapter Summary1117.5Chapter Summary1138.1Inductor Current Levels in Hybrid Converters1138.1Introduction1138.24-level Multi-Inductor Hybrid Converter1138.3Median and Average Value Analysis1168.3.1Flying Capacitor Voltages1178.3.2Inductor Currents1188.3.3Output Voltage1208.4Chapter Summary120Chapter 9Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inherently Balanced Operation Using Symmetric Architecture1229.1Introduction1229.2Voltage-Charge Relationship1249.3Application to Multi-Level Converters1269.3.1Inductor Current with Odd Number of Charging Intervals1269.3.2Inductor Current with Even Number of Charging Intervals1269.3.3Balancing Performance of Other Conventional Hybrid Converters with<br>$V_{out} < \frac{V_H}{N}$ 133Chapter 10General Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues13410.1Introduction133109.5Experimental Verifications13410.2Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues13410.1Introduction13410.2Analysis of Flying Capacitor Swith Non-Id                                                                                                                                                                                                                |           |                                                                              | 105 |

| 7.4.3Verification1117.5Chapter Summary1117.5Chapter Summary1117.5Chapter Summary1138.1Introductor Current Levels in Hybrid Converters1138.1Introduction1138.24-level Multi-Inductor Hybrid Converter1158.3Median and Average Value Analysis1168.3.1Flying Capacitor Voltages1178.3.2Inductor Currents1188.3.3Output Voltage120Chapter 9Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inherently Balanced Operation Using Symmetric Architecture1229.1Introduction1229.2Voltage-Charge Relationship1249.3Application to Multi-Level Converters1269.3.1Inductor Current with Even Number of Charging Intervals1279.3.3Balancing Performance of Other Conventional Hybrid Converters with<br>$V_{out} < \frac{V_B}{N}$ 1289.4Multi-phase Symmetric Converter Architecture for Voltage Balancing1309.5Experimental Verifications1309.6Chapter Summary133Chapter 10General Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues13410.1Introduction13410.2Analysis of FCML Converters13510.3Discussion on Odd Level FCML Converters with Non-Ideal Timing13810.4Discussion on Odd Level FCML Converters with Non-Ideal Timing13910.5 <td></td> <td>7.4.2 Non-Ideal Timing</td> <td>106</td>                                                                                                                                          |           | 7.4.2 Non-Ideal Timing                                                       | 106 |

| 7.5Chapter Summary111Chapter 8An Accurate Approach to Calculate and Measure Capacitor Voltage and<br>Inductor Current Levels in Hybrid Converters1138.1Introduction1138.24-level Multi-Inductor Hybrid Converter1158.3Median and Average Value Analysis1168.3.1Flying Capacitor Voltages1178.3.2Inductor Currents1188.3.3Output Voltage1208.4Chapter Summary1208.4Chapter Summary120Chapter 9Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inherently Balanced Operation Using Symmetric Architecture1229.1Introduction1229.2Voltage-Charge Relationship1249.3Application to Multi-Level Converters1269.3.1Inductor Current with Even Number of Charging Intervals1279.3.3Balancing Performance of Other Conventional Hybrid Converters with<br>$V_{out} < \frac{V_{an}}{V_{an}}$ 1289.4Multi-phase Symmetric Converter Architecture for Voltage Balancing1309.5Experimental Verifications13110.1Introduction13410.2Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues133113Inductor Current with Converters with Non-Ideal Timing13810.4Discussion on Even Level FCML Converters with Non-Ideal Timing13910.5Chapter Summary141Part IVFull Power Delivery Architecture143<                                                                                                                                                  |           | e                                                                            | 111 |

| Inductor Current Levels in Hybrid Converters1138.1Introduction1138.24-level Multi-Inductor Hybrid Converter1158.3Median and Average Value Analysis1168.3.1Flying Capacitor Voltages1178.3.2Inductor Currents1188.3.3Output Voltage1208.4Chapter Summary120Chapter 9Analysis of Capacitor Voltage Imbalance in Hybrid Converters and Inherently Balanced Operation Using Symmetric Architecture1229.1Introduction1229.2Voltage-Charge Relationship1249.3Application to Multi-Level Converters1269.3.1Inductor Current with Odd Number of Charging Intervals1269.3.2Inductor Current with Even Number of Charging Intervals1279.3.3Balancing Performance of Other Conventional Hybrid Converters with<br>$V_{out} < \frac{V_B}{N}$ 1289.4Multi-phase Symmetric Converter Architecture for Voltage Balancing1309.5Experimental Verifications13110General Analysis of Flying Capacitor Multi-Level Converters For Balancing<br>Issues13410.1Introduction13410.2Analysis of FCML Converters13510.3Discussion on Cod Level FCML Converters with Non-Ideal Timing13810.4Discussion on Odd Level FCML Converters with Non-Ideal Timing13910.5Chapter Summary141Part IVFull Power Delivery Architecture14311.1Introductio                                                                                                                                                         | 7.5       |                                                                              | 111 |