# **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Low-loss and nonlinear silicon-based integrated photonic circuits

#### **Permalink**

https://escholarship.org/uc/item/20d931fr

#### **Author**

Tremblay, Jean-Etienne

#### **Publication Date**

2020

Peer reviewed|Thesis/dissertation

Low-loss and nonlinear silicon-based integrated photonic circuits

by

Jean-Étienne Tremblay

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Ming C. Wu, Chair Professor Eli Yablonovitch Professor Holger Müller

Fall 2020

# Low-loss and nonlinear silicon-based integrated photonic circuits

Copyright 2020 by Jean-Étienne Tremblay

#### Abstract

Low-loss and nonlinear silicon-based integrated photonic circuits

by

Jean-Étienne Tremblay

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ming C. Wu, Chair

Photonic integrated circuits enable tight integration of optical components used as building blocks for much larger optical systems, similarly to electronic integrated circuits. In particular, siliconbased photonics can leverage the yield and scaling technology improvements that also benefit the electronics industry. Moreover, photonic integrated circuits can reduce the power consumption in communication and computation applications, and open the door to new applications in sensing and ranging.

The design of linear and nonlinear passive photonic components is key to the performance improvement of integrated photonics. In the first part of this dissertation, we present a platform for creating on-chip frequency combs using materials with a large third-order nonlinear index. Specifically, using chalcogenide glass waveguides, we produce a frequency comb spanning greater than an octave bandwidth using input optical pulses on the picojoule level. In the second part, we discuss fabrication processes and optical designs to improve the fiber-to-chip coupling loss, which is a limiting factor in large-scale optical switch applications. We present the design of an adiabatic evanescent coupler that is polarization diverse and has a bandwidth greater than 100 nm in the O band. Our design achieves better than 2 dB insertion loss and is compatible with different photonic fabrication processes.

To my parents

# **Contents**

| Co | onten           | ts                                                             | ii  |  |  |  |

|----|-----------------|----------------------------------------------------------------|-----|--|--|--|

| Li | List of Figures |                                                                |     |  |  |  |

| Li | st of           | Γables                                                         | vii |  |  |  |

| 1  | Intr            | oduction                                                       | 1   |  |  |  |

| 2  | On-             | chip optical frequency synthesis                               | 2   |  |  |  |

|    | 2.1             | Optical frequency combs                                        | 2   |  |  |  |

|    | 2.2             | Nonlinear Schrödinger equation                                 | 4   |  |  |  |

|    | 2.3             | Materials                                                      | 5   |  |  |  |

|    | 2.4             | Supercontinuum generation                                      | 6   |  |  |  |

|    | 2.5             | Simulation                                                     | 7   |  |  |  |

|    | 2.6             | Coherence                                                      | 9   |  |  |  |

|    | 2.7             | Efficient octave-spanning supercontinuum in chalcogenide glass | 10  |  |  |  |

| 3  | Fabı            | rication techniques                                            | 18  |  |  |  |

|    | 3.1             | Lithography                                                    | 18  |  |  |  |

|    | 3.2             | Propagation loss                                               | 25  |  |  |  |

|    | 3.3             | Chalcogenide glasses                                           | 26  |  |  |  |

|    | 3.4             | Silicon nitride                                                | 28  |  |  |  |

|    | 3.5             | Oxide cladding                                                 | 30  |  |  |  |

|    | 3.6             | Silicon                                                        | 31  |  |  |  |

| 4  | Adia            | abatic component design                                        | 33  |  |  |  |

|    | 4.1             | Adiabatic theorem and mode evolution                           | 33  |  |  |  |

|    | 4.2             | Simulation of adiabatic devices                                | 35  |  |  |  |

|    | 4.3             | Simple tapers                                                  | 35  |  |  |  |

|    | 4.4             | Bent waveguides                                                | 38  |  |  |  |

|    | 4.5             | TE0-TE1 mode converter                                         | 40  |  |  |  |

|    | 4.6             | Spectral filters                                               | 41  |  |  |  |

|    | 4.7             | Optimization of nonlinear tapers                               | 44  |  |  |  |

| 5  | Edge  | e coupling                                   | 46  |

|----|-------|----------------------------------------------|-----|

|    | 5.1   | Chip-to-chip edge coupling                   | 46  |

|    | 5.2   | Chip-to-fiber edge coupling                  | 50  |

|    | 5.3   | Substrate leakage                            | 54  |

| 6  | Silic | on photonics MEMS switch packaging           | 56  |

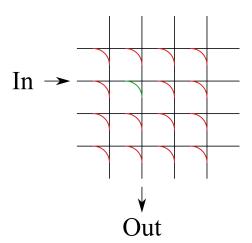

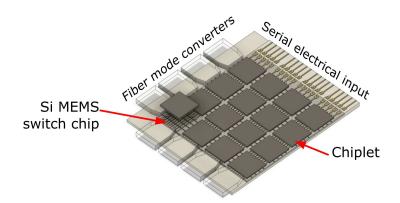

|    | 6.1   | $4 \times 4$ silicon photonics MEMS switch   | 57  |

|    | 6.2   | Electrical packaging                         | 59  |

|    | 6.3   | Optical packaging                            | 61  |

|    | 6.4   | Alignment strategies                         | 63  |

|    | 6.5   | Adhesives                                    | 66  |

| 7  | Evai  | nescent coupling                             | 68  |

|    | 7.1   | Literature review on evanescent couplers     | 69  |

|    | 7.2   | Platforms for intermediate chip              | 70  |

|    | 7.3   | Evanescent coupler design in silicon         | 70  |

|    | 7.4   | Evanescent coupler design in silicon nitride | 72  |

|    | 7.5   | Splitting taper in silicon                   | 73  |

|    | 7.6   | Oxidized taper evanescent coupler            | 77  |

|    | 7.7   | Evanescent coupler alignment                 | 85  |

| 8  | Con   | clusion                                      | 86  |

| Bi | bliog | raphy                                        | 87  |

| A  | Higl  | h voltage parallel MEMS drivers              | 95  |

|    | _     | $4 \times 4$ driver with microcontroller     | 95  |

|    |       | $4 \times 4$ driver with FPGA                | 97  |

|    | A.3   | $16\times 16$ driver with FPGA               | 99  |

| В  | Fico  | nTEC FL300 procedures 1                      | 101 |

|    | B.1   | Components                                   |     |

|    | B.2   | Programs                                     |     |

|    |       | Alignment                                    |     |

# **List of Figures**

| Optical frequency comb representations                                            | 3                              |

|-----------------------------------------------------------------------------------|--------------------------------|

| Self-referenced frequency comb system                                             | 3                              |

|                                                                                   | 4                              |

| 2 <sup>nd</sup> order soliton propagation in a chalcogenide glass waveguide       | 7                              |

| Cross section of the supercontinuum generation device                             | 11                             |

| Chalcogenide glass ring resonator measurement for determining propagation loss    | 12                             |

| Optical frequency domain reflectometry measurement of a 4 cm long waveguide       | 12                             |

| $Ge_{23}Sb_7S_{70}$ material dispersion                                           | 13                             |

| Measured and simulated dispersion of the chalcogenide waveguide for the fundamen- |                                |

| tal modes of the ring resonator                                                   | 14                             |

| Simulated dispersion of the chalcogenide waveguide as a function of width         | 14                             |

| Propagation constant in the moving reference frame                                | 15                             |

| Simulated and measured supercontinuum generation                                  | 16                             |

| Simulated coherence of the generated supercontinuum                               | 16                             |

| Lithography illumination                                                          | 22                             |

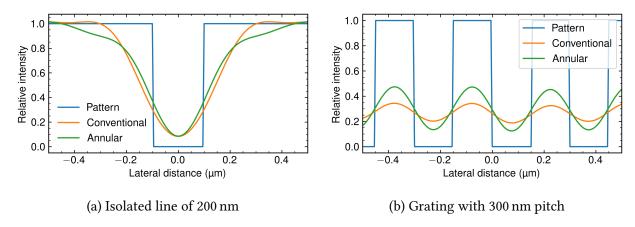

| Comparison of aerial image between conventional and annular illumination          | 23                             |

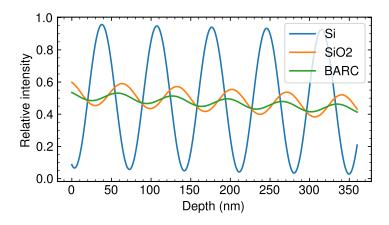

| Standing wave patterns in photoresist                                             | 24                             |

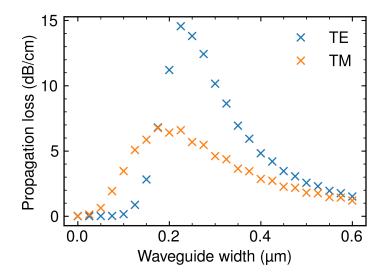

| Propagation loss from sidewall roughness as a function of waveguide width         | 26                             |

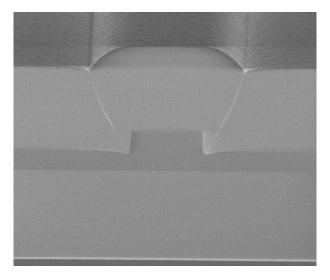

| Chalcogenide waveguide cross section after top cladding deposition                | 28                             |

| Photonic damascene process                                                        | 29                             |

| Photonic damascene stress release                                                 | 29                             |

| Cleaning of silicon grating coupler etch residues in dilute HF                    | 32                             |

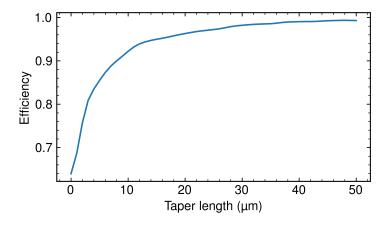

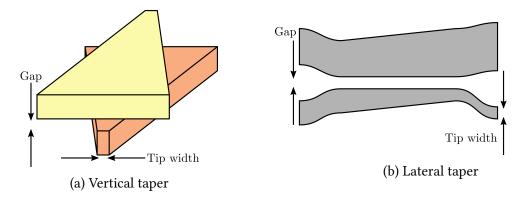

| Wide taper length sweep                                                           | 36                             |

| Narrow taper length sweep                                                         | 37                             |

| Minimum feature size of vertical and lateral double tapers                        | 38                             |

| Refractive index transformation of a waveguide with 10 $\mu m$ bend radius        | 39                             |

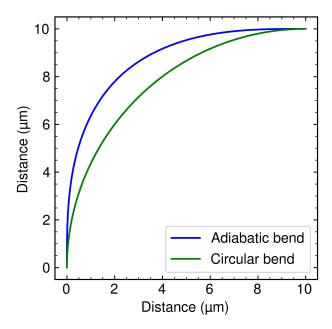

| Waveguide bend shapes                                                             | 40                             |

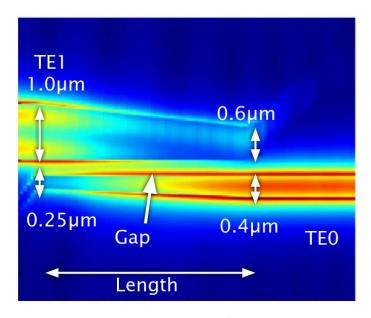

| TE0-TE1 mode converter                                                            | 41                             |

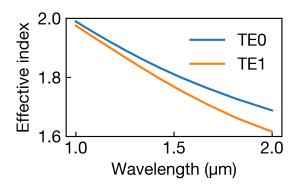

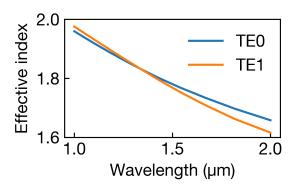

| Modal dispersion between the fundamental and second TE mode in two waveguides     |                                |

| of different widths                                                               | 42                             |

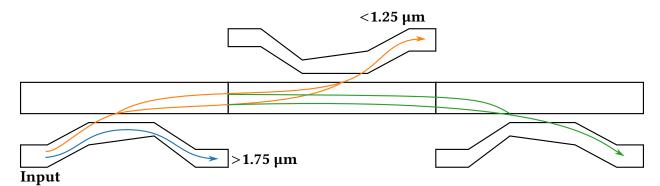

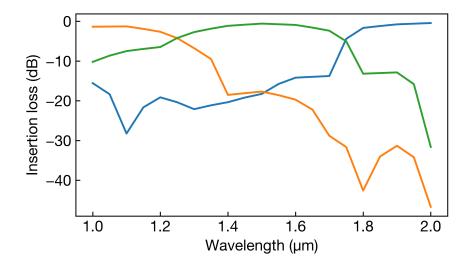

| Adiabatic spectral splitter concept                                               | 42                             |

|                                                                                   | On-chip frequency comb concept |

| 4.9<br>4.10<br>4.11<br>4.12 | Simulation of a $1 \times 3$ spectral splitter                                     | 43<br>45 |

|-----------------------------|------------------------------------------------------------------------------------|----------|

| 5.1                         | Optical chip dicing process                                                        | 47       |

| 5.2                         | Optical facet in $SiO_2$ after trench etching                                      | 48       |

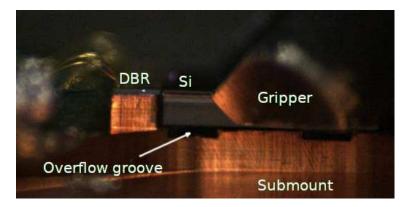

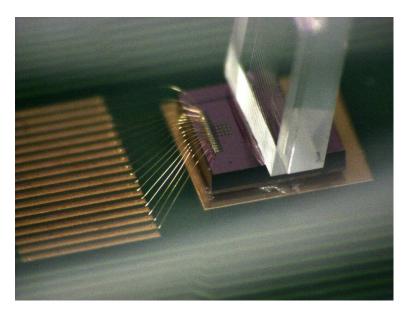

| 5.3                         | Silicon nitride chip edge coupled to an indium phosphide laser chip                | 49       |

| 5.4                         | Mechanical carrier for chip-to-chip alignment                                      | 50       |

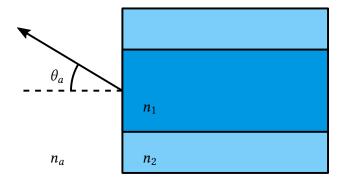

| 5.5                         | Numerical aperture definition                                                      | 51       |

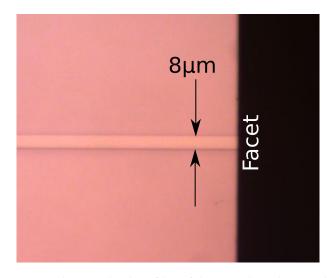

| 5.6                         | Waveguide matched to fiber fabricated with two thin SiN layer                      | 52       |

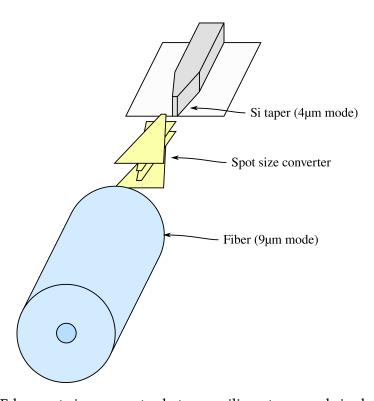

| 5.7                         | Edge spot size converter between silicon taper and single mode fiber               | 52       |

| 5.8                         | Edge spot size converter fabrication process                                       | 53       |

| 5.9                         | Mode size converter array layout                                                   | 53       |

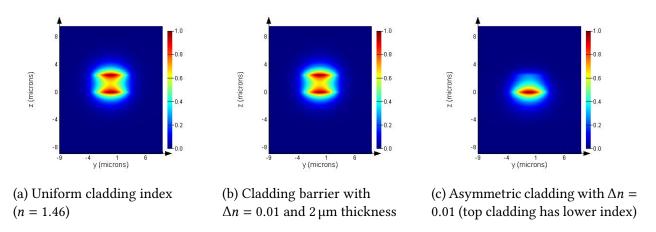

| 5.10                        | Effect of cladding index on mode shape and substrate leakage                       | 55       |

| 6.1                         | Crossbar switch architecture                                                       | E        |

|                             |                                                                                    |          |

| 6.2                         | Epoxy dispensed on 4 × 4 switch                                                    |          |

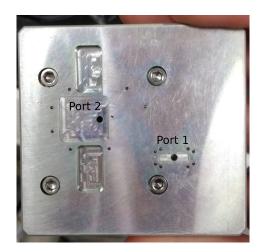

| 6.3                         | Fiber glued to 4 × 4 switch                                                        |          |

| 6.4                         | 4 × 4 switch packaged inside box                                                   |          |

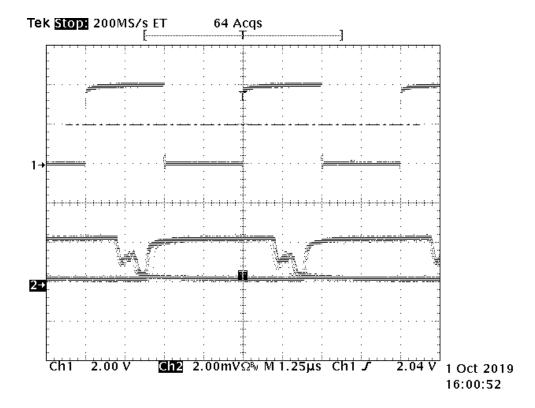

| 6.5                         | 4 × 4 switch optical response time                                                 | 59       |

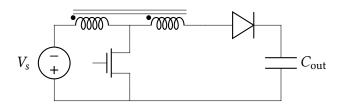

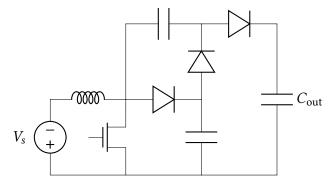

| 6.6                         | Coupled inductor boost converter                                                   | 60       |

| 6.7                         | Voltage doubled boost converter                                                    | 61       |

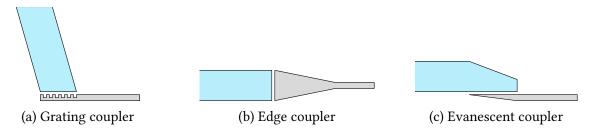

| 6.8                         | Optical coupling methods                                                           | 61       |

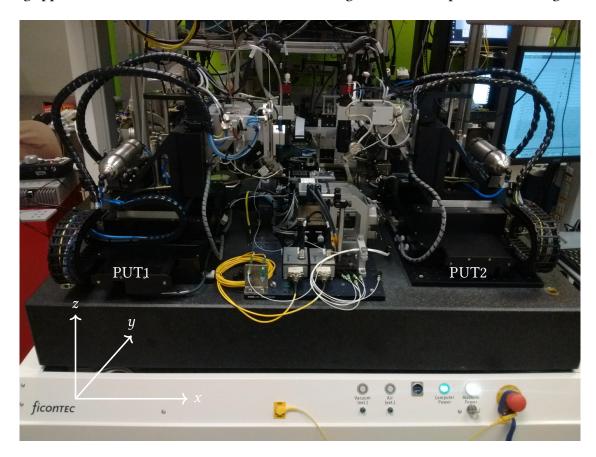

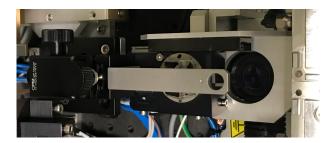

| 6.9                         | FiconTEC FL300                                                                     | 63       |

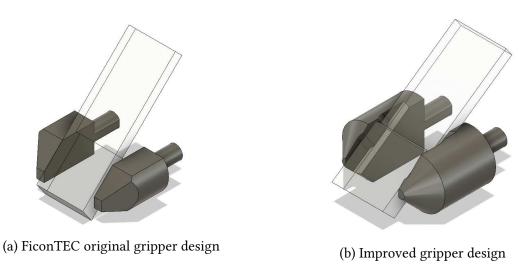

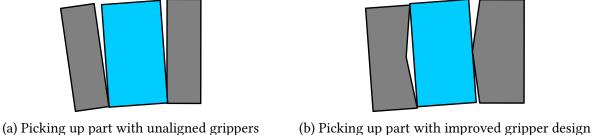

| 6.10                        | Gripper designs                                                                    | 65       |

| 6.11                        | Gripper alignment considerations                                                   | 65       |

| 6.12                        | Fabricated gripper designs                                                         | 66       |

| 7.1                         | Wafer-scale silicon photonics switch concept                                       | 69       |

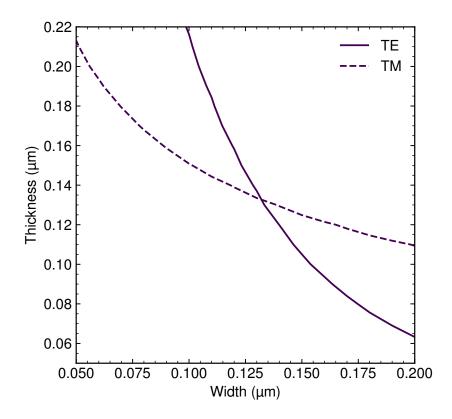

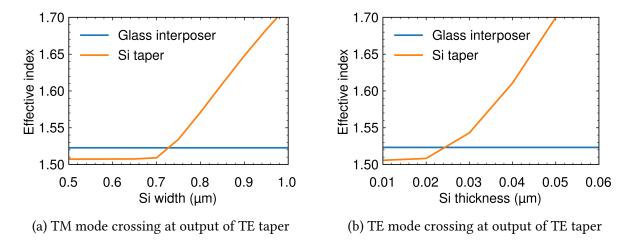

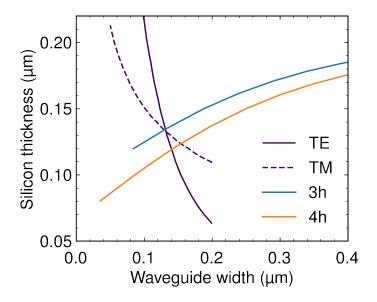

| 7.2                         | Maximum silicon thickness as a function of taper width, for 95 % efficiency        | 71       |

| 7.3                         | 3 step silicon taper design                                                        | 72       |

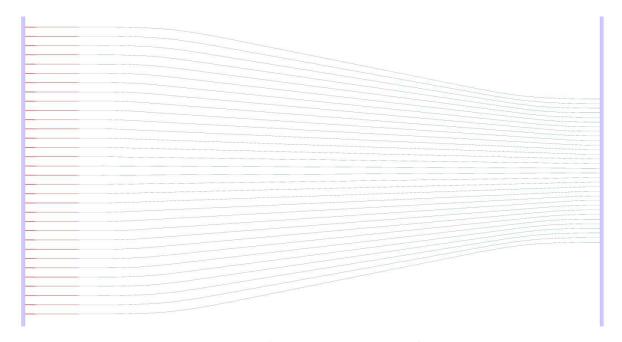

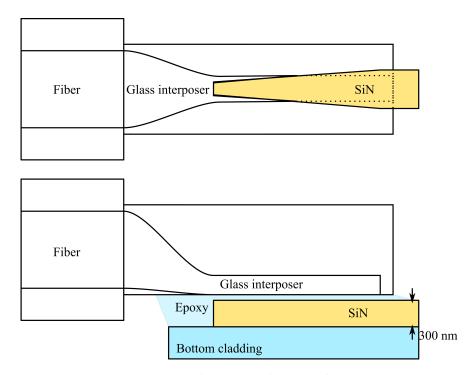

| 7.4                         | Silicon nitride taper design                                                       | 73       |

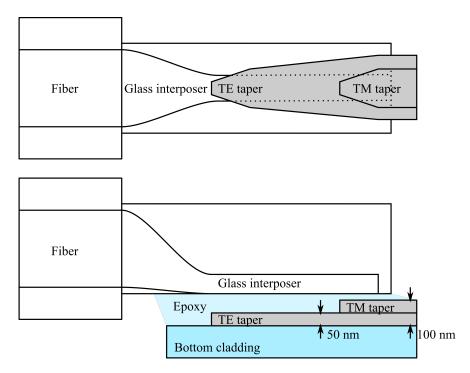

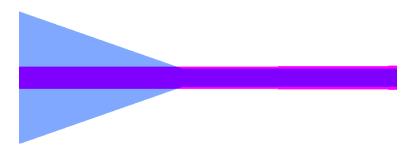

| 7.5                         | Silicon separate TE/TM taper design                                                | 74       |

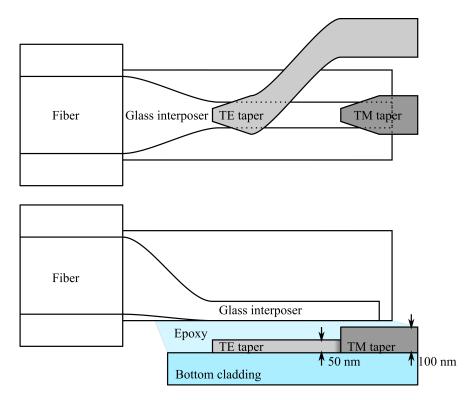

| 7.6                         | TE tip overlap loss for a taper minimum width of 200 nm                            | 75       |

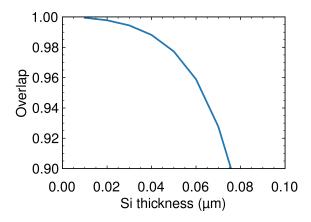

| 7.7                         | Design process of splitting taper evanescent coupler                               | 75       |

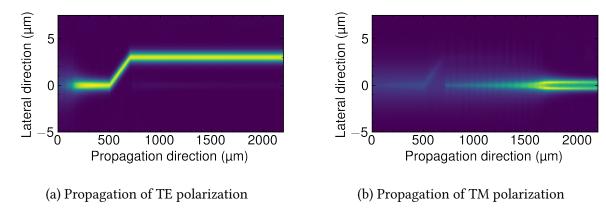

| 7.8                         | E-field propagation along the splitting taper                                      | 76       |

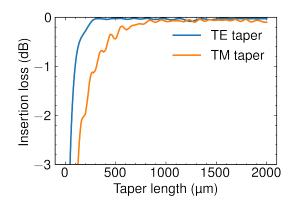

| 7.9                         | Taper length sweep for splitting taper design using eigenmode expansion            | 76       |

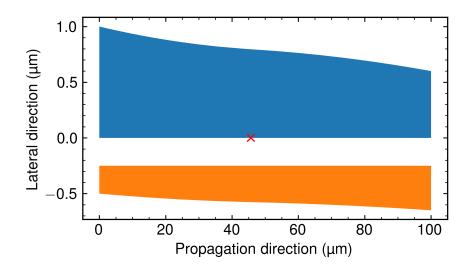

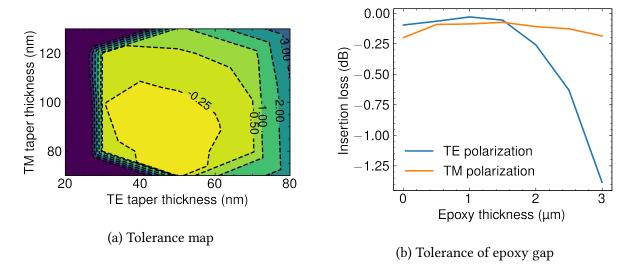

| 7.10                        | Splitting taper evanescent coupler fabrication tolerance                           | 77       |

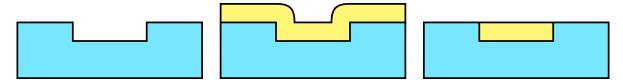

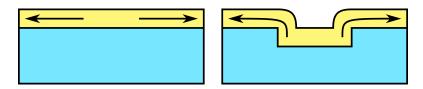

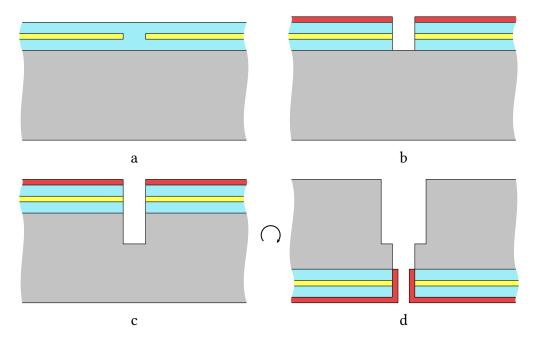

| 7.11                        | Silicon taper oxidation process                                                    | 78       |

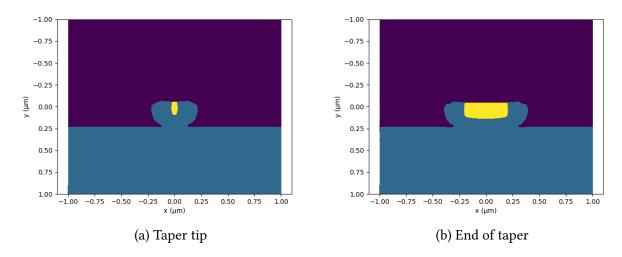

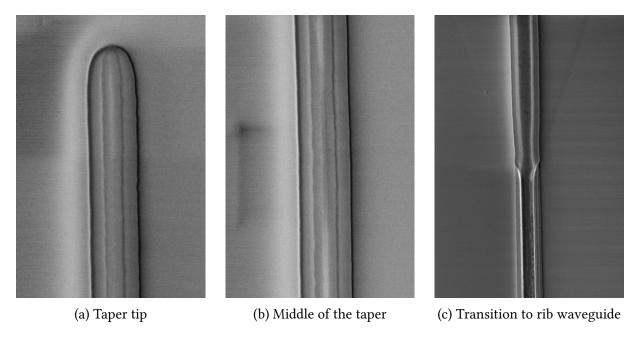

| 7.12                        | Transition between full etch and partial etch region in the oxidized taper process | 79       |

| 7.13                        |                                                                                    | 79       |

| 7.14 | Oxidized silicon taper design space                                                     | 80  |

|------|-----------------------------------------------------------------------------------------|-----|

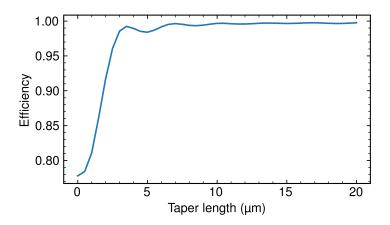

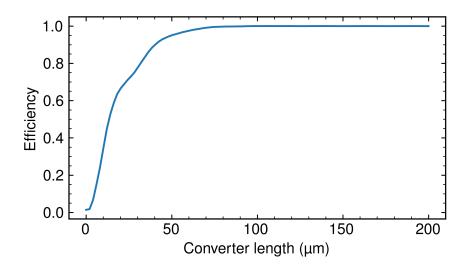

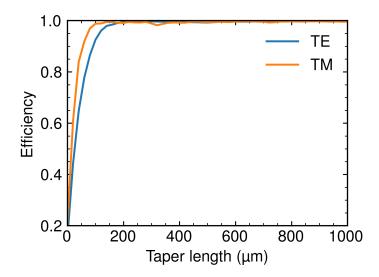

| 7.15 | Taper length sweep of oxidized taper evanescent coupler                                 | 81  |

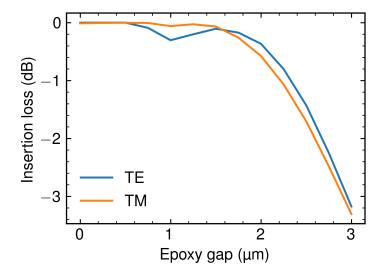

| 7.16 | Tolerance of oxidized tip evanescent to epoxy gap thickness                             | 81  |

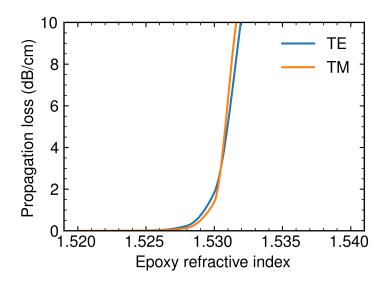

|      | Glass interposer leakage loss as a function of epoxy index                              | 82  |

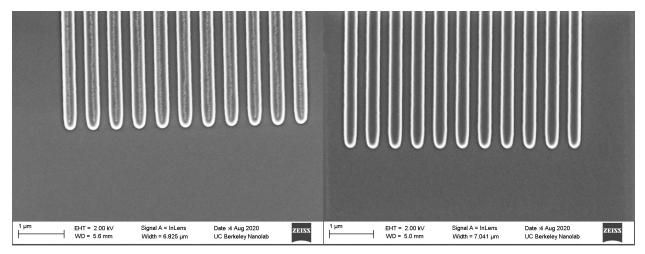

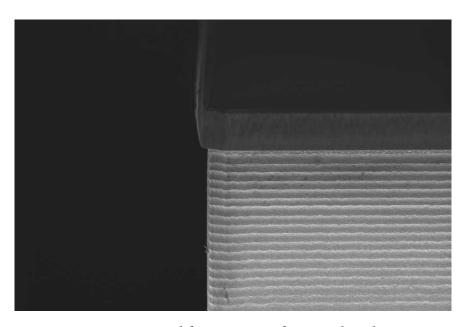

|      | Fabricated oxidized waveguide                                                           | 83  |

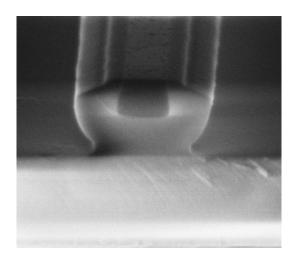

|      | Cross section of oxidized silicon taper                                                 | 83  |

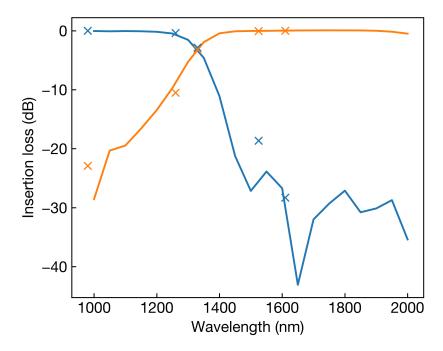

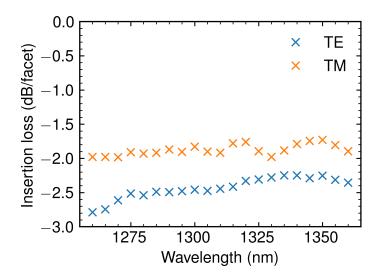

|      | Fiber to silicon insertion loss as a function of wavelength for evanescent coupler with |     |

|      | oxidized tip                                                                            | 84  |

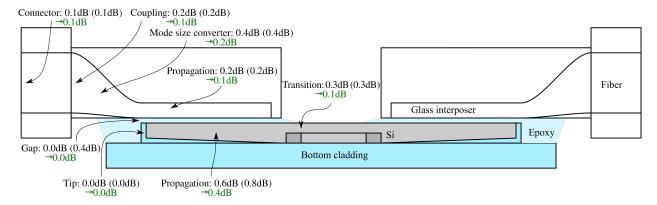

| 7.21 | Potential improvements to evanescent coupler loss                                       | 85  |

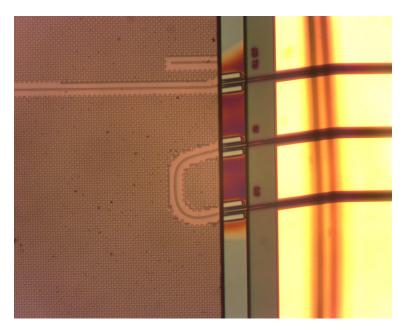

| 7.22 | Interference fringes during evanescent coupler alignment                                | 85  |

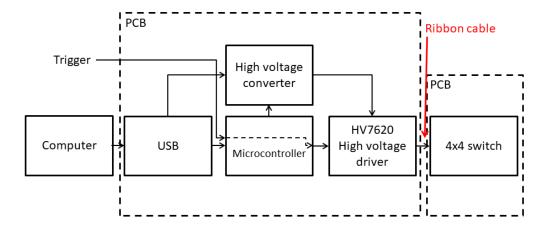

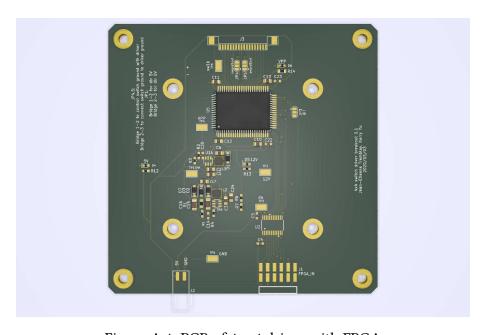

| A.1  | Block schematic of $4 \times 4$ driver with microcontroller                             | 96  |

| A.2  | PCB of $4 \times 4$ driver with microcontroller                                         | 96  |

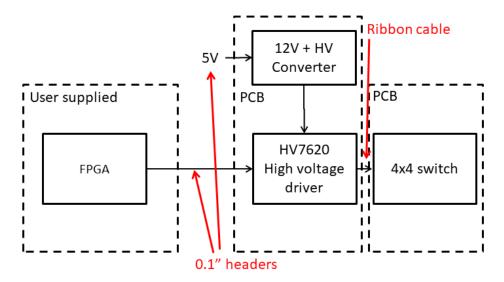

| A.3  | Block schematic of $4 \times 4$ driver with FPGA                                        | 98  |

| A.4  | PCB of $4 \times 4$ driver with FPGA                                                    | 98  |

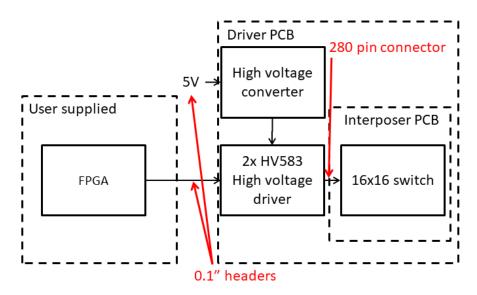

| A.5  | Block schematic of $16 \times 16$ driver with FPGA                                      | 99  |

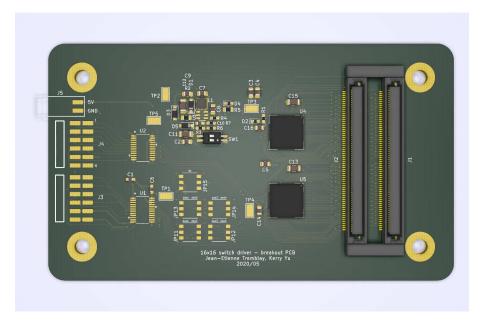

| A.6  | PCB of 16 $\times$ 16 driver with FPGA                                                  | 100 |

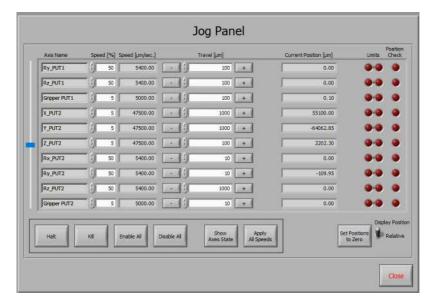

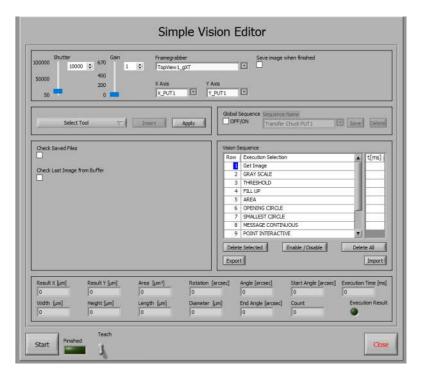

| B.1  | Jog panel                                                                               | 102 |

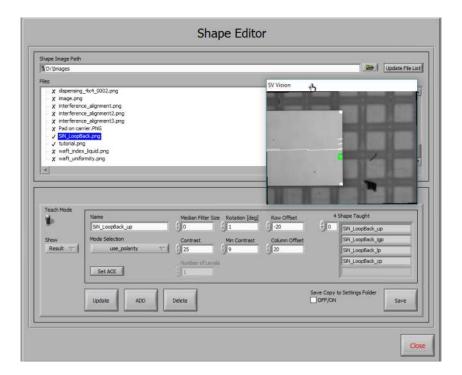

| B.2  | Camera panel                                                                            |     |

| B.3  | Vision algorithm editor                                                                 | 103 |

| B.4  | Shape editor                                                                            | 103 |

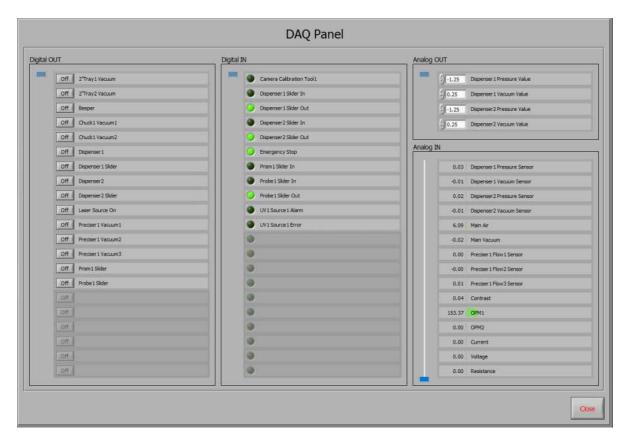

| B.5  | DAQ panel                                                                               | 104 |

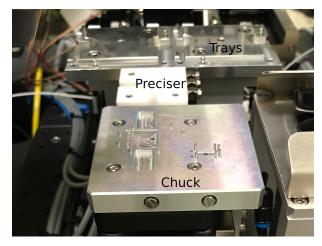

| B.6  | Chucks and mounts                                                                       | 105 |

| B.7  | Bottom view camera calibration tool                                                     | 106 |

# **List of Tables**

| 2.1 | Materials for Kerr nonlinear applications                                                                                                                     | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Bending loss for narrow and wide waveguides of different shapes                                                                                               |    |

| 6.1 | Adhesive selection                                                                                                                                            | 67 |

|     | Breakdown of loss of individual components of separate taper evanescent coupler Breakdown of loss of individual components of oxidized tip evanescent coupler |    |

|     | High voltage driver PCB versions                                                                                                                              |    |

#### Acknowledgments

I would like to thank my great advisor, Professor Ming C. Wu, for all the guidance, support and discussions during my time at Berkeley. It has been a pleasure to work on all these exciting projects with him.

I want to acknowledge all my colleagues in the Wu lab, as well as my colleagues in the Yablonovitch and Chang-Hasnain group for all the extensive discussions and knowledge you shared with me: Andy, Phil, Jodi, Kevin, Jonas, Zain, and many others. A special thanks to Professor Eli Yablonovitch and Professor Holger Müller for serving on my dissertation committee.

None of this research would have been possible without the help of the Marvell Nanolab staff, who work hard to make sure this wonderful facility can run 24h per day, 7 days per week.

A special thanks to my friends who have made this journey manageable: Tristan, Derek and Antoine in California, and Yanick and Alexandre back in Montreal.

Thank you Camille, my wife, for all your encouragements and understanding.

Finally, thank you to my brother Pierre-Antoine, my sister Caroline, and my parents Sylvie and Laval, for your support and love.

# Chapter 1

# Introduction

More than twenty years ago, silicon photonics has emerged as a platform of choice for fabricating integrated photonic circuits. Thanks to the promising compatibility with CMOS fabrication process, massive investment and research has helped leveraging state of the art fabrication facilities to develop photonic devices with great scalability [1, 2].

Even though a huge library of optical components now exists in silicon photonics (e.g. modulators [3, 4] and photodetectors [5]), some devices such as lasers have proven difficult to fabricate in silicon. A promising more recent approach to provide light sources on silicon is through hybrid integration of other materials (such as III-V semiconductors [6]). Another area where silicon photonics can benefit from hybrid integration is nonlinear optics. Indeed, silicon has a large third-order nonlinear index, but suffers from significant two-photon absorption in the ubiquitous telecom bands [7]. In this thesis we explore the use of chalcogenide glass materials for nonlinear applications, in particular supercontinuum generation. Finally, the challenge of coupling light from silicon to other chips or to optical fibers has seen numerous solutions, such as the original inverted nanotaper [8] to more recent vertical grating couplers [9]. In this dissertation, we will also discuss about silicon photonics packaging, from edge coupling to evanescent coupling.

The first part of this thesis covers supercontinuum generation applications. In Chapter 2, we describe how optical frequency combs work, and how they can be generated on-chip. We optimize a chalcogenide glass waveguide for generating a supercontinuum spanning more than one octave, using the nonlinear Schrödinger equation. The details of the fabrication for the nonlinear waveguide are given in Chapter 3, as well as other useful fabrication techniques for nonlinear and low-loss applications. Chapter 4 covers the design of adiabatic components, which have many applications such as mode conversion, spot size converters, and polarization rotation. In particular, we present an adiabatic spectral splitter operating over an octave bandwidth. Chapter 5 discusses the packaging of optical frequency comb waveguides using chip-to-chip edge coupling.

The second part covers packaging designs and techniques for silicon photonics MEMS switch applications. In Chapter 6, we give the details of a fully packaged  $4 \times 4$  optical switch, including automated alignment and electrical control. Finally, Chapter 7 is dedicated to several designs of evanescent couplers, which can be used to package large fiber arrays to wafer-scale silicon photonics switches in a simple process with low insertion loss.

# **Chapter 2**

# On-chip optical frequency synthesis

In this section we first present optical frequency combs and how they can be self-referenced to produce accurate absolute frequencies. We then study the basic theory of nonlinear optical propagation, in particular third-order effects which are present in most materials. Third-order nonlinearities are the source of phenomena such as self-phase modulation, Kerr focusing, four-wave mixing, and supercontinuum generation. We explain how noise affects supercontinuum operation and we show the results of a low power, octave-spanning, coherent supercontinuum generated in a chalcogenide glass waveguide.

## 2.1 Optical frequency combs

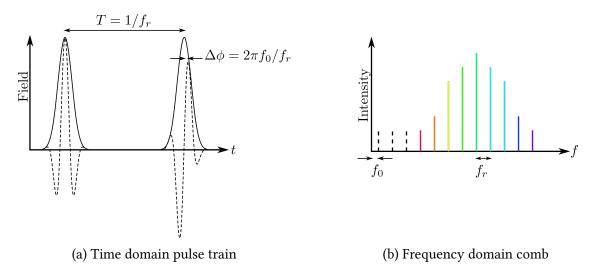

Optical frequency combs are simply an ensemble of optical frequencies with equal spacing  $f_r$  defined by

$$f_n = f_0 + nf_r \tag{2.1}$$

If all the optical frequencies are coherent in phase, the time domain representation of a frequency comb will be a series of short pulse with equal spacing of  $T = 1/f_r$ , the repetition period. The time and frequency domain representation of an optical frequency comb are shown in Figure 2.1. It should be noted that the frequency comb lines near 0 Hz do not necessarily physically exist in the optical frequency comb spectrum, and the minimum time domain pulse width is related to the optical bandwidth of the frequency comb spectrum. The frequency offset of the frequency comb,  $f_0$ , is related in the time domain to the carrier-envelope phase offset that is picked up in between each pulse by

$$\Delta \phi = 2\pi \frac{f_0}{f_r} \tag{2.2}$$

While each comb line frequency is in the optical domain (> 100 THz), the repetition rate  $f_r$  is typically in the microwave domain. The repetition rate can then easily be measured by reading the pulse train signal from a photodiode.

In some cases, it is required to precisely know the absolute frequency of each comb line, or to know the exact phase relationship between each pulse. Such applications include short (single-

Figure 2.1: Optical frequency comb representations

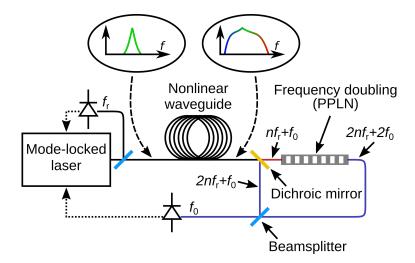

cycle) pulse generation, high accuracy spectroscopy, or the use of optical frequency standards to generate accurate clocks. The offset frequency  $f_0$  cannot be directly measured like the repetition rate since it does not physically exist in the optical signal, however it can be measured through the help of a nonlinear interferometer [10, 11], which then creates a self-referenced frequency comb. This is represented in Figure 2.2.

Figure 2.2: Self-referenced frequency comb system

In its simplest form, the self-referenced frequency comb is initiated from a mode-locked laser, which produces a series of optical pulses but with limited bandwidth. The optical bandwidth of the pulses is greatly increased in a nonlinear waveguide through a process known as *supercontinuum generation*, to create a frequency comb that has more than one octave bandwidth (we will now use the terms supercontinuum and frequency comb interchangeably). The supercontinuum

now contains the frequencies  $f_0 + nf_r$  and  $f_0 + 2nf_r$ , which we refer to as the f and 2f comb lines. We then frequency double the f lines and mix the result with the 2f line to obtain the following

$$f_0 = 2(f_0 + nf_r) - (f_0 + 2nf_r) \tag{2.3}$$

It should be noted that other schemes do exist, for example 2f - 3f [12] when the frequency comb is of limited bandwidth, or f - 3f [13] when a suitable material for frequency doubling is not available. When the optical power in the 2f or 3f line is not sufficient for second or third-harmonic generation, techniques such as amplification [14] or transfer lasers [15] can be used to increase the available signal.

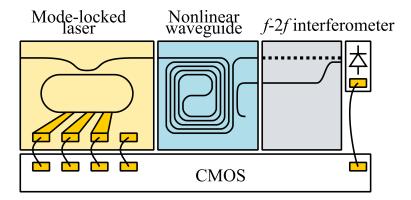

In this work, we explore the use of chalcogenide glass to fabricate integrated waveguides for on-chip supercontinuum generation. This nonlinear waveguide chip is meant to be integrated in a larger self-referenced frequency comb system as shown in Figure 2.3.

Figure 2.3: On-chip frequency comb concept

In the on-chip frequency comb device, the mode-locked laser is fabricated on indium phosphide [16], the f - 2f interferometer is fabricated on lithium niobate [17], and the CMOS control electronics are fabricated using a conventional commercial process.

## 2.2 Nonlinear Schrödinger equation

Typically, optical nonlinearities are excited using pulsed light to achieved great optical intensities without requiring significant average power. The principal way of describing the third-order nonlinear propagation of light is by considering the slowly-varying envelope approximation to derive what is known as the nonlinear Schrödinger equation [18]:

$$\frac{\partial A}{\partial z} = -\frac{\alpha}{2}A - i\frac{\beta_2}{2}\frac{\partial^2 A}{\partial T^2} + i\gamma\left(|A|^2 A + \frac{i}{\omega_0}\frac{\partial}{\partial T}(|A|^2 A) - T_R A\frac{\partial|A|^2}{\partial T}\right)$$

(2.4)

where A(z, T) is the envelope of the propagating pulse,  $\alpha$  is the linear propagation loss,  $\beta_2$  is the dispersion,  $\gamma$  is the nonlinearity coefficient,  $\omega_0$  the carrier frequency and  $T_R$  the slope of the

Raman gain. A will typically be a complex number to account for phase. The Fourier transform in time of A represents the spectral content of the pulse, shifted by the optical carrier frequency. The left side of the equation represents the evolution of the pulse as it propagates in the z direction. The time T is centered around the pulse through a change of variables removing the group delay.

$$T = t - \frac{z}{v_q} \tag{2.5}$$

The right side is divided in linear terms and nonlinear terms. The linear terms accounts for loss and dispersion. If desired, the dispersion can be expanded in more terms, or treated in the frequency domain to account for more complicated dispersion relations.

The nonlinear terms are multiplied by  $\gamma$ , the nonlinearity coefficient. It is calculated from

$$\gamma = \frac{n_2 \omega_0}{c A_{\text{eff}}} = \frac{2\pi n_2}{\lambda A_{\text{eff}}} \tag{2.6}$$

where  $n_2$  is the nonlinear index,  $w_0$  the optical carrier frequency and  $A_{\text{eff}}$  is the effective nonlinear mode area. The first nonlinear term in the nonlinear Schrödinger equation represents the nonlinear phase shift (Kerr effect). The second term comes from the inclusion of the first derivative in the slowly varying envelope approximation and is responsible for self-steepening of the pulse. The last term accounts for the nonlinear Raman response ( $T_R$  is the slope of the Raman gain) and is responsible for self-frequency shift of the pulse.

It should be noted that, in the slowly varying approximation, the high frequency terms accounting for third harmonic generation were dropped, since they are usually not of interest for supercontinuum generation. Nonetheless, the nonlinear Schrödinger equation can account for many third order nonlinear effects, such as the Kerr effect, four-wave mixing, self-phase modulation, modulation instability, and so-on.

#### 2.3 Materials

The main characteristic used to compare materials for Kerr nonlinear applications is the nonlinear index  $n_2$ . However, many materials also have two-photon absorption  $\beta_{TPA}$  which is a 3rd order nonlinear effect as well. The ratio of the nonlinear index and nonlinear loss is included in a figure of merit which is commonly cited in the literature:

$$FOM_{\text{TPA}} = \frac{n_2}{\lambda \beta_{\text{TPA}}} \tag{2.7}$$

A figure of merit larger than unity is advantageous for supercontinuum generation. For silicon photonics, common nonlinear material candidates are silicon and silicon nitride ( $Si_3N_4$ ). Another class of promising materials are chalcogenide glasses [19]. In particular, we are interested in the specific composition  $Ge_{23}Sb_7S_{70}$ . These three materials are compared in Table 2.1. We also include  $SiO_2$  as a reference, since it is well studied in fiber systems. The table also summarizes other

| Material                                                  | Loss<br>(dB/cm) | Nonlin. loss<br>(cm/GW) | Index | $n_2 (10^{-20} \mathrm{m}^2/\mathrm{W})$ | $A_{\rm eff}$ ( $\mu { m m}^2$ ) | γ<br>(1/Wm) | FOM  |

|-----------------------------------------------------------|-----------------|-------------------------|-------|------------------------------------------|----------------------------------|-------------|------|

| Ge <sub>23</sub> Sb <sub>7</sub> S <sub>70</sub> [20, 21] | 0.5             | 0.01                    | 2.2   | 93                                       | 1                                | 7           | 6    |

| $Si_3N_4$ [22]                                            | 0.1             | ~ 0                     | 2.0   | 24                                       | 1                                | 1           | ≫ 1  |

| Silicon [23]                                              | 1.0             | 0.8                     | 3.47  | 400                                      | 0.1                              | 160         | 0.32 |

| SiO <sub>2</sub> [18]                                     | 0.01            | ~ 0                     | 1.45  | 2.7                                      | 10                               | 0.01        | ≫ 1  |

Table 2.1: Materials for Kerr nonlinear applications

properties such as typical waveguide loss, refractive index, waveguide mode area and typical nonlinear parameter  $\gamma$ .

Even though silicon has a very large nonlinear index, the large two-photon absorption prohibits its use for supercontinuum generation in the C band. It has however successfully been used in the mid-infrared [24]. Silicon nitride and chalcogenide glasses are both good candidates for onchip supercontinuum generation. However, the larger nonlinear index of Ge<sub>23</sub>Sb<sub>7</sub>S<sub>70</sub> means that the nonlinear interaction occurs on a shorter length and the device footprint will be minimized.

## 2.4 Supercontinuum generation

A *supercontinuum* is generally defined as beam of light which underwent several nonlinear processes to get massively spectrally broadened. One example of supercontinuum generation would be by pumping a photonic crystal fiber with the short pulses from a mode-locked laser. The spectral broadening can be on the order of one octave or more. Supercontinuum sources can be used for applications requiring broadband light, such as optical coherence tomography, imaging, and optical communication.

A related concept is the *optical frequency comb*. A frequency comb contains several, evenly spaced frequencies which have a well-defined phase relationship. This corresponds to a regular pulse train in the time domain. A frequency comb can be nonlinearly broadened to become a supercontinuum. On the other hand, a supercontinuum which consists of discrete frequency lines could be called a frequency comb.

The formation of supercontinuum can be understood by studying the nonlinear Schrödinger equation. If we simply include the dispersion and first nonlinear term in (2.4), and assuming  $\beta_2 < 0$ , we get solutions of the form

$$A = \sqrt{\frac{|\beta_2|}{T_0^2 \gamma}} \operatorname{sech}\left(\frac{T}{T_0}\right) \exp\left(i\frac{|\beta_2|}{2T_0^2}z\right)$$

(2.8)

This solution is called the fundamental *soliton*. The literature defines the dispersion and non-linear characteristic lengths as following:

$$L_{\rm D} = \frac{T_0^2}{|\beta_2|} \tag{2.9}$$

$$L_{\rm NL} = \frac{1}{\gamma P_0} \tag{2.10}$$

where  $P_0$  is the pulse peak power. For the fundamental soliton, we notice that  $P_0 = |\beta_2|/T_0^2 \gamma$  and hence  $L_D = L_{\rm NL}$ . The soliton propagates unperturbed, or in other words the nonlinearity and dispersion interact on the same length scale.

There also exists higher order solitons which are solutions of the nonlinear Schrödinger equation. These solutions are characterized by the soliton number N:

$$N^2 = \frac{L_{\rm D}}{L_{\rm NL}} \tag{2.11}$$

Instead of propagating unperturbed like the fundamental soliton, the higher order solitons change shape periodically with a soliton period

$$z_0 = \frac{\pi}{2} L_{\rm D} \tag{2.12}$$

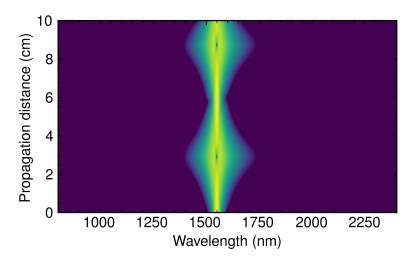

which is independent of the soliton order. The simulated propagation of a soliton with N=2 in a chalcogenide glass waveguide is shown in Figure 2.4.

Figure 2.4:  $2^{\rm nd}$  order soliton propagation in a chalcogenide glass waveguide. The soliton period is about 6 cm.

### 2.5 Simulation

The simulation of supercontinuum generation relies on the discretization of equation (2.4). The field amplitude A is propagated in discrete z steps. At each step, two contributions are calculated.

The linear term coming from loss and dispersion is calculated in the Fourier domain at each z step. This enabled direct multiplication of  $\hat{A}(\omega) = \mathcal{F}(A)$  by the dispersion  $\beta(\omega)$ . The result is converted back in the time domain with an inverse Fourier transform. In other words, we replace the dispersion term in (2.4) with the more general

$$-\frac{\beta_2}{2}\frac{\partial^2 A}{\partial T^2} \to \mathcal{F}^{-1}\left(\beta(\omega)\hat{A}(\omega)\right) \tag{2.13}$$

assuming  $\beta(\omega)$  is expanded as

$$\beta(\omega) = \frac{\beta_2}{2} (\omega - \omega_0)^2 + \frac{\beta_3}{6} (\omega - \omega_0)^3 + \cdots$$

(2.14)

The group delay per unit length  $\frac{1}{v_g} = \beta_1$  is taken care of by the transformation of variable  $T = t - \frac{z}{v_g}$ . This will conveniently keep the pulse centered in the simulation window during propagation.

The nonlinear terms are computed directly in the time domain. The time derivatives can be calculated either by finite difference, or by multiplying by  $\omega$  in the Fourier domain. There are several algorithms available for the z stepping. If we split the linear  $(\hat{D})$  and nonlinear part  $(\hat{N})$  of the nonlinear Schrödinger equation:

$$\frac{\partial A}{\partial z} = (\hat{D} + \hat{N})A \tag{2.15}$$

then the solution is

$$A(z+h) = \exp h(\hat{D} + \hat{N})A \tag{2.16}$$

Since  $\hat{D}$  and  $\hat{N}$  do not commute, the following would only be an approximation to the solution:

$$A(z+h) \approx \exp(h\hat{D}) \exp(h\hat{N}(z)) A(z)$$

(2.17)

As mentioned previously, the linear (dispersion) operator is evaluated in the Fourier domain and we can write this simple method more explicitly:

$$A(z+h) \approx \mathcal{F}^{-1} \exp(h\hat{D}(i\omega)) \mathcal{F} \exp(h\hat{N}(z)) A(z)$$

(2.18)

Moreover, since  $\hat{N}$  is a function of z, this method can only be first order accurate. Several other schemes with higher accuracy have been developed. In particular, in this thesis we use the  $4^{\text{th}}$  order Runge-Kutta method in the interaction picture [25], which has  $4^{\text{th}}$  order accuracy while using a minimal number of Fourier transforms.

#### 2.6 Coherence

During supercontinuum generation, not all nonlinear processes keep a known and predictable phase relationship between the frequencies that constitute the pulses. In particular, certain phenomena such as modulation instability amplify noise [26, 27].

The specific derivation of modulation instability gain can be found in [18]. Here, we are interested in understanding under which condition the coherence of the supercontinuum is preserved.

The first condition for modulation instability is anomalous dispersion ( $\beta_2$  < 0), where the peak modulation instability gain is

$$g_{\rm MI} = 2\gamma P_0 \tag{2.19}$$

with  $P_0$  the pulse peak power. The other condition for modulation instability to occur is that its gain is larger than the linear propagation loss  $\alpha$ . Usually it is desirable to have waveguides with low propagation loss for maximum efficiency, so the modulation instability will not be prevented by the propagation loss.

On the other hand, the supercontinuum broadening accelerates around the soliton fission length  $z_{\rm opt}$ , which is the approximate optimal length of the supercontinuum generating waveguide. Indeed, during the periodic soliton beating, there is a point where the pulse length is minimal and the bandwidth is maximal. This length is empirically related to the dispersion length by [28]

$$z_{

m opt} pprox rac{L_{

m D}}{N} pprox \sqrt{rac{T_0^2}{|eta_2|\gamma P_0}}$$

(2.20)

In Figure 2.4, this corresponds to 3 cm of propagation where the pulse bandwidth is maximal.

From this, we can understand that shorter pulses require less peak power to generate a large bandwidth supercontinuum with the same propagation length. This will lead to smaller modulation instability gain and increased coherence.

We can compare the soliton fission length and the modulation instability characteristic length, which is proportional to the inverse of the modulation instability gain.

$$L_{\rm MI} \propto \frac{1}{\gamma P_0}$$

(2.21)

which corresponds to  $L_{\rm NL}$  defined previously. In practice, we can estimate  $L_{\rm MI} \approx 16 L_{\rm NL}$  [28] which corresponds to sufficient gain to amplify the quantum shot noise level to the typical pulse power level.

On the other hand, since the soliton fission length goes as  $L_{\rm D}/N$ , a high degree of coherence is ensured when

$$16L_{\rm NL} > \frac{L_{\rm D}}{N} \tag{2.22}$$

or N < 16. In other words, a low soliton number is required for greater coherence. For a given average power, reducing the pulse length yields a lower soliton number for the pulse, which once again confirms the intuition that a supercontinuum created from shorter pulses will be more coherent.

We can use these conditions to compare materials having a large nonlinear figure of merit such as GeSbS and SiN defined in Table 2.1. For a given (low) soliton number, we want to minimize the total propagation loss:

$$FOM_{\text{lin}} = \alpha z_{\text{opt}} \sim \alpha L_{\text{NL}} = \frac{\alpha}{\gamma P_0}$$

(2.23)

This is not a fundamental material property, but it can be useful to compare two waveguide platforms under the same input pulse conditions, when the two-photon absorption figure of merit comparison is not meaningful. For example, with  $P_0 = 100$  W, assuming the waveguide dispersion is designed correctly, for GeSbS the linear figure of merit is 0.07, and for silicon nitride it is 0.1. In this case, in addition to having a smaller footprint compared to silicon nitride, the chalcogenide glass waveguide will produce a slightly more efficient supercontinuum given the same input pulse.

In simulation, the coherence properties of the supercontinuum are modelled by adding quantum limited noise with energy variance of one half photon per time bin and random phase, which corresponds to adding one half photon per mode in the frequency domain [27].

$$\sigma_{\delta A}^2 = \frac{h\nu}{2\delta t} \tag{2.24}$$

When converted to a spectral power density, this noise corresponds to the classical shot noise level,

$$S_{\delta P} = \bar{P}h\nu \tag{2.25}$$

which means that the quantum noise simulates the general case of shot noise.

As the pulse propagates in the simulation, the noise will affect the pulse via nonlinear interactions. The coherence of the output pulse is then evaluated with the modulus of the first-order coherence [26]:

$$\left|g_{12}^{(1)}(\lambda)\right| = \left|\frac{\left\langle E_1^*(\lambda)E_2(\lambda)\right\rangle}{\sqrt{\left\langle \left|E_1(\lambda)\right|^2\right\rangle \left\langle \left|E_2(\lambda)\right|^2\right\rangle}}\right| \tag{2.26}$$

The coherence is greater when  $\left|g_{12}^{(1)}\right|$  is closer to 1, and the supercontinuum is incoherent when  $\left|g_{12}^{(1)}\right|=0$ .

# 2.7 Efficient octave-spanning supercontinuum in chalcogenide glass

In this section we summarize the design of chalcogenide glass waveguides for supercontinuum generation, which is described in details in [29].

The devices are fabricated using the chalcogenide glass fabrication process described in Chapter 3. Additionally, in order to couple light efficiently without inducing damage to the facet, we

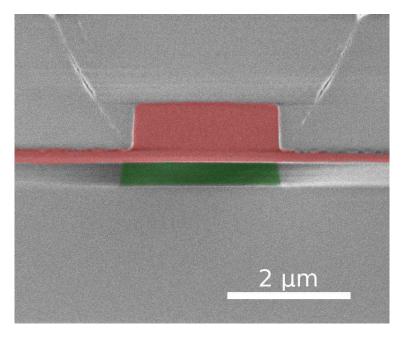

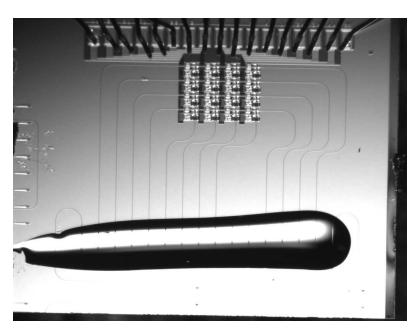

use silicon nitride spot size converters on the edge of the chip [30]. We have successfully fabricated the silicon nitride spot size converters in both the photonic damascene process, as well as using a regular deposition and etch process with plasma-enhanced chemical vapor deposition (PECVD) silicon nitride. A cross section of the device is shown in Figure 2.5. The top cladding is deposited using PECVD, which shows typical voids starting from the inside corners of the rib waveguide.

Figure 2.5: Cross section of the supercontinuum generation device. Red: chalcogenide glass waveguide. Green: silicon nitride layer for edge coupling.

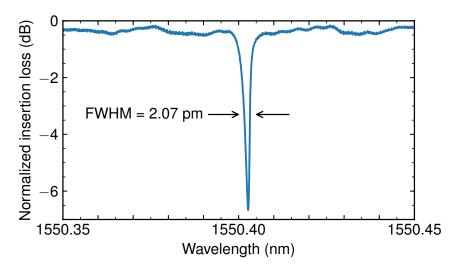

The propagation loss of this device is 0.56 dB/cm, measured using both ring resonators (Figure 2.6) and optical frequency domain reflectometry (Figure 2.7). In the case of the ring resonator measurement, the propagation loss is related to the quality factor with the following [31]:

$$\alpha_{\rm lin} = \frac{2\pi n_g}{Q_{\rm int}\lambda_0} \tag{2.27}$$

The linear propagation loss is related to the dB propagation loss by

$$\alpha_{\rm dB} = 10 \log_{10}(e) \alpha_{\rm lin} \approx 4.34 \alpha_{\rm lin} \tag{2.28}$$

The ring resonance gives us the *loaded* quality factor

$$Q_{\text{loaded}} = \frac{\lambda_0}{\text{FWHM}} \tag{2.29}$$

from which we can determine the *intrinsic* quality factor with [31]

$$Q_{\rm int} = \frac{2Q_{\rm loaded}}{1 + \sqrt{ER^{-1}}} \tag{2.30}$$

where ER is the extinction ratio of the resonance.

Figure 2.6: Chalcogenide glass ring resonator measurement for determining propagation loss

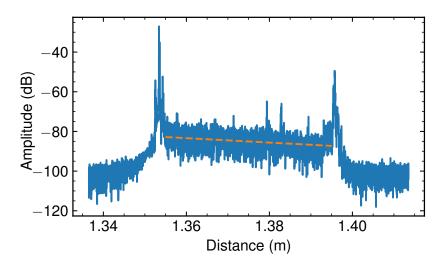

In the case of optical frequency domain measurement, the instrument measures the backscattered signal from the waveguide as a function of distance. Since the emitted backscattered signal is proportional to the attenuated signal, and undergoes the same loss on the way back, the slope of the OFDR signal is twice the propagation loss in the waveguide.

Figure 2.7: Optical frequency domain reflectometry measurement of a 4 cm long waveguide. The slope is related to the propagation loss.

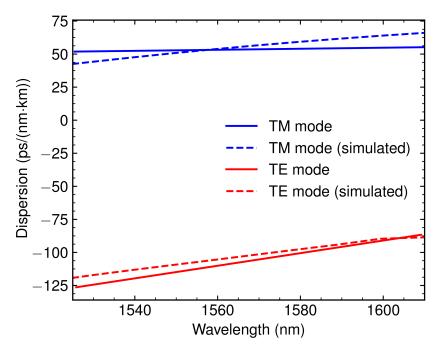

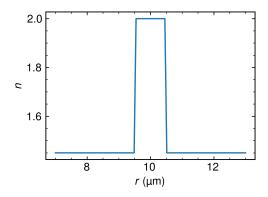

An important parameter to engineer is the waveguide dispersion. We use the material refractive index from [20] which is reproduced in Figure 2.8. We confirm it is adequate to model dispersion by comparing with experimental data from ring resonators. The ring resonators cross section (e.g. Figure 2.5) is simulated in Lumerical MODE and the dispersion is extracted.

Figure 2.8: Ge<sub>23</sub> Sb<sub>7</sub> S<sub>70</sub> material dispersion.

Then, the experimental dispersion is determined by the derivative of the group index  $n_g$ , which is found from the ring resonator mode spacing:

$$n_g = \frac{\lambda^2}{\Delta \lambda L} \tag{2.31}$$

where  $L=2\pi R$  is the ring resonator circumference. We calculate one group index per free spectral range then use a low order polynomial fit to reduce the noise. Then, the dispersion is given by the derivative of the group index. The simulated and experimental dispersions are shown on Figure 2.9 for the fundamental quasi-TE and quasi-TM modes in the ring resonator, with good agreement for both modes.

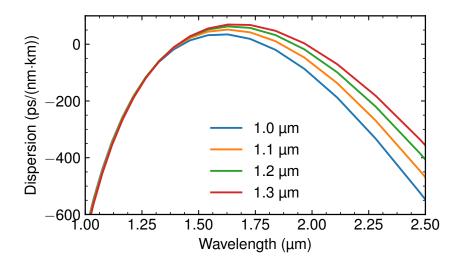

This agreement of the dispersion gives confidence to use the dispersion model over the whole wavelength range. The dispersion from 1  $\mu$ m to 3  $\mu$ m for different waveguide widths is shown in Figure 2.10. The peak dispersion is located around 1.6  $\mu$ m. We notice that changing the waveguide width mostly influences the red side dispersion.

One important feature of supercontinuum is the presence of *dispersive waves*. These are specific wavelength peaks in the supercontinuum which are generated from the resonance between the solitons and other wavelengths. Dispersive waves are useful in a context of self-referenced frequency combs where we would like to concentrate the supercontinuum energy at f and 2f.

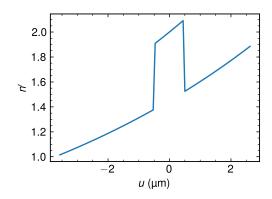

The dispersive wave location cannot be easily determined from the dispersion curve itself (the second derivative of the propagation constant), since it requires a phase matching condition. For

Figure 2.9: Measured and simulated dispersion of the chalcogenide waveguide for the fundamental modes of the ring resonator

Figure 2.10: Simulated dispersion of the chalcogenide waveguide as a function of width

low soliton numbers, the dispersive wave is located at the following resonance condition [32]:

$$\beta(\omega_{\rm R}) - \beta_1(\omega_{\rm R}) = \frac{\gamma(\omega_{\rm S})P_{\rm S}}{2} \tag{2.32}$$

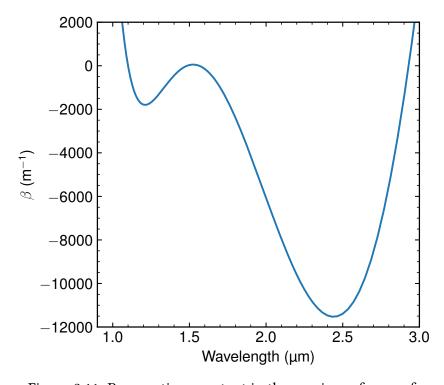

The left hand side represents the propagation constant in the moving frame. In this case, (with a peak power of 77 W in the waveguide) the right hand side equals to  $165\,\mathrm{m}^{-1}$ . In Figure 2.11, which shows the propagation constant for a  $1.2\,\mu\mathrm{m}$  wide waveguide, we can find the dispersive wave location by finding the points where the propagation constant equals the right hand side. In this example, this happens at wavelengths of  $1.1\,\mu\mathrm{m}$  and  $2.9\,\mu\mathrm{m}$ . It should be noted that, for large soliton numbers, there will be a blue shift of the dispersive wave, and a more detailed analysis is required to get the precise dispersive wave location [32].

Figure 2.11: Propagation constant in the moving reference frame

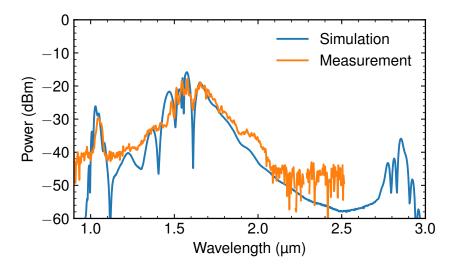

In the supercontinuum simulation on Figure 2.12, the dispersive waves appear near the predicted wavelengths of  $1.1\,\mu m$  and  $2.9\,\mu m$ . The supercontinuum was measured experimentally in the fabricated chalcogenide waveguides. The pump laser is a Calmar FPL-01TP femtosecond fiber laser. The pulse width is 240 fs, measured with a Femtochrome FR-103HS autocorrelator. The repetition rate is 25 MHz. Accounting for the 7 dB insertion loss between the fiber and the waveguide, the peak power inside the waveguide is calculated to be 77 W, and the pulse energy is 26 pJ. For these parameters, we estimate the soliton number to be N=11. The waveguide length is 2 cm, which is close to the calculated optimum length  $z_{\rm opt}=2.05\,{\rm cm}$ . The supercontinuum

spectrum is measured using an OceanOptics NIRQUEST512-2.5 and shown on Figure 2.12. The blue dispersive wave as well as the general shape near the pump wavelength are closely matched experimentally. Unfortunately, the spectrometer range could not extend far enough to detect the red dispersive wave.

Figure 2.12: Simulated and measured supercontinuum generation

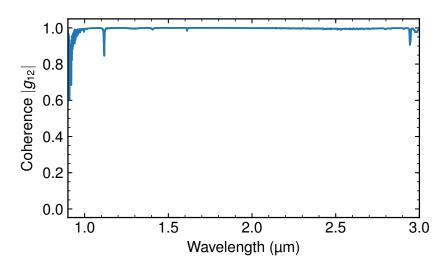

Figure 2.13: Simulated coherence of the generated supercontinuum, showing near-unity from  $1.0\,\mu m$  to  $3.0\,\mu m$

Since the soliton number is estimated to be less than 16, we expect the supercontinuum coherence to be good (close to unity). To simulate the coherence, we simulate multiple propagations

of the same pulse with random noise and average the result according to equation (2.26). The results are plotted on Figure 2.13. Indeed, the simulation predicts near-unity coherent from 1.0  $\mu$ m to beyond 3.0  $\mu$ m.

The supercontinuum coherence is a more difficult parameter to measure. It can be confirmed indirectly, by measuring the f-2f beat note in a nonlinear interferometer. However, a more direct measurement of the pulse to pulse coherence can be done using a regular interferometer and an optical spectrum analyzer [33]. This measurement is difficult to perform with low repetition rate sources (e.g. 25 MHz fiber lasers) because the interferometer length needs to equal the pulse-to-pulse spacing, which can be several meters long.

As mentioned previously, other schemes can be used to measure the  $f_0$  offset frequency. In future work, the dispersion of the waveguide could be further optimized to use the alternate schemes and to improve the efficiency of the nonlinear interferometer. This could enable direct on-chip self-referenced frequency combs, without the use of external amplifiers [14]. Some examples of improvements include:

- In the current waveguide, there is another dispersive wave near  $3\,\mu m$ . The dispersion can be optimized to have the two dispersive waves at exactly  $1.0\,\mu m$  and  $3.0\,\mu m$  and use the f-3f scheme.

- The long wavelength could be shifted towards 2.0  $\mu$ m, to improve the efficiency of the f-2f scheme.

- The short wavelength could be shifted toward  $0.775 \, \mu m$ , to use the pump itself as the f frequency and improve the efficiency of the frequency doubling.

# **Chapter 3**

# **Fabrication techniques**

In this chapter, we describe some relevant techniques for fabricating integrated photonic waveguides. All the processes described here are intended for silicon substrates. They were developed in or adapted for the Marvell Nanofabrication laboratory at UC Berkeley. We first describe some lithography techniques relevant to integrated photonics, then we discuss about edge roughness and propagation loss, and finally we cover deposition, etching and other processes specific to chalcogenide glass, silicon nitride, and silicon waveguides. While most of the material in this chapter is a review of the literature, some emphasis will be made on specific process improvements that we developed.

## 3.1 Lithography

Lithography is one of the most critical fabrication steps. The choice of technology could be determined by the desired feature size, or photoresist selectivity constraints might call for thick photoresists which only work with certain technologies. In this section, we concentrate on wafer-scale lithography processes and we detail the use of 248 nm DUV stepper, I-line stepper and contact aligner for fabricating optical devices. We also mention other technologies available such as maskless aligners, and more advanced DUV steppers available at commercial foundries. Finally, we present considerations for simulating the lithography process.

## **DUV** stepper

The Nanolab has an ASML 5500/300 DUV stepper (248 nm) which can expose 6 inch wafers with field sizes larger than 2 cm by 2 cm. The automated coating tracks can spin photoresists with thicknesses ranging from  $0.36\,\mu m$  to  $4.7\,\mu m$ .

The photoresist thickness for a particular application is chosen based on selectivity, etching depth and resolution requirements. Generally,  $0.43\,\mu m$  thick resist is used for etching GeSbS,  $0.87\,\mu m$  for patterning trenches for silicon nitride deposition, and  $4.7\,\mu m$  for masking the etching of deep trenches before dicing.

The use of a DUV stepper has several advantages for fabricating optical devices:

- Resolution of 250 nm and smaller, which is sufficient to fabricate many directional couplers, ring resonators and nanotapers

- Very fast for exposing large scale devices such as long spiraling waveguides

- Good field stitching and layer to layer alignment capability (typically 50 nm of alignment error)

- Good reproducibility and exposure uniformity

- Quality masks with nm scale address size can print circular feature with high fidelity

The last point is particularly important when fabricating low loss waveguide spirals and ring resonators.

For 220 nm SOI silicon photonics, a thinner resist can be used during etching. In this case we use  $0.36\,\mu m$  UV210 photoresist which has a 4:1 selectivity in the lam8 etcher. In many cases, a bottom anti-reflection coating (BARC) layer will be required when dealing with topography and fine resolution on silicon layers. Indeed, thin film interference effects become very important in this case since the photoresist thickness will vary over the topography. To insure uniform exposure over all the wafer, the BARC coating will prevent these thin film effects. The BARC layer is approximately 60 nm and replaces the hexamethydisilazane (HMDS) priming step. The BARC layer will not be removed by the photoresist developer, so it needs to be etched before the main layer etch. Fortunately, several dry etching chemistries will remove the BARC layer. For example, when etching silicon, the oxide breakthrough step is extended in duration to also etch away the BARC layer. The oxide breakthrough step is designed to etch away the native silicon oxide before the main etch, and uses a fluorine based chemistry (e.g.  $CF_4$ ). The anti-reflection layer we use (AR3-600) is sensitive to humidity, so the wafer is baked at 190 °C for 60 s.

## I-line stepper

The Nanolab also has a GCA-8500 i-line stepper. The resolution is  $0.7 \, \mu m$  and the alignment accuracy is  $0.3 \, \mu m$ . This stepper is compatible with the thick AZ P4620 photoresist used for backend processes. It is possible to include the GCA alignment marks on the first ASML lithography layer, such that both steppers can be used during the same process (mix and match process). This has the advantage of enabling optimal resolution for the critical layers, while opening up the photoresist options for the backend layers. There is a slight rotation ( $-0.47^{\circ}$ ) between the Nanolab ASML and GCA stepper stages, which can be compensated in the ASML job file. The GCA-last mix and match lithography process is as follow:

- 1. Expose and etch the ASML PM mark layer, including the wafer rotation (ASML reticle)

- 2. Expose and etch the GCA alignment mark layer (ASML reticle), including the wafer rotation, aligned to PM marks

- 3. Expose and process any further ASML layers, including wafer rotation, aligned to PM marks

- 4. Expose and process the GCA layers, aligned to GCA marks

#### Contact aligner

In some cases, coarse features are acceptable but thicker photoresist might be required. This is the case for example while etching deep trenches for releasing dies. In contact lithography, a photomask is first aligned to the substrate, then put into direct contact with the photoresist before being exposed. The mask can be as large as the wafer, exposing all the dies in one step. The same alignment fiducials from the DUV lithography step can be reused by including a negative image on the mask. The light source is typically a mercury-vapor lamp emitting both G-line and I-line wavelengths. The resolution can be as good as 1  $\mu$ m, however the alignment is a manual process and highly dependent on the operator and specific alignment marks. An alignment accuracy of 2  $\mu$ m can be achievable with a well-designed process.

For the purpose of fabricating optical facets for edge coupling, we deposit a  $8 \,\mu m$  thick photoresist (AZ P4620) that can withstand etching tens of microns of oxide and hundreds of microns of silicon. The resist is exposed with approximately 300 mJ and hard baked at 90 °C for 30 minutes.

Compared to using an I-line stepper, the contact aligner is faster since it exposes the whole wafer at once. Both lithography methods have similar resolution. However, the contact between the photomask and the photoresist might leave residues on the photomask which needs to be cleaned often, and the alignment accuracy is more dependent on the operator's skills.

## Maskless aligner

Maskless alignment tools use an array of UV lasers and light modulators to scan the wafer. This defines a custom pattern in a manner similar to e-beam lithography, but with conventional UV photoresists such as i-line sensitive resists. The resolution and alignment accuracy is similar to i-line steppers, but it is more convenient for chip-scale lithography since the exposure time is proportional to the area. Unfortunately, since the exposure is rasterized, this technique is not suitable for exposing low-loss photonic components which have bent or tapered structures.

#### **Foundries**

Contrary to electronic devices, the scaling of optical devices is limited by the wavelength of operation. For many optical components, especially operating in the infrared and in low-index contrast systems such as doped glass or silicon nitride, the resolution limit of 248 nm DUV steppers is sufficient. However, there are certain components, especially in high index contrast platforms, which require a feature size smaller than 250 nm.

Some features which might benefit from the better resolution provided by foundries include:

1. Various gratings: grating couplers, Bragg gratings, and especially subwavelength gratings

- 2. Inverse nanotapers for coupling to fibers

- 3. Components using inverse design [34]

#### Lithography simulation and optimization

Reviewing the principles of lithography is useful to understand the effects of different fabrication parameters on the resolution. The simulation is divided in 3 steps. Although more advanced models exist today, we will give an overview of the simple models from [35] since they can easily be implemented and require a limited number of parameters.

The first step is the aerial image formation. In terms of Fourier optics, this step computes the image of the mask considering the source illumination pattern, and the objective lens pupil. Assuming a normalized incoherent source  $S(\chi)$ , a pupil function  $P(f_x)$ , and a mask transparency function  $T(f_x)$ , the intensity a the wafer plane is written as [35]

$$I(x) = \int S(\chi) |\mathcal{F}[T(f_x - \chi)P(f_x)]|^2 d\chi$$

(3.1)

In this representation, the mask is shifted instead of the source to account for source points that hit the mask at an angle.

The aerial image can be readily computed using libraries for computing the image in microscopy systems, such as Microlith [36].

Once the aerial image is calculated, the image in the photoresist is calculated. This can be done in several levels of approximation, depending on the wavelength, photoresist thickness, numerical aperture and feature size:

- The light intensity can be assumed to be constant as a function of depth in the photoresist

- The thin film interference effects and the defocus effects can be added by multiplying the aerial image by the depth dependent interference pattern and adding a defocus phase term in the pupil function

- A scalar or vector wave equation model can be used to propagate the aerial image in the photoresist, for example using the FDTD method. This will take into account any kind of topography. Both light polarizations can be taken into account.

A simple model linking the light intensity to the photoresist image is called the Dill model, which has three parameters, A, B, and C [35].

The light absorption in the photoresist is determined by

$$\frac{\partial I}{\partial z} = -(Am + B)I\tag{3.2}$$

where B is a constant absorption coefficient, and A linked the absorption to the activated concentration m. The activated concentration depends on the light intensity as

$$\frac{\partial m}{\partial t} = -CIM\tag{3.3}$$

where C links the activated concentration to the light intensity. The photoresist image might need to be determined iteratively since the absorption will depend on the absorbed energy. The Dill's model parameters are often cited in the photoresist datasheet.

Positive DUV resists are commonly chemically amplified. The amplification takes place during the post exposure bake. Additional diffusion of the activated species occurs during the bake, which helps in removing the standing wave patterns in the photoresist, but might also affect the linewidth. Because of this, the post exposure bake time and temperature must be well controlled. The amplification and diffusion processes are modelled using additional parameters, but since the post exposure bake recipe we used is fixed (130 °C for 90 s) we will not study this in more detail.

The development rate r can be calculated from different models [35]. Once the development rate is known, the development is modelled using the eikonal equation (3.4).

$$|\nabla u| = \frac{1}{r} \tag{3.4}$$

This problem is similar to geometric optics propagation in a material with a refractive index gradient. The solution represents the shortest time to travel to a certain point. The final resist profile is given by the contour line for the given development time. Several algorithms and libraries exist to solve this equation, such as [37].

During lithography, several parameters can be tweaked to improve the fabrication tolerance (process window). In particular, using a higher numerical aperture will increase the resolution, at the expense of decreased depth of focus. A higher numerical aperture will also increase the proximity effects, which would need to be modelled using more advanced methods to quantify properly.

When smaller features need to be resolved, the use of annular illumination (instead of conventional partially coherent illumination) might also be desirable (Figure 3.1).

Figure 3.1: Lithography illumination

Indeed, when the numerical aperture is not sufficient to resolve the first diffraction order, angled illumination will tilt the diffraction pattern to let pass the first diffraction order (at the expense of the first negative diffraction order). This is similar to dark field illumination in microscopy, which is used to highlight the edges of the sample. The annular illumination parameters

are expressed as a fraction of the numerical aperture, both for the inner and outer limit of the illumination ring.

An example of the difference in aerial image between conventional and annular illumination for a 200 nm line and for a 300 nm pitch grating is given on Figure 3.2. The improvement in linewidth is slight for the isolated line, but the contrast is greatly improved in the case of the grating with small pitch.

Figure 3.2: Comparison of aerial image between conventional and annular illumination

We have used annular illumination to improve the process window of silicon nanotapers down to 200 nm wide on an ASML DUV stapper with a wavelength of 248 nm, with the following parameters:

- NA = 0.63

- $\sigma_{\rm out} = 0.81$

- $\sigma_{\rm in} = 0.51$

It should be noted, however, that annular illumination will enhance some features, such as the examples given above, at the expense of other features. For example, gratings of specific pitches might not resolve properly, and the tolerance on some dimensions larger than the critical dimension might degrade. Finally, an increase in numerical aperture will also decrease the depth of focus and increase the proximity effect.

Another method to improve the process window of small features is to deposit a bottom antireflective coating (BARC) layer underneath the photoresist. This layer readily absorbs UV light while having a refractive index engineered to minimize Fresnel reflections. This will prevent standing wave patterns in the photoresist and make the dose to clear the photoresist less dependent on the exact thickness. The BARC layer has two advantages:

• The photoresist thickness control can be looser while achieving the same critical dimension tolerance

• The topography will have reduced influence on the dimensions, i.e. the features at high and low topographies will resolve at similar doses.

The standing wave pattern is described using [35]

$$E(z) = E_0 \frac{\tau_{12} \left( \exp(-2i\pi n_2 z/\lambda) + \rho_{23} \tau_{\rm D}^2 \exp(2i\pi n_2 z/\lambda) \right)}{1 + \rho_{12} \rho_{23} \tau_{\rm D}^2}$$

(3.5)

where

$$\rho_{ij} = \frac{n_i - n_j}{n_i + n_j}$$

$$\tau_{ij} = \frac{2n_i}{n_i + n_j}$$

$$\tau_{D} = \exp\{-ik_2D\}$$

$$k_j = \frac{2\pi n_j}{\lambda}$$

and  $n_j$  is the complex index of refraction in layer j. When dealing with more than one intermediate layer, libraries using the transfer matrix method can be used [38]

Figure 3.3 gives an example of the standing wave pattern on a Si substrate, on a thick  $SiO_2$  layer and on a 60 nm BARC layer. On a silicon substrate, the standing wave pattern is significant, but can be greatly reduced with the BARC layer. On a  $SiO_2$  layer (e.g. with a thick bottom cladding), the standing wave pattern is not significant enough to justify the use of BARC.

Figure 3.3: Standing wave patterns in photoresist.

## 3.2 Propagation loss

For most photonic devices, the propagation loss is an important performance parameter. The waveguide propagation losses come mainly from three factors

- Material absorption

- Scattering due to surface roughness

- Leakage, especially to a higher index contrast substrate.

The material absorption will be discussed in the next sections for the specific materials, and leakage will be discuss in the next chapters.

Payne and Laycey [39] developed a theoretical model for propagation loss due to scattering by rough surfaces

$$\alpha \le \frac{\sigma^2}{k_0 d^4 n_1} \kappa \tag{3.6}$$

where  $\sigma$  is the roughness amplitude,  $k_0$  is the light wavenumber, d is the waveguide halfwidth,  $n_1$  is the waveguide refractive index, and  $\kappa$  is a constant that depends on the roughness statistics. This represents an upper bound and was developed for a slab waveguide. It is nonetheless useful in the context of 3D waveguides of arbitrary shape: it predicts that the scattering loss depends on the square of the roughness amplitude, and on the 4<sup>th</sup> power of the waveguide width. Consequently, one of the most effective ways to reduce the propagation loss is by design, with wider waveguides. This might be possible up to a certain point, where the waveguide becomes multimode and other properties (such as minimum bending radius) start to degrade. The second most important element to consider when reducing the propagation loss is the amplitude of the roughness. In many cases extra processing steps can be performed to improve the surface of the waveguide.

The Payne and Lacey model is less accurate for two dimensional waveguides and for large index contrasts [40]. In this case, numerical methods can be used to estimate the propagation loss for different waveguide widths. One such method is to model the sidewall roughness as a lossy material with the imaginary part of the refractive index calibrated to a measurement [41].

For wide waveguides, the propagation loss should decrease as determined by the Payne and Lacey models. For very narrow waveguides, since the waveguide confinement decreases the loss is expected to decrease and to be limited instead by the cladding material loss. We simulate a 220 nm silicon strip waveguide with  $SiO_2$  cladding for different widths on Figure 3.4. The sidewalls are modelled using a 10 nm thick region with the imaginary part of the refractive index calibrated for 5 dB/cm loss at 400 nm for the TE mode. This is a typical value that was measured on devices fabricated at UC Berkeley. The propagation loss peaks around 200 nm waveguide width, where there is maximum interaction with the sidewalls. Moreover, the simulation predicts that the propagation loss is lower in general for the TM mode because the fields interact more with the top and bottom surfaces, and less with the sidewalls compared to the TE polarization.

Figure 3.4: Propagation loss from sidewall roughness as a function of waveguide width

Not to be neglected is the roughness of the top and bottom surface. Some deposition methods (e.g. LPCVD SiO<sub>2</sub>) produce a surface with measurable roughness which can be improved using chemical-mechanical polishing (CMP).

Some methods to reduce the sidewall roughness of silicon waveguides include cycles of oxidation and oxide removal [42] and photoresist reflow [43, 44].

#### 3.3 Chalcogenide glasses

Chalcogenide glasses form a family of compounds which contain oxide-like elements (sulfur, selenide, tellurium). Many of them are optically transparent, and often exhibit nonlinear optical properties. They are used as the core of integrated waveguides in applications where transparency in the mid-infrared is required, or when high nonlinearity is desirable.

Some common examples of chalcogenide glasses used for integrated optics include  $As_2S_3$  [45],  $As_2Se_3$  [46] and GeAsSe [47]. We note that many of these compounds contain arsenic, a material which might not be desirable to manipulate in some laboratory settings. Many chalcogenide glass compounds also suffer from photodarkening or photobleaching effects [48].

Chalcogenide glasses such as  $Ge_{23}Sb_7S_{70}$  are readily available in bulk form. They are easy to evaporate (with glass transition temperatures around 250 °C) to create thin films on wafer substrates. Both thermal evaporation and electron beam evaporation have been reported in the literature to evaporate chalcogenide glasses. In this work we only explored thermal evaporation since the extra heating power from an electron beam evaporator was not required.

Several etching techniques can be used with Ge<sub>23</sub>Sb<sub>7</sub>S<sub>70</sub>. Isotropic wet etching (especially in alkaline solutions) has been observed. The film also etches very fast in a XeF2 silicon etching

chamber. It behaves similarly to SiO<sub>2</sub> under plasma etching. Etching using fluorine-based as well as chlorine-based chemistries has been demonstrated [49].

#### **Deposition**

For depositing the chalcogenide glass, we chose thermal evaporation for its simplicity. We used the NRC thermal evaporator in the Marvell Nanofabrication laboratory which did not have material restriction for  $Ge_{23}Sb_7S_{70}$ . The oldest tool in the cleanroom was modified with increased source to wafer distance for greater uniformity (4%), and electrodes with a better clamping mechanism were installed to improve the reproducibility. The film thickness is monitored using a crystal monitor. The tooling factor was calibrated on a known substrate measured using SEM. The evaporator base pressure is typically around  $2 \times 10^{-6}$  Torr or better.

Since a too high evaporation rate might affect the quality and stoichiometry of the film, we chose a deposition rate of approximately  $1.5\,\mathrm{nm/s}$ . The film composition was verified using energy-dispersive X-ray spectroscopy (EDX) and matches the bulk composition within 1% mass composition. After depositing the chalcogenide film, a thin PECVD  $\mathrm{SiO_2}$  layer (usually 10 nm) is deposited to mask the layer from the alkaline photoresist developer which can etch the chalcogenide glass. The PECVD layer is deposited at a lower temperature of 250 °C to prevent melting of crystallization of the film.

#### **Etching**

The Nanolab etcher ptherm is a reactive ion etcher (RIE) chamber with no material restriction and a large variety of etching gasses. A combination of  $80 \, \text{sccm}$  of CHF<sub>3</sub> and  $4 \, \text{sccm}$  of  $O_2$  at a power of  $150 \, \text{W}$  will yield smooth and vertical sidewalls with an etching rate of  $50 \, \text{nm/min}$ . This is similar to a standard recipe for etching  $SiO_2$ . The etched floor is smooth provided that the chamber is conditioned with a dummy wafer coated with a blank GeSbS film for at least one minute prior to etching the sample. Unfortunately the etching non-uniformity is around 10% in this chamber, which lowers the yield on the fabricated devices.

After etching, the photoresist is removed using a combination of  $O_2$  plasma ashing at low power (100 W) for a few minutes and a long soak in 1165 photoresist remover (20 minutes). The use of a more powerful plasma asher such as the matrix tool was found to damage the film. Then, the PECVD  $SiO_2$  cladding is deposited again at 250 °C to prevent damage to the film.

A cross section of the completed waveguide is shown in Figure 3.5. The rib waveguide has nearly vertical sidewalls. Some imperfections from the fabrication process can be observed: the etching loading created a nonuniform slab thickness near the waveguide, and the PECVD deposition being not perfectly conformal creates "rabbit ear" shaped voids in the top cladding.

Figure 3.5: Chalcogenide waveguide cross section after top cladding deposition

#### 3.4 Silicon nitride

Silicon nitride is a material commonly used in CMOS fabrication. The fabrication techniques and limitations are well-known. In integrated optics, silicon nitride is often used as a core material for low propagation loss waveguides. One of the unique challenge in integrated optics processing compared to CMOS is the difficulty to fabricate thick (>300 nm) layers because of the high tensile stress of the deposited films.

Silicon nitride can be deposited using either plasma-enhanced chemical vapor deposition, or low-pressure chemical vapor deposition. The former has a high deposition rate, and is deposited at lower temperature. It is often used in backend processes where the thermal budget is constrained. The latter deposition method requires elevated temperature (>800 °C) but gives a higher quality film. LPCVD silicon nitride also has the desirable property of being conformal: it can fill trenches without voids.

Depending on the gas ratio during deposition, the resulting silicon nitride can be either stoichiometric  $Si_3N_4$  or low stress. The low-stress variant is silicon-rich and has a slightly higher refractive index.

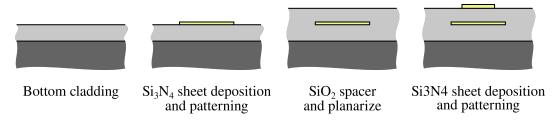

#### Photonic damascene process

A clever way to deal with the silicon nitride film stress is to deposit the waveguide inside a preformed trench [50], a method which is called the photonic damascene process. The preform is made of silicon dioxide and is etched using a mask which is the negative of the waveguide. In our process, we use an amorphous silicon hardmask for etching the silicon dioxide. After depositing the silicon nitride film, the excess is removed using chemical-mechanical polishing (CMP). The process is summarized in Figure 3.6. Silicon nitride is a good candidate material for the photonic damascene process since its deposition is conformal. The geometry of the preform

helps in releasing the stress by converting the tensile stress into bending stress (Figure 3.7), and any remaining stress is removed during the CMP step.