## UC Santa Cruz UC Santa Cruz Electronic Theses and Dissertations

## Title

Design Enhancements And A Validation Framework For ARM Emulator

## Permalink

https://escholarship.org/uc/item/1p85d705

## **Author** Thota, Himabindu

# Publication Date 2013

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA SANTA CRUZ

# DESIGN ENHANCEMENTS AND A VALIDATION FRAMEWORK FOR ARM EMULATOR

A thesis submitted in partial satisfaction of the requirements for the degree of

## MASTER OF SCIENCE

in

## COMPUTER ENGINEERING

by

## Himabindu Thota

June 2013

The Thesis of Himabindu Thota is approved:

Professor Jose Renau, Chair

Professor Matthew Guthaus

Professor Anujan Varma

Tyrus Miller Vice Provost and Dean of Graduate Studies Copyright © by Himabindu Thota 2013

## **Table of Contents**

| Li | st of I | Figures       |                                                                            | vi   |

|----|---------|---------------|----------------------------------------------------------------------------|------|

| Li | st of ] | <b>Fables</b> |                                                                            | vii  |

| Ał | ostrac  | t             |                                                                            | viii |

| Ac | know    | ledgme        | ents                                                                       | ix   |

| 1  | Intr    | oductio       | n                                                                          | 1    |

|    | 1.1     | Motiva        | ation                                                                      | 1    |

|    | 1.2     | ARM A         | Architecture                                                               | 2    |

|    |         | 1.2.1         | ARM, A RISC Architecture                                                   | 2    |

|    |         | 1.2.2         | Memory Organization                                                        | 3    |

|    |         | 1.2.3         | Core Registers                                                             | 3    |

|    |         | 1.2.4         | Data Types                                                                 | 3    |

|    |         | 1.2.5         | Addressing modes                                                           | 4    |

|    |         | 1.2.6         | Instruction Set                                                            | 5    |

|    |         | 1.2.7         | Conditional Execution                                                      | 8    |

|    | 1.3     | The M         | ASC ARM Emulator                                                           | 8    |

|    |         | 1.3.1         | The Emulator Components                                                    | 10   |

|    |         | 1.3.2         | Cracked Emulator Instructions                                              | 11   |

|    |         | 1.3.3         | SCOORE execution engine                                                    | 12   |

|    |         | 1.3.4         | Application Program's Virtual Memory Simulation                            | 13   |

|    |         | 1.3.5         | SCOORE Address Space Translation                                           | 13   |

|    |         | 1.3.6         | System Calls                                                               | 14   |

| 2  | Desi    | gn And        | Implementation Of A Validation Framework                                   | 20   |

|    | 2.1     | Overvi        | iew                                                                        | 20   |

|    | 2.2     | Genera        | ate Expected Results                                                       | 21   |

|    |         | 2.2.1         | Generating Expected Results Using Python - Version I                       | 22   |

|    |         | 2.2.2         | Generating Expected Results Using Two-threaded Implementation - Version II | 22   |

|    |         | 2.2.3         | Generating Expected Results In Chunks - Version III                        | 22   |

|   |     | 2.2.4   | 100x Speedup of Generating Expected Results Using C, GDB MI inter- |    |

|---|-----|---------|--------------------------------------------------------------------|----|

|   |     |         | face                                                               | 23 |

|   | 2.3 | -       | ling And Running The Program <i>generateARMTrace.c</i>             | 23 |

|   |     | 2.3.1   | Instruction Trace File                                             | 24 |

|   |     | 2.3.2   | System Call Trace File                                             | 26 |

|   |     | 2.3.3   | Stack Dump File                                                    | 28 |

|   |     | 2.3.4   | Scmain Command Usage Help File                                     | 28 |

|   |     | 2.3.5   | Special handling of ldrex/strex Instructions                       | 28 |

|   | 2.4 | Validat | te Component Of The Emulator                                       | 29 |

| 3 | Enh | anceme  | nts To The ARM Emulator                                            | 32 |

|   | 3.1 | Overvi  | ew                                                                 | 32 |

|   | 3.2 | Program | m Loading                                                          | 32 |

|   |     | 3.2.1   | Loader Implementation                                              | 33 |

|   |     | 3.2.2   | Emulator Virtual Memory Space and Application Program Simulated    |    |

|   |     |         | Virtual Memory Space                                               | 33 |

|   | 3.3 | Emulat  | tor System Calls                                                   | 34 |

|   |     | 3.3.1   | Calling The Underlying Linux System Call Interface                 | 35 |

|   |     | 3.3.2   | Copying Contents From System Call Trace File To Application Pro-   |    |

|   |     |         | gram Virtual Memory Space Heap                                     | 35 |

|   |     | 3.3.3   | Handling system calls locally using malloc()                       | 35 |

|   |     | 3.3.4   | The brk () System Call                                             | 35 |

|   |     | 3.3.5   | The mmap() System Call $\ldots$                                    | 36 |

|   | 3.4 | Crack   | Code Optimization                                                  | 36 |

|   | 3.5 | U       | xes                                                                | 36 |

|   |     | 3.5.1   | Clear LSB of PC                                                    | 37 |

|   |     | 3.5.2   | Issues With Instruction Decode                                     | 37 |

|   |     | 3.5.3   | Issues With Instruction Cracking                                   | 37 |

|   |     | 3.5.4   | Increment/Decrement Subsequent Memory Addresses                    | 37 |

|   |     | 3.5.5   | Issues With Conditional Execution                                  | 38 |

|   |     | 3.5.6   | Size mismatch of structures defined in unistd.h between 32 and 64- |    |

|   |     |         | bit architectures                                                  | 38 |

|   | 3.6 |         | atic Code Generation of VFP Load/Store Instructions                | 39 |

|   |     | 3.6.1   | Programatic Parsing of the CPU Specification manual                | 39 |

|   |     | 3.6.2   | Auto-generating The Crack Code                                     | 43 |

| 4 | Ran | dom Ins | struction Test Sequence Generation                                 | 46 |

|   | 4.1 |         | d Work                                                             | 46 |

|   | 4.2 | Our Ap  | pproach To Generating RITs                                         | 47 |

|   | 4.3 | -       | tion Macro Library                                                 | 48 |

|   | 4.4 |         | m Test Generator                                                   | 49 |

|   | 4.5 |         | gent Parser                                                        | 51 |

|   | 4.6 | Genera  | ating Random Instruction Tests (RITs)                              | 52 |

|   |     |         |                                                                    |    |

| 5  | Con    | clusion               | 54 |

|----|--------|-----------------------|----|

|    | 5.1    | Contributions         | 54 |

|    | 5.2    | Results               | 54 |

|    | 5.3    | Future Work           | 55 |

| A  | Run    | ning the ARM Emulator | 56 |

| Bi | bliogr | aphy                  | 60 |

# **List of Figures**

| 1.1 | Steps To Run The ARM Emulator.                                                                               | 9  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The Emulator Components.                                                                                     | 10 |

| 1.3 | AND (Register) Instruction.                                                                                  | 12 |

| 1.4 | SCOORE Address Translation.                                                                                  | 14 |

| 2.1 | Steps To Run The ARM Emulator With Validation.                                                               | 21 |

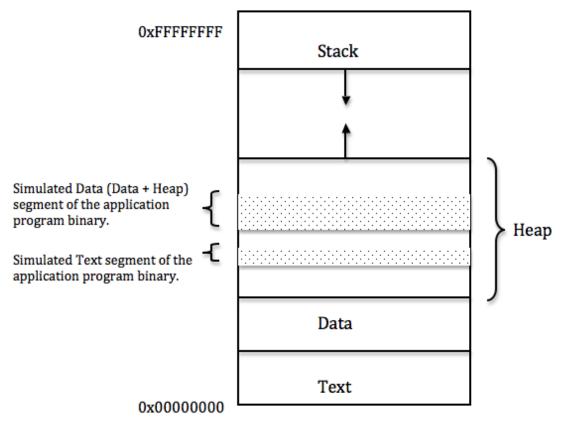

| 3.1 | The Application Program Simulated Virtual Memory With Respect To The Em-<br>ulator Program's Virtual Memory. | 34 |

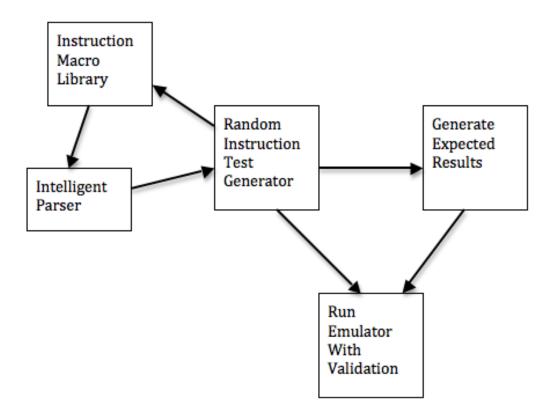

| 4.1 | End-to-end Sequence Of Steps For The ARM Emulator Testing.                                                   | 47 |

## **List of Tables**

| 1.1  | ARM Architecture - Memory.                                            | 3  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | ARM Architecture - Registers                                          | 4  |

| 1.3  | ARM Architecture - Data Types                                         | 4  |

| 1.4  | ARM Architecture - Addressing modes.                                  | 5  |

| 1.5  | ARM Architecture - Data Processing Instructions.                      | 6  |

| 1.6  | ARM Architecture - Load/Store Instructions.                           | 15 |

| 1.7  | ARM Architecture - Load/Store Multiple Instructions.                  | 16 |

| 1.8  | ARM Architecture - Status Register APSR Access Instructions           | 16 |

| 1.9  | ARM Architecture - Advanced SIMD and VFP Load/Store Instructions      | 17 |

| 1.10 | ARM Architecture - Advanced SIMD and VFP Data-Processing Instructions | 17 |

| 1.11 | ARM Architecture - Branch And Block Data Transfer Instrictions        | 18 |

| 1.12 | ARM Architecture - Condition Codes                                    | 18 |

| 1.13 | MASC ARM Emulator - Santa Cruz Micro Operation (scuop) Class Members. | 19 |

| 1.14 | Register Shift Using Type and Imm5 Field Values                       | 19 |

|      |                                                                       |    |

| 3.1  | ARM Architecture - VFP Load/Store Instructions                        | 43 |

| 3.2  | ARM Architecture - Psedocode Specification From The CPU Manual        | 45 |

#### Abstract

## DESIGN ENHANCEMENTS AND A VALIDATION FRAMEWORK FOR ARM EMULATOR

#### by

### Himabindu Thota

Processor emulators allow micro-architecture researchers to evaluate research ideas quickly and at no extra cost. Micro-architecture Santa Cruz (MASC) Laboratory is developing an ARM processor emulator to execute ARM binaries. To ensure correctness of the emulator, it is expected that at the end of every instruction execution the modified registers, their contents, condition codes and any modified values in memory match that of the program execution on a computer with ARM processor. To this end, this work has three parts - first, to design and implement a validation infrastructure for the emulator ISA and the second, to improve the emulator functionality. Interestingly, these two goals go hand-in-hand. Having a validation infrastructure exposes incorrectly implemented or not yet implemented instructions while certain instructions prompt design enhancements in the validation infrastructure. Furthermore, we developed a methodology to generate Random Instruction Tests (RIT) to facilitate regression testing of the ARM emulator.

#### Acknowledgments

Most importantly, I would like to thank my advisor Professor Jose Renau for his invaluable guidance and academic support. I am grateful for the enriching experience working at the MASC lab.

I would also like to thank my committee members Professor Matthew Guthaus and Professor Anujan Varma for their time reviewing my thesis and providing valuable feedback.

I must give special thanks to Ehsan K. Ardestani for engaging in long and productive design discussions, and all my friends and colleagues at the MASC lab.

More personally I would like to thank my husband Sai for his immense patience, support and his constant encouragement to do my best, and my son Hrishikesh and daughter Anagha for always cheering me.

Furthermore, I would like to thank my parents, in-laws, brother, sister and all my friends who have positively influenced my life.

## **Chapter 1**

## Introduction

## 1.1 Motivation

Ever-increasing complexity of microprocessor design with many functional units and complex Instruction Set Architectures (ISA) has prompted the development of high quality software processor emulators to validate design ideas and performance optimizations before the actual microprocessor is fabricated. Even on an in-production microprocessor, evaluating design changes in real hardware is infeasible, as it not only is expensive but is also time-consuming.

Designers and researchers often develop and use microprocessor emulators to evaluate research ideas [7]. Emulators provide a software platform, where functionality can be added and modified with ease and, design choices and optimizations can be evaluated within a reasonable amout of time at no extra cost.

The goal of this work is to develop a high quality ARM processer emulator for use in the Micro-Architecture Santa Cruz (MASC) Research lab. At the beginning of this work, the MASC ARM emulator was able to decode and execute most of the ARM and Thumb-2 instructions. However, the emulator was not ready to execute a complete ARM binary as some of the functions, such as program loading and handling some of the system calls, were not available in the emulator. In addition, not all the implemented instructions were producing the correct results and some instructions were not implemented.

Consequently, as part of this work, first we designed and developed a validation framework to identify the missing emulator functions, incorrectly working and not implemented instructions. Second, by developing the missing emulator functions, fixing incorrectly working instructions and implementing not implemented instructions, we are able to execute complete ARM binaries through the emulator. Furthermore, we developed a methodology to generate test assembly programs with random instruction sequences to facilitate regression testing of the emulator.

The overall structure of the thesis is as follows. Chapter 2 details the design and implementation of the validation framework. Chapter 3 describes the implemented emulator functionalities. Chapter 4 presents the approach for generating regression tests using random instruction sequences and finally, Chapter 5 summarizes our conclusions, results and opportunities for future work.

## **1.2 ARM Architecture**

The following sections provide a summary of the ARM architecture [3].

### 1.2.1 ARM, A RISC Architecture

ARM incorporates typical features of a Reduced Instruction Set Computer (RISC) architecture such as a large uniform register file, simple addressing modes and a load/store architectural approach where data processing instructions operate only on register contents, but not directly on memory contents. Small implementation size, high performance and very low power consumption are key attributes of this architecture.

ARM instruction set is a set of 32-bit instructions providing data-processing and control functions. Thumb instruction set was introduced as a set of 16-bit instructions with a subset of the functionality to provide improved code size. For example, a particular compute functionality, which may require two 32-bit ARM instructions may be acheived by using three 16-bit Thumb instructions, leading to a space savings of 16-bits. However, this comes at a slight reduction in performance as the processor now has to execute one additional instruction in Thumb mode.

ARM supports a switch between the ARM and Thumb states, which allows for assembling performance critical segments using the ARM instruction set. The ARM and Thumb instructions can interwork freely, that is, different procedures can be assembled to different instruction sets. The Thumb-2 instruction set was developed to extend the original 16-bit Thumb instruction set with many 32-bit instructions. Much of the functionality available is identical in ARM and Thumb-2 instruction sets. 16-bit Thumb instructions can be interleaved with 32-bit Thumb instructions within the same procedure resulting in an optimal combination of code size and performance.

## **1.2.2** Memory Organization

ARM instructions are word-aligned and Thumb instructions are halfword-aligned. For data, ARMv7 architecture supports unaligned data access, which is significantly different from the earlier versions of the ARM architecture. Table 1.1 shows the facilities provided by the ARM architecture memory model.

| Address Space  | A single flat address space of $2^{32}$ 8-bit bytes                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addressability | Byte addressable                                                                                                                                                               |

| Facilities     | Faulting unaligned memory access.<br>Restricting access by applications to specified areas of memory.<br>Translating virtual addresses provided by executing instructions into |

|                | physical addresses.<br>Altering the interpretation of word and halfword data between big-endian<br>and little-endian.                                                          |

|                | Optionally preventing out-of-order access to memory.<br>Controlling caches.<br>Synchronizing access to shared memory by multiple processors.                                   |

|                |                                                                                                                                                                                |

Table 1.1: ARM Architecture - Memory.

#### **1.2.3** Core Registers

\_

ARM registers are 32-bits in size. To hold a doubleword, two consecutive registers are used and, to hold a quadword, four consecutive registers are used. Refer to Table 1.2 for a list of ARM registers.

## 1.2.4 Data Types

ARM architecture supports many data types for data held in memory and registers and, for data used in Load/Store operations. See Table 1.3 for a list of data types supported.

| Registers                                                                                            | Function                                                                                         |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| R0 - R12                                                                                             | General Purpose Registers                                                                        |

| R13                                                                                                  | Stack Pointer (SP)                                                                               |

| R14                                                                                                  | Link Register (LR)                                                                               |

| R15                                                                                                  | Program Counter (PC)                                                                             |

| APSR                                                                                                 | Application Program Status Register with N, C, Z, V condition code flags                         |

| ISETSTATE                                                                                            | A set of J, T bits to determine instruction set used by processor<br>J T<br>0 0 ARM<br>0 1 Thumb |

| ITSTATE8-bits wide with top 3 bits indicate If-Then execution condition<br>for Thumb IT instruction. |                                                                                                  |

| ENDIANSTATE                                                                                          | 0 Little-Endian<br>1 Big-Endian                                                                  |

|                                                                                                      | Table 1.2: ARM Architecture - Registers.                                                         |

| Data                        | Supported                                                     |                                              |  |

|-----------------------------|---------------------------------------------------------------|----------------------------------------------|--|

| Location                    | DataTypes                                                     |                                              |  |

|                             | Byte                                                          | 8 bits                                       |  |

| In Memory                   | Halfword                                                      | 16 bits                                      |  |

|                             | Word                                                          | 32 bits                                      |  |

|                             | Doubleword                                                    | 64 bits                                      |  |

|                             | 32-bit pointer                                                | rs                                           |  |

|                             | Unsigned or Signed 32-bit integers                            |                                              |  |

| In Registers                | Unsigned 16-bit or 8-bit integers, held in zero-extended form |                                              |  |

|                             | Signed 16-bit or 8-bit integers, held in zero-extended form   |                                              |  |

|                             | Two 16-bit in                                                 | tegers packed into a register                |  |

|                             | Four 8-bit int                                                | egers packed into a register                 |  |

|                             | Unsigned or                                                   | signed 64-bit integers held in two registers |  |

|                             | Byte                                                          | 8 bits                                       |  |

| For Load & Store Operations | Halfword                                                      | 16 bits                                      |  |

| For Load & Store Operations | Word                                                          | 32 bits                                      |  |

|                             | Doubleword                                                    | 64 bits                                      |  |

|                             | Two or more                                                   | words                                        |  |

Table 1.3: ARM Architecture - Data Types.

## 1.2.5 Addressing modes

Address for a Load/Store operation is formed from two parts - a Base Register and an Offset. See Table 1.4 for supported addressing modes in ARM.

| Base Register    | For Loads       | R0 - R12, PC                       |

|------------------|-----------------|------------------------------------|

|                  | For Stores      | R0 - R12                           |

| Offset Type      | Immediate       |                                    |

| • •              | Register        |                                    |

|                  | Scaled Register |                                    |

| Addressing Modes | Offset          | MemAddr = Base Register +/- Offset |

|                  | Pre-indexed     | MemAddr = Base Register +/- Offset |

|                  |                 | Base Register = MemAddr            |

|                  | Post-indexed    | MemAddr = Base Register            |

|                  |                 | Base Register = MemAddr +/- Offset |

| Table 1.4: ARM Archited | cture - Addressing | modes. |

|-------------------------|--------------------|--------|

|-------------------------|--------------------|--------|

## **1.2.6** Instruction Set

ARM and Thumb-2 architectures support a rich set of instruction types [3]. This section provides a summary of the instruction types with a few examples.

- Branch Instructions, See Table 1.11.

- Data-processing Instructions, See Table 1.5.

- Status Register Access Instructions. See Table 1.8.

- Load/Store Instructions, See Table 1.6.

- Load/Store Multiple Instructions. See Table 1.7

- Advanced Single Command Multiple Data (SIMD) and Vector Floating Point (VFP) Load/Store Instructions. See Table 1.9

- Advanced SIMD and VFP Data-processing Instructions. See Table 1.10

| Instruction               | Examples                                              |

|---------------------------|-------------------------------------------------------|

| Class                     |                                                       |

|                           | AND{S} <rd>,<rn>,<rm>{<shift>}</shift></rm></rn></rd> |

|                           | Instruction performs a bitwise AND of a               |

| Register                  | register value Rn with an optionally-shifted          |

|                           | register value Rm and writes the result to            |

|                           | the destination register Rd.                          |

|                           | ADD{S} <rd>,<rn>,<rm>{<shift>}</shift></rm></rn></rd> |

|                           | Instruction performs a bitwise AND of a               |

|                           | register value Rn with an optionally-shifted          |

|                           | register value Rm and writes the result to            |

|                           | the destination register Rd.                          |

|                           | EOR{S}                                                |

|                           | <rd>,<rn>,<rm><type><rs></rs></type></rm></rn></rd>   |

| Register Shifted Register | Instruction performs a bitwise Exclusive              |

|                           | OR of a register value Rn and a register              |

|                           | shifted register value Rn, Rm and writes the          |

|                           | result to the destination register Rd.                |

|                           | CMN <rd>,<rm><type><rs></rs></type></rm></rd>         |

|                           | Compare Negative Instruction adds a                   |

|                           | register value Rn and a register-shifted              |

|                           | register value Rm, Rs. It updates the                 |

|                           | condition flags based on the result, and              |

|                           | discards the result.                                  |

|                           | SUB{S} <rd>,<rn>,#<const></const></rn></rd>           |

|                           | Instruction subtracts an immediate value              |

| Immediate                 | Continued on next page                                |

Table 1.5: ARM Architecture - Data Processing Instructions.

| Instruction                             | Examples                                              |

|-----------------------------------------|-------------------------------------------------------|

| Class                                   |                                                       |

|                                         | #const from a register value Rn                       |

|                                         | writes the result to the destination register         |

|                                         | Rd.                                                   |

|                                         |                                                       |

| Immediate                               | ADR <rd>,<label></label></rd>                         |

|                                         | Instruction adds an immediate value to                |

|                                         | the PC to form a PC-relative address, and             |

|                                         | writes the result to the destination register         |

|                                         | Rd.                                                   |

|                                         | MUL{S} <rd>,<rn>,<rm></rm></rn></rd>                  |

|                                         | Multiplies two register values Rn, Rm.                |

| Multiply & Multiply Accumulate          | The least significant 32-bits of the                  |

|                                         | result are written to the destination register.       |

|                                         |                                                       |

|                                         | SMULL <rdlo>,<rdhi>,<rn>,<rm></rm></rn></rdhi></rdlo> |

|                                         | Signed Multiply Long multiplies two                   |

|                                         | 32-bit signed register values Rn, Rm                  |

|                                         | to produce a 64 bit result saved in RdLo,             |

|                                         | RdHi.                                                 |

|                                         | QADD <rd>,<rn>,<rm></rm></rn></rd>                    |

|                                         | Instruction adds two register values                  |

| Saturating Addition & Subtraction       | Rm, Rn, saturates the result to the 32-bit            |

|                                         | signed integer range and writes the result to         |

|                                         | the destination register Rd. If saturation            |

|                                         | occurs, it sets the Q flag in the APSR.               |

|                                         | SMLABB <rd>,<rn>,<rm></rm></rn></rd>                  |

|                                         | Signed Multiply Accumulate performs a                 |

| Halfword Multiply & Multiply Accumulate | Continued on next page                                |

Table 1.5 – continued from previous page

|             | 0                                            |

|-------------|----------------------------------------------|

| Instruction | Examples                                     |

| Class       |                                              |

|             | signed multiply-accumulate operation on      |

|             | two 16-bit signed quantities taken from      |

|             | bottom 16-bits of Rn, Rm. The 32-bit         |

|             | product is added to a 32-bit accumulate      |

|             | and the result is written to the destination |

|             | register Rd.                                 |

Table 1.5 – continued from previous page

### **1.2.7** Conditional Execution

Most ARM instructions and, most Thumb instructions can be conditionally executed based on the values of the APSR condition code flags N, Z, C, V.

Bits [31:28] of the ARM instruction contain the condition and if this condition satisfies APSR condition code flags, the instruction is executed, otherwise the instruction acts as a NOP. See Table 1.12 for a list of condition code flags.

Thumb instructions can be made conditional by a preceeding IT instruction which encodes the condition. This 16-bit IT instruction provides an If-Then-Else functionality and makes upto four following instructions conditional. For example, an ITTTE EQ instruction imposes the EQ condition on the first three following instructions and NE condition on the next instruction. The instructions that are made conditional by an IT instruction are called its IT block.

## **1.3 The MASC ARM Emulator**

Micro-architecture Santa Cruz (MASC) Laboratory is developing an emulator research infrastructure to execute ARM, SPARC and x86 binaries. The emulator can run on both x86 and ARM processors with Linux operating system.

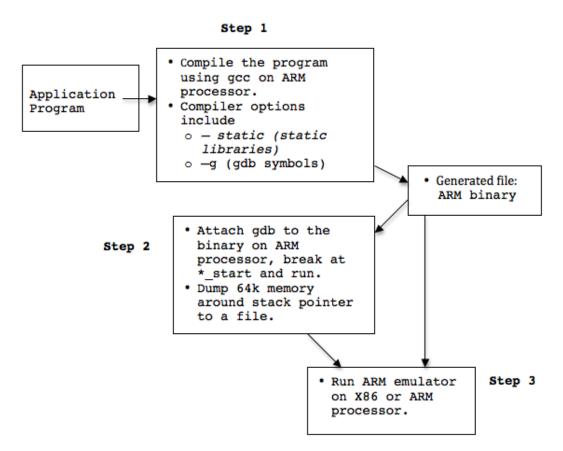

Figure 1.1: Steps To Run The ARM Emulator.

Fig. 1.1 shows the three steps to run the emulator. The first step is to compile the application program with static libraries and gdb symbols on a computer with ARM processor. The second step is to attach gdb to the binary to dump stack memory around the stack pointer to a file and, the third step is to run the emulator on a computer with x86 or ARM based processor.

The emulator requires certain input parameters to run. Mandatory parameters include stack specific information and ARM binary. Optional parameters, which are implemented as part of the validation framework, include an execution trace file and a system call trace file. See Appendix A, *Running the ARM Emulator*.

#### **1.3.1** The Emulator Components

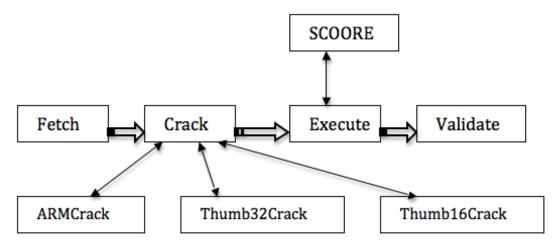

As shown in Fig. 1.2, the execution loop of the emulator fetches an instruction, then cracks the instruction into multiple emulator instructions and executes the cracked instructions. Validate component was developed as part of validation framework. Every instruction passes through Fetch, Crack and Execute stages mandatorily and Validate component optionally. In other words, user has an option to run the emulator with or without validation turned on.

Figure 1.2: The Emulator Components.

During the Fetch stage, instruction associated with the current PC is fetched from the text section of the application program's simulated virtual memory 1.3.4.

In the Crack stage, the instruction is checked for type - ARM, Thumb-16 and Thumb-32, and then cracked into two or more emulator instructions accordingly 1.3.2.

During the Execute stage, each of the cracked emulator instructions is executed using the SCOORE execution engine being developed at the MASC lab 1.3.3. The only exception to this case is when an instruction belongs to an IT block and does not satisfy the IT block condition. In this scenario, not all the cracked instructions may execute.

Validate is responsible for validating the current PC, instruction, modified registers, modified memory and condition codes for every instruction.

#### **1.3.2** Cracked Emulator Instructions

In the emulator, an ARM instruction is cracked into multiple *scinsts - Santa Cruz Instructions* instructions during the Crack stage. Emulator class *scuop* is an abstraction for each of these emulator instructions with members shown in Table 1.13.

#### 1.3.2.1 scuop - Santa Cruz Micro Operation

Format of the *scuop* is as follows:

CrackInst::setup(RAWDInst \*rinst, InstOpcode iop, Scopcode sop, uint8\_t srcA,uint8\_t srcB, uint32\_t immA, uint8\_t dstA, unsigned seticc, unsigned setRND, unsigned getRND);

Where:

- rinst ARM instruction abstraction in the emulator

- *iop* Operation type, examples

- iRALU, iAALU for ALU operations

- iBALU\_BRANCH for control operations ]item iBALU\_JUMP for jump

- iBALU\_CALL, iBALU\_RET for sub-routine call and return

- sop OPCode used by *sccore* engine to execute *scinst*, examples

- OP\_S32\_ADD: Performs 32-bit Arithemetic ADD.

- OP\_S64\_ADD: Performs 64-bit Arithemetic ADD.

- OP\_U16\_ADD: Performs 16-bit unsigned ADD.

- OP\_S08\_SUB: Performs 8-bit SUB.

- srcA: An abstraction for Rn, the Source Register.

- srcB: An abstraction for Rm, the Second Source Register.

- immA: An abstraction for immediate field.

- dstA: An abstraction for Destination Register, Rd.

- seticc: Flag to set condition codes.

#### 1.3.2.2 How Crack Works

In this section, we show a step by step how-to on cracking an ARM instruction into multiple emulator instructions.

Our example ANDS<c><Rd>, <Rn>, <Rm>, <shift> instruction performs a bitwise AND of a register value and an optionally-shifted register value, and writes the result to the destination register.

| 31 30 29 28 | 27 26 | 25 | 24 23 22 2 | 1 20 | 19 18 17 16 | 5 15 14 13 12 | 11 10 9 8 7 | 65   | 4 | 3210 |

|-------------|-------|----|------------|------|-------------|---------------|-------------|------|---|------|

| COND        | 0 0   | 0  | 0000       | s    | Rn          | Rd            | Imm5        | type | 0 | Rm   |

Figure 1.3: AND (Register) Instruction.

Fig. 1.3 shows a bit-level detail of AND (register) instruction. Bits [5:6] - *type* and Bits [7:11] - *imm5* determine the type of shift applied on register Rm, as shown in Table 1.14. The result of bitwise AND of shifted Rm and, Rn is saved to the destination register Rd. Here is the crack implementation for this instruction. Note that the code is shown only for *type* bits [5:6] '00' (LSL).

#### **1.3.3** SCOORE execution engine

SCOORE, the Santa Cruz Out-Of-Order RISC Engine, is a high-performance out-oforder execution engine being developed at the MASC research lab at UCSC to execute each of the *scinsts* generated during the crack stage. The goal of the MASC emulator research infrastructure is to support multiple ISAs, namely SPARC, X86 and ARM architectures. Instructions from these ISAs are cracked into emulator *scinsts* and the SCOORE execution engine executes these instructions independent of the ISA type.

### **1.3.4** Application Program's Virtual Memory Simulation

The ARM emulator allocates memory using malloc() to simulate application program's virtual memory sections stack, text and heap. Note that initialized data section and heap are maintained together by the same memory block in the emulator.

The simulated stack is initialized with the stack dump file which is passed in to the emulator as one of the input parameters.

The ARM binary is encoded in standard ELF format [8] [2] which allows the use of programming interface provided by BFD package [5] to read the input ARM binary sections to initialize text, data and heap segments. In addition, this package provides an API to return the start PC of the instruction execution sequence of the ARM binary, which is used by the emulator to start executing the instruction at this PC.

## 1.3.5 SCOORE Address Space Translation

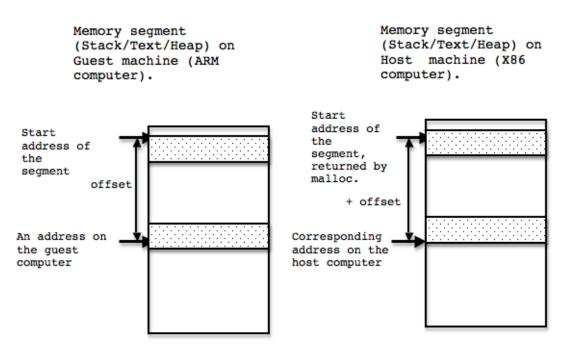

Since the application program is compiled on one computer and is executed through simulation on another computer, there is a need to translate addresses from the guest machine to the host machine. The guest machine refers to the computer with ARM processor on which we compile the application program and the host machine refers to the x86 computer where we run the emulator. A guest address refers to an address in the application program's virtual memory space on the guest machine and a host address refers to an address of the application program's simulated virtual memory space on the host machine.

As shown in Fig. 1.4, the first step to translate a guest address to a host address is to find the segment to which this address belongs to and then find the offset of the address from the start of the segment. Note that the start address of the segments in the application program binary are known and saved in the emulator at the time of program loading, see section 3.2 for details. This offset is then used to compute the corresponding address on the host machine. This computation is valid for any guest adress in stack, text and heap segments.

Figure 1.4: SCOORE Address Translation.

## 1.3.6 System Calls

The emulator handles most of the system calls by calling the underlying Linux system call interface with the same arguments. Some system calls require special handling, see section 3.3 for details.

| Instruction  | Examples                                                                                                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class        |                                                                                                                                                                                                                                              |

| Register     | STR<br><rt>,[<rn>, +/-<rm>{, <shift>}]<br/>Store Register calculates an address from<br/>a base register Rn and an offset register Rm value,<br/>stores a word from register Rt to memory</shift></rm></rn></rt>                             |

|              | LDR<br><rt>,[<rn>, +/-<rm>{, <shift>}]<br/>Load Register calculates an address from<br/>a base register Rn and an offset register Rm value,<br/>loads a word from memory to register Rt</shift></rm></rn></rt>                               |

| Immediate    | STR<br><rt>,[<rn>{,#+/-<imm12>}]<br/>Store Register calculates an address from a base<br/>register Rn and an immediate offset imm12, and<br/>stores a word from register Rt to memory</imm12></rn></rt>                                      |

|              | LDR<br><rt>,[<rn>{,#+/-<imm12>}]<br/>Load Register calculates an address from a base<br/>register Rn and an immediate offset imm12,<br/>loads a word from memory to register Rt</imm12></rn></rt>                                            |

| Literal      | LDR<br><rt>, <label><br/>Store Register calculates an address from<br/>PC and an immediate offset,<br/>and loads a word from memory to register Rt</label></rt>                                                                              |

| Unprivileged | STRT<br><strt rt="">,[<rn>, +/-<rm>{, <shift>}]<br/>Store Register Unprivileged stores a word<br/>from register Rt to memory. The memory access<br/>is restricted as if the processor were running in<br/>User mode</shift></rm></rn></strt> |

|              | LDRT<br><ldrt rt="">,[<rn>, +/-<rm>{, <shift>}]<br/>Store Register Unprivileged stores a word<br/>from register Rt to memory. The memory<br/>access is restricted as if the processor were<br/>running in User mode</shift></rm></rn></ldrt> |

Table 1.6: ARM Architecture - Load/Store Instructions.

| Instruction     | Examples                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class           |                                                                                                                                                                                                                                                                                                                                                                           |

| LDM/LDMIA/LDMFD | LDM <rn>!,<registers>,<br/>Load Multiple Increment After loads multiple<br/>registers from consecutive memory locations<br/>using an address from a base register.</registers></rn>                                                                                                                                                                                       |

| РОР             | POP <registers><br/>Pop multiple loads multiple registers from<br/>the stack, loading consecutive memory locations<br/>starting at the address in SP, and updates SP<br/>to point just above the loaded data.</registers>                                                                                                                                                 |

| STMDB/STMFD     | STMDB <rn>!,<registers>,<br/>Store Multiple Decrement Before stores<br/>multiple registers to consecutive memory<br/>locations using an address from a base register.<br/>The consecutive memory locations end just<br/>below this address, and the address of the first of<br/>those locations can optionally be written back to<br/>the base register.</registers></rn> |

| PUSH            | PUSH <registers><br/>Push Multiple Registers stores multiple registers<br/>to the stack, storing to consecutive memory locations<br/>ending just below the address in SP, and updates SP<br/>to point to the start of the stored data.</registers>                                                                                                                        |

Table 1.7: ARM Architecture - Load/Store Multiple Instructions.

| Instruction | Description                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------|

| Class       |                                                                                                        |

| MRS         | Moves the contents of the Application Program Status<br>Register (APSR) to a general purpose register. |

| MSR         | Moves the contents of a general purpose register to APSR register.                                     |

Table 1.8: ARM Architecture - Status Register APSR Access Instructions.

| Instruction<br>Class | Description                                                                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLDM                 | VLDM <rn>!, <list><br/>Vector Load Multiple loads multiple extension registers from<br/>memory locations using an address from an ARM core register.</list></rn>                          |

| VSTR                 | VSTR <sd>!, [<rn>, #+/-<imm>]<br/>This instruction stores a single extension register to memory, using an<br/>address from an ARM core register, with an optional offset.</imm></rn></sd> |

Table 1.9: ARM Architecture - Advanced SIMD and VFP Load/Store Instructions.

| Example Instructions | Description                                                                                                                                                                                                 |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class                |                                                                                                                                                                                                             |

| VADD                 | VADD <dt>, <qd>, <qn>, <qm><br/>Vector Add adds corresponding elements in two vectors, and<br/>places the results in the destination vector.</qm></qn></qd></dt>                                            |

| VPADAL               | VPADAL <dt>, <qd>, <qm><br/>Vector Pairwise Add and Accumulate Long adjacent pairs of<br/>elements of a vector, and accumulates the results into the<br/>elements of the destination vector.</qm></qd></dt> |

| VDIV                 | VDIV <dd>, <dn>, <dm><br/>This instruction divides one floating-point value by another<br/>floating-point value and writes the result to a third floating-point<br/>register.</dm></dn></dd>                |

| VNEG                 | VNEG <dt>, <qd>, <qm><br/>Vector Negate negates each element in a vector, and places the results<br/>in a second vector. The floating-point version only inverts the sign<br/>bit.</qm></qd></dt>           |

Table 1.10: ARM Architecture - Advanced SIMD and VFP Data-Processing Instructions.

| Instruction                               | Examples                                                    |

|-------------------------------------------|-------------------------------------------------------------|

| Class                                     |                                                             |

| Branch to target address                  | B <label></label>                                           |

|                                           | Branch causes a branch to a target address                  |

| Call a subroutine                         | BL <label></label>                                          |

|                                           | Branch with Link calls a subroutine at a                    |

|                                           | PC-relative address                                         |

|                                           | BLX <label></label>                                         |

| Call a subroutine, change instruction set | Branch with Link Exchange Instruction Sets calls            |

| Can a subroutine, change instruction set  | a subroutine at a PC-relative address, and changes          |

|                                           | instruction set from ARM to Thumb, or from Thumb            |

|                                           | to ARM                                                      |

|                                           | STMDA <rn>,<registers></registers></rn>                     |

|                                           | Store Multiple Decrement After stores multiple registers    |

| Block Data Transfer                       | to consecutive memory locations using address from          |

|                                           | base register Rn                                            |

|                                           | LDM <rn>,<registers pc="" without=""></registers></rn>      |

|                                           | In exception mode, this loads multiple user mode registers  |

|                                           | from consecutive memory locations using an address from     |

|                                           | a register Rn. This instruction is unpredictable in User or |

|                                           | System modes                                                |

| T-11. 1 11. ADM A                         |                                                             |

Table 1.11: ARM Architecture - Branch And Block Data Transfer Instrictions.

| Cond | Mnemonic Extension | Meaning(Integer)             | Condition Flags |

|------|--------------------|------------------------------|-----------------|

| 1110 | None(Al)           | Always                       | Any             |

| 0000 | EQ                 | Equal                        | Z == 1          |

| 0001 | NE                 | Not Equal                    | Z == 0          |

| 0010 | CS                 | Carry Set                    | C == 1          |

| 0011 | CC                 | Carry Clear                  | C == 0          |

| 0100 | MI                 | Minus, Negative              | N == 1          |

| 0101 | PL                 | Plus, Positive or Zero       | N == 0          |

| 0110 | VS                 | Overflow                     | V == 0          |

| 1000 | HI                 | Unsigned Higher              | C == 1 & Z == 0 |

| 1001 | LS                 | Unsigned Lower or Same       | C == 0 & Z== 1  |

| 1010 | GE                 | Signed Greater Than or Equal | N == V          |

| 1011 | LT                 | Signed Less Than             | N != V          |

| 1100 | GT                 | Signed Greater Than          | Z == 0 & N == V |

| 1101 | LE                 | Signed Less Than or Equal    | Z == 1 - N != V |

Table 1.12: ARM Architecture - Condition Codes.

| Member | Description                               |

|--------|-------------------------------------------|

| ор     | SCOORE operation type                     |

| src1   | First Source Register of the instruction  |

| src2   | Second Source Register of the instruction |

| useImm | A flag to indicate if immediate is used   |

| imm    | Value of the immediate                    |

| dst    | Destination Register                      |

| seticc | A flag to set condition codes N,Z,C,V     |

Table 1.13: MASC ARM Emulator - Santa Cruz Micro Operation (scuop) Class Members.

| Type Field | Shift                                                                        | Shift                                                                    |

|------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Bits [5:6] | Туре                                                                         | Value                                                                    |

| 00         | LSL(Logical Shift Left)                                                      | UInt(imm5)                                                               |

| 01         | LSR(Logical Shift Right)                                                     | if imm5 == '00000'                                                       |

| 10         | ASR(Arithmetic Shift Right)                                                  | then 32 else UInt(imm5)<br>if imm5 == '00000'<br>then 32 else UInt(imm5) |

| 11         | imm5 == '00000' then RRX(Rorate Right With Extend)<br>else ROR(Rotate Right) | 1<br>UInt(imm5)                                                          |

Table 1.14: Register Shift Using Type and Imm5 Field Values.

## **Chapter 2**

# Design And Implementation Of A Validation Framework

Having a validation framework for the ARM emulator serves two purposes. First, it helps identify incorrectly implemented or not yet implemented instructions and second, it helps find regression bugs quickly and easily. Regression bugs refer to those bugs that are introduced unintentionally into already working code during new feature development or while trying to fix other bugs. This chapter describes the design and implementation of a validation framework for the ARM emulator.

## 2.1 Overview

Every instruction execution in the ARM emulator may result in modified register or memory values and condition codes. Emulator results need to be validated against expected results obtained from the same program execution on ARM processor. Generation of the expected results and validation of the emulator results against the expected results are automated and are discussed in detail in the subsequent sections. While validating regular instructions is straightforward, handling system calls in the emulator is a bit more involved and is dealt with on a case by case basis. We make the following contributions

- Auto generate expected results.

- Validate the emulator results against the expected results.

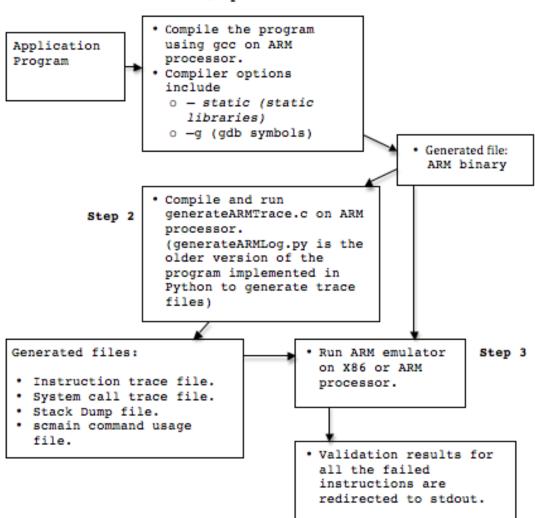

With validation, the sequence of three steps to run the emulator shown in Fig. 1.1 slightly changes to the steps shown in Fig. 2.1.

Step 1

Figure 2.1: Steps To Run The ARM Emulator With Validation.

## 2.2 Generate Expected Results

The program to generate the expected results first attaches gdb to the program, steps through each instruction (with one exception, as described in section 2.3.5), sends commands

to gdb to dump register values and, processes the output returned by gdb. In summary, the program has two distinct but equally important tasks -

- Interact with GDB

- Process GDB Output

The program generates -

- An instruction trace file,

- A system call trace file and

- A file with 64kB binary dump of memory around the stack pointer.

### 2.2.1 Generating Expected Results Using Python - Version I

At first, to generate expected results, a Python Program 'generateARMLog.py' was implemented. It uses the 'pexpect' Python module to interactively communicate with gdb to step through each instruction. It imports the standard Python package 're' to use regular expression symantics of the language to process the output.

Even though the Python program 'generateARMLog.py' generates expected results reliably and was used extensively over the last few months, there is a need to speedup its execution time. With its current processing speed of about 100 instructions per minute, generating expected results for even a simple 'hello world' program takes about 4 hours of time.

## 2.2.2 Generating Expected Results Using Two-threaded Implementation - Version II

As outlined earlier, generating expected results has two tasks. The first task is to interact with gdb process to step through instructions and the second task is to process the gdb output and generate expected results.

To utilize the multi-core ARM processor in MASC lab, our first attempt at speeding up involved implementing a two threaded parallel program with one thread interacting with gdb and the other thread processing gdb output and generating expected results. But with bulk of the time spent on interaction with gdb, this technique did not yield favourable speedup.

#### 2.2.3 Generating Expected Results In Chunks - Version III

This strategy was not so much to speedup the generation of expected results but to alleviate the long wait time before they are generated. In this method, the Python program generates multiple files with each file containing expected results for a predefined number of instructions. This allows the user to start running the emulator to validate a subset of instructions while the expected results for the rest of the instructions are being generated. This strategy works well when the emuator is still under development with the assumption that validation usually finds bugs in the subset and finding the root cause and fixing the bugs usually take time. Fixing bugs in one subset while generating expected results for another subset can happen in parallel. Unfortunately, this strategy does not work well for regression tests.

### 2.2.4 100x Speedup of Generating Expected Results Using C, GDB MI interface

Looking further into the issue of speeding up expected results generation, the key thing to note is that by speeding up the interaction with gdb the overall speedup of the program can be acheived. Python being an interpreted language with pexpect module processing every line returned from gdb considerably slows down the expected results generation.

Our third attempt at speeding up involved implementing a C program using gdb machine interface (MI) library to interact with gdb and process output. Gdb MI [1] is a line based machine oriented text interface to gdb. The library provides interfaces to spawn gdb process in interpreter mode, step through instructions and parse gdb output. With this implementation, generating expected results is significantly faster, with under 2 minutes for the simple 'hello world' program as opposed to 4 hours with the earlier version of the Python program.

## 2.3 Compiling And Running The Program generateARMTrace.c

Compile and run this program on an ARM processor. This program requires 'gdbmi' library. On masca1(an ARM computer in MASC lab), gdbmi library is installed at /root/gdbmi.

To compile the program on mascal:

-----

cc -O0 -Wall -gstabs+3 -I /root/gdbmi/libmigdb/src

```

generateARMTrace.c /root/gdbmi/libmigdb/src/libmigdb.a

-o generateARMTrace

```

To run:

\_\_\_\_\_

./generateARMTrace

Example:

arm-shell# ./generateARMTrace

Usage: generateARMTrace <binary> <results\_dir>

arm-shell# ./generateARMTrace hello logs > output

This program generates the following files...

| logs/scmain_cmd         | scmain (emulator) command |

|-------------------------|---------------------------|

|                         | usage help                |

| logs/stack_mem_dump.bin | stack memory dump         |

| logs/syscall_trace      | system call trace         |

| logs/inst_trace         | instruction trace         |

### 2.3.1 Instruction Trace File

\_\_\_\_\_

This file provides a trace of instruction execution sequence. Every instruction has a dedicated section in this file. Useful information about the executed instruction such as pc, instruction, modified single/double word registers and modified condition codes are saved in the section. Let us look at a couple of sections in detail in this file.

24

```

Instruction number: 3

pc: 0x8790

inst: 0x1b04f85d

r2=0x1

r14=0xbeffe9b4

_____

Instruction number: 4

pc: 0x8794

inst: 0xf84d466a

r3=0xbeffe9b4

_____

Instruction number: 5

pc: 0x8796

inst: 0x2d04f84d

r14=0xbeffe9b0

_____

Instruction number: 6

pc: 0x879a

inst: 0x0d04f84d

r14=0xbeffe9ac

_____

```

The first line line of any section is the instruction sequence number in the program execution. The second line is the PC value and the rest of the lines are for the modified registers and their contents. In the above example, for instruction 3, modified registers are R2 and R14 while for instruction 4, modified register is R3.

Note that in the emulator, the register numbering starts from R1 while on the ARM processor, the register numbering starts from R0. We take care of this by incrementing the modified register number before writing to the instruction trace file.

#### 2.3.2 System Call Trace File

System calls are a means by which a user program can request for the underlying operating system services. Some system calls provide a pointer to a memory buffer as one of the input arguments and request the operating system to populate it with some specific information. The uname () is one such system call, it provides a pointer to the utsname structure and the operating system updates the memory buffer with name and other information about the kernel. Subsequent instructions may load values from this section of the memory to carry out their operations.

In the emulator, system calls are serviced by calling the underlying operating system system call interface. In such scenarios as explained above, where a section of the memory is changed when a system call is executed, the validator can yield false negative results for the subsequent instructions that use the information in the changed memory buffer. This is due to the fact that the validator validates the results by comparing the 'expected results' obtained from the program execution on ARM computer and 'emulator results' obtained from the emulator execution on x86 computer. Obviously, the information returned by the kernels of these two computers will not match in most of the cases. For such system calls, for the validator to work correctly, when generating the system call trace file on ARM computer, the system call resulting memory contents are copied over to the system call trace file. When the emulator finds such system calls, when validation is turned on, the emulator reads the system call results from the system call trace file and copies to the corresponding emulator virtual memory section. Note that this matching is not needed when validation is turned off and in that case, the emulator system call execution falls back to calling the underlying Linux system call interface.

The system call trace file records the sequence of system calls in the program. Every system call has a dedicated section in this file. Each section records the PC, instruction and the system call number for a system call. For system calls that modify the memory, the resulting memory contents are copied to this file as well.

In the current implementation, the resulting memory contents of the uname() and fstat64() system calls are copied to the system call trace file.

Here is an example contents of system call trace file highlighting three different types of information saved in system call trace file depending on the system call.

\_\_\_\_\_

```

pc: 0x25988

syscall: 122 // uname

Linux

masca1

3.0.0-1205-omap4

#10-Ubuntu SMP PREEMPT Thu Sep 29 03:57:24 UTC 2011

armv7l

_____

pc: 0x8de4

syscall: 45

_____

pc: 0x8de4

syscall: 197 // fstat64

d00000000000000b

00000040000000

000000100002190

000000050000dca

000000000008801

000000000000400

20b585ad50636548

20b585ad50636548

37fdfc0150635fd5

000000000000000004

fffffff00068128

00009dc500068128

0002101700068128

000000c0004981c

000205e100068128

```

27

pc: 0x10f04 syscall: 192

\_\_\_\_\_

#### 2.3.3 Stack Dump File

The file 'stack\_mem\_dump.bin' provides a binary dump of the memory around the stack pointer. The binary dump is obtained using the gdb command 'dump binary memory mem start\_addr end\_addr' with start\_addr being SP & 0xFFFF0000 and end\_addr being SP | 0x0000FFFF, where SP is the stack pointer.

#### 2.3.4 Scmain Command Usage Help File

The file 'scmain\_cmd' provides the command to run the scmain (ARM) emulator. This file is useful as it eliminates the need to note down the values of stack pointer and start of the stack buffer which are both required to run the emulator.

#### 2.3.5 Special handling of ldrex/strex Instructions

Load Register Exclusive ldrex and Store Register Exclusive strex instructions require the processor to have an exclusive access to memory. Stepping through either of these two instructions using gdb violates this exclusivity and the instruction execution waits in a tight loop for the lock, which never becomes available. To overcome this situation, a lookahead logic is implemented to not to step through these instructions.

```

89f6: f3bf 8f5f

dmb sy

// First data barrier instruction

89fa: e852 1f00

ldrex r1, [r2] // LDREX

89fe: 4299

cmp r1, r3

bne.n 8a0e < libc start main+0x1ce>

8a00: d105

strex r1, r0, [r2]

8a02: e842 0100

// STREX

8a06: f091 0f00

teg r1, #0

8a0a: d1f6

bne.n 89fa <__libc_start_main+0x1ba>

8a0c: 4619

mov r1, r3

```

8a0e: f3bf 8f5f dmb sy // Second data barrier instruction 8a12: 428b cmp r3, r1

The lookahead logic takes advantage of the use of two Data Memory Barrier dmb instructions that enclose the instruction sequence containing ldrex/strex instructions to provide the exclusivity. The logic looks ahead at the instruction next to dmb to determine if it is an ldrex instruction. If so, it finds the corresponding strex instruction and the closing dmb instruction. Once it is determined that the block of instructions is ldrex/strex, instead of stepping through each instruction, a break point is set for the second dmb instruction and gdb execution is continued using the command continue instead of stepping using the command si through individual instructions.

A similar look ahead logic is implemented in the validate component of the emulator as well.

### 2.4 Validate Component Of The Emulator

Now comes the time to validate the emulator. After every instruction execuiton in the emulator, if the user choses to validate, the validate component reads one section of the instruction trace file to get the expected PC, instruction, modified register contents, condition codes. Then compares these results to the results generated by the emulator and prints pass/fail results with some useful debug information about what was expected and what was generated by the emulator in case the validation fails for that instruction.

When the emulator encounters a system call in the program execution, it reads a section of information from the system call trace file to validate the PC, instruction, system call number. Those system calls for which the resulting memory contents are copied, emulator reads this information and copies over to the corresponding application program's virtual memory space.

If the instruction belongs to ldrex/strex block, the lookahead logic similar to that described in section 2.3.5 is implemented in the emulator to not to validate the set of instructions in ldrex/strex block.

The following is shows examples of the emulator output when an instruction passes validation and another instruction that fails validation.

```

1) Instruction execution with no failures

Th[0] next PC=0X8b8c

// CRACK Expansion

expanded:

+: TMP3 = ZERO OP_S64_COPYPCL ZERO useImm=1 imm=35732 seticc=0

setrnd=0 getrnd=0

+: TMP2 = TMP3 OP_U32_ADD ZERO useImm=1 imm=12 seticc=0 setrnd=0

getrnd=0

+: R3 = TMP2 OP_U32_LD_L ZERO useImm=0 imm=0 seticc=0 setrnd=0

getrnd=0

// Execution information

executed:

Th[0] -: modified state

rf[78]=0x8b94 ccrf=0x0

Th[0] -: modified state

rf[77]=0xc00008ba0 ccrf=0x0

addr(1du32) 0x00008ba0

ldu32 [0x8ba0] -> 0x00009428

Th[0] -: modified state

rf[4]=0x9428 ccrf=0x0

// Validation information

```

```

inITBlock 0, NOPStatus 0, flushDecode 0

inst num: emul Instruction number: 10, trace file Instruction

```

```

reg_val 9428

reg_num 4 reg_val 9428 f_reg_val 0x00009428

```

```

2) Instruction execution with failures

Th[0] next PC=0X8d10

// CRACK Expansion

expanded:

+: R10 = R3 OP_S32_ADD ZERO useImm=0 imm=0 seticc=0 setrnd=0

getrnd=0

// Execution information

executed:

Th[0] -: modified state

rf[11]=0x9428 ccrf=0x0

// Validation information

inITBlock 0, NOPStatus 0, flushDecode 0

inst num: emul Instruction number: 17, trace file Instruction

FAIL: pc values do not match

expected_pv_val 0x8d12 emul_pc_val 0x8d10

reg_val 9428

reg_num 11 reg_val 9428 f_reg_val 0x00009428

```

FAIL: register values don't match

reg\_num 11. exp\_reg\_val 0x00009428. emul\_reg\_val 0x00009000

# **Chapter 3**

# **Enhancements To The ARM Emulator**

While the first part of the thesis work is to design and implement a validation framework, the second, equally important part, is to improve the ARM Emulator functionality inorder to facilitate executing ARM binaries through the emulator. This chapter describes the enhancements made to ARM emulator functionality in various areas.

### 3.1 Overview

At the beginning of this work, the emulator was capable of interpreting most of the instructions. However, the emulator was not ready to execute ARM binaries. To facilitate executing ARM binaries through the emulator, we make the following contributions:

- Implement Program Loader Functionality.

- Implement System Calls.

- Fix incorrectly-working instructions.

- Implement VFP load/store instructions using a rapid development technique.

# 3.2 Program Loading

The Loader is a part of the operating system responsible for loading the program binary from disk to memory and making it ready for execution. The ARM binary follows the standard ELF format [8] [2] and contains sections such as .text, .data and .bss etc. One of the loader's function is to combine two or more sections of the binary into a segment and pad the segment to align it to the page size, which is 4k by default for ARM binaries.

In the emulator, the loader function is implemented by a software routine. This routine uses BFD programming package [5] to read the application binary sections, follows the guidelines specified in ELF standard [2] to create segments, pads the segments to align to the page boundaries and allocates memory for the segments using malloc().

#### 3.2.1 Loader Implementation

After examining the readelf output of a few program binaries, the following assumptions are made about the ARM program binary sections

- The first page of the ELF formated application binary contains .text section.

- The first data section is either .tdata or .bss whichever has the lower virtual memory address.

- The last data section, which is also a part of heap, is either .bss or \_libc\_freeres\_ptrs

These assumptions are working well for binaries compiled with static libraries. Program Loading for binaries with dynamic libraries was not studied as part of this work and may be considered future work.

In the emulator, the loader routine combines sections to creates two segments - text and data. Data segment contains initialized data and also heap. In other words, data and heap of the application program are maintined as one memory block in the emulator.

# 3.2.2 Emulator Virtual Memory Space and Application Program Simulated Virtual Memory Space

Fig. 3.1 shows a pictorial representation of the application program's simulated virtual memory space with respect to the ARM emulator program's virtual memory space. As shown, the application program's simulated text and data segments live in the heap space of the emulator's virtual memory.

Figure 3.1: The Application Program Simulated Virtual Memory With Respect To The Emulator Program's Virtual Memory.

# **3.3 Emulator System Calls**

In the emulator, depending on the system call functionality, its implementation falls into one of the three categories.

- The first type of system calls are serviced by simply calling the underlying Linux system call interface with the same arguments.

- The second type of system calls are serviced by calling the underlying Linux call interface just like in the first case, but the memory contents updated by OS are copied to the system call trace file and this content is copied over to the virtual memory of the application program during emulator validation, see section 2.3.2.

• The third type of implementation is to handle the system calls locally using malloc().

#### 3.3.1 Calling The Underlying Linux System Call Interface

The system calls read(), write(), exit() are some of the examples of the system calls for which the emulator calls the undelying Linux system call interface to get the work done.

# **3.3.2** Copying Contents From System Call Trace File To Application Program Virtual Memory Space Heap

When emulator encounters system calls in the program execution, it reads a section of information from the system call trace file for pc, instruction and system call number. For the system calls uname() and fstat64(), saved memory buffer information (refer to section 2.3.2) from the system call trace file is copied over to the application program's virtual memory space at the corresponding location.

#### **3.3.3 Handling system calls locally using malloc()**

The emulator needs to handle some of the system calls locally using malloc() without calling the underlying Linux system call API. These system calls are usually associated with application program's virtual memory space, specifically heap.

#### 3.3.4 The brk () System Call