# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

### **Title**

Designing network traffic managers with throughput, fairness, and worst-case performance guarantees

### **Permalink**

https://escholarship.org/uc/item/1nj1s4cd

#### **Author**

Wang, Hao

### **Publication Date**

2011

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Designing Network Traffic Managers with Throughput, Fairness, and Worst-case Performance Guarantees

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Communication Theory and Systems)

by

Hao Wang

## Committee in charge:

Professor Bill Lin, Chair Professor Pamela C. Cosman Professor Sujit Dey Professor Rajesh K. Gupta Professor Andrew B. Kahng Professor Tajana S. Rosing

© Copyright Hao Wang, 2011 All rights reserved.

| The dissertation of Hao Wang is approved, and it is accept- |

|-------------------------------------------------------------|

| able in quality and form for publication on microfilm and   |

| electronically:                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

|                                                             |

| Chair                                                       |

University of California, San Diego

# **DEDICATION**

To my parents.

### **EPIGRAPH**

If one learns but does not think, one will be bewildered.

If one thinks but does not learn from others, one will be imperiled.

—Confucius, Analects, c.400 B.C.

## TABLE OF CONTENTS

| Signature Pag  | ge .    |                                                            |   |   | iii   |

|----------------|---------|------------------------------------------------------------|---|---|-------|

| Dedication .   |         |                                                            |   |   | iv    |

| Epigraph       |         |                                                            |   |   | V     |

| Table of Con   | tents   |                                                            |   |   | Vi    |

| List of Figure | es      |                                                            |   |   | X     |

| List of Tables | s       |                                                            |   |   | xii   |

| Acknowledge    | ements  | 5                                                          |   |   | xiii  |

| Vita           |         |                                                            |   |   | xvi   |

| Abstract of th | ne Diss | sertation                                                  |   |   | xviii |

| Chapter 1      | Intro   | oduction                                                   |   |   | 1     |

|                | 1.1     | Network Traffic Management                                 |   |   | 1     |

|                |         | 1.1.1 Statistics Accounting                                |   |   | 3     |

|                |         | 1.1.2 Packet Scheduling                                    |   |   | 4     |

|                | 1.2     | Techniques for Providing Throughput, Fairness, and Wor     |   |   |       |

|                |         | case Performance Guarantees                                |   |   | 6     |

|                |         | 1.2.1 Pipelined Architectures                              |   |   | 6     |

|                |         | 1.2.2 Load-balancing and Parallelism                       |   |   | 7     |

|                | 1.3     | Problem Statement and Contributions                        |   |   | 8     |

|                | 1.5     | Troblem Statement and Contributions                        | • | • | O     |

| Chapter 2      | Mai     | ntaining State Information with Millions of Counters       |   |   | 13    |

| enapter 2      | 2.1     | Introduction                                               |   |   |       |

|                | 2.1     | 2.1.1 DRAM Can Be Plenty Fast                              |   |   |       |

|                |         | 2.1.2 Our Approach                                         |   |   | 16    |

|                |         | 2.1.2 Summary of Contributions                             | • | • | 17    |

|                |         | 2.1.4 Outline of Chapter                                   | • | • | 19    |

|                | 2.2     | 1                                                          |   |   | 19    |

|                | 2.2     | Related Work                                               |   |   |       |

|                | 2.3     | Randomized Counter Architecture                            |   |   | 21    |

|                | 2.4     | Performance Analysis                                       |   |   | 24    |

|                |         | 2.4.1 Union Bound – The First Step                         |   |   | 25    |

|                |         | 2.4.2 Mathematical Preliminaries                           |   |   | 27    |

|                |         | 2.4.3 Worst Case Update Request Sequence                   |   |   | 29    |

|                |         | 2.4.4 Relaxations of $X_{m^*}$ for Computational Purposes. |   |   | 31    |

|                | 2.5     | Performance Evaluation                                     |   |   | 35    |

|           |       | 2.5.1    | Implementation Details                            | 35 |

|-----------|-------|----------|---------------------------------------------------|----|

|           |       | 2.5.2    | Traffic Traces                                    | 37 |

|           |       | 2.5.3    | Tail Bounds for Randomized Counter Architecture . | 37 |

|           |       | 2.5.4    | Cost-Benefit Comparison                           | 41 |

|           | 2.6   | Conclu   | ision                                             | 43 |

| Chapter 3 | Optii | mizing S | Statistics Counter Array for Internet Traffic     | 45 |

| <u>-</u>  | 3.1   | _        | action                                            | 45 |

|           | 0.1   | 3.1.1    | Summary of Contributions                          | 46 |

|           | 3.2   |          | RAM Emulation for Statistics Counter              | 47 |

|           | 3.3   |          | oposed Design                                     | 48 |

|           | 3.3   | 3.3.1    | Counter Architecture                              | 49 |

|           |       | 3.3.2    | Why Merging Request Queues are Necessary?         | 51 |

|           | 3.4   |          | mance Analysis                                    | 52 |

|           | Э.Т   | 3.4.1    | Preliminaries                                     | 52 |

|           |       | 3.4.2    | Union Bound - System Overflow Probability         | 54 |

|           |       | 3.4.3    | Request Merging Probability                       | 55 |

|           |       | 3.4.4    | Average Merging Probability for Internet Flows    | 59 |

|           | 3.5   |          | tness Against Adversaries                         | 62 |

|           | 3.6   |          | mance Evaluation                                  | 65 |

|           | 3.0   | 3.6.1    | Traffic Traces                                    | 65 |

|           |       | 3.6.2    |                                                   |    |

|           |       |          | Experimental Results                              | 65 |

|           | 2.7   | 3.6.3    | Cost-benefit Comparison with Other Approaches     | 70 |

|           | 3.7   | Concil   | ision                                             | 71 |

| Chapter 4 |       |          | nory Systems for Network Processing               | 73 |

|           | 4.1   |          | action                                            | 73 |

|           |       | 4.1.1    | Motivation                                        | 74 |

|           |       | 4.1.2    | Our Approach                                      | 76 |

|           |       | 4.1.3    | Outline of Chapter                                | 77 |

|           | 4.2   |          | d Work                                            | 78 |

|           |       |          | Statistics Counter Arrays                         | 78 |

|           |       | 4.2.2    | Memory Systems with Restricted Accesses           | 79 |

|           |       | 4.2.3    | General Memory Systems with Unrestricted Accesses | 80 |

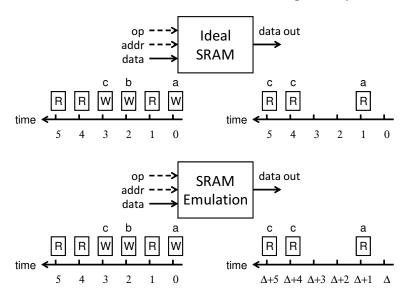

|           | 4.3   |          | RAM Emulation                                     | 82 |

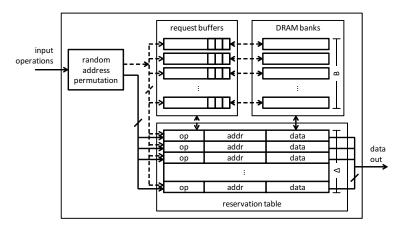

|           | 4.4   | The Ba   | asic Memory Architecture                          | 84 |

|           |       | 4.4.1    | Architecture                                      | 84 |

|           |       | 4.4.2    | Operations                                        | 85 |

|           |       | 4.4.3    | Adversarial Access Patterns                       | 86 |

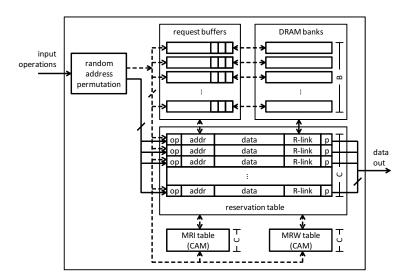

|           | 4.5   | The Ex   | stended Memory Architecture                       | 86 |

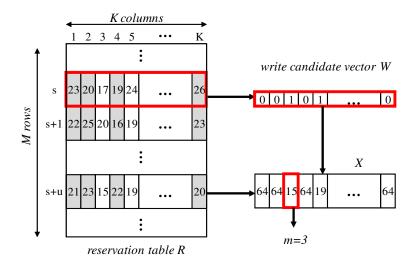

|           |       | 4.5.1    | Reservation Table Management                      | 88 |

|           |       | 4.5.2    | Memory Operations                                 | 89 |

|           |       | 4.5.3    | Operation Merging Rules                           | 92 |

|           | 4.5.4 Arrivals to Request Buffers                 | 94  |

|-----------|---------------------------------------------------|-----|

|           | 4.6 Performance Analysis                          | 95  |

|           | 4.6.1 Worst-Case Parameter Setting                | 96  |

|           | 4.6.2 Request Queue Overflow Probability          | 98  |

|           | 4.7 Performance Evaluation                        | 100 |

|           | 4.7.1 Numerical Examples of the Tail Bounds       | 101 |

|           | 4.7.2 Cost-Benefit Comparison                     | 103 |

|           | 4.8 Conclusion                                    | 105 |

| Chapter 5 | Priority Queues for High Speed Scheduling         | 106 |

|           | 5.1 Introduction                                  | 106 |

|           | 5.2 Related Work                                  | 109 |

|           | 5.3 Scheduling in Per-flow Queueing               | 110 |

|           | 5.3.1 Scheduling Algorithm                        | 111 |

|           | 5.3.2 Per-flow Queueing Operations                | 112 |

|           | 5.4 Succinct Priority Indexing Abstraction        | 113 |

|           | 5.4.1 Abstraction                                 | 113 |

|           | 5.4.2 Index Update Operations                     | 114 |

|           | 5.5 Counting-Priority-Index                       | 115 |

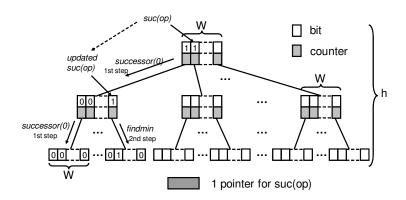

|           | 5.5.1 Structure of CPI                            | 115 |

|           | 5.5.2 Operations in CPI                           | 116 |

|           | 5.5.3 Memory and Complexity                       | 118 |

|           | 5.6 Pipelined Counting-Priority-Index             | 119 |

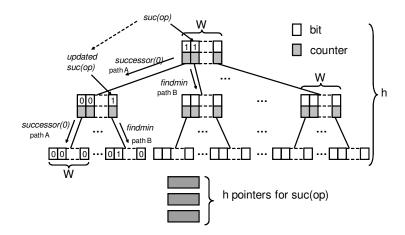

|           | 5.6.1 Structure of pCPI                           | 119 |

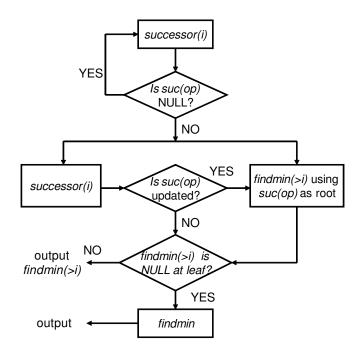

|           | 5.6.2 Operations in pCPI                          | 119 |

|           | 5.6.3 Memory and Complexity                       | 121 |

|           | 5.7 pCPI for Per-flow Queueing                    | 122 |

|           | 5.7.1 Index Mapping                               | 123 |

|           | 5.7.2 Timestamp Mapping                           | 124 |

|           | 5.7.3 Queue Mapping using Hash Functions          |     |

|           | 5.7.4 CAM for Queue Mapping                       |     |

|           | 5.8 Implementing Priority Queues in Packet Buffer | 129 |

|           | 5.8.1 Packet Buffer Abstraction                   | 129 |

|           | 5.8.2 Packet Buffer Architecture with pCPI        | 130 |

|           | 5.9 Performance Evaluation                        | 131 |

|           | 5.10 Conclusion                                   | 134 |

| Chapter 6 | Packet Buffers in High Speed Routers              | 136 |

| 1         | 6.1 Introduction                                  | 136 |

|           | 6.2 Related Work                                  | 140 |

|           | 6.3 System Model - Packet Buffer Abstraction      | 142 |

|           | 6.4 Deterministic Frame-sized Packet Buffer       | 143 |

|           | 6.4.1 Architecture                                | 143 |

|              |      | 6.4.2     | Packet Access Conflicts            | 145 |

|--------------|------|-----------|------------------------------------|-----|

|              |      | 6.4.3     | Memory Management Implementation   | 147 |

|              | 6.5  | Detern    | ninistic Block-sized Packet Buffer | 152 |

|              |      | 6.5.1     | Architecture                       | 152 |

|              |      | 6.5.2     | Reservation Table                  | 153 |

|              |      | 6.5.3     | Packet Access Conflicts            | 154 |

|              |      | 6.5.4     | Memory Management Implementation   | 157 |

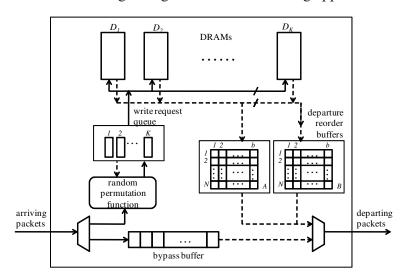

|              | 6.6  | Rando     | mized Block-sized Packet Buffer    | 161 |

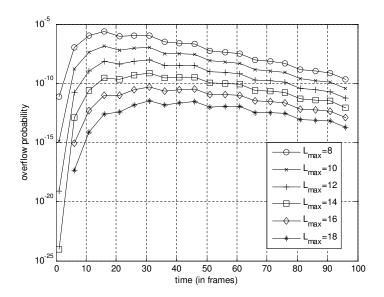

|              | 6.7  | Perfori   | mance Analysis                     | 165 |

|              | 6.8  | Conclu    | sion                               | 169 |

| Chapter 7    | Cond | clusions  |                                    | 171 |

| Appendix A   | Proo | of of The | eorem 3                            | 173 |

| Bibliography |      |           |                                    | 178 |

## LIST OF FIGURES

| Figure 1.1:             | Router architecture                                                                                             | 1<br>7 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|--------|

| Figure 1.2: Figure 1.3: | A three-stage pipeline with three concurrent jobs                                                               | 8      |

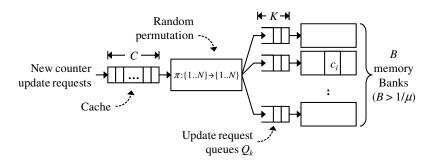

| Figure 2.1:             | Memory architecture for randomized DRAM-based counter schemes.                                                  | 22     |

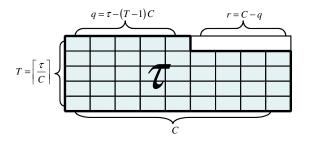

| Figure 2.2: Figure 2.3: | Relationship of $q$ , $r$ , $T$ and $\tau$                                                                      | 36     |

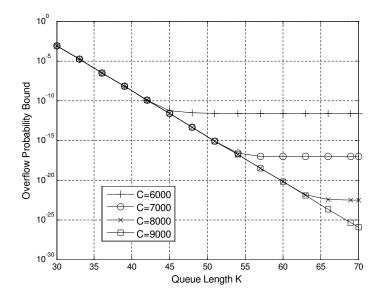

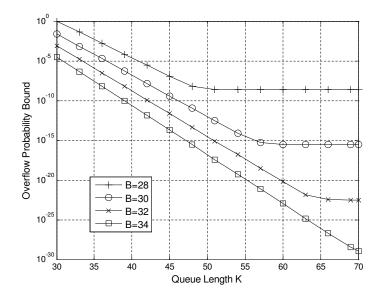

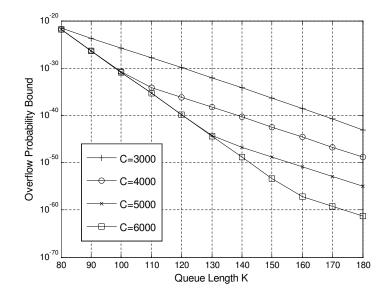

| Figure 2.4:             | Overflow probability bounds as a function of request queue size $K$ with $\mu = 1/16$ and $B = 32$              | 38     |

| Figure 2.5:             | Overflow probability bounds as a function of the number of memory banks $B$ with $\mu = 1/16$ and $C = 8000$    | 39     |

| Figure 2.6:             | Overflow probability bounds as a function of queue size $K$ with $\mu = 1/12$ and $B = 32$                      | 40     |

| Figure 2.7:             | Overflow probability bounds as a function of number of memory banks $B$ with $\mu = 1/12$ and $C = 4000$        | 41     |

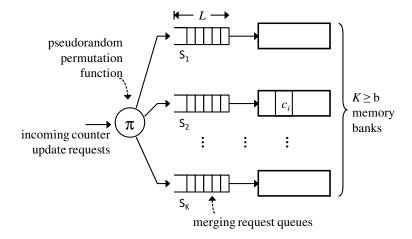

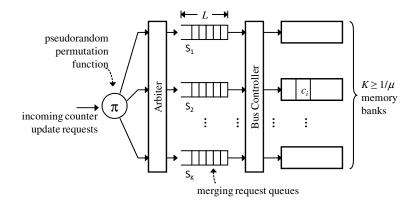

| Figure 3.1:             | Statistics counter array architecture                                                                           | 49     |

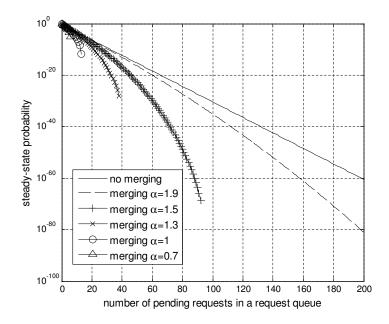

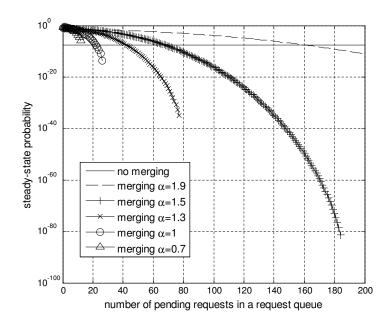

| Figure 3.2:             | Steady-state probability for merging request queue under heavy-tailed traffic with $b = 16$ and $K = 32$ banks  | 61     |

| Figure 3.3:             | Steady-state probability for merging request queues under heavy-tailed traffic with $b = 16$ and $K = 16$ banks | 62     |

| Figure 3.4:             | Statistics counter array with shared request queues                                                             | 64     |

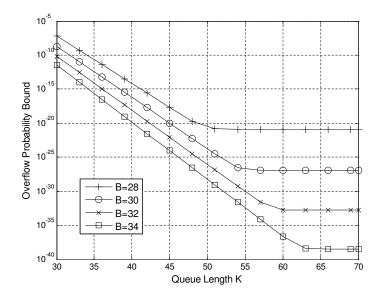

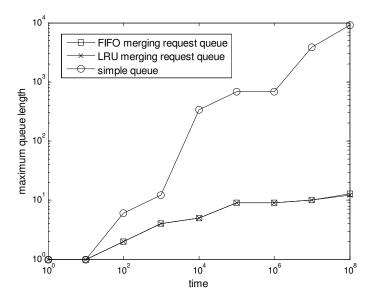

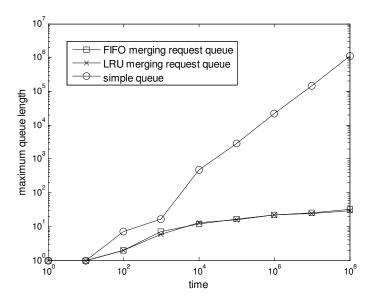

| Figure 3.5:             | Maximum queue length, $K = 32$ , USC trace                                                                      | 66     |

| Figure 3.6:             | Maximum queue length, $K = 16$ , USC trace                                                                      | 67     |

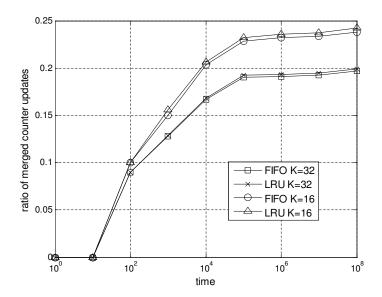

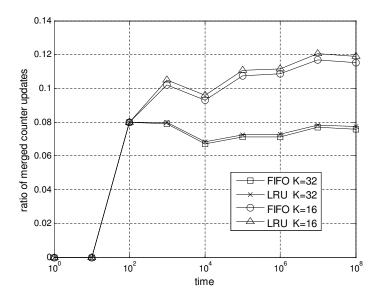

| Figure 3.7:             | Ratio of merged counter updates, USC trace                                                                      | 68     |

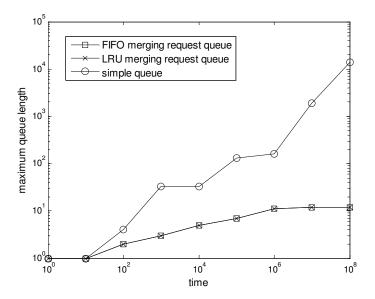

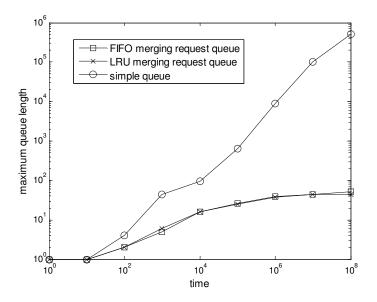

| Figure 3.8:             | Maximum queue length, $K = 32$ , UNC trace                                                                      | 69     |

| Figure 3.9:             | Maximum queue length, $K = 16$ , UNC trace                                                                      | 70     |

| Figure 3.10:            | Ratio of merged counter updates, UNC trace                                                                      | 71     |

| Figure 4.1:             | SRAM emulation of memory systems for network processing                                                         | 83     |

| Figure 4.2:             | Basic memory architecture                                                                                       | 84     |

| Figure 4.3:             | Extended memory architecture                                                                                    | 87     |

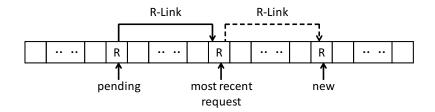

| Figure 4.4:             | R-link for read operations                                                                                      | 90     |

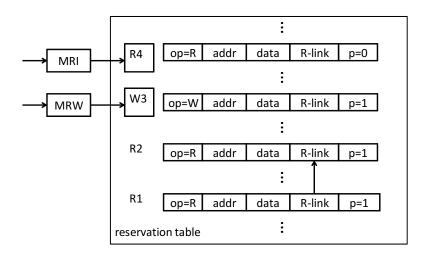

| Figure 4.5:             | Reservation table snapshot                                                                                      | 91     |

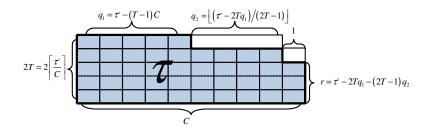

| Figure 4.6:             | Relationship of $q_1, q_2, r, T$ and $\tau'$                                                                    | 96     |

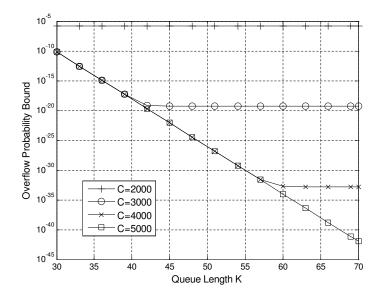

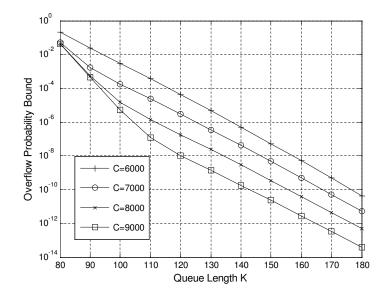

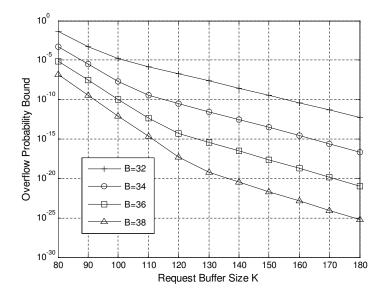

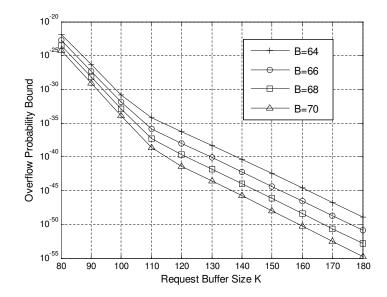

| Figure 4.7:             | Overflow probability bound as a function of request buffer size $K$                                             | 101    |

| Figure 4.8:             | Overflow probability bound as a function of request buffer size $K$                                             | 102    |

| Figure 4.9:  | Overflow probability bound as a function of number of memory |

|--------------|--------------------------------------------------------------|

|              | banks <i>B</i> with $\mu = 1/10$ and $C = 8000$              |

| Figure 4.10: | Overflow probability bound as a function of number of memory |

|              | banks <i>B</i> with $\mu = 1/10$ and $C = 4000$              |

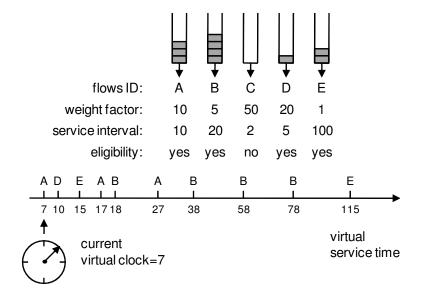

| Figure 5.1:  | Example of weighted round robin (WRR) service schedules 112  |

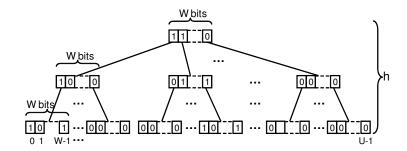

| Figure 5.2:  | Data structure of a PI with $h = 3$ levels                   |

| Figure 5.3:  | Example of a successor(0) operation in a CPI                 |

| Figure 5.4:  | Example of a successor(0) operation in a pCPI                |

| Figure 5.5:  | Flow graph of successor(i) operation in a pCPI               |

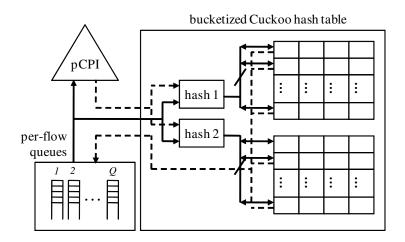

| Figure 5.6:  | pCPI for per-flow queue scheduling using hash tables         |

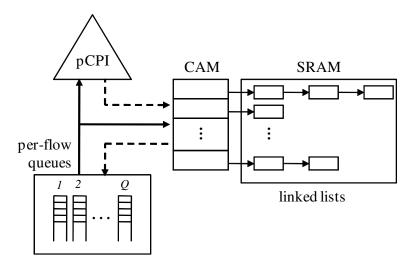

| Figure 5.7:  | pCPI for per-flow queue scheduling using CAM                 |

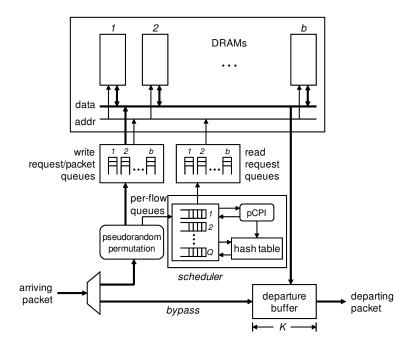

| Figure 5.8:  | Per-flow scheduling for large packet buffers using pCPI 130  |

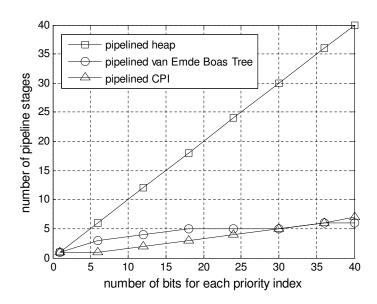

| Figure 5.9:  | Number of pipeline stages in three data structures           |

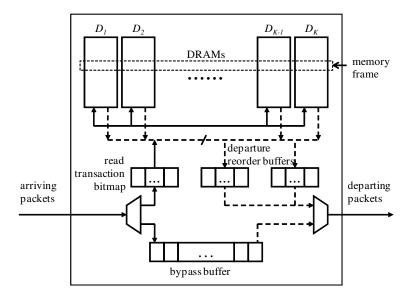

| Figure 6.1:  | Deterministic frame-sized packet buffer architecture         |

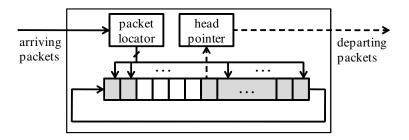

| Figure 6.2:  | Bypass buffer architecture                                   |

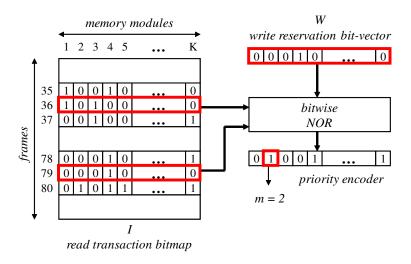

| Figure 6.3:  | DRAM selection logic for frame-sized packet buffer           |

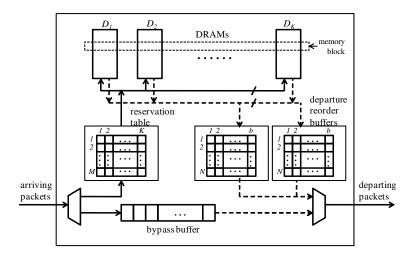

| Figure 6.4:  | Deterministic block-sized packet buffer architecture         |

| Figure 6.5:  | DRAM selection logic for block-sized packet buffer           |

| Figure 6.6:  | Randomized block-sized packet buffer system architecture 16  |

| Figure 6.7:  | Overflow probability for a write request queue               |

## LIST OF TABLES

| Table 2.1:               | Comparison of different schemes for a reference configuration with 16 million 64-bit counters. For our method, $K = 50$ , $B = 32$ , and $C = 7000$ | 42  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1:               | Comparison of different schemes for a reference configuration with 16 million 64-bit counters. For our method, $K=32$ and $L=20.$                   | 72  |

| Table 4.1:               | Comparison of different schemes for a reference configuration with 16 million addresses of 40 bytes data, $\mu = 1/10$ , $B = 32$ , and $C = 8000$  | 104 |

| Table 5.1:<br>Table 5.2: | Operations supported by a succinct priority indexing structure Sizes of bucketized Cuckoo hash tables to store 256 K keys                           |     |

| Table 6.1:               | SRAM sizes (in MB) for different N with a line rate of 40 Gb/s for a deterministic block-sized packet buffer                                        |     |

| Table 6.2:               | SRAM sizes (in MB) for different <i>N</i> with line rate at 100 Gb/s for deterministic block-sized packet buffer                                    | 166 |

| Table 6.3:               | Comparison of SRAM size requirements                                                                                                                |     |

| Table 6.4:               | SRAM requirement comparison with a prefetching-based packet                                                                                         |     |

| Table 6.5:               | buffer                                                                                                                                              |     |

| Table 6.5:               | Comparison of randomized packet buffer schemes                                                                                                      | 100 |

#### **ACKNOWLEDGEMENTS**

First and foremost, I owe my deepest gratitude to my advisor, Professor Bill Lin, who has supported me throughout my graduate study with both wisdom and encouragement. He is the one who guided me in my research projects, inspired me with his keen intuitions and logical thinking, and offered me help when there was turmoil in my life.

I give my thanks to my coauthors, Professor Jun Xu and his students Haiquan Zhao and Nan Hua from Georgia Institute of Technology for their help and contributions towards this dissertation. I will always remember the delightful discussions with Professor Xu on work and life. I really appreciate the help from Haiquan on both research projects and my career. My lifetime friendship with Nan will always be with me.

I thank my dissertation committee members, Professor Pamela C. Cosman, Professor Sujit Dey, Professor Rajesh K. Gupta, Professor Andrew B. Kahng, and Professor Tajana S. Rosing, for their insightful comments and advice.

I thank my internship mentors Sailesh Kumar and William Lynch at Huawei Technologies (USA), and Rong Pan and Flavio Bonomi at Cisco Systems, from whom I gained valuable industry experience. I thank the friends I made during my internships, Bin Xiao, Deming Liu, Haoyu Song, Wei Cao, Zhen Chen, Hengwen Tong, Ken Yi, Rongfeng Hong, Joji Philip, Xiangyang Zhang, Hongbo Yang, Jifei Song, Wumao Chen, Patrick Liu, Zhaoming Hu, and Fei Xu at Huawei Technologies (USA), and Michele Caramello, Chiara Piglione, and Mei Wang at Cisco Systems.

I would also like to thank my colleagues and friends at UCSD, especially Rohit Ramanujam, Shan Yan, Jerry Chou, Ting-Lan Lin, Chia-Wei Chang, Junsheng Han, Zheng Wu, Seyhan Karakulak, Rathinakumar Appuswamy, Amir Hadi Djahanshahi, and Abhijeet Bhorkar for providing me with an enjoyable research and learning environment.

Lastly but most importantly, I thank my parents, Liquan Wang and Xiangfen Zhang, for their love and sacrifice that made everything possible. I would have been nothing without them in every conceivable way, and to them I dedicate this dissertation.

Chapter 2, in full, is a reprint of the material as it appears in the following pub-

### lications:

- Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "DRAM-Based Statistics Counter Array Architecture with Performance Guarantee", IEEE/ACM Transactions on Networking (ToN), 2011.

- Haiquan (Chuck) Zhao, Hao Wang, Bill Lin, and Jun (Jim) Xu, "Design and Performance Analysis of a DRAM-based Statistics Counter Array Architecture", ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS), Princeton, NJ, October 19-20, 2009.

- Bill Lin, Jun (Jim) Xu, Nan Hua, Hao Wang, and Haiquan (Chuck) Zhao, "A Randomized Interleaved DRAM Architecture for the Maintenance of Exact Statistics Counters", ACM Special Interest Group on Performance Evaluation (SIGMET-RICS), Seattle, WA, June 15-19, 2009.

The dissertation author was the primary investigator and author of the papers.

Chapter 3, in part, has been submitted for publication of material as it may appear in the IEEE Transactions on Parallel and Distributed Systems, Hao Wang, Bill Lin, and Jun (Jim) Xu, "Robust Statistics Counter Arrays with Interleaved Memories". The dissertation author was the primary investigator and author of the paper.

Chapter 4, in part, is a reprint of the material as it appears in the following publications:

- Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "Robust Pipelined Memory System with Worst Case Performance Guarantee", *IEEE Transactions* on Computers (TC), 2011.

- Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "Design and Analysis of a Robust Pipelined Memory System", *IEEE International Conference on Computer Communications (INFOCOM)*, San Diego, CA, March 15-19, 2010.

The dissertation author was the primary investigator and author of the papers.

Chapter 5, in part, is a reprint of the material as it appears in the following publications:

- Hao Wang and Bill Lin, "Per-flow Queue Scheduling with Pipelined Counting Priority Index", *IEEE Symposium on High-Performance Interconnects (HOTI)*, Santa Clara, CA, August 24-26, 2011.

- Hao Wang and Bill Lin, "Succinct Priority Indexing Structures for the Management of Large Priority Queues", *IEEE International Workshop on Quality of Service (IWQoS)*, Charleston, SC, July 13-15, 2009.

Chapter 5, in full, has been submitted for publication of material as it may appear in IEEE Transactions on Parallel and Distributed Systems, Hao Wang and Bill Lin, "Perflow Queue Management with Succinct Priority Indexing Structures for High Speed Packet Scheduling". The dissertation author was the primary investigator and author of the papers.

Chapter 6, in part, is a reprint of the material as it appears in the following publications:

- Hao Wang and Bill Lin, "Block-Based Packet Buffer with Deterministic Packet Departures", *IEEE International Conference on High Performance Switching* (HPSR), Dallas, TX, June 13-16, 2010.

- Hao Wang and Bill Lin, "A Block-Based Reservation Architecture for the Implementation of Large Packet Buffers", ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS), Princeton, NJ, October 19-20, 2009.

The dissertation author was the primary investigator and author of the papers.

#### **VITA**

| 2005 | Bachelor of Engineering in Electronic Engineering, Tsinghua University, Beijing, P. R. China                           |

|------|------------------------------------------------------------------------------------------------------------------------|

| 2008 | Master of Science in Electrical Engineering (Communication Theory and Systems), University of California, San Diego    |

| 2008 | Intern, Advance Architecture and Research Group, Cisco Systems, San Jose, California                                   |

| 2011 | Intern, American Network Division, Huawei Technologies (USA), Santa Clara, California                                  |

| 2011 | Doctor of Philosophy in Electrical Engineering (Communication Theory and Systems), University of California, San Diego |

#### **PUBLICATIONS**

Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "DRAM-Based Statistics Counter Array Architecture with Performance Guarantee", *IEEE/ACM Transactions on Networking (ToN)*, 2011.

Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "Robust Pipelined Memory System with Worst Case Performance Guarantee", *IEEE Transactions on Computers* (*TC*), 2011.

Hao Wang and Bill Lin, "Per-flow Queue Scheduling with Pipelined Counting Priority Index", *IEEE Symposium on High-Performance Interconnects (HOTI)*, Santa Clara, CA, August 24-26, 2011.

Hao Wang and Bill Lin, "Designing Efficient Codes for Synchronization Error Channels", *IEEE International Workshop on Quality of Service (IWQoS)*, San Jose, CA, June 5-7, 2011.

Hao Wang and Bill Lin, "Block-Based Packet Buffer with Deterministic Packet Departures", *IEEE International Conference on High Performance Switching (HPSR)*, Dallas, TX, June 13-16, 2010.

Hao Wang, Haiquan (Chuck) Zhao, Bill Lin, and Jun (Jim) Xu, "Design and Analysis of a Robust Pipelined Memory System", *IEEE International Conference on Computer Communications (INFOCOM)*, San Diego, CA, March 15-19, 2010.

Hao Wang and Bill Lin, "A Block-Based Reservation Architecture for the Implementation of Large Packet Buffers", *ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS)*, Princeton, NJ, October 19-20, 2009.

Haiquan (Chuck) Zhao, Hao Wang, Bill Lin, and Jun (Jim) Xu, "Design and Performance Analysis of a DRAM-based Statistics Counter Array Architecture", *ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS)*, Princeton, NJ, October 19-20, 2009.

Hao Wang and Bill Lin, "Succinct Priority Indexing Structures for the Management of Large Priority Queues", *IEEE International Workshop on Quality of Service (IWQoS)*, Charleston, SC, July 13-15, 2009.

Bill Lin, Jun (Jim) Xu, Nan Hua, Hao Wang, and Haiquan (Chuck) Zhao, "A Randomized Interleaved DRAM Architecture for the Maintenance of Exact Statistics Counters", *ACM Special Interest Group on Performance Evaluation (SIGMETRICS)*, Seattle, WA, June 15-19, 2009.

Hao Wang and Bill Lin, "Pipelined van Emde Boas Tree: Algorithms, Analysis, and Application", *IEEE International Conference on Computer Communications (INFOCOM)*, Anchorage, AK, May 7-11, 2007.

Hao Wang and Bill Lin, "On the Efficient Implementation of Pipelined Heaps for Network Processing", *IEEE Global Communications Conference (GLOBECOM)*, San Francisco, CA, November 27-December 1, 2006.

Hao Wang, Bill Lin, and Jun (Jim) Xu, "Robust Statistics Counter Array with Interleaved Memories", *IEEE Transactions on Parallel and Distributed Systems (TPDS)*, under review.

Hao Wang and Bill Lin, "Efficient Channel Codes for Synchronization Error Correction", *IEEE Transactions on Communications (TCOM)*, under review.

Hao Wang and Bill Lin, "Per-flow Queue Management with Succinct Priority Indexing Structures for High Speed Packet Scheduling", *IEEE Transactions on Parallel and Distributed Systems (TPDS)*, under review.

#### ABSTRACT OF THE DISSERTATION

# Designing Network Traffic Managers with Throughput, Fairness, and Worst-case Performance Guarantees

by

### Hao Wang

Doctor of Philosophy in Electrical Engineering (Communication Theory and Systems)

University of California, San Diego, 2011

Professor Bill Lin, Chair

On the Internet, network routers are typically implemented to provide strategic controls over the growing demands on limited and expensive bandwidth for an increasingly diverse traffic spectrum. A router consists of two major components: a set of switch fabric and multiple linecards. The functionalities of a linecard can be categorized into three parts: packet classification, statistics accounting, and packet scheduling. Packet classification includes functionalities such as routing table lookup, admission control, and deep packet inspection. Statistics accounting is implemented to store essential information such as flow statistics and network counting sketches, for the purpose of traffic monitoring and traffic management. Packet scheduling includes functionalities

such as packet buffering, packet shaping, rate control, and hierarchical queue management. Sophisticated algorithms have been developed to improve the throughput and fairness on the network, however, the costs of implementing the new algorithms constantly outweigh their performance gains. This dissertation focuses on bridging the gap between advanced algorithms and their implementations in real-world network equipments by adopting a throughput- and fairness-driven design of network traffic managers which incorporate most of the functionalities of statistics accounting and packet scheduling, while providing worst-case performance guarantees for the whole router system. First, we explore parallelism to design high throughput statistics counter arrays that are robust against adversarial traffic. Second, we develop robust pipelined memory systems with worst-case performance guarantees for network processing. In our new memory systems, memory operations are finished within a fixed delay, which greatly simplifies the designs of network processors. Third, we present novel succinct priority index data structures that can be implemented for scheduling packets maintained in a large number of priority queues at line rate, which is essential in providing quality-ofservice for per-flow queueing. Last, we show several reservation-based packet buffer architectures with interleaved memories that take advantage of the known packet departure times to achieve simplicity and determinism. They are scalable to growing packet storage requirements in routers to provide fine-grained per-flow queue buffering, while matching increasing line rates. All these approaches significantly improve the overall system throughput while providing better fairness, quality-of-service and worst-case performance guarantees over existing solutions.

# Chapter 1

# Introduction

# 1.1 Network Traffic Management

Network traffic management has been the focus of research in the networking community in the past decade. The performance of a network is typically measured by its throughput, fairness, quality-of-service (QoS), reliability, response time, latencies, etc. Network traffic management transforms the network into a manageable source. It includes essential functionalities to provide QoS guarantees for millions of flows on the network at the line rate, to buffer packets at the line rate in order to cope with packet retransmissions and network congestions, and to maintain flow statistics to provide support for network accounting, network planning, network forecasting, security monitoring, and many other features.

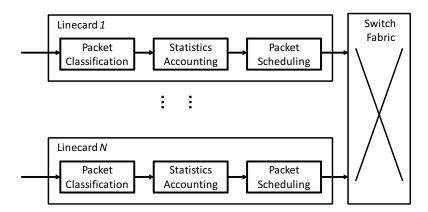

Figure 1.1: Router architecture.

The growing demands on limited and expensive bandwidth for an increasingly diverse traffic spectrum require strategic controls, which are typically implemented in network routers. The architecture of a typical router is shown in Figure 1.1. A router consists of two major components: a set of switch fabrics and multiple linecards. There have been extensive research efforts on the designs and implementations of switch fabrics [4, 15–17, 47, 56, 62, 69, 93] in order to provide high throughput in sending packets from input linecards to their destination output linecards. In general, current switch fabric designs can be categorized into two groups. One group includes the designs with a centralized arbiter configuring the interconnection of linecards at any instant of time to optimize the number of packets that can be sent across the switch fabric, which is essentially solving a matching problem. Various algorithms have been proposed to solve the matching problem on a switch fabric, such as output scheduling [69], wavefront arbiter (WFA) [93], parallel iterative matching (PIM) [4], and iSLIP [62]. The other group includes the designs without a centralized arbiter, where load-balancing techniques are typically deployed to better utilize the links on a switch fabric. Load-balanced routers are first proposed in [15, 16] which do not require a centralized arbiter unit to make matching decisions. In general, they suffer from the problem that packets sent through the switch fabric may be miss-sequenced, which would dramatically degrade the performance for TCP traffic by causing excessive retransmissions [2]. Many load-balance router extensions have been proposed to provide for in-order packet departures, such as the full-frame-first switch [47], the mailbox switch [17], and the concurrent matching switch [56]. State-of-the-art switch fabric technologies are mature enough so that various merchant chips have been built to implement these algorithms.

Inside a linecard, there are three major components provided: packet classification, statistics accounting, and packet scheduling. Packet classification includes functionalities such as access control list [55,75], routing table lookup [61,92], admission control [25,103], and deep packet inspection [23,53,104], which have all been well studied and widely deployed in network routers. This dissertation focuses on the other two components, statistics accounting and packet scheduling, which are essential for network traffic management.

### 1.1.1 Statistics Accounting

Statistics accounting is essential in network performance measurement, router management, intrusion detection, traffic engineering, and data streaming management. After a packet is processed by the packet classification module, its related information such as flow record and packet size will be recorded by the statistics accounting module. Statistics counter arrays are typically implemented to store the information for statistics analysis. For example, by counting the total size of the packets with the same flow record, it is possible to study the network traffic pattern, distinguish heavy users, and quickly identify network abnormalities such as a virus exploitation. The QoS provided by the traffic manager also relies heavily on the information recorded in the statistics counters. For example, counters are essential in providing committed access rate (CAR) support, which includes the committed information rate (CIR) and the peak information rate (PIR) statistics, so that a traffic manager can offer differentiated services to different flows based on the service level agreements (SLA) of their fair-share bandwidth and the amount of bandwidth they are actually utilizing. Counters are implemented to keep track of the leftover bandwidth for each specific type of traffic, which can be implemented at flow, user group, virtual queue, port, or other service levels. For the packets belonging to the same traffic type, the corresponding counter values will be decremented according to arriving packet sizes to reflect the leftover bandwidth. On the other hand, the counter values need to be incremented periodically to reflect the fair-share bandwidth allocated to that traffic type for the next service period. It is easy to see that the bandwidth can be more accurately managed if the service period is made arbitrarily small and the amount of increments to the counters in each service period are reduced accordingly. Therefore, it is highly desirable to build counters that support both increment and decrement operations at high speed. Moreover, a practical counter array solution needs to be able to cope with any arbitrary incoming sequence of counter update requests. This is true especially for security applications such as intrusion detection where an adversary has incentives to compromise any performance guarantees provided by the statistics counter array system. The problem of efficiently maintaining a large number (say millions) of statistics counters that need to be updated at very high speeds (e.g. 40 Gb/s) has received considerable research attention in recent years [20, 36, 37, 59, 65, 76, 81, 87, 91, 108]. It proves too costly to store such large counter arrays entirely in static random access memory (SRAM) while dynamic random access memory (DRAM) is viewed as too slow for providing wirespeed updates at high line rates.

### 1.1.2 Packet Scheduling

The packet scheduling module includes functionalities such as managing the packets stored in a packet buffer, implementing a traffic shaper based on the SLA, and also scheduling packets for departure.

Network routers need to temporarily store a large number of packets in response to network congestion and retransmission. Packet buffers are constantly built into linecards on the commercial routers deployed at the center or edge of the network. When a packet arrives at a router, it will be stored in a packet buffer for a period of time which typically corresponds to the round-trip-time of the network. The common buffer sizing rule is that  $B = RTT \times C$ , where B is the size of the buffer, RTT is the average round-trip-time of a flow passing through the link, and C is the line rate [96]. At an average round-trip-time of 250 ms on the Internet, and a line rate of 100 Gb/s (100GE), it translates to a buffer size of 3.125 GB at each linecard. A packet buffer implemented with SRAM is clearly infeasible, since the state-of-the-art SRAM has a capacity of only about 32 Mb. On the other hand, there are typically millions of flows arriving at the router. Packets are necessarily aggregated in the packet buffer physically or logically according to the flows they belong to in order to provide for differentiated services. Later, these packets need to be retrieved from the corresponding flows when they are due for departure. On a 100 Gb/s link, a minimum sized packet of 64 bytes may arrive every 5 ns. In order to match the line rate, the corresponding packet insertion to the packet buffer has to be completed within this time frame. Also, a packet previously inserted into the packet buffer may need to be removed for departure within the same time frame. Current DRAM has a random access latency of about 32 ns, which makes a naïve DRAM implementation of the packet buffer too slow for the current and future line rates.

Based on the SLA, a traffic shaper makes use of the information collected by the statistics accounting module to manage the packets stored in a packet buffer. For example, if a flow is sending at a rate lower than its committed rate, the packets in the flow will not incur any further delay in the traffic shaper. However, if the flow is sending at a rate higher than its committed rate, the packets in the flow will experience a certain delay in order to effectively "smooth" the flow. If the flow is sending at a rate higher than the peak allowable rate, its packets will be labeled accordingly so that they can be dropped or processed at a much lower priority by the packet scheduling module. The information collected by the statistics accounting module and the updated information from the traffic shaper need to be stored in a memory system that is robust against adversarial attacks, while providing high throughput to meet the ever-increasing line rate. Many other network applications also require wirespeed accesses to large data structures or a large amount of packet and flow-level data, such as routing table lookups, admission control, and deep packet inspection, which all require memory systems specialized for network processing. It is essential for the memory systems of a router to be able to support both read and write accesses to such data at link speeds. As link speeds continue to increase, router designers are constantly grappling with the necessary tradeoffs between the speed and cost of SRAM and DRAM. The capacity of SRAMs is woefully inadequate in many cases and it generally proves too costly to store large data structures entirely in SRAM, while DRAM is too slow for providing wirespeed updates at high line rates.

In the advanced scheduling of per-flow queues with QoS requirements, priority queues have received the most attention. Different flows may have different QoS requirements that correspond to different data rates, end-to-end latencies, and packet loss rates. A single queue cannot satisfy the service requirement since it only supports first-come-first-served policy. In order to achieve differentiated service guarantees, per-flow queueing is necessarily in advanced high-performance routers to manage packets for different flows in separate logical queues. Scheduling algorithms are required to decide the order of service for per-flow queues at line rate. Most of the advanced scheduling techniques are based on assigning deadline timestamps to packets depending on their urgency, and on servicing flows in the earliest-deadline-first order. This earliest-deadline-first scheduling approach can be facilitated using a priority queue. Scalable priority queue implementation requires solutions to two fundamental problems. The

first is to sort queue elements in real-time at ever increasing line speeds. The second is to effectively maintain a huge number of packets upon packet arrival and schedule them on time for departure.

In general, the advancement of network processor designs and faster memory systems make the current network equipments more capable than their predecessors in processing speed, power efficiency, and latency. However, the performance gains are easily overshadowed by the growing demands pushed by the ever-increasing line rate. Sophisticated algorithms have been developed to provide for improved throughput or fairness on the network. Many of the algorithms, however, are too complex to be implemented in any commercially feasible system, or the costs of implementing them constantly outweigh the benefits of the performance improvements. This dissertation aims at bridging the gap between advanced algorithms and their implementations in real-world network systems in order to build network traffic managers with high throughput, better fairness, and worst-case performance guarantees.

# 1.2 Techniques for Providing Throughput, Fairness, and Worst-case Performance Guarantees

There are several key techniques adopted in this dissertation to improve the throughput, fairness, and worst-case performance of traffic managers.

# 1.2.1 Pipelined Architectures

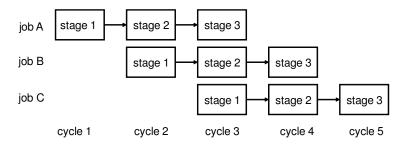

The principle of pipelining has been a major architectural attribute of current computer systems, which all have pipeline processing capabilities in the form of internally pipelined instruction and arithmetic units or in the form of pipelined special purpose functional units [77]. Network equipments can benefit from pipelining as well to achieve higher throughput without reducing the latency of each operation by dividing sequential processes into subprocesses, each of which can be executed efficiently on a special dedicated module. The higher throughput is achieved by arranging the special dedicated modules to operate concurrently. An example of a three-stage pipeline with

three concurrent jobs is shown in Figure 1.2. Even though each job shown in the figure takes three cycles to finish, the amortized time complexity for the pipeline is only one cycle when it is running at full capacity.

**Figure 1.2**: A three-stage pipeline with three concurrent jobs.

Pipelined architecture is the key technique to achieving high throughput implementation of priority queues for per-flow scheduling. On the Internet with millions of concurrent flows, a priority queue implementation needs to locate the packet with the earliest departure time for service at line rate among all flows. In the worst case with minimum size ethernet packets, as many as 150 million packets need to be scheduled for departure in every second on a 100 Gb/s link. As the line rate increases, the throughput of the packet scheduler needs to be increased accordingly to accommodate the worst-case scenario where all the packets are of the smallest size. Such a high throughput is only achievable with pipelined architectures.

# 1.2.2 Load-balancing and Parallelism

Load-balancing and parallelism have been widely adopted in the networking area, such as in the design of load-balanced routers [15, 16]. Parallelism refers to the practice of using multiple slow systems to match the behaviors of a much faster system in terms of throughput, fairness, and worst-case performance. Load-balancing refers to the practice of distributing work among slow systems so that the work-load to different systems are evenly distributed. Efficient and effective load-balancing algorithms and techniques are keys to building high performance and robust parallel systems with worst-case performance guarantees which can mimic the behavior of a faster system. Load-balancing and parallelism will be applied extensively in this dissertation to provide both

high throughput and guaranteed worst-case performance for statistics counter arrays, robust network memory systems, and also for high speed packet buffers.

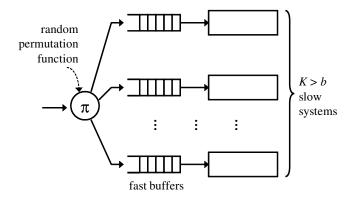

Figure 1.3: A parallel system architecture.

Figure 1.3 shows the architecture of a parallel system consisting of K slow systems and K fast buffers. Assume that a fast system is b times faster than each of the slow systems, Then by designing K > b, the parallel system potentially provides a higher throughput than the faster system. With an effective load-balancing algorithm which is implemented as a random permutation function  $\pi$ , the average work-load can be distributed into the K slow systems uniformly-at-random [14]. The K fast buffers are implemented to temporarily store the pending work to a slow system, since the work-load to different slow systems can never be perfectly equal due to randomness as exemplified by the Birthday Paradox [63]. Such a design is not robust, however, against worst-case work-load distributions, as there can be certain incoming work-load patterns that will cause more work to be sent to certain slow systems, causing system overflow by flooding the fast buffers. In this dissertation, we improve the parallel system design of Figure 1.3 by developing robust architectures for statistics counter arrays and network memory systems. We also build robust deterministic packet buffer systems with parallel memories by adding more constraints to the packet arrival processes.

# 1.3 Problem Statement and Contributions

In this section, we formally define the problem targeted in this dissertation:

How can one design traffic managers with throughput, fairness, and quality-of-service guarantees, while providing worst-case performance guarantees?

We solve this problem by improving the throughput, fairness, and worst-case performance of several components in a traffic manager. In particular, we design parallel statistics counter arrays with load-balancing algorithms that are robust against adversarial arriving counter updates while matching the line rate throughput. We design a pipelined memory system for network processing that is robust against even the worst-case memory access patterns. We design succinct priority indexing structures with pipelined architectures for the management of large priority queues at line rate. Also, we design reservation-based packet buffers that can guarantee deterministic packet departures with the help of both pipelined architectures and parallelism.

The main contributions of the dissertation are as follows:

• Robust Statistics Counter Arrays: We propose two DRAM based counter architectures that can effectively maintain wirespeed updates to large counter arrays. Both of them can harness the performance of modern commodity DRAM offerings by interleaving counter updates to multiple memory banks. The first proposed architecture makes use of a simple randomization scheme, a small cache, and small request queues to statistically guarantee a near-perfect load-balancing of counter updates to the DRAM banks. The statistical guarantee of the proposed randomized scheme is proven using a novel combination of convex ordering and large deviation theory. The second architecture is based on the observation that most flows on the Internet consist of multiple packets that are transmitted during a relatively short period of time, which are described as traffic bursts. This architecture makes use of a simple randomization scheme and a set of small, fully associative request queues to statistically guarantee a near-perfect load-balancing of counter updates to the memory banks. This architecture explores the benefits of traffic bursts to greatly reduce the size of the request queues while providing a diminishing overflow probability guarantee. We also develop a queueing model to show that, as long as the flow sizes are heavy-tailed distributed, the maximum request queue length is always bounded by a finite number. Our simulations confirm the effectiveness of the queueing model. Both of our proposed statistics

counter array architectures can support arbitrary increments and decrements at wirespeed, and can support different number representations, including both integer and floating point number representations. They can effectively maintain wirespeed updates to large counter arrays while providing a diminishing system overflow probability. The two statistics counter arrays are described in details in Chapter 2 and Chapter 3, respectively.

- Memory Systems for Network Processing: We propose a robust pipelined memory architecture that can emulate an ideal SRAM by guaranteeing with very high probability that the output sequence produced by the pipelined memory architecture is the same as the one produced by an ideal SRAM under the same sequence of memory read and write operations, except time-shifted by a fixed pipeline delay of Δ. Given a fixed pipeline delay abstraction, no interrupt mechanism is required to indicate when read data is ready or a write operation has completed, which greatly simplifies the use of the proposed solution. The design is based on the interleaving of DRAM banks together with the use of a reservation table that serves in part as a data cache. In contrast to prior interleaved memory solutions, this design is robust under all memory access patterns, including adversarial ones, which makes our robust pipelined memory suitable for network applications, particularly network security applications, where worst-case performance is the focus of concern. The details of this work are discussed in Chapter 4.

- Pipelined Architectures for Per-flow Scheduling: Priority queues are essential building blocks for implementing advanced per-flow disciplines and hierarchical QoS at high-speed network links. Scalable priority queue implementation requires solutions to two fundamental problems. The first is to sort queue elements in real-time at ever increasing line speeds (e.g., at OC-768 rates). The second is to store a huge number of packets (e.g., millions of packets). We present novel solutions by decomposing the problems into two parts, a succinct priority index in SRAM that can efficiently maintain a real-time sorting of priorities, coupled with a DRAM-based implementation of large packet buffers. In particular, we propose three related novel succinct priority index data structures for implementing high-speed priority indexes: a Priority-Index (PI), a Counting-Priority-Index

(CPI), and a pipelined Counting-Priority-Index (pCPI). We show that all three of these structures can be very compactly implemented in SRAM using only  $\Theta(U)$  space, where U is the size of the universe required to implement the priority keys (timestamps). We also show that the proposed priority index structures can be implemented very efficiently as well by leveraging hardware-optimized instructions that are readily available in modern 64-bit processors. The operations on the PI and CPI structures take  $\Theta(\log_W U)$  time complexity, where W is the processor word-length (i.e., W=64). Alternatively, operations on the pCPI structure take amortized constant time with only  $\Theta(\log_W U)$  pipeline stages (e.g., only 4 pipeline stages for U=16 million). Finally, we show the application of our proposed priority index structures for the scalable management of large packet buffers at line speeds. The pCPI structure can be implemented efficiently in high-performance network processing applications such as advanced per-flow scheduling with QoS guarantee. The details are presented in Chapter 5.

• Packet Buffers with Deterministic Packet Departure: Existing DRAM-based architectures for supporting linespeed queue operations can be classified into three categories: prefetching-based, randomization-based, and reservation-based. They are all based on interleaving memory accesses across multiple parallel DRAM banks for achieving higher memory bandwidths, but they differ in their packet placement and memory operation scheduling mechanisms. In this dissertation, we present efficient reservation-based packet buffer architectures with interleaved memories that take advantage of the known packet departure times to achieve simplicity and determinism. We develop three new packet buffer architectures: a deterministic frame-sized packet buffer, a deterministic block-sized packet buffer, and a randomized block-sized packet buffer. The number of interleaved DRAM banks required to implement the proposed packet buffer architectures is independent of the arrival traffic pattern, the number of active flows, and the number of priority classes, yet the proposed architectures can achieve the performance of an SRAM implementation with throughput and worst-case performance guarantee. In particular, the proposed block-based solution achieves an order of magnitude reduction in the total SRAM size compared to previous solutions. It is scalable to growing packet storage requirements in future routers while matching increasing line rates. The design, implementation, and evaluation of the proposed packet buffer architectures are described in Chapter 6.

# Chapter 2

# **Maintaining State Information with Millions of Counters**

# 2.1 Introduction

It is widely accepted that network measurements are essential for the monitoring and control of large networks. For tracking various network statistics (e.g. performing SNMP link counts) and for implementing various network measurements, router management, intrusion detection, traffic engineering, and data streaming applications, there is often the need to maintain very large arrays of statistics counters at wirespeed (e.g. many millions of counters for per-flow measurements [76, 87]). In general, each packet arrival may trigger the updates of multiple per-flow statistics counters, resulting in possibly tens of millions of updates per second. For example, on a 40 Gb/s OC-768 link, a new packet can arrive every 8 ns, and the corresponding counter updates need to be completed within this time frame. Large counters, such as 64 bits wide, are needed for tracking accurate counts even in short time windows if the measurements take place on high-speed links as smaller counters can quickly overflow. Additionally, a practical counter array solution has to be able to handle any arbitrary sequence including adversarial incoming sequences of counter addresses, i.e. indices, to be incremented because statistics counter arrays may often be used in security applications, such as intrusion detection, and in settings where an adversary has incentives to compromise the performance guarantees.

Although implementing large counter arrays in SRAM can satisfy the performance needs, the amount of SRAM required can be both infeasible and impractical. As reported in [108], real-world Internet traffic traces show that a very large number of flows can occur during a measurement period. For example, an Internet traffic trace from UNC has 13.5 million flows. Assuming 64 bits for each flow counter, 108 MB of SRAM would already be needed for just the counter storage, which is prohibitively expensive. Therefore, researchers have been actively seeking alternative ways to realize large arrays of statistics counters at wirespeed [20, 36, 37, 59, 65, 76, 81, 87, 91, 108].

Several designs of large counter arrays based on hybrid SRAM/DRAM counter architectures have been proposed [76, 81, 87, 108]. Their basic idea is to store some lower order bits (e.g. 9 bits) of each counter in SRAM, and all its bits (e.g. 64 bits) in DRAM. Increments are made only to these SRAM counters. When the values of the SRAM counters come close to overflowing, they are scheduled to be "flushed" back to the corresponding DRAM counters. These schemes significantly reduce the SRAM cost. In particular, the scheme by Zhao et al. [108] achieves the theoretically minimum SRAM cost of 4 to 5 bits per counter when the SRAM-to-DRAM access latency ratio is between 1/10 (4ns/40ns) and 1/20 (3ns/60ns). While this is a substantial reduction over a straightforward SRAM implementation, storing say 4 bits per counter in SRAM for 13.5 million flows would still require nearly 7 MB of SRAM, which is a significant amount and difficult to implement on-chip. Moreover, since the bounds on SRAM requirements for the hybrid SRAM/DRAM approaches are based on preventing SRAM counter overflows, the SRAM requirements are also dependent on the size of the increments. If a wide range of increments is needed, and *large* increments are possible, the possibility for a counter to overflow could occur much earlier, and more SRAM counter bits would be needed to compensate, resulting in yet larger SRAM requirements. On the other hand, in our counter array scheme we only need to increase the storage for several thousand entries. To maintain 16 million active counters, the size increase in our scheme is less than the traditional SRAM/DRAM schemes by more than 3 orders of magnitude. In addition, the existing hybrid SRAM/DRAM approaches do not support arbitrary decrements and are based on an integer number representation, whereas a *floating point number* representation may be needed in some applications [38, 106] to maintain values such as the entropies of data streams.

### 2.1.1 DRAM Can Be Plenty Fast

In this chapter, we challenge the main premise behind previous hybrid SRAM/DRAM architecture proposals. Their main premise is that DRAM accesses are too slow for wirespeed updates, though DRAMs provide plenty of storage capacity for maintaining exact counts for large arrays of counters. However, our main observation is that modern DRAM architectures have advanced architecture features [35,58,101,102] that can be exploited to make a DRAM solution practical. We propose DRAM-based counter architectures that allow for wirespeed updates to large counter arrays.

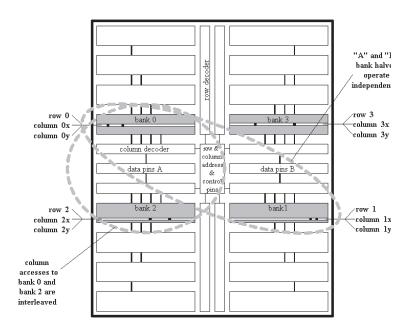

Motivated by a seemingly insatiable appetite for extremely aggressive memory data rates in graphics, multimedia, video game, and high-definition television applications, the memory semiconductor industry has continuously been driving aggressive roadmaps in terms of ever increasing memory bandwidths that can be provided at commodity pricing. For example, the Cell processor from IBM/Sony/Toshiba [32] uses two 32-bit channels of XDR memories [78] with an aggregated memory bandwidth of 25.6 GB/s. Using an approach called micro-threading [101], the XDR memory architecture provides internally 16 independent banks inside just a single DRAM chip, 256 memory banks across 16 DRAM chips that are typically packaged into a single memory module. Next generation memory architectures [79] are expected to achieve a data rate upwards of 16 GB/s on a single 16-bit channel, 64 GB/s on an equivalent dual 32-bit channel interface used by the Cell processor. This enormous amount of memory bandwidth can be shared or time-multiplexed by multiple network functions. The Intel IXP network processor [40] is another example of a state-of-the-art network processor that has multiple high-bandwidth memory channels. Besides XDR, other memory consortia have similar capabilities and advanced architecture features on their roadmaps as well, since they are driven by the same demanding consumer applications. For example, extremely high data efficiency can be achieved using DDR3 memories as well [102].

Although these modern high-speed DRAM offerings provide extraordinary memory bandwidths, the peak access bandwidths are only achievable when memory

locations are accessed in a *memory interleaving mode* to ensure that *internal memory bank conflicts* are avoided. Unlike graphics and video applications with mostly sequential memory access patterns, which are known to be friendly to memory interleaving, the conventional wisdom is that the random or even adversarial access nature of network measurement applications would *render interleaved access modes unusable*. For example, for XDR memories [78], a new memory operation could be initiated every 4 ns when the internal memory banks are interleaved, but a worst-case access latency of 40 ns is required for a read or a write operation if memory bank accesses are unrestricted.

# 2.1.2 Our Approach

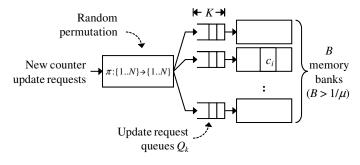

Our main idea is to randomly distribute the memory addresses to which consecutive counter indices are mapped across the memory banks so that a near-perfect balancing of memory access loads can be provably achieved, under both arbitrary and adversarial counter update patterns. Suppose the SRAM-to-DRAM random access latency ratio is  $\mu$ , e.g.  $\mu$  = 4ns/64ns = 1/16. The randomized counter scheme works by using  $B > 1/\mu$  DRAM banks and randomly distributing the array of counters across these DRAM banks so that when the loads of these memory banks are perfectly balanced, the worst-case load factor of any DRAM bank is  $1/(B\mu) < 1$ . In particular, we apply a random permutation function to the counter index to obtain a randomly permuted counter index, which is in turn mapped to a memory bank according to the traditional memory interleaving scheme in use.

The randomized scheme does not require extra DRAM. It works by ensuring that the memory load is evenly distributed when different counters are updated over time, *under arbitrary counter update sequences*. However, an adversary can conceivably overload a memory bank by sending traffic that would trigger the update of the same counter because these counter updates will necessarily be mapped to the same memory bank. This case can be easily handled through caching. By caching pending counter update requests, we can ensure that repeated updates to the same counter within a certain time window will not result in any new memory operations. Instead, the pending counter update request is simply modified to reflect the new counter update request.

While this architecture of randomization plus caching sounds simple and

straightforward, a key contribution of this chapter is a mathematical one: we prove that index randomization combined with a reasonably sized cache can handle with overwhelming probability arbitrary including adversarial counter update patterns without having overload situations as reflected by long queuing delays (to be made precise in Section 2.4). This result is a worst-case large deviation theorem in nature [71] because it establishes a bound on the largest/worst case value among the tail probabilities of having long queueing delays under all admissible including adversarial counter update patterns. In the course of proving this result, we establish a novel general methodology for establishing worst-case large deviation bounds. Worst-case large deviation bounds, such as ours are very hard to obtain because the parameter space of all admissible counter update patterns underlying the large deviation tail bound problem is gigantic. Although given a particular parameter setting, i.e., a particular counter update sequence, establishing the tail bound in our problem is straightforward through the Chernoff technique, enumerating this procedure over the entire parameter space is computationally impossible, and finding the maximum of such bounds appears to be analytically impossible as well through tractable optimization techniques.

Our methodology to overcome this difficulty is a novel combination of convex ordering and large deviation theory. To our surprise, we found that we are able to find a parameter configuration, i.e., a counter update sequence that dominates all other configurations by the convex order. Since the exponent function is a convex function, we are able to dominate the moment generating function (MGF) of queueing delays, which is a random variable, under all other parameter settings by the MGF under the worst-case parameter setting. We can then apply the Chernoff technique to this worst-case MGF to obtain very sharp tail bounds. Using this theoretical framework, we show that only very small queues on the order of K = 45 entries per request queue are required to ensure a negligible overflow probability (e.g. under  $10^{-14}$ ).

# 2.1.3 Summary of Contributions

We make several contributions in this work:

• We propose a DRAM-based counter architecture that can effectively maintain wirespeed updates to large counter arrays. As we shall see, our proposed counter

scheme can leverage the internal independent memory banks already available inside a modern DRAM chip without the expense of multiple parallel memory channels, thus making it very cost effective.

- We develop a novel mathematical methodology for establishing worst-case large deviation bounds. As one of its applications, we present a rigorous theoretical analysis on the performance of our proposed randomized counter architecture in the worst-case.

- We present concrete evaluations of our proposed scheme using the XDR memory architecture [78, 79, 101], which has 16 internal independent memory banks in each memory chip and 256 memory banks across 16 memory chips in a single memory module. We show that wirespeed performance can be achieved without the expense of multiple memory channels.

- Compared to existing hybrid SRAM/DRAM counter architectures [76, 81, 87, 108], our randomized counter solution offers three clear advantages. First, our solution can achieve the same update speeds to counters, without the need for a non-trivial amount of SRAMs for storing partial counts. Second, our solution can easily accommodate increments/decrements of any arbitrary integer (needed for counting bytes) or floating point values (needed in certain data streaming applications [38, 106]), while hybrid SRAM/DRAM counter architectures typically can only accommodate "increment by 1" efficiently. Finally, as we shall show in Section 2.5, our DRAM-based solution requires only a small amount of "control" SRAM, the size of which is *independent* of the number of counters being maintained. Therefore, this approach is scalable to future application scenarios in which vastly larger counter arrays are possible. This is in contrast to hybrid SRAM/DRAM architectures where the SRAM requirement grows linearly with the number of counters being maintained. Our solution only grows linearly in the DRAM requirement with respect to the number of counters, which is practical given the low cost of DRAM<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>As of this writing, 4GB of DRAM costs under \$20, over 200MB/\$.

#### 2.1.4 Outline of Chapter

The rest of the chapter is organized as follows. Section 2.2 outlines additional related work. Section 2.3 describes a proposed randomized counter architecture in details. Section 2.4 provides a rigorous analysis of the performance of our randomized counter architecture under the worst case memory access pattern. Section 2.5 presents evaluations of the proposed architecture. Finally, Section 2.6 concludes the chapter.

#### 2.2 Related Work

In this section, we outline prior work related to our problem. As already discussed in Section 2.1, the naïve approach of storing full counters in SRAM is prohibitively expensive. Although a hybrid SRAM/DRAM architecture [76, 81, 87, 108] significantly reduces the SRAM requirement, the amount of SRAM required for tracking a large number of counters (say in the tens of millions) is still substantial and difficult to implement on-chip.

Besides hybrid SRAM/DRAM architectures, several complementary SRAMbased approaches have also been proposed that aim to make feasible the storage of large counter arrays in SRAM through efficient representations. One category of approaches is approximate counting [20, 65, 91], which are all based on the basic idea invented by Morris [65]. Approximate counting keeps the cost low by sacrificing counter accuracy. The idea is to probabilistically increment a counter based on the current counter value. However, approximate counting in general has very large error margin when the number of bits per counter used is small, and possible estimation values are very sparsely distributed in the range of possible counts. Therefore, when the counter values are small, the estimation can cause very high relative errors (well over 100%). Thus this approach is only applicable to those network measurement and data streaming applications that can tolerate such inaccuracies. The approach may not be acceptable for those network accounting and data streaming applications where small counter values are important for the overall measurement accuracy. Other such systems include the NetFlow from Cisco [27], the filter-based accounting from Juniper [86], and the sample-and-hold solution [28].

A second approach is a counter architecture called counter braids [59], which was inspired by the construction of low-density parity-check codes which keeps track of the exact counts of all flows without remembering the association between flows and counters<sup>2</sup>. At each packet arrival, counter increments can be performed quickly by hashing the flow label to several counters and incrementing them. The counter values can be viewed as a linear transformation of flow counts, where the transformation matrix is the result of hashing all flow labels during a measurement epoch. In a way, counter braids are "more passive" than SRAM/DRAM hybrid architectures. Flow counts can be decoded through an iterative decoding process at the end of the measurement period. The decoding process incurs significantly longer delay than a DRAM access, and it can be processed off-line.

A third approach is based on an efficient variable-length counter representation called BRICK [37]. It uses a simple operator called rank-indexing to link together counter segments rather than using expensive memory pointers. This counter architecture has the advantage that it can support "active" counter applications in which individual counter values need to be retrieved at wirespeed. For such applications, this approach provides a much more efficient representation than a naïve SRAM implementation.

In all three above SRAM-based approaches, significant amounts of SRAM are still necessary for very large counter arrays (e.g. for tens of millions of counters). In contrast, our proposed solution stores all counters in DRAM only. We believe these approaches are complementary as they have different design tradeoffs. It is worth noting that general memory systems supporting arbitrary memory read and write accesses [1, 100] are applicable for the maintenance of large counter arrays. They are not as efficient, however, and incur large delays compared to memory systems specialized for this purpose.

Several packet buffer designs [43, 99] use interleaved DRAM banks, so that packets can be written to multiple DRAM banks following a certain order and later retrieved according to their departure times. Only one bank can be addressed in each cycle to avoid bank conflicts. Even though our counter array also explores DRAM inter-

<sup>&</sup>lt;sup>2</sup>Counter braids consider a more general problem that also addresses flow association.

leaving, the problems of managing statistics counters and buffering packets are fundamentally different. For packet buffer design, the goal is to find one DRAM bank entry among all banks in which to store an arriving packet so that it can be retrieved in time for departure. While for statistics counters, the counters are stored at fixed locations with a guarantee that any counter update requests can be successfully processed.

Finally, the idea of using DRAM interleaving to implement large counter arrays was first proposed in [57]. We extend that work considerably in this chapter by presenting a new mathematical framework for analyzing the behavior of such architectures under practical conditions, as detailed in Section 2.4. We also introduced a cache module in the architecture to combat adversarial counter update patterns, which adds considerably to the complexity of our analysis.

#### 2.3 Randomized Counter Architecture

In the past, memory interleaving has been successfully used for improving the performance of computer systems [58, 73, 80], for graphics or video intensive applications [101], and for implementing routing functions like high-performance packet buffers [89]. In this section, we describe how this technique can be employed for statistics counting.