# **UC San Diego**

# **UC San Diego Electronic Theses and Dissertations**

### **Title**

Physical Design and Technology Optimizations for Advanced VLSI Manufacturing

### **Permalink**

https://escholarship.org/uc/item/1fm1g9qx

### **Author**

Lee, Hyein

# **Publication Date**

2018

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Physical Design and Technology Optimizations for Advanced VLSI Manufacturing

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Hye In Lee

## Committee in charge:

Professor Andrew B. Kahng, Chair Professor Chung-Kuan Cheng Professor Ian A. Galton Professor Rajesh K. Gupta Professor Ryan Kastner

Copyright

Hye In Lee, 2018

All rights reserved.

| The dissertation of Hye In Lee is approved, and it is accept- |

|---------------------------------------------------------------|

| able in quality and form for publication on microfilm and     |

| electronically:                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

|                                                               |

| Chair                                                         |

University of California, San Diego

2018

# DEDICATION

To my family.

# TABLE OF CONTENTS

| Signature Pa    | .ge          |                                                                                                          |                                                                                                                                                                        |      |    | ٠   |      | •                                     |      |     | iii                                                                  |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|-----|------|---------------------------------------|------|-----|----------------------------------------------------------------------|

| Dedication .    |              |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | iv                                                                   |

| Table of Con    | itents .     |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | v                                                                    |

| List of Figur   | es           |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | vii                                                                  |

| List of Table   | s            |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | xii                                                                  |

| Acknowledg      | ments.       |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | xiv                                                                  |

| Vita            |              |                                                                                                          |                                                                                                                                                                        |      |    |     |      |                                       |      |     | xvi                                                                  |

| Abstract of the | he Diss      | ertation                                                                                                 |                                                                                                                                                                        |      |    |     |      |                                       |      |     | xviii                                                                |

| Chapter 1       | Intro<br>1.1 |                                                                                                          | Challenges in Advanced Technology Nodes  Challenges in Gate Sizing Optimization  Challenges in Placement Optimization  Challenges in Design-Technology Co-optimization | <br> |    |     | <br> |                                       | <br> |     | 1<br>2<br>2<br>4<br>4                                                |

|                 | 1.2          |                                                                                                          | hesis                                                                                                                                                                  |      |    |     |      |                                       |      |     | 5                                                                    |

| Chapter 2       | Gate 2.1     | _                                                                                                        | Optimizations for Advanced VLSI Technologies                                                                                                                           | try  | IC | De: | sig  | 1 C                                   | Con  | tex | 9<br>t 10<br>14<br>17<br>19<br>38<br>46                              |

|                 | 2.2          | Minim<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>Heuri<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5 | Related Work                                                                                                                                                           | nt   |    |     |      | · · · · · · · · · · · · · · · · · · · |      |     | 47<br>51<br>52<br>55<br>61<br>64<br>66<br>68<br>70<br>75<br>80<br>86 |

|                 | 2.4          | Ackno                                                                                                    | wledgments                                                                                                                                                             |      |    |     |      |                                       |      |     | 88                                                                   |

| Chapter 3    | Deta | niled Placement Optimizations for Advanced VLSI Technologies 90             |

|--------------|------|-----------------------------------------------------------------------------|

|              | 3.1  | Scalable Detailed Placement Legalization for Complex Sub-14nm Constraints 9 |

|              |      | 3.1.1 Related Work                                                          |

|              |      | 3.1.2 Our Approach                                                          |

|              |      | 3.1.3 Experimental Setup and Results                                        |

|              |      | 3.1.4 Conclusion                                                            |

|              | 3.2  | Vertical M1 Routing-Aware Detailed Placement for Congestion and Wirelength  |

|              |      | Reduction in Sub-10nm Nodes                                                 |

|              |      | 3.2.1 Related Work                                                          |

|              |      | 3.2.2 MILP-based Optimization                                               |

|              |      | 3.2.3 Overall Flow                                                          |

|              |      | 3.2.4 Experimental Setup and Results                                        |

|              |      | 3.2.5 Conclusion                                                            |

|              | 3.3  | Acknowledgments                                                             |

| Chapter 4    | Eval | luations of Design Enablements for Advanced VLSI Technologies               |

| •            | 4.1  | Evaluation of BEOL Design Rule Impacts Using an Optimal ILP-based De-       |

|              |      | tailed Router                                                               |

|              |      | 4.1.1 Related Work                                                          |

|              |      | 4.1.2 Optimal Routing Formulation                                           |

|              |      | 4.1.3 Empirical Studies                                                     |

|              |      | 4.1.4 Conclusion                                                            |

|              | 4.2  | Performance- and Energy-Aware Optimization of BEOL Interconnect Stack       |

|              |      | Geometry in Advanced Technology Nodes                                       |

|              |      | 4.2.1 Related Work                                                          |

|              |      | 4.2.2 Path-Based Simulation                                                 |

|              |      | 4.2.3 Block-Level Validation                                                |

|              |      | 4.2.4 Experimental Setup and Results                                        |

|              |      | 4.2.5 Conclusion                                                            |

|              | 4.3  | PROBE: A Placement, ROuting, Back-End-of-line Measurement Utility 17        |

|              |      | 4.3.1 Related Work                                                          |

|              |      | 4.3.2 Assessment of Design Enablements                                      |

|              |      | 4.3.3 Experimental Setup and Results                                        |

|              |      | 4.3.4 Additional Study of Routing Hotspot and Routing Failure 199           |

|              |      | 4.3.5 Conclusion                                                            |

|              | 4.4  | Acknowledgments                                                             |

| Chapter 5    | Sum  | nmary                                                                       |

|              |      |                                                                             |

| Bibliography |      |                                                                             |

# LIST OF FIGURES

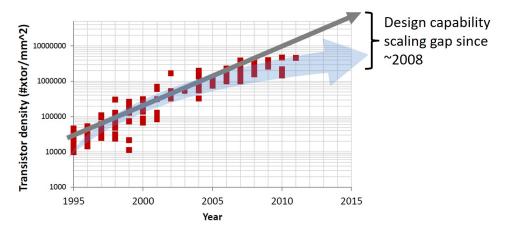

| Figure 1.1:  | Design capability gap [182][81]. The gray arrow shows the "available" density scaling, and the red squares show the "actual" density scaling, in MPU products                                                                                                                      | 2  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

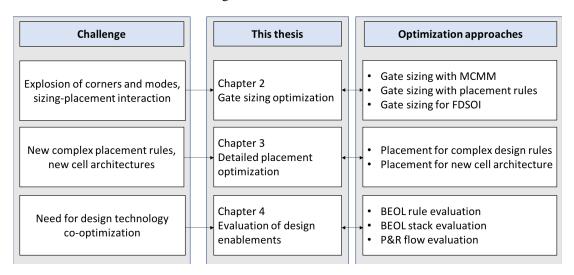

| Figure 1.2:  | Scope and organization of this thesis                                                                                                                                                                                                                                              | 6  |

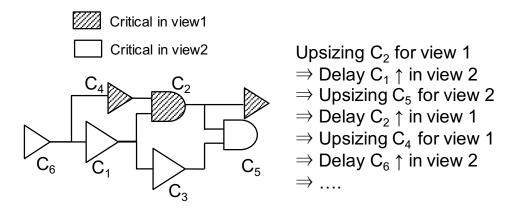

| Figure 2.1:  | Example showing a ping-pong situation during timing recovery for MCMM                                                                                                                                                                                                              | 18 |

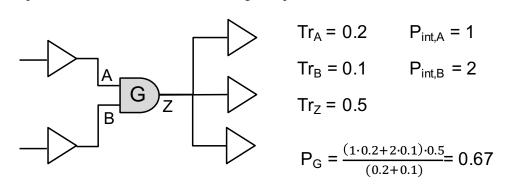

| Figure 2.2:  | Example internal power estimation of a 2-input cell                                                                                                                                                                                                                                | 27 |

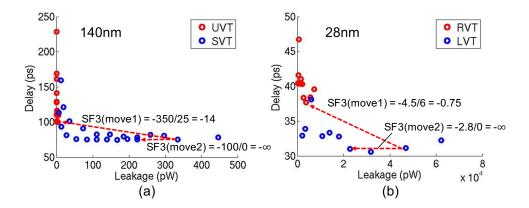

| Figure 2.3:  | Leakage versus delay of $V_t$ swapping and sizing in (a) $140nm$ (TT, $1.5V$ , $25^{\circ}C$ ) and (b) $28nm$ LP (TT, $1.0V$ , $25^{\circ}C$ )                                                                                                                                     | 30 |

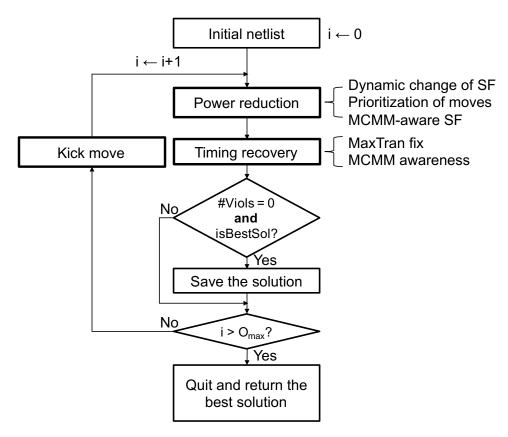

| Figure 2.4:  | Overview of the overall optimization flow.                                                                                                                                                                                                                                         | 33 |

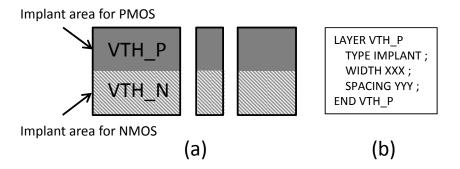

| Figure 2.5:  | (a) Illustration of implant layer regions in standard cells. (b) An example of an implant                                                                                                                                                                                          |    |

|              | layer rule in a LEF5.7 file.                                                                                                                                                                                                                                                       | 48 |

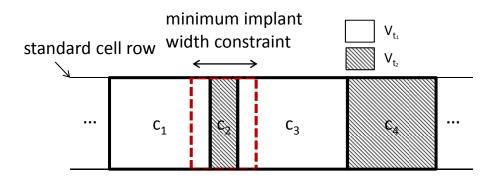

| Figure 2.6:  | An example of the minimum implant area violation. The dotted line indicates the minimum width constraint of the implant layer. The cell instance $c_2$ ( $V_{t_2}$ ) violates the constraint as it is narrow and sandwiched by two cells ( $c_1$ and $c_3$ ) that have a different |    |

|              | $V_t(V_{t_1})$                                                                                                                                                                                                                                                                     | 49 |

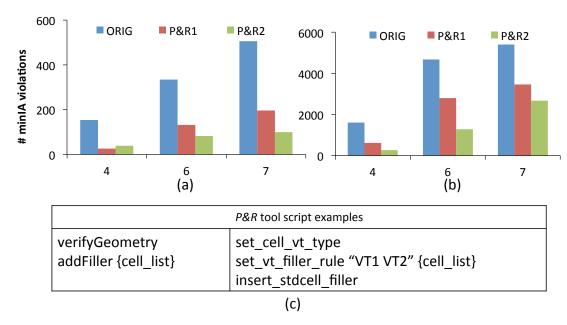

| Figure 2.7:  | Minimum implant area violation fix results from two commercial tools (P&R1 and                                                                                                                                                                                                     |    |

|              | P&R2) through filler cell insertion, for two testcases: (a) DMA and (b) AES. The                                                                                                                                                                                                   |    |

|              | x-axis shows the minimum implant width constraints in the number of grids. (c) The commands used for filler cell insertion flow.                                                                                                                                                   | 50 |

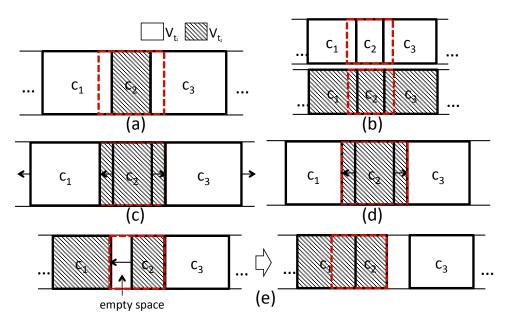

| Figure 2.8:  | Available fixing approaches for MinIA rule violations. A given violation, depicted                                                                                                                                                                                                 | 50 |

| 8            | in (a), can be fixed by using (b) $V_t$ -swapping, or (c) moving a neighbor cell, or (d)                                                                                                                                                                                           |    |

|              | downsizing a neighbor, or (e) moving the narrow cell                                                                                                                                                                                                                               | 55 |

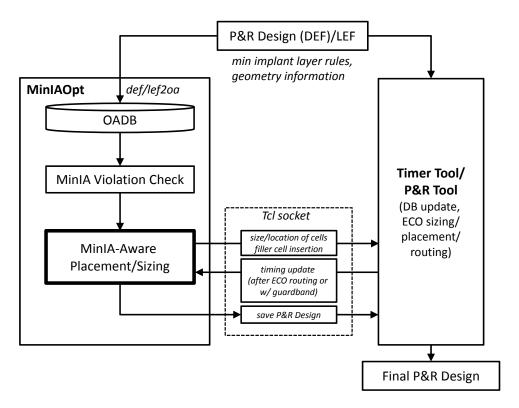

| Figure 2.9:  | Overall flow of our optimizer, <i>MinIAOpt</i>                                                                                                                                                                                                                                     | 61 |

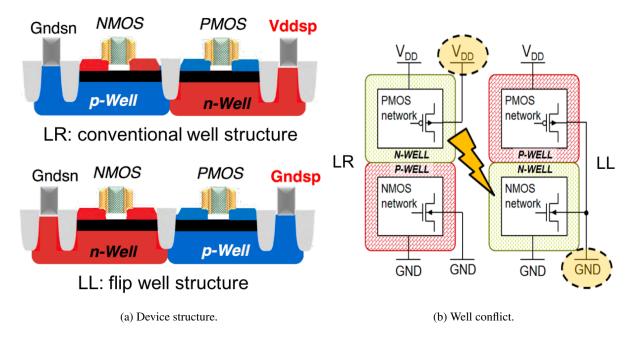

| Figure 2.10: | (a) The FDSOI device structure. (b) The LL and LR cells cannot be abutted due to                                                                                                                                                                                                   |    |

| E' 2.11.     | well bias conflicts [45]                                                                                                                                                                                                                                                           | 68 |

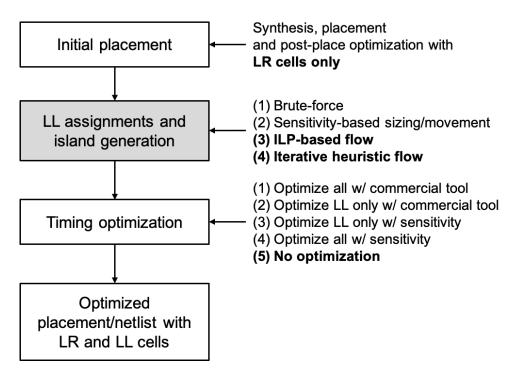

| Figure 2.11: | Overall flow, showing options explored in background studies. Superior flow options are shown in bold font                                                                                                                                                                         | 72 |

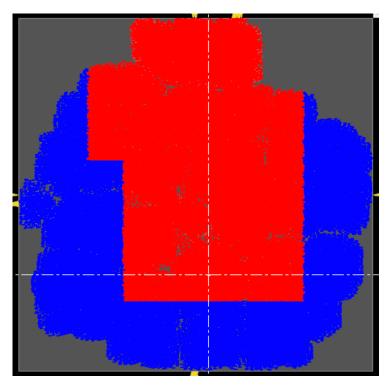

| Figure 2.12: | Island shape obtained by ILP-2 for the viterbi testcase in Enable1. LL regions are                                                                                                                                                                                                 | 12 |

| 115010 2.12. | highlighted in red                                                                                                                                                                                                                                                                 | 78 |

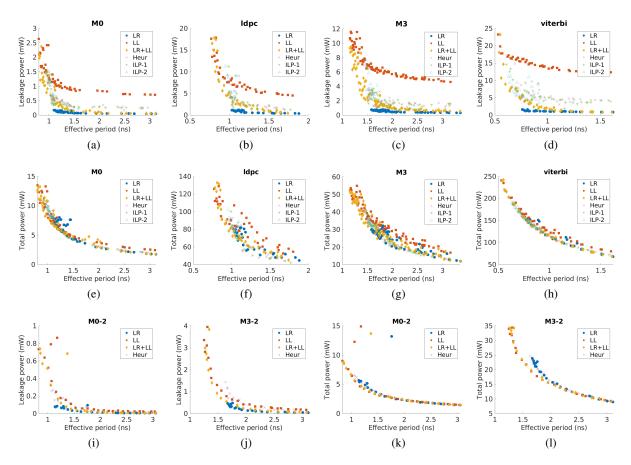

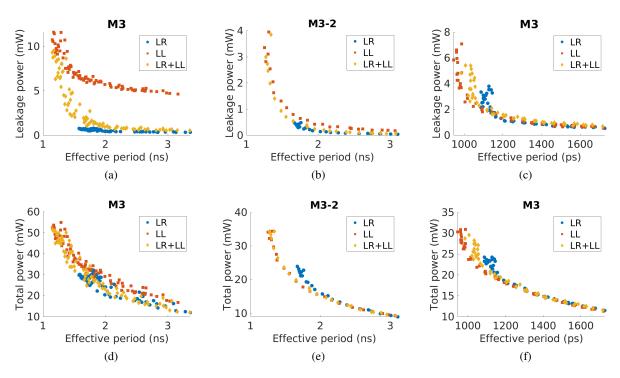

| Figure 2.13: | (a)-(d) Leakage power versus effective periods for the four designs implemented with                                                                                                                                                                                               |    |

|              | Enable1; (e)-(h) total power versus effective periods for the four designs implemented                                                                                                                                                                                             |    |

|              | with Enable1; (i)-(j) leakage and (k)-(l) total power versus effective periods for the                                                                                                                                                                                             |    |

| E' 0.1.1     | two designs implemented with Enable2                                                                                                                                                                                                                                               | 81 |

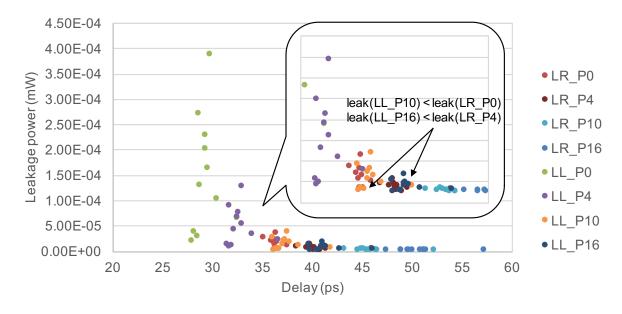

| Figure 2.14: | Leakage versus delay curves of buffer cells with various $V_t$ and poly bias options                                                                                                                                                                                               |    |

|              | available in Enable2. The delay is measured with input slew $50ps$ and output load of $4\times$ the input capacitance of each cell. LL_P16 and LL_P10 consume less leakage                                                                                                         |    |

|              | power than LR_P4 and LR_P0                                                                                                                                                                                                                                                         | 82 |

| Figure 2.15: | Leakage power versus effective period curves for various M3 implementations with                                                                                                                                                                                                   | -  |

| Č            | (a) Enable1, (b) Enable2 and (c) Enable3, along with total power versus effective                                                                                                                                                                                                  |    |

|              | period curves for various M3 implementations with (d) Enable1, (e) Enable2 and (f)                                                                                                                                                                                                 |    |

|              | Enable3                                                                                                                                                                                                                                                                            | 84 |

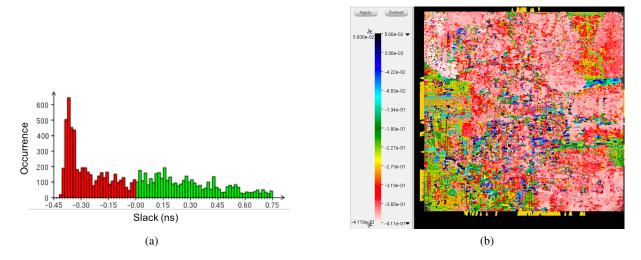

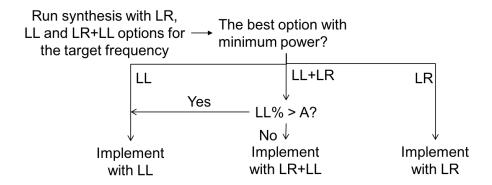

| Figure 2.17: Figure 2.18: | Timing information of M3 implemented with Enable2. (a) Histogram of path slack values, showing existence of wall of slack. 30% of paths must be fixed to achieve a 4% speed improvement. (b) Map of instance timing slacks of M3 implemented with Enable2, with legend shown in the left bar. White and red cells are timing-critical Notional decision tree for FDSOI implementation option choice | 85<br>86<br>88 |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

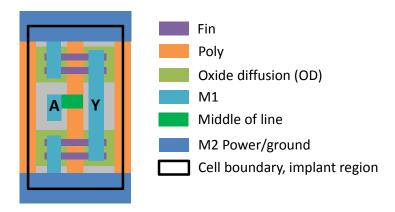

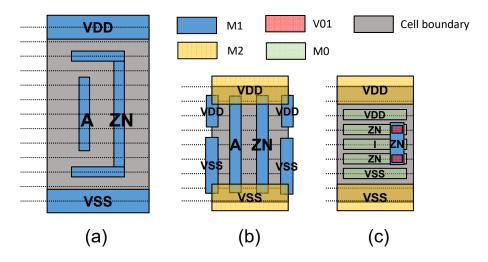

| Figure 3.1:               | Illustration of inverter cell layout in N10 node                                                                                                                                                                                                                                                                                                                                                    | 93             |

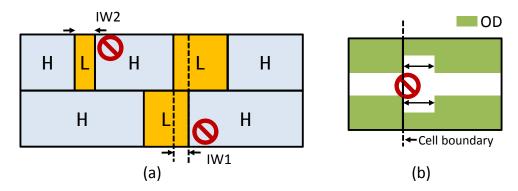

| Figure 3.2:               | (a) Examples of minimum implant width violations [186]. (b) The design rule for OD jogs                                                                                                                                                                                                                                                                                                             | 93             |

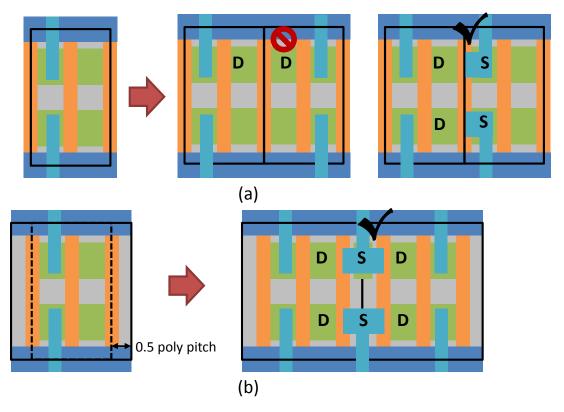

| Figure 3.3:               | (a) Drain-drain abutment violation with an example standard cell layout. (b) Use of dummy poly gates in the library design style can avoid DDA violation in a correct-by-                                                                                                                                                                                                                           |                |

| Figure 3.4:               | construction manner                                                                                                                                                                                                                                                                                                                                                                                 | 94             |

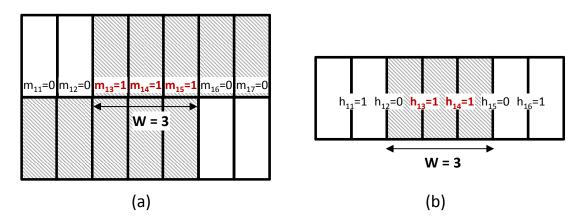

|                           | (gray and white) of regions indicates $V_t$                                                                                                                                                                                                                                                                                                                                                         | 100            |

| Figure 3.5:               | Overall flow of detailed placement legalization                                                                                                                                                                                                                                                                                                                                                     | 103            |

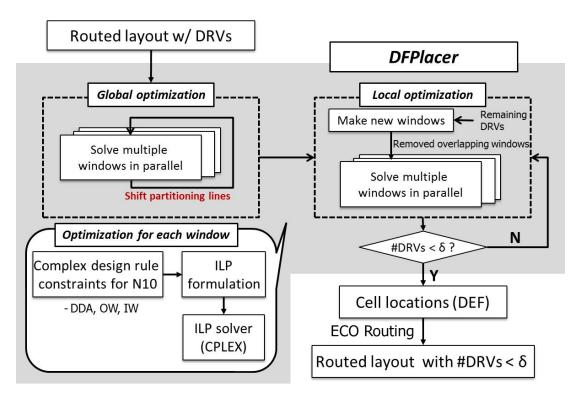

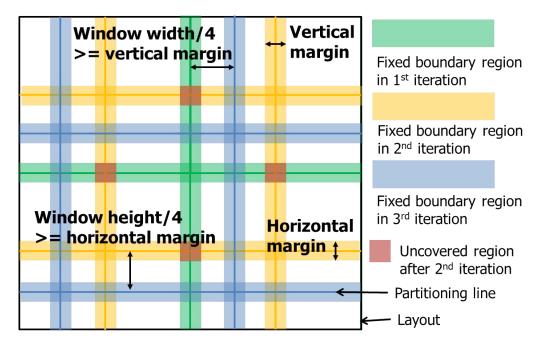

| Figure 3.6:               | Partitioning of layout for parallel global optimization                                                                                                                                                                                                                                                                                                                                             | 105            |

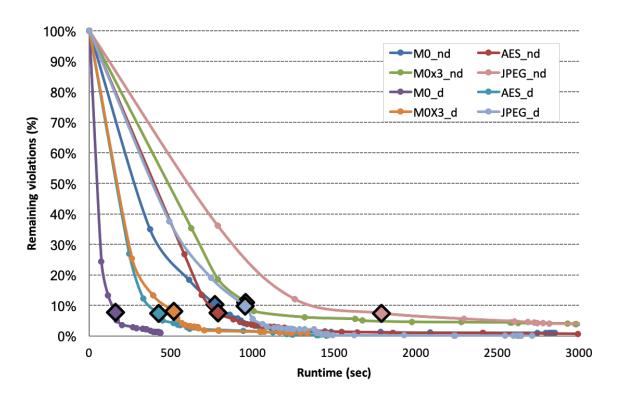

| Figure 3.7:               | Remaining violations versus runtime. Each dot indicates an iteration; after the third iteration, local optimization is performed. The diamond-shaped markers represent                                                                                                                                                                                                                              | 109            |

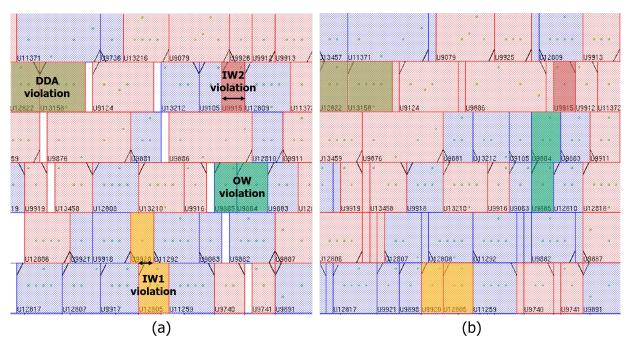

| Figure 3.8:               | third-iteration points                                                                                                                                                                                                                                                                                                                                                                              | 105            |

|                           | optimization. The DRVs in the initial layout are fixed                                                                                                                                                                                                                                                                                                                                              | 110            |

| Figure 3.9:               | New cell architectures to gain additional routing resources. (a) Conventional 12-track INV; (b) <i>ClosedM1</i> 7.5-track INV; (c) <i>OpenM1</i> 7.5-track INV                                                                                                                                                                                                                                      | 113            |

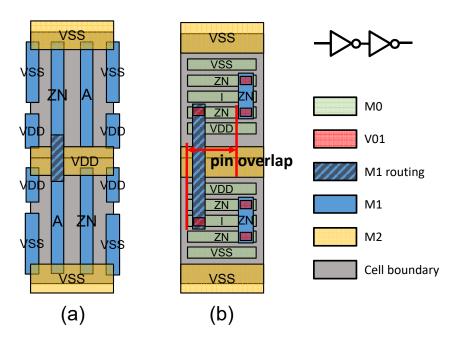

| Figure 3.10:              | Direct vertical M1 routing examples: (a) ClosedM1 and (b) OpenM1                                                                                                                                                                                                                                                                                                                                    | 114            |

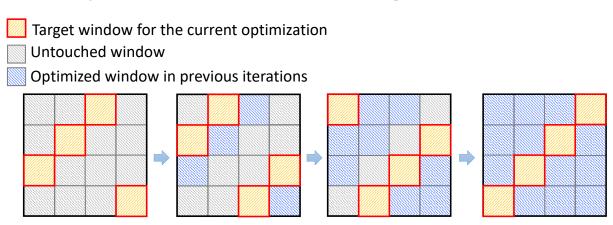

| Figure 3.11:              | Illustration of distributable optimization                                                                                                                                                                                                                                                                                                                                                          | 122            |

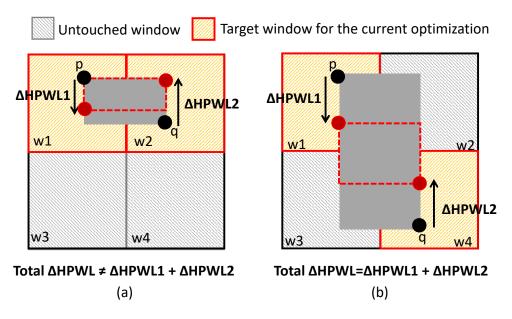

| Figure 3.12:              | HPWL calculation for two cases. (a) Target windows with intersecting projections on the y-axis. (b) Windows with disjoint projections. In the case of (a), the total $\Delta HPWL$ is not equal to the sum of $\Delta HPWL$ values that are calculated from each                                                                                                                                    |                |

|                           | window                                                                                                                                                                                                                                                                                                                                                                                              | 123            |

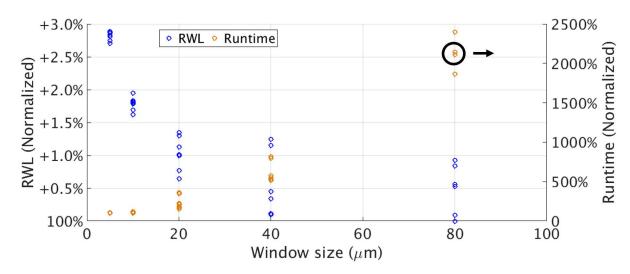

| •                         | ,                                                                                                                                                                                                                                                                                                                                                                                                   | 126            |

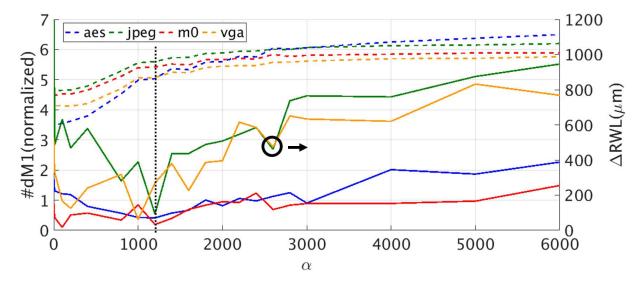

| Figure 3.14:              | Sensitivity of total routed wirelength (RWL) and the number of direct vertical M1 routings (#dM1) to $\alpha$                                                                                                                                                                                                                                                                                       | 126            |

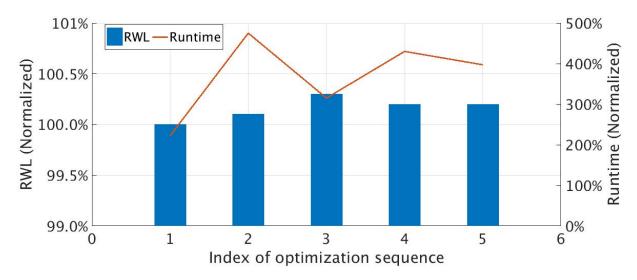

| Figure 3.15:              | Results of various optimization sequences                                                                                                                                                                                                                                                                                                                                                           | 127            |

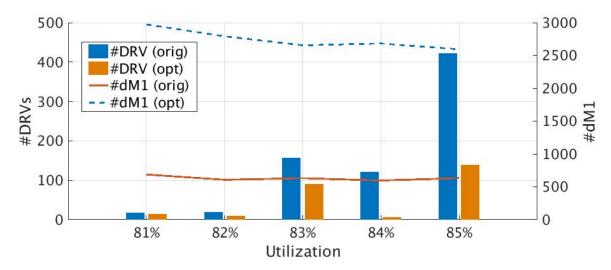

| -                         | The number of DRVs after optimization for AES design with various utilizations. Also shown: the number of direct vertical M1 routings                                                                                                                                                                                                                                                               | 129            |

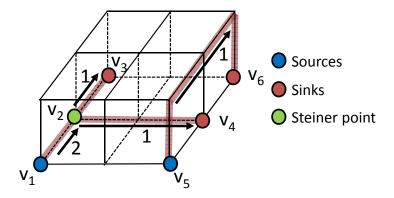

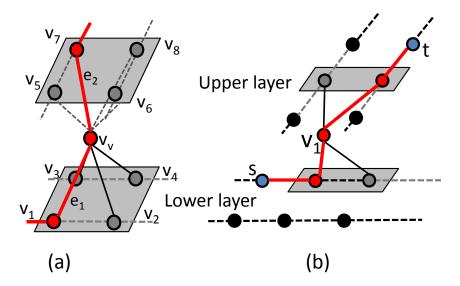

| Figure 4.1:               | Example showing multi-pin nets and the routing solution                                                                                                                                                                                                                                                                                                                                             | 139            |

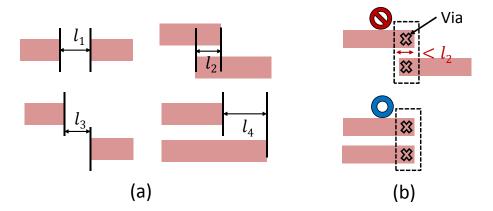

| Figure 4.2: Figure 4.3:   | Via shape. (a) $2 \times 2$ square via. (b) $2 \times 1$ bar via                                                                                                                                                                                                                                                                                                                                    | 141            |

|                           | SADP-aware rules                                                                                                                                                                                                                                                                                                                                                                                    | 147            |

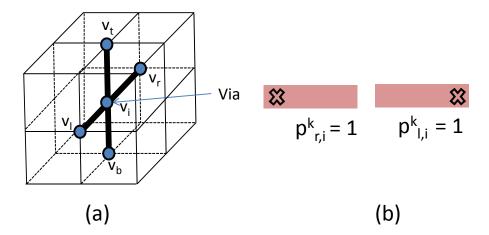

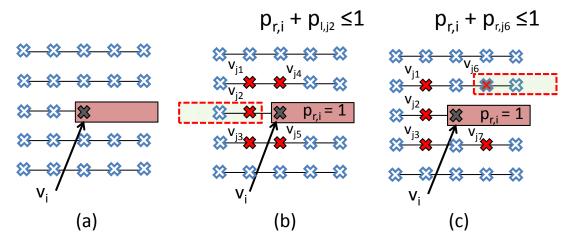

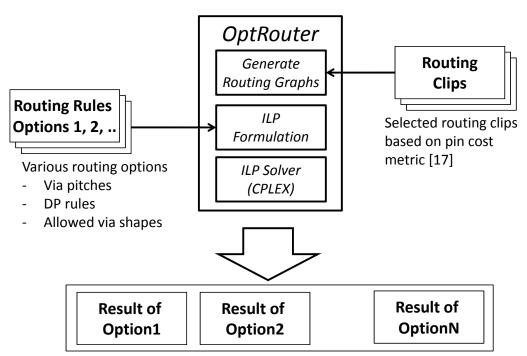

| Figure 4.4:  | An example of a routing graph. (a) The $p$ variable of a vertex $v_i$ is determined by                                                                           |       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|              | flow variables of edges with vertex $v_i$ 's neighbor vertices $v_t$ , $v_b$ , $v_l$ and $v_r$ . (b) Wire                                                        |       |

|              | segment geometries that respectively result when $p_{r,i}^k = 1$ and $p_{l,i}^k = 1$                                                                             | 142   |

| Figure 4.5:  | (a) A wire segment, of which the EOL is located at vertex $v_i$ with the wire coming                                                                             |       |

|              | from the right side. (b) Forbidden via locations for other wire segments with $p_{l,j} = 1$ .                                                                    |       |

|              |                                                                                                                                                                  | 144   |

| Figure 4.6:  | ···                                                                                                                                                              | 146   |

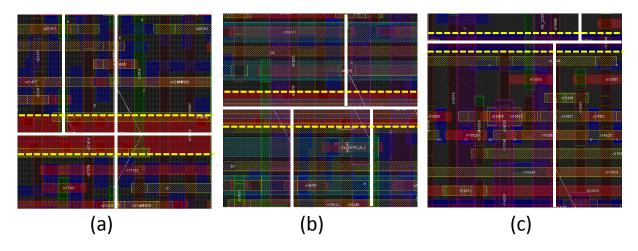

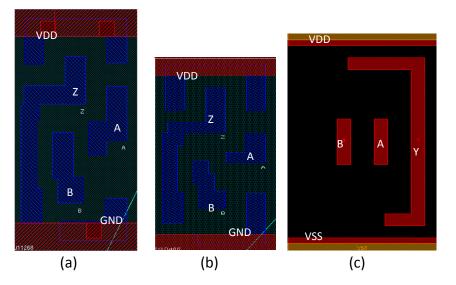

| Figure 4.7:  | Routing clips from (a) N28-12T, (b) N28-9T and (c) N7-9T. Standard cell boundaries                                                                               |       |

|              | and power/ground rail are highlighted with white lines and yellow dashed lines,                                                                                  |       |

|              | respectively                                                                                                                                                     | 147   |

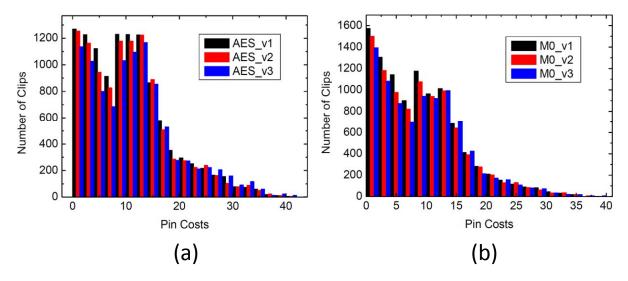

| Figure 4.8:  | Pin cost distributions (per the $PEC + PAC + PRC$ metrics in [148]) of (a) AES and                                                                               |       |

|              | (b) M0 with different utilizations                                                                                                                               | 148   |

| Figure 4.9:  | Pin shapes in NAND2X1: (a) N28-12T, (b) N28-8T and (c) scaled N7-9T                                                                                              | 150   |

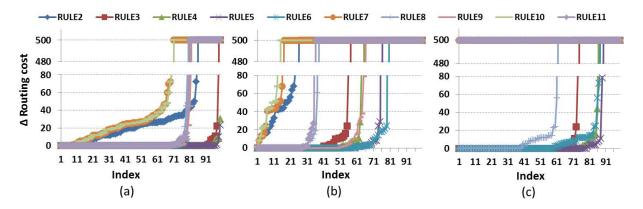

| Figure 4.10: | $\Delta$ cost with different RULE* in (a) N28-12T, (b) N28-8T and (c) N7-9T                                                                                      | 150   |

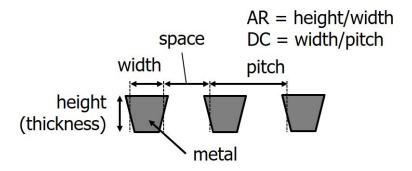

| Figure 4.11: | Illustration of height/width aspect ratio (AR) and width/pitch duty cycle (DC)                                                                                   | 154   |

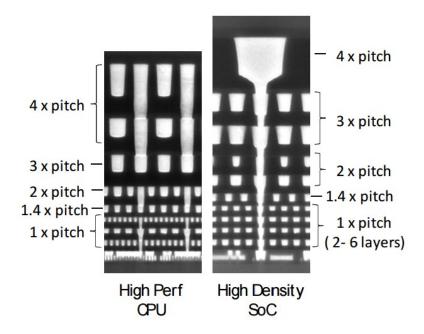

| Figure 4.12: | Interconnect architecture comparison of $22nm$ CPU and SoC [76]                                                                                                  | 154   |

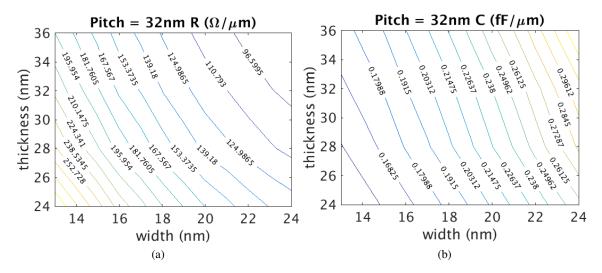

| Figure 4.13: | Contour maps of (a) resistance and (b) capacitance per unit length $(\mu m)$ for metal                                                                           |       |

|              | pitch 32 <i>nm</i>                                                                                                                                               | 158   |

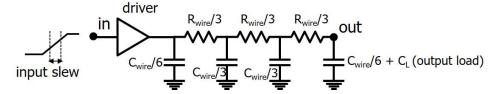

| Figure 4.14: | Circuit structure for SPICE simulation                                                                                                                           | 159   |

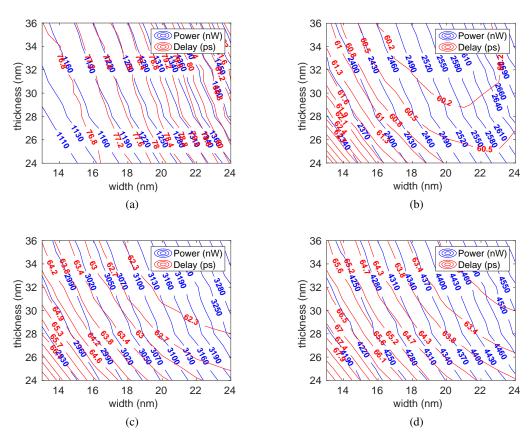

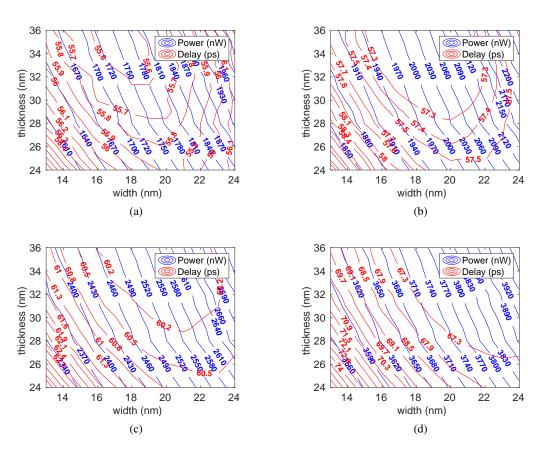

| Figure 4.15: | Sensitivity of power and delay to driver strength: (a) BUF_X1, (b) BUF_X2, (c)                                                                                   |       |

|              |                                                                                                                                                                  | 160   |

| Figure 4.16: | Sensitivity of power and delay to wirelength: (a) $5\mu m$ , (b) $10\mu m$ , (c) $15\mu m$ and (d)                                                               |       |

|              | $20\mu m$                                                                                                                                                        | 161   |

| Figure 4.17: |                                                                                                                                                                  | 162   |

| Figure 4.18: |                                                                                                                                                                  | 163   |

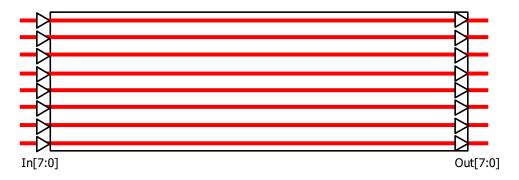

| Figure 4.19: | The artificial testcase with eight bits of single-stage paths                                                                                                    | 164   |

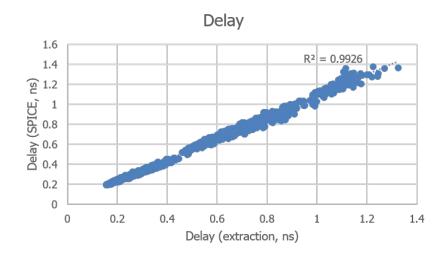

| Figure 4.20: |                                                                                                                                                                  | 164   |

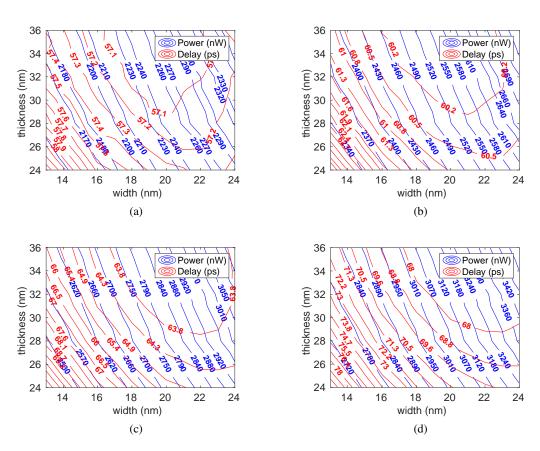

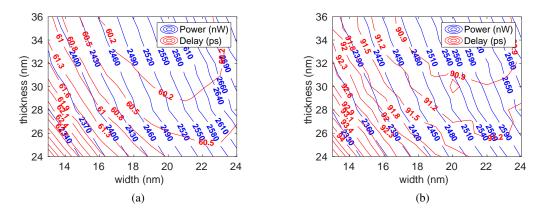

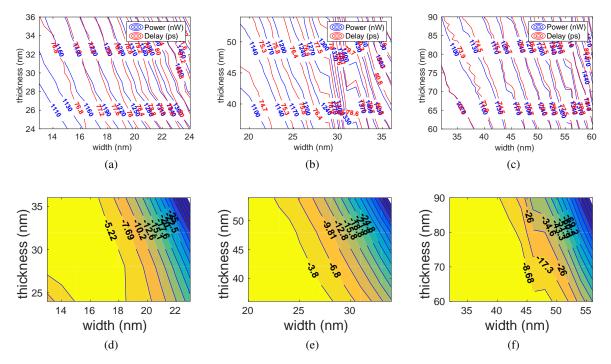

| Figure 4.21: | Block-level validation to single-stage SPICE simulation: (a) – (c) contour maps                                                                                  |       |

|              | of power and delay (BUF_X1) for $1\times$ , $1.5\times$ and $2.5\times$ metal layers, respectively,                                                              |       |

|              | assuming wirelength of $10\mu m$ and load of $2fF$ ; (d) – (f) contour maps of TNS (total                                                                        |       |

|              |                                                                                                                                                                  | 166   |

| Figure 4.22: | Block-level validation to single-stage SPICE simulation: (a) – (c) contour maps                                                                                  |       |

|              | of power and delay (BUF_X4) for $1 \times$ , $1.5 \times$ and $2.5 \times$ metal layers, respectively,                                                           |       |

|              | assuming wirelength of $10\mu m$ and load of $3fF$ ; (d) – (f) contour maps of TNS (total                                                                        |       |

|              |                                                                                                                                                                  | 167   |

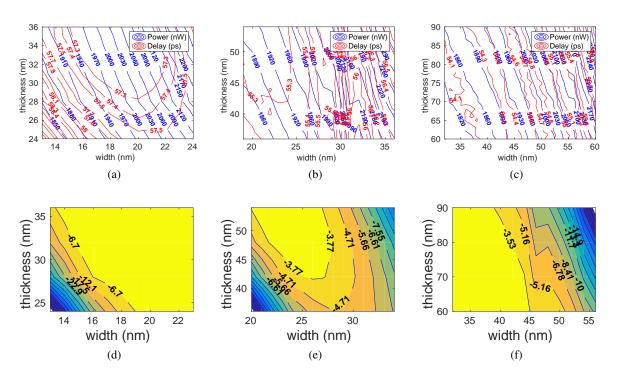

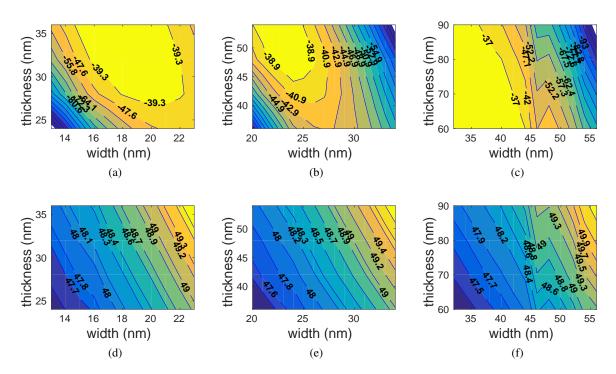

| Figure 4.23: | Contour maps of (a) – (c) TNS (total negative slack) and (d) – (f) power when varying                                                                            |       |

|              |                                                                                                                                                                  | 168   |

| Figure 4.24: | ·                                                                                                                                                                | 170   |

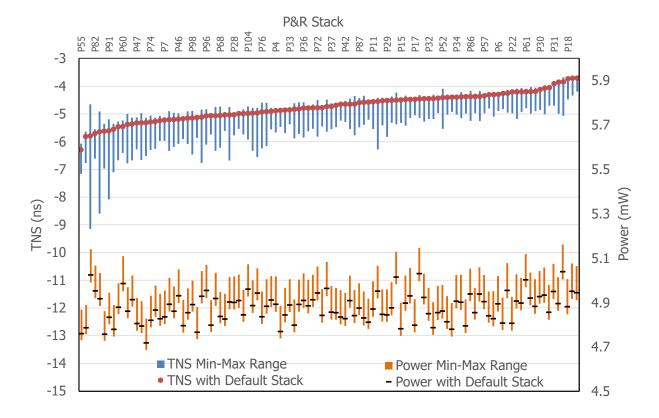

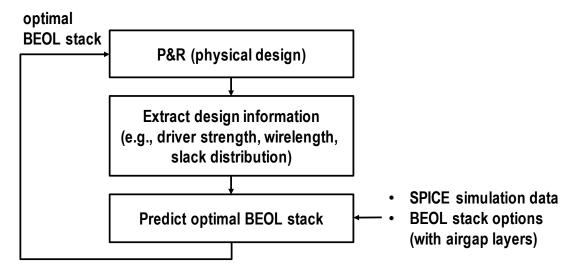

| Figure 4.25: | Co-optimization of SoC physical implementation (design process) with BEOL stack                                                                                  | 1.7.1 |

| E: 4.06      | optimization (manufacturing process). BEOL stack options include airgap layers                                                                                   | 171   |

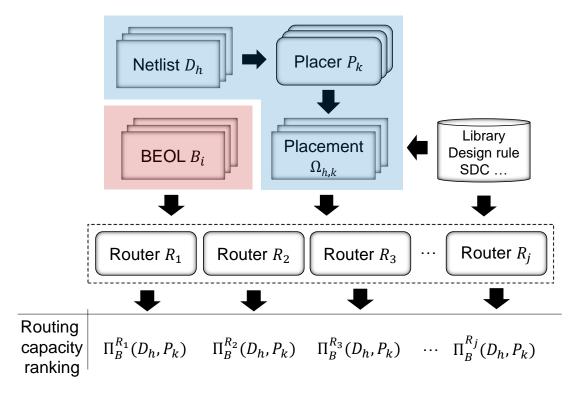

| Figure 4.26: |                                                                                                                                                                  |       |

|              | BEOL stacks in terms of routing capacity, and potentially a ranking of place-and-route                                                                           | 170   |

| Figure 4 27. |                                                                                                                                                                  | 179   |

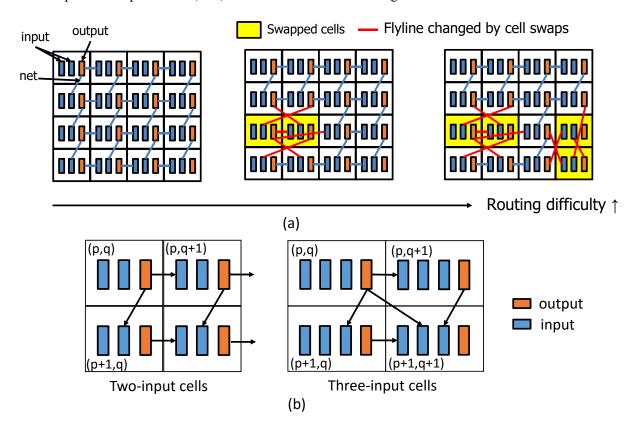

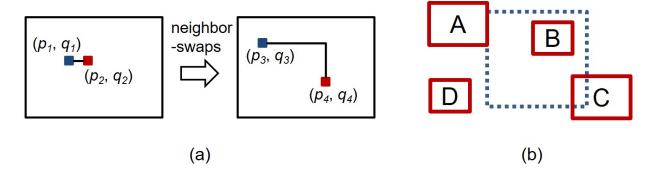

| Figure 4.27: | <ul><li>(a) Illustration of mesh-like placement and perturbations by two neighbor-swap moves.</li><li>(b) Connections for 2-pin cells and 3-pin cells.</li></ul> | 100   |

|              | (U) CONNECTIONS FOR Z-PIN CENS AND 3-PIN CENS                                                                                                                    | 180   |

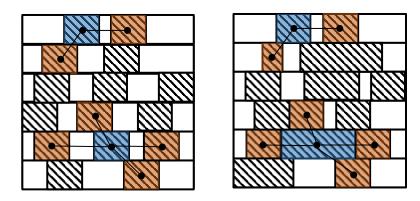

| Figure 4.28: | Illustration of the <i>neighbor</i> cell relation in a placement generated by a commercial        |     |

|--------------|---------------------------------------------------------------------------------------------------|-----|

|              | P&R tool, for the cases of one adjacent row and two adjacent rows. Left: cells with               |     |

|              | uniform (bloated) widths. Right: cells with non-uniform (non-bloated) widths                      | 182 |

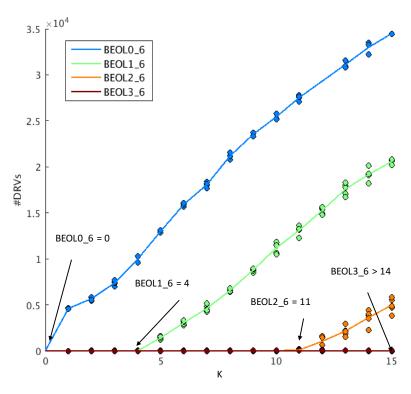

| Figure 4.29: | The number of DRVs versus $K$ . This result is from a mesh-like placement imple-                  |     |

|              | mented with 5000 AOI21 cells, and row utilization of 90%                                          | 187 |

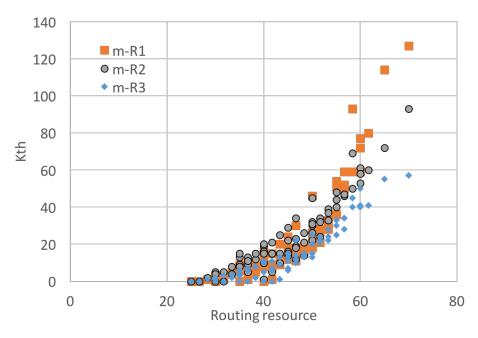

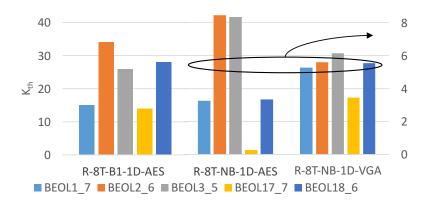

| Figure 4.30: | $K_{th}$ values versus routing resource with three commercial routers (R1, R2 and R3).            |     |

|              | The results are extracted using mesh-like placements implemented with 5000 AOI21                  |     |

|              | cells and 90% row utilization. Each dot corresponds to a BEOL stack option                        | 188 |

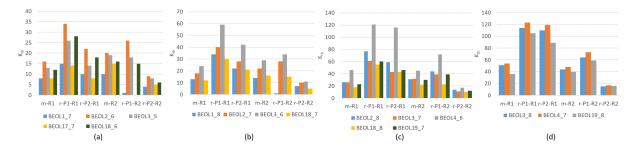

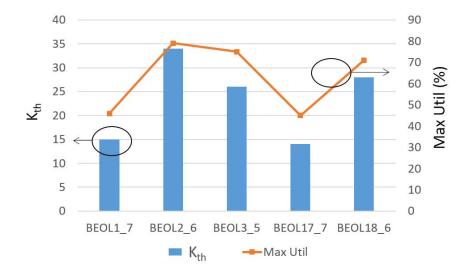

| Figure 4.31: | $K_{th}$ values for (a) Group 1, (b) Group 2, (c) Group 3 and (d) Group 4 of BEOL stack           |     |

| 8            | options in Table 4.9                                                                              | 188 |

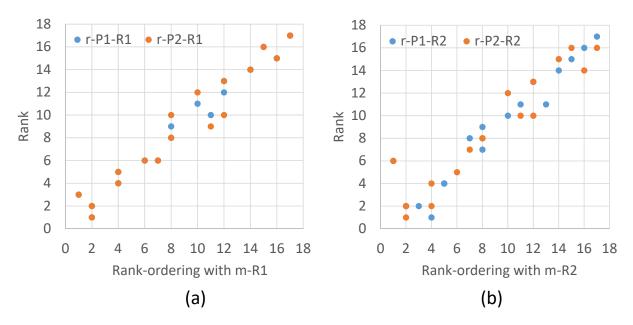

| Figure 4 32: | Correlations of the rank-ordering of BEOL stack options (in increasing order of $K_{th}$ )        |     |

| 118010 1.52. | between mesh-like placement results and cell width-regularized placement results: (a)             |     |

|              | R1 and (b) R2                                                                                     | 190 |

| Figure 4.33: | The $K_{th}$ values obtained from cell width-regularized placements versus maximum                | 170 |

| 11guie 4.55. |                                                                                                   |     |

|              | achievable (initial) row utilization values. The BEOL stack options in Group 1 are                |     |

|              | tested using the AES design and $R1$ . We record the maximum achievable utilization               | 101 |

| F: 4.2.4     | values such that #DRVs < 150 (shown in the orange trace)                                          | 191 |

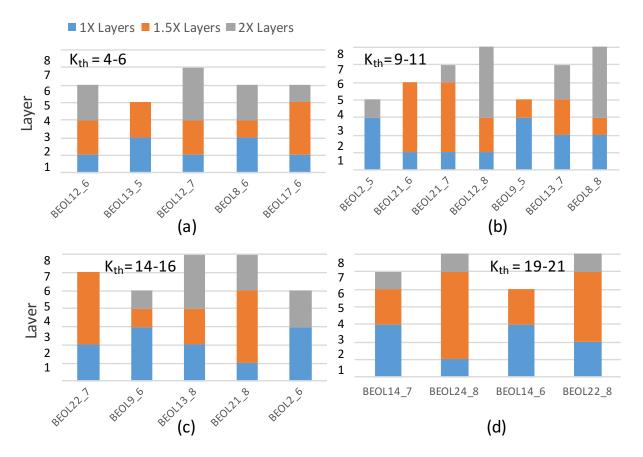

| Figure 4.34: | Results of $m$ - $R1$ , shown for subsets of BEOL stack options that have the same $K_{th}$       |     |

|              | values. (a) BEOL stack options with $K_{th} = 4-6$ ; (b) BEOL stack options with $K_{th} =$       |     |

|              | 9–11; (c) BEOL stack options with $K_{th} = 14$ –16; and (d) BEOL stack options with              |     |

|              | $K_{th} = 19-21.$                                                                                 | 193 |

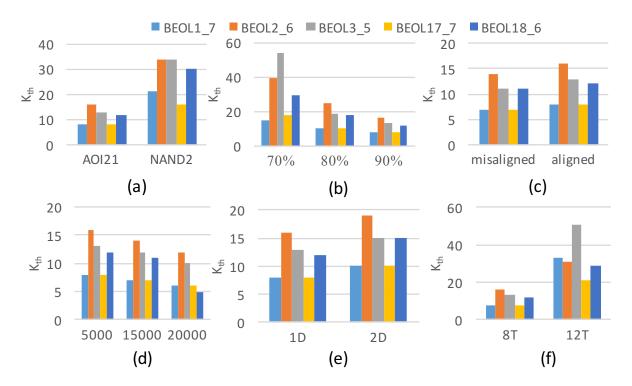

| Figure 4.35: | $K_{th}$ of mesh-like placements with various configurations. (a) Different cell types:           |     |

|              | AOI21 (three-input cell) and NAND2 (two-input cell); (b) different row utilizations:              |     |

|              | 70%, 80% and 90%; (c) different pin alignments; (d) different total number of in-                 |     |

|              | stances: 5K, 15K and 20K; (e) 1D and 2D routing; and (f) 8T and 12T cells                         | 195 |

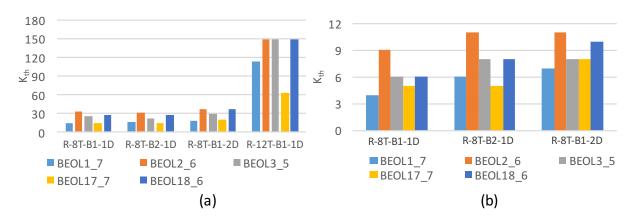

| Figure 4.36: | $K_{th}$ values of the BEOL stack options in Group 1 for various cases: (i) R-8T-B1-1D,           |     |

|              | (ii) R-8T-B2-1D, (iii) R-8T-B1-2D and (iv) R-12T-B1-1D. The results are obtained (a)              |     |

|              | using $(P1, R1)$ and (b) using $(P2, R2)$                                                         | 199 |

| Figure 4.37: | $K_{th}$ values of the BEOL stack options in Group 1 for AES and VGA placements with              |     |

| C            | non-bloated 8T cells (R-8T-NB-1D-AES and R-8T-NB-1D-VGA). R-8T-B1-1D-AES is                       |     |

|              | shown for a reference. The results are obtained using $(P1, R1)$                                  | 199 |

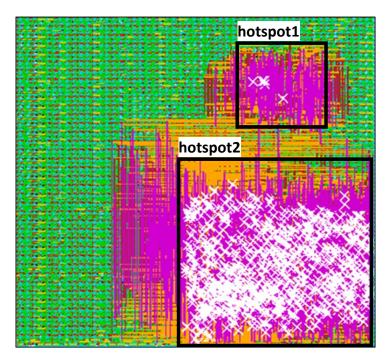

| Figure 4 38: | A routed layout with two hotspots. DRVs are indicated by white crosses. Other colors              |     |

| 118410 11301 | (green, pink, orange) indicate metal layers. Although each hotspot is perturbed by the            |     |

|              | same $K$ (× $S^2$ , where $S$ is the dimension of the $S \times S$ hotspot), hotspot ( $S = 16$ ) |     |

|              | produces noticeably fewer DRVs than hotspot2 ( $S=33$ )                                           | 201 |

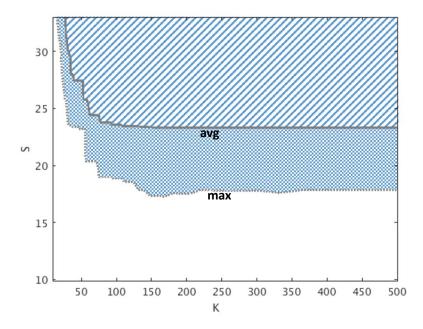

| Figure 4 30: | A contour map that indicates routability for various $(S, K)$ pairs. The solid line is            | 201 |

| 11guic 4.39. | the contour based on the average number of DRVs, and the dotted line is the contour               |     |

|              | <del>-</del>                                                                                      |     |

|              | based on the maximum number of DRVs in 10 trials per each $(S, K)$ pair. Based on                 | 202 |

| E: 4.40      | the contour lines, the upper shaded regions show where routing fails                              | 202 |

| Figure 4.40: | Illustrations of edge mapping, $ED$ and $CC$ .                                                    | 202 |

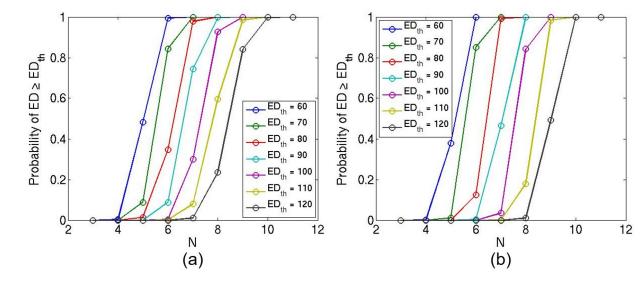

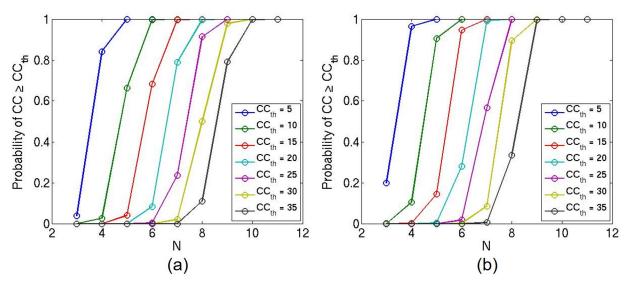

| Figure 4.41: | Probability of $ED \ge ED_{th}$ increases with N. Shown: $K = 50$ based on (a) Monte              | 201 |

| <b>T</b>     | Carlo simulation and (b) transition matrix exponentiation.                                        | 206 |

| Figure 4.42: | Probability of $CC \ge CC_{th}$ increases with N. Shown: $K = 50$ based on (a) Monte              |     |

|              | Carlo simulation and (b) transition matrix exponentiation                                         | 206 |

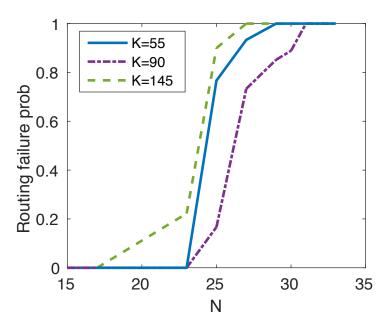

| Figure 4.43: | Routing failure probabilities versus $N$ for $K = 55, 90$ and 145                                 | 208 |

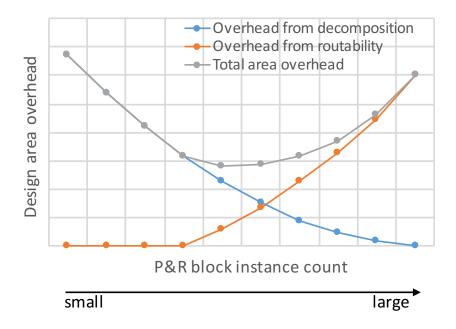

Figure 4.44: A hypothesized tradeoff between overall design area and instance count in individual P&R blocks. The x-axis shows block instance count, and the y-axis shows overall design area overheads induced by (1) decomposition and (2) difficulty of routing. 210

# LIST OF TABLES

| Table 2.1:  | Summary of works on gate sizing optimization                                            | 15  |

|-------------|-----------------------------------------------------------------------------------------|-----|

| Table 2.2:  | Comparisons of Trident [84] (Tri) and this work (Szr)                                   | 21  |

| Table 2.3:  | Notations                                                                               | 22  |

| Table 2.4:  | Sensitivity functions for a single view and MCMM                                        | 23  |

| Table 2.5:  | Parameter conditions and their implications                                             | 23  |

| Table 2.6:  | User-defined input parameters                                                           | 33  |

| Table 2.7:  | Timing view definitions.                                                                | 40  |

| Table 2.8:  | Summary of testcases. The designs are optimized with high-effort optimization options   |     |

|             | for leakage and dynamic power using C1. The values are reported by TMP                  | 41  |

| Table 2.9:  | Design of experiments                                                                   | 41  |

| Table 2.10: | Reproduction of ISPD Trident (Tri) results with Tri-R, and comparison with Sizer (Szr). |     |

|             | The values are reported by PT                                                           | 42  |

| Table 2.11: | Leakage optimization result comparison between Tri-R, Sizer (Szr) and a commercial      |     |

|             | tool (C2). The results are reported by PT                                               | 43  |

| Table 2.12: | Leakage and total power optimization results                                            | 44  |

| Table 2.13: | Leakage optimization results of $65nm$ designs with various SF                          | 45  |

| Table 2.14: | Leakage optimization results of $65nm$ designs with various MSF                         | 45  |

| Table 2.15: | Leakage optimization results for NXPIC                                                  | 46  |

| Table 2.16: | Notations used in this work.                                                            | 53  |

| Table 2.17: | Testcases used in the experiments. WS, Period, Leak respectively indicate worst slack,  |     |

|             | clock period and leakage power after routing, before filler cell insertion              | 62  |

| Table 2.18: | Results for a simple filler insertion and our heuristic method                          | 62  |

| Table 2.19: | Results for our heuristic sizing algorithm. Const3 is used for the minimum implant      |     |

|             | width constraint in this experiment                                                     | 63  |

| Table 2.20: | Notations                                                                               | 73  |

| Table 2.21: | Testcases                                                                               | 77  |

| Table 2.22: | Results of ILP-1, ILP-2 and Heur                                                        | 80  |

| Talala 2 1. | Natations                                                                               | 00  |

| Table 3.1:  | Notations                                                                               | 98  |

| Table 3.2:  | <b>.</b>                                                                                | 107 |

| Table 3.3:  |                                                                                         | 108 |

| Table 3.4:  |                                                                                         | 119 |

| Table 3.5:  | Results of Expt2                                                                        | 128 |

| Table 4.1:  | Notations                                                                               | 137 |

| Table 4.2:  | Benchmark designs                                                                       | 146 |

| Table 4.3:  | BEOL design rule configurations                                                         | 149 |

| Table 4.4:  | Wirelength distribution per layer type (normalized) grouped by driver cells             | 166 |

| Table 4.5:  | A noteworthy subset of BEOL stack configurations                                        | 168 |

| Table 4.6:  | Description of notations used in our work                                               | 178 |

| Table 4.7:  | Testcases                                                                               | 184 |

| Table 4.8:  | BEOL stack options                                                                      | 185 |

| Table 4.9:  | $K_{th}$ values for groups of BEOL stack options having the same routing resource. The    |     |

|-------------|-------------------------------------------------------------------------------------------|-----|

|             | routing resource $(T)$ value for each group is shown in the first column. $K_{th}$ values |     |

|             | are measured based on six types of implementations: (i) $m-R1$ ; (ii) $r-P1-R1$ ; (iii)   |     |

|             | r- $P$ 2- $R$ 1; (iv) $m$ - $R$ 2; (v) $r$ - $P$ 1- $R$ 2; and (vi) $r$ - $P$ 2- $R$ 2    | 189 |

| Table 4.10: | $K_{th}$ results of various 2D options                                                    | 194 |

#### **ACKNOWLEDGMENTS**

First of all, I would like to thank my advisor Professor Andrew B. Kahng for his continuous support and invaluable advice throughout my Ph.D. study. I have learned many lessons from him not only on research but also on life.

I would like to thank my family: my husband Kyu Hyun Kim and our loving son, Han Kim; my father Si Ryong Lee, my mother Cheong Hui Lee and my brother Sang Gyu Lee; my father-in-law Nam Hee Kim and my mother-in-law Ho Sung Kim for their endless support and encouragement.

I would like to thank my fellow labmates in the UCSD VLSI CAD Laboratory (Kwangsoo Han, Minsoo Kim, Uday Mallappa, Vaishnav Srinivas, Lutong Wang, Mingyu Woo, Bangqi Xu and Payal Agarwal) and former lab members (Dr. Tuck-Boon Chan, Dr. Wei-Ting (Jonas) Chan, Dr. Jiajia Li, Dr. Ilgweon Kang, Professor Seokhyeong Kang, Mulong Luo, Dr. Siddhartha Nath, Tushar Shah, Yaping Sun and Sriram Venkatesh) for their assistance and enthusiastic discussions.

My sincere thanks also go to my thesis committee members Professor Chung-Kuan Cheng, Professor Rajesh Gupta, Professor Ian A. Galton and Professor Ryan Kastner for their time, encouragement and insightful comments.

Last, but not least, I would like to thank my industrial collaborators (Peter Debacker, Dr. Hamed Fatemi, Professor Jose Pineda de Gyvez and Dr. Praveen Raghavan) for their invaluable guidance and feedback in many of my research projects.

The material in this thesis is based on the following publications.

Chapter 2 contains the reprint of Andrew B. Kahng and Hyein Lee, "Minimum Implant Area-Aware Gate Sizing and Placement", *Proc. ACM Great Lakes Symposium on Very Large Scale Integration*, 2014. Chapter 2 also contains the draft submitted to *Integration*, *the VLSI Journal*, Hamed Fatemi, Andrew B. Kahng, Hyein Lee, Jiajia Li and José Pineda de Gyvez, "Enhancing Sensitivity-Based Power Reduction for an Industry IC Design Context", 2018. Chapter 2 also contains the draft submitted to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Hamed Fatemi, Andrew B. Kahng, Hyein Lee and José Pineda de Gyvez, "Heuristic Methods for Fine-Grain Exploitation of FDSOI", 2018. The dissertation author is a main contributor to, and a primary author of, each of these papers.

Chapter 3 contains reprints of Peter Debacker, Kwangsoo Han, Andrew B. Kahng, Hyein Lee, Praveen Raghavan and Lutong Wang, "Vertical M1 Routing-Aware Detailed Placement for Congestion and Wirelength Reduction in Sub-10nm Nodes", *Proc. ACM/EDAC/IEEE Design Automation Conference*, 2017; and Kwangsoo Han, Andrew B. Kahng and Hyein Lee, "Scalable Detailed Placement Legalization for Complex Sub-14nm Constraints", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2015. The dissertation author is a main contributor to, and a primary author of, each of these papers.

Chapter 4 contains reprints of Alex Kahng, Andrew B. Kahng, Hyein Lee and Jiajia Li, "PROBE: A Placement, ROuting, Back-End-of-line Measurement Utility", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 37(7) 2018; Kwangsoo Han, Andrew B. Kahng, Hyein Lee and Lutong Wang, "Performance- and Energy-Aware Optimization of BEOL Interconnect Stack Geometry in Advanced Technology Nodes", *Proc. International Symposium on Quality Electronic Design*, 2017; and Kwangsoo Han, Andrew B. Kahng and Hyein Lee, "Evaluation of BEOL Design Rule Impacts Using an Optimal ILP-Based Detailed Router", *Proc. ACM/EDAC/IEEE Design Automation Conference*, 2015. The dissertation author is a main contributor to, and a primary author of, each of these papers.

My coauthors (Mr. Peter Debacker, Dr. Hamed Fatemi, Professor José Pineda de Gyvez, Mr. Kwangsoo Han, Mr. Alex Kahng, Professor Andrew B. Kahng, Dr. Jiajia Li, Dr. Praveen Raghavan and Mr. Lutong Wang, listed in alphabetical order) have all kindly approved the inclusion of the aforementioned publications in my thesis.

#### **VITA**

| 2003 | B. S., Electronics Engineering,<br>Yonsei University, Seoul, South Korea                                  |

|------|-----------------------------------------------------------------------------------------------------------|

| 2005 | M. S., Electronics Engineering,<br>Korea Advanced Institute of Science & Technology, Daejeon, South Korea |

| 2015 | C. Phil., Electrical Engineering (Computer Engineering),<br>University of California, San Diego           |

| 2018 | Ph. D., Electrical Engineering (Computer Engineering), University of California, San Diego                |

All papers co-authored with my advisor Professor Andrew B. Kahng have authors listed in alphabetical order.

### **PUBLICATIONS**

- A. Kahng, A. B. Kahng, **H. Lee** and J. Li, "PROBE: A Placement, ROuting, Back-End-of-line Measurement Utility", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 37(7) (2018), pp. 1459-1472.

- C. Han, K. Han, A. B. Kahng, **H. Lee**, L. Wang and B. Xu, "Optimal Multi-Row Detailed Placement for Yield and Model-Hardware Correlation Improvements in Sub-10nm VLSI", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2017, pp. 667-674.

- P. Debacker, K. Han, A. B. Kahng, **H. Lee**, P. Raghavan and L. Wang, "Vertical M1 Routing-Aware Detailed Placement for Congestion and Wirelength Reduction in Sub-10nm Nodes", *Proc. ACM/IEEE Design Automation Conference*, 2017, pp. 1-6.

- P. Debacker, K. Han, A. B. Kahng, **H. Lee**, P. Raghavan and L. Wang, "MILP-Based Optimization of 2D Block Masks for Timing-Aware Dummy Segment Removal in Self-Aligned Multiple Patterning Layouts", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 36(7) (2017), pp. 1075-1088.

- K. Han, A. B. Kahng, **H. Lee** and L. Wang, "Performance- and Energy-Aware Optimization of BEOL Interconnect Stack Geometry in Advanced Technology Nodes", *Proc. International Symposium on Quality Electronic Design*, 2017, pp. 104-110. (**Invited Paper**)

- A. B. Kahng, **H. Lee** and J. Li, "Measuring Progress and Value of IC Implementation Technology", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2016, pp. 27:1-27:8. (**Invited paper**)

- K. Han, A. B. Kahng and **H. Lee**, "Scalable Detailed Placement Legalization for Complex Sub-14nm Constraints", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2015, pp. 867-873.

- K. Han, A. B. Kahng, **H. Lee** and L. Wang, "ILP-Based Co-Optimization of Cut-Mask Layout, Dummy Fill and Timing for Sub-14nm BEOL Technology", *Proc. SPIE/BACUS Symposium on Photomask Technology and Management*, 2015, pp. 96350E:1-96350E:14.

- K. Han, A. B. Kahng and **H. Lee**, "Evaluation of BEOL Design Rule Impacts Using an Optimal ILP-Based Detailed Router", *Proc. ACM/IEEE Design Automation Conference*, 2015, pp. 1-6.

- A. B. Kahng and **H. Lee**, "Minimum Implant Area-Aware Gate Sizing and Placement", *Proc. ACM Great Lakes Symposium on Very Large Scale Integration*, 2014, pp. 57-62.

- A. B. Kahng, **H. Lee** and J. Li, "Horizontal Benchmark Extension for Improved Assessment of Physical CAD Research", *Proc. ACM Great Lakes Symposium on Very Large Scale Integration*, 2014, pp. 27-32.

- A. B. Kahng and **H. Lee**, "Margin Recovery with Flexible Flip-Flop Timing", *Proc. International Symposium on Quality Electronic Design*, 2014, pp. 496-503.

- A. B. Kahng, S. Kang, **H. Lee**, I. L. Markov and P. Thapar, "High-Performance Gate Sizing with a Signoff Timer", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2013, pp. 450-470.

- A. B. Kahng, S. Kang and **H. Lee**, "Smart Non-Default Routing for Clock Power Reduction", *Proc. ACM/IEEE Design Automation Conference*, 2013, pp. 91:1-91:7.

- A. B. Kahng, S. Kang, **H. Lee**, S. Nath and J. Wadhwani, "Learning-Based Approximation of Interconnect Delay and Slew in Signoff Timing Tools", *Proc. ACM International Workshop on System-Level Interconnect Prediction*, 2013, pp. 1-8.

- K.-T. Do, J. Y. Choi, S. Kim, **H. Lee**, H.-S. Won and K.-M. Choi, "A Practical Framework for Statistical Leakage Estimation", *Proc. ACM/IEEE Design Automation Conference User Track*, 2010.

- **H. Lee**, S. Paik and Y. Shin, "Pulse Width Allocation and Clock Skew Scheduling: Optimizing Sequential Circuits based on Pulsed Latches", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 29(3) (2010), pp. 355-366.

- **H. Lee**, S. Paik and Y. Shin, "Pulse Width Allocation with Clock Skew Scheduling for Optimizing Pulsed Latch-based Sequential Circuits", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2008, pp. 224-229.

#### ABSTRACT OF THE DISSERTATION

### Physical Design and Technology Optimizations for Advanced VLSI Manufacturing

by

### Hye In Lee

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California, San Diego, 2018

Professor Andrew B. Kahng, Chair

Recent years have seen a significant slowdown of density scaling in advanced semiconductor integrated-circuit products, despite multiple innovations in patterning technologies, device and cell architectures, and design methodologies. Designers are unable to fully leverage the potential power, performance, area and cost benefits offered by new process technologies. Root causes of this inability include the explosion of scenarios in timing signoff, front-end-of-line (FEOL) layout rules that affect placement, sizing-placement interactions that require new co-optimizations, back-end-of-line (BEOL) layout rules and cell height scaling that impact routing, and the increasingly dominant role of BEOL parasitics on final design quality. To address these challenges for modern system-on-chip physical design and signoff in advanced manufacturing nodes, new design optimization techniques as well as methodologies for design-

technology co-optimization are required. Accordingly, this thesis presents new physical optimization and evaluation methodologies, organized according to three main thrusts.

To address the explosion of corners and modes in timing signoff and the emergence of new sizing-placement interactions, the *post-placement gate sizing optimization* thrust of this thesis presents a gate sizing optimization considering multi-corner multi-mode constraints; a minimum implant rule-aware gate sizing and placement co-optimization; and heuristics for potential fine-grain exploitation of FDSOI technologies.

To address the challenges to scaling brought by new placement rules and reduced-track cell architectures, the *detailed placement optimization* thrust of this thesis presents an integer linear programming-based incremental detailed placement optimization that considers inter-row and intra-row placement constraints; and a detailed placement optimization that reduces wirelength in the context of new cell architectures with vertical M1 pins.

To address the need for design-technology co-optimization, the *evaluation of design enablement* thrust of this thesis presents analyses of impacts of patterning technology choices and associated routing rules on physical implementation density; a study of impacts of BEOL dimensions on block-level power and area; and a methodology for assessment of routing capacity of a BEOL stack as well as inherent capability of routers.

# **Chapter 1**

# Introduction

In recent years, the semiconductor industry has struggled to continue the scaling trajectory of Moore's Law, i.e.,  $2\times$  transistor layout density in each successive technology node. Density scaling in recent technology nodes has been achieved using a variety of levers, including new patterning technologies, new device and cell architectures, and new design methodologies. This has come at the cost of enormous R&D investments in manufacturing technology and design enablement. However, despite these efforts, the past decade has seen a notable slowdown in the scaling of actual IC product *quality of results* (QoR). This slowdown is due to a weakened ability of design methodologies to exploit the "available scaling" afforded by process and device innovation. In other words, current design enablements are unable to extract sufficient power, performance, area and cost (PPAC) benefits from new nodes. As depicted in Figure 1.1, there is a significant gap between the *actual* density scaling and the *available* scaling from technology. Since 2008, the actual density scaling (red squares) has slowed down to  $1.6\times$  per node, in contrast to  $2\times$  per node of available density scaling (gray arrow).

This thesis addresses root causes of the slowdown in scaling of IC design quality, and proposes improved design methodologies to tackle physical design challenges in advanced technology nodes.

**Figure 1.1**: Design capability gap [182][81]. The gray arrow shows the "available" density scaling, and the red squares show the "actual" density scaling, in MPU products.

# 1.1 New Challenges in Advanced Technology Nodes

Root causes of the slowdown in design scaling include the explosion of scenarios in timing signoff, front-end-of-line (FEOL) layout rules that affect placement, sizing-placement interactions that require new co-optimizations, back-end-of-line (BEOL) layout rules and cell height scaling that impact routing, and the increasingly dominant role of BEOL parasitics on final design quality.

### 1.1.1 Challenges in Gate Sizing Optimization

Discrete gate sizing has been widely adopted for timing and power optimization. The gate sizing optimization has been studied for many years in academia. However, with new timing signoff challenges introduced by the explosion of signoff modes and corners, and with new placement constraints in particular technologies (i.e., Fully Depleted Silicon On Insulator (FDSOI) and sub-22nm), traditional gate sizing methods are no longer suitable for optimization of current real-world designs.

### **Explosion of Signoff Modes and Corners**

Design methodologies for complex modern systems-on-chip (SOCs) introduce a large number of signoff modes and corners, resulting in a huge burden for timing signoff and gate sizing optimization tools. A primary cause of this complexity is the need for extreme low-power consumption in modern SoC designs, such as mobile and IoT products. Multiple scenarios or modes are mandatory, along with mode-specific

design optimizations. For example, mobile products can have sleep and functional modes, and mode-specific power minimization is required to maximize battery life. Modern SoC products can have dozens of modes, each with its own signoff criteria; these modes typically include functional (scenario-based, overdrive, underdrive) and test (scan, at-speed, BIST) modes.

In addition to multiple functional modes, multiple supply voltages and multiple power domains increase voltage corners. In recent technologies, particular with FinFET devices, the use of extreme supply voltage scaling has completely changed the delay-power tradeoff in gate sizing, and has brought many new challenges (e.g., slew times and gate-dominance vs. wire-dominance across signoff corners) to gate sizing optimizations. The growing impact of manufacturing variations in back-end-of-line (BEOL) and front-end-of-line (FEOL) processes further increases the number of corners that must also be considered during design optimization and signoff. For example, BEOL corners now include Cw, Ccw, Cb, RCw, RCb, etc.; FEOL corners now include FF, SS, TT, FS, SF, SSG, FFG, etc.

#### **Gate Sizing and Placement Interaction**

Continued technology scaling has been possible only with introduction of multiple-patterning technologies and complex design rules. In older technologies before the 22nm node, standard-cell layouts are "composable by construction": arbitrary placements of cells in rows are legal and manufacturable, unless there is an overlap between two cells. However, in advanced technology nodes, the individual cell size has continued to decrease relative to minimum patternable feature sizes. As a result, free composability of cells in placement rows is no longer guaranteed, and placement legality can depend on how a cell is placed in relation to its neighbors. This leads to new challenges for physical design, e.g., interdependencies between gate sizing and detailed placement. Two prominent examples of new placement constraints are the *minimum implant area* (MinIA) constraint and the  $V_t$  abuttment rule in FDSOI.

Implant (active) layers, which indicate regions for ion implantation, determine the threshold voltage  $(V_t)$  of transistors. The implant layer dimension is typically matched to the width of standard cells if the cells consist of single- $V_t$  transistors. Due to the limitation of patterning technologies, minimum width rules for implant layers are introduced to form legal shapes in terms of patterning. Such minimum width rules have become smaller than the minimum cell width in sub-22nm – such that narrow cells

cannot be sandwiched between different- $V_t$  cells. As a result, sizing problem formulations of downsizing and  $V_t$ -swapping operations (which by definition do not cause overlaps, and are hence benign in older technologies) must now comprehend spatially adjacent cell instances and whitespace in order to avoid creation of sandwiched narrow cells.

Another example of sizing-placement interaction can be seen in FDSOI. Due to the unique FDSOI device structure that does not have a body node, low- $V_t$  devices are implemented using a special *flip* well structure, while regular  $V_t$  devices are implemented using the conventional well. As the wells are flipped, abutting low  $V_t$  and regular  $V_t$  cells induces a well bias conflict. Due to these constraints, sizing optimizations must have region awareness: low- $V_t$  cells must be spatially contiguous, forming islands in the placement.

### 1.1.2 Challenges in Placement Optimization

Technology scaling to 10nm and below introduces complex intra-row and inter-row constraints in standard-cell detailed placement. Examples of such constraints are found in rules for drain-drain abutment, minimum implant region area and width, oxide diffusion (OD) notching and jogging. These new rules change the definition of "legal" placement, which was simply "non-overlapping" placement in older technologies. Detailed placers must now consider intra-row and inter-row constraints during the optimization to maintain the wirelength / timing / power QoR while achieving legal placements.

Cell architectures also have been changed for better detailed routing. For example, "middle-of-line" layers below M1 are used to gain additional routing resources. New cell architectures wherein inter-row M1 routing is allowed force consideration of vertical alignment of cells. The rapid emergence of new placement rules and new cell architectures motivates the introduction of a new final legalization phase for standard-cell placement tools in advanced (particularly, 10nm and 7nm) foundry nodes.

### 1.1.3 Challenges in Design-Technology Co-optimization

In advanced technology nodes, BEOL interconnect geometry has become a key lever for design enablement, and a focal point for design-technology co-optimization, due to its significant impact on physical design QoR. Complex design rules and more pervasive use of multi-patterning in the BEOL has

increased the difficulty of maintaining high layout densities. Intuitively, emerging constraints such as unidirectional patterning or increased via spacing will decrease achievable density of the final place-and-route solution, worsening die area and product cost. Also, the rapid increase of interconnect RC leads to not only performance loss from interconnect delay increase, but circuit power and area degradation as well. Optimization of BEOL dimensions (i.e., wire width, spacing and thickness subject to a given layer's pitch constraint) across the entire metal layer stack is crucial to achieve better product performance, power, area and cost.

### 1.2 This Thesis

To address the new challenges in modern SoC physical design and signoff in advanced nodes, this thesis presents new physical optimization and technology assessment methodologies. Figure 1.2 illustrates the scope and organization of this thesis, in which three main thrusts respectively address three major challenges:

- Post-placement gate sizing optimization;

- Detailed placement optimization; and

- Evaluation of design enablement.

To address the explosion of corners and modes in timing signoff and the emergence of new sizing-placement interactions, the *post-placement gate sizing optimization* thrust of this thesis presents a gate sizing optimization considering multi-corner multi-mode constraints; a minimum implant rule-aware gate sizing and placement co-optimization; and heuristics for potential fine-grain exploitation of FDSOI technologies.

To address the challenges to scaling brought by new placement rules and reduced-track cell architectures, the *detailed placement optimization* thrust of this thesis presents an integer linear programming-based incremental detailed placement optimization that considers inter-row and intra-row placement constraints; and a detailed placement optimization that reduces wirelength in the context of new cell architectures with vertical M1 pins.

To address the need for design-technology co-optimization, the *evaluation of design enablement* thrust of this thesis presents analyses of impacts of patterning technology choices and associated routing rules on physical implementation density; a study of impacts of BEOL dimensions on block-level power and area; and a methodology for assessment of routing capacity of a BEOL stack as well as inherent capability of routers.

The remainder of this thesis is organized as follows.

Figure 1.2: Scope and organization of this thesis.

• Chapter 2 presents three distinct gate sizing methodologies that address new challenges in timing signoff, and the interaction between sizing and detailed placement. First, we study important constraints of modern industrial designs that are generally not comprehended by previous academic sizing works. In our study, we point out that various optimization techniques used in academic sizers can fail to offer benefits in product design contexts due to differences in the underlying optimization formulation and constraints. To address this gap, we develop a new robust academic sizer, *Sizer*, from a fresh implementation of *Trident* [84]. Experimental results show that Sizer is able to achieve up to 10% leakage power and 4% total power reductions compared to leading commercial tools on designs implemented with foundry technologies, and 7% leakage power reduction on a modern industrial design in the multi-corner multi-mode (MCMM) context. Second, we propose heuristic methods that fix MinIA violations and reduce power with gate sizing, while minimizing placement perturbations

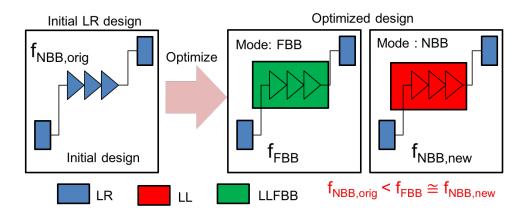

that potentially create extra timing violations. Compared to recent versions of commercial place-and-route (P&R) tools, our methodologies achieve significant reductions (up to 100%) in the number of MinIA violations while satisfying timing and power constraints. Third, we study heuristic methods for potential exploitation of fine-grained mixed-Vt (and body biasing) in FDSOI implementation, via a novel "speed domain partitioning" (SDP) problem formulation. We explore a broad space of implementation flows, then perform a detailed investigation of two implementation flows: an integer linear programming (ILP)-based approach, and a sensitivity function-based heuristic approach. For implementations using "generic" library options, up to 20% speed improvement with 53% LL region area is seen for one out of four testcases studied. For implementations using "rich" library options, up to 7% speed improvement with 26% LL region area is achieved. In our experiments, we observe that outcomes are strongly library- and design-dependent. We therefore provide a discussion of root-cause, intrinsic difficulties of fine-grained exploitation of mixed-Vt in FDSOI technology. We furthermore suggest a "decision tree" to help assess a design's amenability to fine-grained mixed-Vt (as well as body-biasing based) implementation, and to help guide design flow selection for better design QoR.