## **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

#### **Title**

Graphene Device Fabrication and Applications in Communication Systems

#### **Permalink**

https://escholarship.org/uc/item/1796k64w

#### **Author**

Liu, Guanxiong

### **Publication Date**

2012

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Graphene Device Fabrication and Applications in Communication Systems

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Guanxiong Liu

June 2012

Dissertation Committee:

Dr. Alexander A. Balandin, Chairperson

Dr. Roger Lake Dr. David Kisailus

| The Dissertation of Guaxiong Liu is approved by: |                       |  |

|--------------------------------------------------|-----------------------|--|

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  |                       |  |

|                                                  | Committee Chairperson |  |

|                                                  |                       |  |

|                                                  |                       |  |

University of California, Riverisde

### Acknowledgements

First and foremost, I would like to express my deep appreciation to my advisor, Professor Alexander A. Balandin. He is a very knowledgeable, insightful and encouraging professor, and guided me to the right direction many times in my research work. At the same time, he gave me a lot of freedom in doing all kinds of research experiment that I want, even when the experiment seemed to be of only minor meaning. Also, Professor Balandin offered me a lot of great opportunities to attend conference all around the world. He also coached me on my presentation skills and the ways to talk with world class researchers.

I would also like to thank our previous group member Dr. Qinghui Shao, who was very helpful and patient in training me with the cleanroom fabrication techniques when I was a rookie member in the lab. Moreover, he was very kind in sharing with me his knowledge about the semiconductor physics which helped me to understand the basics of graphene that I started to work on for the following five years.

I am grateful to other previous group members Dr. Desalegne Teweldebrhan, Dr. Irene Calizo, Dr. Muhammad Rahman Dr. Suchismita Ghosh, Dr. Samia Subrina, Dr. Viveck Goyal, Dr. Craig Nolen, Dr. Md. Zahid Hossain, and Dr. Javed Khan, as well as current members Zhong Yan, Jie Yu and Pradumna Goli for their helpful discussions and contributions towards my research work.

I am thankful to cleanroom stuff Dexter Humphrey, Dong Yan and Mark Heiden for their great help in training me with cleanroom fabrication skills and useful discussions on my experiments.

I would also like to thank the researches that I worked with when I did internship at IBM T.J. Watson Research Center during 2010 summer. They are my mentor Dr. Christos Dimitrakopoulos, who guided me in using excellent chemicals to pattern graphene; my manager Dr. Alfred Grill, who provided me almost all kinds of resources to complete my project; my collaborators Dr. Yu-Ming Lin and Dr. Yanqing Wu, who helped me with device fabrications and measurement; Dr. Joy Cheng, who advised me in using chemicals which was entirely new to me.

I also want to thank our research collaborators Prof. Sergey Rumyantsev (Rensselaer Polytechnic Institute), who taught and advised me how to setup the low-frequency noise system and the measurement techniques; Prof. Michael Shur (Rensselaer Polytechnic Institute), who provided helpful and insightful discussions to our projects; Prof. Kartik Mohanram (now at Pittsburg University), who brought the idea of triple-mode amplifier by using graphene; Xuebei Yang (Rice University), whom I worked together with to demonstrate the graphene amplifier.

Finally but not least, I would like to thank my parents Liang Liu and Juan Li for providing their love, support, and understanding through all my educational endeavors. It is my father's passion towards science that encourages me to finish my PhD study; it is my mother's love that alleviates my anxiety when I encountered the new environment

away from home. Without their spiritual and financial supports, I would not be able to continue and successfully finish my educational life.

## Dedication

To my parents Liang Liu and Juan Li.

谨以此文献给我的父亲刘良,母亲李娟。

#### ABSTRACT OF THE DISSERTATION

Graphene Device Fabrication and Applications in Communication Systems

by

#### Guanxiong Liu

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, June 2012 Professor Alexander A. Balandin, Chairperson

High carrier mobility, saturation velocity and thermal conductivity make graphene a promising material for high-frequency, analog and communication applications. The ambipolar properties of graphene provide opportunities for increased functionality in unconventional circuit architectures. In this dissertation, I describe the fabrication process of graphene devices, including the optical and Raman spectroscopic characterization and electron-beam lithography. The different electrical characteristics of the single-layer and bilayer graphene field-effect devices reflect differences in the electron band structures of the two systems. The fabricated graphene transistors have been used to design and experimentally demonstrate electronic circuits with communication functionalities such as phase-shift keying, frequency-shift keying and phase detection. Compared with conventional semiconductor electronic designs based on multiple unipolar transistors, the demonstrated graphene amplifiers and phase detectors have advantage of a simplified

structure. An important issue for high-frequency and analog applications is the low-frequency noise, which up-converts and contributes to the phase noise of the systems. It was found that the low-frequency noise in graphene devices is dominated by 1/f noise in the frequency range from 1 Hz to 100 kHz (f is the frequency). The device exposure to different gases results in appearance of characteristic peaks in the noise spectral density. The latter can be utilized for selective gas sensing with graphene. The metal-graphene contact contributions to the 1/f noise can be strongly reduced via the use of the graded thickness graphene channels in the device structure. I have also investigated a possibility of tuning graphene properties via controllable exposure to the low-energy electron-beam irradiation. It was found that the charge neutrality point and resistivity can be tuned over a wide range of values. The obtained results are important for the proposed applications of graphene in analog electronics, communications and sensors.

## Contents

| Lis | st of Figures                                                         | xii |

|-----|-----------------------------------------------------------------------|-----|

| Lis | st of Tables                                                          | xvi |

| 1.  | Introduction and overview.                                            | 1   |

|     | 1.1 Introduction                                                      | 1   |

|     | 1.2 Overview.                                                         | 2   |

|     | Reference                                                             | 3   |

| 2.  | Graphene device fabrications                                          | 5   |

|     | 2.1 Graphene samples preparation                                      | 5   |

|     | 2.2 E-beam lithography                                                | 7   |

|     | 2.3 Dual-gate graphene field-effect transistors.                      | 8   |

|     | 2.4 Etching graphene.                                                 | 11  |

|     | Reference                                                             | 13  |

| 3.  | Electrical Characterization of Graphene Devices.                      | 14  |

|     | 3.1 Electrical measurement of back-gate graphene devices              | 14  |

|     | 3.2 Electrical measurement of dual-gate single layer graphene devices | 18  |

|     | 3.3 Electrical measurement of dual-gate bilayer graphene devices      | 28  |

|     | Reference                                                             | 36  |

| 4.  | Analog Applications of Graphene                                       | 38  |

|     | 4.1 Introduction.                                                     | 38  |

|     | 4.2 Phase Shift Keying and Frequency Shift Keying                     | 38  |

|    | 4.3 Phase Detector.                                            | 52   |

|----|----------------------------------------------------------------|------|

|    | 4.4 Summary                                                    | 56   |

|    | Reference                                                      | 57   |

| 5. | Low-Frequency Noise in Graphene.                               | 59   |

|    | 5.1 Introduction of low-frequency noise                        | 59   |

|    | 5.2 Noise measurement setup.                                   | . 61 |

|    | 5.3 Low-frequency noise in back-gate graphene transistor       | 64   |

|    | 5.4 Low-frequency noise in top-gate graphene transistor        | . 68 |

|    | 5.5 Noise reduction in graded thickness graphene.              | . 70 |

|    | 5.6 Summary                                                    | 77   |

|    | Reference                                                      | 79   |

| 6. | Modification of Graphene through E-beam Irradiation            | 82   |

|    | 6.1 Introduction of Quality control through Raman Spectroscopy | 82   |

|    | 6.2 E-beam irradiation effects on single layer graphene        | 85   |

|    | 6.3 E-beam irradiation effects on bilayer graphene             | 93   |

|    | 6.4 Summary                                                    | 98   |

|    | Reference                                                      | 99   |

| 7  | Summary                                                        | 101  |

# List of Figures

| List of Figuresxii                                                                                        |

|-----------------------------------------------------------------------------------------------------------|

| List of Tables. xvi                                                                                       |

| Fig. 2.1. Optical image of graphene on SiO <sub>2</sub> substrate. 5                                      |

| Fig. 2.2. Raman spectra of single layer graphene (SLG) and bi-layer graphene (BLG) 6                      |

| Fig. 2.3. The process of a typical electron beam lithography                                              |

| Fig. 2.4. Optical image of a typical graphene device made by EBL                                          |

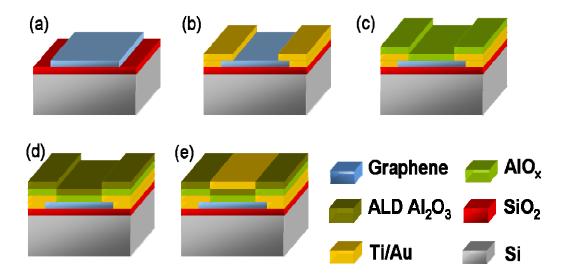

| Fig. 2.5. Fabrication process of dual-gate graphene device                                                |

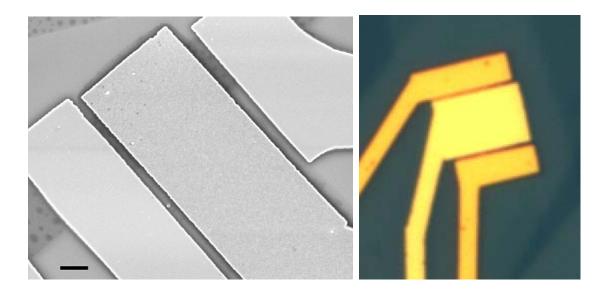

| Fig. 2.6. (a) SEM image and (b) optical image of dual-gate graphene device                                |

| Fig. 2.7. Etching graphene into the pattern of Nano-Device Laboratory logo and UCR                        |

| logo                                                                                                      |

| Fig. 3.1. (a) Schematics of electrical measurement of back-gate graphene device. (b)                      |

| Typical $I_{DS}$ - $V_{BG}$ curve of SLG device with mobility as high as 6900 cm2/Vs                      |

| Fig. 3.2. Typical transfer characteristics of BLG back-gate device                                        |

| Fig. 3.3. Schematics of electrical measurement of dual-gate graphene device                               |

| Fig. 3.4. (a) The current $I_{DS}$ as a function of top-gate $V_{TG}$ sweep under different back-gate     |

| $V_{BG}$ bias. (b) The current $I_{DS}$ as a function of $V_{BG}$ sweep under different $V_{TG}$ bias 21  |

| Fig. 3.5. (a) THe CNP position as a function of $V_{\text{BG}}$ . (b) The fitting results based on the    |

| resistance model of graphene dual-gate transistor. 22                                                     |

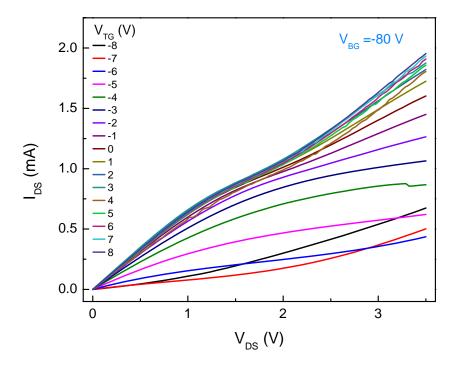

| Fig. 3.6. (a) Low-bias ( $I_{DS}$ - $V_{DS}$ ) output characteristics of dual-gate SLG transistor. Linear |

| relation is observed under various gate voltage. (b) High-bias output characteristics of                  |

| dual-gate SLG transistor under different top-gate voltage at fixed back-gate                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>BG</sub> =40V                                                                                                                               |

| Fig. 3.7. Explanation of the saturation and de-saturation effects on graphene dual-gate                                                            |

| devices. 27                                                                                                                                        |

| Fig. 3.8. Electrical characteristics of dual-gate BLG device. 29                                                                                   |

| Fig. 3.9. The electrical filed induced band gap versus back-gate bias                                                                              |

| Fig. 3.10. High field electrical measurement of dual-gate BLG devices                                                                              |

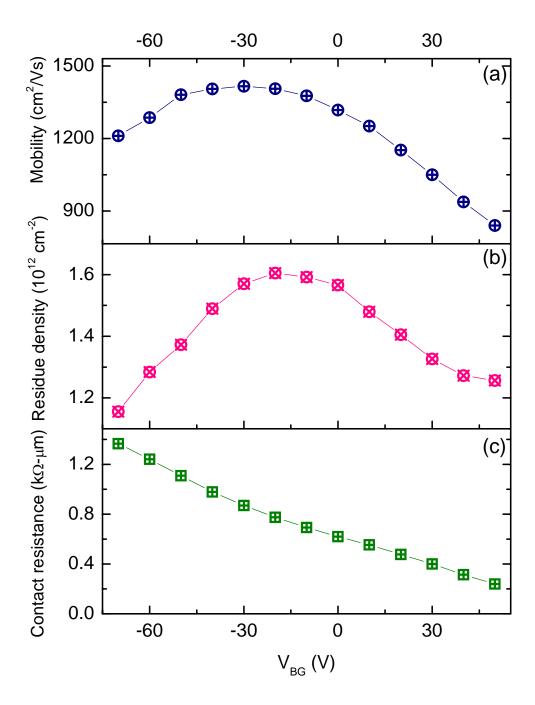

| Fig. 3.11. (a) The carrier mobility as a function of $V_{\text{BG}}$ . (b) The residue carrier                                                     |

| concentration reflects the conductivity at the CNP.(c) The width normalized contact                                                                |

| resistance decreases as the back-gate voltage increases                                                                                            |

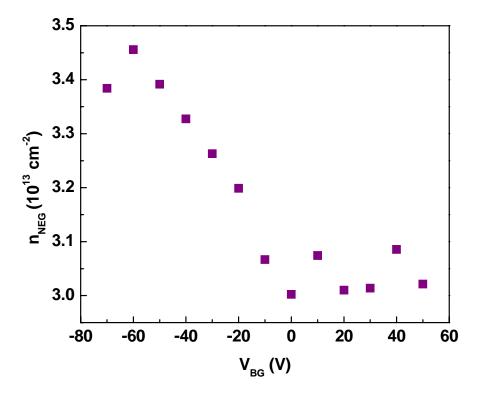

| Fig. 3.12. The carrier concentration when the negative transconductance appears as a                                                               |

| function of back-gate bias. 34                                                                                                                     |

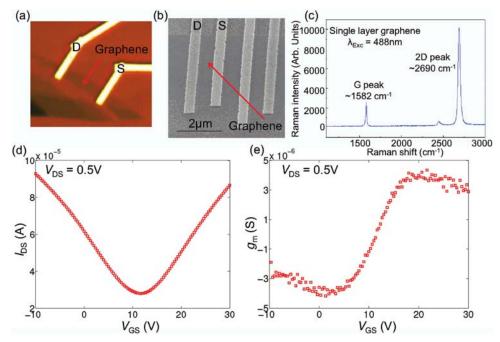

| Fig. 4.1 (a) Optical micrograph image of a representative fabricated back-gated graphene                                                           |

| transistor. (b) SEM image of source and drain electrodes of a representative back-gated                                                            |

| graphene transistor. (c) The Raman spectrum of the singlelayer graphene. (d) $I_{DS}\text{-}V_{GS}$                                                |

| characteristics of the graphene transistor for $V_{DS}$ =0.5 V. The current is minimum at the                                                      |

|                                                                                                                                                    |

| charge neutrality point. (e) $g_m$ -V <sub>GS</sub> characteristics for $V_{DS}$ =0.5 V. The transconductance                                      |

| charge neutrality point. (e) $g_m$ - $V_{GS}$ characteristics for $V_{DS} = 0.5$ V. The transconductance $g_m$ is 0 at the charge neutrality point |

|                                                                                                                                                    |

| g <sub>m</sub> is 0 at the charge neutrality point. 41                                                                                             |

| g <sub>m</sub> is 0 at the charge neutrality point                                                                                                 |

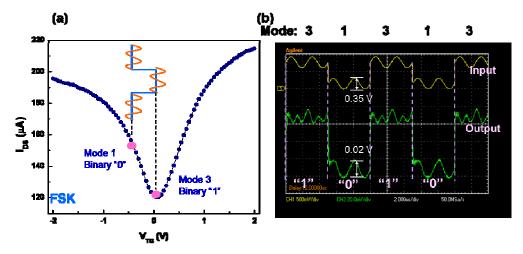

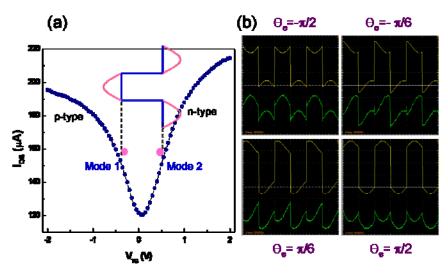

| Fig. 4.4. The results for three-mode amplifier build on top-gate graphene device                  | 47    |

|---------------------------------------------------------------------------------------------------|-------|

| Fig. 4.5. Experimental results for BPSK modulation.                                               | 50    |

| Fig. 4.6. Experimental results for BFSK modulation.                                               | 51    |

| Fig. 4.7. Schematic of the proposed graphene multiplier phase detector                            | 53    |

| Fig. 4.8. Experimental results for phase detector.                                                | 55    |

| Fig. 4.9. DC component $u_{out}$ at different $\theta_e$ (in degree) between $u_1$ and $u_2$      | 56    |

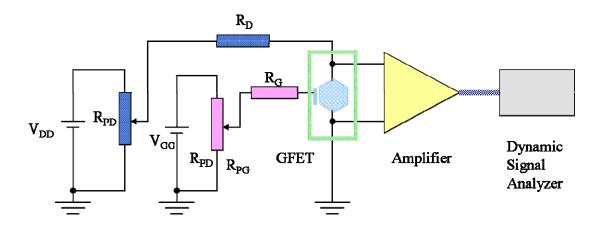

| Fig. 5.1. Schematic of the graphene device noise measurement of Graphene FET (GF                  | ET)   |

| is biased with quiet battery and potential meter circuit.                                         | 63    |

| Fig. 5.2. Noise measurement setup inside the shielding box                                        | 63    |

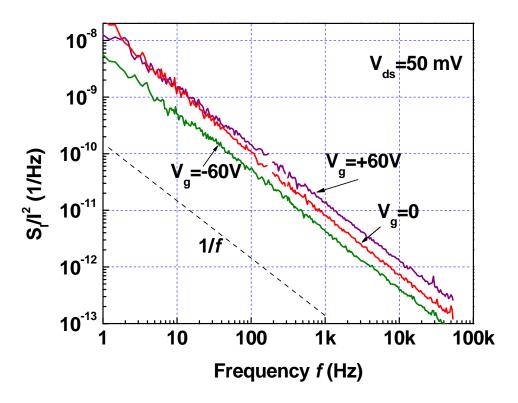

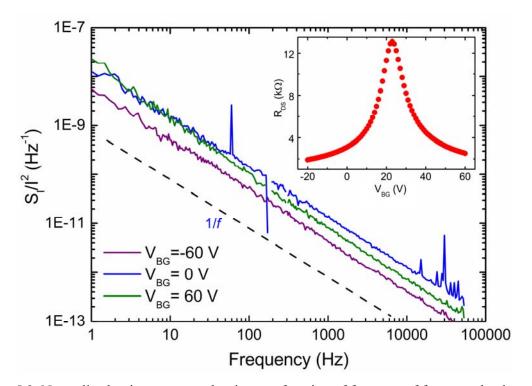

| Fig. 5.3. Normalized spectrum density of graphene back-gate transistors under diffe               | rent  |

| gate bias                                                                                         | 66    |

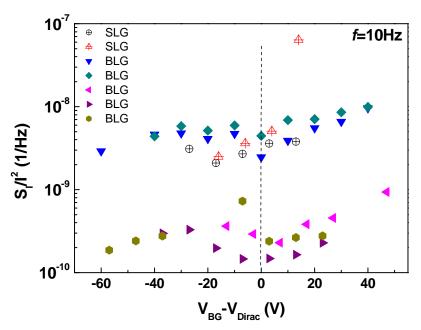

| Fig. 5.4. Normalized noise spectral density $S_{I}$ / $I^{2}$ for several devices as functions of | the   |

| gate bias                                                                                         | 67    |

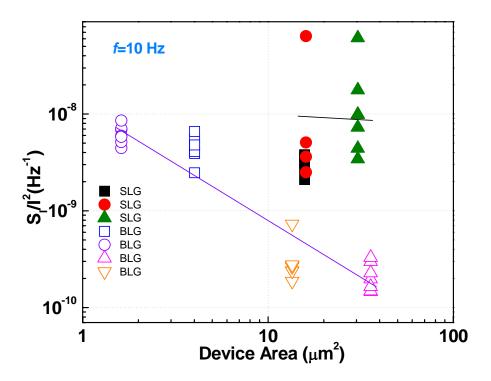

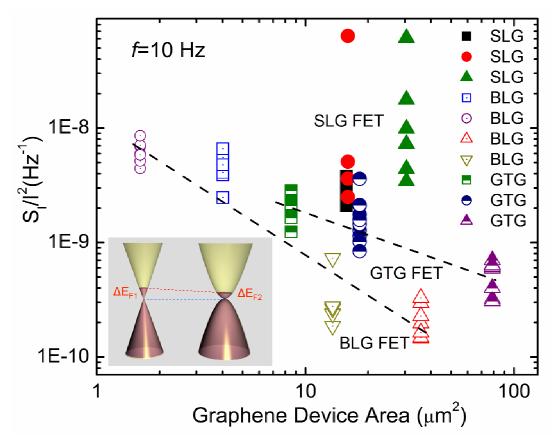

| Fig. 5.5. The noise spectral density as a function of device area size                            | 68    |

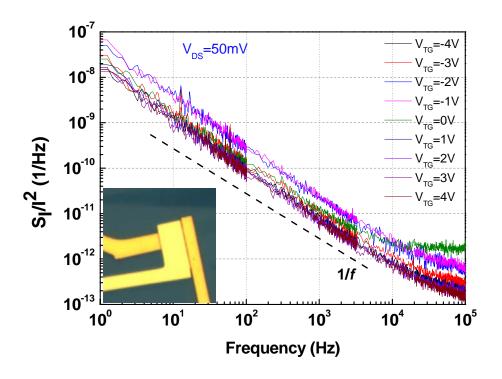

| Fig. 5.6. (a) Noise spectral density of a top-gate BLG graphene device under diffe                | erent |

| gate bias. (b) The gate dependence of noise and the $I_{DS}\text{-}V_{GS}$ characteristics        | 69    |

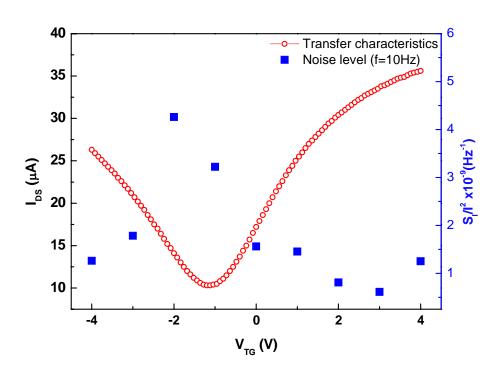

| Fig. 5.7. Schematic of the proposed graphene graded-thickness field-effect transistors            | and   |

| an optical microscopy image showing one of such devices.                                          | 71    |

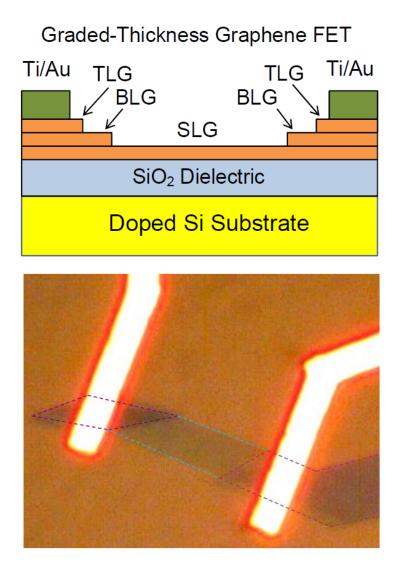

| Fig. 5.8. Raman spectra from different regions of the same flake used for fabrication             | n of  |

| the channel of the graphene graded-thickness transistor.                                          | 72    |

| Fig. 5.9. Normalized noise spectrum density as a function of frequency f for sev                  | eral  |

| values of the back-gate bias                                                                      | 73    |

| Fig. 5.10. Normalized noise spectral density of the GTG FETs and the reference SLG and         |

|------------------------------------------------------------------------------------------------|

| BLG FETs as the function of the graphene channel area                                          |

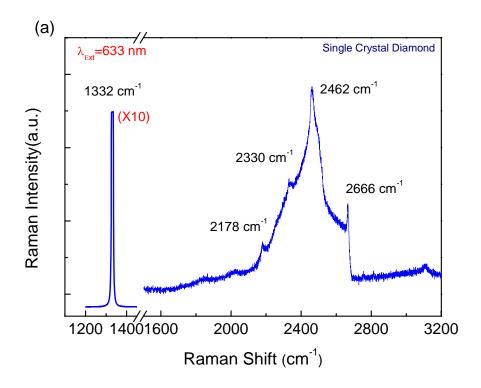

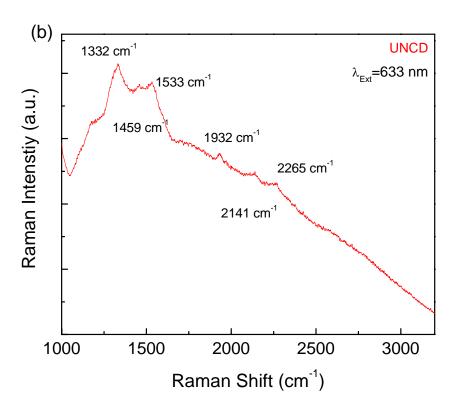

| Fig. 6.1. Raman spectrum of (a) synthetic single crystal diamond and (b) ultra nano            |

| crystalline diamond (UNCD). The numbers indicates the positions of the peaks 83                |

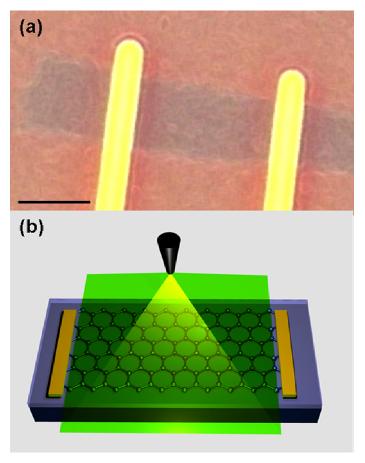

| Fig. 6.2. (a) Optical image of a typical graphene device used in this work. (b) Schematic      |

| of the irradiation by the electrion beam. 87                                                   |

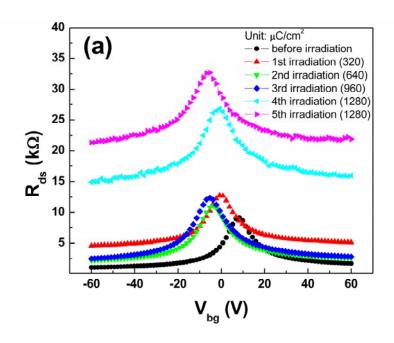

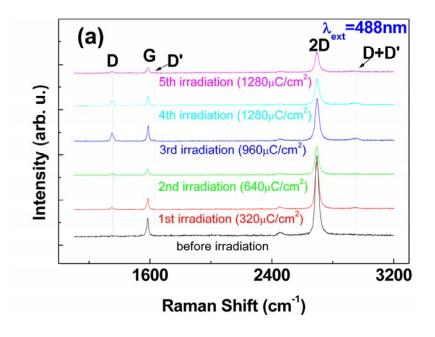

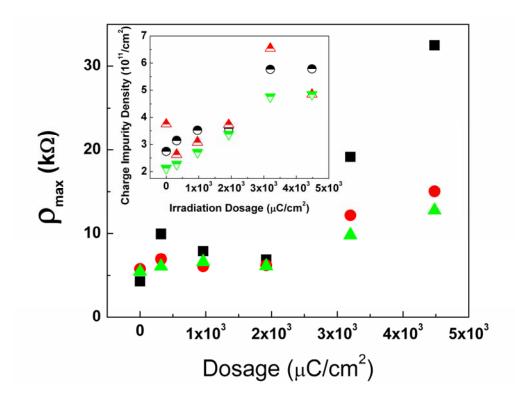

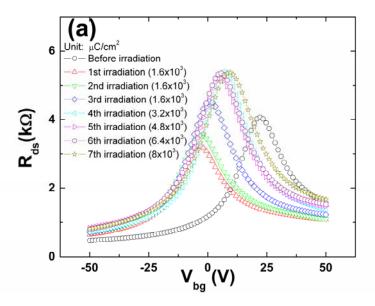

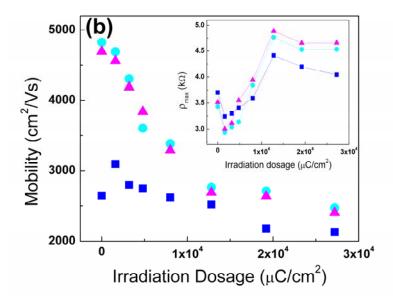

| Fig. 6.3. (a) Evolution of the transfer characteristics of SLG with increasing irradiation     |

| dose. The electrical resistance of SLG devices was measured after each irradiation step.       |

| (b) Charge carrier mobility as a function of the irradiation dose for three SLG devices,       |

| represents by red, green and black data points, respectively                                   |

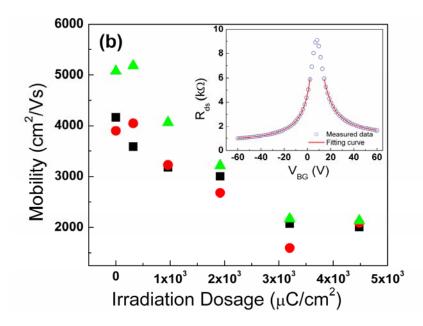

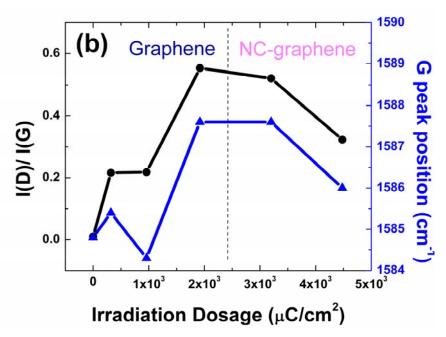

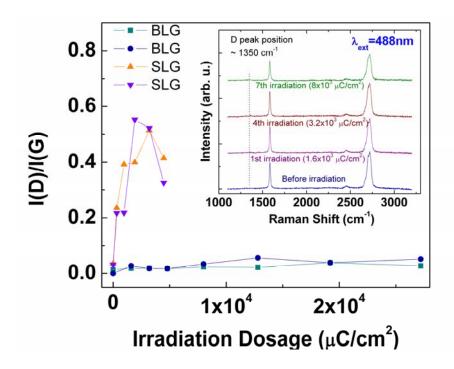

| Fig. 6.4. (a) Evolution of Raman spectrum of SLG with increasing irradiation dose. (b)         |

| The ratio I(D)/I(G) initially increases with the irradiation dose but starts to decrease after |

| the 3 <sup>rd</sup> irradiation step                                                           |

| Fig. 6.5. Evolution of SLG resistivity with irradiation dose                                   |

| Fig. 6.6. (a) Evolution of the transfer characteristics of BLG with increasing irradiation     |

| dose. (b) Carrier mobility of BLG devices as a function of the irradiation dose for three      |

| BLG devices95                                                                                  |

| Fig. 6.7. Evolution of Raman spectrum of BLG with increasing irradiation dose 96               |

## List of Tables

| Table 2.1. Oxygen Plasma etching recipe for etching graphene           | 12 |

|------------------------------------------------------------------------|----|

| Table 6.1. The Raman peak assignment of single crystal diamond         | 84 |

| Table 6.2. The Raman peak assignment of ultra nano crystalline diamond | 84 |

## Chapter 1

#### **Introduction and Overview**

#### 1.1 Introduction

Graphene, a single layer of carbon atoms arranged in honeycomb lattice, is probably the most discussed new material ever since its experimental discovery in 2004 [1]. Its giant carrier mobility [2], large thermal conductivity [3] and extreme thickness of only one atomic layer, as well as high intrinsic mechanical strength [4] make it very interesting among many fields such as physics, chemistry, materials and electrical engineering. The theoretical investigations of graphene, about half-century ahead of its experimental demonstration, were conducted to understand the electronic properties of graphite[5, 6], which is an important material for nuclear reaction. It had been predicted thermodynamically unstable due to the pure two dimension crystal structure [7, 8] and should not exist in real world. However, this exiting material has been experimentally discovered in 2004 by a very rudimentary but robust method of using adhesive tape [1]. Since graphene produced by this method is boned to a substrate, it is not contradicted to the thermodynamics argument of 2D crystals [9, 10]. Ever since the exploration of the excellent properties of graphene, numerous novel applications have been demonstrated based on graphene, such as high speed electronics [11, 12], thermal management [13], mechanical oscillator [14], as well as graphene sensors [15]. The first graphene production was made by exfoliating

graphite by adhesive tape [1]. The chemical methods, chemical vapor deposition (CVD) [16] and epitaxail growth method [17], had been invented to growth high quality and large scale graphene. Yet, the simplest method, exfoliation mean, still provides better graphene than the other two methods.

#### 1.2 Overview

In chapter 2, the graphene device fabrication processes are described in details. Both back-gate and top-gate devices are included. In chapter 3, electrical measurement and results on single layer garphene and bilayer graphene transistors are discussed in depth. Chapter 4 presents the application of graphene in analog communication systems. We experimentally demonstrate functionalities of phase shift keying, frequency shift keying and phase detector. Chapter 5 discusses the low-frequency noise in graphene, which is an important issue for device working in analog systems. Chapter 6 presents the study of tuning graphene electrical and material properties by means of electron beam irradiation. Chapter 7 is the summary.

#### Reference

- [1] K.S. Novoselov, A.K. Geim, S.V. Morozov, D. Jiang, Y. Zhang, S.V. Dubonos, I.V. Grigorieva and A.A. Firsov, *Science*, **306**, 666 (2004).

- [2] K. Bolotin, K.J. Sikes, Z. Jiang, M. Klima, G. Fudenberg, P.K. J. Hone and H.L. Stormer, *Solid State Commun.*, **146**, 351 (2008).

- [3] A.A. Balandin, S. Ghosh, W. Bao, I. Calizo, D. Teweldebrhan, F. Miao and C.N. Lau, *Nano Lett.*, **8**, 902 (2008).

- [4] C. Lee, X. Wei, J.W. Kysar and James Hone, *Science*, **321**, 385 (2008).

- [5] P. R. Wallace, *Phys. Rev.*, **71**, 622 (1947).

- [6] J.C. Slonczewski and P.R. Weiss, *Phys. Rev.*, **109**, 272 (1958).

- [7] L. Landau, Physikalische Zeitschrift der Sowjetunion 11, 26 (1937).

- [8] N.D. Mermin, *Phys. Rev.*, **176**, 250 (1968).

- [9] C. Oshima and A. Nagashima, J. Phys.: Condens. Matter, 9, 1 (1997).

- [10] A.E. Karu and M. Beer, Pyrolytic *J. Appl. Phys.*, **37**, 2179 (1966).

- [11] Y.-M. Lin, C. Dimitrakopoulos, K.A. Jenkins, D.B. Farmer, H.-Y. Chiu, A. Grill and P. Avouris, *Science*, **327**, 662 (2010).

- [12] L. Liao, Y.-C. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K.L. Wang, Y. Huang and X. Duan, *Nature*, **467**, 305 (2010).

- [13] Z. Yan, G. Liu, J.M. Khan and A. A. Balandin, *Nat. Comm.* (2012) in print.

- [14] Y. Xu, C. Chen, V. V. Deshpande, F. A. DiRenno, A. Gondarenko, D. B. Heinz, S. Liu, P. Kim and J. Hone, *Appl. Phys. Lett.*, **97**, 243111 (2010).

- [15] S. Rumyantsev, G. Liu, M. Shur, R.A. Potyrailo and A.A. Balandin, *Nano Lett.*,100, 033103 (2012).

- [16] X. Li, W. Cai, J. An, S. Kim, J. Nah, D. Yang, R. Piner, A. Velamakanni, I. Jung,E. Tutuc, S.K. Banerjee, L. Colombo and R.S. Ruoff, *Science*, 324, 1312 (2009).

- [17] C. Berger, Z. Song, X. Li, X. Wu, N. Brown, C. Naud, D. Mayou, T. Li, J. Hass, A.N. Marchenkov, E.H. Conrad, P.N. First and W.A. de Heer, *Science*, **3012**, 1191 (2006)

## Chapter 2

## **Graphene Device Fabrications**

### 2.1 Graphene Samples Preparation

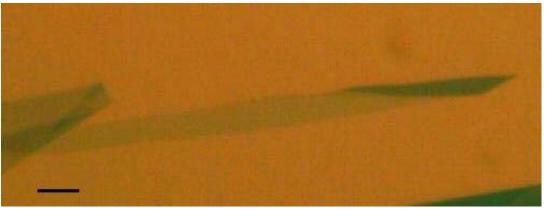

We use mechanical exfoliation method to produce graphene. The fabrication starts with peeling graphite from bulk material HOPG (highly ordered pyrolytic graphite) by adhesive tape, and then the tape are gently scrubbed onto a SiO<sub>2</sub> substrate. The thickness of the SiO<sub>2</sub> has to be carefully selected in order to have good optical contrast of graphene, so that we can see this atomic thin material under the optical microscope [1]. We choose the substrate with 300 nm SiO<sub>2</sub>. A typical optical image is shown in Fig. 2.1.

Fig. 2.1 Optical image of graphene on  $SiO_2$  substrate. The light blue ribbon in the center is single layer graphene. The scale bar is 3  $\mu$ m.

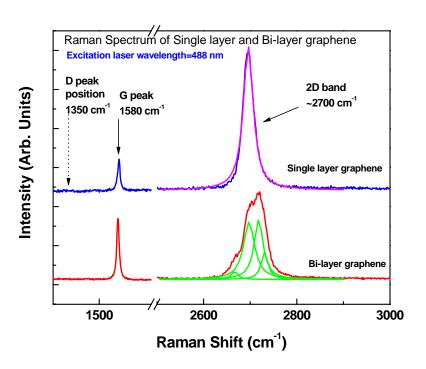

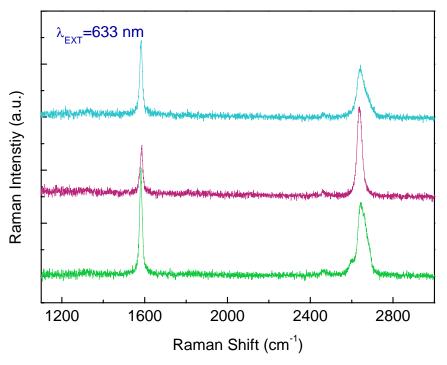

This method yields good quality of graphene that can be validated by Raman spectroscopy. The amount of defects in crystal material is a significant issue. As the defect in a pure crystal has a different dispersion relation, a distinctive peak will

appear on the Raman spectrum. In graphene, a D peak at 1350 cm<sup>-1</sup> characterizes the defects in this sp<sup>2</sup> carbon. Fig. 2.2 shows the Raman spectrum of a SLG and BLG. Note that the absence of D peak in both spectrum. Another important reason of using Raman to characterize graphene is that this technique can distinguish the number of layers of graphene through de-convolution method of 2D band. In SLG, the 2D band (2700 cm<sup>-1</sup>) can be fitted by only one elementary Lorenzian peak, where in BLG this band needs 4 Lorenzian peaks to fit [2, 3]. Meanwhile, the intensity ratio of 2D band over G peak (1580 cm<sup>-1</sup>) for SLG is about 3-4, which is much larger than the ratio of BLG with about 1.

Fig. 2.2. Raman spectra of single layer graphene (SLG) and bi-layer graphene (BLG). The number of layer can be distinguished by de-convolution method. The 2D band of SLG can be fitted by only one elementary Lorenzian peak, where the BLG needs four peaks to fit. Also the intensity ration of 2D over G peak for SLG is much larger than BLG. Meanwhile, the good crystal quality can be characterized by the absence of D peak at 1350 cm<sup>-1</sup>.

## 2.2 E-beam Lithography

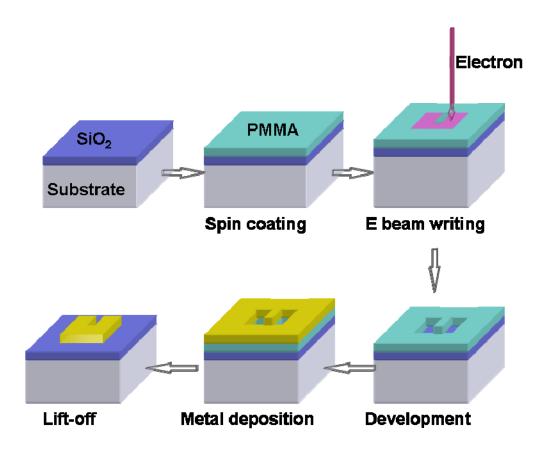

E-beam Lithography (EBL) is a lithography process that uses a focused electron beam to form patterns needed for material deposition on, or removal from the target substrate. Comparing with optical lithography which uses UV light, EBL offers higher patterning resolution because of the shorter wavelength possessed by the 10-50 keV electrons. The current technology allows a small-diameter focused beam of electrons to scan over a surface, while the EBL system does not need masks to perform its mask (unlike optical lithography, which uses photo-masks to project the patterns). An EBL system simply "draws" the pattern over the resist coated wafer using the electron beam. A typical EBL system consists of the following parts: 1) an electron gun or electron source that supplies the electrons; 2) an electron column using lenses and electrodes to "shapes" and focuses the electron beam; 3) a mechanical stage that positions the wafer under the electron beam; and 5) a computer system that controls the equipment.

Fig. 2.3 shows a typical EBL process from very beginning to final lift-off. Electron beam resist Polymethyl methacrylate (PMMA), with high resolution, is spin coated on the sample surface. Then e-beam expose the selected area, making the exposed area is soluble in the developer solution. After development, electron beam evaporator is used to deposit a layer of metal on the sample surface. Then lift-off is performed to remove the unexposed PMMA together with metal on it and leave the designed pattern filled with metal.

Fig. 2.3 The process of a typical electron beam lithography. The e-beam resist PMMA is coated on the substrate. E-beam writes on the designed region to expose the PMMA. The irradiated PMMA will be dissolved in the developer and then followed by metal deposition. Lift-off process will remove the metal on un-exposed PMMA and leave the designed pattern with metal.

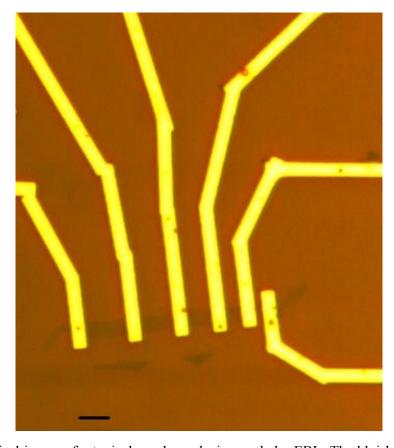

Since the exfoliated graphene flakes have random location on the substrate, we will need to fabricate alignment marks close to the graphene flakes, which help the electrodes and other patterns to be located accurate on the desired location. Fig. 2.4 is the optical image of a typical graphene device.

## 2.3 Dual-Gate Graphene Field Effect Transistors

In order to make graphene devices to work in a similar way such as MOSFET,

we need to make top-gate graphene devices. Since we always have the back-gate, an additional gate will make the device a dual-gate device. The key challenge here is to make good quality top-gate oxide with low gate leakage current and the method by which oxide is deposit does not introduce substantial defects to the graphene.

Fig. 2.4. Optical image of a typical graphene device made by EBL. The bluish color flake is graphene. The scale bar is 3  $\mu m$ .

There are several methods of gate oxide deposition, such as PECVD, E-beam evaporation, atomic layer deposition (ALD), etc. PECVD requires plasma involved in the deposition process, however, plasma enhanced gases molecule will attack graphene surface and even remove it. E-beam evaporation needs to reach a very low pressure (10<sup>-9</sup> torr) to get a high quality of oxide. In contrast, ALD does not needs that

high vacuum and the process will not generate energetic molecules, which is perfect for making top gate oxide for graphene.

However, the high quality clean graphene surface is hydrophobic, forbidden the direct ALD growth. A seeding layer that can help the following layer to grow uniform oxide is needed to coat on graphene. We here choose to deposit a thin layer of aluminum with 2 nm, and this aluminum can easily get oxidized in air so that it would not short the graphene channel, and this oxidized aluminum can provide a good surface for the next step of ALD [4]. The dual-gate graphene device fabrication is illustrated in the Fig. 2.5. The quality of this oxide stacking layer is proved by the very small gate leakage current and decent graphene device mobility.

Fig. 2.5. Fabrication process of dual-gate graphene device. (a) Identify graphene flake on  $SiO_2$  substrate. (b) Make source/drain contact by EBL and evaporation, the metal we use is Ti/Au (6/60 nm). (c) Deposit a thin layer of Al (2 nm) by evaporation, and store in air for self-oxidation. (d) Grow ALD oxide at low temperature 110°C. (e) Make gate electrode by EBL and evaporation.

Fig. 2.6. (a) SEM image and (b) optical image of dual-gate graphene device. Scale bar is 1  $\mu m$ .

## 2.4 Etching Graphene

Exfoliated graphene often has random shape as we transfer them on the substrate. When we want to study a regular shape or sometimes a specific designed shape, we need to pattern the graphene, and etch the excessive portion. This can be done by using EBL to draw a mask pattern and then use Oxygen Plasma to remove the uncovered regions.

We use reactive ion etching (RIE) tools to perform the graphene etching, the recipe is listed in below table. The etching speed of graphene is actually very fast considering the thickness is only 0.34 nm. It usually takes 6-8 sec to remove one layer using our recipe. The PMMA mask turns out to protect the un-exposed graphene very well. Fig. 7 shows the etching results that patterns a graphene flake into UCR logo and Nano-Device Laboratory logo.

| RIE r.f. power           | 50 W          |

|--------------------------|---------------|

| O <sub>2</sub> flow rate | 50 sccm       |

| Pressure                 | 30 mTorr      |

| Time                     | 6-8 sec/layer |

| Mask                     | PMMA          |

Table 2.1. Oxygen Plasma etching recipe for etching graphene.

Fig. 2.7. Etching graphene into the pattern of Nano-Device Laboratory logo and UCR logo. The dark color regions are graphene and the light color is the substrate. The scale bar is  $2\mu m$ .

## Reference

- [1] P. Blake, E.W. Hill, A.H.C. Neto, K.S. Novoselov, D. Jiang, R. Yang, T.J. Booth and A.K. Geim, *Appl. Phys. Lett.*, **91**, 063124 (2007)

- [2] A.C. Ferrari, J.C. Meyer, V. Scardaci, C. Casiraghi, M. Lazzeri, F. Mauri, S. Piscanec, D. Jiang, K.S. Novoselov, S. Roth and A.K. Geim, *Phys. Rev. Lett.*, **97**, 187401 (2006).

- [3] I. Calizo, F. Miao, W. Bao, C.N. Lau and A.A. Balandin, *Appl. Phys. Lett.*, **91**, 071913 (2007).

- [4] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc and S. Banerjee, *Appl. Phys. Lett.*, **94**, 062107 (2009).

## Chapter 3

## Electrical Characterization Graphene Devices

#### 3.1 Electrical Measurement of Back-Gate Graphene Device

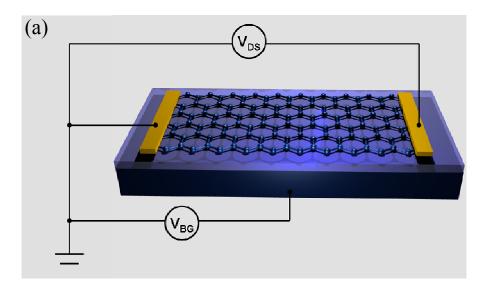

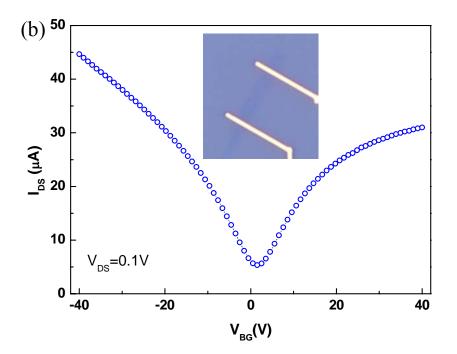

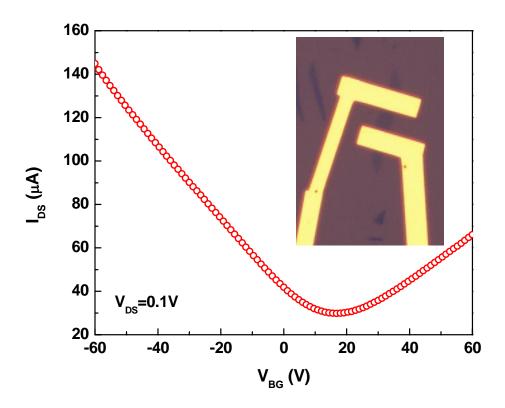

Graphene is a very good conducting material considering its single atomic layer thickness. The sheet resistance at low temperature is around the 6.4 K $\Omega$ . What's more interesting is that the conductivity can be tuned by changing the Fermi level of graphene. Due to the linear dispersion E-k (energy-momentum) relationship, lifting (lowering) the Fermi energy in conduction (valence) band can increases the concentration of electron (hole), and thus increases the conductance of graphene. The Fermi level tuning is carried out by changing the gate voltage. Fig. 3.1 (a) shows an electrical measurement biasing condition of graphene back-gate device. The source is grounded and V<sub>DS</sub> is applied on the drain. The V<sub>BG</sub> is applied on the heavily doped silicon substrate which is used as a gate. Fig. 3.1 (b) shows a typical electrical result of transfer characteristics (I<sub>DS</sub>-V<sub>BG</sub>) of SLG back-gate device measured at room temperature. When fixing the V<sub>DS</sub>, electrical current I<sub>DS</sub> is recorded at different V<sub>BG</sub> sweeping from -40V to 40V. Note that around zero back-gate voltage, the resistivity or sheet resistance for a 2D material, reach its maximum value at the charge neutrality point (Dirac point) with  $R_{CNP}$ =4 K $\Omega$ . This is because of the Fermi level is in line with the Dirac cone where the conduction band and valence band meet. This point has the minimum carrier (electron or hole) concentration. The R<sub>CNP</sub> at room temperature is

smaller than at low temperature, which is due to the thermally excited carrier that can be frozen out at several Kelvin condition.

Fig. 3.1. (a) Schematics of electrical measurement of back-gate graphene device. (b) Typical  $I_{DS}$ - $V_{BG}$  curve of SLG device with mobility as high as 6900 cm<sup>2</sup>/Vs. The inset shows the optical image of this device.

As the gate voltage increases, the conductance of the graphene increases as

expected. According to Drude model  $\sigma=\mu ne$ , if we have the value for carrier concentration and the conductance, we can estimated the carrier mobility of graphene. The carriers are induced by the back gate capacitor, which can be considered as the parallel plate structure,  $c_{BG}=\varepsilon_r\varepsilon_0/t$ . For our substrate of 300 nm SiO<sub>2</sub>, the  $c_{BG}=0.115\times10^{-3}$  F/m<sup>2</sup>. The mobility can be expressed as  $\mu=(L/W)g_m/(c_{BG}V_{DS})$ , where  $g_m$  is the transconductance of the device. For this particular device shown in Fig. 3.1 (b), the mobility is around 7000 cm<sup>2</sup>/Vs. A common range of our SLG devices under ambient condition is 3000~10,000 cm<sup>2</sup>/Vs.

Fig. 3.2. Typical transfer characteristics of BLG back-gate device. The inset shows the optical image of the device.

For bilayer graphene (BLG), the electrical characteristic is different, especially in

the vicinity of Driac point. As shown in Fig. 3.2, the BLG exhibits slowly increased conductivity with increase of charge density comparing with SLG. The explanation is that a band gap will be induced when a perpendicular electrical field is applied on the BLG [1]. The carrier mobility of is lower comparing with SLG, usually below 2000 cm<sup>2</sup>/Vs.

It is worth to mention the theoretical work that developed for graphene and its bi-layer counterpart by using tight-bonding approach [2]. For SLG, the Hamiltonian that describes the electronic properties near the Fermi level can be approximated as

$$H = \begin{pmatrix} 0 & \hbar v_F (k_x - ik_y) \\ \hbar v_F (k_x + ik_y) & 0 \end{pmatrix}$$

(1)

where k is the momentum and  $v_F$  is the Fermi velocity,  $\hbar$  is the reduced Plunk constant. This Hamiltonian results in the Dirac-like linear dispersion relation between energy and momentum,  $E=\pm \hbar v_F |k|$  [3]. The positive and negative correspond to the conduction band and valence band, respectively. When the two band meets, k=0, meaning no band gap.

In BLG, considering the Bernal stacking order, there are four bands, two low energy bands and two high energy bands. Considering the high energy band is about 0.3 eV higher than the low energy, which is usually difficult to active by the  $\sim 10^{12}$  cm<sup>2</sup> density induced by back-gate, the transport is dominated by the low energy band. The Hamiltonian of low energy can be expressed as [1]

$$H = \begin{pmatrix} \Delta & -\frac{\hbar^2}{2m} (k_x - ik_y)^2 \\ -\frac{\hbar^2}{2m} (k_x + ik_y)^2 & -\Delta \end{pmatrix}$$

(2)

where  $\Delta$  is the onset energy between the two layers. In absence of perpendicular electrical field,  $\Delta$ =0, the Hamiltonian reduced to a spectrum similar to SLG, but with a parabolic dispersion relation E=± $\hbar^2k^2/2$ m. With an applied perpendicular E field,  $\Delta$ ≠0, the band gap opens between conduction band and valence band. The band gap size depends on the E field [3].

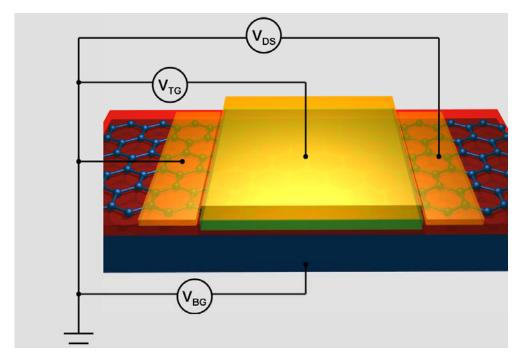

### 3.2 Electrical Measurement of Dual-Gate Single Layer Graphene Device

The thickness of SiO<sub>2</sub> of typical back-gate graphene devices is about 300 nm, which to some extent is required since it offers the best optical contrast for this atomic thin material. However, this thickness is too big if we want to consider practical applications, such as transistors. The modern MOSFET has the gate oxide with EOT of a few nm [4]. We need to build dual-gate graphene devices with smaller thickness of oxide to demonstrate practical applications with graphene transistors. On the other hand, with an additional gate, we can bias the graphene under various conditions so that see more interesting phenomenon.

The details of the dual-gate device fabrications are described in Chapter 2. Here we show the IV characteristics of the dual-gate graphene device, where the top-gate oxide is made of self oxidized AlO<sub>x</sub>, and ALD grown Al<sub>2</sub>O<sub>3</sub>. Fig. 3.3 shows the

measurement schematics of the dual-gate graphene device.

Fig. 3.3. Schematics of electrical measurement of dual-gate graphene device. The back-gate electrode can be used as an extra control node so that it can tune the transport independently with the top-gate.

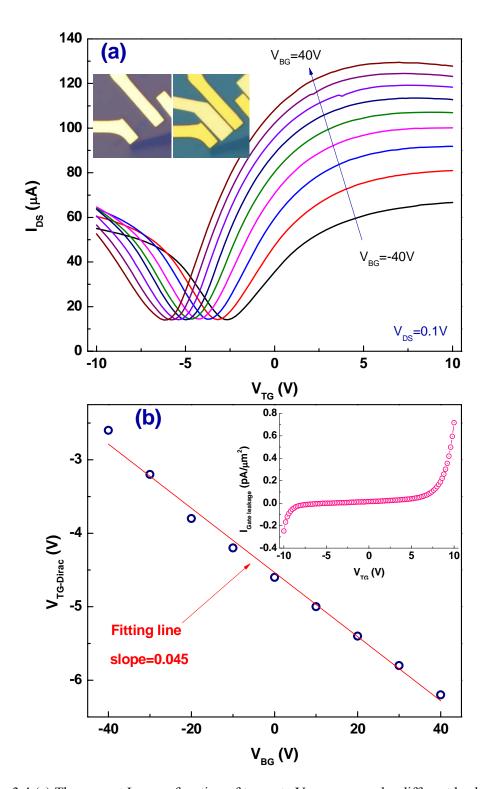

Fig. 3.4 (a) shows the transfer characteristics ( $I_{DS}$ - $V_G$ ) of the dual-gate SLG device under different back-gate bias. The  $V_{DS}$  is fixed at 0.1V during this measurement. The inset pictures show the device before and after the top gate oxide and gate electrode fabrication. This device has the source drain separation of 5.38  $\mu$ m, gate length 4.20 $\mu$ m and channel width 2.45  $\mu$ m. The thickness of the oxide is about 23 nm. As shown in this figure that the CNP shifts to the negative voltage direction as the back-gate bias changes from -40V to 40V. Fig. 3.4 (b) shows the CNP position as a function of the  $V_{BG}$ . CNP appears when the charge induced by the top-gate and back-gate are canceled each other. Adopting the parallel plate capacitor model for

both gates,  $c_{TG}/\Delta V_{TG} = c_{BG}/\Delta V_{TG}$ , the slop of the fitting line in Fig. 3.4 (b) is the ratio of  $c_{BG}/c_{TG}$ . Since we know the  $c_{BG}$  =0.115×10<sup>-3</sup> F/m<sup>2</sup>, the  $c_{TG}$  is 2.56×10<sup>-3</sup> F/m<sup>2</sup> [5, 6]. The current value at  $V_{TG}$ =10V has large difference, owing to the back-gate effect on the contact resistance and the access resistance. The as-fabricated dual-gate device is usually n-type doped due to the Al doping. As the  $V_{BG}$  changes from -40V to 40V, the access resistance decreases. Since the SLG has no band gap and band structure also does not influenced by the perpendicular electrical field, the conductance at the CNP stays constant with different back-gate bias, as shown in Fig. 3.4 (a). Fig. 3.4 (b) inset shows that the top-gate leakage is lower than 1 pA/ $\mu$ m<sup>2</sup> within the range of -10V to 10V. This value indicated very good insulating quality of the gate oxide.

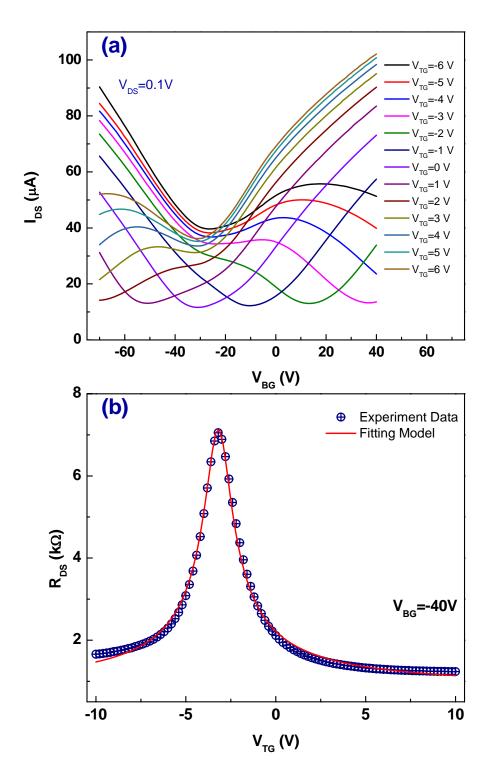

Fig.3.5 (a) shows the transfer characteristics as a function of back-gate voltage under different top-gate bias. The  $I_{DS}$  experiences two valleys as the  $V_{BG}$  sweeps from -70V to 40V [7, 8]. This phenomenon is also related to the access regions which are not covered by the top-gate in graphene device. With different gate bias combinations, the graphene channel experiences different states, such as p-p-p, i-p-i, n-p-n, n-i-n, n-n-n, so that there are two local current minimums appearing as the  $V_{BG}$  sweeps. n, p and i here indicate n-type, p-type doping and intrinsic, respectively. It was also find that, with large top-gate bias,  $V_{TG}$ =-6V for example, a larger back-gate voltage is needed to change from on state to the next one, so that it appeared a more pronounced the "two valleys" effect. With small top-gate bias, this "two valleys" effect becomes weaker.

Fig. 3.4 (a) The current  $I_{DS}$  as a function of top-gate  $V_{TG}$  sweep under different back-gate  $V_{BG}$  bias. The shift of CNP with different  $V_{BG}$  reflects the electrostatic relatioship between top-gate capacitance and back-gate capacitance. The inset show the optical images of the graphene device before and after the fabircation of top-gate oxide and electrode. (b) The current  $I_{DS}$  as a function of  $V_{BG}$  sweep under different  $V_{TG}$  bias.

Fig. 3.5 (a) THe CNP position as a function of  $V_{BG}$ . The slop of the linear fitting line indicates the capacitance ratio of  $c_{BG}$  to  $c_{TG}$ . The inset shows the leakage current of the top-gate oxide, which is below 1 pA/ $\mu$ m2 within the range of -10V to 10V. (b) The fitting results based on the resistance model of graphene dual-gate transistor.

The mobility of the device can be estimated from the following expression for dual-gate graphene device,  $R_{DS}$ =2 $R_C$ +L/W/[ $\mu$ ×e× $\sqrt{(n_0^2+n_g^2)}$ ], where  $R_{DS}$  is the total resistance,  $R_C$  is the sum of contact resistance and access resistance, L is the gate length, W is the channel width,  $\mu$  is the mobility, e is the elementary charge,  $n_0$  is the residue charge which is due to the impurity scattering and thermal emission,  $n_g$ =  $|c_{TG}|$  ×( $V_{TG}$ - $V_{$

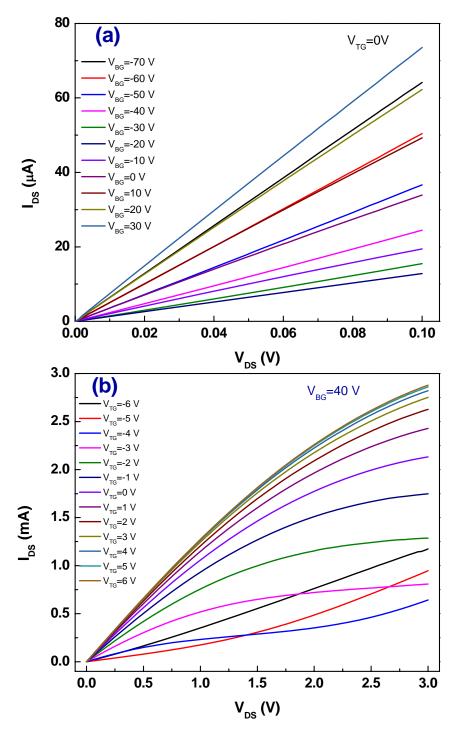

The output characteristics ( $I_{DS}$ - $V_{DS}$ ) of graphene dual-gate transistor is also measured and shown in Fig. 3.6. In the low-field case (small  $V_{DS}$ ), the SLG exhibits linear relation of  $I_{DS}$ - $V_{DS}$ , as shown in Fig. 3.6(a). However, as we bias the graphene device under the high-field condition with larger  $V_{DS}$  ( $E\sim10^4$  V/cm), the linear relationship do not hold any more. Current saturation effect starts to appear around  $V_{DS}$ =1V, and even below with certain gate voltage, as shown in the Fig. 3.6 (b).

Saturation is important for analog applications, since it directly relates to the gain of the transistors. The gain  $A_V=g_mR_O$ , where  $g_m$  is the transconductance and  $R_O$  is the output resistance. A larger gain is preferred, so as the  $R_O$ . When saturation happens, the  $I_{DS}$  is less effected by the  $V_{DS}$ , meaning the dynamic resistance is large.

Fig. 3.6 (a) Low-bias ( $I_{DS}$ - $V_{DS}$ ) output characteristics of dual-gate SLG transistor. Linear relation is observed under various gate voltage. (b) High-bias output characteristics of dual-gate SLG transistor under different top-gate voltage at fixed back-gate  $V_{BG}$ =40V. Current saturation appears, especially at  $V_{TG}$ =-3V. Another type of de-saturation IV curve appears when  $V_{TG}$ =-4V, showing the current saturates at certain value of  $V_{DS}$ , but with  $V_{DS}$  increases, current becomes not saturates again.

In conventional MOSFET, saturation happens when the  $V_{DS}$  is large enough to pinch-off the channel, so that the current do not increase much there after [10]. However, unlike the Si and other semiconductor material, there is no full saturation happening on graphene. The reason is that graphene is a zero band gap material, and the ambipolar property allows both electrons and holes to transport in the same graphene flake [9]. Also, almost no energy loss when the transition from electron to hole happens in graphene [11]. Therefore, no pinch-off happens on graphene, which in turn results in no full current saturation. Nevertheless, certain level of saturation still appears at high-field. For example, as Fig. 3.6 (b) shows, when  $V_{TG}$ =-3V, the differential resistance at high  $V_{DS}$  is 20 times larger than at small  $V_{DS}$ . Another type of IV de-saturation curve appears on graphene dual-gate devices, such as the one when  $V_{TG}$ =-4V. The current saturates at certain value of  $V_{DS}$ , but with  $V_{DS}$  increases, current becomes not saturates again.

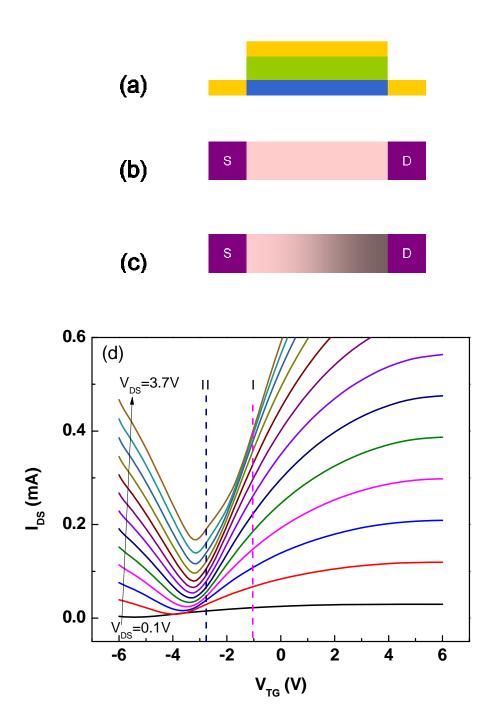

Both the saturation and the de-saturation effects on graphene dual-gate device can be explained by Fig. 3.7. The side-view of the graphene top-gate device is sketched in Fig. 3.7 (a). Under certain gate bias and small  $V_{DS}$ , the charge is uniformly distributed across the channel, as shown in Fig. 3.7 (b), where pink color represents p-type doping. As the  $V_{DS}$  increases, the gate voltage on the drain side  $V_{GD}$  becomes substantially different with the source side  $V_{GS}$  so that the charge distribution is not uniform any more. If the source side is p-type doping, the drain side is be much less p-type doped and even neutral, shown in dark region in Fig. 3.7 (c).

The graphene channel now can be regards as two connecting channels with different CNP point, where one is several volts smaller than the other. So the overall behavior is that the CNP conductance valley becoming wider and shifting to the positive side as the V<sub>DS</sub> increases, as shown in the experimental results Fig. 3.7 (d). As a result, a region where many curves overlap each other appears. If we draw a vertical line "I" (meaning at certain gate bias) on Fig. 3.7 (d) across this region, we will see very good current saturation at this gate bias. Similarly, if we bias at a different gate voltage, which is equivalent to draw another vertical line, for example line "II", we see that this line passes through a dense region and then entering a less dense region. This is what happens when the de-saturation occurs. Note in Fig. 3.7 (d), the I<sub>DS</sub>-V<sub>GS</sub> are measured under different  $V_{DS}$  bias from 0.1V to 3.7V with 0.3V as step size. The intersect points of any vertical line with the family of the IV curves can be regarded as a linear sweep of I<sub>DS</sub>-V<sub>DS</sub>. When the V<sub>DS</sub> keeps increasing, the local gate bias at the drain side could induce n-type doping. Since there is no band gap in graphene, the transition of carrier from hole to electron happens with almost not energy loss. Hence the pinch-off, which occurs in other semiconductors, such as Si, is not likely happens in graphene.

Since the saturation is very important to the analog applications, and it is found in graphene that the saturation is not as good as in other semiconductors, new designs of device structure and operation ranges are needed to be explored.

Fig. 3.7. Explanation of the saturation and de-saturation effects on graphene dual-gate devices. (a) Schematic of graphene to-gate device. (b) Uniform charge distribution in graphene channel when  $V_{DS}$  is small. Pink color represents the p-type doping. (c) As the  $V_{DS}$  increases to a large enough value, the charge would not be distributed uniformly in the graphene channel as the gate bias is different at different location of the channel. Dark color represents the less p-type doping. (d) Experimental results of  $I_{DS}$ - $V_{GS}$  under different  $V_{DS}$  bias from 0.1V to 3.7V with 0.3V as the step. The CNP position shifts to the positive side and the conductance valley becomes wide as the  $V_{DS}$  increases. Two vertical lines "I" and "II" across the curves represent the cases of good current saturation and de-saturation.

### 3.3 Electrical Measurement of Dual-Gate Biayer Graphene Device

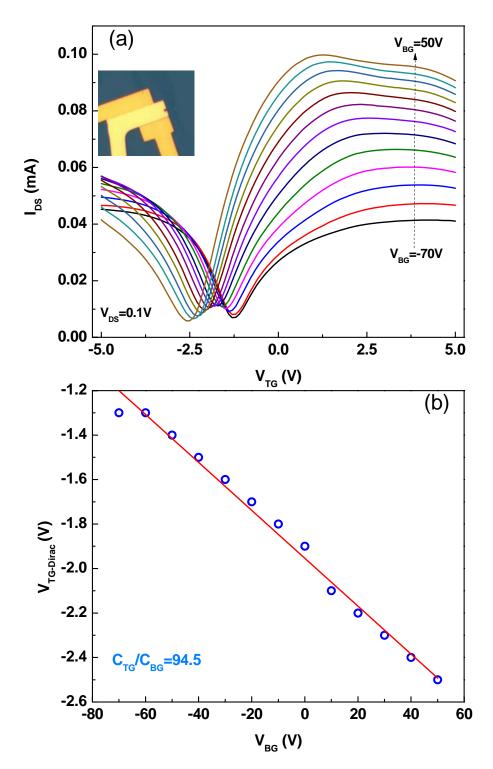

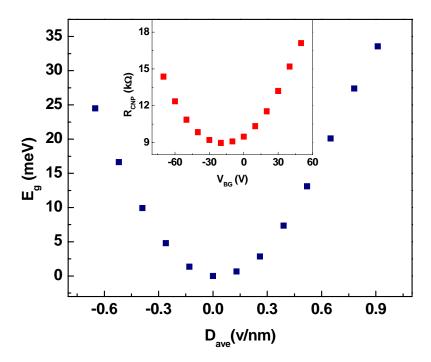

Dual-gate BLG device is very interesting to study since the band structure is parabolic instead of linear in SLG case. Moreover, a band gap can be induced by applying a perpendicular electrical field in BLG system [12-16]. The device fabrication process is the same as the SLG graphene device mentioned above. The only difference here is that the oxide is HfO<sub>2</sub> and self oxidized AlO<sub>x</sub> with total thickness of ~13 nm. Fig. 3.8 shows the electrical measurement results. There are several distinctive differences with SLG and one of the most interesting ones is the induced band gap by perpendicular electrical field. As one can see in Fig. 3.8 (a), the conductance at CNP experiences an evolution of increase and decrease as the back-gate voltage changes from -70V to 50V. This is a direct result of band gap induced in BLG system. The band gap induced by the E filed can be estimated by  $R_{CNP} \propto \exp(E_g/2k_BT)$  at different gate bias [14, 16]. Since the  $I_{CNP}$  is maximum when V<sub>BG</sub>=-20V, it can be treated as no gap case. The induced band gap can be expressed as  $E_g=2k_BT\times ln(R_{CNP(VBG)}/R_{CNP(-20)})$ , where is 26 meV at room temperature. At the charge-neutrality condition,  $D \approx \epsilon_{SiO2}(V_{BG}-V_{BG-CNP})/d_{SiO2}$ , where  $\epsilon_{SiO2}$  (~3.9) is the dielectric constant of the back gate oxide, V<sub>BG-CNP</sub> is the Dirac offset voltage (-20 V here), and  $d_{SiO2}$  (300 nm) is the thickness of the back gate oxide. Fig. 3.9 shows the relation between average electical displacement Dave field and the induced band gap in BLG device. With =0.9 V/nm, the band gap is about 35 meV. The inset shows the R<sub>CNP</sub> as a function of back-gate voltage, comparable with results from others [14, 16].

Fig. 3.8. Electrical characteristics of dual-gate BLG device. (a)  $I_{DS}$  as a function of  $V_{TG}$  under different  $V_{BG}$  bias. The  $I_{DS}$  is not constant under different  $V_{BG}$  indicating an E filed induced band gap in BLG system. The conductance at high carrier concentration exhibits negative transconductance behavior. (b) The charge neutrality point  $V_{TG-CNP}$  as a function of  $V_{BG}$ . The slop reflects the capacitance ratio of of  $c_{TG}/c_{BG}$ =94.5.

Fig. 3.9. The electrical filed induced band gap versus back-gate bias. The inset shows the peak resistance value under different back-gate bias.

Fig. 3.10. High field electrical measurement of dual-gate BLG devices. No strong saturation effect appears

Fig. 3.11 (a) The carrier mobility as a function of  $V_{BG}$ . The maximum value happens when the gate induced band gap is zero, at  $V_{BG}$ =-30~20V. With the increasing of the band gap, mobility decreases. (b) The residue carrier concentration reflects the conductivity at the CNP, which also related to the band gap. (c) The width normalized contact resistance decreases as the back-gate voltage increases.

The High filed measurement (larger  $V_{DS}$ ) is also conducted in BLG system. Since the weak saturation effect in SLG is in part due to the absence of band gap, it is expected that a more prominent saturation effect would be appear in BLG. However, the saturation is also not strong in our BLG devices. This is probably because the band gap induced is too small, shown in Fig. 3.10.

The carrier mobility of our BLG dual-gate devices is estimated by the same method mentioned above for SLG dual-gate devices. The extraction of the top-gate capacitance is by fitting the relation of the  $V_{TG-CNP}$  with  $V_{BG}$ , as shown in Fig. 3.8 (b). The slop indicates the capacitance ratio of  $c_{TG}/c_{BG}$ =94.5. The  $c_{TG}$  is  $10.87\times10^{-3}$  F/m<sup>2</sup>, considering the  $c_{BG}$  is  $0.115\times10^{-3}$  F/m<sup>2</sup>. The dielectric constant  $\epsilon_{HfO2}$  is estimated to be 16, which is a reasonable value for low-temperature ALD grown HfO<sub>2</sub> [9].

Since the band-gap induced by the gate voltage, the mobility is not a constant as the back-gate bias changes. As one can see from the Fig. 3.11 (a), the mobility reaches the maximum value around  $V_{BG}$ =-20~-30V, this is the region where no significant band gap created. With the back-gate voltage increasing (smaller than -30V or larger than -20V), the mobility starts to decrease monotonically. This is expected since the band gap would reduce the mobility. The residue concentration, shown in Fig. 3.11(b), is directly related to the conductivity at the CNP. The maximum value happens at the  $V_{BG}$ =-20V, which consists with the results in Fig. 3.8(a). The contact resistance is represented with the width normalized unit,  $k\Omega$ - $\mu$ m, same as the conventionally used unit for MOSFET. Since our devices have the

channel region covered by the top-gate, the access region between the drain/source and the edge of the top-gate is very small, <50nm, comparing with the  $\mu m$  scale device channel. The contact resistance here should not include much of the access resistance. Fig. 3.11(c) shows the contact resistance changes from 1.2 k $\Omega$ - $\mu m$  to 0.2 k $\Omega$ - $\mu m$  as the back-gate voltage sweeps from -70 to 50V.

Another interesting behavior on dual-gate BLG is the negative transconductance with increasing of carrier density at very high carrier concentration  $n>10^{13}$  cm<sup>-2</sup>, as shown in Fig. 3.8 (a). The conductivity of BLG reaches a maximum value and then decreases with the increase of gate voltage. In the back-gate device, the maximum carrier concentration induced by the back-gate voltage is usually less than  $7.2\times10^{12}$  cm<sup>-2</sup>, considering the conventionally used 300 nm SiO<sub>2</sub> and common instrument limit of 100V. With high-k dielectric material, HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> as top-gate oxide, one can reach a much higher carrier concentration of  $n>10^{13}$  cm<sup>-2</sup>. Owing to the high quality of our dual-gate device, we can apply large gate voltage up to  $\pm10$  V even with gate thickness of 13nm. As mentioned above that the  $c_{TG}$  is  $10.87\times10^{-3}$  F/m<sup>2</sup>, we can apply the carrier concentration up to  $7\times10^{13}$  cm<sup>-2</sup>, about one order of magnitude larger than by 300 nm SiO<sub>2</sub> back-gate.

This negative transconductance behavior is only observed before with electrolyte gate, where the dielectric constant is much larger [17-19] than common solid state oxide. Our result is the first one, as best to our knowledge, that observes this phenomenon with a solid state gate dielectric. As shown in Fig. 3.8 (a), the negative

transconductance effect tends to be stronger as the  $V_{BG}$  increases from -70V to 50V. At  $V_{BG}$ =50V, the conductance drop ~10% as we compare the conductance of peak value with that of at  $V_{TG}$ =5V. This behavior can be understood by activation of high energy in BLG system.

Fig. 3.12. The carrier concentration when the negative transconductance appears as a function of back-gate bias. The value of  $n_{Neg}$  is about  $\sim 3 \times 10^{13}$  cm<sup>-2</sup>, which corresponds to the gap energy from high energy band to low energy band in BLG.

BLG has four bands, while two low energy ones meet at zero energy and two high energy ones split away from zero energy with  $\pm \gamma_1$ . With increasing of carrier concentration, the Fermi level is being pulled down (up) towards the high energy band of BLG in valence band (conduction band). The hole (electron) density at which the higher band starts to be filld is  $n=g\gamma_1/(2\pi\hbar^2v^2)\approx 3\times 10^{13}$  cm<sup>-2</sup>.  $\gamma_1$  is 0.377 eV [20], g is

4 here considering the valley degeneracy 2 and spin degeneracy 2, v is the Fermi velocity  $1.01\times10^6$  m/s [21]. The carrier density is calculated at which the peak conductance appeas by  $n_{\text{Neg}} = c_{\text{TG}} \times (V_{\text{TG-Neg}} - V_{\text{TG-CNP}})/e + c_{\text{BG}} \times (V_{\text{BG}} - V_{\text{BG-CNP}})/e$ . Fig. 3.12 shows the  $n_{\text{Neg}}$  as a function with  $V_{\text{BG}}$ . The  $n_{\text{Neg}}$  is  $\sim 3\times10^{13}$  cm<sup>-2</sup>, which indicates that the negative transconductance is probably due to the activation of high energy band of BLG. While in this band, the intraband scattering starts to play an important role to reduce the carrier transport.

### Reference

- [1] E. McCann, and V.I. Fal'ko, *Phys. Rev. Lett.*, **96**, 086805 (2006).

- [2] P.R. Wallace, *Phys. Rev.*, 71, **622** (1947).

- [3] A.H. Castro Neto, F. Guinea, N.M.R. Peres, K.S. Novoselov and A.K. Geim, *Rev. Mod. Phys.*, **81**, 109 (2009).

- [4] International Technology Roadmap for Semiconductors 2011 Edition, Front End Processes (2011).

- [5] S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, and S. Banerjee, Appl. Phys. Lett., 94, 062107 (2009).

- [6] D. Farmer, Y.-M. Lin, and P. Avouris, *Appl. Phys. Lett.*, **97**, 013103 (2010).

- [7] B. O"zyilmaz, P. Jarillo-Herrero, D. Efetov, D.A. Abanin, L.S. Levitov and P. Kim, *Phys. Rev. Lett.*, **99**, 166804 (2007).

- [8] B. Huard, J.A. Sulpizio, N. Stander, K. Todd, B. Yang and D. Goldhaber-Gordon, *Phys. Rev. Lett.*, **98**, 236803 (2007).

- [9] I. Meric, M.Y. Han, A.F. Young, B. Ozyilmaz, P. Kim and K. L. Shepard, *Nat. Nanotechnol.*, **3**, 654–659 (2008).

- [10] Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices. New York, NY: Cambridge University Press, 2009.

- [11] M.I. Katsnelson, K.S. Novoselov and A.K. Geim, *Nat. Phys.*, **2**, 620 (2006).

- [12] A.H. Castro Neto, F. Guinea, N.M. R. Peres, K.S. Novoselov and A.K. Geim, *Rev. Mod. Phys.*, **81**, 109, (2009).

- [13] J.B. Oostinga, H.B. Heersche, X. Liu, A.F. Morpurgo and L.M.K. Vandersypen, *Nat. Mat.*, **7**, 151 (2008).

- [14] F. Xia, D.B. Farmer, Y.-M. Lin and P. Avouris, Nano Lett., 10, 715 (2010).

- [15] Y. Zhang, T.-T. Tang, C. Girit, Z. Hao, M.C. Martin, A. Zettl, M.F. Crommie, Y.R. Shen and F. Wang, *Nature*, **459**, 820 (2009).

- [16] B.N. Szafranek, D. Schall, M. Otto, D. Neumaier and H. Kurz, *Appl. Phys. Lett.*,96, 112103 (2010).

- [17] J. Ye, M.F. Craciun, M. Koshino, S. Russo, S. Inouea, H. Yuan, H. Shimotani, A. F. Morpurgo and Y. Iwasa, *PNAS*, **108**, 13002 (2011).

- [18] D.K. Efetov, P. Maher, S. Glinskis and P. Kim, *Phys. Rev. B*, **84**, 161412 (2011).

- [19] Z.Q.Li, E.A. Henriksen, Z. Jiang, Z. Hao, M.C. Martin, P. Kim, H.L. Stormer and D.N. Basov, *Phys. Rev. Lett.*, **102**, 037403 (2009).

- [20] B. Partoens and F.M. Peeters, *Phys. Rev. B.*, **74**, 075404 (2006).

- [21] G.M. Rutter, S. Jung, N.N. Klimov, D.B. Newell, N.B. Zhitenev and J.A. Stroscio, *Nat. Phys.*, **7**, 649 (2011).

# Chapter 4

# Analog Applications of Graphene

### 4.1. Introduction

Owing to its very high carrier mobility up to 15,000 cm<sup>2</sup>/Vs even at room temperature, graphene has been proposed as the material for high frequency electronics [1]. Several groups have demonstrated that graphene transistors can be operated at >100 GHz [2-4]. Analog applications such as frequency doubler [5], amplifier [6], phase shift keying, frequency shift keying [7] and phase detector [8] have been experimentally shown using graphene transistors and circuits.

## 4.2. Phase Shift Keying and Frequency Shift Keying

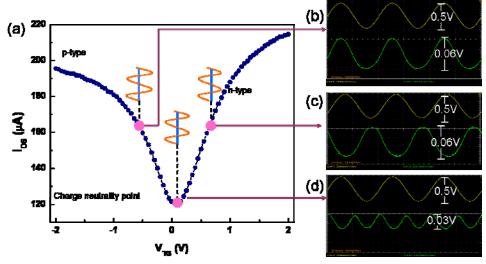

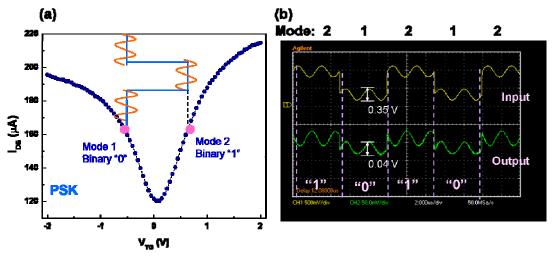

Besides the high carrier mobility, another important property of graphene is the ambipolar transport, where n-type and p-type can be achieved by just change the gate bias. Taking advantage of this ambipolarity of graphene, we demonstrated the circuits that achieve the functionalities such as frequency shift keying (FSK) and phase shift keying (PSK) by using single graphene device which greatly simplify the circuitry.

The single-transistor amplifier, which consists of one transistor and one load resistor, is one of the most basic and important building blocks in analog circuits. There are three types of single-transistor amplifiers: common-source, common-drain, and common-gate, each of which exhibits different characteristics. One of the key

differences between the three types of amplifiers is the small-signal voltage gain, defined as  $V_{out}/V_{in}$ . The common-source amplifier provides negative gain, whereas the common-drain and common-gate amplifiers provide positive gain. Since different applications usually prefer different types of single-transistor amplifiers, it would be very attractive if the same amplifier can be configured in-field into more than one type. However, in Si based metal-oxide-semiconductor field effect transistor (MOSFET) technology, the type of an amplifier is only dependent on its physical configuration, i.e., the node where the input  $V_{in}$  is applied, the node where the output  $V_{out}$  is obtained, and the placement of the resistor. Therefore, in-field configuration of an amplifier is usually infeasible since the physical configuration of the amplifier is determined during fabrication.

With graphene as the channel material, by properly adjusting the gate-source voltages, the transistor can be switched from n-type to p-type, with electron and hole conduction dominating the current, respectively. The ambipolar nature of the charge carrier transport may create problems for conventional applications based on graphene transistors. At the same time, however, it opens up opportunities for increased functionality in nontraditional circuit architectures. For example, graphene transistors have been utilized to demonstrate a frequency multiplier [5, 9, 10], a functional logic gate [11], and an inverter [12]. We demonstrate a single-transistor amplifier with three modes of operation utilizing the ambipolarity of a three-terminal graphene transistor.

Depending on whether the graphene transistor is biased at the left branch, the

minimum conduction point, or the right branch of the ambipolar curve, the amplifier will be configured in the common-drain, the frequency multiplier, or the common-source mode of operation. The proposed triple-mode amplifier is demonstrated using a three-terminal back-gated graphene transistor. We also show theoretically and experimentally that our graphene amplifier can greatly simplify communications applications such as phase shift keying (PSK) and frequency shift keying (FSK). Compared to conventional designs for these applications, the proposed triple-mode graphene amplifier (i) has a significantly simpler structure, (ii) promises a larger bandwidth and higher frequency of operation, and (iii) promises low power consumption.

To demonstrate the triple-mode graphene amplifier, we have fabricated back-gated graphene transistors from exfoliated graphene flakes. A representative fabricated device, the scanning electron microscope (SEM) image, the Raman spectrum of the single-layer graphene, the  $I_{DS}$ - $V_{GS}$  characteristics, and  $g_m$ - $V_{GS}$  characteristics are shown in Fig.4.1(a)-(e). Fabrication and measurement details are provided in the Chapter 2 and Chapter 3. Strong ambipolar conduction was observed in the graphene transistors as evidenced by the "V"- shaped  $I_{DS}$ - $V_{GS}$  curve. In the ambipolar graphene transistor, the transport is dominated by electrons and holes for high and low gate voltages, respectively, and the minimum conduction point  $V_{CNP}$  corresponds to the charge neutrality point where electrons and holes contribute equally to the transport. The ambipolar graphene transistor should be regarded as

n-type or p-type at high gate voltage ( $V_{GS} > V_{CNP}$ ) or low gate voltage ( $V_{GS} < V_{CNP}$ ), respectively, and as hybrid-type when the gate voltage is equal to  $V_{CNP}$ . The small-signal transconductance  $g_m$  is a key factor dominating the high-frequency performance of a transistor and the gain of the amplifier. As shown in Figure 1e,  $g_m$  is positive when  $V_{GS} > V_{CNP}$  and negative when  $V_{GS} < V_{CNP}$ , reflecting electron current and hole current, respectively.

Fig. 4.1 (a) Optical micrograph image of a representative fabricated back-gated graphene transistor. (b) SEM image of source and drain electrodes of a representative back-gated graphene transistor. (c) The Raman spectrum of the singlelayer graphene. (d)  $I_{DS}$ - $V_{GS}$  characteristics of the graphene transistor for  $V_{DS}$ =0.5 V. The current is minimum at the charge neutrality point. (e)  $g_m$ - $V_{GS}$  characteristics for  $V_{DS}$ =0.5 V. The transconductance  $g_m$  is 0 at the charge neutrality point. Reprinted with permission from X. Yang, G. Liu, A. A. Balandin, and K. Mohanram, *ACS Nano*, 4, 5532 (2010). Copyright (2010) American Chemical Society.

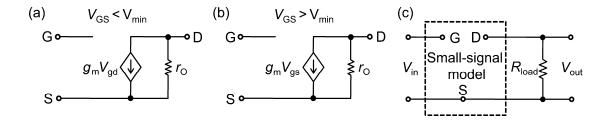

The small-signal model for the back-gated graphene transistor, also referred to as the hybrid- $\pi$  model, under different  $V_{GS}$  is shown in Fig.4.2 panels a and b. Here,  $r_{O}$  is

the output resistance and  $g_m$  is the small signal transconductance of the graphene transistor. Since the graphene transistor is p-type when  $V_{GS} < V_{CNP}$ , the small-signal model is similar to that of a p-type MOSFET [13] in Fig.4.2 (a). Note that for a p-type MOSFET, the voltage-controlled current source is controlled by  $V_{GS}$ , yet in the graphene transistor, it is controlled by  $V_{GD}$ , because here we denote the terminal with higher voltage as the drain for consistency. Since the transistor is n-type when  $V_{GS} > V_{CNP}$ , the small-signal model is similar to that of an n-type MOSFET [13] in Fig.4.2 (b). For  $V_{GS}$  close to  $V_{CNP}$ , the graphene transistor should be considered as hybrid type instead of either n-type or p-type. Therefore, neither the n-type nor the p-type small-signal model is suitable to describe the performance of the graphene transistor. Finally, Fig.4.2 (c) illustrates the circuit for small-signal analysis of the triple-mode graphene amplifier, which will be described in details.

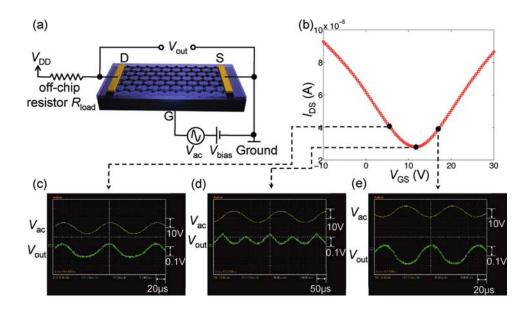

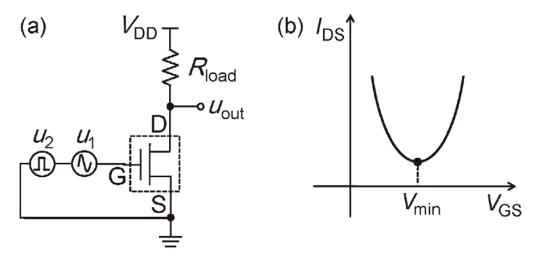

The triple-mode amplifier is built using a singe back-gate graphene transistors and an off-chip resistor. The schematic of the graphene amplifier is shown in Fig.4.3 (a). The supply voltage  $V_{DD}$  is set to 1 V, and the resistor  $R_{load}$  is 20 k $\Omega$ .  $V_{bias}$  is a fixed DC voltage and  $V_{ac}$  is a small sinusoidal AC signal. The gate-source voltage of the graphene transistor is hence equal to  $V_{bias}+V_{ac}$ . We show that depending on the relationship between  $V_{bias}$  and the charge neutrality point  $V_{CNP}$ , this amplifier can have three modes of operation. In each mode, the amplifier exhibits different performance in terms of the small-signal voltage gain  $\Delta V_{out}/\Delta V_{in}$ , which is given by the expression  $\Delta (V_{DD}-I_{DS}R_{load})/\Delta V_{in}$ .

Fig. 4.2. (a,b) Small-signal model for the back-gated graphene transistor, also referred to as the hybrid- $\pi$  model, under different  $V_{GS}$ . Here,  $g_m$  is the transconductance and  $r_O$  is the output resistance. The small-signal model in (a) is used when  $V_{GS} < V_{CNP}$ . Under this condition, the graphene transistor is p-type and the small-signal model is similar to that of a p-type MOSFET. As  $V_{GS}$  increases, the back-gated graphene transistor turns from p-type to n-type and the small-signal model in (b) is used when  $V_{GS} > V_{CNP}$ . Under this condition, the graphene transistor is n-type and the small-signal model is similar to that of an n-type MOSFET. Note that when  $V_{GS}$  is close to  $V_{CNP}$ , the graphene transistor should be considered as hybrid-type instead of either n-type or p-type. Therefore, neither the n-type nor the p-type small-signal model is suitable to describe the performance of the graphene transistor. (c) is the circuit for small-signal analysis of the triple-mode graphene amplifier from Fig.4.3 (a). Note that in small-signal circuit analysis, the power supply is shorted and the nodes for  $V_{DD}$  and ground are replaced by a single reference. Reprinted with permission from X. Yang, G. Liu, A. A. Balandin, and K. Mohanram, ACS Nano, 4, 5532 (2010). Copyright (2010) American Chemical Society.

When  $V_{bias}$  < $V_{CNP}$ , mode 1, the transistor is biased at the left branch of the ambipolar conduction curve, so the small-signal transconductance  $g_m$  of the transistor is negative. In the positive phase of  $V_{ac}$ ,  $I_{DS}$  decreases as  $V_{GS}$  increases. As a result, the voltage drop across the resistor decreases and  $V_{out}$  increases. It can be similarly inferred that in the negative phase of  $V_{ac}$ ,  $V_{out}$  will decrease. Therefore, the small-signal voltage gain in mode 1 is positive, and the input and the output signals have the same phase. From the transport perspective, when  $V_{bias}$  < $V_{CNP}$ , the current is mainly due to hole conduction, so the transistor can be regarded as p-type. Under this condition, the circuit is configured as a common-drain amplifier. Analytically, the

gain of the amplifier in this mode is given by the expression  $|g_m|R_{total}/(|g_m|R_{total}+1)$ , where  $R_{total}$  is the parallel combination of the load resistor  $R_{load}$  and the inherent output resistance  $r_O$  of the graphene transistor. This expression can be derived from the small-signal analysis of the complete circuit illustrated in Fig.4.2 (c), using the small-signal model for the graphene transistor shown in Fig.4.2 (a). The measured result for mode 1 is presented in Fig.4.3 (c). The applied bias voltage  $V_{bias}$  is 6.5 V and the frequency of the input AC signal  $V_{ac}$  is 10 kHz.

When  $V_{bias} > V_{CNP}$ , mode 2, the transistor is biased at the right branch of the ambipolar conduction curve, so the small-signal transconductance  $g_m$  of the transistor is positive. In the positive phase of  $V_{ac}$ ,  $I_{DS}$  increases as  $V_{GS}$  increases. As a result, the voltage drop across the resistor increases and  $V_{out}$  decreases. It can be similarly inferred that in the negative phase of  $V_{ac}$ ,  $V_{out}$  will increase. Therefore, the small-signal voltage gain in mode 2 is negative, and the output signal will exhibit a phase shift of  $180^{\circ}$  with respect to the input signal. From the transport perspective, when  $V_{bias} > V_{CNP}$ , the current is mainly due to electron conduction, so the transistor can be regarded as n-type. Under this condition, the circuit is configured as a common-source amplifier. Analytically, the gain of the amplifier in this mode is given by the expression - $|g_m|R_{total}$ , where  $R_{total}$  is the parallel combination of  $R_{toad}$  and  $r_0$ . As in mode 1, this expression can be derived from the small-signal analysis of the complete circuit illustrated in Fig.4.2 (c), using the small-signal model for the graphene transistor shown in Fig.4.2 (b). The measured result for mode 2 is presented

in Figure in Fig.4.3 (e). The applied bias voltage  $V_{\text{bias}}$  is 17.5 V and the frequency of the input AC signal Vac is 10 kHz.

When  $V_{bias}$  = $V_{CNP}$ , mode 3, the transistor is biased at the minimum conduction point. In the positive phase of  $V_{ac}$ , the small-signal transconductance is positive. As a result, the small-signal voltage gain is negative, as analyzed in mode 2. In contrast, in the negative phase of  $V_{ac}$ , the small-signal transconductance is negative. As a result, the small-signal voltage gain of the amplifier is positive, as analyzed in mode 1. Thus, when  $V_{bias}$  is equal to  $V_{CNP}$ , the input signal sees a positive gain in its positive phase and a negative gain in its negative phase, resulting in frequency doubling. The measured result for mode 3 is presented in Fig.4.3 (d). The applied bias voltage  $V_{bias}$  is 11.1 V and the frequency of the input AC signal  $V_{ac}$  is 4kHz. The spectral purity of the obtained output was analyzed using the fast Fourier transform. Frequency doubling effect is clearly observed since it is observed that 83% of energy of the output signal is at the frequency of 8 kHz. This effect has also been previously reported [5].

The proposed single-transistor graphene amplifier utilizes the key concept of biasing in analog circuits, that is, only a small range of I-V characteristics near the bias point are necessary to optimize the circuit performance. For this reason, ambipolar conduction can provide a larger design-space than unipolar conduction because of the richer diversity of I-V characteristics.

Fig. 4.3. (a) The schematic for the triple-mode single-transistor graphene amplifier based on an off-chip resistor R<sub>load</sub>. (b) The I<sub>DS</sub>-V<sub>GS</sub> characteristics of the graphene transistor. The three dots represent three representative bias voltages for the three different modes of operation. From the left to the right, for the three bias voltages, the amplifier is configured in the common-drain mode, the frequency multiplication mode, and the common-source mode, respectively. (c) The AC coupled input (yellow waveform) and output (green waveform) signals when the amplifier is biased at the left branch of the ambipolar curve. In this configuration, the amplifier is in the common-drain mode, and the output signal has the same frequency and phase as the input signal. (d) The AC coupled input and output signals when the amplifier is biased at the CNP. In this configuration, the amplifier is in the frequency multiplication mode, and the frequency of the output signal is doubled as compared to that of the input signal. (e) The AC coupled input and output signals when the amplifier is biased at the right branch of the ambipolar curve. In this configuration, the amplifier is in the common-source mode, and the output signal has the same frequency but a 180° phase shift as compared to the input signal. Reprinted with permission from X. Yang, G. Liu, A. A. Balandin, and K. Mohanram, ACS Nano, 4, 5532 (2010). Copyright (2010) American Chemical Society.

Compared to the traditional amplifiers based on unipolar devices, the proposed single-transistor amplifier provides greater in-field controllability as it can switch between the three modes during operation. To the best of our knowledge, this is the first work to demonstrate that a single-transistor amplifier based on a three-terminal

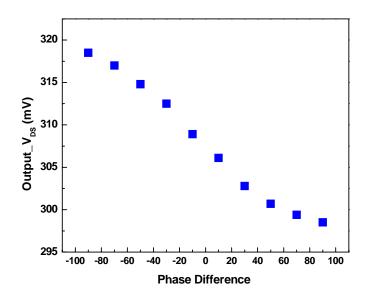

device can be in-field configured to function as both a common-source and a common drain amplifier. The small-signal gain observed in the three modes of operation is 0.01, which is mainly due to the very thick back-gate oxide of 300 nm  $SiO_2$ . As we adopt the top-gate structure, where the top-gate oxide is ~23nm of high k  $Al_2O_3$ , the gain is improved by a factor of 10, as shown in Fig. 4.4.