## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

## Title

Hierarchical Transactions for Hardware/Software Cosynthesis

### Permalink

https://escholarship.org/uc/item/1360652q

## Author

Arya, Kunal Arun

# Publication Date 2014

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA Santa Barbara

## Hierarchical Transactions for Hardware/Software Cosynthesis

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Engineering

by

Kunal Arya

Committee in Charge: Professor Forrest Brewer, Chair Professor Timothy Sherwood Professor Li-C. Wang Professor Tevfik Bultan

December 2014

The Dissertation of Kunal Arya is approved:

Professor Timothy Sherwood

Professor Li-C. Wang

Professor Tevfik Bultan

Professor Forrest Brewer, Committee Chair

September 2014

Hierarchical Transactions for Hardware/Software Cosynthesis

Copyright © 2014

by

Kunal Arya

## Abstract

## Hierarchical Transactions for Hardware/Software Cosynthesis

#### Kunal Arya

Modern heterogeneous devices provide of a variety of computationally diverse components holding tremendous performance and power capability. Hardwaresoftware cosynthesis offers system-level synthesis and optimization opportunities to realize the potential of these evolving architectures. Efficiently coordinating high-throughput data to make use of available computational resources requires a myriad of distributed local memories, caching structures, and data motion resources. In fact, storage, caching, and data transfer components comprise the majority of silicon real estate. Conventional automated approaches, unfortunately, do not effectively represent applications in a way that captures data motion and state management which dictate dominant system costs. Consequently, existing cosynthesis methods suffer from poor utility of computational resources. Automated cosynthesis tailored towards memory-centric optimizations can address the challenge, adapting partitioning, scheduling, mapping, and binding techniques to maximize overall system utility.

This research presents a novel hierarchical transaction model that formalizes state and control management through an abstract data/control encapsulation semantic. It is designed from the ground-up to enable efficient synthesis across heterogeneous system components, with an emphasis on memory capacity constraints. It intrinsically encourages a high degree of concurrency and latency tolerance, and provides verification tools to ensure correctness. A unique data/execution hierarchical encapsulation framework guarantees scalable analysis, supporting a novel concept of state and control mobility. A front-end language allows concise expression of designer intent, and is structured with synthesis in mind. Designers express families of valid executions in a minimal format through high-level dependencies, type systems, and computational relationships, allowing synthesis tools to manage lower-level details. This dissertation introduces and exercises the model, discussing language construction, demonstrating control and data-dominated applications, and presenting a synthesis path that exhibits near-linear scalability with problem size. To my family, for their love, support, and joy. To Hinal, who always managed to put a smile on my face. To my friends who kept me in good spirits and (perhaps more importantly) kept me on my toes. To Forrest, for sharing his enthusiasm, consideration, time, and singularly unique approach to engineering.

## Contents

| st of | Figur                                      | es                                                                                                                                                                 | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of | Acron                                      | ıyms                                                                                                                                                               | xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Intr  | oducti                                     | ion                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1   | From                                       | Codesign to Cosynthesis                                                                                                                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 1.1.1                                      | The Case for Cosynthesis                                                                                                                                           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 1.1.2                                      | The State of the Art                                                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                            | 1.1.2.1 Exposing and Modeling Dominant System Costs                                                                                                                | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |                                            | 1.1.2.2 A Symbiotic Development Relationship                                                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.2   | Contra                                     | ibutions                                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 1.2.1                                      | Computational and State Mobility                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.3   | Overv                                      | iew                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Stat  | te of ti                                   | he Field                                                                                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1   | Behav                                      | ior and State Representation Models                                                                                                                                | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.1                                      | _                                                                                                                                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.2                                      |                                                                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.3                                      | -                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.4                                      |                                                                                                                                                                    | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.5                                      |                                                                                                                                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                            |                                                                                                                                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                            |                                                                                                                                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                            | 2.1.5.3 Nested Transactions and Software Transactional                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |                                            | Memories                                                                                                                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       |                                            | 2.1.5.4 Transactors                                                                                                                                                | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.6                                      |                                                                                                                                                                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.1.7                                      | An Overview of Cosynthesis Models                                                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | st of<br>Intr<br>1.1<br>1.2<br>1.3<br>Stat | st of Acron<br>Introducti<br>1.1 From<br>1.1.1<br>1.2<br>1.2 Contri<br>1.2.1<br>1.3 Overv<br>State of th<br>2.1 Behav<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5 | 1.1.1       The Case for Cosynthesis         1.1.2       The State of the Art         1.1.2       The State of the Art         1.1.2.1       Exposing and Modeling Dominant System Costs         1.1.2.1       Exposing and Modeling Dominant System Costs         1.1.2.1       Exposing and Modeling Dominant System Costs         1.1.2.2       A Symbiotic Development Relationship         1.2       Contributions         1.2.1       Computational and State Mobility         1.3       Overview         1.3       Overview         2.1       Computational and State Mobility         1.3       Overview         2.1       Behavior and State Representation Models         2.1.1       Early Computing Models         2.1.2       Moving Towards Novel Models         2.1.3       Data-flow and Task Graph         2.1.4       Latency Tolerance         2.1.5       Transactions, TLM, and Transactors         2.1.5.1       Transaction Level Modeling         2.1.5.2       Synthesizable TLM         2.1.5.3       Nested Transactions and Software Transactional Memories         2.1.5.4       Transactors         2.1.6       Hardware/software Partitioning |

|          |     | 2.1.7.1 Magellan                                                                         | 21 |

|----------|-----|------------------------------------------------------------------------------------------|----|

|          |     | 0                                                                                        | 22 |

|          |     |                                                                                          | 23 |

|          | 2.2 | -                                                                                        | 24 |

|          |     | 2.2.1 Model Representation                                                               | 25 |

|          | 2.3 |                                                                                          | 26 |

| 3        | Hie | erarchical Transactions                                                                  | 27 |

|          | 3.1 | Abstraction                                                                              | 27 |

|          | 3.2 | Challenges in Cosynthesis                                                                | 28 |

|          | 3.3 | Semantic Model                                                                           | 31 |

|          |     | 3.3.1 Hierarchical Transactions                                                          | 31 |

|          |     | 3.3.2 Overview                                                                           | 33 |

|          |     | 3.3.3 Computational and State Mobility                                                   | 34 |

|          |     | 3.3.4 Token-based Control                                                                | 35 |

|          |     | 3.3.4.1 Combining and Forking Tokens                                                     | 36 |

|          |     | 3.3.5 Latency Tolerance                                                                  | 37 |

|          |     | 3.3.6 Upholding Abstraction                                                              | 39 |

|          |     | 3.3.7 Concurrency                                                                        | 39 |

| <b>4</b> | Hie | erarchical Guarded Atomic Rule-based Language                                            | 41 |

|          | 4.1 | Introduction                                                                             | 41 |

|          |     | 4.1.1 Existing Languages                                                                 | 42 |

|          |     | 4.1.2 Aesthetics $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 43 |

|          | 4.2 | Core Language Philosophy                                                                 | 44 |

|          |     |                                                                                          | 44 |

|          | 4.3 |                                                                                          | 45 |

|          |     |                                                                                          | 46 |

|          | 4.4 |                                                                                          | 47 |

|          |     |                                                                                          | 49 |

|          |     | 4.4.2 Atomicity                                                                          | 51 |

|          |     | 4.4.3 Conditional Statements                                                             | 52 |

|          |     | 4.4.4 Rule Instances                                                                     | 53 |

|          |     | 4.4.4.1 Rule Instance Syntax                                                             | 53 |

|          |     | ·                                                                                        | 55 |

|          |     |                                                                                          | 56 |

|          |     |                                                                                          | 57 |

|          |     |                                                                                          | 57 |

|          |     |                                                                                          | 58 |

|          |     | 1                                                                                        | 59 |

|          |      | $4.4.7.2  \text{Matrix Class}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      | 4.4.8 Modifiers                                                                                                                                              |

|          | 4.5  | Compiler                                                                                                                                                     |

|          |      | 4.5.1 Parsing                                                                                                                                                |

|          | 4.6  | Static Analysis                                                                                                                                              |

|          |      | 4.6.1 Static Analysis for Constant Inference                                                                                                                 |

|          |      | $4.6.1.1  \text{Local vs. Global}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  65$                                                                      |

|          |      | 4.6.1.2 AST-level Constant Inference                                                                                                                         |

|          |      | 4.6.1.3 Rule-level Constant Inference                                                                                                                        |

|          | 4.7  | Simulator                                                                                                                                                    |

| <b>5</b> | Iter | eators 69                                                                                                                                                    |

|          | 5.1  | Motivation                                                                                                                                                   |

|          | 5.2  | The Array Primitive                                                                                                                                          |

|          | 5.3  | Communicating Designer Intent                                                                                                                                |

|          | 5.4  | Execution Semantics                                                                                                                                          |

|          | 5.5  | Syntax & Semantics                                                                                                                                           |

|          |      | $5.5.1$ Token Scoping $\ldots \ldots \ldots$ |

|          |      | 5.5.2 Sequential vs. Concurrent Iterators                                                                                                                    |

|          |      | 5.5.3 Multiple Iterators through Co-iteration                                                                                                                |

|          |      | 5.5.4 Ordering of Iterator versus Iterator Execution                                                                                                         |

|          | 5.6  | Built-in Iterators                                                                                                                                           |

|          | 5.7  | FFT through Iterators                                                                                                                                        |

| 6        | Pra  | ctical Analysis and Model Translation 79                                                                                                                     |

|          | 6.1  | Closure & Distributed Transaction Control                                                                                                                    |

|          | 6.2  | Race Condition Detection                                                                                                                                     |

|          |      | 6.2.1 Mutually Concurrent Sets                                                                                                                               |

|          |      | 6.2.2 Dependency Classifier Matrix                                                                                                                           |

|          |      | 6.2.3 Mutual Concurrent Set Construction                                                                                                                     |

|          |      | 6.2.4 Performance                                                                                                                                            |

|          |      | 6.2.5 Isolating and Reporting Race Conditions                                                                                                                |

|          | 6.3  | Conversion into Existing Semantic Models                                                                                                                     |

|          |      | 6.3.1 Transactions to Pure Functions                                                                                                                         |

|          | 6.4  | Transactions to Control/Data-Flow Graphs                                                                                                                     |

|          |      | 6.4.1 Flow-graphs from Iterators                                                                                                                             |

|          |      | 6.4.2 Software Scheduling                                                                                                                                    |

| <b>7</b>     | Cor   | ntrol-Dominant Application Study            | 101          |

|--------------|-------|---------------------------------------------|--------------|

|              | 7.1   | The MSP430 Microprocessor                   | 102          |

|              | 7.2   | Processor Specification                     | 102          |

|              |       | 7.2.1 Decoding                              | 103          |

|              | 7.3   | Race Condition Detection                    | 105          |

|              |       | 7.3.1 The Original Problem                  | 105          |

|              | 7.4   | Transactional Simulator                     | 108          |

|              | 7.5   | Direct-to-RTL Realization                   | 109          |

| 8            | Hig   | h Performance Arithmetic Applications       | 110          |

|              | 8.1   | Memory Capacity and Data Motion             | 111          |

|              | 8.2   | Problem Setup                               | 111          |

|              |       | 8.2.1 Commercial IP Options                 | 112          |

|              |       | 8.2.2 Challenges in Digraph Clustering      | 113          |

|              | 8.3   | Scheduler-Driven Partitioning               | 114          |

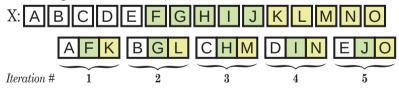

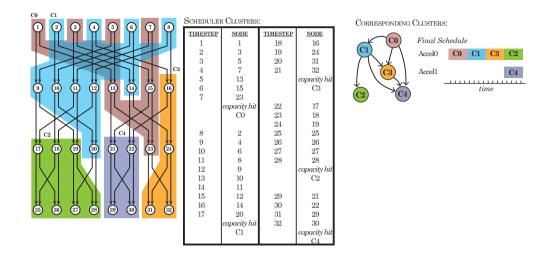

|              |       | 8.3.1 8-point FFT Clustering Illustration   | 117          |

|              |       | 8.3.2 Target Algorithms                     | 118          |

|              | 8.4   | Results                                     | 120          |

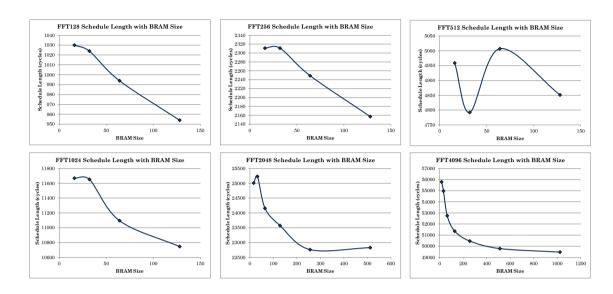

|              |       | 8.4.1 FFT                                   | 120          |

|              |       | 8.4.2 Matrix Multiplication                 | 123          |

|              |       | 8.4.2.1 Complex DSP Algorithm               | 127          |

|              |       | 8.4.3 Utility and BRAM vs SPM Effectiveness | 128          |

|              | 8.5   | Scaling to Very Large Problems              | 128          |

|              | 8.6   | Designer Insight                            | 131          |

| 9            | Cor   | nclusions                                   | 132          |

|              | 9.1   | Hierarchical Transaction Solutions          | 133          |

|              | 9.2   | Open Problems                               | 135          |

| Bi           | bliog | graphy                                      | 137          |

| $\mathbf{A}$ | HT    | L Grammar                                   | 152          |

| в            | FF    | Γ and MSP430 Code Listing                   | 158          |

| D            | B.1   | FFT HTL Code Listing                        | 158          |

|              | B.2   | MSP430 Code Listing                         | $150 \\ 159$ |

| $\mathbf{C}$ | Tab   | les of Matrix Multiplication Clustering     | 177          |

|              | C.1   | Matrix Multiplication Size Sweep Data       | 177          |

|              | C.2   | Software-Pipelining Data                    | 179          |

| D            | Tables of FFT Clustering              | 181 |

|--------------|---------------------------------------|-----|

|              | D.1 FFT Size Sweep Data               | 181 |

| $\mathbf{E}$ | Tables of Large Pipelined DSP Example | 182 |

## List of Figures

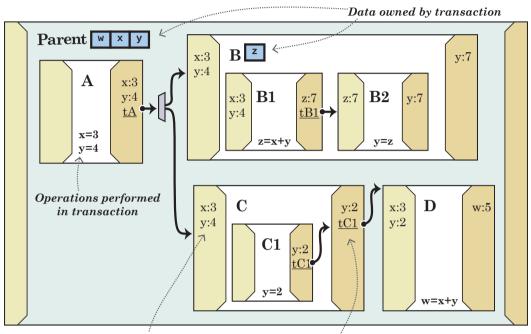

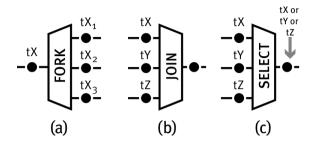

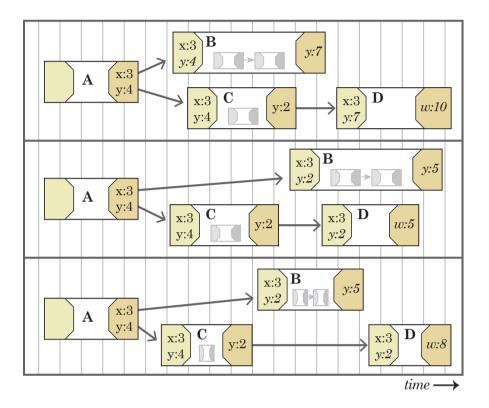

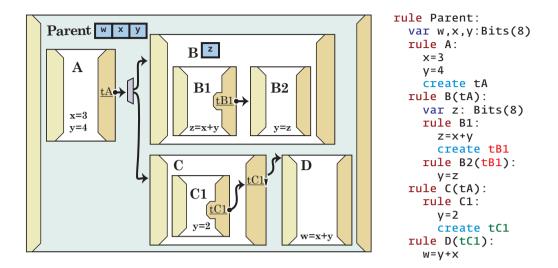

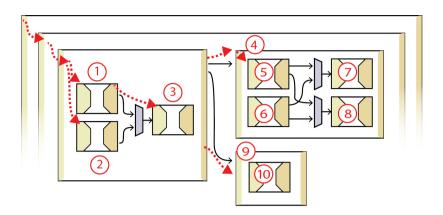

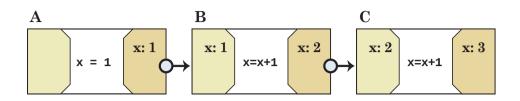

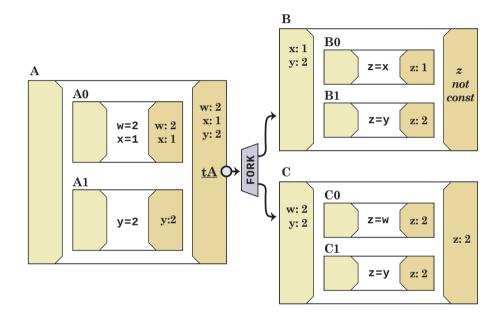

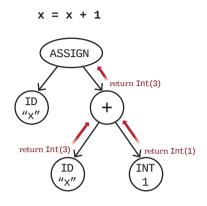

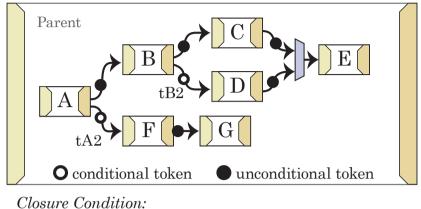

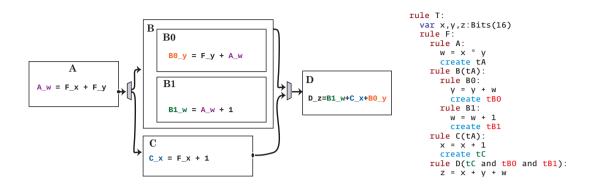

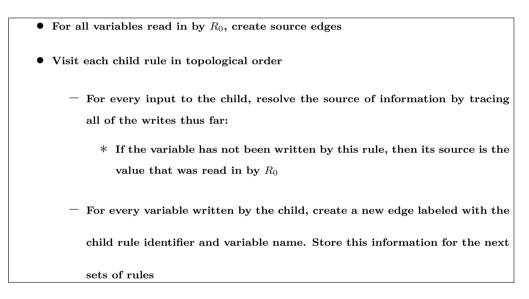

3.1 A small hierarchical transaction design, annotated with possible variable values from a single execution. Each transaction shows variables that are read-in on the left, and variables and tokens committed on the right. The PARENT transaction owns variables w, x, and y. When each of its child transactions begins, they make a local copy of these variables. Transaction B owns a variable called z. Tokens are shown in italicized underlined text in the commit lists. Transaction C illustrates hierarchical token passing – tokens may only pass through their parent to reach higher transactions, following the same commit rules as data. Transaction C1 creates a token tC1 which is passed to C before finally 323.2 (a) FORK nodes replicate tokens when multiple transactions are guarded by the same token. (b) JOIN nodes wait for all input tokens to arrive before generating its output token. (c) SELECT nodes wait for 36 3.3 The same transactions from fig. 3.1 shown executing in different orders. As is demonstrated, the internal workings of transactions B & C do not need to be included. They are abstracted along the transaction 38 boundaries. This idea is crucial to bounded concurrency analysis. . . . Example of token-guarded hierarchical rule language used to spec-4.1 454.2 Rule tree traversal order – it dives into the child rules first, visiting them in topological order based on their dependency. This guarantees that by the time a rule is visited, all of its predecessors have already been visited..... 614.3644.4Constant inference demonstrating rule-level parallel writes. . . . 64

| 4.5 AST-level constant value inference – assume that the rule is provided x with a constant value of Int(3). The AST walker visits each node hierarchically and returns an evaluated result for the sub-tree. If the subtree is not constant (dynamic), then it returns a NULL value 4.6 Constant inference for "if" statement example                                                                                               | 65<br>66             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

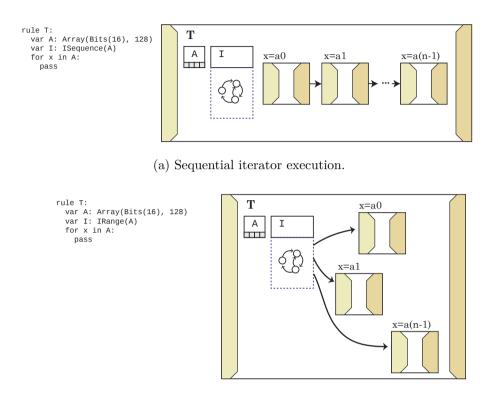

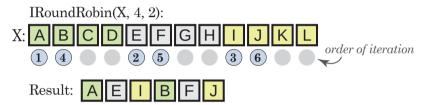

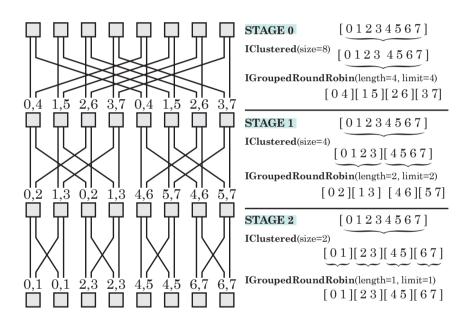

| <ul> <li>5.1 Illustration of execution semantics between sequential and concurrent iterators.</li> <li>5.2 Built-in iterators provided to allow FFT indexing .</li> <li>5.3 Code listing of FFT with Iterators. Each iteration is a new transaction. The double-pipe operator composes parallel iterations – elements are selected from the iterators specified and passed to the iteration transaction at the same time.</li> </ul> | 73<br>76<br>77       |

| <ul> <li>5.4 FFT indexing achieved through iterators</li></ul>                                                                                                                                                                                                                                                                                                                                                                       | 78<br>80<br>81       |

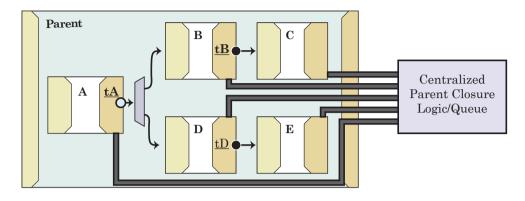

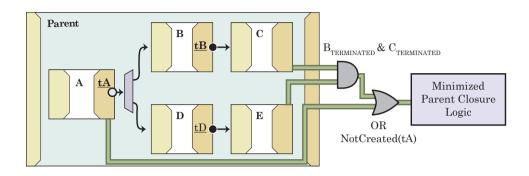

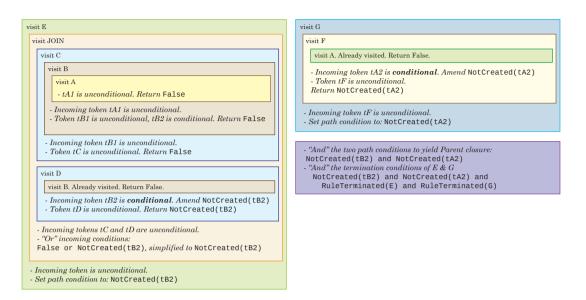

| <ul> <li>6.3 Distributed control using counter tokens to implement synthesized closure logic.</li> <li>6.4 Constructing the condition under which Parent can be closed, demonstrating how conditional tokens may terminate paths and must be ac-</li> </ul>                                                                                                                                                                          | 81                   |

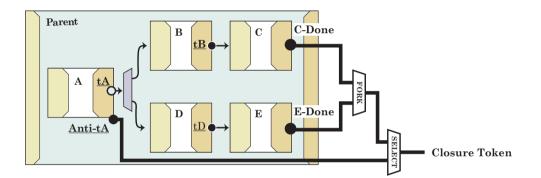

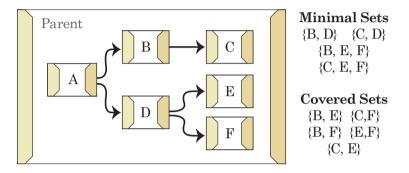

| <ul> <li>counted for.</li> <li>6.5 A trace of the closure algorithm</li> <li>6.6 Possible concurrent transactions captured in sets. Every covered set is a strict subset of one of the minimal sets. Minimal sets are used for CCR analysis, while the both set types are used in race condition</li> </ul>                                                                                                                          | 82<br>85             |

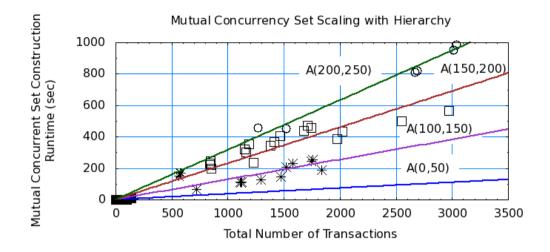

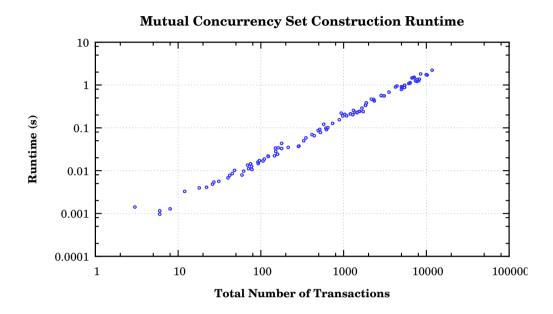

| detection (if they commit to the same variables)                                                                                                                                                                                                                                                                                                                                                                                     | 86                   |

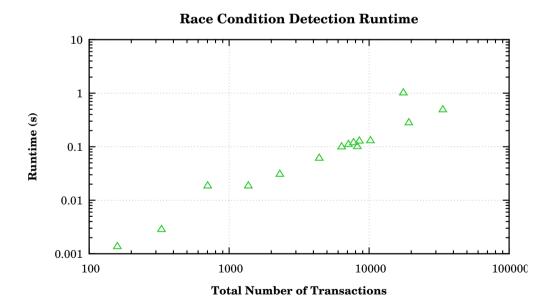

| <ul> <li>parent. "A(0,50)" means hierarchies with ANTP between 0 and 50</li> <li>6.8 Mutual concurrency set construction runtime</li> <li>6.9 Race condition detection scaling</li></ul>                                                                                                                                                                                                                                             | 90<br>91<br>91<br>94 |

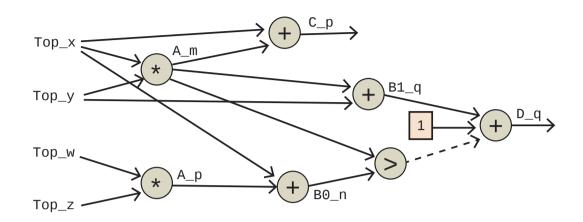

| <ul> <li>6.11 Hierarchical Transactions to CDFG Example. Solid lines are data edges. Dotted lines are control edges</li></ul>                                                                                                                                                                                                                                                                                                        | 98                   |

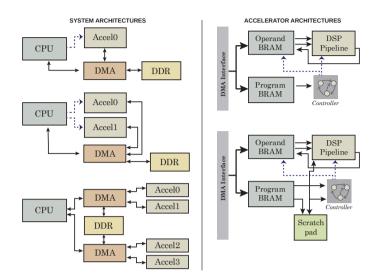

| ators. Right: Accelerator without and with scratchpad memory (SPM)<br>8.2 Illustration of clustering that can induce cycles                                                                                                                                                                                                                                                                                                          | 112<br>113           |

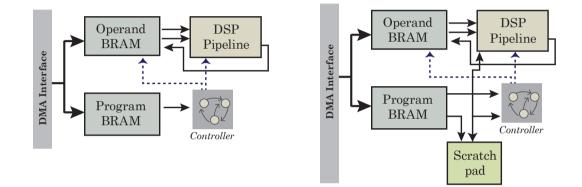

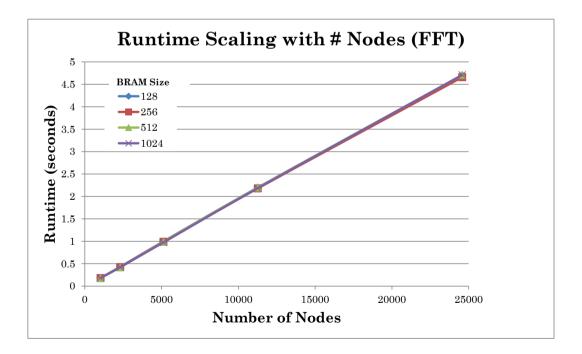

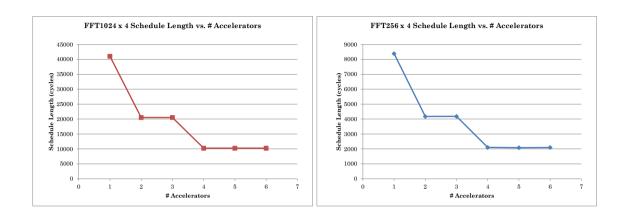

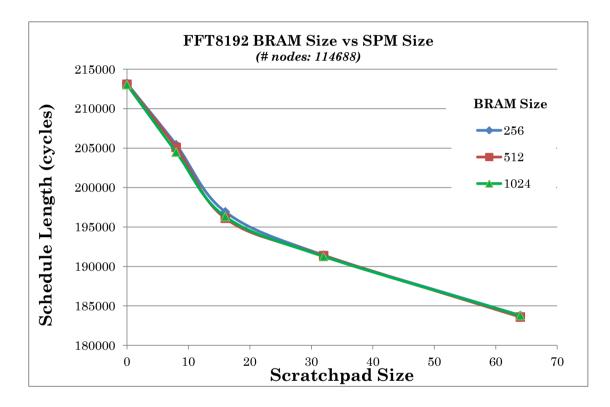

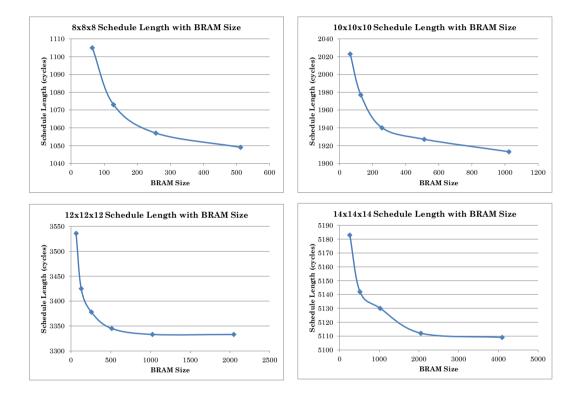

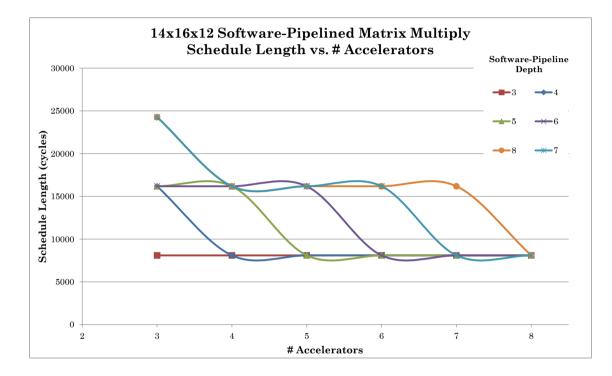

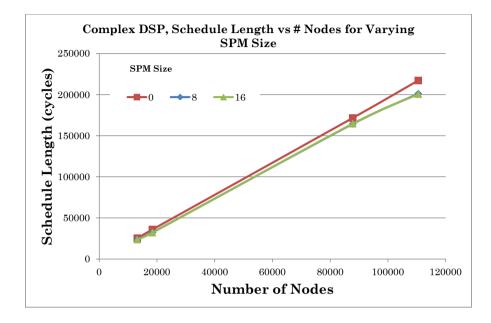

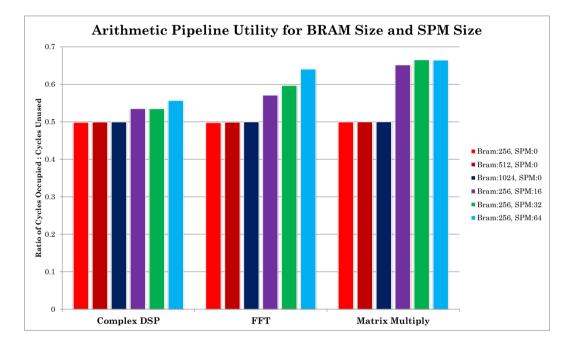

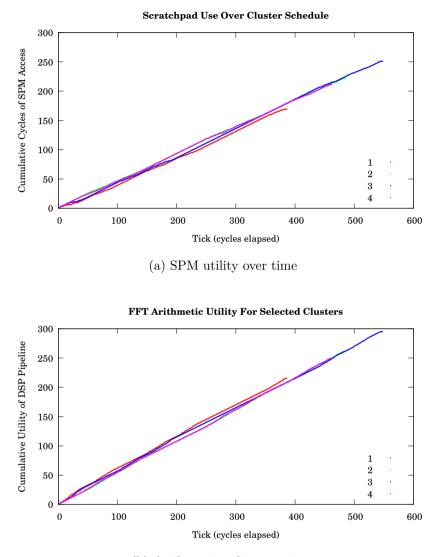

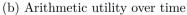

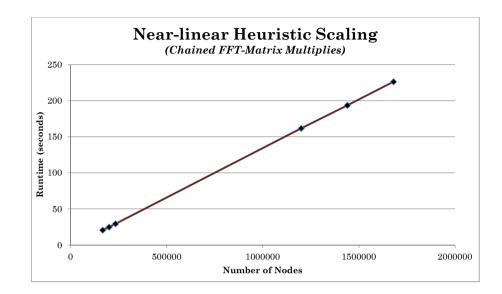

8.3 Internal architecture for peripheral. The bus provides initial operands and the program. A controller executes this program and uses the local operand block RAM (BRAM) to store intermediate operations. After the program has completed, the controller initiates a transfer to the DMA controller while simultaneously asserting an interrupt for the main CPU. When the DMA is configured in scatter-gather mode, the next set of operations arrives automatically, based on an internal linked list of data copying blocks. The peripheral on the right adds a local scratchpad memory to provide local, higher utility access to operand data. . . . . 1158.4 Scheduler-driven clustering of FFT with corresponding cluster graph and system-level schedule for FFT 118 8.5FFT total schedule length (including bus transfers) versus size of BRAM for a 2-accelerator architecture. 122Heuristic runtime scaling with increasing node counts on FFT in-8.6 122stances. For fixed BRAM size, both FFTs of size 1K and 256 exhibited the 8.7 same shape across different peripheral accelerator configurations. 123. . . 8.8 Across different BRAM sizes, the SPM size was varied. Clearly, there is little to no improvement with larger BRAM. This correlates to utility limits stemming from a single port constraint. . . . . . . . . . . 124Matrix multiply total schedule length versus BRAM size constraint 8.9 for 2-accelerator architecture. 1258.10 Matrix multiplication (of a 14x16 matrix with a 16x12 matrix) performance versus software pipeline depth & number of accelerators. It is interesting to note the trade-off between performance and device area. The jump for high-depth software pipelined designs shows a Pareto 1268.11 Scaling for complex DSP application illustrates the heuristics ability to preserve near-linear scalability for a variety of design shapes. . . 1278.12 Algorithms chained together to form a complex DSP demonstration. 128 8.13 For each application, the utility represents the ratio of the used versus idle cycles in the arithmetic pipeline. As the BRAM size is varied, the utility remains relatively constant. Introducing a small scratchpad immediately increases utility; scratchpad size has a much greater impact 1298.14 Visualization of scratchpad memory (SPM) and arithmetic pipeline utility for the same selected clusters of an FFT1024. The two are highly correlated: SPM size correlates strongly with higher performance, since fast access to operands allows the pipeline to remain busy. . . . . . 130

| 8.15 | Heuristic | runtime up | to | millions o | f nod | es . |  |  |  |  |  |  |  |  |  |  |  |  |  | 131 |

|------|-----------|------------|----|------------|-------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|------|-----------|------------|----|------------|-------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

# List of Acronyms

| LT    | Latency Tolerant/Tolerance                         |

|-------|----------------------------------------------------|

| RTL   | Register Transfer Logic                            |

| FPGA  | Field-Programmable Gate Array                      |

| HTL   | Hierarchical Transaction Language                  |

| HTSS  | Hierarchical Transaction Simulator and Synthesizer |

| SoC   | System-on-a-Chip                                   |

| RSoC  | Reconfigurable System-on-a-Chip                    |

| ASIC  | Application-Specific Integrated Circuit            |

| CPU   | Central Processing Unit                            |

| GPGPU | General Purpose Graphics Processing Unit           |

| DSP   | Digital Signal Processor                           |

| ABI   | Application Binary Interface                       |

| RAM   | Random Access Memory                               |

| BRAM  | Block RAM                                          |

| CDFG  | Control/Data-flow Graph                            |

| TLM   | Transaction-Level Modeling                         |

| KPN   | Kahn Process Network                               |

| AST   | Abstract Syntax Tree                               |

## Acknowledgements

We thank the National Science Foundation for their generous funding. We also thank Intel, along with the Silicon Research Corporation, through whom we received custom funding into latency tolerant synthesis (the foundation of this work).

# Chapter 1 Introduction

Heterogeneous hardware/software cosynthesis is the automated binding, allocation, and scheduling of an application onto hardware and software components. The target architecture spans the spectrum across arithmetic units, microprocessors, memory hierarchies/allocations, and the myriad bus/communication interfaces that allow them to execute cooperatively. This dissertation introduces the hierarchical transactional semantic, an abstract application specification model designed from the ground up to target cosynthesis in a way that balances high-level behavior abstraction with high performance synthesis. This balance is achieved through a novel hierarchical data/control encapsulation semantic, encouraging architectural exploration through tool-accessible flexibility in how state and execution are realized. With any abstract specification model comes the risk of imposing performance-hindering constraints, such as handshaking or tight synchronization mechanisms that prevent exploitation of parallel performance. The model, however, enables scalable synthesis, bounded analysis, clean and concise design specification, and verification without sacrificing performance. Finally, the management of memory and memory capacity is crucial to meeting high performance implementations. The presented semantics allow direct control over data motion, capturing cost models that genuinely reflect their underlying architecture.

The evolution of computationally diverse heterogeneous platforms has opened new opportunities to meet high performance constraints across remarkably diverse architectures. Device advances have shaped the system-on-a-chip (SoC) landscape, including field-programmable gate arrays (FPGAs), hybrid FGPAs, full custom integrated chips, and commercial fixed-architecture platforms. The common thread across these platforms is the integration of complex distributed memory architectures, including caching hierarchies and local scratchpad memories (SPMs); in fact, the majority of silicon real estate is dedicated to memory and caching resources. Conventional automated approaches focus on functional components, specifically operations and arithmetic resource binding. Management of state and caching resources, however, are often treated as a secondary effect. In this work, clear representation and management of global state ensures that operational units are adequately used, and becomes a primary goal of the synthesis strategy. The importance of this effort grows as application memory demands scale beyond the capacity of local resources. Making efficient use of available data resources is an enormous ongoing challenge, and calls for a fundamental rethinking of the computational and memory models.

This research introduces a novel specification model with unique underlying data and execution semantics designed to enable cosynthesis across varying computational domains without sacrificing performance. Its focus is on application specification, restricting designer behavior while encouraging explicit and clear expression of designer intent. At its core is the hierarchical transactional model, a formal, abstract model of computation that captures state and execution common across heterogeneous semantic and execution models. The model enables structured cosynthesis that is resilient to shifting platforms and varying constraints, all the while leveraging a unique data/execution encapsulation framework to guarantee scalable analysis. At the front end is a practical, understandable specification language that encourages concise design of complex applications.

## **1.1** From Codesign to Cosynthesis

The impetus behind software/hardware co-design is simple: software models are sufficiently abstracted from hardware, allowing easy adaptation to new architectures. A stringent set of abstractions shield software from changes in e.g. caching layout, protocol interfacing, and physical memory constraints, none of which affect correct execution. Comprehensive tool suites and well-honed design practices allow software to be practically scalable and are key to faster time-tomarket.

In addition to easy adaptation, co-design is a mature field with a wealth of research, industry support, and tools to ameliorate challenges that may arise during software development. Device vendors maintain stable ABIs to assist development on shifting platforms, encouraging incremental design coinciding with platform upgrades. Co-simulation packages simplify validation and integrate well with existing engineering methodologies, facilitating short design iterations and quick exposure of otherwise-evasive bugs.

#### Chapter 1. Introduction

When software can no longer meet application performance demands (be it high throughput, low latency, and/or meeting real-time deadlines), designers employ hardware accelerators. Manually converting software into hardware is practical for small-to-medium applications and often involves significant algorithm restructuring to better leverage available concurrency. Mixing concurrent software and hardware, however, can quickly lead to a litany of component integration challenges. Reaching high performance, high utility designs involves significant engineering effort to navigate around concurrency bugs, resource arbitration complexity, and mixed protocol integration. At the same time, there are no global strategies for maximizing use of distributed, heterogeneous memories. The reality of state-of-the-art co-design exposes a gap between potential performance versus practicable design methods. Automated cosynthesis

#### 1.1.1 The Case for Cosynthesis

In the most general sense, cosynthesis optimizes applications across varying computational domains. The most common instance refers to embedded system synthesis: the automatic creation of hardware accelerators interacting with a larger software application. At the very minimum, it includes scheduling and binding of bus interfaces and memories, along with synchronization infrastructure required to make it work coherently.

Specification-to-silicon cosynthesis holds tremendous potential to provide a fundamentally robust design methodology that not only adapts to shifting platforms, but exploits available resources to reach unprecedented performance. Its benefits are across the board: improved time-to-market, rapid development iterations to determine system costs early in the design process, and effective architectural level optimization. Such a framework would allow designers to exploit novel memory architectures and complex intrachip networks, all the while equipping them with the tools they need to validate and verify otherwise difficult-to-debug concurrent applications.

#### 1.1.2 The State of the Art

In reality, the heterogeneous computing landscape is rife with scaling challenges, ill-suited specifications that are incompatible with the underlying hardware, concurrency bugs, and poorly modeled system costs. Available cosynthesis tools simply cannot cope with meeting difficult constraints against such a diverse design space, especially as applications scale up in size. One of the fundamental issues is a distinct lack of a unified model capable of bridging different computational domains together. Without a comprehensive representation model, there is strong reliance on graph-based approaches and software-to-RTL models. Scalable, practical synthesis is possible with an expressive specification language designed around system-level optimization, rather than adapted from existing approaches. A unified computation model can accommodate vastly different data and execution models to exploit varying degrees of potential parallelism. It requires capture of dominant system costs and a high degree of flexibility in realizing behaviors across different classes of components.

#### 1.1.2.1 Exposing and Modeling Dominant System Costs

When profiling applications, designers rely heavily on experience, as there are no straightforward ways to intuit a system's cost without comprehensive simulation and implementation. Even with rich modeling tools, the true costs of a system may not become apparent until the application is executing in silicon.

In current generation heterogeneous computers, application performance is dominated by the motion and storage of information. Computational pipelines vastly outpace memory interface speeds, often by several orders of magnitude. Hierarchical transactions were designed to expose and codify real system costs, particularly with respect to data motion. They allow direct capture and management of data motion costs to reflect modern architectural realities.

#### 1.1.2.2 A Symbiotic Development Relationship

Robust design methods are clearly advantageous to designers. There is another key benefit: it has the potential to liberate commercial vendors and IC manufacturers from legacy interfaces. When a company releases an SoC product, they are beholden to uphold the same or compatible ABI for further versions of their product. The first iteration effectively sets in stone core architectural features that define its platform. Pressure to preserve these configurations comes from both sides: significant effort goes into developing compilers, simulators, libraries, etc. and vendors are reticent to redesign their tool chain. On the other side, customers demand backwards compatibility to avoid the risky task of reimplementing their application. For example, a first iteration SoC may contain a centralized, cache-coherent RAM. In the next design iteration, newer research or device technology could make available e.g. distributed, lower power memories through crossbars. However, neither side is incentivized to adopt the technology because of rigidly coupled specifications paired with long, cumbersome design and verification times. Worse, customers' applications are tightly coupled to the platform's original architecture; leveraging the next generation's architecture may require a rewrite.

## **1.2** Contributions

The hierarchical transaction computational model lays groundwork for a unified semantic data and execution model. It codifies high-level application behavior through a carefully constructed semantic and syntactic model designed to ensure robust design methodology. Transactional data semantics guarantee verifiable behavior of latency-tolerant concurrent tasks. The notion of computational and state mobility supports maximal exploitation of parallelism – at their core, hierarchical transactions localize all state and control. This encapsulation enables use of hierarchy that is scalable to very large designs. As a result, access to the optimization space is not hindered by complexity in analyzing a specification.

At the front end is a novel specification language to directly represent hierarchical transactions. It focuses designer intent through specific limitations in how state is accessed. Designers are empowered with tools to directly identify and address concurrency bugs. The language is structured with synthesis in mind – it provides methods of expression that are confined to actions commensurate with optimization. Designers express families of valid executions in a minimal format through high-level dependencies, type systems, and computational relationships. Low-level resources such as computational pipelines, protocols, and memories appear as interchangeable resources.

A corresponding compiler enables rapid behavioral simulations including fast identification of race conditions while providing direct paths to high-utility synthesis. Through a unique iterator specification, a compiler generates boundedlifetime dataflow representations well suited for high performance computation. Often, in an embedded system, heterogeneity arises from the use of highly concurrent arithmetic pipelines. The primary bottleneck becomes the management and allocation of local state. This is addressed with a series of clustering heuristics that exploit controlled variable lifetime and high-flexibility transactional tasks to make efficient use of distributed memories and computational pipelines.

#### 1.2.1 Computational and State Mobility

Traditional scheduling contains a notion of mobility for a given node/task – this describes its relative ability to "shift" in time, essentially describing its scheduling flexibility. Hierarchical transactions enforce a notion of computational and state mobility. This extends the concept of operational mobility to include a task's overall behavior, its intermediate and long-term storage, and its timing characteristics, especially across varying memory granularities.

There are three dimensions to the mobility of a behavior: (1) computational mobility describes flexibility of *the domain* that can implement the behavior; (2) state mobility describes *where* it may be realized, essentially representing how

#### Chapter 1. Introduction

tightly coupled the operations are to their associated storage; and (3) scheduling mobility describes *when* a task may begin or end. The tighter any of the three properties are constrained, the less opportunity there is to reach a feasible architectural implementation. Contrawise, greater flexibility across all three enables a design space amenable to architectural, system-wide optimization.

Computational mobility can only occur if the application specification is sufficiently abstract, e.g. it is not bound to any particular computation unit. State mobility requires that any computation be localized to its state – if a task needs to be done, both its state *and* its computation/control is treated as a discrete, mobile object. Scheduling mobility requires true timing decoupling through intrinsically latency tolerant design (intrinsically, as opposed to explicit, requires a fundamental guarantee *a priori* and a natively latency tolerant input specification).