## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

Architectural support for efficient on-chip parallel execution

#### **Permalink**

https://escholarship.org/uc/item/0r1593xh

#### **Author**

Brown, Jeffery Alan

## **Publication Date**

2010

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Architectural Support for Efficient On-chip Parallel Execution

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science

by

Jeffery Alan Brown

#### Committee in charge:

Professor Dean Tullsen, Chair

Professor Brad Calder

Professor Sadik Esener

Professor Tim Sherwood

Professor Steven Swanson

Copyright

Jeffery Alan Brown, 2010

All rights reserved.

| The dissertation of Jeffery Alan Brown is approved, and |

|---------------------------------------------------------|

| it is acceptable in quality and form for publication on |

| microfilm and electronically:                           |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

| Chair                                                   |

University of California, San Diego

2010

## DEDICATION

To Mom.

## EPIGRAPH

Do what you think is interesting, do something that you think is fun and worthwhile, because otherwise you won't do it well anyway.

—Brian Kernighan

$Numerical\ examples,\ are\ good\ for\ your\\ soul.$

—T. С. Hu

## TABLE OF CONTENTS

| Signature Pa  | ge                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .  |                                                                                                                                                                                                                                                                                                                                                                                         |

| Epigraph .    |                                                                                                                                                                                                                                                                                                                                                                                         |

| Table of Cor  | tents                                                                                                                                                                                                                                                                                                                                                                                   |

| List of Figur | es                                                                                                                                                                                                                                                                                                                                                                                      |

| List of Table | s                                                                                                                                                                                                                                                                                                                                                                                       |

| Acknowledge   | ements                                                                                                                                                                                                                                                                                                                                                                                  |

| Vita and Pu   | blications                                                                                                                                                                                                                                                                                                                                                                              |

| Abstract of t | he Dissertation                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 1     | Introduction11.1 Complications from Parallelism21.2 Memory Latency & Instruction Scheduling31.3 Cache Coherence on a CMP Landscape41.4 Thread Migration51.4.1 Explicit Thread State: Registers61.4.2 Implicit State: Working Set Migration7                                                                                                                                             |

| Chapter 2     | Experimental Methodology & Metrics       8         2.1 Execution-driven Simulation       8         2.1.1 SMTSIM       9         2.1.2 RSIM       10         2.2 Metrics       11         2.2.1 Weighted Speedup       11         2.2.2 Normalized Weighted Speedup       13         2.2.3 Interval Weighted Speedup       14         2.2.4 Interval IPC & Post-migrate Speedup       15 |

| Chapter 3     | Handling Long-Latency Loads on Simultaneous Multithreading Processors                                                                                                                                                                                                                                                                                                                   |

|           | 3.5 Metrics                      |                                             | 6   |

|-----------|----------------------------------|---------------------------------------------|-----|

|           | 3.6 Detecting and Handling Lon   | g-latency Loads 2                           | 6   |

|           | 3.7 Alternate Flush Mechanisms   | 3                                           | 1   |

|           | 3.8 Response Time Experiments    | 3                                           | 3   |

|           |                                  | lem                                         | 6   |

|           | 3.10 Summary                     |                                             | 9   |

| Chapter 4 | Coherence Protocol Design for Ch | nip Multiprocessors 4                       | 2   |

|           | 4.1 Introduction                 | 4                                           | .2  |

|           | 4.2 Related Work                 | 4                                           | 4   |

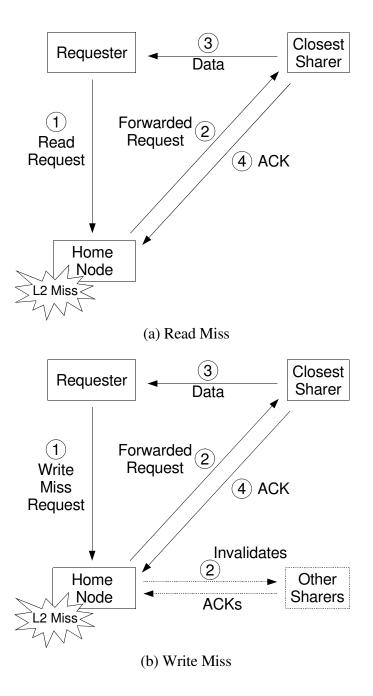

|           |                                  | Directory-based Coherence 4                 | 6   |

|           |                                  | 4                                           | 6   |

|           |                                  | Protocol 4                                  |     |

|           |                                  | Proximity Awareness 5                       |     |

|           | ~                                |                                             |     |

|           | 30                               |                                             |     |

|           | •                                | 6                                           |     |

| Chapter 5 | The Shared-Thread Multiprocesso  | or 6                                        | 5   |

| -         | 5.1 Introduction                 | 6                                           | 5   |

|           |                                  | 6                                           | 7   |

|           |                                  | l Multi-core Architecture 6                 | 8   |

|           |                                  | 6                                           |     |

|           |                                  | areaded cores 6                             |     |

|           |                                  | y operations 7                              |     |

|           | e v                              | chanisms & Policies 7                       |     |

|           | ě                                |                                             |     |

|           |                                  | ol unit                                     |     |

|           |                                  |                                             |     |

|           |                                  | Thread Multiprocessor 7                     |     |

|           | ~                                | es — Hiding long latencies . 7              |     |

|           | <b>-</b>                         | es — Rapid rebalancing 7                    |     |

|           | _                                |                                             |     |

|           |                                  | ion                                         |     |

|           | ~                                |                                             |     |

|           |                                  |                                             |     |

|           |                                  |                                             |     |

|           | -                                | memory stalls 8                             |     |

|           | G                                | •                                           |     |

|           |                                  | over memory latency 8 improved scheduling 8 |     |

|           | ~                                | improved scheduling o<br>9                  |     |

|           | 5.7 Summary                      | 9                                           | / I |

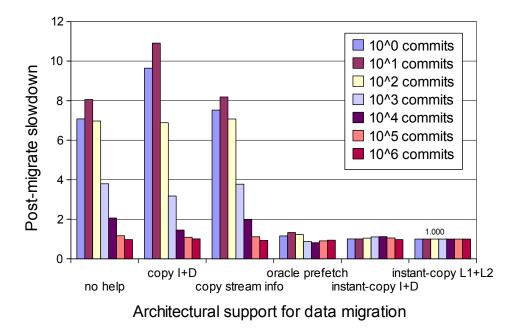

| Chapter 6    | Fast | Thread Migration via Working Set Prediction 93       |

|--------------|------|------------------------------------------------------|

|              | 6.1  | Introduction                                         |

|              | 6.2  | Related Work                                         |

|              | 6.3  | Baseline Multi-core Architecture                     |

|              | 6.4  | Motivation: Performance Cost of Migration            |

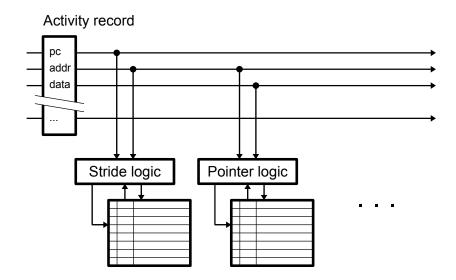

|              | 6.5  | Architectural Support for Working Set Migration 102  |

|              |      | 6.5.1 Memory logger                                  |

|              |      | 6.5.2 Summary generator                              |

|              |      | 6.5.3 Summary-driven prefetcher                      |

|              | 6.6  | Methodology                                          |

|              |      | 6.6.1 Simulator configuration                        |

|              |      | 6.6.2 Workloads                                      |

|              |      | 6.6.3 Metrics                                        |

|              | 6.7  | Analysis and Results                                 |

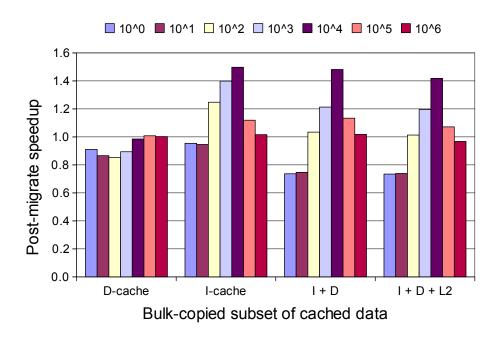

|              |      | 6.7.1 Bulk cache transfer                            |

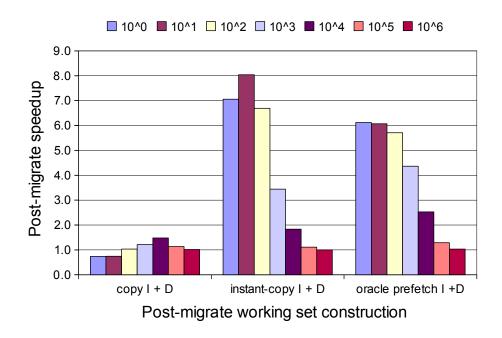

|              |      | 6.7.2 Limits of prefetching                          |

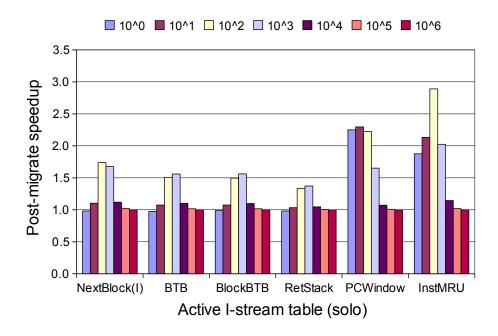

|              |      | 6.7.3 I-stream prefetching                           |

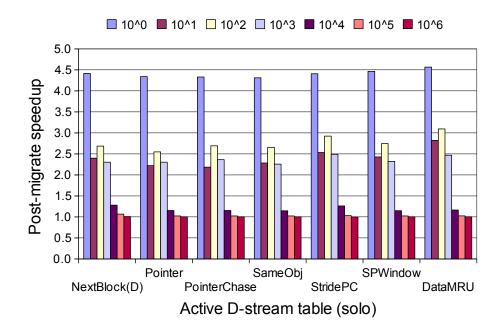

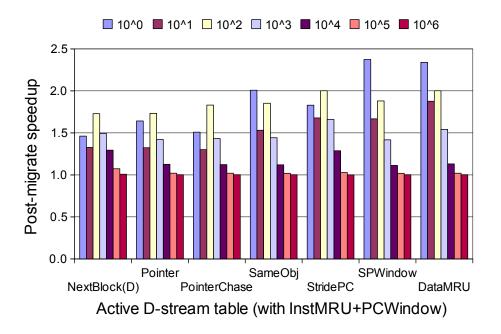

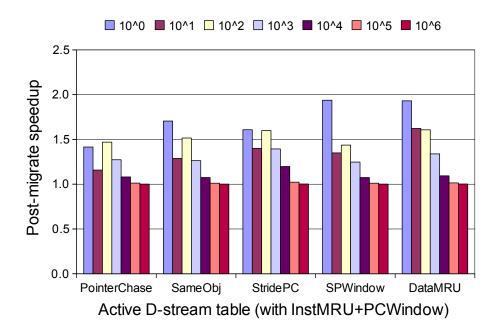

|              |      | 6.7.4 D-stream prefetching                           |

|              |      | 6.7.5 Combined prefetchers                           |

|              |      | 6.7.6 Allowing previous-instance cache re-use 119    |

|              |      | 6.7.7 Impact on other threads                        |

|              |      | 6.7.8 Adding a shared last-level cache 121           |

|              |      | 6.7.9 Simple hardware prefetchers                    |

|              | 6.8  | Summary                                              |

| Chapter 7    | Cond | elusion                                              |

|              | 7.1  | Memory Latency in Multithreaded Processors 125       |

|              | 7.2  | Cache Coherence for CMPs                             |

|              | 7.3  | Multithreading Among Cores                           |

|              |      | 7.3.1 Registers: Thread Migration & Scheduling 128   |

|              |      | 7.3.2 Memory: Working Set Prediction & Migration 129 |

|              | 7.4  | Final Remarks                                        |

| Bibliography |      |                                                      |

## LIST OF FIGURES

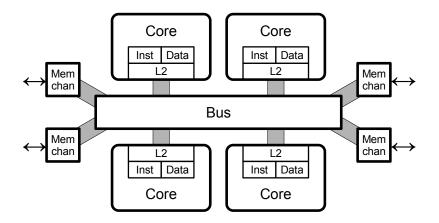

| Figure 1.1:  | Example chip-level parallel architecture               | . 2   |

|--------------|--------------------------------------------------------|-------|

| Figure 2.1:  | Interval weighted speedup compression function         | . 15  |

| Figure 3.1:  | Performance impact of long-latency loads               | . 19  |

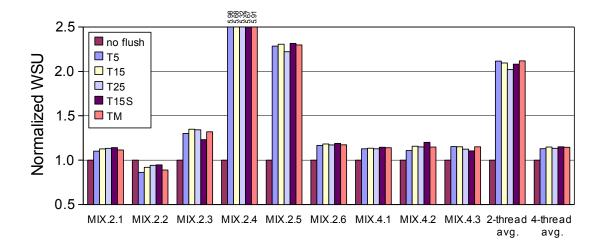

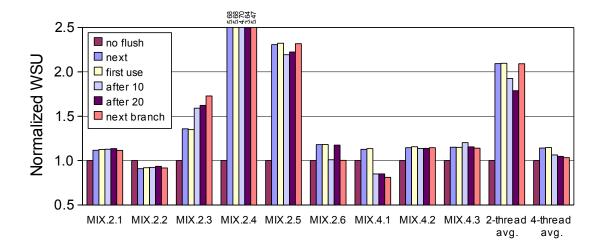

| Figure 3.2:  | Throughput benefit of a simple flushing mechanism      |       |

| Figure 3.3:  | Comparison of long-load detection mechanisms           |       |

| Figure 3.4:  | Performance of flush-point selection techniques        |       |

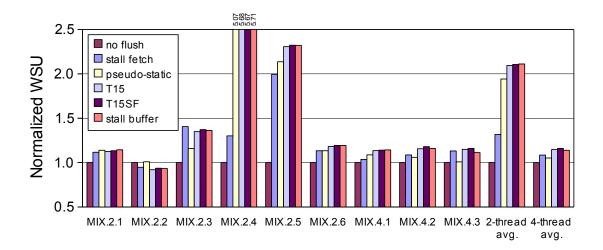

| Figure 3.5:  | Performance of alternative flush mechanisms            |       |

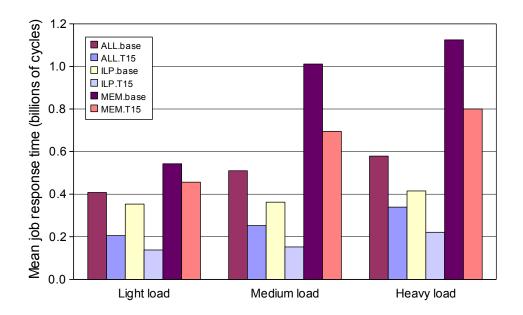

| Figure 3.6:  | Mean response times in an open system                  |       |

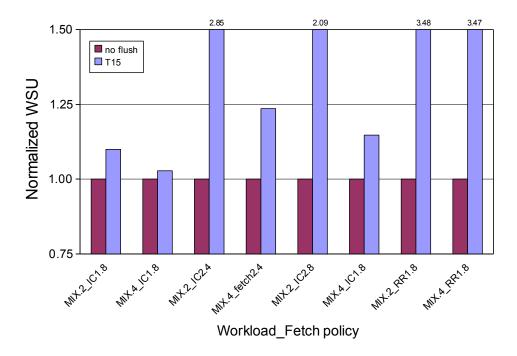

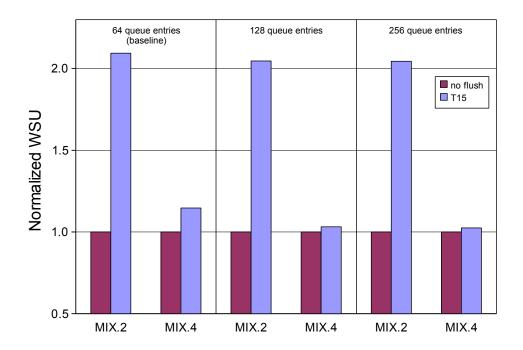

| Figure 3.7:  | Impact on alternate SMT fetch policies                 |       |

| Figure 3.8:  | Performance with different instruction queue sizes     |       |

| 1 18410 0.0. | Torrormance with american most accion queue sizes      |       |

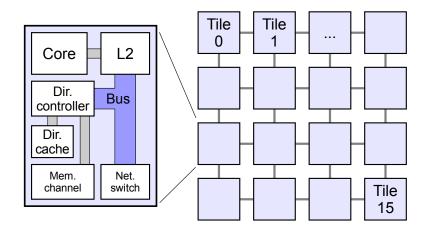

| Figure 4.1:  | Baseline chip multiprocessor                           | . 47  |

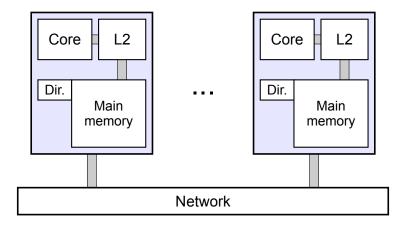

| Figure 4.2:  | A traditional multiprocessor                           |       |

| Figure 4.3:  | Proximity-aware coherence                              | . 52  |

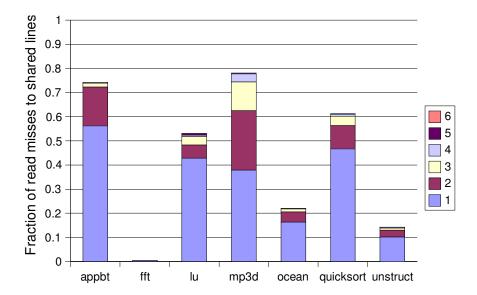

| Figure 4.4:  | Potential benefit from proximity-aware coherence       | . 58  |

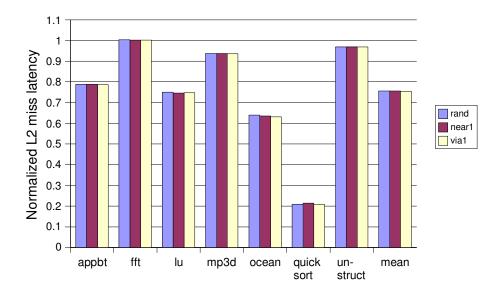

| Figure 4.5:  | Reduction in L2 miss-service latency                   |       |

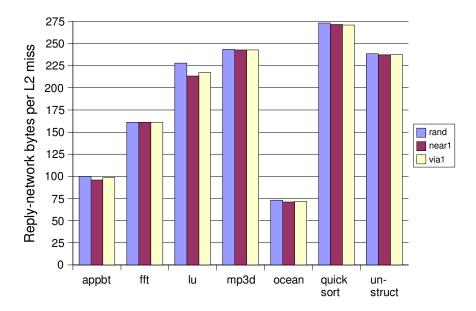

| Figure 4.6:  | Reply-network utilization                              | . 61  |

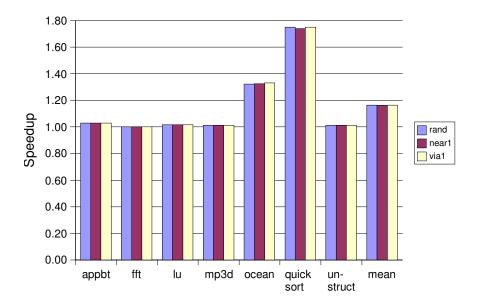

| Figure 4.7:  | Speedup from proximity-aware coherence                 |       |

|              |                                                        |       |

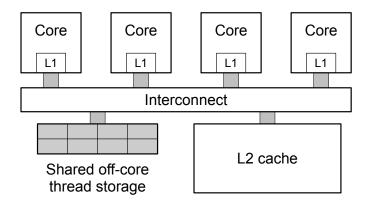

| Figure 5.1:  | The Shared-Thread Multiprocessor                       |       |

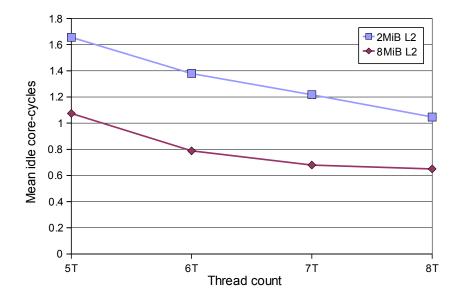

| Figure 5.2:  | Idle time from memory stalls in fully-occupied cores   |       |

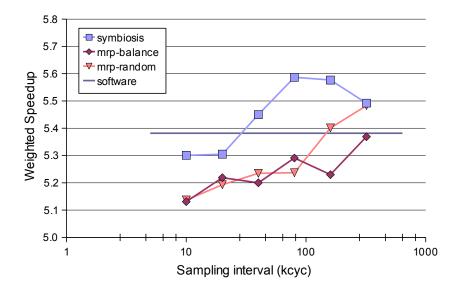

| Figure 5.3:  | Performance of stall-covering schemes                  |       |

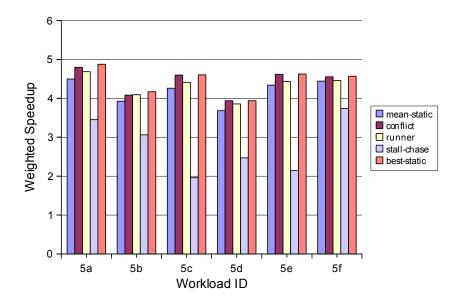

| Figure 5.4:  | Performance of dynamic schedulers                      | . 89  |

| Figure 6.1:  | Baseline multi-core processor                          | . 99  |

| Figure 6.2:  | Performance cost of migration                          | . 100 |

| Figure 6.3:  | Memory logger overview                                 | . 104 |

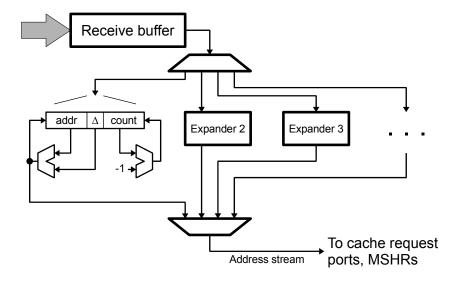

| Figure 6.4:  | Summary-driven prefetcher                              |       |

| Figure 6.5:  | Impact of bulk cache transfers                         |       |

| Figure 6.6:  | The limits of a future-oracle prefetcher               |       |

| Figure 6.7:  | Comparison of instruction stream prefetchers           |       |

| Figure 6.8:  | Comparison of data stream prefetchers                  |       |

| Figure 6.9:  | Speedup from combined instruction and data prefetchers |       |

| Figure 6.10: |                                                        |       |

|              |                                                        |       |

## LIST OF TABLES

| Table 3.1: | Single-threaded benchmarks       |

|------------|----------------------------------|

| Table 3.2: | Multi-threaded workloads         |

| Table 3.3: | Processor configuration          |

| Table 4.1: | Architecture details             |

|            | Workloads                        |

| Table 5.1: | Architecture details             |

| Table 5.2: | Component benchmarks             |

| Table 5.3: | Composite workloads              |

| Table 6.1: | Activity record fields           |

| Table 6.2: | Baseline processor parameters    |

| Table 6.3: | Prefetcher activity and accuracy |

#### **ACKNOWLEDGEMENTS**

I thank my advisor, Dean Tullsen, for making this dissertation possible; for setting an example of professional and personal integrity for us all to aspire toward; and especially for standing by me during the tough years – when experiments weren't working – displaying unwavering confidence at times when I was ready to panic.

I thank the additional members of my thesis committee – Brad Calder, Sadik Esener, Tim Sherwood, and Steven Swanson – for donating their valuable time to me, for reviewing my work, and overseeing the completion of this dissertation. I send further thanks to Geoff Voelker and Glenn Reinman, for contributing at earlier stages of this work, and to Geoff for providing a voice of calm counsel and reassurance over the years. To you all, I'm humbled by your assistance; thank you.

Thanks to my mother, to which I owe everything in life, for always being there for me with unconditional moral support; for burying me with books since before I could walk, then engaging and encouraging me ever since: from reviewing spelling while driving to school ("o-c, e-a-n"), to listening with bewildered patience each time I would explain how I *still* wasn't finished with graduate school. I love you Mom; you are the best.

I wouldn't be who I am today without my big brother. The years we spent finishing each others' sentences were the happiest of my life. I only ever wanted to be like you; I would give absolutely anything to have you back.

I thank my stepfather, for setting a lifelong example of what it means to stand up and be a man; for teaching me that anything worth doing, is worth doing right; for teaching me to be curious, to always wonder what's over the next hill, around the next bend in the river; for supporting us in the most important ways. Five by five, Chief. I'm sorry I couldn't finish this a few months sooner for you.

I thank my father, for his endless patience during my formative years; for encouraging me to ask questions; for always having time for one more "why?", no matter how exhausted he was; for teaching me that being "just a kid" was not something to keep me from comprehending or attempting grown-up things.

Life at UCSD has been enhanced by all the great people I've met in the CSE department. Thanks to my lab-mates for keeping life fun. To John, Tim, and Jeremy: thanks for the hilarious antics over the years; it's a miracle we didn't break anything. Thanks to Jeremy for the times we spent together, those many hours on sysadmin duty; to Rakesh for teaching me the power of a smile, and of perspective; to Leo for listening to me complain during the worst of times; to Jack – a quirky guy, to be sure – for making me laugh, and for being as dependable a friend as they come. Thank you to my roommates Nathan and Jack, for putting up with my strange hours, my griping about school, and most of all for keeping life at home drama-free: school would've been impossible without that. I'm going to miss UCSD — it's a great place to be!

Chapter 3 contains material from "Handling Long-Latency Loads in a Simultaneous Multithreading Processor", by Dean M. Tullsen and Jeffery A. Brown, which appears in *Proceedings of the 34th annual International Symposium on Microarchitecture (MICRO)*. The dissertation author was the secondary investigator and author of this paper. The material in Chapter 3 is copyright ©2001 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

Chapter 4 contains material from "Proximity-Aware Directory-based Coherence for Multi-core Processor Architectures", by Jeffery A. Brown, Rakesh Kumar, and Dean Tullsen, which appears in *Proceedings of the Nineteenth Annual Symposium on Parallelism in Algorithms and Architectures (SPAA)*. The dissertation author was the primary investigator and author of this paper. The material in Chapter 4 is copyright ©2007 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must

be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapter 5 contains material from "The Shared-Thread Multiprocessor", by Jeffery A. Brown and Dean M. Tullsen, which appears in *Proceedings of the 2008 ACM International Conference on Supercomputing (ICS)*. The dissertation author was the primary investigator and author of this paper. The material in Chapter 5 is copyright ©2008 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapter 6 contains material from "Fast Thread Migration via Cache Working Set Prediction", by Jeffery A. Brown and Dean M. Tullsen, which has been submitted for possible publication by the Association for Computing Machinery in *Proceedings of the Nineteenth International Conference on Parallel Architectures and Compilation Techniques (PACT)*. The dissertation author was the primary investigator and author of this paper.

#### VITA

| 2000      | Bachelor of Science in Computer Science summa cum laude University of California, San Diego       |

|-----------|---------------------------------------------------------------------------------------------------|

| 2000      | Internship<br>Computing Sciences Research Center at Bell Labs<br>Murray Hill, New Jersey          |

| 2001–2003 | Graduate Research Fellow<br>National Science Foundation                                           |

| 2002      | Master of Science in Computer Science<br>University of California, San Diego                      |

| 2002      | Internship<br>Intel Corporation, Microarchitecture Research Lab<br>Santa Clara, California        |

| 2004      | Internship<br>Intel Corporation, Microarchitecture Research Lab<br>Santa Clara, California        |

| 2006      | Instructor<br>Department of Computer Science & Engineering<br>University of California, San Diego |

| 2010      | Doctor of Philosophy in Computer Science<br>University of California, San Diego                   |

#### **PUBLICATIONS**

"The Shared-Thread Multiprocessor" Jeffery A. Brown, Dean M. Tullsen. *Proceedings of the 2008 ACM International Conference on Supercomputing (ICS)*, pages 73–82, June 2008.

"Proximity-Aware Directory-based Coherence for Multi-core Processor Architectures" Jeffery A. Brown, Rakesh Kumar, Dean Tullsen. *Proceedings of the Nine-teenth Annual Symposium on Parallelism in Algorithms and Architectures (SPAA)*, pages 126–134, June 2007.

"Speculative Precomputation on Chip Multiprocessors" Jeffery A. Brown, Hong Wang, George Chrysos, Perry H. Wang, John P. Shen. *Proceedings of the 6th Workshop on Multithreaded Execution, Architecture, and Compilation (MTEAC)*, pages 35–42, November 2002.

"Code-Red: a case study on the spread and victims of an Internet worm" David Moore, Colleen Shannon, Jeffery Brown. ACM SIGCOMM Internet Measurement Workshop (IMW), pages 273–284, November 2002.

"Handling Long-Latency Loads in a Simultaneous Multithreading Processor" Dean M. Tullsen, Jeffery A. Brown. *Proceedings of the 34th International Symposium on Microarchitecture (MICRO)*, pages 318–327, December 2001.

"Network Performance Visualization: Insight Through Animation" Brown J.A., McGregor A.J., Braun H-W. *Proceedings of the 1st Passive and Active Measurement Workshop (PAM)*, pages 33–41, April 2000.

#### ABSTRACT OF THE DISSERTATION

#### Architectural Support for Efficient On-chip Parallel Execution

by

Jeffery Alan Brown

Doctor of Philosophy in Computer Science

University of California, San Diego, 2010

Professor Dean Tullsen, Chair

Exploitation of parallelism has for decades been central to the pursuit of computing performance. This is evident in many facets of processor design: in pipelined execution, superscalar dispatch, pipelined and banked memory subsystems, multithreading, and more recently, in the proliferation of cores within chip multiprocessors (CMPs). As designs have evolved, and the parallelism dividend of each technique have been exhausted, designers have turned to other techniques in search of ever more parallelism.

The recent shift to multi-core designs is a profound one, since available parallelism promises to scale farther than at prior levels, limited by interconnect degree and thermal constraints. This explosion in parallelism necessitates changes in how hardware and software interact. In this dissertation, I focus on hardware aspects of this interaction, providing support for efficient on-chip parallel execution in the face of increasing core counts.

First, I introduce a mechanism for coping with increasing memory latencies in multithreaded processors. While prior designs coped well with instruction latencies in the low tens of cycles, I show that long latencies associated with stalls

for main memory access lead to pathological resource hoarding and performance degradation. I demonstrate a reactive solution which more than doubles throughput for two-thread workloads.

Next, I reconsider the design of coherence subsystems for CMPs. I show that implementation of a traditional directory protocol on a CMP fails to take advantage of the latency and bandwidth landscape typical of CMPs. Then, I propose a CMP-specific customization of directory-based coherence, and use it to demonstrate overall speedup, reduced miss latency, and decreased interconnect utilization.

I then focus on improving hardware support for multithreading itself, specifically for thread scheduling, creation, and migration. I approach this from two complementary directions. First, I augment a CMP with support for rapidly transferring register state between execution pipelines and off-core thread storage. I demonstrate performance improvement from accelerated inter-core threading, both by scheduling around long-latency stalls as they occur, and by running a conventional multi-thread scheduler at higher sample rates than would be possible with software alone. Second, I consider a key bottleneck for newly-forked and newly-rescheduled threads: the lack of useful cached working sets, and the inability of conventional hardware to quickly construct those sets. I propose a solution which uses small hardware tables that monitor the behavior of executing threads, prepares working-set summaries on demand, and then uses those summaries to rapidly prefetch working sets when threads are forked or migrated. These techniques as much as double the performance of newly-migrated threads.

# Chapter 1

## Introduction

Much progress in processor architecture can be characterized as the successful exploitation of parallelism in computation, by increasingly-parallel hardware. Each generation of hardware is capable of performing many more simultaneous operations than its predecessor, prompting the recurring challenge of keeping that hardware occupied with useful work. There is an ever-growing gap between the amount of raw parallelism available in hardware, and the effectiveness with which we are able to use it. As transistor development continues apace, architecture design becomes more demanding: with ever-more transistors at our disposal, we must expose and exploit ever-more parallelism in order to efficiently utilize them.

The raw hardware in a processor is highly parallel by nature, yet the amount of parallelism available at a point in computation – the number of independent operations which can begin at that point – varies greatly, both with overall workload and also moment-to-moment within a single workload. A central theme in processor design is the organization of hardware, and the software interface to that hardware, so that computation can be expressed as fragments which hardware can execute efficiently, overlapping operations wherever possible for higher performance.

The focus of this dissertation is enabling efficient, on-chip parallel execution. We will consider a prototypical chip-level parallel architecture, some roadblocks to utilizing increasingly-parallel hardware, and methods to mitigate those problems.

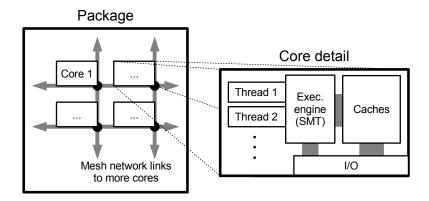

Figure 1.1: Example chip-level parallel architecture.

## 1.1 Complications from Parallelism

Consider the prototypical chip-multiprocessor, or CMP, depicted in Figure 1.1. This chip is composed of several tiles, interconnected by an on-chip mesh network; each tile contains a superscalar, simultaneous-multithreaded general-purpose processor core, cache storage, and network interface hardware. Such a processor has abundant opportunities for parallel execution:

- Instruction-level parallelism (ILP): Pipelined execution breaks each instruction into multiple steps, and overlaps the steps of different instructions, allowing the next instruction to begin execution before a given instruction is complete. Furthermore, superscalar hardware allows multiple independent instructions to begin execution at the same time. Both features multiply potential parallelism.

- Same-core, thread-level parallelism (TLP): During execution, there are points where a given software thread does not offer many independent instructions, leaving the execution hardware mostly idle. One approach to boost resource utilization is Simultaneous Multithreading (SMT): modest additional hardware allows instructions from multiple software threads to contend for executions resources in each cycle. Aside from explicit synchronization operations, instructions from different threads are guaranteed independent of each other,

enabling better utilization of each core's parallel execution hardware without relying on additional speculation.

• Cross-core parallelism: The tiles shown in Figure 1.1 operate independently of each other, except when communicating either with each other for cache-coherence purposes, or with off-chip devices (e.g. memory). As such, software threads submitted to different cores execute independently; each additional core contributes another set of execution units, offering yet more parallelism throughout the system.

While this example is a contemporary design that offers significant parallelism and promises to scale well with increased transistor counts, we will see that straightforward implementations of multi-core designs fall short of their potential. The introduction of more complicated interconnects and contending cores give rise to bottlenecks which are not a factor in single-core designs. We will identify, explore, and address several of these problems.

## 1.2 Memory Latency & Instruction Scheduling

One common performance obstacle for general-purpose processors is long-latency memory operations – i.e. loads that miss in local caches – which can occur unpredictably. While such a request is pending, the processor cannot complete dependent operations, effectively decreasing the amount of parallelism available in that instruction stream.

Simultaneous multithreading processors were introduced in part to better utilize processors in such situations, by freely scheduling instructions from independent threads to cover deficits in the instruction-level parallelism available from any one thread. SMT copes well with short- to medium-term latencies – e.g. cachemisses which are serviced on-chip – since it is able to bring in additional instructions as needed, on a cycle-by-cycle basis, without the thread-switching overhead that prevents prior multithreading techniques from being profitably applied at these time scales.

In Chapter 3 of this dissertation, we show that the use of SMT introduces a new scheduling problem: SMT processors do not handle very-long-latency operations as well as other models of multithreading; even the best among the resource-allocation policies of prior work fall victim to resource hoarding, which arises in the face of long-latency loads. By holding resources when stalled for a long-latency load, a stalled thread impedes the execution of others, even though there is no explicit dependence between them, and without any performance gain that might justify the resource imbalance. The root of the problem is that, even under the best of the prior policies, stalled threads are able to both hold previously-acquired execution resources, and to continue to trickle in additional instructions; the scheduler has no way to revoke these resources.

We present hardware techniques to identify instances of resource-hoarding behavior, before they lead to pathological slow-down: we detect when a thread is stalled on a load which has missed in the L2 cache – a simple "cycles-since-issue" timer suffices – and then flush dependent instructions from the responsible thread, using existing speculative-execution facilities. After reclaiming execution resources from the stalled thread, we block it from fetching until the offending load completes, allowing co-scheduled threads better use of the system in the meantime. We show that this leads to significantly higher and more predictable throughput for all threads.

## 1.3 Cache Coherence on a CMP Landscape

In current multi-core designs, common hardware memory models feature shared memory, wherein any core can directly access any piece of physical memory at any time. Cache coherence is necessary in such systems to ensure that caching is done safely: individual cores have their own caches for the sake of performance, and when one core attempts to write to a block which is also cached on another, action must be taken to prevent inconsistency. As coherence policy governs all interaction between processors and memory modules, both the policy and implementation are performance-critical details of our increasingly-parallel systems.

Cache coherence has been well-studied over the years, traditionally in the context of large distributed-memory machines. Traditional systems present individual processors grouped with memory modules into compute nodes, which are separated from other nodes through a relatively high-latency interconnect; local memory is "closer" than peer processors or their memory. Multi-core designs offer a different processor-memory topology: the processors themselves are tightly grouped, often fabricated together on the same die, with a fast on-die interconnect; memory modules are separated from the processors by another, high-latency interconnect. Peer processors are then "closer" than any memory, and this offers different communication trade-offs.

In Chapter 4 we evaluate a directory-based coherence protocol on a CMP system. We show that simply implementing traditional directory protocols within a chip does not provide the most effective solution, due to the altered communication latency landscape. We demonstrate an improved protocol which prefers communication with on-chip peers over off-chip memory: in the service of L2 cache misses, we query the caches of "bystander" nodes listed as sharers, before resorting to main-memory access; these queries are further ordered to minimize reply-network bandwidth utilization. Our protocol customizations decrease overall miss-service latency by searching on-chip where possible, and decrease the total amount of communication performed system-wide by preferring shorter return paths for data-carrying replies.

## 1.4 Thread Migration

As system core counts increase and software is adapted to utilize these cores, thread-level parallelism is taking on ever-increasing significance in the quest for performance. Though this progression presents interesting programming model and operating system challenges, the efficiency of underlying thread-management mechanisms is inescapably critical: software solutions to the problems of expressing TLP still rely on the underlying hardware to carry out scheduling decisions.

Our growing dependence on thread-level parallelism ensures that thread-

management mechanisms will hold a central role in enabling system-wide performance scaling. Any inefficiencies in thread activation, deactivation, spawning, or migration will take a toll, both by decreasing the rate at which scheduling decisions can profitably be made, and increasing the minimum granularity for profitably creating new threads – or activating worker threads from an idle pool – to exploit short-term or irregular parallelism.

#### 1.4.1 Explicit Thread State: Registers

While several historical parallel systems featured efficient hardware context-switching, these machines sacrificed single-thread performance, required extensive additional hardware for thread state storage, or required workloads be expressed as data-flow streams. Parallel systems today, by contrast, typically perform scheduling using minimal hardware support – privileged software makes scheduling decisions, which are then effected by executing a series of ordinary loads and stores followed by a specialized jump instruction – with minimum latencies of hundreds to thousands of cycles.

In Chapter 5 we start with a multi-core SMT processor, to which we add a mechanism for rapidly moving architected thread state between execution pipelines and shared, off-core inactive-thread storage. We implement these context switches by halting a thread's normal execution, and then injecting register "spill" and "fill" pseudo-instructions into the pipeline. Each of these pseudo-instructions uses the existing renaming and dependence-resolution hardware to copy one logical register value between the core execution state and a small transmit/receive buffer, which is in turn transferred to or from the shared inactive-thread storage. This enables low-latency "multithreading-like" context switching across cores, with latencies in the dozens of cycles.

Using minimal additional hardware, this approach combines the relative simplicity of contemporary multi-core designs with the flexibility and high utilization of large-scale multithreaded systems. We demonstrate that this system can perform scheduling quickly enough to allow for thread scheduling to take advantage of idle resources during memory stalls, and to reschedule batches of threads to detect and avoid inter-thread resource conflicts more effectively than with unassisted software.

#### 1.4.2 Implicit State: Working Set Migration

Even with the hardware support we provide in Chapter 5, the performance cost of creating or moving a thread remains high, requiring tens of thousands of commits for performance to recover afterward. The most significant source of this degradation is due to the lack of cache-resident working set. While architected thread state (e.g. register values) can be easily cataloged and transferred, instruction and data working sets are not explicitly exposed to hardware, and migrated or spawned threads are left to implicitly recreate their own working set as they generate demand references. Unfortunately, the lack of a resident working set limits the amount of ILP visible to the processor – everything becomes stalled for cache misses – severely restricting the rate at which the thread can generate new demand references to bring in more of its working set.

In Chapter 6, we frame this working-set problem more specifically in terms of performance degradation subsequent to individual thread migrations. We show that performance suffers greatly in these instances, due to cache effects, effectively placing a lower limit on the grain-size which is available for scheduling. We also show that simply copying existing cache state is ineffective over the time scales in which performance suffers the most.

We introduce a mechanism to address this. Our system creates compact summaries of a threads' working sets as they execute, and uses that summary data to efficiently prefetch useful instruction and data working sets when a thread is moved to a different core. Thread summary data is passively collected by a set of small hardware tables which are inspired by prefetcher design – with one table detecting striding memory accesses, another detecting repeated accesses to heap objects, etc. – and summary data is compacted into a simple range-encoded format for transfer to other cores and later prefetching. We evaluate a range of behavior-specific hardware tables, and find that even a combination of the simplest ones as much as doubles the performance of threads shortly after migrations.

## Chapter 2

# Experimental Methodology & Metrics

The central ideas we present in this dissertation apply to a variety of instruction sets and underlying processor architectures. However, for the sake of experimental evaluation, we must select a specific execution platform, an implementation methodology, suitable workloads, and evaluation metrics which fairly capture the phenomena we seek to address. In the following sections, we describe our choices for each of these.

## 2.1 Execution-driven Simulation

We rely on processor and memory-system simulators to implement and evaluate our proposed architectures. Simulation has long been an accepted basis for architectural experimentation, in part due to the relative ease of simulation compared to the enormous expense of physically implementing modern microprocessors. While recent advances in prototyping technology such as FPGAs have brought experimental hardware into the reach of university courses and research projects, simulation-driven evaluation remains dominant in the field of computer architecture research.

Simulation allows us to evaluate experimental models at the level of detail with which we conceive them; a researcher need only implement the details they consider significant, versus requiring full implementation at the lowest levels before measurements are possible. Simulation readily admits the use of oracle techniques, such as latency-free communication, or perfect knowledge of future behavior; this is useful for limit studies. Within a given research budget, simulation allows for more rapid exploration, and hence a wider variety of models and parameters may be considered, but with the pitfall than an incautious researcher may overlook important factors when constructing models, leading to unrealistic results.

There are a variety of approaches to simulation, offering different trade-offs in simulation speed, accuracy, and implementation complexity. In this dissertation we study multi-core processors featuring aggressive cores, designed to exploit instruction-level parallelism (ILP) in general-purpose computation. Our workloads are multi-threaded, featuring both cooperative multithreading (with communicating threads) and competitive multithreading (with independent threads). Both high-ILP execution and multithreading lead to substantial re-ordering of operations: individual cores aggressive overlap execution with outstanding memory operations, while concurrent execution allows re-ordering among different threads; these re-orderings have been shown [PRA97a, KT98] to significantly affect the resulting performance. Trace-based simulators are, in general, unable to capture the execution and network effects of dynamic reordering; given its importance in determining overall performance, we thus rely on execution-driven simulation in this dissertation.

We use two well-known processor and memory-system simulators: SMTSIM and RSIM.

#### 2.1.1 SMTSIM

Our primary simulator – which we use for all research in this dissertation except for that in Chapter 4 – is a descendant of the original SMTSIM [Tul96]. We have extended the original simulator to support multiple cores, multiple levels of coherent private caches, and a MESI coherence protocol [PP84] atop a broadcast-based interconnect.

We use SMTSIM to model an out-of-order superscalar processor, includ-

ing speculative execution, executing unaltered native DEC OSF/1 Alpha binaries. This simulator models all typical sources of latency, including instruction execution, dependence stalls, cache misses, branch mispredictions, TLB misses, and stalls for coherence transfers. Conflicts are modeled for many types of resources, including renaming registers, issue queue entries, functional units, commit bandwidth, etc. Latency and bandwidth constraints are modeled for all cache, memory, and interconnect resources. Wrong-path behavior is included, execution down wrong paths between branch misprediction and branch misprediction recovery.

SMTSIM is highly configurable; we take advantage of this, using different processor and memory-system configurations for our different studies. In Chapter 3, we simulate a single-core two-way multithreaded processor with eight-wide issue, to demonstrate in detail the effect of memory stalls on co-scheduled threads. For Chapter 5, we configure SMTSIM as a four-core processor with a shared L2 cache and two threads per core, and then evaluate extending "multithreading-style" thread-switching across cores. In Chapter 6, we again model a four-core processor, but this time with a deeper private memory hierarchy and a single thread per core, in order to emphasize the ability of our working-set migration system. In each of these chapters, we provide additional details of the specific configurations used for that chapter.

#### 2.1.2 RSIM

For the coherence research we present in Chapter 4, we used a derivative of RSIM [PRA97b], an event-driven multiprocessor and mesh-network simulator. While SMTSIM models a coherent multi-core processor, it simulates a bus-based interconnect, which is inappropriate for a processor with more than a handful of cores due to broadcast scalability problems.

In order to experiment atop a more scalable on-chip network, of the sort we envision for future chip multiprocessors, we sought a more capable network model for simulation. In order to experiment with the coherence implementation itself, we sought workloads which rely significantly on the coherence system; shared-memory parallel benchmarks in particular. RSIM provides both elements out-of-the-box: it

has a very detailed simulation of a 2-D mesh network, and support for benchmarks from several parallel benchmark suites.

RSIM has detailed models of execution cores, split L1 caches, private L2 caches, and a 2-D mesh network. However, RSIM was constructed to model a more traditional "cabinet-level" distributed shared-memory multiprocessor. We modified RSIM to simulate on-chip multiprocessing with an on-chip network; significant changes were required to model the proposed directory-based coherence implementations.

## 2.2 Metrics

We rely on a variety of metrics when performing our experimental evaluations and when presenting results. These include conventional metrics rooted in simulated execution time – speedup, request service latency, task response time – as well as simulated operation counts, e.g. total network message transfers. While simulated-time speedup is the de facto standard for evaluating experiments on single-thread workloads, most of the experiments we present in this dissertation involve parallel workloads, some with cooperating threads and some with competing threads.

For cooperatively-threaded parallel workloads, speedup is still an appropriate metric, so long as the workloads are evaluated over equivalent amounts of progress in the underlying task. This is the case for the coherence research we present in Chapter 4: we simulate the entire benchmark execution, so simulated times across experimental configurations are directly comparable. We report conventional speedup in that chapter.

## 2.2.1 Weighted Speedup

Workloads composed of competing independent threads pose a methodological challenge: unless great care is taken to ensure that every component thread makes the same amount of progress in each experiment, traditional metrics such as speedup or aggregate instructions-per-cycle (IPC) are easily skewed by the run-

time behavior of individual threads. In parallel execution, each experiment leads to a different interleaving of instructions from each thread, since the behavior of each thread influences (by way of resource contention) how it gets interleaved with others.

This problem is most dramatic when we evaluate policies which may bias execution against a particular thread or threads. For example, if we were to measure total IPC over a fixed number of system-wide commits, this metric would tend to unrealistically favor policies which prefer threads that exhibit higher IPC, by starving lower-IPC threads of execution resources for the duration of simulation. Any policy which favors high-IPC threads can boost the total IPC by increasing the contribution from those favored threads. Such a situation is unlikely to yield performance gain in a real system, however: while the IPC over a particular measurement interval might be higher, in a practical system low-IPC threads cannot be deferred forever. Eventually, the system would be left to execute a workload inordinately heavy in low-IPC threads, and the artificially-generated gains would disappear. (This problem is explored in more detail in previous work [ST00].)

Many of our experiments are simulated over time-scales which do not capture the reality of having to execute low-IPC threads eventually. This motivates the use of a metric which guides us toward better overall performance while taking into account the relative progress made by each thread in a given experiment. We evaluate multithreaded performance in terms of weighted speedup (WSU), as defined in [ST00], and used frequently in other studies of SMT and multi-core architectures:

Weighted Speedup =

$$\sum_{i \in threads} \frac{IPC_{i,experimental}}{IPC_{i,standalone}}$$

(2.1)

In weighted speedup, each thread's experimental IPC is derated by its single-thread IPC, as measured in separate execution on a single core featuring the same hardware configuration, over the same dynamic instructions committed during the experimental run. To supply standalone IPC values, we simulate each benchmark in isolation – on each hardware configuration – logging simulated cycle counts to a database every ten thousand commits. When computing weighted

speedups, we query the database for each thread, retrieving the two logged points nearest the experimental commit count; we apply linear interpolation to estimate the baseline time to the given commit number.

We use weighted speedup in its original form (Equation 2.1) to report overall performance results for the Shared-Thread Multiprocessor in Chapter 5.

## 2.2.2 Normalized Weighted Speedup

We make two modifications to the standard weighted speedup formula when evaluating overall performance in the load-flushing experiments of Chapter 3:

- Instead of derating each thread by its stand-alone IPC, we derate each thread by the IPC it achieves on the baseline processor when run within the same mix of threads.

- We introduce an additional normalizing factor, dividing by the overall threadcount in each experiment.

The resulting equation we use to compute weighted speedup for the loadflushing research in Chapter 3 is:

Normalized WSU =

$$\frac{1}{|threads|} \cdot \sum_{i \in threads} \frac{IPC_{i,experimental}}{IPC_{i,baseline}}$$

(2.2)

Despite the altered baseline, the spirit of the metric is the same: to make it impossible to quote artificial speedups by simply favoring high-IPC threads. We make this modification for two reasons: first, since Chapter 3 focuses on single-core SMT execution with a constant set of threads for each simulation, a given set of threads is always co-scheduled, which provides us a well-defined baseline for comparison; and second, when multiple threads are running slowly together, we benefit from any of them running faster, regardless of how they would perform when run independently.

The normalizing factor in Equation 2.2 affords us the convenience of plotting weighted speedups across workloads with different thread counts on a common axis; as it is constant for any particular workload, it does not introduce any additional bias between policies.

#### 2.2.3 Interval Weighted Speedup

While we use weighted speedup (Equation 2.1) to report overall performance results for the Shared-Thread Multiprocessor of Chapter 5, some of the scheduling policies therein require online estimates of multithreaded performance. Weighted speedup as a goal function is not suitable for online decision-making, since it requires detailed single-threaded execution detail,  $IPC_{i,single}$ , which is not available at run-time.

This raises a new challenge: finding a suitable basis for evaluating IPC samples, such that all values are available at run-time, and which provides a reasonable baseline for the estimation of the changes in performance. IPC itself is a dangerous metric on which to base runtime optimization decisions, for the same reasons that it is a misleading indicator of overall multithreaded performance. We introduce a new metric, *interval weighted speedup*, an adaptation of traditional weighted speedup to our online scheduling environment.

To enable online evaluation, we use the aggregate IPC of each thread over the entire previous round of scheduling as the basis, in place of  $IPC_{i,single}$ , when evaluating the performance of the  $IPC_{i,exper}$  samples taken during each sample interval. This strikes a balance, providing a measure of stability in values – particularly when comparing alternative schedules within a given round – yet still adapting over time to changes caused by earlier scheduling decisions.

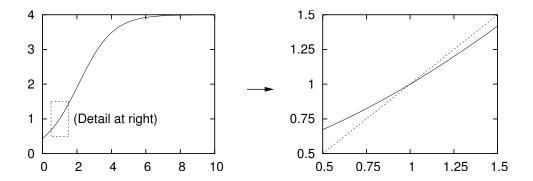

We make one further modification to weighted speedup: given a direct application of the Equation 2.1 over shorter time scales, it is possible for individual quotients within the overall sum to generate very large outputs, e.g. when the basis IPC for an application is abnormally low due to execution conditions. It is important to prevent one such component from dominating the overall sum; while such a sample may cause only a short-term degradation when used for an individual scheduling decision, it can be disastrous when used with schedulers which aggregate data over multiple rounds of scheduling. We guard against this by compressing each thread's contribution to the sum from  $[0, \infty)$  down to the range [0, 4], using a smooth sigmoid function which is nearly linear in the range near 1.0 (where samples are most frequent).

Figure 2.1: Interval Weighted speedup compression function, Equation 2.4.

The resulting equation, incorporating the alternate baseline and the compression function:

Interval WSU =

$$\sum_{i \in threads} comp\left(\frac{IPC_{i,sample}}{IPC_{i,basis}}\right)$$

$$comp(x) = \frac{4.0}{1 + e^{(ln(3)+1-x)}}$$

(2.3)

$$comp(x) = \frac{4.0}{1 + e^{(\ln(3) + 1 - x)}}$$

(2.4)

Figure 2.1 shows the behavior of the range-compression function of Equation 2.4. Although we used it in our evaluation, the sigmoid function itself is not essential; linear scaling with clamping worked nearly as well.

To reiterate, as used within the Shared Thread Multiprocessor chapter, weighted speedup is the metric we use to evaluate and report performance, while interval weighted speedup is an online metric used internally to evaluate the effectiveness of scheduling decisions; the latter does not appear in any results.

#### Interval IPC & Post-migrate Speedup 2.2.4

For the thread-migration research of Chapter 6, we encounter another unconventional performance evaluation challenge. For that work, we wish to gauge the impact of architectural changes on performance in the immediate wake of migration operations, which we repeatedly induce. By triggering fairly infrequently, and capturing the immediate post-migration behavior at various intervals, we can capture both the short-term and long-term performance impact of each migration.

Given the relatively infrequent migrations used in our experimental setup, traditional whole-program metrics such as IPC are unsuitable for evaluating performance over the shorter time scales we are most interested in, since those metrics will be dominated by the much longer periods between migrations. These long periods of undisturbed execution are desirable – they allow a given core to "warm up" to a thread's execution, providing a contrast for the next time that thread is migrated – but we do not want their statistics included in the post-migrate performance evaluation. Whole-program metrics also do not provide a useful way to analyze how the impact of a given migration varies across time scales.

We introduce a new performance metric for Chapter 6, the interval IPC of a migrating thread. After each migration, we concurrently measure the IPC over an exponential progression of commit intervals: we measure the time it takes to commit the  $10^n$  instructions immediately following each migration operation, for  $n \in \{0...6\}$ . We measure time from the first post-migrate fetch until the cycle of the  $10^{n\text{th}}$  commit. This results in a vector of seven measured time values for each migration, and seven corresponding interval IPCs. For a particular experiment, we first compute an arithmetic mean for each interval, taken across all migrations of a single simulation, which results in seven mean interval IPCs per simulation. Rather than report interval IPCs directly, we compute ratios of these IPCs versus the interval IPCs of the same thread running on the baseline architecture and migrating at the same points in execution. We report these rations as either post-migrate speedup or post-migrate slowdown, depending on the sense of the ratio. We report means of these ratios, taken across our workload suite.

# Chapter 3

# Handling Long-Latency Loads on Simultaneous Multithreading Processors

## 3.1 Introduction

Simultaneous multithreading (SMT) [TEL95, TEE<sup>+</sup>96, YN95, HKN<sup>+</sup>92] is an architectural technique that allows a processor to issue instructions from multiple hardware contexts, or threads, to the functional units of a superscalar processor in the same cycle. It increases instruction-level parallelism available to the architecture by allowing the processor to exploit the natural parallelism between threads each cycle.

Simultaneous multithreading outperforms previous models of hardware multithreading primarily because it hides short latencies (which can often dominate performance on a uniprocessor) much more effectively. For example, neither finegrain multithreaded architectures [ACC<sup>+</sup>90, LGH94], which context switch every cycle, nor coarse-grain multithreaded architectures [AKK<sup>+</sup>93, SBCvE90], which context switch only on long-latency operations, can hide the latency of a single-cycle integer add if there is not sufficient parallelism in the same thread.

What has not been shown previously is that an SMT processor does not

necessarily handle very long-latency operations as well as other models of multithreading. SMT typically benefits from giving threads complete access to all resources every cycle, but when a thread occupies resources without making progress, it can impede the progress of other threads. In a coarse-grain multithreaded architecture, by contrast, a stalled thread is completely evicted from the processor on a context switch; however, with SMT a stalled thread continues to hold instruction queue or reservation station space, and can even continue fetching instructions into the machine while it is stalled.

The ability of one SMT thread to uselessly degrade another, in the absence of any true dependence between them, is a pipeline-level impediment to our overall quest in this dissertation for on-chip parallel execution. In this chapter we demonstrate that an SMT processor can be throttled by a single thread with poor cache behavior; however, by identifying threads that become stalled, and limiting their use of machine resources, this problem can be eliminated. This provides not only significantly higher overall throughput, but also more predictable throughput, as threads with good cache behavior are much more insulated from co-scheduled threads with poor cache behavior.

## 3.2 The Impact of Long-latency Loads

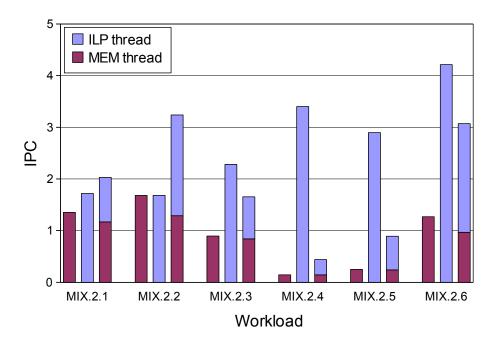

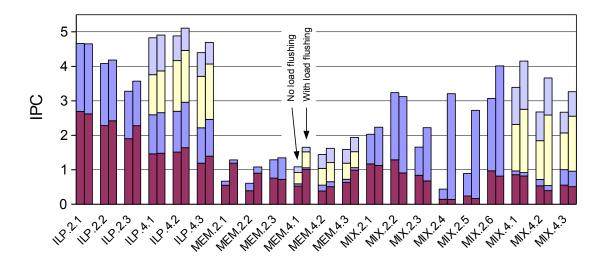

We demonstrate the problem of long-latency loads using a simple experiment, with results depicted in Figure 3.1. For six combinations of two threads (the actual workloads and experimental configuration are described in Section 3.4), the figure shows three results: the IPC of each of the two threads running alone, and of the two threads running together on the SMT processor. In each case the light bars represent memory-intensive benchmarks, and the gray bars represents applications with good cache behavior.

This example shows that a thread exhibiting poor cache performance can become a significant inhibitor to another thread with good cache behavior. There are two factors that allow an application with poor cache locality to cripple coscheduled applications. First, an application that regularly sweeps through the

Figure 3.1: The performance of several two-thread mixes of memory-bound and ILP-bound applications. The stacked bars represent two-thread runs, while the single bars depict single-thread runs of the two component benchmarks of each group.

shared cache will evict data from the other applications, degrading their cache hit rates. Second, the memory-bound application can acquire and hold critical execution resources while it is not making progress due to long-latency memory operations, degrading every thread's performance. In this chapter, we focus on the latter problem.

Few applications contain sufficient parallelism to hide long memory operations (e.g., more than a dozen cycles). While multithreading allows other threads to hide that latency, if the stalled thread fills the instruction queue with waiting instructions, it shrinks the window available for the other threads to find instructions to issue. Thus, when parallelism is most needed – when one or more threads are no longer contributing to the instruction flow – fewer resources are available to expose that parallelism.

This is most clearly demonstrated for the instruction queues by the MIX.2.5 workload, for which the integer queue is on average 97% occupied when at least one L2 miss is outstanding, but only 62% occupied at other times. Besides instruction queues, other resources that are potentially held or used by a thread stalled waiting for a long memory operation include renaming registers and fetch/decode bandwidth. We will demonstrate that contention for shared resources is by far the dominant factor causing the poor performance shown in Figure 3.1.

#### 3.3 Related Work

Simultaneous multithreading [TEL95, TEE<sup>+</sup>96, YN95, HKN<sup>+</sup>92] is an architectural technique that allows a processor to issue instructions from multiple hardware contexts, or threads, to the functional units of a superscalar architecture each cycle. The experiments in this chapter build upon the SMT architecture presented in [TEE<sup>+</sup>96]; previous SMT research has not exposed the problem (or solutions) examined here. One important reason for that has been the inability of pre-2000 instantiations of the SPEC benchmark suite to put significant pressure on a reasonable cache hierarchy.

Less aggressive models of multithreading are less prone to such problems.

Coarse-grain multithreading [AKK<sup>+</sup>93, SBCvE90] is aimed *only* at the long-latency load problem, and makes no attempt to address any other machine latency. Because coarse-grain architectures allow only one thread to have access to execution resources at any time, they alway flush stalled threads completely from the machine. Fine-grain multithreading [ACC<sup>+</sup>90, LGH94] could potentially have shared scheduling resources which exhibit this problem, depending on the architecture. However, these architectures (e.g., the Cray/Tera MTA [ACC<sup>+</sup>90]) have traditionally been coupled with in-order execution, where scheduling windows only need to keep a few instructions per thread visible.

We ignore the latency of synchronization operations (the other source of long and non-deterministic latencies) in this analysis. Tullsen, et al.[TLEL99] have shown the advantage of a synchronization primitive which both blocks and flushes a thread from the queue when it fails to acquire a lock; however, the performance implications of not flushing were not investigated, and that paper gives no indication that a similar technique is necessary for loads.

Previous work on the interaction of SMT processors and the cache hierarchy has focused on cache size and organization (Nemirovsky and Yamamoto [NY98]), bandwidth limitations (Hily and Seznec [HS98]), or cache partitioning [TEL95].

Cache prefetching [CB95, MLG92] attacks the long-latency load problem in a different way, seeking to eliminate the latency itself. Recent work in prefetching targets multithreaded processors specifically, using idle hardware contexts to initiate prefetching. These include Collins, et al. [CWT<sup>+</sup>01], Luk [Luk01], and Zilles and Sohi [ZS01].

Following the original publication of the work in this chapter, numerous later research projects have noted the impact of the resource-hoarding problems we have identified here, and have expanded upon our solution in different ways. El-Moursy et al. [EMA03] introduce several fetch-gating policies which seek to avoid the hoarding of instruction queue resources that we identify and react to here, without the cost of flushing. They evaluate several dynamic fetch-gating schemes, driven by outstanding load counts and predictions thereof, with an eye toward reducing queue occupancy with minimal performance degradation.

Balanced Multithreading (BMT) [TKTC04] takes advantage of the lull in forward progress following a stall for off-chip memory access, using it as an opportunity to replace the stalling thread with one that is ready for execution. By rotating additional threads into the processor at opportune times, BMT augments the ILP visible to an SMT execution engine by bringing in "fresh" threads in the face of memory stalls, instead of simply flushing instructions and blocking fetch as we consider here.

Cazorla et al. [CRVF04b] evaluate several of the policies in this chapter along with several from [EMA03]. They consider in more detail the effects of both overlapping and sequential memory stalls from multiple threads, and demonstrate several refinements to our policies which result in improved throughput and fairness. In further work [CRVF04a], they introduce a detailed feedback-directed hardware resource management policy which dynamically partitions the instruction queues and register files among threads to avoid the hoarding we characterize in this chapter.

Eyerman et al. [EE07] introduce a nuanced approach which predicts, for each long-latency load event, the amount of memory-level parallelism (MLP) available at that point in the program. In addition to flushing and stalling, their policy can also allow a thread to proceed a short distance past each memory stall in order to expose additional predicted MLP before corrective action is taken. In further work [EE09], they introduce a detailed cycle-accounting mechanism which explicitly accounts for cycles spent stalled for memory, as well as those dominated by the execution of co-scheduled threads; this provides a online quantification of the inter-thread resource conflicts we consider only after the fact.

### 3.4 Methodology

Table 3.1 summarizes the benchmarks used in our simulations. All benchmarks are taken from the SPEC2000 suite and use the reference data sets. Six are memory-intensive applications: those which, in our system, experience between 0.02 and 0.12 L2 cache misses per instruction on average, over the simulated por-

Table 3.1: The single-threaded benchmarks used in this chapter, along with the data set and the number of instructions emulated before beginning measured simulation.

| Benchmark               | Input             | Fast-forward ( $\times 10^9$ ) |  |

|-------------------------|-------------------|--------------------------------|--|

| Memory-intensive, "MEM" |                   |                                |  |

| ammp                    | ref               | 1.7                            |  |

| applu                   | ref               | 0.7                            |  |

| art                     | c756hel.in (ref)  | 0.2                            |  |

| mcf                     | ref               | 1.3                            |  |

| swim                    | ref               | 0.5                            |  |

| twolf                   | ref               | 1.0                            |  |

| ILP-intensive, "ILP"    |                   |                                |  |

| apsi                    | ref               | 0.8                            |  |

| eon                     | cook (ref)        | 1.0                            |  |

| fma                     | ref               | 0.1                            |  |

| gcc                     | integrate.i (ref) | 0.5                            |  |

| gzip                    | log (ref)         | 0.1                            |  |

| vortex                  | ref               | 0.5                            |  |

tion of the code. The other six benchmarks are taken from the remainder of the suite and have lower miss rates, and hence higher inherent ILP. Table 3.2 lists the multithreaded workloads used in our simulations. All of the simulations in this chapter either contain threads all from the first group (the MEM workloads in Table 3.2), all from the second group (ILP), or an equal mix from each (MIX). Most of this chapter focuses on the MIX results; however, the other results are included to demonstrate the universality of the problem.

We simulate execution with a derivative of SMTSIM [Tul96], as introduced in Chapter 2. The baseline processor configuration used for most simulations is shown in Table 3.3. The instruction queues for our eight-wide processor are roughly twice the size of the four-issue Alpha 21264 (15 FP and 20 integer entries) [Com00]. In addition, the 21264 queues cannot typically remain completely full due to the implemented queue-add mechanism, a constraint we do not model with our queues. These instruction queues, as on the 21264, remove instructions upon issue, and thus can be much smaller than, for example, a register update unit [SV87] which holds instructions until retirement. Section 3.9 also investigates larger instruction

Table 3.2: The multi-threaded workloads evaluated.

| 0.2. The main unreaded workloads evan |                           |  |

|---------------------------------------|---------------------------|--|

| ID                                    | Component Benchmarks      |  |

| ILP.2.1                               | apsi, eon                 |  |

| ILP.2.2                               | fma3d, gcc                |  |

| ILP.2.3                               | gzip, vortex              |  |

| ILP.4.1                               | apsi, eon, fma3d, gcc     |  |

| ILP.4.2                               | apsi, eon, gzip, vortex   |  |

| ILP.4.3                               | fma3d, gcc, gzip, vortex  |  |

| MEM.2.1                               | applu, ammp               |  |

| MEM.2.2                               | art, mcf                  |  |

| MEM.2.3                               | swim, twolf               |  |

| MEM.4.1                               | ammp, applu, art, mcf     |  |

| MEM.4.2                               | art, mcf, swim, twolf     |  |

| MEM.4.3                               | ammp, applu, swim, twolf  |  |

| MIX.2.1                               | applu, vortex             |  |

| MIX.2.2                               | art, gzip                 |  |

| MIX.2.3                               | swim, gcc                 |  |

| MIX.2.4                               | ammp, fma3d               |  |

| MIX.2.5                               | mcf, eon                  |  |

| MIX.2.6                               | twolf, apsi               |  |

| MIX.4.1                               | ammp, applu, apsi, eon    |  |

| MIX.4.2                               | art, mcf, fma3d, gcc      |  |

| MIX.4.3                               | swim, twolf, gzip, vortex |  |

Table 3.3: Processor configuration.

| Parameter                        | Value                               |

|----------------------------------|-------------------------------------|

| Fetch width                      | 8 instructions per cycle            |

| Fetch policy                     | ICOUNT.2.8 [TEE+96]                 |

| Pipeline depth                   | 8 stages                            |

| Min branch misprediction penalty | 6 cycles                            |

| Branch predictor                 | 2K gshare                           |

| Branch Target Buffer             | 256 entry, 4-way associative        |

| Active List Entries              | 256 per thread                      |

| Functional Units                 | 6 Integer (4 also load/store), 3 FP |

| Instruction Queues               | 64 entries (32 integer, 32 FP)      |

| Registers For Renaming           | 100 integer, 100 FP                 |

| Inst Cache                       | 64 KiB, 2-way, 64-byte lines        |

| Data Cache                       | 64 KiB, 2-way, 64-byte lines        |

| L2 Cache                         | 512 KiB, 2-way, 64-byte lines       |

| L3 Cache                         | 4 MiB, 2-way, 64-byte lines         |

| Latency from previous level      | L2 10 cycles, L3 20 cycles          |

| (with no contention)             | Memory 100 cycles                   |

#### queues.

The policies of the SMT fetch unit have a significant impact on our results. Our baseline configuration uses the ICOUNT.2.8 mechanism from [TEE+96]. The ICOUNT mechanism fetches instructions from the thread or threads least represented in the pre-execute pipeline stages. This mechanism already goes a long way towards preventing a stalled thread from filling the instruction queue (Section 3.9 shows how much worse the load problem becomes without ICOUNT), but we show that it does not completely solve the problem. In particular, if the processor is allowed to fetch from multiple threads per cycle, it becomes more likely a stalled thread (while not of the highest priority) can continue to dribble in new instructions. Our baseline fetch policy (ICOUNT.2.8) does just that, fetching eight instructions total from two threads. Section 3.9 also looks at fetch policies that only fetch from one thread per cycle, demonstrating that the problem of long-latency loads persists even in that scenario.

#### 3.5 Metrics