# UC Irvine ICS Technical Reports

### Title

Behavioral modeling of DRACO : a peripheral interface ASIC

### Permalink

https://escholarship.org/uc/item/0qz176xg

### **Authors**

Gupta, Rajesh Dutt, Nikil D.

# Publication Date 1990-06-19

Peer reviewed

Z 699 C 3 no. 95-13

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

\_\_\_\_\_

## BEHAVIORAL MODELING OF DRACO: A PERIPHERAL INTERFACE ASIC

by

Rajesh Gupta Nikil D. Dutt

**Technical Report 90-13**

Information and Computer Science University of California at Irvine Irvine, CA 92717

### Keywords

ASIC Design Modeling, Design Specification, VHDL, Reverse Engineering from Data Sheets.

. .

.

### Behavioral Modeling of DRACO: A Peripheral Interface ASIC

by

Rajesh Gupta Nikil D. Dutt

### Abstract

This paper describes the behavioral modeling of DRACO, a peripheral interface Application Specific Integrated Circuit (ASIC) developed by Rockwell International for numerical control applications. The behavioral model was generated from a data sheet of the fabricated chip, which primarily described the chip's input-output functionality, physical and operational characteristics, and a functional block diagram. The data sheet contained very little abstract behavioral information. This report describes the abstract behavioral model of the DRACO chip, and uses flowcharts and VHDL to capture the behavior. The behavioral model was developed through reverse engineering of the data sheet description, supplemented by further consultation with designers of the DRACO ASIC at Rockwell International. The report describes typical behavioral test sequences that were applied to the DRACO VHDL model to verify its correctness. The appendices contain the original DRACO datasheet and the VHDL code used to capture DRACO's behavior.

----

-----

- -

\_ \_ \_

### TABLE OF CONTENTS

-----

----

### CHAPTER

| 1. | INTRODUCTION                                | 1  |

|----|---------------------------------------------|----|

| 2. | ROCKWELL DRACO CHIP                         |    |

|    | 2.1. Functional Description of DRACO        | 3  |

|    | 2.2. DRACO's Structural Model               | 6  |

| 3. | BEHAVIORAL MODEL OF DRACO                   | 6  |

| 4. | VHDL DESCRIPTION OF DRACO                   | 19 |

|    | 4.1. Treatment of Timing Constraints        | 19 |

|    | 4.2. Type Declarations                      | 21 |

|    | 4.3. Resolution Functions                   | 21 |

|    | 4.4. Stimulus to the VHDL Description       | 22 |

|    | 4.5. Simulator Specifics: Vantage and Zycad | 22 |

| 5. | EXAMPLES                                    | 23 |

|    | 5.1. Example 1                              | 23 |

|    | 5.2. Example 2                              | 24 |

|    | 5.3. Example 3                              | 27 |

|    | 5.4. Example 4                              | 30 |

|    | 5.5. Example 5                              | 33 |

| 6. | Acknowledgements                            | 40 |

| 7. | Summary                                     | 40 |

| 8. | References                                  | 41 |

| AP | PENDIX A. Rockwell DRACO Data Sheet         | 42 |

| AP | PENDIX B. VHDL Source Code for DRACO        | 74 |

June 19, 1990

\_\_\_\_\_

### 1. INTRODUCTION

A commercial chip design is typically described using logic schematics and data sheets which give a structural and functional view of the design from a logic designer's perspective. Unfortunately, such a description does not describe the abstract behavior of the design in a complete fashion. Although some of this behavioral information may be present in each chip's data sheets and schematics, the lack of complete, more rigorous behavioral descriptions of chip designs is a pressing problem faced by many system houses, chip manufacturers and end users. With technological changes occurring at such a rapid pace, chip designs can become obsolete quickly, requiring retargetting of the intial design specification to a new technology or library. Since there is no well documented behavioral description of the design, retargetting of the design is a tedious process involving the reverse engineering of the schematics and data sheets to understand the abstract behavior of the design. This means a longer time to design, and therefore a longer time to a finished product, in a market where chip designs get obsolete very quickly.

Furthermore, chip complexities are increasing at a tremendous pace; by the year 1994, we can expect to see a microprocessor-on-a-chip with 6 million transistors on a 750 sq. mm. die, delivering 200 mips of performance running on a 100 Mhz clock [Sumn89]. To cope with this explosion of design complexity, there is an urgent need for design tools that capture designs at higher levels of description, and which automate higher levels of the design process, so that design alternatives can be explored quickly and accurately. Moreover, several nationally recognized figures have indicated that the competitiveness of the U.S. semiconductor industry is dependent on our ability to integrate tools that permit rapid turnaround of chip designs, from concept, all the way to manufacturing [IEEE90].

June 19, 1990

All of these indicators underscore the need for better design specifications using more rigorous media such as behavioral hardware description languages. Such specifications can provide behavioral models for simulation, verification and synthesis of designs. They also document the design in a systematic, comprehensible fashion, removing the need for reverse engineering of lower level descriptions.

In this report, we attempt to describe the behavior of a commercial chip design (DRACO) developed by Rockwell International. Rockwell's design specification for DRACO consisted of a data sheet and a set of VHDL netlists (schematics) representing the final chip design. The functionality in the data sheet only described the block diagram of the chip and a description of its input-output characteristics. There was no comprehensive abstract behavioral description of the chip available at Rockwell International. As a result, there were no behavioral test cases available, nor were there any typical design scenarios for the chip.

Using this data sheet description, an abstract behavioral model of the chip was developed using simple flow charts. This required some reverse engineering in order to avoid references to specific hardware constructs. The flowcharts deliberately use pseudocode instead of a particular hardware description language. This facilitated easier development of the behavioral model. Inconsistencies and clarifications were resolved by communication with designers at Rockwell International [Lars90] [Pase90]. Once the complete behavior of the chip had been described, a set of behavioral test scenarios were developed to test typical operational sequences of the chip.

At this point, a behavioral VHDL (VHSIC Hardware Description Language) model of the DRACO chip was developed. This model was subjected to test stimuli corresponding to

### Modeling DRACO

the typical operational scenarios developed previously, to verify its operational correctness.

This report begins with the functional description and structural view of the DRACO chip in sections 2 and 3. Section 4 describes the behavioral model of the DRACO chip using flowcharts and pseudocode. Section 5 describes how DRACO was modeled in behavioral VHDL. Section 6 gives five typical operational sequences that were used to test the behavioral VHDL model. Appendix I contains Rockwell's data sheet for DRACO<sup>1</sup>, while appendix II lists the actual behavioral VHDL code used to model DRACO.

### 2. ROCKWELL DRACO CHIP

DRACO is a peripheral interface Application Specific Integrated Circuit (ASIC) developed by Rockwell International for numerical control applications. This section reviews the functional and structural characteristics of the DRACO chip as presented in the Rockwell DRACO data sheet. Appendix I contains the actual data sheet for DRACO, which has a more detailed description of DRACO's functionality.

### 2.1. Functional Description of DRACO

DRACO's basic function is to interface 16 I/O ports to a microprocessor's 8 bit multiplexed address/data bus and control signals. DRACO may be connected remotely through an 18 inch long ribbon cable. Such a configuration may introduce errors in the transmitted signal due to Electro Magnetic Interference (EMI). To minimize any danger that may be caused by the receipt of corrupt data, several security features have been built into

<sup>&</sup>lt;sup>1</sup> Rockwell International has granted U.C. Irvine permission to duplicate the data sheets for educational purposes.

DRACO. These special features are:

- (1) Hardware Key: DRACO has a key which must be unlocked prior to configuring the chip. This configuration protocol adds an extra level of security since an incorrect configuration of the chip could result in considerable operational havoc. Furthermore, configuration registers may be written into only when the configuration is unlocked and the I/O ports may be written into only when data is unlocked.

- (2) Address Parity Check: DRACO may optionally be configured to perform parity checks on all received addresses from the host.

- (3) Data Parity Check: DRACO may optionally be configured to perform data parity checks on data received from the host and may generate parity while loading data onto the address bus.

- (4) Checksum: DRACO generates an inverted checksum from the data to be output, compares it with the the received checksum and updates the I/O ports only if the checksums are equivalent.

Such extensive error checking measures ensures nearly error-free operation in the presence of EMI.

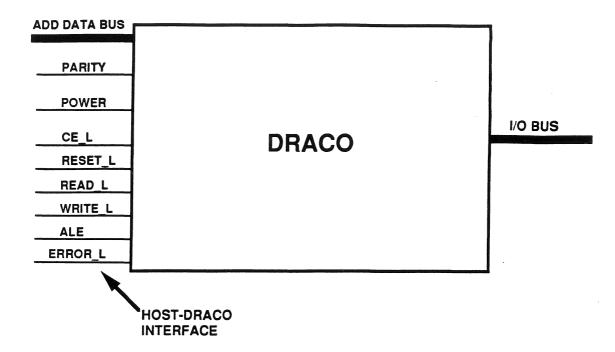

DRACO's input-output configuration is presented in Figure 1. A description of some of DRACO's pins follows:

ADD\_DATA\_BUS: The bus transfers address and data from the host to DRACO and data from DRACO to the host.

June 19, 1990

Modeling DRACO

# Figure 1. DRACO's I/O Configuration

PARITY: Carries address and data parity from the host to DRACO and data parity from DRACO to the host.

POWER: Indicates power on / power off status.

RESET\_L: This input is used to initialize all internal registers and latches; it should be held low after power is applied.

READ\_L: A low on this input causes internal read data to be placed on the address data bus and the parity to be placed on the parity pin when data is enabled.

WRITE\_L: A low to high transition on this input causes external data on the address data bus and parity pins (when data parity is enabled) to be written into DRACO.

June 19, 1990

CE\_L: This is a Chip enable input, which must be held low to execute a read or write cycle.

IO\_BUS: These pins carry the output data and the data to be read in from DRACO.

ERROR\_L: This is an active low output which is asserted whenever an error occurs in the data transmission between DRACO and the host microprocessor. This output will be latched low and must be reset by the user.

### 2.2. DRACO's Structural Model

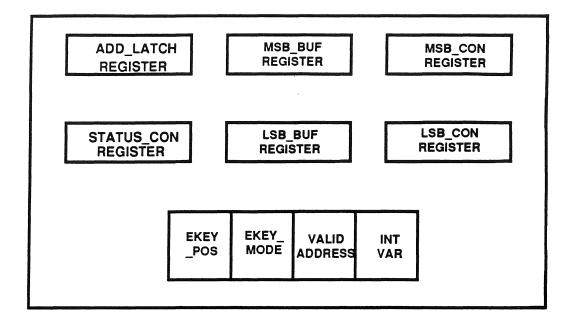

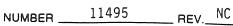

The DRACO's structural model is shown in Figure 2. The structure consists of 6 registers and 4 D Flip Flops which store the data and DRACO's configuration.

### 3. BEHAVIORAL MODEL OF DRACO

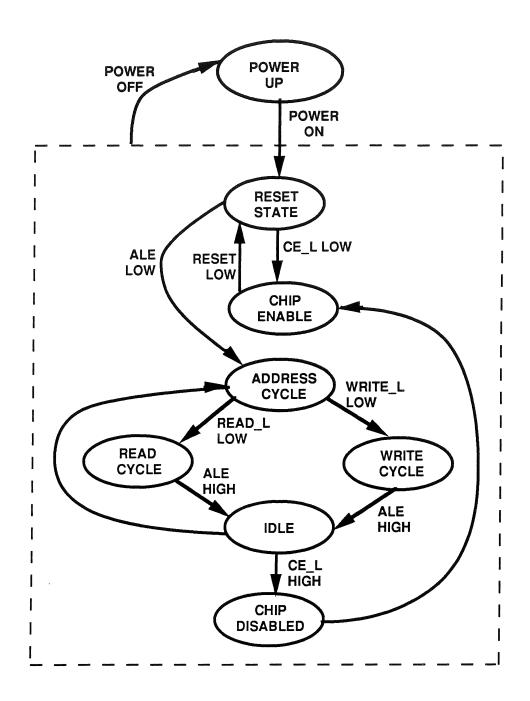

The behavior of DRACO can be naturally modeled using a state transition diagram consisting of the following 8 primary states:

(1) Reset State

- (2) Chip enabled

- (3) Address Cycle

- (4) Read Cycle

- (5) Write Cycle

### Figure 2. Behavioral Structure For DRACO

- (6) Idle

- (7) Chip Disabled

- (8) Power Off

Figure 3 shows the state transition diagram using these eight states.

A typical initial sequence of operations for DRACO would involve turning the power on (Power-Up to Reset State), enabling the chip (Reset to Chip Enable State) and then resetting the chip (Chip Enable to Reset State) so as to configure DRACO using default settings (data/address parity off, ports set to be bidirectional, etc.). Subsequently, data can

June 19, 1990

# Figure 3. DRACO State Diagram

be written into or read from DRACO.

For a data access from DRACO, the chip passes through Address Cycle and the Read Cycle. The following sequence of events occurs: Address appears on the address/data bus, ALE goes low, READ\_L goes low and finally data is placed by DRACO on the address/data bus. When ALE goes low, data from the bus is latched into DRACO if it is valid. DRACO places data on the bus a specified time after the READ\_L signal goes low.

For writing to DRACO, the chip sequences through the Address Cycle and the Write Cycle. The following sequence of events occurs: Address appears on the address/data bus, ALE goes low, WRITE\_L goes low, data appears on the address/data bus, and WRITE\_L goes high. When ALE goes low, the address, if valid, is latched into DRACO. When WRITE\_L goes high, data is written into DRACO.

DRACO is in the Idle State when power is on and the chip is enabled, but is not executing the Read, Write or Address Cycles. During this state ALE, READ\_L and WRITE\_L are all high. DRACO enters this state after the Read and Write cycles.

Whenever power is switched on, the chip immediately sequences to the RESET State; there is no "Power On" State, since this is effectively the Reset State.

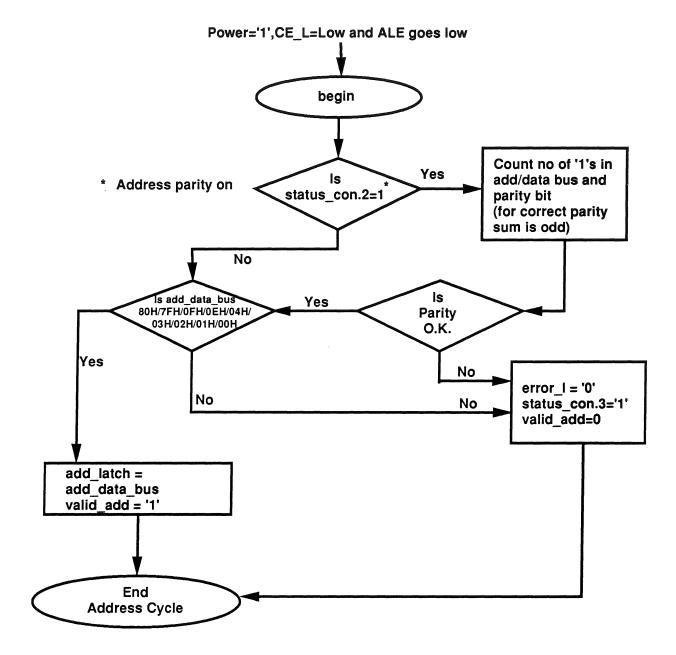

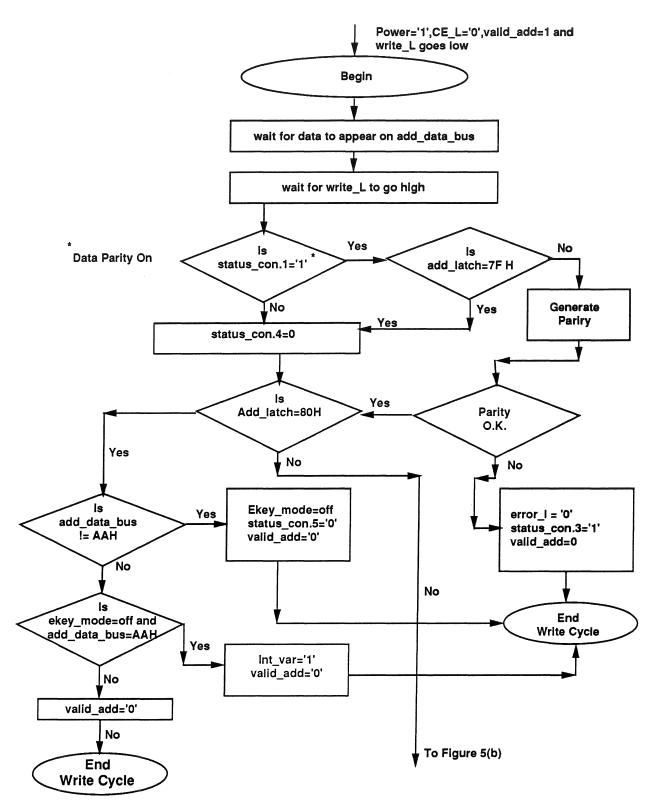

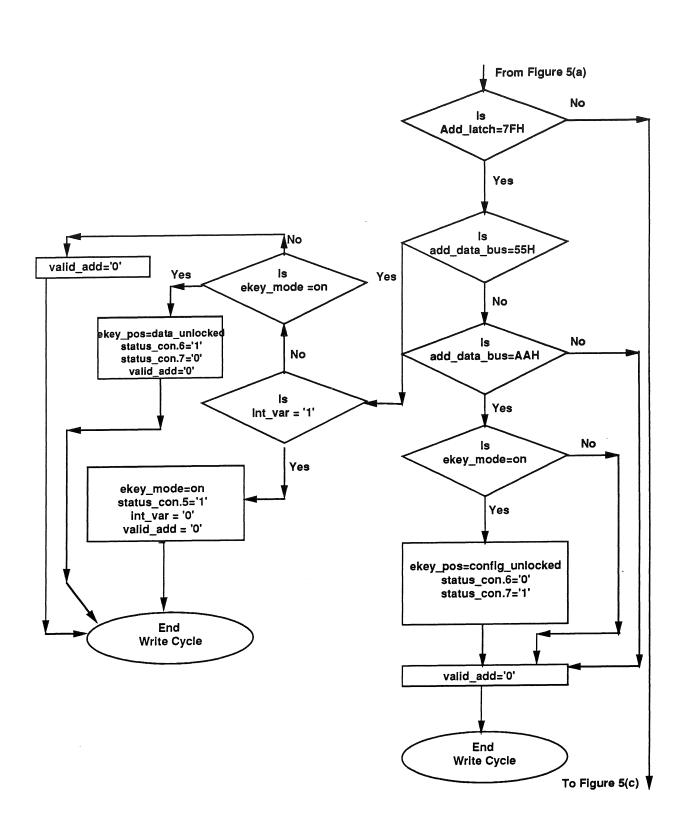

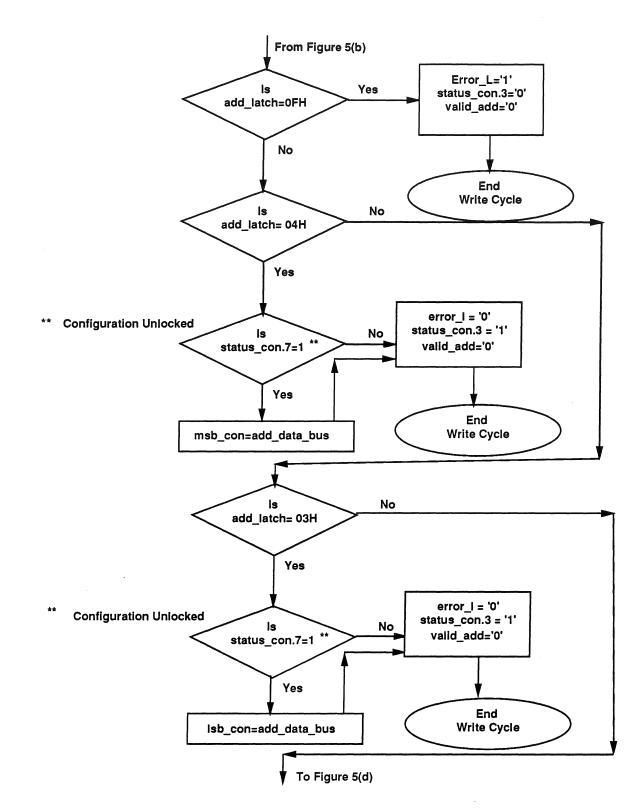

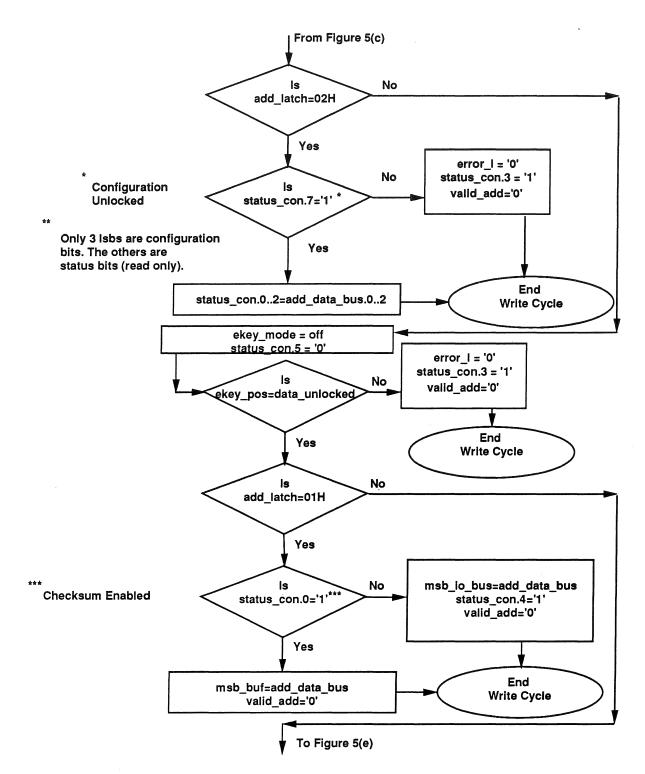

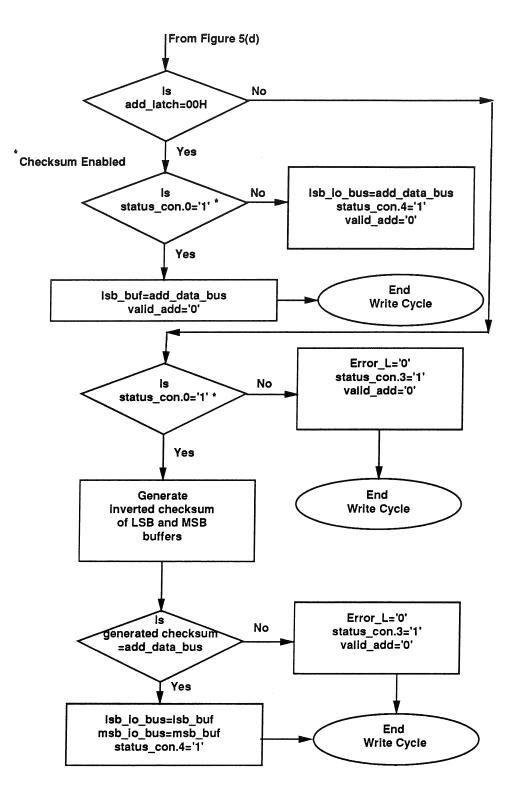

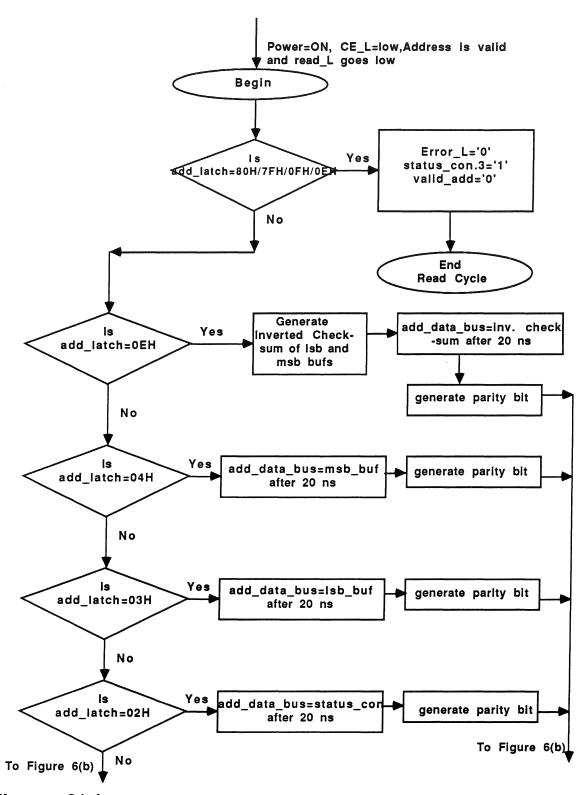

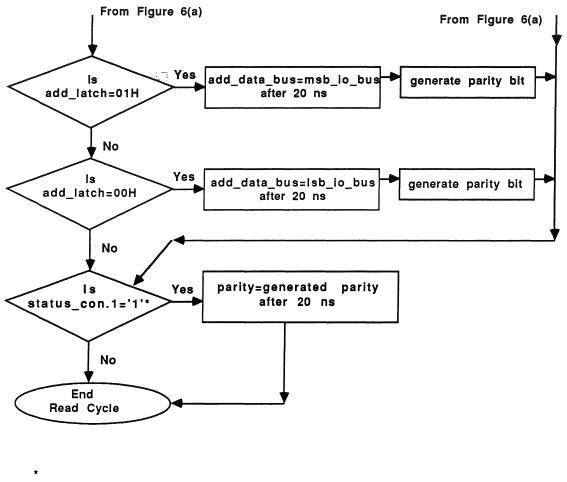

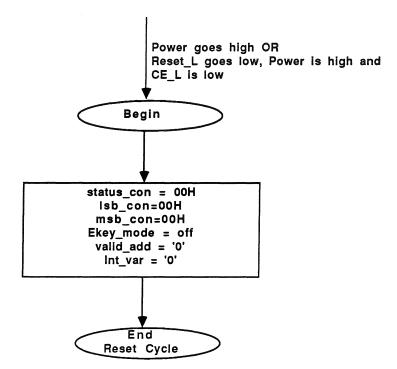

Each of the the 4 states Address Cycle, Write Cycle, Read Cycle and Reset Cycle are described by secondary sequential state diagrams. The flowcharts and pseudo-code for the Address, Write, Read and Reset Cycles are given in Figures 4, 5, 6 and 7 respectively. These flowcharts should be fairly self-explanatory.

# Figure 4. Secondary State Diagram for ADDRESS CYCLE

Figure 5(a). Secondary State Diagram of WRITE CYCLE

# Figure 5(b). Secondary State Diagram of WRITE CYCLE (contd.)

Figure 5(c). Secondary State Diagram of WRITE CYCLE (contd.)

Figure 5(d). Secondary State Diagram of WRITE CYCLE (contd.)

Figure 5(e). Secondary State Diagram of WRITE CYCLE (contd.)

Figure 6(a). Secondary State Diagram of READ CYCLE

Modelling DRACO

Data Parity On

# Figure 6(b). Secondary State Diagram of READ CYCLE (contd.)

Modelling DRACO

# Figure 7. Secondary State Diagram of RESET CYCLE

Modelling DRACO

### 4. VHDL DESCRIPTION OF DRACO

The behavior of the DRACO chip was described in VHDL using the flowcharts and pseudo-code as the preliminary design specification. The behavioral VHDL description used both block and process statements.

Each of DRACO's eight primary states was modeled using a VHDL block, in which a resolved signal of type "state" (described later in this section) is assigned the appropriate state value. The guard at entry to each block specifies the conditions under which a state is to be entered, while the body of each VHDL block includes a guarded signal assignment to the resolved signal. The Read, Write, Address and Reset Cycles were described using a process each for the actions performed in those states.

### 4.1. Treatment of Timing Constraints

The timing specifications in the DRACO data sheet represent the physical characteristics of the completed chip design. The data sheet did not have any behavioral timing specifications in it. As a result, the data sheet's timing specifications will be used as the timing constraints which must be met by the final design. We will look into how these timing specifications get transformed into timing constraints for internal structures (register, adder, etc.) of DRACO in forthcoming reports which will describe synthesis of the DRACO chip.

Assertions were added to the VHDL description to validate the correct sequence of critical signals received from the host. Error messages are reported when incorrect sequences are encountered. For example, an attempt to write to DRACO must be preceded by an address latch. The description, however, does not care about the minimum and

June 19, 1990

maximum timing constraints, but only checks and ensures sequentiality. Therefore, for error-free operation, the host only needs to make sure that it writes data into DRACO after latching a valid address; there is no minimum (or maximum) time constraint between these two events (latching of valid address and writing into the chip).

Moreover, the host should ensure that no two out of the four signals: read\_l, write\_l, reset\_l and ale become active simultaneously (the behavior of the chip cannot be predicted if any pair of these signals is active simultaneously). However, power failures may occur at any time. If the power signal becomes active simultaneously with any other signal, the power signal is selected with priority while the other signal is ignored. Prioritized treatment of the power-off signal is built into the resolution function of the signal representing the chip's state.

From DRACO's state diagram (Figure 3), we can construct the following list which describes the eight states and the conditions under which they are entered:

- RESET STATE: POWER goes high or RESET\_L signal falls low and POWER is high and chip is enabled.

- (2) CHIP ENABLE: CE\_L falls low and POWER is on.

- (3) ADDRESS CYCLE: POWER is high, CE\_L is low and ALE goes low.

- (4) READ CYCLE: POWER is high, CE\_L is low, VALID ADDRESS is true and READ\_L goes low.

- (5) WRITE\_CYCLE: POWER is high, CE\_L is low, VALID ADDRESS is true and WRITE\_L goes low.

June 19, 1990

Modeling DRACO

- (6) IDLE: ALE goes high, power is on and chip is enabled.

- (7) CHIP DISABLED: CE\_L goes high and chip is enabled.

- (8) POWER OFF: POWER goes low.

### 4.2. Type Declarations

A user defined type state has been defined which can assume the following values:  $state = \{ reset, chip\_enabled, chip\_disabled, write, \\ read, address, idle, power\_off \}$

The DRACO chip sequences through these states as indicated in Figure 3.

### 4.3. Resolution Functions

Since the VHDL description has several blocks that make assignments to this signal, a resolution function is declared to resolve the final value assigned to the state signal. This resolution function will give priority to the power\_off state as discussed previously.

For status/configuration registers which have more than one source (for example, status bits of the status/configuration register are updated in all the 4 cycles: read, write, address and reset), we need to define resolution functions. Also, in some cases we need to address individual bits of these registers, both separately and in different processes. Thus each of the configuration registers is declared as an array of resolved bit type. Specifically, the exact VHDL statements are:

function bit\_res\_fun (Input bit\_res) return bit;

June 19, 1990

subtype bitres is bit\_res\_fun bit;

status\_con\_reg: array (7 downto 0) of bitres Register;

The first statement declares a bit resolution function that returns a signal of type bit. The second statement declares a resolved signal subtype called bitres and the last statement declares a register (width 8) of type bitres.

### 4.4. Stimulus to the VHDL Description

In the current VHDL description, input stimuli to the chip are generated without the use of a stimulus/command file. Instead, the ports which carry signals to DRACO from the host are commented out from the entity declaration and declared as signals in the architecture body. These signals are then assigned waveforms in a process body within the architecture. The process "generate\_signals" in the VHDL description performs the function of generating input stimuli for exercising the VHDL model.

### 4.5. Simulator Specifics: Vantage and Zycad

Simulations of DRACO's VHDL behavior were attempted on the Vantage [Vant89] and Zycad [Zyca89] simulators.

The Zycad simulator supported the resolved types described above. However, the Vantage simulator (version 1.203) could not simulate the description, since that version did not support bit-slicing. A description to be simulated on Vantage would therefore require each bit of the register status\_con\_reg to be separated as shown below:

June 19, 1990

status\_con\_reg: bitres; for

$$i = 0$$

to 7

With such a description, a probe file (command file) has to assign values to a register by addressing each bit individually. This is an onerous task when dealing with even a few registers and buses.

### 5. EXAMPLES

This section describes five typical operational scenarios for the DRACO chip. Included with each scenario (labeled "Example") are the stimulus files and the simulation results generated by the Zycad simulator.

### 5.1. Example 1

The first example writes data (FFH) onto the low byte of the I/O ports. In this example the following signals are received by DRACO:

Power on at 25 fs;

### Chip enabled at 50 fs;

Following the receipt of these two signals, the chip is reset and is set to execute further commands such as address latch and reset. In the reset state, the address parity, data parity and checksum are off, the electronic key is off and data and configurations are locked. To write data into the low byte of the I/O ports, the following states have to execute four times:

address cycle ----> write cycle ----> idle

June 19, 1990

In the first two cycles, the electronic key is switched on; data is unlocked in the third cycle, while data is written to the I/O ports in the fourth cycle.

Details of each cycle are given below:

cycle1: write data AAH at address 80H followed by

cycle2: write data 55H at address 7FH.

cycle3: write data 55H at address 7FH

cycle4: write data FFH at address 00H

These four cycles execute between 100 fs and 500 fs. Finally the chip is disabled at 1910 fs and the power is turned off at 1920 fs after completion of these four cycles.

The stimulus file for this example is shown in Figure 8.

Tabular results obtained from the simulation are shown in Figure 9.

### 5.2. Example 2

This example simulates the behavior of DRACO when the parity checks are enabled. DRACO needs to be configured to activate these checks. As with the previous example, the following actions are required after the electronic key is switched on:

1) Unlock the DRACO configuration

2) Set the 1st and 2nd bits of the configuration register to enable parities.

The first step requires writing AAH at address 7FH, while the second step requires writing 06H at address 02H.

June 19, 1990

Modeling DRACO

### STIMULUS FILE FOR EXAMPLE 1

-----

--------

| STIMULUS FILE FOR EXAMPLE 1                               |  |  |

|-----------------------------------------------------------|--|--|

| 40 LINES                                                  |  |  |

| GENERATE_SIGNALS:                                         |  |  |

| process                                                   |  |  |

| begin                                                     |  |  |

| This example unlocks the key, unlocks the data and writes |  |  |

| to the lsb I/O bus.                                       |  |  |

| POWER SIGNAL                                              |  |  |

|                                                           |  |  |

| power $\leq = 0$ ,<br>'1' after 25 fs,                    |  |  |

| $^{1}$ after 25 is,<br>$^{0}$ after 1920 fs:              |  |  |

| 0 atter 1920 is,                                          |  |  |

| CHIP ENABLE SIGNAL                                        |  |  |

| $ce_{\perp} <= '1'$                                       |  |  |

| '0' after 50 fs,                                          |  |  |

| '1' after 1910 fs;                                        |  |  |

|                                                           |  |  |

| $add_data_bus <= X"80"$ after 105 fs,                     |  |  |

| X"AA" after 140 fs,                                       |  |  |

| X"7F" after 205 fs,<br>X"55" after 240 fs,                |  |  |

| X"55" after 240 fs,                                       |  |  |

| X"7F" after 305 fs,                                       |  |  |

| X"55" after 340 fs,                                       |  |  |

| X"00" after 405 fs,                                       |  |  |

| X"FF" after 440 fs;                                       |  |  |

|                                                           |  |  |

| ale $<=$ '1', '0' after 110 fs, '1' after 170 fs,         |  |  |

| '0' after 210 fs, '1' after 270 fs,                       |  |  |

| '0' after 310 fs, '1' after 370 fs,                       |  |  |

| '0' after 410 fs, '1' after 470 fs;                       |  |  |

| write_ $l <= '1'$ , '0' after 130 fs, '1' after 160 fs,   |  |  |

| '0' after 230 fs, '1' after 260 fs,                       |  |  |

| '0' after 330 fs, '1' after 360 fs,                       |  |  |

| '0' after 430 fs, '1' after 460 fs;                       |  |  |

| ,                                                         |  |  |

| $read_l <= '1';$                                          |  |  |

| wait;                                                     |  |  |

|                                                           |  |  |

| end process GENERATE_SIGNALS;                             |  |  |

Figure 8. Stimulus File for Example 1.

June 19, 1990

Modeling DRACO

#### SIMULATION RESULTS FROM EXAMPLE 1

SMON9 CE ACTIVE /DRACO/ERROR\_L SMON8 CE ACTIVE /DRACO/MSB\_BUF CE ACTIVE /DRACO/LSB\_BUF SMON7 CE ACTIVE /DRACO/DATA\_BUS SMON6 SMON5 CE ACTIVE /DRACO/MSB\_IO\_BUS CE ACTIVE /DRACO/LSB\_IO\_BUS SMON4 SMON3 CE ACTIVE /DRACO/CYCLE CE ACTIVE /DRACO/EKEY\_POS SMON2 SMON1 CE ACTIVE /DRACO/ADD\_DATA\_BUS CE ACTIVE /DRACO/EKEY\_MODE SMON 25 FS SMON3: ACTIVE /DRACO/CYCLE (value = RESET) SMON: ACTIVE  $/DRACO/EKEY\_MODE$  (value = OFF) ACTIVE /DRACO/EKEY\_POS (value = LOCKED) SMON2: SMON: ACTIVE  $/DRACO/EKEY\_MODE$  (value = OFF) SMON2: ACTIVE /DRACO/EKEY\_POS (value = LOCKED) 50 FS SMON3: ACTIVE /DRACO/CYCLE (value = CHIP\_ENABLED) 105 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"80") 110 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 130 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 140 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") SMON1: 170 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 205 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value =  $X^{"7}F"$ ) 210 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 230 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 240 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") 260 FS SMON: ACTIVE /DRACO/EKEY\_MODE (value = ONN) 270 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 305 FS SMON1: ACTIVE  $/DRACO / ADD_DATA_BUS$  (value = X"7F") 310 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 330 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 340 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") SMON1: 360 FS SMON2: ACTIVE /DRACO/EKEY\_POS (value = DATA\_UNLOCKED) 370 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 405 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"00") 410 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 430 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 440 FS SMON1: ACTIVE  $/DRACO / ADD_DATA_BUS$  (value = X"FF") 460 FS

| SMON4:  | ACTIVE $/$ DRACO/LSB_IO_BUS (value = X"FF")                                       |

|---------|-----------------------------------------------------------------------------------|

| SMON:   | ACTIVE /DRACO/LSB_IO_BUS (value = X"FF")<br>ACTIVE /DRACO/EKEY_MODE (value = OFF) |

| 470 FS  |                                                                                   |

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)                                         |

| 1910 FS |                                                                                   |

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = CHIP_DISABLE)                                 |

| 1920 FS |                                                                                   |

| SMON3:  | ACTIVE /DRACO/CYCLE (value = POWER_OFF)                                           |

| 2000 FS |                                                                                   |

### Figure 9. Tabular Results For Example 1.

Except for the last cycle, the parity of data and addresses received by DRACO from the host are correct. However, the address parity bit received in the last cycle is incorrect.

The tabular results obtained as a result of simulating this example are shown Figure 11. Note that a warning message is generated on receipt of incorrect parity (corrupted data). The subsequent write cycle is also aborted since there is no valid address to write the data.

Power is turned on at 25 fs, chip is enabled at 50 fs. In the end the chip is disabled at 1910 fs and power turned off at 1920fs.

The stimulus file for this example is shown in Figure 10.

### 5.3. Example 3

This example simulates the behavior for a test case which is identical to EXAMPLE 2 except that in the last cycle, the data parity (instead of the address parity) bit is received in error.

The stimulus file for this example is shown in Figure 12.

June 19, 1990

### **STIMULUS FILE FOR EXAMPLE 2**

-- 59 LINES GENERATE\_SIGNALS: process begin -- THIS PROCESS CONFIGURES DRACO TO ENABLE DATA AND ADDRESS

-- PARITIES. IT THEREAFTER UNLOCKS DATA AND WRITES FF TO THE -- LSB I/O PORT. SINCE ADDRESS PARITY IS FALSE IN THE -- LAST WRITE THE OPERATION IS UNSUCCESSFUL. -- POWER SIGNAL power  $\langle = '0',$ '1' after 25 fs, '0' after 1920 fs; -- CHIP ENABLE SIGNAL  $ce_{-} <= '1',$ '0' after 50 fs, '1' after 1910 fs; ale <= '1', '0' after 110 fs, '1' after 170 fs, 1, 0 after 110 is, 1 after 170 '0' after 210 fs, '1' after 270 fs, '0' after 310 fs, '1' after 370 fs, '0' after 410 fs, '1' after 470 fs, '0' after 510 fs, '1' after 570 fs, '0' after 610 fs, '1' after 670 fs;  $add_data_bus <= X"80"$  after 105 fs, X"AA" after 140 fs, X "AA after 140 is, X"7F" after 205 fs, X"55" after 240 fs, X"7F" after 305 fs, X"AA" after 340 fs, X"02" after 405 fs, X"06" after 440 fs, X"7F" after 505 fs, X"55" after 540 fs, X"00" after 605 fs, X"FF" after 640 fs; write\_l <= '1', '0' after 130 fs, '1' after 160 fs, '0' after 230 fs, '1' after 260 fs, 0' after 330 fs, '1' after 360 fs, '0' after 330 fs, '1' after 360 fs, '0' after 430 fs, '1' after 460 fs, '0' after 530 fs, '1' after 560 fs, '0' after 630 fs, '1' after 660 fs; read\_l  $\leq$  '1'; -- PARITY SIGNAL parity  $\langle = '0'$  after 505 fs, '1' after 540 fs, -- incorrect address parity correct data parity '0' after 605 fs, '1' after 640 fs; wait; end process GENERATE\_SIGNALS;

Figure 10. Stimulus File for Example 2.

#### SIMULATION RESULTS FROM EXAMPLE 2

SMON9 CE ACTIVE /DRACO/ERROR\_L SMON8 CE ACTIVE /DRACO/MSB\_BUF SMON7 CE ACTIVE /DRACO/LSB\_BUF SMON6 CE ACTIVE /DRACO/DATA\_BUS CE ACTIVE /DRACO/MSB\_IO\_BUS CE ACTIVE /DRACO/LSB\_IO\_BUS CE ACTIVE /DRACO/CYCLE SMON5 SMON4 SMON3 CE ACTIVE /DRACO/EKEY\_POS SMON2 SMON1 CE ACTIVE /DRACO/ADD\_DATA\_BUS SMON CE ACTIVE /DRACO/EKEY\_MODE 25 FS ACTIVE /DRACO/CYCLE (value = RESET) SMON3: ACTIVE /DRACO/EKEY\_MODE (value = OFF) ACTIVE /DRACO/EKEY\_POS (value = LOCKED) ACTIVE /DRACO/EKEY\_MODE (value = OFF) SMON: SMON2: SMON: ACTIVE /DRACO/EKEY\_POS (value = LOCKÉD) SMON2: 50 FS SMON3: ACTIVE /DRACO/CYCLE (value = CHIP\_ENABLED) 105 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"80") 110 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 130 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 140 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") 170 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 205 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"7F") 210 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 230 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 240 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") SMON1: 260 FS SMON: ACTIVE /DRACO/EKEY\_MODE (value = ONN) 270 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 305 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"7F") 310 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 330 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 340 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") 360 FS SMON2: ACTIVE /DRACO/EKEY\_POS (value = CONFIG\_UNLOCKED) 370 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 405 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X''02'') 410 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 430 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 440 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"06") 470 FS

| SMON3:           | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)        |

|------------------|--------------------------------------------------|

| 505 FS           |                                                  |

| SMON1:           | ACTIVE $/DRACO/ADD_DATA_BUS$ (value = X"7F")     |

| 510 FS           |                                                  |

| SMON3:           | ACTIVE $/DRACO/CYCLE$ (value = ADDRESS)          |

| 530 FS           |                                                  |

| SMON3:           | ACTIVE /DRACO/CYCLE (value = WRITE)              |

| 540 FS           |                                                  |

| SMON1:<br>560 FS | ACTIVE $/DRACO/ADD_DATA_BUS$ (value = X"55")     |

| SMON2:           | ACTIVE /DRACO/EKEY_POS (value = DATA_UNLOCKED)   |

| 570 FS           | $ACHVE / DARCO/EREI_FOS (value = DATA_ONLOCKED)$ |

| SMON3:           | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)        |

| 605 FS           | ROITVE / DIROO/OTOLE (Value = IDLE)              |

| SMON1:           | ACTIVE /DRACO/ADD_DATA_BUS (value = X"00")       |

| 610 FS           | KOIIVE / DIACO/ADD_DAIA_DOD (Valle = X 00 )      |

|                  | ACTIVE /DRACO/CYCLE (value = ADDRESS)            |

| Assertion W      | ARNING in BEHAVIOURAL: "ERROR 12"                |

| SMON9:           | ACTIVE /DRACO/ERROR_L (value = '0')              |

| 630 FS           |                                                  |

| Assertion W      | ARNING in BEHAVIOURAL: "ERROR 8"                 |

| 640 FS           |                                                  |

| SMON1:           | ACTIVE /DRACO/ADD_DATA_BUS (value = X"FF")       |

| 670 FS           |                                                  |

| SMON3:           | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)        |

| 1910 FS          |                                                  |

| SMON3:           | ACTIVE $/DRACO/CYCLE$ (value = CHIP_DISABLE)     |

| 1920 FS          |                                                  |

| SMON3:           | ACTIVE /DRACO/CYCLE (value = POWER_OFF)          |

| 2000 FS          |                                                  |

# Figure 11. Tabular Results For Example 2.

The tabular results for this simulation are shown in Figure 13.

# 5.4. Example 4

In this example both the address and data parity bits are received correctly in the last

cycle.

The stimulus file for this example is shown in Figure 14.

The results are shown in Figure 15.

Note that in this example the data does get written to the I/O bus of the DRACO chip correctly.

June 19, 1990

Modeling DRACO

Page 30

#### STIMULUS FILE FOR EXAMPLE 3

-- 54 LINES GENERATE\_SIGNALS: process -- THIS PROCESS CONFIGURES DRACO TO ENABLE DATA AND ADDRESS -- PARITIES. IT THEREAFTER UNLOCKS DATA AND WRITES FF TO THE -- LSB I/O PORT. SINCE DATA PARITY IS FALSE IN THE -- LAST WRITE THE OPERATION IS UNSUCCESSFUL. begin -- THIS PROGRAMS -- POWER SIGNAL power  $\langle = '0',$ '1' after 25 fs, '0' after 1920 fs; -- CHIP ENABLE SIGNAL  $ce_{-} <= '1',$ '0' after 50 fs, '1' after 1910 fs; ale <= '1', '0' after 110 fs, '1' after 170 fs, '0' after 210 fs, '1' after 270 fs, 0' after 310 fs, '1' after 370 fs, '0' after 410 fs, '1' after 370 fs, '0' after 410 fs, '1' after 470 fs, '0' after 510 fs, '1' after 570 fs, '0' after 610 fs, '1' after 670 fs;  $add_data_bus <= X"80"$  after 105 fs, Dus  $\leq = X$  so after 1 X"AA" after 140 fs, X"7F" after 205 fs, X"55" after 240 fs, X"7F" after 305 fs, X"AA" after 340 fs, X"02" after 405 fs, X"06" after 440 fs, X"7F" after 505 fs, X"55" after 540 fs, X"00" after 605 fs, X"FF" after 640 fs; write\_l <= '1', '0' after 130 fs, '1' after 160 fs, '0' after 230 fs, '1' after 260 fs, 0' after 330 fs, '1' after 360 fs, '0' after 430 fs, '1' after 460 fs, '0' after 530 fs, '1' after 560 fs, '0' after 630 fs, '1' after 660 fs; read  $\bot$  <= '1'; -- PARITY SIGNAL parity  $\langle = '0'$  after 505 fs, '1' after 540 fs, - correct address parity incorrect data parity '1' after 605 fs,

end process GENERATE\_SIGNALS;

'0' after 640 fs;

Figure 12. Stimulus File for Example 3.

June 19, 1990

wait;

## SIMULATION RESULTS FROM EXAMPLE 3

SMON9 CE ACTIVE /DRACO/ERROR\_L SMON8 CE ACTIVE /DRACO/MSB\_BUF SMON7 CE ACTIVE /DRACO/LSB\_BUF CE ACTIVE /DRACO/DATA\_BUS SMON6 CE ACTIVE /DRACO/MSB\_IO\_BUS SMON5 CE ACTIVE /DRACO/LSB\_IO\_BUS SMON4 CE ACTIVE /DRACO/CYCLE CE ACTIVE /DRACO/EKEY\_POS SMON3 SMON2 CE ACTIVE /DRACO/ADD\_DATA\_BUS SMON1 SMON CE ACTIVE /DRACO/EKEY\_MODE 25 FS SMON3: ACTIVE /DRACO/CYCLE (value = RESET) ACTIVE /DRACO/EKEY\_MODE (value = OFF) ACTIVE /DRACO/EKEY\_POS (value = LOCKED) ACTIVE /DRACO/EKEY\_MODE (value = OFF) SMON: SMON2: SMON: SMON2: ACTIVE /DRACO/EKEY\_POS (value = LOCKÉD) 50 FS SMON3: ACTIVE /DRACO/CYCLE (value = CHIP\_ENABLED) 105 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"80") 110 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 130 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 140 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") 170 FS ACTIVE /DRACO/CYCLE (value = IDLE) SMON3: 205 FS SMON1: ACTIVE  $/DRACO/ADD_DATA_BUS$  (value = X"7F") 210 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 230 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 240 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") 260 FS SMON: ACTIVE /DRACO/EKEY\_MODE (value = ONN) 270 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 305 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value =  $X^{"7}F"$ ) 310 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 330 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 340 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") SMON1: 360 FS SMON2: ACTIVE /DRACO/EKEY\_POS (value = CONFIG\_UNLOCKED) 370 FS ACTIVE /DRACO/CYCLE (value = IDLE) SMON3: 405 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"02") 410 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 430 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 440 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"06") 470 FS

June 19, 1990

## Modeling DRACO

Page 32

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)         |

|---------|---------------------------------------------------|

| 505 FS  |                                                   |

| SMON1:  | ACTIVE /DRACO/ADD_DATA_BUS (value = $X^{"7}F"$ )  |

| 510 FS  |                                                   |

| SMON3:  | ACTIVE / DRACO/CYCLE (value = ADDRESS)            |

| 530 FS  |                                                   |

| SMON3:  | ACTIVE / DRACO/CYCLE (value = WRITE)              |

| 540 FS  |                                                   |

| SMON1:  | ACTIVE /DRACO/ADD_DATA_BUS (value = $X^{"55}$ ")  |

| 560 FS  |                                                   |

| SMON2:  | ACTIVE /DRACO/EKEY_POS (value = DATA_UNLOCKED)    |

| 570 FS  |                                                   |

| SMON3:  | ACTIVE / DRACO/CYCLE (value = IDLE)               |

| 605 FS  |                                                   |

| SMON1:  | ACTIVE /DRACO/ADD_DATA_BUS (value = X"00")        |

| 610 FS  |                                                   |

| SMON3:  | ACTIVE / DRACO/CYCLE (value = ADDRESS)            |

| 630 FS  |                                                   |

| SMON3:  | ACTIVE $/$ DRACO/CYCLE (value = WRITE)            |

| 640 FS  |                                                   |

| SMON1:  | ACTIVE $/$ DRACO $/$ ADD_DATA_BUS (value = X"FF") |

| 660 FS  | ADVING & DEVIAUTODAL BODODA                       |

|         | ARNING in BEHAVIORAL: "ERROR 14"                  |

| SMON9:  | ACTIVE $/$ DRACO/ERROR_L (value = '0')            |

| 670 FS  |                                                   |

| SMON3:  | ACTIVE / DRACO/CYCLE (value = IDLE)               |

| 1910 FS |                                                   |

| SMON3:  | $ACTIVE / DRACO/CYCLE (value = CHIP_DISABLE)$     |

| 1920 FS |                                                   |

| SMON3:  | ACTIVE /DRACO/CYCLE (value = POWER_OFF)           |

| 2000 FS |                                                   |

# Figure 13. Tabular Results For Example 3.

### 5.5. Example 5

In this example DRACO is configured so as to enable data and address parities as well as the checksum mode. Power is switched on, the chip is enabled and configured. Thereafter, the data is unlocked and data is written to the I/O ports. The data gets loaded into the buffers since checksum is enabled. A checksum byte is written, subsequently. A checksum of the msb and lsb bytes stored in the buffers is internally generated and compared with the checksum obtained from the host. A generated checksum which tallies with the checksum written by the host causes the data stored in the buffers to be transfferred to the I/O ports. Finally, the checksum of the low and high bytes of the data stored in the buffers is read from DRACO.

June 19, 1990

#### **STIMULUS FILE FOR EXAMPLE 4**

-- 58 LINES GENERATE\_SIGNALS: process begin -- THIS PROCESS CONFIGURES DRACO TO ENABLE DATA AND ADDRESS -- PARITIES. IT THEREAFTER UNLOCKS DATA AND WRITES FF TO THE -- LSB I/O PORT. -- POWER SIGNAL power  $\langle = '0',$ '1' after 25 fs, '0' after 1920 fs; -- CHIP ENABLE SIGNAL  $ce_{-} < = '1',$ '0' after 50 fs, '1' after 1910 fs; ale <= '1', '0' after 110 fs, '1' after 170 fs, 1, 0 after 110 is, 1 after 270 fs, '0' after 210 fs, '1' after 270 fs, '0' after 310 fs, '1' after 370 fs, '0' after 410 fs, '1' after 470 fs, '0' after 510 fs, '1' after 570 fs, '0' after 610 fs, '1' after 670 fs;  $add_data_bus <= X"80"$  after 105 fs, Dus  $\leq = X \, 80$  atter 1 X"AA" after 140 fs, X"7F" after 205 fs, X"55" after 240 fs, X"7F" after 305 fs, X"AA" after 340 fs, X"02" after 405 fs, X"06" after 440 fs, X"7F" after 505 fs, X "55" after 540 fs, X"00" after 605 fs, X"FF" after 640 fs; write\_l <= '1', '0' after 130 fs, '1' after 160 fs, '0' after 230 fs, '1' after 260 fs, '0' after 330 fs, '1' after 360 fs, <sup>0</sup> after 430 fs, '1' after 460 fs, '0' after 530 fs, '1' after 560 fs, '0' after 630 fs, '1' after 660 fs; read\_l  $\leq$  '1'; -- PARITY SIGNAL parity <= '0' after 505 fs, '1' after 540 fs, -- correct address parity correct data parity '1' after 605 fs, '1' after 640 fs;

wait:

end process GENERATE\_SIGNALS;

Figure 14. Stimulus File for Example 4.

#### SIMULATION RESULTS FROM EXAMPLE 4

SMON9 CE ACTIVE /DRACO/ERROR\_L SMON8 CE ACTIVE /DRACO/MSB\_BUF CE ACTIVE /DRACO/LSB\_BUF CE ACTIVE /DRACO/DATA\_BUS CE ACTIVE /DRACO/MSB\_IO\_BUS SMON7 SMON6 SMON5 SMON4 CE ACTIVE /DRACO/LSB\_IO\_BUS SMON3 CE ACTIVE /DRACO/CYCLE CE ACTIVE /DRACO/EKEY\_POS SMON2 SMON1 CE ACTIVE /DRACO/ADD\_DATA\_BUS CE ACTIVE /DRACO/EKEY\_MODE SMON 25 FS SMON3: ACTIVE /DRACO/CYCLE (value = RESET) ACTIVE  $/DRACO/EKEY_MODE$  (value = OFF) SMON: ACTIVE  $/DRACO/EKEY_POS$  (value = LOCKÉD) SMON2: SMON: ACTIVE  $/DRACO/EKEY_MODE$  (value = OFF) SMON2: ACTIVE  $/DRACO/EKEY_POS$  (value = LOCKED) 50 FS SMON3: ACTIVE /DRACO/CYCLE (value = CHIP\_ENABLED) 105 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"80") 110 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 130 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 140 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") 170 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 205 FS SMON1: ACTIVE  $/DRACO/ADD_DATA_BUS$  (value = X"7F") 210 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 230 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 240 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") 260 FS SMON: ACTIVE  $/DRACO/EKEY\_MODE$  (value = ONN) 270 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 305 FS SMON1: ACTIVE  $/DRACO/ADD_DATA_BUS$  (value = X"7F") 310 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 330 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 340 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") SMON1: 360 FS ACTIVE /DRACO/EKEY\_POS (value = CONFIG\_UNLOCKED) SMON2: 370 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 405 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"02") SMON1: 410 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 430 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 440 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"06") SMON1: 470 FS

| 505 FS<br>SMON1: ACTIVE /DRACO/ADD_DATA_BUS (value = X"7F")<br>510 FS |    |

|-----------------------------------------------------------------------|----|

|                                                                       |    |

|                                                                       |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS)                          |    |

| 530  FS                                                               |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = WRITE)                            |    |

| 540 FS                                                                |    |

| SMON1: ACTIVE /DRACO/ADD_DATA_BUS (value = X"55")                     |    |

| 560 FS                                                                |    |

| SMON2: ACTIVE /DRACO/EKEY_POS (value = DATA_UNLOCKEI                  | )) |

| 570 FS                                                                |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = IDLE)                             |    |

| 605 FS<br>SMON1: ACTIVE /DBACO/ADD DATA BUS (value = X"00")           |    |

| SMON1: ACTIVE /DRACO/ADD_DATA_BUS (value = X"00")<br>610 FS           |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS)                          |    |

| 630  FS                                                               |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = WRITE)                            |    |

| 640 FS                                                                |    |

| SMON1: ACTIVE /DRACO/ADD_DATA_BUS (value = X"FF")                     |    |

| 660 FS                                                                |    |

| SMON4: ACTIVE /DRACO/LSB_IO_BUS (value = X"FF")                       |    |

| SMON: ACTIVE $DRACO/EKEY_MODE$ (value = OFF)                          |    |

| 670 FS<br>SMON3: ACTIVE /DBACO/CYCLE (value = IDLE)                   |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = IDLE)<br>1910 FS                  |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = CHIP_DISABLE)                     |    |

| 1920 FS                                                               |    |

| SMON3: ACTIVE /DRACO/CYCLE (value = POWER_OFF)                        |    |

| 2000 FS                                                               |    |

# Figure 15. Tabular Results For Example 4.

The stimulus file for this example is shown in Figure 16.

The tabular results obtained as a result of simulation are shown in Figure 17.

## SIMULATION RESULTS FROM EXAMPLE 5

| SMON9  |                                              |

|--------|----------------------------------------------|

|        | CE ACTIVE /DRACO/ERROR_L                     |

| SMON8  | CE ACTIVE /DRACO/MSB_BUF                     |

| SMON7  | CE ACTIVE /DRACO/LSB_BUF                     |

| SMON6  | CE ACTIVE /DRACO/DATA_BUS                    |

| SMON5  | CE ACTIVE /DRACO/MSB_IO_BUS                  |

| SMON4  | CE ACTIVE /DRACO/LSB_IO_BUS                  |

| SMON3  | CE ACTIVE /DRACO/CYCLE                       |

| SMON2  | CE ACTIVE /DRACO/EKEY_POS                    |

| SMON1  | CE ACTIVE /DRACO/ADD_DATA_BUS                |

| SMON   | CE ACTIVE /DRACO/EKEY_MODE                   |

| 25 FS  |                                              |

| SMON3: | ACTIVE $/$ DRACO $/$ CYCLE (value = RESET)   |

| SMON:  | ACTIVE $DRACO/EKEY_MODE$ (value = $OFF$ )    |

| SMON2: | $ACTIVE / DRACO / EKEY_POS (value = LOCKED)$ |

| SMON:  | ACTIVE $DRACO/EKEY_MODE$ (value = OFF)       |

| SMON2: | ACTIVE /DRACO/EKEY_POS (value = LOCKÉD)      |

Modeling DRACO

Page 36

#### **STIMULUS FILE FOR EXAMPLE 5**

-- 85 LINES GENERATE\_SIGNALS: process begin

-- This example configures DRACO to enable data parity

-- address parity and checksum. The key is in unlock config

-- positions while configuring. Thereafter the data is

-- unlocked and data is written to the lsb and msb I/O

-- ports. Subsequently, checksum is written to and read from

-- DRACO. A successful write of checksum writes data onto

-- the I/O ports.

-- POWER SIGNAL power <= '0', '1' after 25 fs, '0' after 1920 fs;

ية من من يون

-- CHIP ENABLE SIGNAL ce\_l <= '1',

'0' after 50 fs,

'1' after 1910 fs;

ale <= '1', '0' after 110 fs, '1' after 170 fs, '0' after 210 fs, '1' after 270 fs, '0' after 310 fs, '1' after 370 fs, '0' after 410 fs, '1' after 470 fs, '0' after 510 fs, '1' after 570 fs, '0' after 610 fs, '1' after 670 fs, '0' after 710 fs, '1' after 770 fs, '0' after 810 fs, '1' after 870 fs, '0' after 910 fs, '1' after 970 fs;

add\_data\_bus <= X"80" after 105 fs, X"AA" after 140 fs, X"7F" after 205 fs, X"55" after 240 fs, X "7F" after 305 fs, X"AA" after 340 fs, X "02" after 405 fs, X "07" after 440 fs, -- unlock data X"7F" after 505 fs, X"55" after 540 fs, -- write into the lsb buf X"00" after 605 fs, X "08" after 640 fs, -- write into the msb\_buf X"01" after 705 fs, X"04" after 740 fs, -- write inverted checksum X"0E" after 805 fs, X"F3" after 840 fs, -- read checksum X"0E" after 905 fs;

write\_l <= '1', '0' after 130 fs, '1' after 160 fs, '0' after 230 fs, '1' after 260 fs,

```

'0' after 330 fs, '1' after 360 fs,

'0' after 430 fs, '1' after 460 fs,

'0' after 530 fs, '1' after 560 fs,

'0' after 630 fs, '1' after 660 fs,

'0' after 730 fs, '1' after 760 fs,

'0' after 830 fs, '1' after 860 fs;

read_l <= '1',

'0' after 930 fs;

-- PARITY SIGNAL

parity \leq = '0' after 505 fs.

'1' after 540 fs

'1' after 605 fs,

'0' after 640 fs,

'0' after 705 fs,

'0' after 740 fs.

'0' after 805 fs,

'1' after 840 fs.

'0' after 905 fs;

```

wait:

```

end process GENERATE_SIGNALS;

```

#### Figure 16. Stimulus File for Example 5.

50 FS ACTIVE /DRACO/CYCLE (value = CHIP\_ENABLED) SMON3: 105 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"80") 110 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 130 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 140 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") SMON1: 170 FS ACTIVE /DRACO/CYCLE (value = IDLE) SMON3: 205 FS SMON1: ACTIVE  $/DRACO/ADD_DATA_BUS$  (value = X"7F") 210 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 230 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 240 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") SMON1: 260 FS ACTIVE /DRACO/EKEY\_MODE (value = ONN) SMON: 270 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 305 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"7F") 310 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 330 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 340 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"AA") 360 FS ACTIVE /DRACO/EKEY\_POS (value = CONFIG\_UNLOCKED) SMON2: 370 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 405 FS

SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X''02'') 410 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 430 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 440 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"07") 470 FS ACTIVE /DRACO/CYCLE (value = IDLE) SMON3: 505 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"7F") SMON1: 510 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 530 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 540 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"55") 560 FS ACTIVE /DRACO/EKEY\_POS (value = DATA\_UNLOCKED) SMON2: 570 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 605 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"00") 610 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 630 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 640 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"08") SMON1: 660 FS SMON7: ACTIVE  $/DRACO/LSB_BUF$  (value = X"08") SMON: ACTIVE  $/DRACO/EKEY\_MODE$  (value = OFF) 670 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 705 FS SMON1: ACTIVE  $/DRACO/ADD_DATA_BUS$  (value = X"01") 710 FS ACTIVE /DRACO/CYCLE (value = ADDRESS) SMON3: 730 FS SMON3: ACTIVE /DRACO/CYCLE (value = WRITE) 740 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X''04'') SMON1: 760 FS SMON8: ACTIVE  $/DRACO/MSB_BUF$  (value = X"04") ACTIVE /DRACO/EKEY\_MODE (value = OFF) SMON: 770 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 805 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"0E") 810 FS SMON3: ACTIVE /DRACO/CYCLE (value = ADDRESS) 830 FS ACTIVE /DRACO/CYCLE (value = WRITE) SMON3: 840 FS SMON1: ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"F3") 860 FS ACTIVE /DRACO/MSB\_IO\_BUS (value = X"04") SMON5: ACTIVE /DRACO/LSB\_IO\_BUS (value = X"08") SMON4: ACTIVE  $DRACO/EKEY_MODE$  (value = OFF) SMON: 870 FS SMON3: ACTIVE /DRACO/CYCLE (value = IDLE) 905 FS ACTIVE /DRACO/ADD\_DATA\_BUS (value = X"0E") SMON1:

June 19, 1990

## Modeling DRACO

- ----

| 910 FS  |                                                |

|---------|------------------------------------------------|

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = ADDRESS)   |

| 930 FS  |                                                |

| SMON3:  | ACTIVE / DRACO / CYCLE (value = READ)          |

| 950 FS  |                                                |

| SMON6:  | ACTIVE $/$ DRACO $/$ DATA_BUS (value = X"F3")  |

| 970 FS  |                                                |

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = IDLE)      |

| 1910 FS |                                                |

| SMON3:  | ACTIVE /DRACO/CYCLE (value = CHIP_DISABLE)     |

| 1920 FS |                                                |

| SMON3:  | ACTIVE $/$ DRACO $/$ CYCLE (value = POWER_OFF) |

| 2000 FS |                                                |

|         |                                                |

#### Figure 17. Tabular Results For Example 5.

### 6. Acknowledgements

Bob Larsen provided useful input and comments on an earlier draft of this paper. Sanjiv Narayan and Frank Vahid helped to refine an initial behavioral model of DRACO, and also suggested some stylistic improvements to the VHDL code used to model the DRACO chip. Dan Gajski and Bob Larsen acted as catalysts in this industry-university effort. The authors would like to thank all of these people.

# 7. Summary

This report described the behavioral model of a commercial chip design named DRACO from Rockwell International, which was initially documented with only a data sheet and associated logic schematics. The behavioral model was developed using flowcharts and pseudo-code. A set of five typical operational test cases was also developed. Subsequently, these flowcharts and test scenarios were described using behavioral VHDL and associated stimulus files. The VHDL code was tested on two commercial simulators (Vantage and Zycad) to verify the correctness of the behavior with respect to the operational test cases. The behavioral flowcharts, VHDL behavioral code, the stimulus files and

results of the simulation runs are all included in this report.

Future work will attempt to use this DRACO behavioral description as input to a suite of behavioral, logic and layout synthesis tools at U.C. Irvine.

## 8. References

- [IEEE90] The IEEE Institute, "Save U.S. semiconductor industry now or lose technical edge, Bush told," Volume 14, Number 1, January 1990.

- [Lars90] Robert P. Larsen, Rockwell International, private communication, April 1990.

- [Pase90] Dave Pasela, Rockwell International, private communication, May 1990.

- [Sumn89] Larry W. Sumney, "Workstations, Semiconductors, and Competitiveness," Keynote Address at the First IEEE Workstations Symposium,, Baltimore, MD, Oct. 1989.

- [VHDL87] IEEE Standard VHDL Language Reference Manual, IEEE, 1987.

- [Vant89] Vantage Analysis Systems, Inc, Fremont, CA 1989.

- [Zyca89] Zycad Corporation, Menlo Park, CA 1989.

# APPENDIX A.

# Rockwell DRACO Data Sheet

| PREPARED BY                                                                                                                                                                      |                                                                     | NUMBER            |              |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------|--------------|--|--|

| Johnny Sitou                                                                                                                                                                     | Rockwell International                                              |                   | 1495         |  |  |

| APPROVALS                                                                                                                                                                        |                                                                     | TYPE              |              |  |  |

| AFFROVALS                                                                                                                                                                        | 4                                                                   | PO1 Sp            | ecification  |  |  |

| Robert W. Polkinghorn                                                                                                                                                            | ROCKWELL INTERNATIONAL CORPORATION                                  | DATE              |              |  |  |

|                                                                                                                                                                                  | SEMICONDUCTOR PRODUCTS DIVISION                                     | November 20, 1989 |              |  |  |

|                                                                                                                                                                                  | FSCM NO. 34576                                                      | REV.LTR           |              |  |  |

|                                                                                                                                                                                  | PROPRIETARY INFORMATION OF<br>SEMICONDUCTOR PRODUCTS DIVISION       | NC                | PAGE 1 of 32 |  |  |

|                                                                                                                                                                                  | NO DISSEMINATION OR USE ALLOWED<br>WITHOUT PRIOR WRITTEN PERMISSION | TOTAL PAGES       | 32           |  |  |

| TITLE                                                                                                                                                                            |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

| EN                                                                                                                                                                               | GINEERING REPORT                                                    |                   |              |  |  |

| PRODUCT: Discrete                                                                                                                                                                | I/O Backplane ASIC (DRACO)                                          |                   |              |  |  |

| PART NUMBER 1149                                                                                                                                                                 | 5                                                                   |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

| SYNOPSIS: This document describes the custom integrated<br>circuit that interfaces 1781 single and quad<br>discrete I/O modules to Allen Bradley 1781<br>communication adapters. |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

|                                                                                                                                                                                  |                                                                     |                   |              |  |  |

ROCKWELL INTERNATIONAL PROPRIETARY INFORMATION

----

- ----

| NUMBER |  |

|--------|--|

11495 REV. NC

PAGE \_\_\_\_\_

.

2

| FSCM | NO. | 34576 |  |

|------|-----|-------|--|

|      |     |       |  |

|      |     |       |  |

. . . . . .

| 1. Overview                                             | 1      |

|---------------------------------------------------------|--------|

| 2. Applications                                         | 2      |

| 2.1 1781 Backplanes                                     | 2      |

| 2.2 1781 Adapter Interface                              | 2      |

| 2.3 I/O Modules                                         | 2      |

| 3. Functional Overview                                  | 2      |

| 3.1 EMI Precautions                                     | 3      |

| 3.2 User Configuration                                  | 3      |

|                                                         | 0      |

| 4. Functional Blocks                                    | 4      |

| 4.1 Address Decoding Block                              | 4      |

| 4.1.1 Invalid Address / Address Parity Error Indication | 5<br>5 |

| 4.1.2 Electronic Key                                    |        |

| 4.1.2.1 On/Off - Unlock/Lock Encoding                   | 6      |

| 4.2 Checksum / Parity / Error Block                     | 6      |

| 4.2.1 Configuration Register / Status Register          | 6      |

| 4.2.2 Checksum Generator / Comparator                   | 7      |

| 4.2.3 Data Parity Generator / Comparator                | 8      |

| 4.2.4 Error Register                                    | 8      |

| 4.3 I/O Block                                           | 9      |

| 4.3.1 Updating Outputs                                  | 9      |

| 4.3.2 I/O Direction Register                            | 9      |

| 5. User Interfaces                                      | 10     |

| 5.1 Bus Interface                                       | 10     |

| 5.1.1 Embedded Addresses                                | 10     |

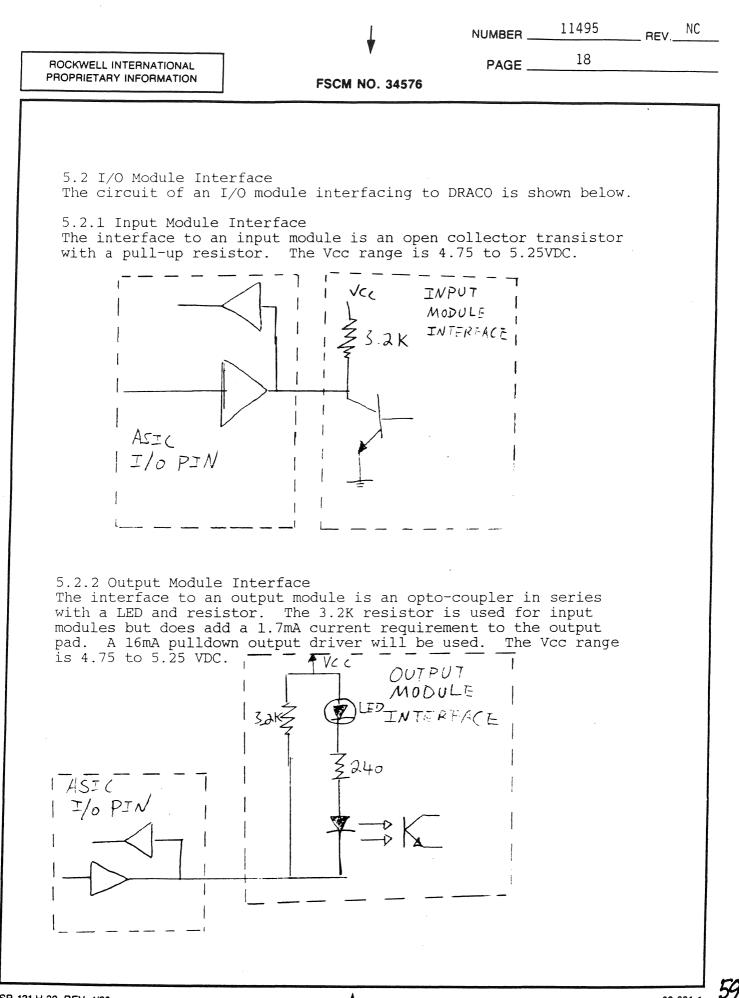

| 5.2 I/O Module Interface                                | 12     |

| 5.2.1 Input Module Interface                            | 12     |

| 5.2.2 Output Module Interface                           | 12     |

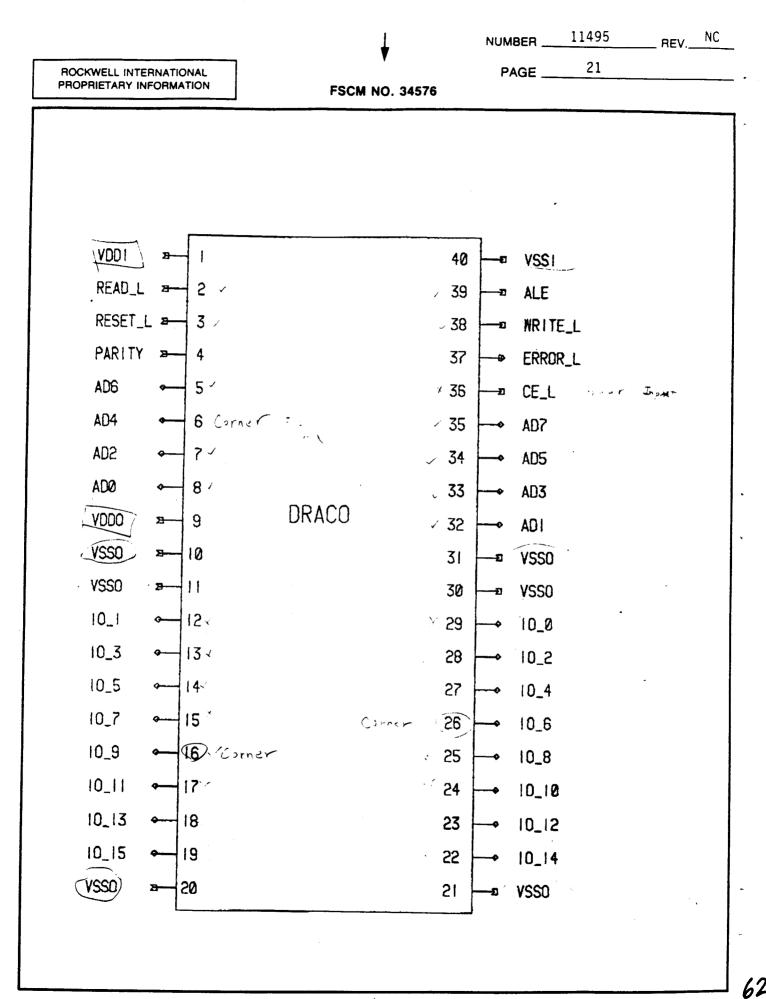

| 5.3 Pin Description                                     | 13     |

| 5.4 Timing Diagrams                                     | 14     |

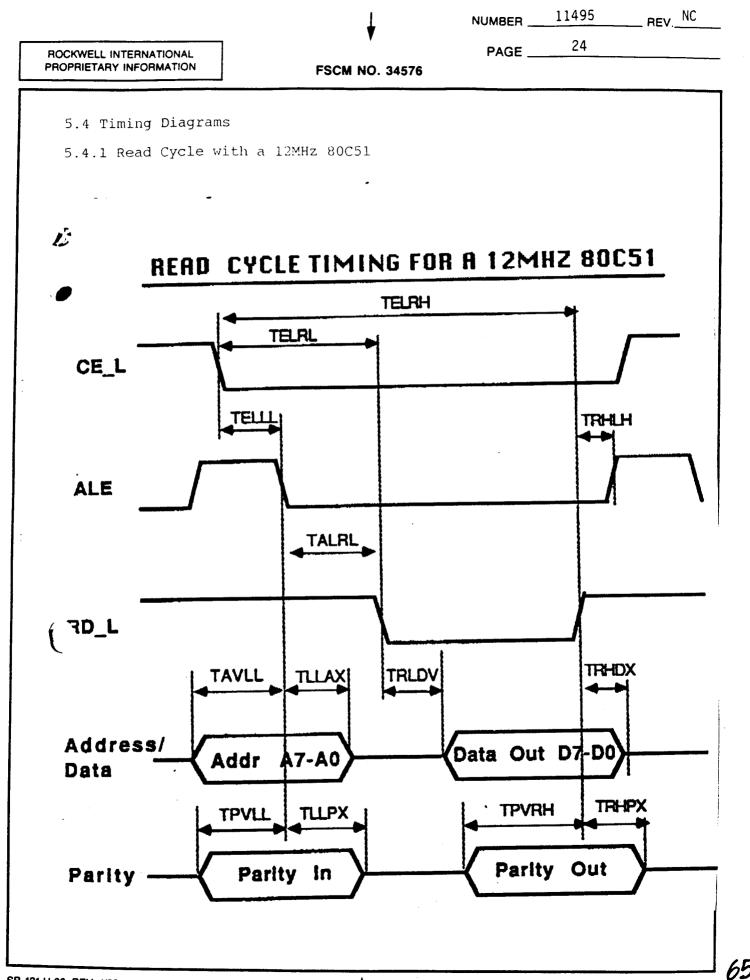

| 5.4.1 Read Cycle with a 12MHz 80C51                     | 14     |

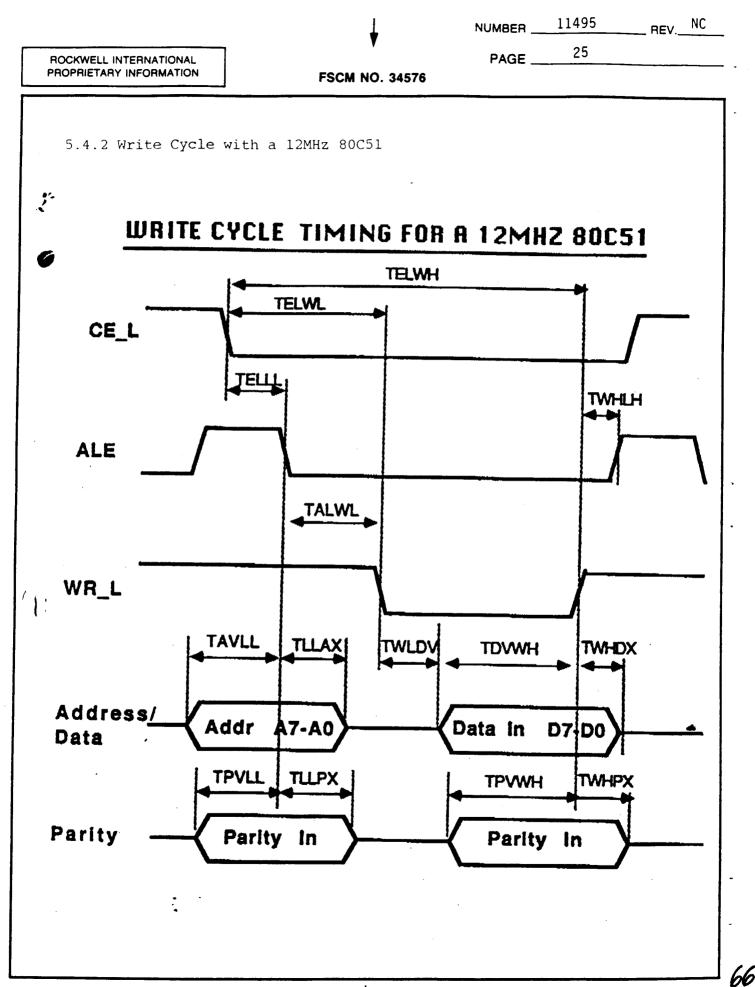

| 5.4.2 Write Cycle with a 12MHz 80C51                    | 15     |

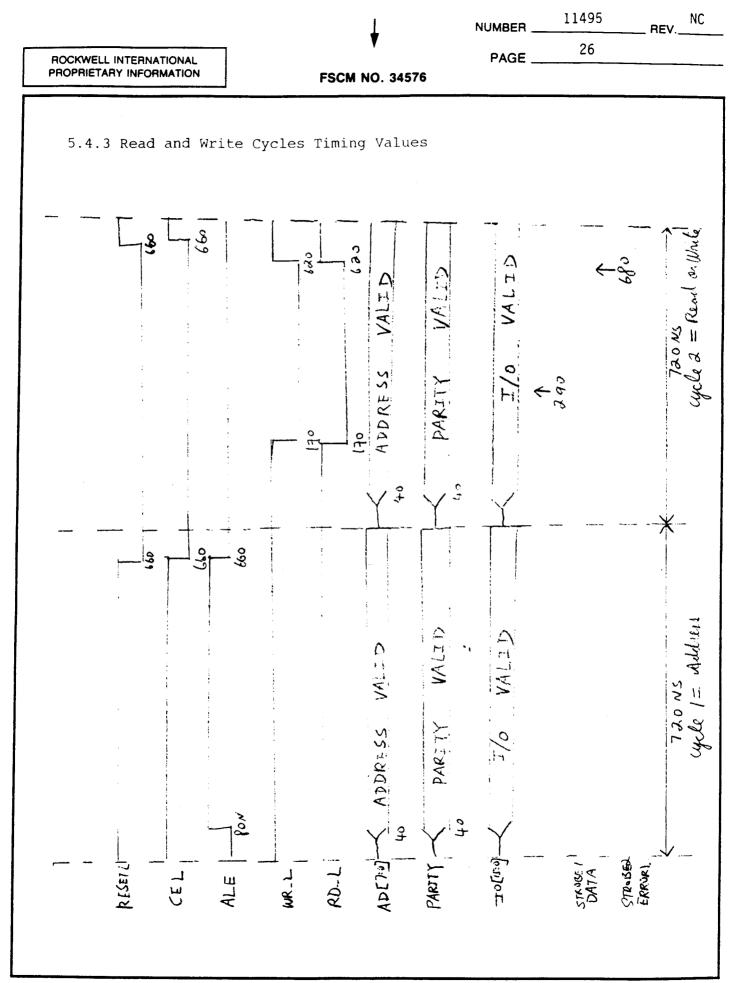

| 5.4.3 Read and Write Cycles Timing Values               | 16     |

| 5.4.4 Miscellaneous Timing Values                       | 17     |

|                                                         |        |

| 6. General Specifications                               | 17     |

| 6.1 Packaging                                           |        |

| 6.2 Electrical Specifications                           | 17     |

| 6.2.1 Absolute Maximum Specifications                   | 17     |

| 6.2.2 Recommended Operating Conditions                  | 17     |

| 7. Quality Assurance Requirements                       | 18     |

| 7.1 Device Markings                                     | 18     |

| 7.2 Solvent Resistance                                  | 18     |

| 7.3 Product Handling                                    | 18     |

| 7.4 Solderability                                       | 18     |

| 7.5 General Quality Assurance Provisions                | 18     |

| 7.6 Testability                                         | 18     |

|                                                         |        |

**•**

\_\_\_\_\_

-----

---- --

2

43

|                         | Ţ              | NUMBER |                                                 | REV                                  | NC |

|-------------------------|----------------|--------|-------------------------------------------------|--------------------------------------|----|

| ROCKWELL INTERNATIONAL  | <b>v</b>       | PAGE   | 3                                               |                                      |    |

| PROPRIETARY INFORMATION | FSCM NO. 34576 |        | ana ng salatan kana pan kumatan kana Dala da 19 | idani <del>n a</del> nya ana ana ang |    |

|                         |                |        |                                                 |                                      |    |

| 8. Future Applicat      | ions           |        |                                                 | 19                                   |    |

| FIGURE 1 - DRACO B      | LOCK DIAGRAM   | •••••  |                                                 | 20                                   |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         | ÷              |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

|                         |                |        |                                                 |                                      |    |

| ROCKWELL IN | TERNATIONAL |

|-------------|-------------|

| PROPRIETARY | INFORMATION |

PAGE

4

REV. NC

**FSCM NO. 34576**

1. Overview

This document defines the operation, performance characteristics and quality assurance requirements for the 1781 discrete I/O backplane custom integrated circuit (941425-61). The ASIC's codename is DRACO and will be referenced as so throughout this document.

In a general sense, DRACO is a general purpose peripheral interface device. The function of DRACO is to interface 16 I/O ports to a microprocessor's 8-bit multiplexed address/data bus and control signals. DRACO has several optional features that assists data integrity in the presence of EMI. DRACO contains a hardware key that must be unlocked by the user prior to operation which adds a level of security to its applications. The versatility of the interface will allow future 1781 adapters to interface to DRACO.

In particular, DRACO will interface de facto standard single and quad point discrete I/O modules (1781-xx5S and 1781-xx5Q) to 1781-Jxx remote discrete I/O adapters. Initially DRACO will be used with the 1781-JAD remote adapter, however, due to the generic bus interface, DRACO will accommodate future 1781 discrete I/Oadapters.

Features of DRACO:

- 16 bidirectional I/O ports with read/write byte integrity (16mA sink capacity)

- \* A checksum generator/comparator for output data.

- \* Odd parity generator/comparator for read and write addresses.

- Odd parity generator/comparator for write data.

- \*

- Odd parity generator for read data. Individual selection of parity error checking on address only \* or data only or both. Facilitates data parity generation in firmware.

- \* Checksum or Immediate modes for writing to output modules.

- \* Latched error output to indicate invalid address or parity or checksum error (reset by user).

- \* I/O direction register to set I/O ports as bidirectional or input-only.

- \* Electronic key for security and to prevent inadvertent writes to configuration and direction registers.

- \* Status register to read electronic key, error, and write acknowledge status.

- Standard 8051 8-bit bus interface with optional parity.

ROCKWELL INTERNATIONAL PROPRIETARY INFORMATION NUMBER \_

11495

5

REV. NC

PAGE \_\_\_\_

2. Applications

2.1 1781 Backplanes DRACO will be installed on all Allen Bradley 1781-ADxx discrete I/O backplanes. 1781 discrete I/O modules will coexist with the ASIC on the backplanes.

**FSCM NO. 34576**

DRACO will be installed on the following 1781 Discrete I/O backplanes: 1781-AD4 4 single point backplane 1 ASIC per backplane 1781-AD8 8 single point backplane 1 ASIC per backplane 1781-AD16 16 single point backplane 1 ASIC per backplane 1781-AD4Q 4 quad point backplane(16pt) 1 ASIC per backplane 1781-AD4Q 8 quad point backplane(32pt) 2 ASICs per backplane

For additional information on these backplanes, refer to DS#PC 4235

2.2 1781 Adapter Interface

Initially DRACO will be used in conjunction with the 1781-JAD Discrete I/O adapter. The adapter to DRACO interface is a buffered 80C51 address/data 8-bit bus plus parity and may be connected remotely through an 18-inch long ribbon cable. Provisions will be made within DRACO for the propagation delays due to the buffer circuitry and ribbon cable.

2.3 I/O Modules All Allen Bradley 1781-xx5S and 1781-xx5Q I/O modules will operate with DRACO.

Other manufacturers' single/quad modules are electrically compatible to operate with DRACO, however, the form factor of competitor's I/O modules will not allow non-1781 modules to reside in 1781-ADxx backplanes

#### 3. Functional Overview

DRACO provides an interface from an 8-bit multiplexed address/data bus with accompanying parity and control signals to sixteen I/O ports. Each of the 16 I/O ports can be connected to an Allen Bradley 1781 input or output module (or equivalent). DRACO will accommodate a maximum of 16 input OR 16 output points OR a combination thereof.

DRACO will operate as an I/O mapped device to the user's microcontroller. All data communications between DRACO and the microcontroller is performed with read and write instructions to embedded address locations within DRACO. DRACO provides an interrupt signal (ERROR\_L) to the host microcontroller to indicate an unsuccessful read or write instruction. The use of this interrupt pin is optional.

NUMBER \_\_\_\_\_11495

6

REV NC

FSCM NO. 34576

DRACO has two options for writing data to output modules; immediate and checksum. The immediate option only requires writing output data to either the high-byte or low-byte I/O address. Each output data byte immediately transfers to the I/O ports. The checksum option requires writing a checksum byte in addition to the output data before the I/O ports are updated. The data bytes are first buffered and validated with a checksum before updating the I/O ports. This option is controlled by the checksum enable bit in the configuration register.

Due to the bidirectional I/O module interface, the user has the ability to write to all and read from all of DRACO's 16 I/O ports. To prevent inadvertent writes to an input module, each port may optionally be configured as an input-only port. An I/O direction register can be loaded by the user to configure an I/O port as bidirectional or read-only.

## 3.1 EMI Precautions