## **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

### **Title**

Automated Testing, Verification and Repair of RTL Hardware Designs

### **Permalink**

https://escholarship.org/uc/item/0c3656n2

### **Author**

Laeufer, Kevin

### **Publication Date**

2024

Peer reviewed|Thesis/dissertation

## Automated Testing, Verification and Repair of RTL Hardware Designs

by

### Kevin Läufer

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Koushik Sen, Chair Assistant Professor Sarah E. Chasins Professor Borivoje Nikolić Associate Professor Adrian Sampson

Summer 2024

## Automated Testing, Verification and Repair of RTL Hardware Designs

Copyright 2024 by Kevin Läufer

#### Abstract

Automated Testing, Verification and Repair of RTL Hardware Designs

by

#### Kevin Läufer

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Koushik Sen, Chair

All modern marvels of computer technology are built on microchips – grains of sand turned into computational components. Over more than five decades, we have seen rapid progress in computing performance, primarily thanks to semiconductor technology improvements that lowered power consumption and raised clock speeds. Recently, progress has stalled, and general-purpose hardware can no longer keep up with rising computational demands. Specialized hardware is the only way. Low-volume specialization is often not profitable, though, because chips are too expensive to design. While modern software developers have access to tools that allow them to innovate rapidly, hardware design tools are difficult to access and use. For this thesis, I investigated how ideas from modern software engineering can be applied to the hardware design domain.

Inspired by work on software compilers, I developed a new approach for adding coverage feedback to hardware designs such that many different simulators can be targeted with minimal effort. I built the RFUZZ tool, which uses coverage feedback to generate new test inputs, taking inspiration from work on mutational fuzz testing for software. I added support for formal verification to the open-source ChiselTest library, focusing on accessibility for new users. Finally, I designed the RTL-REPAIR tool, which automatically generates plausible repairs from a buggy hardware description and a failing test case through a combination of formal methods and simulation.

All four projects illustrate how we can improve the state-of-the-art hardware testing, verification, and debugging tools by integrating with the open-source ecosystem and applying a compiler engineering mindset. This approach has allowed me to quickly build superior coverage feedback and formal verification infrastructure for the new Chisel hardware language. It has also enabled the first hardware fuzzer, RFUZZ, which spawned a new line of research on hardware fuzzing, and the RTL-REPAIR tool, which provides correct repairs within seconds, several orders of magnitude faster than prior work.

Für meine Großeltern.

# Contents

| Contents |                                        |                                                                                                                                                                                                                                    |                                  |  |

|----------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| Li       | st of                                  | Figures                                                                                                                                                                                                                            | iv                               |  |

| Li       | ${f st}$ of                            | Tables                                                                                                                                                                                                                             | vi                               |  |

| 1        | Intr                                   | roduction                                                                                                                                                                                                                          | 1                                |  |

| 2        | Bac                                    | kground                                                                                                                                                                                                                            | 6                                |  |

|          | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Register Transfer Level (RTL) Circuit Design  Hardware Description Languages  Hardware Construction Languages  RTL Intermediate Representations and Compilers  Simulation-based Testing of RTL Designs  Formal Verification of RTL | 6<br>10<br>12<br>14<br>16<br>21  |  |

| 3        | Sim                                    | ulator Independent Coverage                                                                                                                                                                                                        | 24                               |  |

|          | 3.1<br>3.2<br>3.3<br>3.4<br>3.5        | Simulator Independent Coverage Interface  Coverage Instrumentation and Report Generators  Evaluation  Limitations  Discussion                                                                                                      | 25<br>30<br>35<br>38<br>40       |  |

| 4        | Cov                                    | rerage-Directed Fuzz Testing of RTL on FPGAs                                                                                                                                                                                       | 41                               |  |

|          | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Coverage-Directed Mutational Fuzz Testing  Fuzz Testing of RTL Circuits  Implementation  Evaluation  Advanced Coverage Metrics as Fuzzing Feedback  Discussion                                                                     | 42<br>45<br>50<br>53<br>56<br>57 |  |

| 5        |                                        | en-Source Formal Verification for Chisel                                                                                                                                                                                           | 58                               |  |

|          | 5.1                                    | Our Formal Verification Flow                                                                                                                                                                                                       | 59                               |  |

|              | 5.2   | A Formal Backend for FIRRTL                    | 62  |

|--------------|-------|------------------------------------------------|-----|

|              | 5.3   | Reset Assumptions                              | 66  |

|              | 5.4   | Simple Temporal Assertions                     | 66  |

|              | 5.5   | Advantages over SymbiYosys for Chisel          | 67  |

|              | 5.6   | Discussion                                     | 68  |

| 6            | A S   | tudy on Random Testing and BMC for RTL Designs | 69  |

|              | 6.1   | Anatomy of Automated Bug Finding for RTL       | 69  |

|              | 6.2   | Coverage Based Fuzz Testing Evaluation         | 71  |

|              | 6.3   | OR1200 Processor Security Bugs                 | 74  |

|              | 6.4   | Deepbugs                                       | 75  |

|              | 6.5   | Discussion                                     | 79  |

| 7            | Fast  | Symbolic Repair of Hardware Design Code        | 81  |

|              | 7.1   | Repair Example                                 | 82  |

|              | 7.2   | The RTL-REPAIR Repair Algorithm                | 86  |

|              | 7.3   | Output / State Divergence Delta                | 93  |

|              | 7.4   | Evaluation                                     | 96  |

|              | 7.5   | Discussion                                     | 105 |

| 8            | Rela  | ated Work                                      | 106 |

|              | 8.1   | Coverage-Directed Fuzz Testing of RTL          | 106 |

|              | 8.2   | Automated Repair of Hardware Design Code       | 111 |

| 9            | Con   | nclusion                                       | 112 |

| Bi           | bliog | graphy                                         | 116 |

| $\mathbf{A}$ | Cha   | apter 5 Example Source Code                    | 129 |

# List of Figures

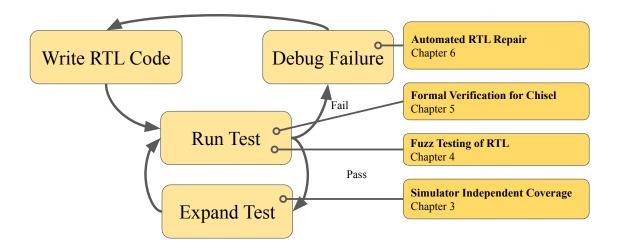

| 1.1               | The agile RTL hardware development flow                                                                                          | 3               |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.1<br>2.2<br>2.3 | Lowering a counter from a behavioral to a structural RTL description False paths when lowering from behavioral to structural RTL | 8<br>9<br>13    |

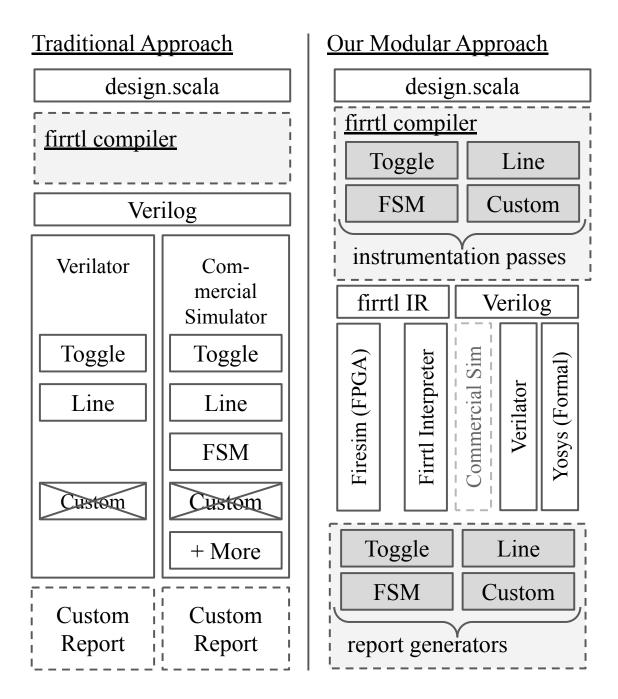

| 3.1               | Traditional vs. Modular Coverage Implementation                                                                                  | 26              |

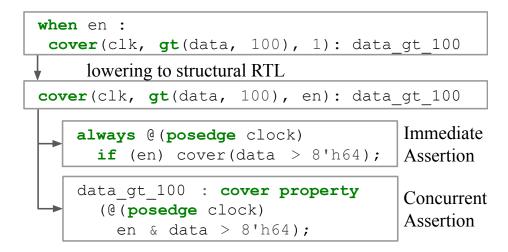

| 3.2               | Lowering the Cover Statement to SystemVerilog                                                                                    | 27              |

| 3.3               | Example of Misleading Line Coverage for the Generated Verilog                                                                    | 28              |

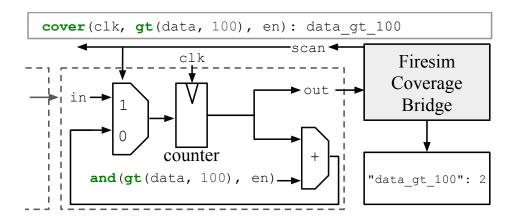

| 3.4               | Scan Chain Implementation for Cover Statement on FPGA                                                                            | 29              |

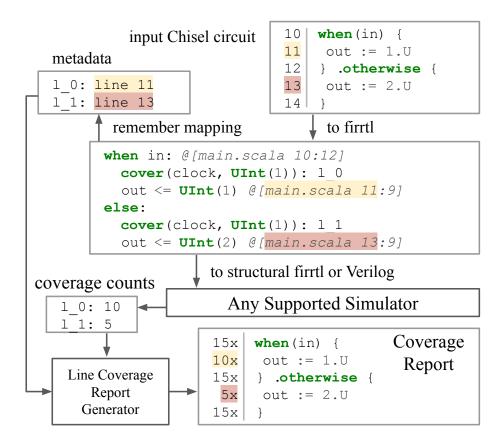

| 3.5               | Line Coverae Pass                                                                                                                | 31              |

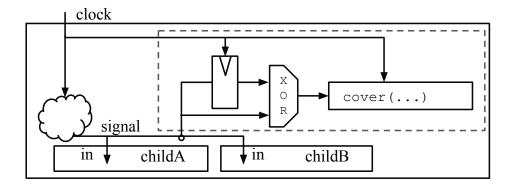

| 3.6               | Toggle Coverage Pas                                                                                                              | 32              |

| 3.7               | Finite State Machine Coverage Pass                                                                                               | 33              |

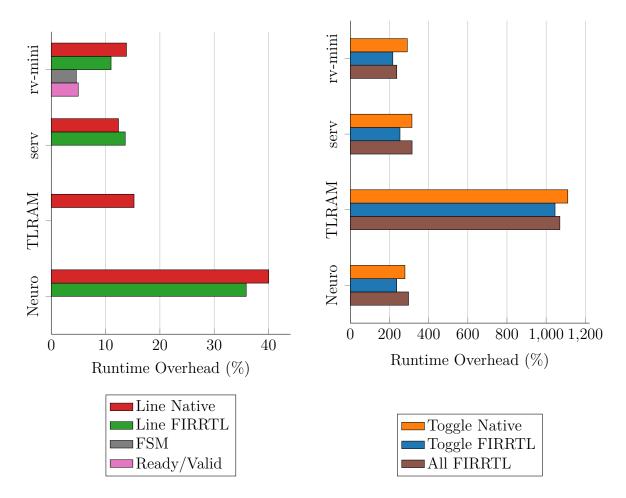

| 3.8               | Coverage Instrumentation Overhead for Verilator                                                                                  | 35              |

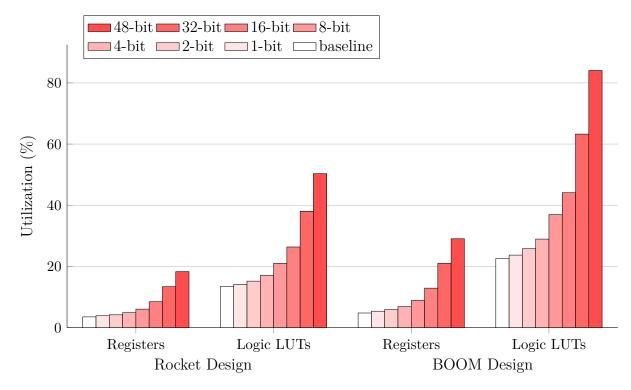

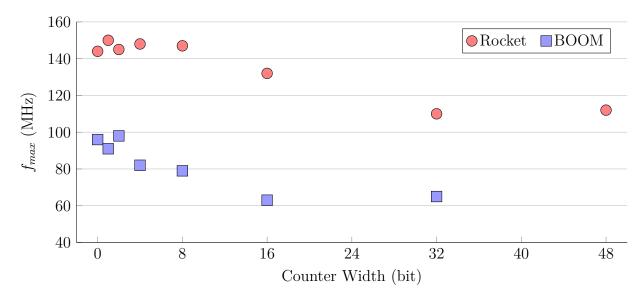

| 3.9               | FireSim simulator FPGA resource utilization versus counter width on two differ-                                                  | 0.7             |

| 2.10              | ent processor designs                                                                                                            | 37              |

| 3.10<br>3.11      | FireSim simulator $f_{max}$ versus counter width                                                                                 | $\frac{38}{39}$ |

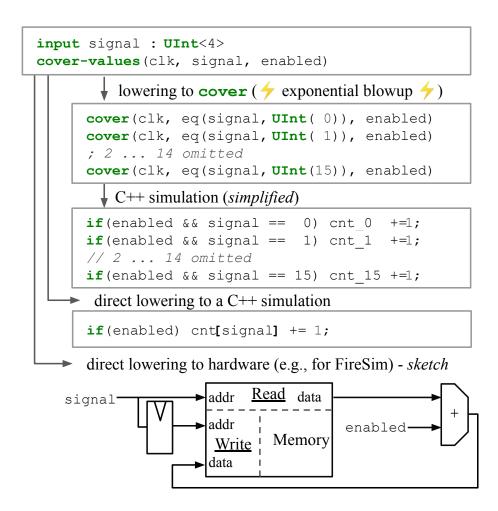

| 5.11              | Illustration of cover-values statement                                                                                           | 99              |

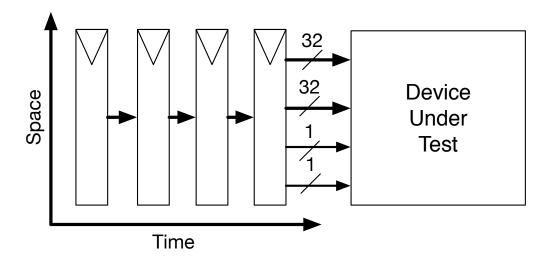

| 4.1               | Input definition.                                                                                                                | 44              |

| 4.2               | Meta reset transformation                                                                                                        | 47              |

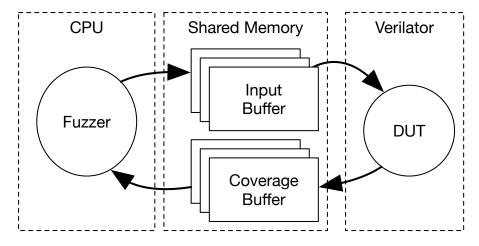

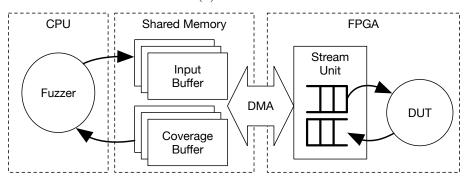

| 4.3               | Shared memory implementations for communication between the fuzzer and the                                                       |                 |

|                   | test harness                                                                                                                     | 51              |

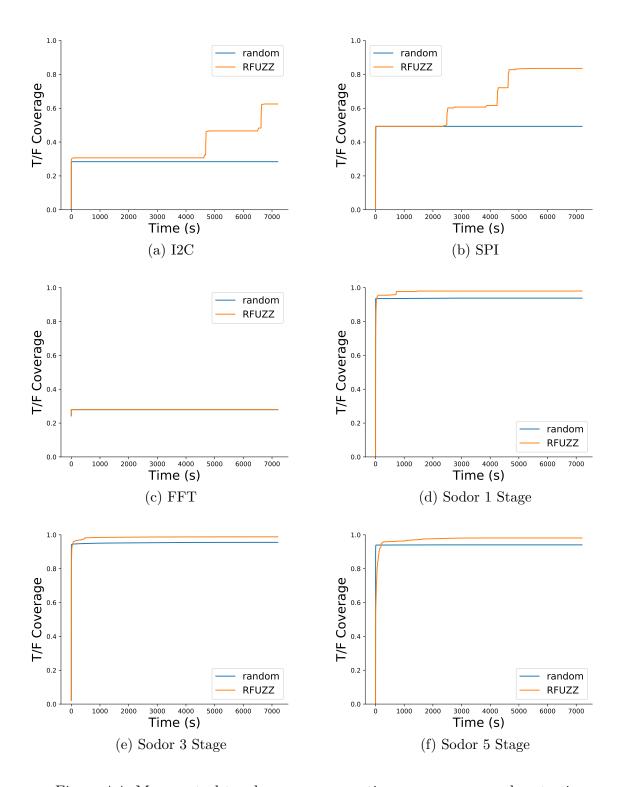

| 4.4               | Mux control toggle coverage over time: RFUZZ vs. random testing                                                                  | 55              |

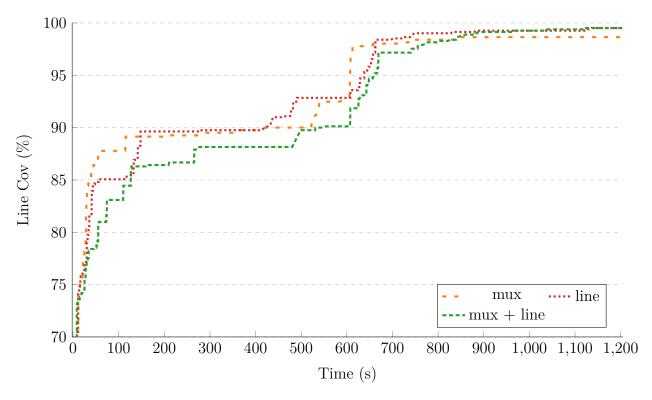

| 4.5               | Cumulative line coverage of inputs to the I2C peripheral discovered through                                                      |                 |

|                   | fuzzing with various feedback metrics. Averaged over five runs                                                                   | 57              |

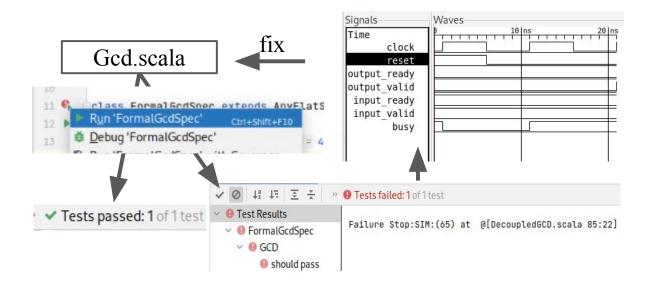

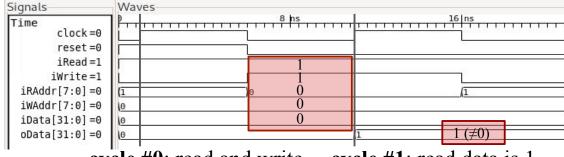

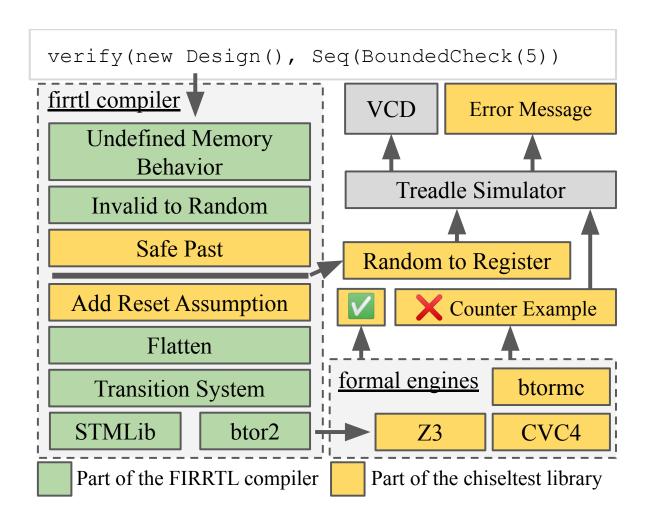

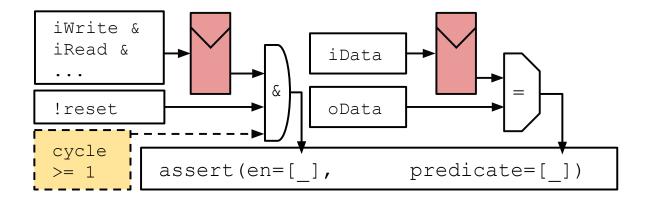

| 5.1               | Formal Verification with an IDE                                                                                                  | 59              |

| 5.2               | ZipCPU verification quiz implemented with ChiselTest                                                                             | 62              |

| 5.3               | Implementation of the verify Command                                                                                             | 63              |

| 5.4               | Implementation of the past Function.                                                                                             | 67              |

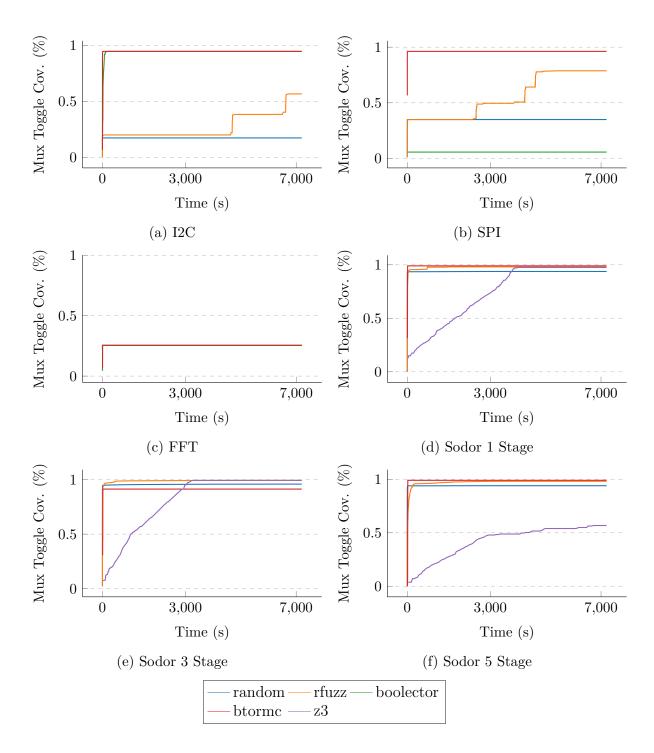

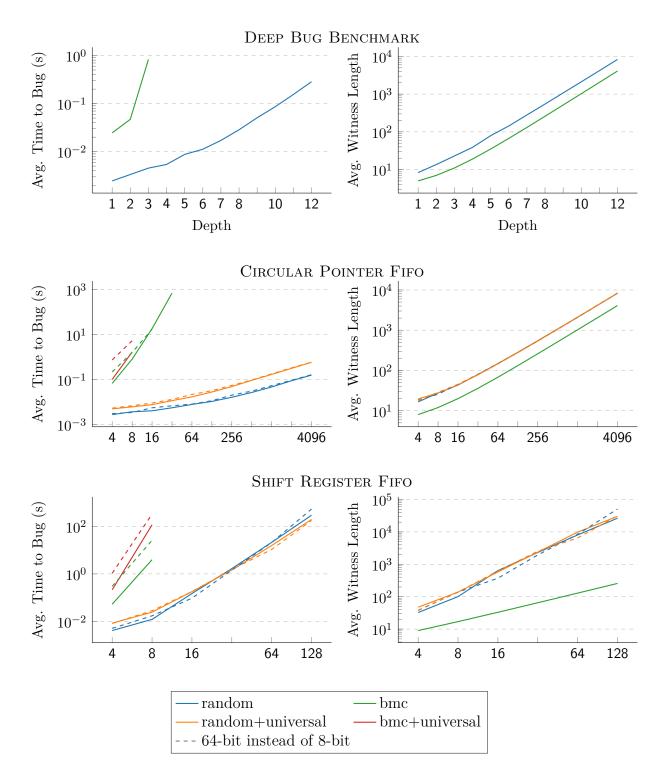

| 6.1 | Mux control toggle coverage over time. BMC-based coverage generators generally |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | outperform the fuzzer and the random baseline                                  | 72  |

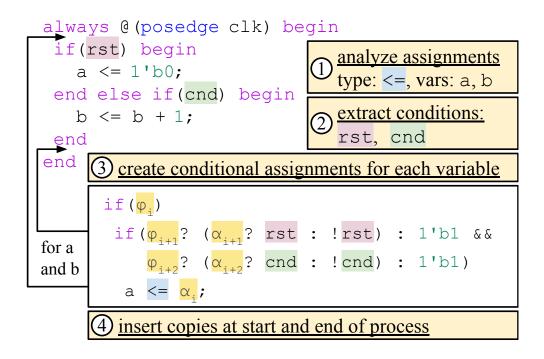

| 6.2 | Average time to find a bug and average length of the witness over the depth of |     |

|     | the design                                                                     | 76  |

| 6.3 | Average time to find a bug and average length of the witness over the depth of |     |

|     | the design on a second set of benchmarks                                       | 77  |

| 7.1 | A counter circuit with a missing reset value                                   | 83  |

| 7.2 | Repairing the counter circuit from Figure 7.1                                  | 85  |

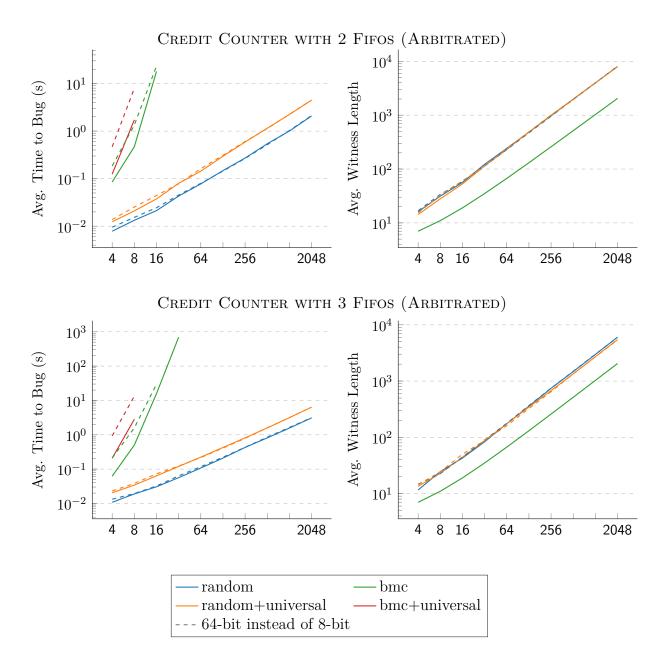

| 7.3 | RTL-Repair Flow                                                                | 87  |

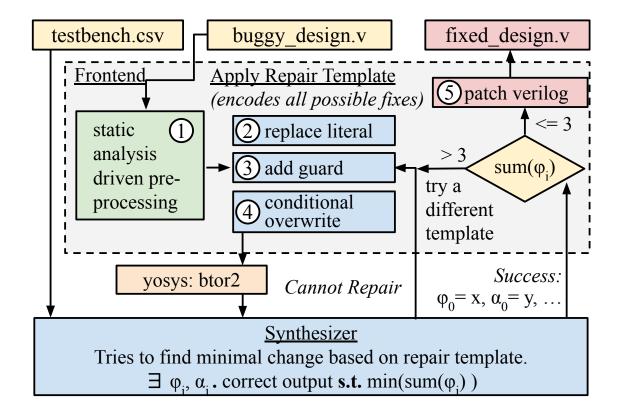

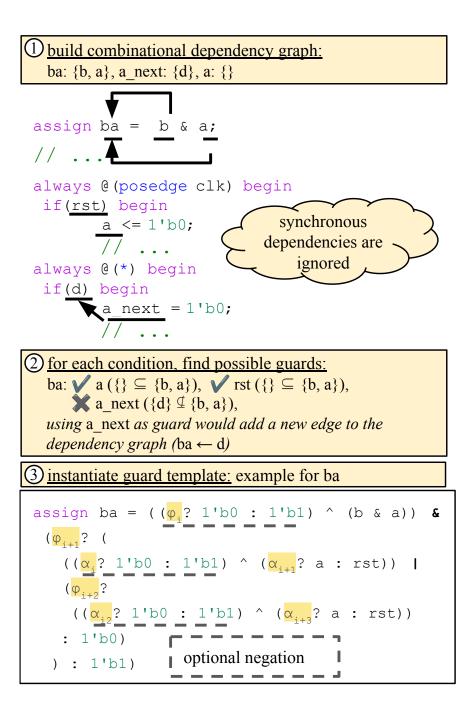

| 7.4 | Conditional Overwrite Repair Template                                          | 89  |

| 7.5 | Add Guard Repair Template                                                      | 90  |

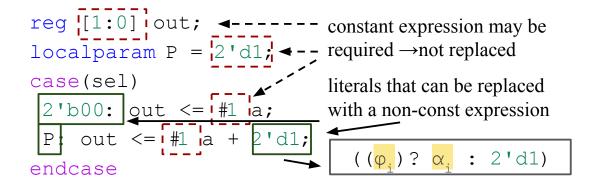

| 7.6 | Replace Literals Repair Template                                               | 91  |

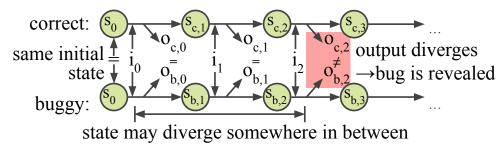

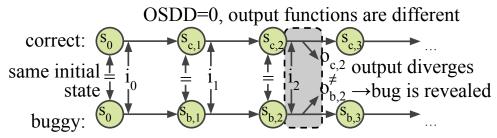

| 7.7 | Output / State Divergence Delta (OSDD) Example                                 | 95  |

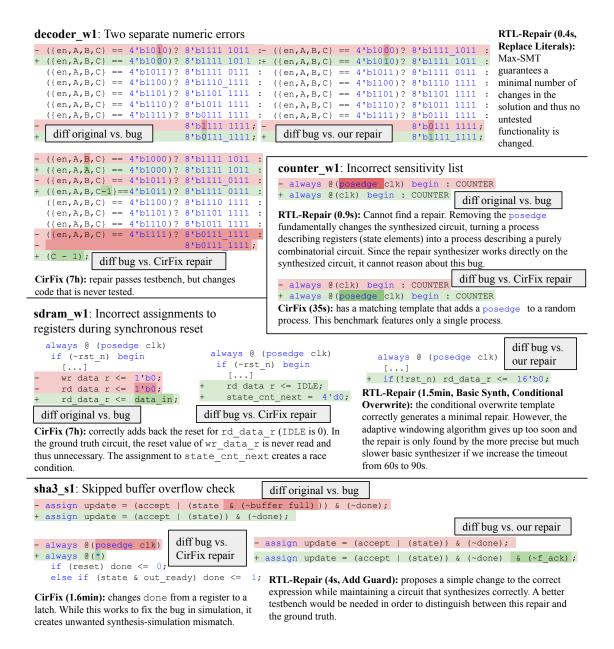

| 7.8 | Qualitative Comparison of RTL-Repair and CirFix Repairs on Four Different      |     |

|     | Benchmarks                                                                     | 99  |

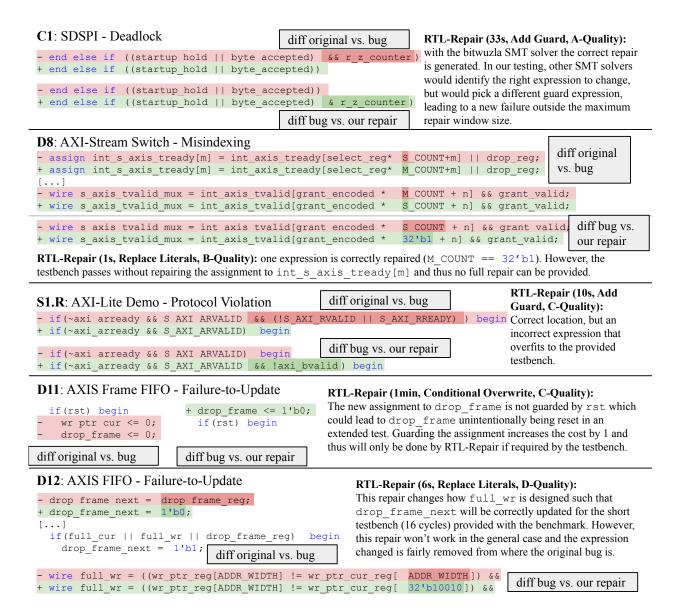

| 7.9 | Repairs produced by RTL-Repair for the Open-Source bugs discussed in Sec-      |     |

|     | tion 7.4                                                                       | 104 |

## List of Tables

| 3.1 | Lines of code for coverage passes and report generators                                                                                                                                                                                                                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Coverage Benchmark Overview                                                                                                                                                                                                                                                                                       |

| 4.1 | Deterministic mutation techniques                                                                                                                                                                                                                                                                                 |

| 4.2 | Non-deterministic havoc mutations                                                                                                                                                                                                                                                                                 |

| 4.3 | Benchmarks                                                                                                                                                                                                                                                                                                        |

| 4.4 | Speedup: FPGA vs software simulation                                                                                                                                                                                                                                                                              |

| 4.5 | Machine specifications for speedup evaluations                                                                                                                                                                                                                                                                    |

| 6.1 | Number of coverage holes and best time to achieve maximum coverage across rfuzz benchmark designs and input generators. Note that for fuzzing, we do not consider the time it takes to compile the simulation of the design under test, while BMC times include the time it takes to parse and load the design 74 |

| 7.1 | RTL-Repair vs state-of-the-art tool                                                                                                                                                                                                                                                                               |

| 7.2 | Output / State Divergence Delta Evaluation                                                                                                                                                                                                                                                                        |

| 7.3 | RTL-Repair Benchmark Overview                                                                                                                                                                                                                                                                                     |

| 7.4 | Repair Correctness Evaluation                                                                                                                                                                                                                                                                                     |

| 7.5 | Repair Speed Evaluation                                                                                                                                                                                                                                                                                           |

| 7.6 | RTL-REPAIR Results for Bugs from Open-Source Projects                                                                                                                                                                                                                                                             |

## Acknowledgments

First and foremost, I would like to thank my advisor, Koushik Sen, who stuck with me for all seven years of my PhD. He discovered my potential and encouraged me to apply to PhD programs in the United States. He never stopped believing in me, giving me the stability to follow my own research agenda, even though – at times – I could not explain to him exactly what I was working on. Thank you, Koushik!

Jonathan Bachrach was another of my early supporters. He is always full of inspiring ideas, and he has helped me appreciate the artist's approach to research. I will always be motivated by his deeply held belief in the power of programming language designs to radically simplify common programming and design tasks.

Sanjit Seshia was my favorite teacher at Berkeley. With his insightful lectures and precise and compassionate way of answering student questions, Sanjit is one of my biggest role models for my own teaching style. My favorite time as a teaching assistant was working with Sarah Chasins, who was excellent at running her compilers class and always ensured that her TAs could grow their teaching skills without being overworked. Borivoje Nikolić always provided excellent, actionable feedback on paper drafts, even when I added him to the document out of the blue.

Most projects in this thesis would not have been possible without my great collaborators. Jack Koenig wrote the original FIRRTL compiler passes for RFUZZ (Chapter 4), and Donggyu Kim almost magically enabled RFUZZ to run on an FPGA within just a couple of days. David Biancolin ran all the FPGA benchmarks for the work on simulator independent coverage (Chapter 3) and wrote down the results for our paper. Brandon Fajardo and Abhik Ahuja worked with me for two years while they were undergraduates at Berkeley and provided me with an excellent study of all the bugs in the CirFix dataset, enabling me to design the RTL-REPAIR tool (Chapter 7).

Vighnesh Iyer was always the first person I would discuss research ideas with. He kept me sane, meeting with me weekly over Zoom while we were working from home because of the COVID-19 pandemic and later when I was working remotely from Cambridge. Tianrui Wei provided much-needed enthusiasm during the final years of my PhD. His insights into industry tools and his challenges to many of my ideas about tools and hardware language designs have resulted in many new research directions.

I want to express my gratitude to several members of the Chisel and greater hardware open-source community. Deborah Soung helped me understand how Chisel coverage is obtained in a commercial setting. Chick Markley was instrumental in adding cover support to the Treadle simulator. Tom Alcorn originally suggested adding a cover statement to FIR-RTL, ultimately leading me to the idea presented in Chapter 3. Several members of the Chisel community helped lay the groundwork for the formal verification support described in Chapter 5: Tom Alcorn, Daniel Kasza, Jack Koenig, Deborah Soung, Chick Markley, Schuyler Eldridge, and Jiuyang Liu. I would also like to thank Claire Wolf for all she has done to advance the open-source Verilog ecosystem. Without the open-source yosys tool, many of my projects would have been impossible.

One of my biggest regrets about my PhD is that I never published a paper with any of the excellent researchers in my research group. I fondly remember Rohan Padhye explaining the intricate details of the Java ecosystem and the JVM to me. Caroline Lemieux and Rohan also worked on some fuzzing projects with me. They introduced me to the idea of keeping a second coverage map for valid inputs, which I used for the RFUZZ implementation. Caroline also showed me how to properly run evaluations of fuzz testing tools and the importance of quantitative data analysis for computer science research. Rafael Dutra graciously included me in his Quicksampler paper, introducing me to the paper-writing process shortly after I started my PhD. Rohan Bhavishi is one of the hardest-working people I know. He single-handedly saved our class project with monumental effort. We also spent many lunches supporting each other throughout grad school.

Benjamin Brock was the first person I befriended in Berkeley. I remember that on one of our daily runs, we talked about how cool it would be for me to also start a PhD in Berkeley, and then that actually happened when I got accepted about half a year later. Ben and Michael Dennis were my most important support system when – all of a sudden – I was applying to U.S. graduate schools with only a month left until the deadline. Without their feedback on my statement drafts and company, while working late at the lab, I could not have made it. Federico Mora was not only the foremost expert on SMT during my time at Berkeley but also an excellent friend. Backpacking provided me with important time away from research, and none of my trips would have been as much fun without this great group of people: Stanley Smith, Regina Eckert, Sarah Sterman, Justin Yim, and Emma Alexander. I also enjoyed several years of working with the CS graduate student association. In particular, I would like to thank Gabriel Fierro and Alon Amid for their leadership.

No research department works without staff who can help distracted professors and graduate students stay organized. The Aspire, Adept, and Slice labs that I was part of had an excellent team of staff who helped me succeed in my PhD: Roxana Infante, Tamille Chouteau, Ria Briggs, and Kostadin Ilov. On the department side, Shirley Salanio and Jean Nguyen helped me navigate the university bureaucracy and patiently answered my many questions.

I would like to thank my parents, who never cared about my grades as long as I put in the effort. They always supported me in my dreams, even if these took me far away from them, starting with a year of high school in the United States, leaving to study at RWTH Aachen, and then pursuing my PhD in Berkeley.

Finally, I would like to thank my soul mate. My wife has always believed in me, even when I was doubting that I would finish my PhD. She has brought me so much joy and supported me through the ups and downs of doing a PhD. I would also like to thank our two-year-old daughter for supporting me by taking regular naps and not missing me while she has fun at daycare.

## Chapter 1

## Introduction

The ability to execute programs at super-human speed and accuracy is the primary enabler of applied computer science. Most computation now happens on integrated digital chips comprising billions of transistors manufactured on a silicon wafer. Over the previous half-century, engineers have developed an elaborate stack of abstractions that enable us to build such complex systems [38, 125].

Many innovations have happened at the transistor and manufacturing level, making it possible to fit more transistors yearly on the same chip area, often for the same price. Gordon Moore at Intel observed in 1975 that the number of transistors doubled roughly every two years without an increase in cost, thus coining the term Moore's Law [34]. Dennard scaling enabled increased compute frequency for each semiconductor generation. By lowering the supply voltage, the power needed to switch a transistor is reduced, and thus, the switching frequency can be increased [40]. However, Dennard scaling does not consider that a minimum threshold voltage needs to be met for a transistor to switch reliably. Also, once the energy used to switch a transistor is sufficiently reduced, the so-called *leakage current*, consumed by any transistor powered on, becomes an essential factor. Thus, the frequencies at which digital VLSI designs could realistically be run stopped improving in the early 2000s [18]. The end of Dennard Scaling led to new power-aware designs that would selectively power down unused transistors or scale the operating frequency dynamically to stay within a defined power budget [139]. However, nowadays, in 2024, most experts agree that the pace of technological advancement has slowed down, the number of transistors is no longer increasing at the same speed, and the cost per transistor is not falling as rapidly anymore, thus spelling out the end of Moore's Law [140].

The vast improvements in transistor density and power consumption from the 1970s to the mid-2000s led to a focus on programmable general-purpose processor designs. There was little incentive to invest significant engineering resources into specialized chip designs if, by the time that design was finished, a programmable CPU manufactured in a new VLSI technology would be performant enough to make the specialized design obsolete. The electronic design automation (EDA) software that emerged is still heavily influenced by this singular focus. The tools are built for large teams of experts focused on heavily optimizing a

single design. It is very much acceptable for a single EDA tool to require a dedicated engineer to configure and run. The focus on detailed optimizations means very little modularization and reuse.

In software engineering, however, development speed and time to market are paramount. Software development will always be different from hardware because it is feasible to update software, while changing a VLSI design after it has been fabricated is impossible. However, maturing VLSI technology and the need for specialization make it feasible and necessary to forgo some performance optimizations for lower engineering costs <sup>1</sup>. Small teams can use mature open-source compilers and libraries to build sophisticated software applications quickly. On the other hand, state-of-the-art industrial hardware design projects rely on proprietary simulators and synthesis tools of varying quality and feature support. Reuse mostly happens on a very coarse grain level of IP blocks. It often consists of copying source code into a project instead of linking to a library version that receives continuous updates.

The academic and open-source community has started to address some of these issues over the last 15 years. Work on new hardware construction languages (HCLs) has tried to answer the reuse problem by providing the means to implement flexible hardware generator libraries. Important examples are Chisel [7], Migen [20], Amaranth [150], SpinalHDL [116], Magma [142] and PyMTL [88]. The open-source yosys [153] synthesis tool enabled numerous new research tools that take advantage of its Verilog frontend and the RTL-IR circuit representation. Yosys can convert Verilog circuits into the much simpler botr2 [111] format, enabling a new generation of academic model checkers to work with standard circuits. Yosys is also an integral component of the OpenROAD project, which aims to provide a fully open-source flow for compiling register transfer level circuit descriptions into mask sets that can be fabricated [3]. An important research goal of OpenROAD is to allow for this conversion with minimal configuration and no human intervention. There is also a new generation of accelerator design languages (ADLs) which aim to raise the level of design abstraction such that abstract algorithm descriptions can be compiled down to efficient hardware [112, 124, 129].

New HCLs and ADLs offer a promising approach to making hardware designers more productive. However, just as important as creating the designs is to test that they work as expected. A recent study [56] reports that commercial semiconductor projects generally have more engineers working on verification than on design. These numbers reflect both the fact that testing and formal verification are paramount for a project's success, as well as the problem that current industry practices and tools require a lot of human engineering effort. In contrast to industry, a recent academic study found that many open-source hardware projects include few tests. Of the 50 most popular open-source projects for FPGAs on GitHub, "88% do not include test cases to reproduce bugs" [90]. This thesis presents four projects and tools that promise to make hardware verification engineers more productive,

<sup>&</sup>lt;sup>1</sup>Intel, for example, decided to rely more on standard cells for their recent Lion Cove design, sacrificing maximum performance for faster time to market and reduced engineering costs. https://chipsandcheese.com/2024/06/03/intels-lion-cove-architecture-preview/

Figure 1.1: The agile RTL hardware development flow.

complementing the prior research on improving hardware design productivity.

Digital hardware is designed at many levels of abstraction: Functional simulators, RTL descriptions, and physical and standard cell design are all part of the process. However, most bugs are introduced at the register transfer level (RTL) [56]. RTL code is written by designers who use informal natural language descriptions of the expected functionality, which offers many opportunities to introduce incorrect behaviors. The RTL code precisely specifies the circuit's cycle-by-cycle behavior, and generating a mask set for tape-out is a mostly automated process, leaving little room for human-introduced errors. In the hardware context, verification refers to both testing an RTL design by executing it with a simulator (dynamic verification), as well as verifying a design with model checkers, proof assistants, or other formal tools (formal verification). The term testing is often used to talk about the process of finding manufacturing defects, which needs to take implementation details below the register transfer level into account. Throughout this thesis, which I write from a mixed software and hardware engineering perspective, I use RTL testing and dynamic verification interchangeably to try to bridge both worlds.

Through my research and my interactions with RTL designers in academia and industry, I have developed an idealized mental model of how RTL is or should be, written. This model is somewhat aspirational in treating verification as an integral part of development, similar to the test-driven development [11] methodology in software engineering. This lofty goal often falls short in practice because hardware designers feel they do not have time to write tests or because testing the whole system is too slow. Testing individual components is too difficult because of a lack of a cleanly defined interface or functionality. Nonetheless, this model has the advantage of being simple and helpful in illustrating verification ideas while being close enough to reality - especially for greenfield RTL projects - so they are not entirely irrelevant.

Figure 1.1 illustrates the agile RTL hardware development flow. The RTL designer writes

RTL code and then executes any available tests. If a test fails, they will have to look into the failure, figure out what is going wrong, and then update the RTL design to fix a bug. If all tests pass, this might mean that the RTL design is done and working as expected. However, it might also indicate insufficient testing, which means the engineer must expand the test suite. Throughout this thesis, I present four tools that promise to address the testing and debugging experience for RTL designers.

When RTL engineers write tests that simulate their design under test, they want to measure how thoroughly the existing tests cover the design functionality and identify parts of the design that require further testing. Coverage metrics quantify how often different features of a design are executed. Simple automated metrics check how many lines in the RTL source code are executed, how many states in a finite state machine are visited, or how many bits in a signal are toggled during a test's execution. More sophisticated functional coverage metrics require user input to define high-level features that must be covered. An example would be if the RTL designer writes code to capture how often the RTL implementation of a cache component executes a particular memory transaction.

While these coverage metrics are helpful, well known, and well supported in commercial SystemVerilog simulators, none of the simulators created for new hardware construction languages like Chisel supported them, and there were not enough engineers to painstakingly implement support for each metric in each simulator individually. Instead, I developed a new approach where coverage metrics are implemented only once as instrumentation passes in the FIRRTL compiler, which processes every Chisel-generated circuit. These passes generate synthesizable hardware, which simulators already had to support, and one new cover statement construct. I carefully designed this statement to be easy to implement across various simulators – from interpreters to FPGA-accelerated simulation – while being powerful enough to represent all standard coverage metrics. Chapter 3 shows how different coverage metrics and simulator support were implemented and that performance overhead is generally negligible.

Traditionally, engineers use the feedback from coverage metrics to extend and enhance their test suite manually. Would it be possible to use the coverage feedback to generate new test inputs directly, leading to greater coverage? I developed such a tool based on coverage-directed mutational fuzz testing, which had previously only been applied to finding security vulnerabilities and other bugs in software projects. Chapter 4 details the necessary steps to adapt the idea to hardware. I define a new coverage feedback metric that is easy to instrument, a way of mapping fuzzer-produced inputs to the cyclic execution of digital RTL circuits. I also demonstrate a tool architecture and isolation techniques that make it feasible to fuzz test designs running on an FPGA.

Simulation-based tests are easy to set up, and the required tools are widely available. However, they suffer from the fact that it is infeasible for all but the simplest circuits to explore all possible inputs exhaustively. On the other hand, formal verification promises to prove properties of a given design for all possible inputs and execution traces. However, formal verification tools have a reputation for requiring extensive background knowledge and being difficult to use. In Chapter 5, I detail my work on integrating bounded model checking

into the ChiselTest library, making this powerful capability available to all Chisel users. This support was first released with ChiselTest 0.5.0 in 2021 and has since been used to write exhaustive tests for components from the Chisel standard library.

Finding a bug in the RTL design is only half the work. Once designers are faced with a failing test case, they still need to invest countless hours in analyzing the failure and developing a fix for the design. Automatic program repair promises to automate that task fully. However, results from a prior attempt to build such a tool for RTL designs were disappointing. The genetic algorithm-based tool would take minutes or hours to come up with a plausible repair, and many of these repairs would actually introduce new subtle bugs where the design would pass simulation, but the circuit generated from the high-level description would be buggy. Chapter 7 describes my RTL-REPAIR tool, which uses a novel repair algorithm based on ideas from bounded model checking to quickly (within seconds) generate repairs with a low false-positive rate. Since repairs are generated very quickly and with minimal changes, RTL-REPAIR has the potential to become an integral part of an RTL designer's workflow.

This thesis presents four tools for automated testing, verification, and repair of RTL hardware designs. All tools take advantage of and contribute back to the emerging new generation of open-source tools for chip design. While the majority of tools I built during the seven years of my PhD will not be successful in their own right, I believe they form a blueprint for how we can innovate in this new landscape of open EDA tools. We need to question and re-build the fundamentals of EDA software instead of trying to perform research on top of commercial tools, which we cannot modify or introspect. I could not build RTL-REPAIR without the formal verification library I built for ChiselTest and the yosys synthesis tool from the open-source community. The FIRRTL compiler and the open-source Verilator simulator enabled me to build the high-performance RFUZZ fuzzing tool. A commercial simulator would have made the task much more difficult.

## Chapter 2

## Background

This chapter introduces basic concepts, tools, and methodologies for developing digital hardware. We define the register transfer level (RTL) of abstraction used by all hardware designs discussed in this thesis. All four tools from this thesis ingest descriptions of hardware designs expressed in a hardware description language (HDL) or hardware construction language (HCL). Thus, we provide context on both concepts. We then discuss in detail how bugs in RTL designs are found through simulation-based dynamic verification and formal verification.

## 2.1 Register Transfer Level (RTL) Circuit Design

Each chip design undergoes multiple levels of abstraction, eventually resulting in a set of photolithography masks used to fabricate the chip on a wafer. Each level of abstraction reduces the designer's cognitive load by limiting the degrees of freedom and the number of physical phenomena that need to be considered. Engineers always designed chips at various levels of abstraction, simulating a CPU design in software before drawing schematics and later polygons for photolithography masks. However, nowadays, the formerly painstaking and error-prone process of manually translating between abstraction layers has been mostly automated with software [38, 125]. Design still happens at all levels of abstraction. Still, most circuits are now designed at a high abstraction level and then automatically mapped to small primitives designed at a lower level of abstraction. For example, a high-level CPU description gets mapped to adders, flip-flops, SRAM memories, and other standard cells. Some common levels of abstraction are functional models, register transfer models, which include cycle accurate timing, gate-level models with gate delay information, gate-level netlists, which use standard cells of a particular VLSI process, circuit model simulations (SPICE), and mask sets.

In this thesis, we exclusively work with digital, synchronous circuits. Digital means that every wire in our resulting circuit carries either a zero or one value encoded as a voltage above or below a defined threshold. The voltage will fluctuate during computation, but the

wire should carry a clear digital value when looking at converged instead of transient states. Synchronous means that state elements like registers and memories are all updated together with one global clock event. This implies that the slowest path for signal propagation through the circuit will determine the maximum frequency at which we can update our state elements. One single path determining the maximum frequency, a significant factor in computation speed, is a major downside that can be mitigated through various approaches, such as automated or manual retiming. The advantage of the synchronous approach is that fully automated tools exist to go from a high-level (RTL) description to a working circuit. Static timing analysis tools analyze the gate-level graph to ensure that no timing violations can happen. While asynchronous circuit design can mitigate the problem of the longest path determining computation speed, designing them requires much more manual effort, and often, the trade-offs are not worth it.

We define register transfer level (RTL) to mean that the designer explicitly defines each state element, like registers and memories. In our model, non-state, i.e., combinational circuit elements, do not carry delay information; outputs change instantaneously with the inputs. We can thus define each output bit as a boolean function of all input and state bits in the circuit. Circuit state elements are updated synchronously whenever a clock event happens. Each state bit's value after the clock event – the *next* value – is defined by a boolean function of all input and state bits before the clock event. Instead of working with boolean variables and operators directly, we often define *output* and *next* functions in terms of a finite bit-vector logic that simplifies our expressions while maintaining a straightforward lowering to boolean functions. This lowering is often called *bit-blasting*.

There are many ways of encoding the functions for the next value of a state element or the value of a circuit output. This thesis broadly distinguishes structural and behavioral descriptions. A structural description generally consists of a directed graph in which each node represents a combinational circuit element like a logic gate or adder, and edges denote connections between outputs and inputs and outputs of these elements. This description closely matches the resulting circuit of standard cells. It is also akin to the concept of a dataflow graph in the compiler literature. A behavioral description, on the other hand, is essentially a pure function that performs a bounded amount of computation over the function inputs and yields the output value as a result. Please note that the term behavioral in particular has carried various definitions in the literature, so our definition might not always agree with how other texts and researchers use the term.

## Converting Behavioral to Structural RTL

We can lower a behavioral function into a structural dataflow graph through symbolic execution where each function argument is initialized to a symbol; computations are applied symbolically to build up the data flow graph, and all possible branches through the program are explored. Branches are integrated into the data flow graph as If-Then-Else (ITE) expressions or multiplexers. ITE is the name used in the software domain; 2-input multiplexers are muxes that fulfill the same function in the hardware domain. Figure 2.1 shows

```

module Counter(

input clock, input reset, input enable,

output reg [3:0] count, output reg overflow

always_ff @(posedge clock) begin

if(reset) begin

count <= 'd0;</pre>

overflow <= 1'b1;</pre>

end else begin

if(enable) begin

count <= count + 'd1;</pre>

if(count == 4'b1111) begin

overflow <= 1'b1;</pre>

end

end

end

endmodule

```

(a) Behavioral RTL description

```

module Counter(

input clock, input reset, input enable,

output reg [3:0] count, output reg overflow

);

// wire declarations elided ...

// registers

always @(posedge clock)

count <= count_next;</pre>

always @(posedge clock)

overflow <= overflow_next;</pre>

// structural combinational logic

assign count_plus_1 = count + 32'd1;

assign count_is_15 = count == 4'hf;

assign count_mux = enable ? count_plus_1[3:0] : count;

assign count_next = reset ? 4'h0 : count_mux;

assign overflow_mux = count_is_15 ? 1'h1 : overflow;

assign overflow_next = reset ? 1'h1 : overflow_mux;

endmodule

```

(b) Structural RTL description

Figure 2.1: Lowering a counter from a behavioral to a structural RTL description.

```

module FalsePath(input a, input b, output logic [2:0] c);

logic [2:0] d;

always_comb begin

if(a) d = 'd0;

else d = 'd1;

if(a & d) c = 'd2;

else c = 'd3;

end

endmodule

```

(a) Behavioral RTL description. The assignment on the highlighted line is unreachable.

(c) Structural RTL description after Optimization

Figure 2.2: Lowering of a behavioral design with an unreachable branch using yosys [153]. Naive symbolic execution creates a mux that includes the unreachable path condition a & d. Optimization can discard the false path.

the behavioral description of a simple counter circuit as well as the structural description of the same circuit. The open-source synthesis tool yosys [153] was used to parse the behavioral Verilog and to lower it into a structural version using the proc command. The resulting Verilog was then cleaned up manually to reduce the number of intermediate signals and to provide better names for signals generated by yosys. We see how every register is connected to two muxes, which reflects the three possible values they might transition to. The count register can either be reset to zero, updated with the sum of its prior value and one, or stay the same, which is expressed by assigning the old value.

There are two major challenges when converting a behavioral to a structural description: (1) naive approaches will include false paths with mutually exclusive path conditions, and (2) finding correct bounds for unrolling loop is hard. False paths are generally avoided through heuristics that let hardware compilers filter out trivially unreachable paths. This is often sufficient since behavioral hardware descriptions are often much simpler than general software programs. Figure 2.2 shows an example where the yosys synthesis tool includes a false path when lowering from behavioral to structural RTL (using the proc command). The false path is later optimized away through the synth command. The issue of bounding loops can be avoided by not allowing loops, like in the Chisel language [7], or by requiring that loop bounds must only depend on compile time known values like in the synthesizable

subset of SystemVerilog [62].

## 2.2 Hardware Description Languages

The concept and challenges of register transfer level design are generally independent of the concrete hardware language that implements them. While countless languages have more narrowly focused on register transfer modeling, the industry's most popular hardware description languages are SystemVerilog [62] and VHDL [64]. Both languages support modeling circuits across several levels of abstraction, from behavioral RTL down to analog components and precise circuit delays. The underlying execution model of SystemVerilog and VHDL is based on parallel processes that emit and are scheduled in response to events such as value changes. The event-based model enables developers to simulate a wider variety of circuit components; however, efficiently mapping arbitrary circuit descriptions to an actual circuit implementation is essentially impossible. Thus, while simulators generally support all language constructs, other tools, like circuit synthesis or formal verification tools, work with much smaller synthesizable subset of the language [61, 38]. This thesis uses SystemVerilog and its predecessor language, Verilog, in various examples, such as Figure 2.1 and 2.2 in this chapter. A paper on "Verilog HDL and Its Ancestors and Descendants" [50] contains a more thorough historical perspective on the SystemVerilog language.

Synthesizability. Not all simulation constructs have a mapping to actual hardware, which leads to the definition of a synthesizable subset of the language [61, 135]. The mix of simulation language and automated translation can complicate hardware design: Circuits that seem to work well in simulation might fail to synthesize. A much more severe problem is synthesis-simulation mismatch, where a design is quietly accepted by the synthesis tool, but the resulting hardware behaves differently from the high-level HDL description [102]. Standard approaches to detect simulation-synthesis mismatch are combinational equivalence checking [77], which attempts to prove equivalence between the high-level RTL and the low-level netlist and gate-level simulations [50].

X-Propagation. In a SystemVerilog program, most values are 4-state bit-vectors: each bit can take on a value of 0, 1, Z, or X. The Z value is used to model tri-state buses. The X value is used to model unknown values. For example, these can originate from uninitialized state variables, out-of-bounds reads, unconnected signals, or explicit assignments of a signal to X [144]. Simulation with X values could be considered abstract interpretation since an X can stand for 0 and 1. However, in SystemVerilog, execution with X values is neither sound nor complete, meaning that for some computations with X, the result is over-approximated, and for others, it is under-approximated. Over-approximation, also known as X-optimism, can lead to a mismatch between the 4-state simulation and the 2-state circuit generated by the synthesis tool. X-propagation is thus a common source of synthesis-simulation mismatch.

## Shortcomings of Traditional HDLs

While SystemVerilog remains one of the most widely used languages in the industry, it has several significant problems: (1) language complexity, (2) semantic gap between event-driven execution model and circuits, and (3) lack of powerful meta-programming. The following paragraphs describe each problem in detail.

The complexity of language means that as of 2024, 19 years after IEEE first standardized it, there are no open-source tools that fully support the SystemVerilog standard <sup>1</sup>. Also, while hard data is difficult to come by, industry tools are also known to be lacking in full standard compliance, leading each semiconductor company to define its own subset of SystemVerilog that is safe to use with all tools. Static analysis tools called linters are then employed to ensure all code is written in the approved subset. In software development, on the other hand, many modern programming languages <sup>2</sup> feature only a single official frontend which defines all the languages semantics and thus all language features can be used and should work across development setups. In the past, older languages like C and C++ have struggled with similar problems to SystemVerilog, where different compilers would implement different versions of the language. Lots of standardization work and consolidation of compilers have mostly solved this problem. Currently, only three remaining C++ compilers follow the standard: Clang, GCC, and Microsoft Visual C++. ARM, IBM, and Intel abandoned their custom C++ frontends and now use Clang to process the input to their proprietary compilers [101, 35, 33].

The flexibility of the event-driven execution model makes it challenging to implement tools that need to extract a circuit view of a design. This includes circuit synthesis tools that lower a SystemVerilog description to a gate-level netlist, most formal verification tools, and circuit instrumentation tools for scan-chain insertion. While defining a synthesizable subset helps, it can be difficult for SystemVerilog users to understand which features are synthesizable. Even circuit descriptions that stay within the synthesizable subset can experience simulation synthesis mismatch. Strict linting rules can mitigate this problem. However, linters need to be purchased and configured.

While SystemVerilog features powerful circuit modeling capabilities, its features to generate circuit descriptions programmatically remain limited. Circuits can be parameterized using SystemVerilog parameters, generate-for and generate-if blocks, and compile-time evaluated loops and if-statements. These features are often used to set the bit widths of signals and configure optional features of circuit components. However, there are two general problems: (1) some approaches, like relying on partial evaluation at compile-time to generate hardware, depend on the sophistication of the particular compiler and thus are not guaranteed to be portable (2) more sophisticated generators that need to read in files or process information with custom data-structures are hard or impossible to implement with SystemVerilog. The

<sup>&</sup>lt;sup>1</sup>The slang parser claims full SystemVerilog support, however, parsing is only a small step and - for example - the most popular open-source SystemVerilog simulator Verilator only supports a small subset of the language.

<sup>&</sup>lt;sup>2</sup>Examples of modern programming languages with one a single official compiler are Rust, Go, and Swift.

standard approach for generating networks on chips or bus interconnects is thus to write a program in a general-purpose programming language like Perl or Python, which then generates SystemVerilog source code. Producing SystemVerilog strings directly, without going through a robust abstraction, can be error-prone and hard to debug, though.

These issues make it difficult to create reusable hardware components that can be shared across companies and teams. The language complexity also makes it very difficult to build new, innovative developer tools without a large team of engineers. Basic RTL descriptions are very simple, but SystemVerilog has evolved to contain a lot of accidental complexity [21], which must be dealt with to build reliable tools. Academic research is still feasible by focusing on a subset of SystemVerilog features required for the benchmarks used in a particular paper. However, none of these tools ever make it into the hands of end users since supporting arbitrary SystemVerilog designs is too difficult.

## 2.3 Hardware Construction Languages

While the languages discussed in the previous section focus on describing hardware behavior, a new generation of so-called hardware construction languages (HCLs) instead shifts the focus to writing reusable hardware generators. With ever-increasing SoC complexity, many designers aim to write RTL generators that can be extensively parameterized and reused. A prime example is the RocketChip SoC generator, which essentially takes in a list of devices to instantiate (e.g., cores, peripherals, accelerators) and automatically generates an RTL implementation of interconnects and device instantiations [6].

Hardware construction languages (HCLs), a term coined by the Chisel paper [7], provide a simple hardware description language that is in a general-purpose programming language that allows for powerful meta-programming. A Chisel generator is a Scala [113] program, which uses various functions from the Chisel package to build up a circuit description while executing. This process is called *elaboration*. Chisel is *deeply embedded* in the Scala host language since it builds up the circuit representation in memory [51].

The main contrast to previous approaches of generating, e.g., Verilog from a Perl script, is that the RTL constructs are not just strings but native objects in the host language, leading to better type safety and maintainability. Many HCLs are designed to make non-parameterized circuits look like they were written in a regular hardware description language. Chisel, for example, provides a when branch construct and assignment operators that work similarly to non-blocking assignments in Verilog.

Other HCLs are migen [20], which had its first commit in 2011, shortly after Chisel development had started and before the first paper on Chisel was published. Migen is embedded in Python. Its successor, which was rewritten from scratch, is Amaranth [150], which, among other things, generates hierarchical RTL descriptions. Migen would place all circuitry in a single module, making the output harder for humans to read and for backend tools to process. Other well-known HCLs are Magma [142] and PyMTL [88, 69], both of which are embedded in Python, as well as SpinalHDL [116] which is embedded in Scala.

```

class Counter extends Module {

val enable = IO(Input(Bool()))

val count = IO(Output(UInt(4.W)))

val overflow = IO(Output(Bool()))

val count_reg = RegInit(0.U(4.W))

count := count_reg

val overflow_reg = RegInit(false.B)

overflow := overflow_reg

when(enable) {

count_reg := count_reg + 1.U

}

when(count === "b1111".U) {

overflow_reg := true.B

}

}

```

(a) Behavioral Chisel description

```

module Counter :

// wire declarations elided ...

// registers

reg count_reg : UInt<4>, clock with :

reset => (UInt(0), count_reg)

reg overflow_reg : UInt<1>, clock with :

reset => (UInt(0), overflow_reg)

// structural combinational logic

node count_plus_1 = add(count_reg, UInt(1))

node count_is_15 = eq(count, UInt(15))

node count_mux = mux(enable, tail(count_plus_1, 1), count_reg)

count_reg <= mux(reset, UInt(0), count_mux)

node overflow_mux = mux(count_is_15, UInt(1), overflow_reg)

overflow_reg <= mux(reset, UInt(0), overflow_mux)</pre>

```

(b) Structural LoFIRRTL description

Figure 2.3: The counter from Figure 2.1 expressed in behavioral Chisel and its structural FIRRTL description.

## 2.4 RTL Intermediate Representations and Compilers

We first need to compile the Scala source code of a Chisel generator into Java byte code. Then, we execute the resulting binary, which uses the Chisel library to generate a circuit description. Some HCLs are implemented in a host language that does not need to be compiled, so we can skip the compilation step. However, the *elaboration* phase in which the generator is executed to create a circuit description is common to all HCL implementations. After *elaboration*, we generally want to obtain a description of the generated circuit that can be simulated, formally verified, or mapped to an FPGA or ASIC implementation. Commonly, HCLs produce an RTL description of the circuit in a subset of the Verilog or SystemVerilog language. Verilog is used as an interchange format since it is supported by virtually all open-source and commercial backend tools.

Some HCLs directly generate a Verilog description during elaboration. However, many HCLs feature an intermediate representation (IR) that represents the circuit after elaboration and a compiler that converts the IR to a Verilog output. Chisel used to generate Verilog directly, but since the Chisel 3 release, it utilizes the FIRRTL IR and compiler to perform the lowering from high-level, Chisel-like IR into a normalized structural circuit representation [67]. The low-level representation can then be exported into a subset of Verilog that was chosen as a common subset supported by the majority of backend tools. The introduction of a compiler simplifies the conversion from Chisel circuit constructs to an equivalent description in Verilog. The compiler implements type-checking, width inference, lowering of behavioral constructs and advanced data types, and some simple optimizations as individual passes. It is generally easier to correctly implement these individual passes than a single monolithic conversion to Verilog during elaboration. Other HCLs also feature an IR similar to FIRRTL [142, 150].

When I started working on this thesis in 2017, the FIRRTL compiler was under heavy development, and Chisel 3, the first version to rely on a compiler, was about to be released. While the most crucial advantage of the new architecture was to make correct Verilog generation more reliable and easier to maintain, Jack Koenig and Adam Izraelevitz were already looking for other applications that would benefit from this new compiler. I quickly picked up my colleagues' enthusiasm, and finally, three of the four projects I present in this thesis heavily use the FIRRTL compiler. For more details on the Chisel and FIRTL, I recommend reading Adam's PhD thesis [66].

The fuzzing framework I present in Chapter 4 features several new FIRRTL passes to collect coverage information and implement isolation techniques that allow us to quickly reset the design on an FPGA between running different fuzzer-generated inputs. Chapter 3 generalizes the coverage instrumentation approach using the newly developed cover construct to implement various coverage metrics as FIRRTL passes. The generated instrumentation is independent of the backend simulator, showing how the concept of retargetable compiler also applies to RTL development. Finally, the formal verification infrastructure presented in Chapter 5 relies on a new backend to the FIRRTL compiler, which I developed to turn RTL designs into transition systems that a model checker can consume. The new past

construct presented in that chapter is a good showcase of the extensibility of the FIRRTL compiler, which makes it possible to easily post-process circuit primitives through annotations that attach meta-data to them and automatically schedule associated compiler passes to be executed. The simplicity of the FIRRTL representation allowed these tools to work with virtually all Chisel circuits. In contrast, academic tools for SystemVerilog-based designs, for which no open-source compiler or IR exists, tend to be brittle and only work for benchmarks used in the respective papers.

Since Adam Izraelevitz graduated from UC Berkeley in 2019, most of the Chisel and FIRRTL infrastructure has transitioned from being maintained by graduate students to a team of full-time engineers primarily working for the SiFive semiconductor company. SiFive started re-implementing the FIRRTL compiler in 2020 under the leadership of Chris Lattner and using C++ and the MLIR compiler framework [82] to deal with larger designs and changing business requirements. Converting large designs at SiFive from FIRRTL to Verilog would often take several minutes up to half an hour with the old Scala-based research compiler. With the new compiler, this time has been drastically reduced [43].

Internally, SiFive builds most of its RISC-V CPU cores using Chisel. It then sells this IP to customers who receive the generated Verilog code. When these customers need to debug their design containing SiFive RISC-V cores, they thus need to rely on the output, rather than the input of the FIRRTL compiler, to investigate what is going wrong. This challenges the assumptions under which the original FIRRTL compiler was built. It is generally much easier, less error-prone, and compatible with many more tools to stick with simple Verilog constructs. Everyone who worked on the first Chisel-based designs at Berkeley had access to the original Chisel code. Thus, the generated Verilog could be treated as akin to assembly generated by a software compiler. In transitioning to the new compiler, SiFive engineers spent much energy and time to generate SystemVerilog output that would look better to customers by incorporating more advanced SystemVerilog features. While more bug-prone and time-consuming to implement, this approach does make sense when transitioning Chisel from academia to industry.

Open-source compilers and intermediate representations are not limited to hardware construction languages. There has been recent work in the area of high-level synthesis [112, 124, 129], as well as for established industry languages like Verilog [127, 153], and the CIRCT project which is trying to grow from a new implementation of the FIRRTL compiler to become a unifying compiler framework for hardware construction [43]. The open-source synthesis tool yosys also features an internal representation called RTL-IL [153]. Many ideas developed for this thesis can be applied to any of these new compilers, sometimes even for more significant gain. The CIRCT project, for example, is currently close to gaining a way to import SystemVerilog designs and compile them down to the simple core dialects. Thus, if someone re-implements the system for unified coverage that I represent in Chapter 3 for CIRCT, we would be able to obtain, e.g., a single toggle coverage pass that works not only for Chisel designs (via the FIRRTL frontend of CIRCT) but also for SystemVerilog and combined Chisel / SystemVerilog designs. Recently, I advised a Master's thesis on implementing some of the ideas I present in Chapter 5 with CIRCT, which will make them

available for SystemVerilog designs once CIRCT gains the import capabilities [41].

## 2.5 Simulation-based Testing of RTL Designs

Designing hardware at the register transfer level can be difficult and error-prone, even with modern languages like Chisel. Digital hardware executes in a highly parallel manner; complex operations must be manually broken up and mapped to multiple cycles to meet timing; physical concerns like power efficiency must be addressed; and designers need to add extra complexity to enable testing the resulting semiconductor chip for manufacturing defects. Thus, it is paramount to test or verify each RTL hardware design comprehensively.

To obtain the highest level of fidelity and test execution speed, we would have to manufacture the hardware design. We would then be able to execute our tests on the final implementation. This approach is prohibitively expensive; circuit manufacturing takes a long time, and the visibility of the manufactured design is poor. Instead, the most common approach to executing an RTL description for testing is to use a software simulator or accelerated simulation with specialized chips. Testing designs in simulation is often referred to as dynamic verification in the hardware community.

### RTL Hardware Simulators

A variety of open-source and commercial simulators exist. Most of them focus on traditional hardware description languages like SystemVerilog and VHDL [136, 52]. Still, some recent options build on the FIRRTL compiler and thus exclusively work with circuits described in Chisel [97, 73, 10]. Software simulator implementations navigate a spectrum of latency vs. throughput regardless of the input language trade-offs. Simulators that interpret the RTL circuit description with little preprocessing are low latency in that they take very little time before simulation of the first cycle of execution. However, interpretation is generally slow; the number of cycles simulated per second, i.e., the throughput, tends to be low. Most commercial Verilog simulators started as interpreters because they are easy to implement [50] before switching to compiled simulation. The open-source simulator Icarus Verilog [151] and the Treadle [97] simulator for FIRRTL both use the interpreter approach.

The simulation throughput can be improved by converting the RTL circuit description into a compiled simulation. Open-source tools like Verilator [131] and ESSENT [10] achieve this by generating a simulation as C++ code, which is then compiled to optimized native machine code through a C++ compiler. Generating and compiling the C++ code takes significant time, thus increasing the latency but leading to much higher throughput.

For even higher throughput, we need specialized hardware that can take advantage of the massive amount of fine-grain parallelism contained in RTL designs [38]. RTL designs can be mapped to a network of small compute cores, enabling high throughput with some increase in latency that is required to perform the process of mapping the design across a large number of processing elements. Recent work has explored this option with custom bulk parallel processors as well as using off-the-shelf machine learning accelerators [45, 44]. There are also commercial products that use similar techniques, but details are hard to come by.

Even higher throughput can be achieved through FPGA-accelerated simulation as implemented by the FireSim tool [73, 76, 74, 94, 12] for Chisel designs. Unfortunately, mapping an RTL design to an FPGA after transforming it with the Golden Gate compiler [93] can take hours or nearly one day. In addition to that, the visibility is poor since the internal design state cannot easily be transferred out of a running design. There are options to gain more visibility. However, they require the design to be paused every time we need to inspect state [149]. Similar to the bulk synchronous option, there are also commercial products that use FPGAs to simulate RTL designs, but few details are publically available [12]. Simulating RTL designs on specialized hardware has the downside in that software testbenches can not easily be used to drive the design since the cost of communicating with the design on the simulation accelerator on a per-cycle basis is too high.

### **Testbenches**

The ability to simulate the execution of a given RTL hardware design is necessary but not sufficient to test the design. Most hardware designs are not closed systems. Instead, they feature input and output pins that communicate with the environment. In order to test a given design under test (DUT), we need to provide values to the input pins and check that the values on the outputs match our expectations. Often, we might also want to initialize states like registers and memories or check that they contain the values we expect them to contain. Thus, we need a setup called a testbench that lets us provide inputs to a DUT running in a simulator. This testbench generally takes on the form of a program interacting with the DUT, an event-driven model of some external hardware interacting with the DUT, extra RTL hardware used for testing that will not be included in the final design, or a combination of all three.

#### SystemVerilog Testbenches

A simple testbench can be directly implemented in Verilog. Since Verilog is primarily a simulation language, it is not restricted to circuit descriptions but also features verification constructs. A Verilog testbench consists of a top-level module with no input or output pins - a closed system - which instantiates the DUT and connects to its input and output pins. The clock input of the DUT can be driven by toggling a variable between zero and one using a simple Verilog process and the delay construct to define the clock period. The other inputs are driven to chosen test inputs, also called test stimuli, through assignments in another process. Output values are checked with a simple if statement, and the finish statement can be used to terminate the simulation if there is a failure. Verilog also supports printing values to a file or standard output, which can be used to implement a check against a file containing the expected outputs. A recent study found that a large number of open-source RTL projects do not include self-checking testbenches [90]. Instead, a developer presumably

checked the outputs as they were implementing the RTL design. These manual checks are often performed on a wave dump, i.e., a record of all signal values over time during a given simulation run. These wave dumps can be visualized with a waveform viewer like GTKWave or Surfer to aid debugging.

SystemVerilog [62] was developed to allow developers to program elaborate testbenches. It contains many features from general-purpose programming languages, like classes, methods, and functions, as well as specialized hardware testing features. SystemVerilog makes it possible to randomly initialize struct according to user constraints. This enables constrained random testing in which test engineers guide the random stimuli generation to explore the behavior of the design under test thoroughly. SystemVerilog Assertions provide an expressive, declarative temporal property language for runtime monitoring and formal verification. The Universal Verification Methodology (UVM) [63] is an industry-standard verification framework that takes advantage of many of SystemVerilog's new features. Unfortunately, no open-source simulator currently supports enough SystemVerilog features to run UVM testbenches. The reason for this is that a language that is meant to be useful for verification and hardware modeling incurs a lot of complexity, making it hard to implement support for the whole language.

#### Simulator APIs

The open-source community and the vast majority of new hardware languages have thus taken a different approach. Instead of adding testing constructs to the hardware language, one can interface with the simulator from a general-purpose programming language and use that to implement a testbench. A classic example is Verilator, which converts an RTL design into the C++ source of a simulation of said design. The generated simulation code can then be instantiated and driven by a C++ program. As the testbench is compiled with the simulation, this approach leads to fast testbenches. Unfortunately, the API is fairly barebone, difficult to use, and simulator-specific, making testbenches non-portable.

#### Testbench Libraries

Testbench libraries implemented in a general-purpose programming language provide a more powerful and user-friendly approach. Cocotb is an open-source library implemented in Python that allows users to interface with hardware designs simulated in a wider variety of commercial and open-source simulators [59]. Like Verilog, it uses an event-driven programming model, allowing users to implement processes that interact with the design under test based on Python async/await co-routines. Cocotb uses the standard DPI interface [62], which makes it compatible with many simulators. Unfortunately, DPI and the even-driven paradigm can lead to slow test execution. The Amaranth language features a testing library that uses Python co-routines for low overhead threading but interfaces directly with a Python-based simulator, thus reducing the communication overhead [150].

#### ChiselTest

The ChiselTest library provides a rich Scala-based API to interact with Chisel-based designs under test [87, 42]. I was the maintainer and most frequent contributor between 2021 and 2024, taking over from Richard Lin, who started the project in 2018. ChiselTest originated from many prior attempts to support easy unit testing for Chisel designs and - in true Chisel tradition - eschews any event-based modeling. Instead, time only progresses when the clock of a synchronous design is stepped. Outputs that depend combinational on inputs take on their value immediately after an input has changed. This enables a simple interface, where users interact with a circuit by *poking* values to its inputs, *peeking* values at its outputs, and *stepping* the clock when needed.