### UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Thermal and Power Management for Network and Data Center Applications

Permalink https://escholarship.org/uc/item/07b0x5nq

**Author** Chou, Chih-Hsun

Publication Date 2017

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

Thermal and Power Management for Network and Data Center Applications

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Chih-Hsun Chou

September 2017

Dissertation Committee:

Dr. Laxmi N. Bhuyan, Chairperson Dr. Shaolei Ren Dr. Daniel Wong

Copyright by Chih-Hsun Chou 2017 The Dissertation of Chih-Hsun Chou is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

It is my great pleasure to thank those who made this dissertation possible. I would never have been able to finish it without the guidance of my committee members, help from friends, and support from my family.

I would like to express my deepest gratitude to my advisor, Dr. Laxmi Bhuyan, for his excellent guidance, caring, patience, and providing me with a pleasant atmosphere for doing research. I would also like to thank Dr. Daniel Wong and Dr. Shaolei Ren for guiding my dissertation, giving precious advice and participating in my final defense committee.

I would like to thank my dear wife and the entire family. They were always supporting me and encouraging me with their best wishes.

I would like to thank all members from my lab, who were always willing to help, discuss ideas, and give helpful suggestions. It would have been a lonely lab without them. Many thanks to all my collaborators and friends for helping me complete my Ph.D study. Without them, it would have been difficult to write this dissertation. This dissertation includes content published in the following journals and proceedings:

ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS), 2013

Proceedings of the tenth ACM/IEEE symposium on Architectures for networking and communications systems (ANCS), 2014

33rd IEEE International Conference on Computer Design (ICCD), 2015

Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED), 2016

IEEE 37th International Conference on Distributed Computing Systems (ICDCS), 2017

#### ABSTRACT OF THE DISSERTATION

Thermal and Power Management for Network and Data Center Applications

by

Chih-Hsun Chou

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, September 2017 Dr. Laxmi N. Bhuyan, Chairperson

The last decade has brought an explosive growth of delay-sensitive interactive services that have become an integral part of our lives and constituted an increasingly high portion of network and data center workloads. To attract users and generate revenue, interactive services require high-quality and timely responses. Further, these applications are typically deployed over a large set of high performance servers consuming a significant amount of power/energy. The high power/energy consumption not only directly impacts the operation cost, it also results in high operating temperature, which incurs exponentially increased cooling cost and performance degradation.

In this thesis, we focus on developing power management techniques for network and data center applications. We propose various techniques to reduce the power/energy consumption while satisfying different performance constraints. First, we propose a per-core power management technique based on CPU sleep states for various network applications. The packets are queued in a buffer so that the core can sleep longer. In order to limit the operating temperature, we control the duration that a core can be active and inactive. Moreover, we develop a heterogeneous load distribution algorithm to achieve better tradeoff between thermal behavior and power saving. Second, due to random nature of packet arrivals and packet processing times, satisfying the packet delay constraint is challenging. By developing statistical performance models, we develop a runtime technique to determine when, how long and which cores should be inactive to reduce the power consumption.

Unlike network applications, performance of interactive applications is defined by strict tail latency constraints. With the fast-varying traffic patterns, to satisfy the tail latency constraint, we first propose a dynamic sleep scheme which adjusts the wakeup time of the CPU cores based on request arrivals. Followed by a detailed performance analysis, we conclude that the state transition overhead is another source of energy inefficiency. We propose an all-encompassing power management technique, called  $\mu$ DPM, which coordinates sleep, speed scaling and request dispatching to reduce active, idle and state transition energy consumption all together. Finally, we consider a web search application and observe that the result quality and tail latency together determine the system-wide performance and energy consumption. We explore the application characteristics and propose a quality and latency aware power management technique by judiciously discarding long query executions with ISN-aggregator coordination. Through extensive experiments, we conclude that our schemes significantly reduce the energy consumption while satisfying both the quality and tail latency constrains.

# Contents

| Li             | st of | Figures                                                            | xi  |  |

|----------------|-------|--------------------------------------------------------------------|-----|--|

| Li             | st of | Tables                                                             | xiv |  |

| 1 Introduction |       |                                                                    | 1   |  |

| <b>2</b>       | Rela  | ated Work                                                          | 13  |  |

|                | 2.1   | Power Management Techniques                                        | 13  |  |

|                | 2.2   | Thermal aware power management technique                           | 16  |  |

|                |       | 2.2.1 Task Migration                                               | 16  |  |

|                |       | 2.2.2 Power Reduction                                              | 17  |  |

|                | 2.3   | Tail latency-constrained power management technique                | 19  |  |

|                | 2.4   | Quality and latency aware power management technique               | 20  |  |

| 3              | Pow   | ver and thermal Management on Network Applications                 | 23  |  |

|                | 3.1   | Introduction                                                       | 23  |  |

|                | 3.2   | Packet Processing on a Multicore Server                            | 25  |  |

|                |       | 3.2.1 Packet Processing Characteristics                            | 25  |  |

|                |       | 3.2.2 Power Consumption and Thermal Behavior                       | 27  |  |

|                |       | 3.2.3 Problem with Existing Idle State Power Management Scheme     | 28  |  |

|                | 3.3   | Vacation Thermal and Power Management Schemes                      | 30  |  |

|                |       | 3.3.1 Fixed Vacation Scheme                                        | 31  |  |

|                |       | 3.3.2 Dynamic Vacation Scheme                                      | 34  |  |

|                |       | 3.3.3 Vacation Schemes Performance analysis                        | 36  |  |

|                | 3.4   | Multicore Vacation Scheme                                          | 42  |  |

|                |       | 3.4.1 Performance Analysis of the Vacation Scheme in multicore CPU | 42  |  |

|                |       | 3.4.2 Experiment Setup                                             | 45  |  |

|                |       | 3.4.3 Performance evaluation of the multicore vacation scheme      | 46  |  |

|                | 3.5   | Multicore Vacation Scheme with Thermal Constraint                  | 50  |  |

|                |       | 3.5.1 Achievable throughput                                        | 51  |  |

|                |       | 3.5.2 Heterogeneous Load Distribution                              | 54  |  |

|                |       | 3.5.3 Performance evaluation of HLD                                | 56  |  |

| 4        | Pov            |                  | nagement with Smart Sleep                                           | <b>59</b>  |

|----------|----------------|------------------|---------------------------------------------------------------------|------------|

|          | 4.1            | Introd           | uction                                                              | 59         |

|          | 4.2            | Power            | Consumption in Network and Data Center Applications                 | 64         |

|          |                | 4.2.1            | Basic Request Processing Behavior                                   | 64         |

|          |                | 4.2.2            | Problem Formulation                                                 | 65         |

|          |                | 4.2.3            | Power Consumption Model with Idle States                            | 66         |

|          |                | 4.2.4            | Problem with Existing Idle state Linux Governor                     | 68         |

|          | 4.3            | Smart            | Sleep                                                               | 70         |

|          |                | 4.3.1            | Power Consumption                                                   | 72         |

|          |                | 4.3.2            | Response time                                                       | 72         |

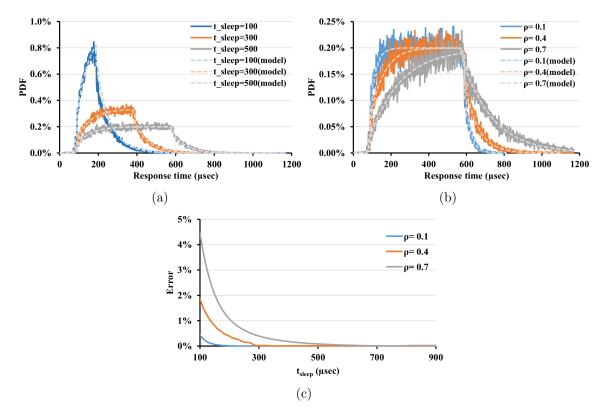

|          | 4.4            | Multic           | core Smart Sleep Framework                                          | 79         |

|          |                | 4.4.1            | Core Sizing                                                         | 80         |

|          |                | 4.4.2            | Power Optimization Heuristic                                        | 81         |

|          |                | 4.4.3            | Runtime Framework                                                   | 83         |

|          | 4.5            | Perform          | mance Evaluation                                                    | 85         |

|          |                | 4.5.1            | Experiment setup                                                    | 85         |

|          |                | 4.5.2            | Single Core Results                                                 | 87         |

|          |                | 4.5.3            | Multicore Results                                                   | 92         |

|          |                | 4.5.4            | Runtime Results with real world traffic trace                       | 95         |

|          |                |                  |                                                                     |            |

| <b>5</b> | Pov            |                  | nagement under Tail Latency constraint                              | 99         |

|          | 5.1            |                  | uction                                                              | 99         |

|          | 5.2            |                  | 1                                                                   | 101        |

|          |                | 5.2.1            |                                                                     | 102        |

|          |                | 5.2.2            | 1                                                                   | 103        |

|          |                | 5.2.3            | 1                                                                   | 105        |

|          |                | 5.2.4            | Evaluation                                                          | 108        |

|          |                | 5.2.5            |                                                                     | 109        |

|          | 5.3            | -                | ations of microsecond request service time on dynamic power manage- |            |

|          |                |                  |                                                                     | 114        |

|          | 5.4            | $\mu \text{DPM}$ |                                                                     | 124        |

|          |                | 5.4.1            |                                                                     | 124        |

|          |                | 5.4.2            |                                                                     | 128        |

|          |                | 5.4.3            | 0                                                                   | 134        |

|          |                | 5.4.4            |                                                                     | 137        |

|          |                | 5.4.5            | $\mu$ DPM Evaluation                                                | 138        |

| c        | D              |                  | we never the day Orality and Latence construint                     | 150        |

| 6        | <b>Pov</b> 6.1 |                  |                                                                     | 150<br>150 |

|          | • • =          |                  |                                                                     | 150<br>154 |

|          | 6.2            |                  | 8                                                                   | 154<br>156 |

|          | 6.3            |                  |                                                                     | 156<br>159 |

|          | 6.4            |                  | 0                                                                   | 158<br>159 |

|          |                | 6.4.1            | 3                                                                   | 158        |

|          |                | 6.4.2            |                                                                     | 161        |

|          |                | 6.4.3            | Query response quality                                              | 162        |

|              | 6.5 | TailCu  | $ut Design \ldots \ldots$ | 165 |

|--------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              |     | 6.5.1   | TailCut Overview                                                                                                                                 | 165 |

|              |     | 6.5.2   | TailCut Design Principle                                                                                                                         | 168 |

|              |     | 6.5.3   | TailCut Performance Analysis                                                                                                                     | 169 |

|              | 6.6 | Config  | guration of TailCut                                                                                                                              | 172 |

|              | 6.7 | Evalua  | ation                                                                                                                                            | 177 |

|              |     | 6.7.1   | Experiment Setup                                                                                                                                 | 177 |

|              |     | 6.7.2   | Results                                                                                                                                          | 179 |

| 7            | Con | clusior | ns                                                                                                                                               | 184 |

| Bibliography |     |         |                                                                                                                                                  |     |

# List of Figures

| 1.1  | The packet/request processing and power consumption pattern                        | 2  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Significant Latency Gap Exists                                                     | 8  |

| 3.1  | The experiment platform                                                            | 26 |

| 3.2  | Power consumption and thermal behavior during packet processing                    | 27 |

| 3.3  | Power consumption under different scenarios.                                       | 29 |

| 3.4  | Flowchart of the fixed vacation scheme                                             | 31 |

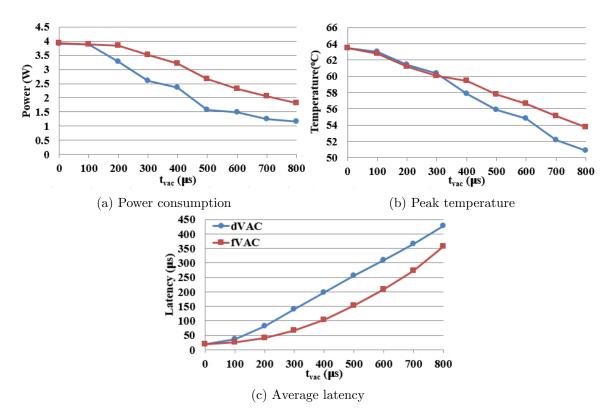

| 3.5  | Power consumption and thermal behavior under fixed vacation scheme                 | 33 |

| 3.6  | Flowchart of the dynamic vacation scheme.                                          | 34 |

| 3.7  | Power consumption and thermal behavior under dynamic vacation scheme.              | 35 |

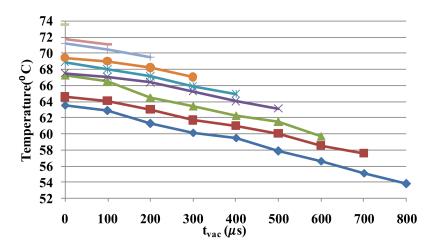

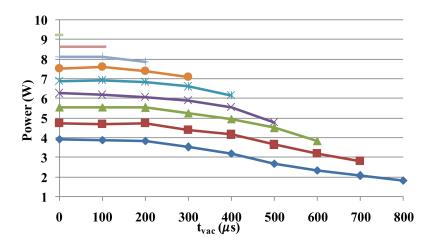

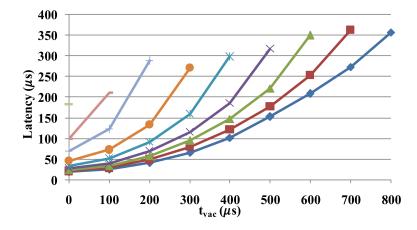

| 3.8  | Peak temperature under fix vacation approach                                       | 36 |

| 3.9  | Power consumption under fix vacation approach                                      | 37 |

| 3.10 | Average packet latency under fix vacation approach                                 | 38 |

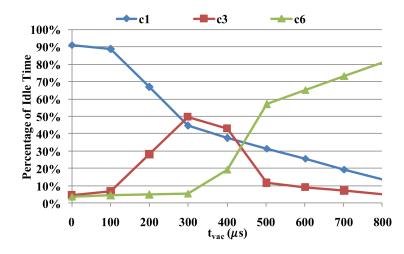

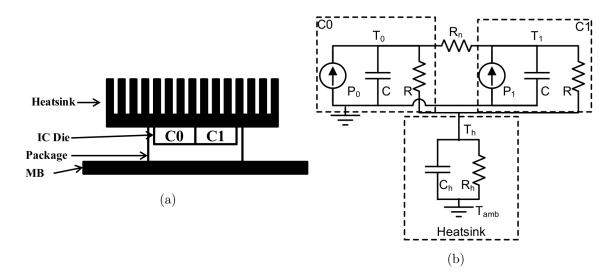

| 3.11 | Percentage of idle period that the core resides in different C-states under fix    |    |

|      | vacation approach ( $\rho = 0.1$ )                                                 | 39 |

| 3.12 | Performance comparison between dynamic vacation and fixed vacation ap-             |    |

|      | proach                                                                             | 40 |

| 3.13 | Percentage of idle period that the core resides in different C-states under        |    |

|      | dynamic vacation approach ( $\rho = 0.1$ )                                         | 41 |

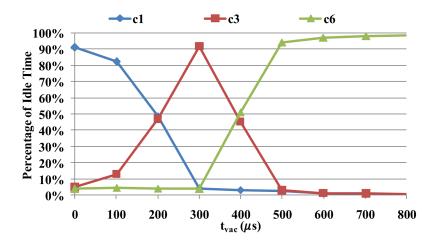

| 3.14 | Thermal model for a typical multicore CPU                                          | 43 |

| 3.15 | Modeled and measured temperature rising of the vacation scheme under dif-          |    |

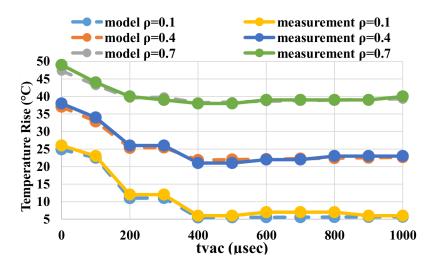

|      | ferent traffic                                                                     | 48 |

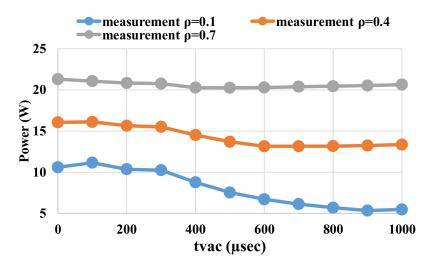

| 3.16 | Measured power of the vacation scheme under different traffic                      | 49 |

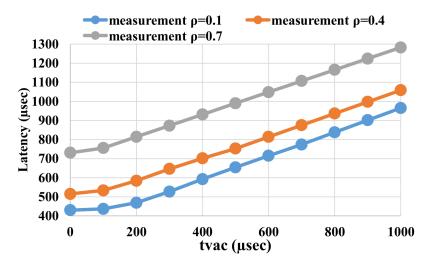

| 3.17 | Measured latency rising of the vacation scheme under different traffic             | 50 |

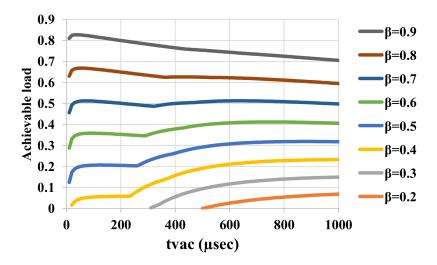

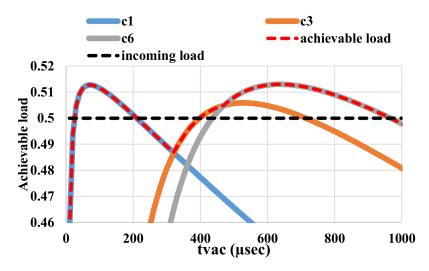

| 3.18 | Achievable load with vacation scheme with different thermal constraint             | 51 |

| 3.19 | Achievable load with vacation scheme under thermal constraint with $\beta = 0.7$ . | 53 |

| 3.20 | Heterogeneous load distribution illustration.                                      | 54 |

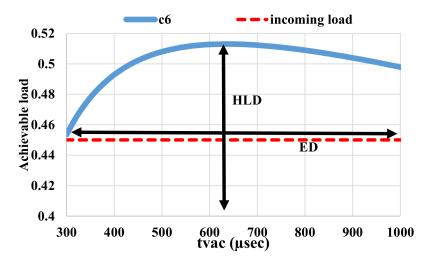

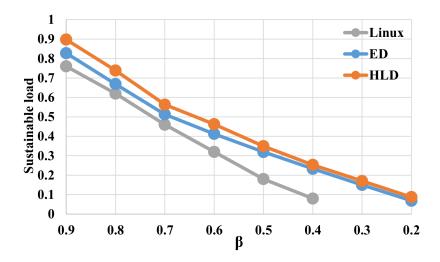

| 3.21 | Per-core power consumption with different traffic load under ED                    | 55 |

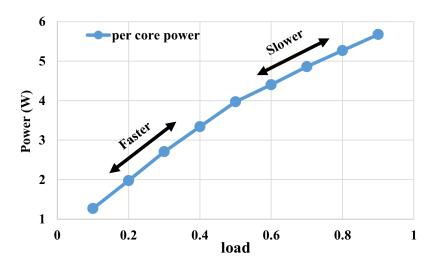

| 3.22 | Sustainable load of different thermal management scheme                            | 57 |

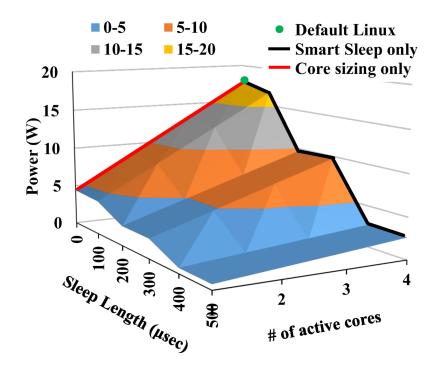

| 4.1  | Illustration of our proposed multicore smart sleep scheme                          | 61 |

| 4.2  | Power consumption under default (green dot), smart sleep only (black line),     |

|------|---------------------------------------------------------------------------------|

|      | core sizing (red line) and multicore smart sleep scheme (3D surface).           |

| 4.3  | Power consumption under different scenarios                                     |

| 4.4  | The packet/request processing and power consumption pattern                     |

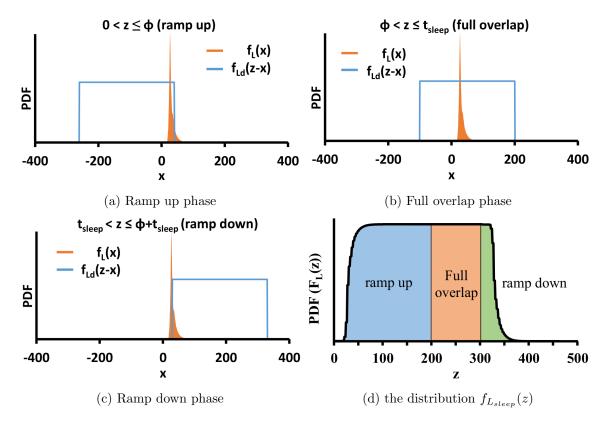

| 4.5  | Illustration of $f_{L_{sleep}}(z)$ through sliding window summation of $f_L(x)$ |

| 4.6  | Illustration of sliding overlap when $\phi \geq z$                              |

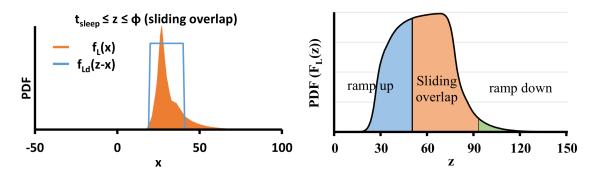

| 4.7  | Experimental and model results for response time distribution under smart       |

|      | sleep                                                                           |

| 4.8  | The overview of multicore smart sleep framework.                                |

| 4.9  | Power consumption under different scenarios                                     |

|      | The break down of the C-states residency with different sleep period            |

|      | Average response time under different scenarios.                                |

|      | Different tail latencies under smart sleep scheme.                              |

| 4.13 | Power consumption after applying multicore smart sleep scheme with differ-      |

|      | ent configuration and traffic loads.                                            |

| 4.14 | Response time after applying multicore smart sleep scheme with different        |

|      | configuration and traffic loads.                                                |

|      | Power saving comparison among different schemes at different traffic load.      |

|      | One day traffic trace recorded from CAIDA [2].                                  |

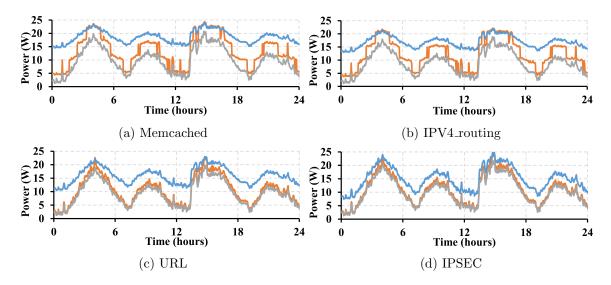

| 4.17 | Power consumption of multicore smart sleep with four different applications     |

|      | under real traffic trace. (peak traffic load 0.8).                              |

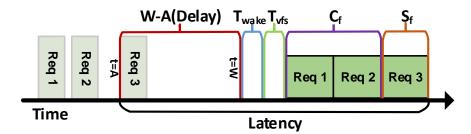

| 5.1  | Illustration of the latency slack.                                              |

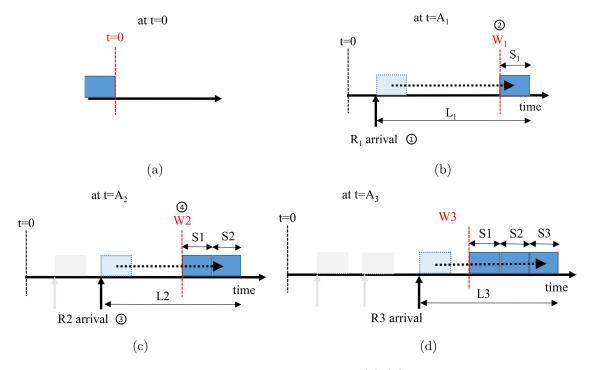

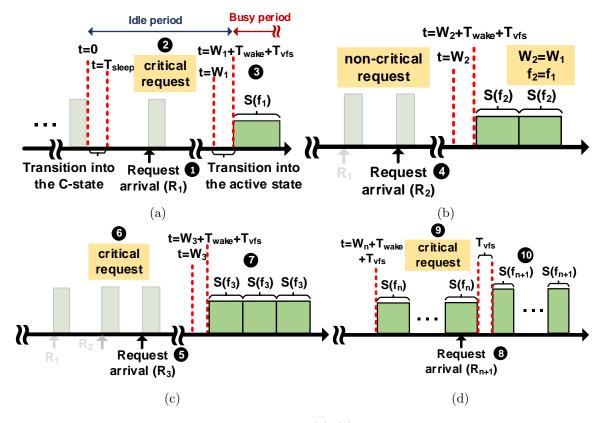

| 5.2  | Illustrative example of dynamic sleep scheme.                                   |

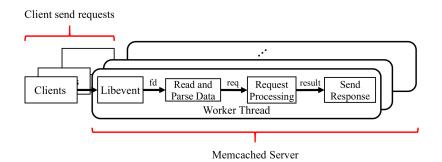

| 5.3  | The process flow of the baseline Memcached.                                     |

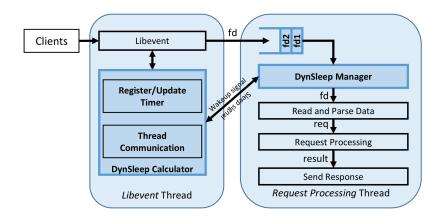

| 5.4  | Dynamic sleep implementation of Memcached.                                      |

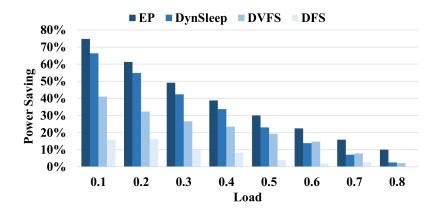

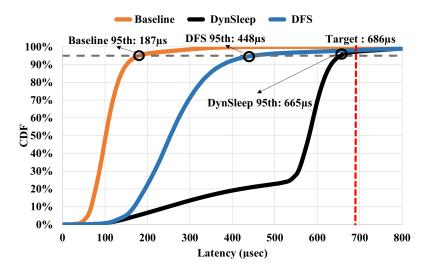

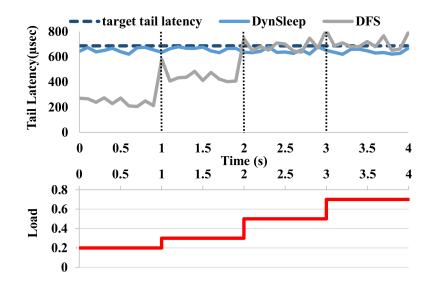

| 5.5  | Power saving comparison among different power management schemes                |

| 5.6  | Latency distribution and tail latency under different power management          |

|      | schemes.                                                                        |

| 5.7  | The tail latency of different power management scheme and different load.       |

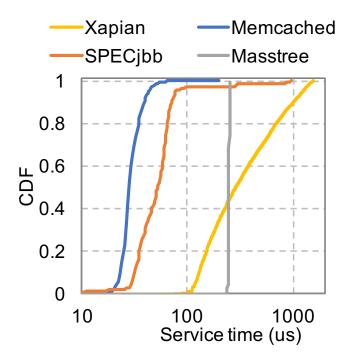

| 5.8  | Service time dist.                                                              |

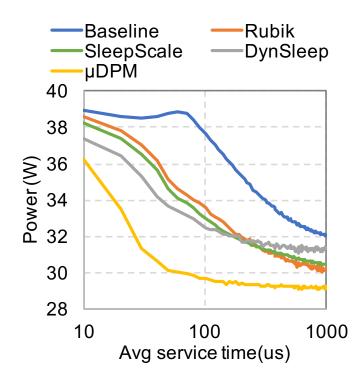

| 5.9  | Power consumption.                                                              |

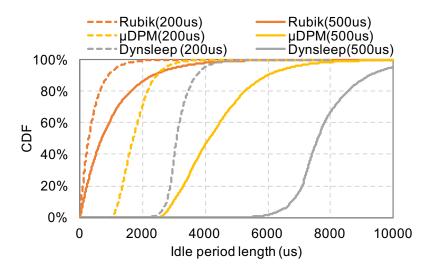

| 5.10 | Idle period length.                                                             |

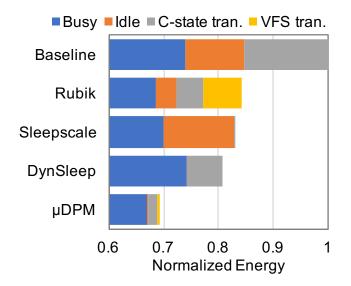

| 5.11 | Energy consumption breakdown.                                                   |

|      | Illustrative example of $\mu$ DPM                                               |

| 5.13 | Service time variations under different system load. The shaded areas are       |

|      | the PDF under each scenario with the width representing the probability at      |

|      | certain service time.                                                           |

|      | $\mu$ DPM performance model                                                     |

|      | Implementation options of $\mu$ DPM                                             |

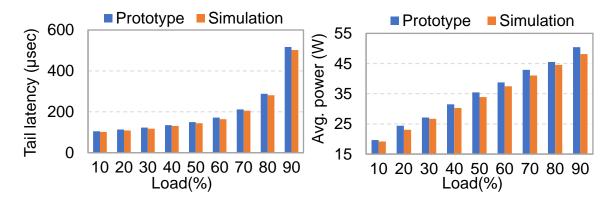

|      | Prototype vs simulation validation.                                             |

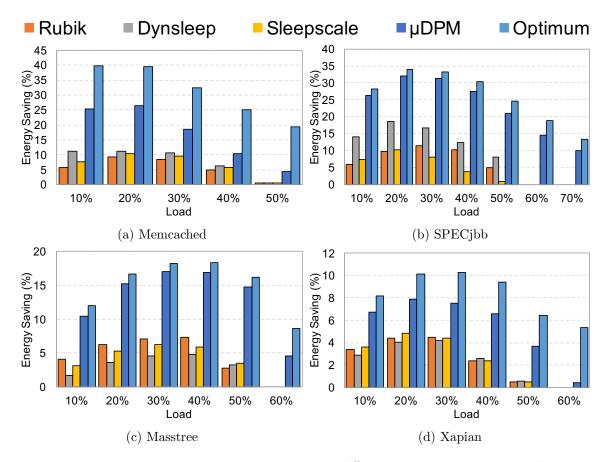

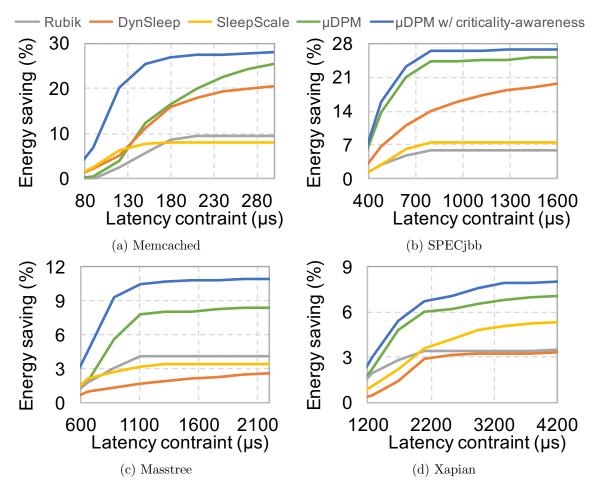

|      | Energy saving comparisons among different power management schemes              |

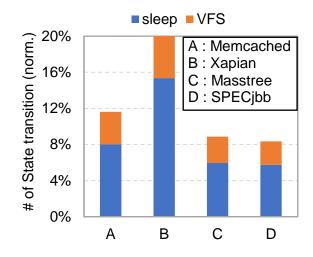

|      | State transition reduction with criticality-awareness                           |

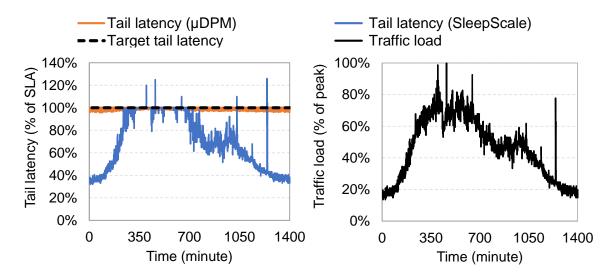

|      | Tail latency under varying traffic load                                         |

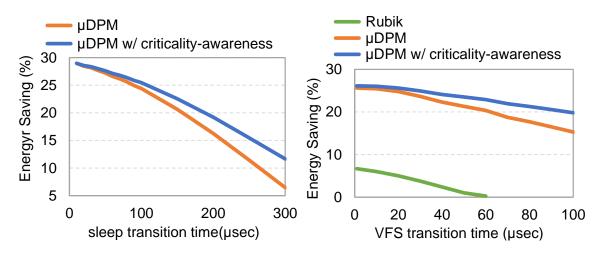

| 5.20 | Sensitivity to target tail latency.                                             |

| 5.21 | Sensitivity to transition time                                                       | 149 |

|------|--------------------------------------------------------------------------------------|-----|

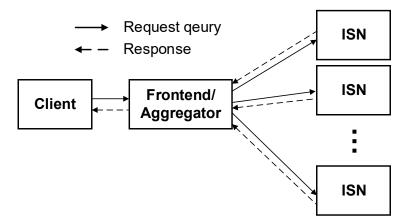

| 6.1  | Search engine architecture.                                                          | 155 |

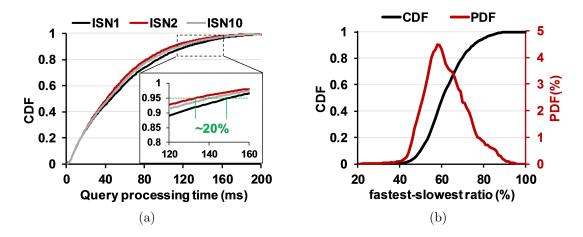

| 6.2  | ISNs processing times diversity.                                                     | 159 |

| 6.3  | Correlation among ISNs' query processing time                                        | 160 |

| 6.4  | Query processing time and energy distribution.                                       | 161 |

| 6.5  | The ISN quality contribution.                                                        | 164 |

| 6.6  | TailCut system overview.                                                             | 166 |

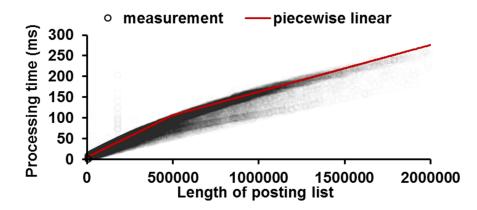

| 6.7  | Relationship between query processing time and the total length of postings          |     |

|      | lists.                                                                               | 168 |

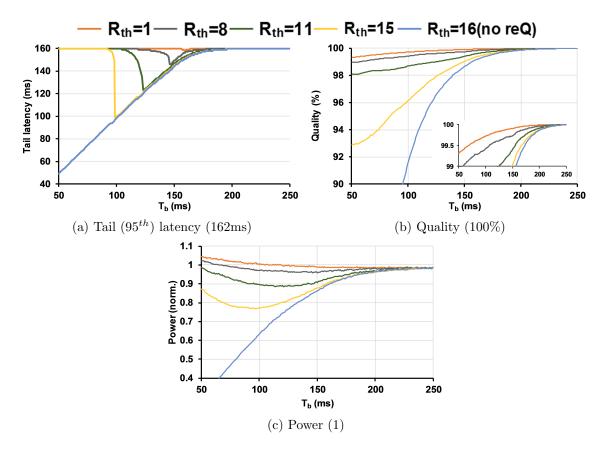

| 6.8  | TailCut performances with different $T_b$ and $R_{th}$ . The baseline system perfor- |     |

|      | mances are given in parenthesis.                                                     | 171 |

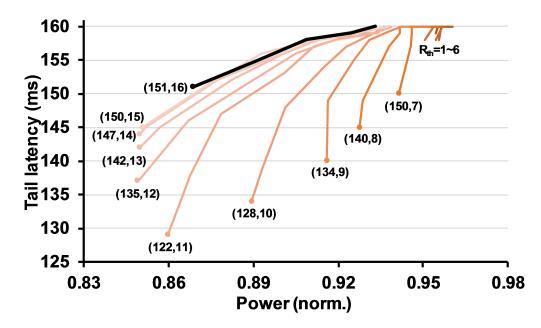

| 6.9  | Power-latency performance under quality constraint (99%). For each line, $T_b$       |     |

|      | is decreasing from 200ms, with $T_b = 200$ ms at the right most point of each line.  | 173 |

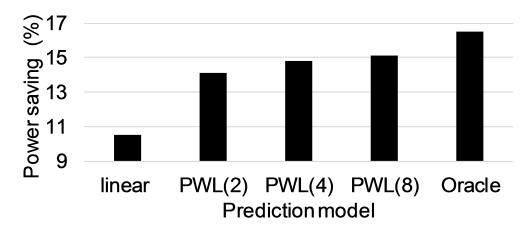

| 6.10 | TailCut performance under different query processing time prediction model.          | 180 |

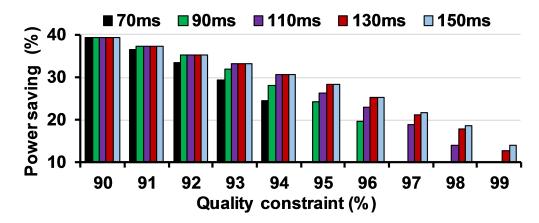

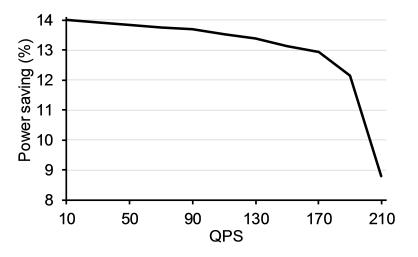

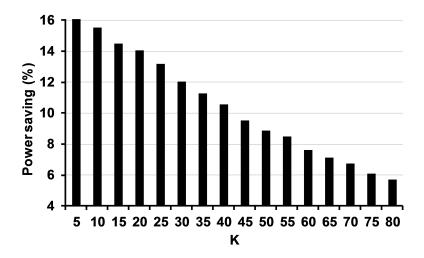

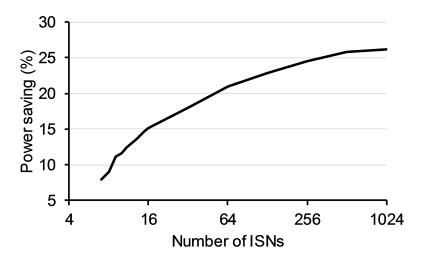

| 6.11 | TailCut power saving under different quality and latency constraints                 | 181 |

| 6.12 | TailCut power saving under different load (QPS).                                     | 181 |

| 6.13 | TailCut power saving under different matched documents (Top-K)                       | 182 |

| 6.14 | TailCut power saving under different number of ISNs.                                 | 183 |

# List of Tables

| 3.1 | Normalized power consumption of ED and HLD                                                                    | 57  |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Characteristics of CPU core C-states.                                                                         | 66  |

| 4.2 | Characteristic of packet processing and datacenter applications                                               | 87  |

| 4.3 | Power saving and energy proportionality (EP) of the multicore smart sleep scheme with different applications. | 97  |

| 5.1 | Measured CPU core C-states on Intel Xeon E5-2697 v2 processor.                                                | 123 |

| 5.2 | Workload characteristics.                                                                                     | 140 |

| 6.1 | Baseline system configuration                                                                                 | 178 |

### Chapter 1

# Introduction

With the explosive growth in the amount of data over the Internet, the network infrastructure and content providers require orders-of-magnitude increase in the capability to meet the throughput and QoS requirement of users. The applications range from network packet processing to the servers in data centers that serve the users requests. The general purpose multicore processors provide the flexibility and high performance to deploy various packet processing algorithms, such as IP forwarding [41], packet classification [89] and deep packet inspection [101], and are commonly deployed in the network infrastructure. Similarly, they form the basic server architecture for data center applications, such as memcached [7, 47] and web search [1,47]. Usually, the network and data center infrastructures are designed with over provisioning to meet the QoS demands, giving rise to low energy proportionality. Thus, increasing the performance and decreasing the power consumption are first-order design goals of modern network and datacenter servers.

We consider network packet processing and data center applications under the

same umbrella because the requests arrive at a server and are served non-deterministically. The service time and arrival pattern vary from request to request and application to application. Along with the high throughput, power consumption plays an increasingly important role in network and datacenter applications. Due to the varying traffic load and non-deterministic request arrival pattern, current multicore servers for these applications lack *energy proportionality* – the power consumption does not scale down proportionally with the traffic load. Because the service capability is provisioned with peak traffic demand, significant amount of energy is wasted during the medium and low traffic periods.

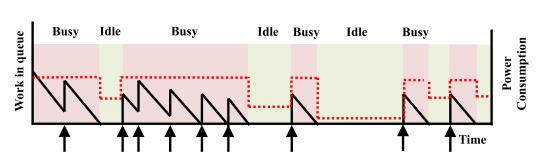

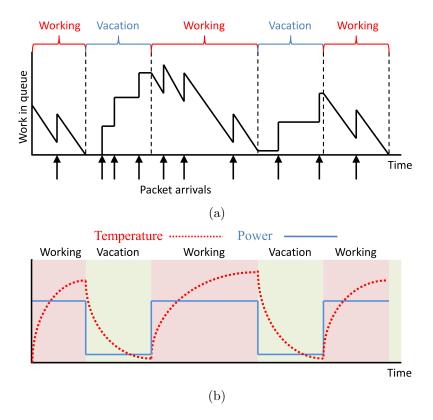

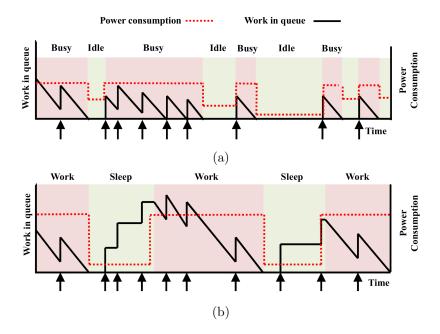

Both network and datacenter applications exhibit ON/OFF patterns [23], as shown in figure 1.1. The x-axis shows the random packet arrivals to a server and y-axis shows the work in queue. The power consumption of the server is shown in dotted red line. The CPU core consumes active power during the ON period (also known as *busy period*) when requests are being processed. During the OFF period (or *idle period*), where no request arrives, the CPU consumes idle power, which is less than the active power, but still quite high. The OFF period between batches of requests provides opportunities to perform

Work in queue

Power consumption .....

Figure 1.1: The packet/request processing and power consumption pattern.

power management. It is important to note that the length of ON/OFF period is not deterministic, and depends on the request arrival and service rates. At the hardware level, two main techniques are used for reducing the energy consumption: (1) Dynamic Voltage and Frequency Scaling and (2) CPU Sleep. The first technique, Dynamic Voltage and Frequency Scaling (DVFS), reduces or increases processor voltage/frequency just enough to meet the performance requirement. DVFS can be either chip-wide, where the entire chip is scaled as one unit, or per-core, where individual cores on the chip can be scaled at different rates. Per-core DVFS adjusts the frequency of each core individually at runtime with on-chip voltage regulators. Although it is more complex to implement, per-core DVFS achieves greater power savings with its fine-grain control over individual cores. DVFS has been applied for network packet processing and data center applications [23, 76, 78, 80, 92]. However, two main physical limitations greatly affect the effectiveness of DVFS. First, the operating voltage approaches the transistor threshold voltage as technology advances, hence decreasing the room for voltage down-scaling [93]. Second, DVFS focuses on reducing the dynamic power consumption only, but static power consumption has become more dominant in today's multicore processors with more advanced manufacturing process [66,72]. These limitations can not be overcome without some breakthrough in the transistor design.

The second technique, CPU sleep, minimizes leakage current when a core is idle by powering down different CPU components. Modern CPUs provide succession of per-core idle states (called sleep states or C-states), where different CPU core components are turned off. The transition time of a sleep state depends on the degree of sleep. The deeper the sleep state, the more time it takes to enter/exit. Because of the state transition overhead, it only makes sense to enter a C-state if inactive time is beyond a certain threshold. Some work proposed to put the entire processor/device into idle states during periods of inactivity [76,91]. Also, a few papers considered switching off a few CPU cores depending on the throughput requirement [48,80,92]. While it is promising on reducing energy consumption, some application execution characteristics limit the use of CPU sleep state for energy reduction. First, for parallel network/datacenter applications, the idle periods of individual cores, each serving independent jobs, hardly ever align. As a result, the effectiveness of processor idle low-power modes is reduced because of the needs of frequent waking up. The processor-wide idleness rapidly vanishes as the traffic load or number of cores grows. Also, waking up the cores from processor level idle states takes a long time for which the OS does not drive them to switch off modes during normal operation. Second, because of the state transition energy overhead, the natural idle periods are not long enough for the OS to put cores into the processor level deep sleep states.

Several researches have been done on reducing the energy consumption by turning off the servers. In [100], "buffer and burst" is proposed to turn off the network router for a fixed amount of time and its impact on the energy consumption and packet latency is investigated. However, this approach focuses on a single device and does not address the problem in multiple cores/servers scenario. Also, it still suffers from the limitation of long state transition latency. In [48], a similar situation of multiple servers with active and inactive states is analyzed. This work focuses on developing various policies to determine when and which sleep states the server should enter. However, they focus on the centralized queue scheme, where off state is a natural extension of the sleep states. The multicore packet processing is usually modeled as distributed queue scheme, where off and sleep states differ significantly. Second, they did not incorporate various C-states in the CPU that suffers from long transition overhead or practically verify the analysis.

Besides power and energy, temperature and thermal constraints also pose a significant challenge to future system design. As the size of the multicore chip decreases with the advancement of the manufacture process, the power density increases significantly. This poses a major challenge toward thermal management in order to maintain the chip temperature within the operating limit. It is known that high operating temperature adversely affects not only the system performance and leakage power, but also the throughput [43], circuit reliability and chip lifetime [111]. In addition, the cooling and packaging cost for heat dissipation increases exponentially with the peak temperature [110]. In the "run-tofinish" scientific applications, the CPU always consumes active power and generates heat while running, and its temperature simply rises to saturation point until it stabilizes. The ON/OFF pattern of network applications exhibit a sawtooth temperature behavior, where the CPU core temperature rises during the ON period, and falls during the idle period. Although reducing the busy/idle period power consumption through DVFS and CPU sleep will help slow down the temperature rise and speed up the CPU cooling, the *length* of busy/idle period will also need to be considered while designing thermal aware scheduling algorithm. Moreover, in multicore CPU, since the cores are densely packed, the temperature variation of a core will have great impact on its neighboring core due to the horizontal heat flows. These complex thermal interactions make the problem challenging in multicore thermal management.

In chapter 3, we present a novel power aware thermal management algorithm to achieve power saving in multicore processors by employing a vacation scheme. In vacation scheme, we focus on controlling the duration of both active and sleep periods. We force the core to sleep for a fixed amount of time in different sleep states. We implement the scheme through the idle states (C-state) provided by the OS in the CPU and show their effectiveness both through analysis and experimental data. Then, we apply thermal constraint to our scheme. To predict the performance, we develop the multicore thermal RC models considering the temperature coupling among cores. Moreover, we derive the power consumption model considering the CPU C-states, and latency model through vacation queuing theory [113]. By combining these models, we can accurately depict the performance with our multicore vacation scheme. Due to the non-linear performance behaviour with different traffic loads, we propose a heterogeneous load distribution, which creates more opportunities for power saving. Besides maintaining processor temperature below the temperature constraint, our technique achieves higher sustainable load and better power saving with minimum latency increase compared to existing thermal management techniques. In chapter 4, we propose a multicore idle period power management scheme by dynamically adjusting the per-core sleep time with different traffic. During the sleep period, the core can enter deep idle state without being waken up prematurely. We call this "smart sleep", when the core sleeps and the arriving requests are queued. Moreover, we explore the possibility of completely turning off some CPU cores by redistributing the traffic onto a subset of cores. By doing so, minimizing the power consumption becomes a two-dimensional optimization problem with both time (sleep) and space (off) variations.

We derive the expected idle and busy periods by considering the length of the core sleep, the number of inactive cores, request service time and the traffic load. By combining these models, we can find the behavior of power consumption under our proposed scheme. Also, we derive the response time model using the M/G/1 queuing model with vacation [113]. Our proposed technique overcomes the limitations that currently exist in the CPU sleep power management scheme, and provide better power-performance trade-offs compared with the existing techniques. The experimental results show that our proposed technique can achieve more than 35% power saving and 60% increase in energy proportionality under real world traffic trace compared with the existing power management techniques.

While throughput remains critical performance requirement for network applications, latency-critical applications are becoming increasingly common in current data centers and pose new challenges for system designers. They exhibit similar ON/OFF characteristics as network applications. Moreover, tail latency, not average latency, determines the quality of service for these applications. Servers running latency-critical workloads are kept lightly loaded to meet strict latency targets, with typical utilization between 10% and 50% [21,91]. This low utilization wastes billions of dollars annually because servers are not energy-proportional and have poor energy efficiency at low server utilization [21,69,86,117].

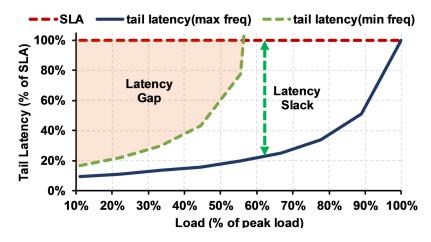

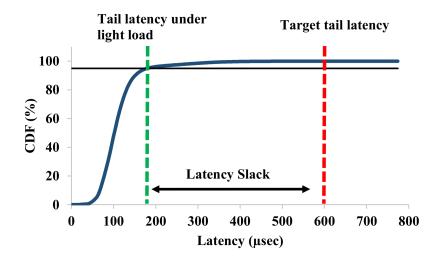

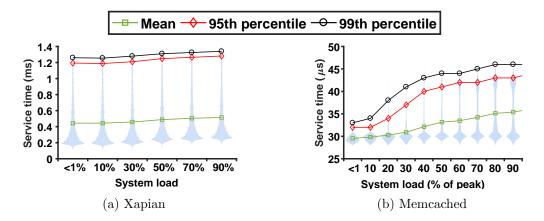

Although servers are usually kept lightly loaded, peak load is considered when setting the proper target tail latency. Thus, the tail latency of servers running under low load will be far lower than the target tail latency. Figure 1.2 shows the tail latency (95<sup>th</sup> percentile latency) of a server running the Memcached application [7] under different loads. We can see that there exists a "latency slack" between the tail latency of the server (solid

Figure 1.2: Significant Latency Gap Exists

black) and the target tail latency as defined in the service level agreement (SLA)(dotted red line). This latency slack provides opportunities for achieving energy proportionality.

Several DVFS-based techniques [69,85,86,114] have been proposed to exploit this latency slack to slow down processing so that the requests finish just before the target tail latency. However, their benefits are limited due to the "floor" of frequency scaling. Figure 1.2 shows the tail latency at minimum frequency(dotted green) and at maximum frequency(solid black). Clearly, DVFS can close the latency slack at higher load above ~50%. However, there still exists a significant "latency gap" at 10%~50% even under the minimum frequency. This low utilization range is where most data center servers spend most of their time [21,91]. Clearly, there exists significant opportunity for power savings by targeting this latency gap. Other prior works exploit CPU sleep states by batching and delaying the processing of requests to create idleness [44,91,93]. However, these techniques do not adhere to strict SLA levels and are not suitable for latency-critical applications.

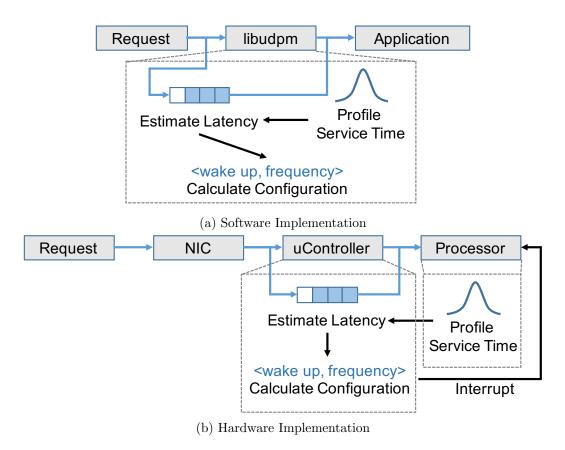

In data centers, traffic pattern often exhibits high short-term variability. Requests arrive at unpredictable times and are often bursty. These short-term spikes dominate tail latency [64, 69] and must be accounted for. To address these issues, in chapter 5, we focus on developing the power management techniques with the consideration of this traffic variability. To exploit the opportunities of power saving with latency slacks, First, we propose a dynamic sleep scheme, a fine-grain power management scheme that exploits latency slack by dynamically postponing request processing. By doing so, the idle periods between two active periods will be prolonged, and the CPU core can efficiently enter deep sleep states to save power. Unlike previous works that require some hardware changes, such as per-core DVFS with nanosecond level transition time [69] and fast sleep state transition techniques [91,93], our proposed technique uses the commonly supported per-core sleep state. Then, we perform a detailed analysis for both sleep and DVFS based power management schemes and find out that the existing dynamic power management techniques are largely ineffective because of the high state transition overhead, short request service time and strict tail latency constraint. Our analysis also shows that sleep or DVFS alone can not fully exploit the latency slack for power saving. We take the lessons learned here to design  $\mu$ DPM, an all encompassing power management framework that coordinates request delaying, per-core sleep states, voltage frequency scaling and load distribution.  $\mu$ DPM extends our dynamic sleep scheme by taking into the account of request processing speed. Also, we develop an novel request redirection algorithm which aims to minimize the both sleep and DVFS state transitions, which are the major sources of energy inefficiency while applying sleep and DVFS power management.

In the data centers, hundreds of thousands of servers work together to achieve strict performance requirements. Instead of per server performance, the system-wide performance is becoming more and more important for online data-intensive applications (OLDI), such as Web Search, social networking and e-commerce. Needless to say, these applications need to meet strict performance constraints, which directly affect users satisfaction as well as revenues [108]. These applications need to process tens of thousands of requests every second over billions of documents, but users expect the response time to be under a few hundred milliseconds. Although high-quality to users queries are crucial in search results, the service provider may often have to compromise the quality in order to meet the stringent latency requirement. Additionally, the system-wide power consumption is also a critical performance metric. With hundreds of thousands of machines, significant power consumption is already leading to a soaring operating cost for the search service provider. As a result, reducing power consumption while meeting the quality and latency constraints is a major challenge in designing OLDI system.

Query processing in OLDI applications often share a common characteristic: They employ a multi-level tree-like software architecture where each query first goes to the aggregator and then goes to all or many index serving nodes (ISN). Since the aggregator needs to wait for all responses from the ISNs, the response time depends on the slowest ISN. Due to significant response time variation among the ISNs, a long latency at any ISN manifests as a slow query response at the aggregator level [18, 37, 71]. At each ISN, returning top-K results requires exhaustively computing the relevance score for each indexed document. This is time consuming and often unnecessary since most of the evaluated documents will not make to the ISN-level top-K results. Moreover, most of the results at ISNs are not used because only the top-K results from the aggregator will be sent back to the user. Clearly, these unnecessary computations, albeit useful for producing high-quality search results, lead to long query response time and power wastage.

Several techniques have been proposed to reduce request processing time at the ISN level. For example, dynamic pruning (or early termination) reduces the number of documents to be evaluated by skipping the documents that can not make to the top-K results [39,40]. Although the pruning methods reduce some unnecessary computations and improve the average query processing time at the ISN, the query processing time variation among ISNs is still high [65]. As a result, the improvement of the query response time at the aggregator level is limited. Another method is proposed to employ an aggregator timeout, which determines how long the aggregator waits for its ISNs before sending the results back to users [120]. The key idea is to trade off the result quality and the response time: the shorter the aggregator waits, the less ISN response it collects, which improves responsiveness but potentially degrades the quality due to missing of results from certain ISNs. The aggregator policies improve the response time subject to a quality constraint, but does not address the power consumption issue since the ISNs still perform the query processing for all queries with unnecessary power wastage. Further, [120] defines the quality as the number of responses received from the ISNs, but this does not capture the characteristic of a distributed search engine that different ISN responses may contribute to the final result differently due to ISN heterogeneity.

To satisfy quality and latency constraint in the search system, in chapter 6,we develop a cooperative aggregator-ISN policy that cuts out the slow ISN responses for fast response time and reduces energy consumption. First, at the aggregator, a "time budget" is assigned to the ISNs for request processing based on the expected quality level. Based on the budget, each ISN serves the request only if the predicted processing time is within the time budget, and disregards the request for energy saving otherwise. Furthermore, the aggregator may choose to re-send the query for full execution in case the response quality is not satisfactory. By doing so, we essentially reduce the ISN processing workload and aggregator level latency, while still meeting the quality constraint. Since the time budget is known to the ISNs, we propose to proactively put selected ISNs to sleep state to save power when the time budget cannot be met.

The rest of this thesis is organized as follows. Chapter 2 presents related work and motivation for our work. In chapter 3, we introduce thermal-aware power management scheme. In chapter 4, we propose a statistical model based latency constrained power management scheme. Chapter 5 focuses on latency-constrained power management technique for data center applications. We propose a system-wide quality and latency-aware scheduling scheme for distributed OLDI applications in chapter 6. Finally, chapter 7 concludes this thesis.

### Chapter 2

## **Related Work**

### 2.1 Power Management Techniques

Much work has been done on reducing power/energy consumption of computer systems. Based on the techniques, we can classify these works into three categories: (1) Dynamic Voltage Frequency Scaling (DVFS), (2) CPU sleep state and (3) Dynamic resource provisioning.

The first group utilize the DVFS to slow down the processor processing speed to reduce power/energy consumption. [50] minimizes energy usage by choosing the best combination of voltages for each task based on the task dependency. [107] applies genetic list scheduling algorithms (GLSA) to schedule and map tasks, considering the processor's power profile during a refined voltage section. Some works focus on differentiating program execution phases based on different CPU/memory-bound ratios and apply DVFS accordingly, because reducing processor frequency when the program is in the memory-bound phase will not affect performance. Specifically, [60] analyzes various global power management policies using per-core DVFS to maximize performance for a given power budget. In [61], they propose a runtime phase predictor that works cooperatively with DVFS. [35] regulates concurrency and changes processors/threads configuration as the program executes by hardware event driven profiling. In [78], Kuang et al. use DVFS for scheduling of networking applications. This scheme allocates frequencies to the pipeline stages statically and is not aimed at exploiting different traffic variations. However, two main physical limitations greatly affect the effectiveness of DVFS. First, the operating voltage approaches the transistor threshold voltage as technology advances, hence decreasing the room for voltage and frequency down-scaling [93]. Second, DVFS focuses on reducing the dynamic power consumption only, but static power consumption has become more dominant in today's multicore processors with more advanced manufacturing process [66,72]. These limitations drive the research communities to develop the power management technique without relying on DVFS.

In the second category, CPU sleep reduces static power when a core is idle by powering down different CPU components. Some works proposed to forced the core into deep sleep state when idle. In [76,91], the authors proposed to put the network devices into power saving mode during the idle period, and wake up the processor when a packet arrives. In [91,93], the CPU enters the deep sleep state when no pending task exists. In [100], the authors proposed "buffer and burst" to throttle the execution. It buffers the incoming tasks for a period of time, during which the devices will stay idle. With this approach, the incoming traffic is reshaped into small bursts of arrival; devices wake up to transmit a burst of packets, and then sleep until the next burst arrives. The intent is to provide sufficient time for devices to enter the power saving mode with lower power consumption. However, these approaches use server/device level sleep and are highly depends on the task arriving pattern. it only achieves good energy efficiency when the task interarrival time is long enough to compensate the long (10-100 seconds) sleep state transition overhead. On the other hand, some works proposed to select the best sleep state for each idle period. In [85], the sleep state the core will enter is determined through design space exploration with the simulator based on the previous task arrival pattern. [98] uses a stochastic model to predict the sleep state a core will enter based on the workload characteristic. However, these approaches does not consider the network and data center applications, where the length of the idle period mostly falls within 100  $\mu$ seconds, and can only enter shallow sleep state.

In the third category, observing that the resource demand may vary dynamically, either because of the traffic variation or workload characteristic, several works proposed to dynamically "turn-off" the hardware resources, such as the number of server and CPU cores, to reduce static power/energy consumption. In [48], the number of server staying responsive is dynamically determined based on analytical model and traffic demand. To achieve better energy efficiency in multicore processors, it is necessary to combine the dynamic resource provisioning with DVFS and sleep states. achieve fine grained power management. In [80], the authors developed an analytical model to determine how many cores can be turned off, and assign different frequency to the active cores with per-core DVFS. CARB [122] is proposed to use a C-State power management arbiter which dynamically turn off the core based on a feedback-based controller. However, the active cores still utilize the default Linux C-state governor which performs poorly under network and datacenter applications. Much is still not known about whether deferring execution and idle states are useful in the multicore processor. Our work takes a unified approach, modeling a general multicore system with many low-power sleep states having different characteristics. It seeks to jointly manage the configuration of the number of active cores and the choice of both the length of sleep period and which sleep state to enter, and more importantly, how these decisions should be made online with the existence of the QoS requirement.

#### 2.2 Thermal aware power management technique

Much work has been done in thermal-related research area. We classify related work in this section into two groups based on their approaches in thermal management design: (1) task migration, and (2) power reduction. Below, we introduce past work in each group.

#### 2.2.1 Task Migration

In a multi-core single-chip processor, the temperature of a core is not only determined by the power consumption of the software program running on it but also on its heat dissipation ability and the temperature of its neighbors. The basic concept of temperatureaware task migration is to dynamically move "hot" processes to cores with superior heat dissipation and/or cores surrounded by cooler neighbors while moving "cool" processes to cores with inferior heat dissipation and/or cores surrounded by hotter neighbors.

[49] proposes heat-and-run SMT thread assignment to increase processor-resource

utilization by co-scheduling threads that use complementary resources and heat-and-run CMP thread migration to migrate threads away from overheated cores to alternate cores. [30] investigates the trade-offs between temporal and spatial hot spot mitigation schemes and thermal time constants, workload variations and microprocessor power distribution. By leveraging spatial and temporal heat slacks through task migration, their thermal-aware scheduling schemes enable lowering of on-chip unit temperatures. In [96], they propose and study a thread migration method that maximizes performance under a temperature constraint, while minimizing the number of migrations and ensuring fairness between threads. While the above mentioned techniques are reactive approaches, it requires temperature monitor and may lack responsiveness based on the monitor period. Several works proposed predictive power migration to reduce spatial and temporal temperature difference by redistributing the heat generating locations. [119] propose a thermally-aware task migration policy called Predictive Dynamic Thermal Management (PDTM). When a task running on a processor is projected to exceed the temperature threshold, it will be moved to a processor that is predicted to be the coolest in the future. [17] proposed a light weight thermal predictor through band-limited property of the temperature frequency spectrum, and migrate the task among different CPU socket to create a thermal balance and reduce peak temperature. [79] built a novel predictive model based for the periodic tasks, and apply task migration to achieve thermal balancing under given temperature constraints.

#### 2.2.2 Power Reduction

While task migration focus on running hot processes on cooler core, the power reduction techniques try to decrease the heat generation and lower the peak temperature.

[27] is the first paper to investigate different thermal management techniques through DFS and DVFS. [110] applies control-theoretic techniques to control DVFS to avoid thermal emergencies while minimizing performance loss. [115] proposed a chip-level power control algorithm that is based on optimal control theory. Their algorithm can precisely control the power of a CMP chip through DVFS to the desired set point while maintaining per-core temperature below a specified threshold. In [116], they develop a thermal model called Matrix Model to derive core temperature and present a novel slack allocation algorithm using DVFS to minimize peak temperature. [52] proposes to use both DVFS and task-tocore allocation schemes to optimally increase the performance of multicore processors under thermal constraints. [82] proposes to optimize throughput by applying both per-core power gating and DVFS to power and thermal-constrained multicore processors. While the above techniques use DVFS to reduce the power and heat generation during the processing, it has same limitations as we discussed in the previous section. Several works proposed to throttle the CPU execution to reduce peak temperature. [19] proposed to idle cycle injection to stop-and-resume the CPU execution, during the stop period, the CPU cores will be power gated. [109] proposed to use formal feedback control and idle cycle injection to decrease thermal emergencies. However, these techniques does not consider the long state transition latency entering/exiting power gating states.

While all these works focus on reduce the heat generation, no work exploit the possibility of speed up the temperature falling in the period tasks. [79] proposed a stopand-go technique which force CPU core to be idle and cool down its temperature. However, it assumes that the core will consumes no power during idle, which might not be the case when the idle period is too short. Also, it does not consider the impact on packet latency. Our work focus on investigating the complex performance trade-offs among temperature, power consumption and latency in network applications with the force idle technique.

#### 2.3 Tail latency-constrained power management technique

Several techniques [69, 85, 86, 114] have been proposed to exploit latency slack by applying dynamic voltage and frequency scaling (VFS). Pegasus [86] takes a cluster-level feedback-based approach by monitoring tail latency periodically and adjusting frequency every few seconds to keep tail latency within a given bound. Pegasus is only able to exploit latency slack during low utilization. Building on this, TimeTrader [114] is able to exploit the latency slack at the request-level, rather than at the cluster-level. Observing that there exists not only server but also network latency slack, TimeTrader can save energy even during high utilization exploiting network slack and and identifying sub-critical requests to slow down using VFS. Rubik [69] proposed to save power by dynamically adjusting the frequency at request arrival and departure events. By observing the number of queued requests, Rubik pick a minimum frequency that will satisfy the tail latency constraint of every request in the system. All these prior techniques focus on VFS policies, and do not rely on sleep states. However, with technology scaling, the dynamic range of frequency scaling has decrease, along with static power consumption growing dominant [72]. Recognizing this, SleepScale [85] combines a history-based predictive VFS scheme with optimal C-state selection (based on runtime simulation). Unlike the aforementioned techniques, SleepScale cannot close the latency slack as VFS settings are determined by coarse-grain prediction of future workloads. As data center traffic tend to have short-term variability, the frequent mispredictions can violate the tail latency target.

Other works utilize sleep states only to achieve power savings [91, 93]. Power-Nap [91] proposed a server level fast sleep transition technique and put the server into a deep sleep state as soon as the server becomes idle, taking advantage of full-system millisecond-level idleness. Dreamweaver [93] extends PowerNap by putting entire multicore processors into deep sleep state by aligning the idle periods of cores through job preemption. While achieving good power saving, the latency overhead introduced by aligning idle periods and job preemption, results in as much as 3x tail latency increase for 40% power savings. Unfortunately, as server core count increases, full-system idleness disappears, limiting the effectiveness of Dreamweaver. While proposing sleep state techniques in chapter 4.3 and 3, they are unresponsive to short-term variability due to the fact that statistical queuing models is meaningful only when the traffic is stable for a long period of time. To address these issue, we propose a dynamic sleep scheme to determine the sleep period at the request level. Furthermore, with detail performance analysis on these state-of-the-art techniques, we are the first to illustrate that state transition overhead is the major source of energy inefficiency, and proposed a technique to combine VFS, sleep state and request redirection to minimize energy consumption with the tail latency constraint.

#### 2.4 Quality and latency aware power management technique

In the previous section, several techniques are proposed to reduce the energy consumption by exploiting the latency slack. They does not focus on reducing the tail latency and considering the result quality in a system-wide manner. Several works proposed to use adaptive parallelism [54, 65] and computation sprinting [57, 124] to reduce query latency. In [65], the query processing will be perform in parallel when it is predicted to have long processing time. In [54], the degree of parallelism of query processing is dynamically increasing. The longer a request executes, the more parallelism it adds, hence reduce the latency of the long running requests. In [57], authors proposed to boost the operating frequency when a query identified as long query, which increase the computation power and reduce the query latency. Although these techniques improve query latency, they require additional resources. The trade-off with other system level performances, such as power consumption, is yet unclear.

Other work proposed to trade the query quality for latency reduction. Servers in the web search system often employ dynamic pruning to early terminate the postings list traversing of a query and to avoid scoring the postings for the documents that unlikely make the top-k retrieved set [39,40]. Early termination is an example that reduce latency by trading the completeness of query response [40]. [55] quantifies the relationship of quality and latency at ISNs, and trades quality for latency under heavy loads. For the aggregator level latency reduction, Yun, et.al [120] observed the latency heterogeneity among leaf servers and proposed an aggregator policy where results are sent back to users without waiting all servers' responses. By categorizing queries' behaviour among servers, the aggregator will adjust its waiting period to achieve a good latency-quality tradeoff. While being effective on reducing tail latency, it did not address the system-wide energy efficiency which is the major performance matrix in modern search system design. While the above mentioned works focusing on quality-latency trade-off, no work has been done on simultaneously considering quality, latency and energy efficiency. In [42] exploited the quality-latency relationship and proposed a energy efficient scheduler to trade the quality for energy consumption. However, this work neither addresses the latency constraint commonly exists in the datacenter, nor provides system-wide performance analysis. To address this issue, we propose a quality and latency aware power management technique which minimizes the system-wide energy consumption while satisfying both quality and latency constraint.

# Chapter 3

# Power and thermal Management on Network Applications

# 3.1 Introduction

In this chapter, we address the thermal management issue for network packet processing. We aim at optimizing power consumption and throughput under given thermal constraint by appropriately applying per-core smart sleep. The intent is to reshape packet processing pattern and force longer CPU core idle periods to create opportunities for a CPU core to enter deeper C-states and cool down the core faster. Also, we limit the length of busy periods which prevents the core from overheating. We name our technique as a vacation scheme denoting that the server (core) has taken a vacation for a period, and the arriving packets must wait in a buffer to be processed later. This enables the core to enter into a deep sleep mode. By adopting our proposed vacation schemes, we can reduce the heat generation, power consumption, and allow the temperature to drop during idle (vacation) periods. This will avoid the peak temperature exceeding the thermal constraint. We design two vacation schemes (fixed and dynamic) and provide performance analysis to show that the dynamic vacation scheme gives better temperature and power consumption with acceptable latency overhead.

Then, to understand the effectiveness of the vacation scheme, we develop the thermal, power and latency models for our scheme in the multicore processor by adopting the vacation queuing theory [83, 113]. Unlike single core processor, the thermal behavior of multicore processor is more complicated because of the temperature interaction between cores. Through the use of our models, we can select proper limits for vacation and busy period with a given traffic load.

Lastly, we apply our vacation scheme with the thermal constraint in the multicore processor. With our proposed thermal model, we can properly limit the length of the busy period and avoid thermal emergency. The result shows that, compared with the existing scheme, our vacation scheme can effectively satisfy the thermal constraint while sustaining higher traffic load. Also, through proper vacation period selection, the power consumption can be reduced. Furthermore, by taking the thermal and C-state characteristics of the multicore architecture into account, we propose heterogeneous load distribution, which effectively redistributes the load and heat generation in the spatial domain, and creates more opportunities for power saving under the thermal constraint. To the best of our knowledge, we are the first to develop a vacation scheme considering all temperature constraint, power consumption and latency for packet processing on a multicore server. This chapter makes the following contributions.

- We propose and implement a vacation scheme on top of the idle states (C-states) provided by the OS and observe the packet processing characteristics.

- We derive analytical models for power, thermal and latency characteristics for the vacation scheme based on the vacation queuing theory.

- We explore the effectiveness of our vacation scheme under the thermal constraint.

- We design and implement heterogeneous load distribution scheme, and evaluate our on-line algorithm experimentally.

# **3.2** Packet Processing on a Multicore Server

This section describes the high-level network application characteristic, and relates it to the power and thermal behavior while processing on a multicore processor.

#### 3.2.1 Packet Processing Characteristics

The "run-to-finish" applications always consume active power while running, and the temperature simply rises to saturation point until it stabilizes. But network packet processing exhibits an ON/OFF pattern [23,77], where the CPU core temperature rises and consumes active power during the ON period, (also known as busy period) when the packet is being processed. During the OFF period when no packet arrives, the CPU still runs and consumes idle power which is less than the active power. The OFF period between packet processing provides the opportunities to do power and thermal management. Also, the length of ON/OFF period is not deterministic, and depends on the random packet arrival

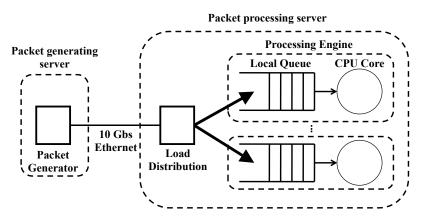

Figure 3.1: The experiment platform

and service rates.

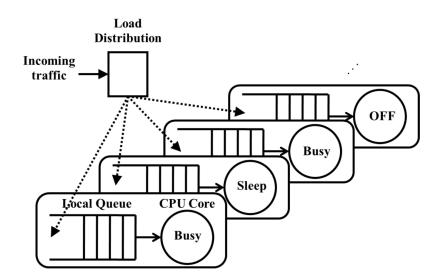

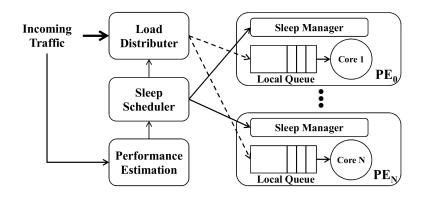

We start by considering how packets arrive and are served. Figure 3.1 shows the packet processing system we use in this chapter; our system consists of a packet generating server and a packet processing server. The system consists of many processing engines (PEs); each PE has a local queue and a CPU core. The processing server receives packets from the packet generator through Ethernet link. Once the packet arrives at the receiving server, it will first go through NIC and TCP stack, and will be passed to the socket. Finally, the application will fetch the packets through *sock\_read* system call and process the packets. The incoming packets are distributed among PEs through the load distributor. The packets arriving at each PE are stored in its local queue, and the CPU core will fetch and process a packet in the queue in an FIFO fashion driving the CPU to the active state. On the other hand, while the CPU core finds no packet in the queue, it will become idle (entering idle state) until the next packet arrives and is stored in the queue.

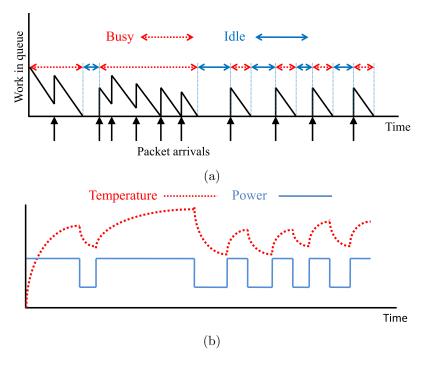

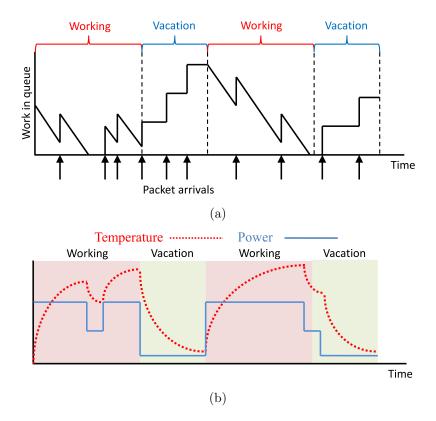

Figure 3.2: (a) Packets processing pattern. (b) Power consumption and thermal behavior during packet processing.

#### 3.2.2 Power Consumption and Thermal Behavior

Figure 3.2(a) depicts the packet processing pattern of a PE in the multicore packet processing server [31]. The solid lines represent the amount of work in PE queue with time. The solid up arrows under the x-axis represent the packet arrivals to the PE, which cause the step increase of the work in the queue. Although the amount of work could be discrete, without loss of generality, we use slant line representing the packet being processed by a processor with the slope representing the service rate. The busy and idle periods are shown in the top of the figure. Clearly, the busy and idle periods during packet processing are randomly distributed with the expected lengths of  $\frac{1}{(\mu-\lambda)}$  and  $\frac{1}{\lambda}$ , where,  $\lambda$  is the packet arrival rate and  $\mu$  is the service rate of a PE. Figure 3.2(b) shows power consumption and thermal behavior corresponding to the packet arrival pattern of figure 3.2(a). When PE is active, it consumes high power, and drops to a lower level when idle. The temperature trace is like the shape of sawtooth, which is caused by the continuous busy and idle periods. The longer the busy period, the higher the temperature will rise until a steady state. On the contrary, the longer the idle period, the lower the temperature will fall. Also, the power consumption during the busy and idle periods will decide the steady state temperature. Furthermore, due to the heat flows between CPU cores in a multicore architecture, their temperature behavior will interact with each other. The complicated thermal behaviors pose a major challenge for the temperature management.

#### 3.2.3 Problem with Existing Idle State Power Management Scheme

As we mentioned previously, the CPU core will become idle when it finds no work to do, and still consumes power. Modern CPUs provide succession of per-core idle states (called sleep states or C-states), where different CPU core components are turned off. States are named numerically from  $C_0$  to  $C_N$ , where  $C_0$  represents the normal operating mode. As the C-state number increases, the more components in the CPU core are turned off, and the heat generation and power consumption reduces with the increased state transition time. Because of the state transition overhead, it only makes sense to enter a C-state if inactive time is beyond certain threshold, called energy-breakeven-time (EBT), and this threshold increases as the C-state gets deeper.

Because of the EBT, the length of the idle period should be known beforehand to select the most energy efficient C-state a core should enter. In the Linux kernel, the prediction-based sleep-state selection algorithm, called menu idle governor [3], is used for this purpose. It uses a history-based idle length predictor. If the variation among the

Figure 3.3: Power consumption under different scenarios.

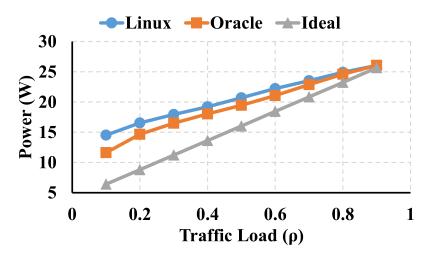

past idle intervals is small, the average of past idle intervals will be used as the prediction; otherwise the next scheduled OS timer event will be used as the prediction. However, due to the *unpredictable nature of the request arrival*, the menu governor or any history based idle period predictor is not very useful with the non-deterministic execution pattern [38], where over-prediction (predicted idle period is shorter than the actual one) will cause energy inefficiencies and under-prediction will cause unnecessary latency increase and power wastage due to the large state transition overhead.

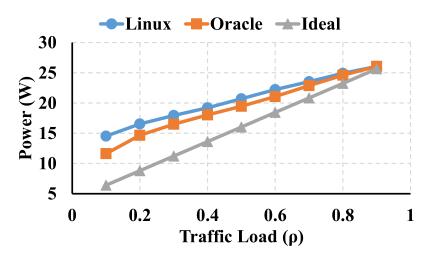

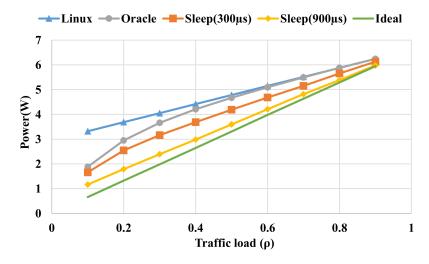

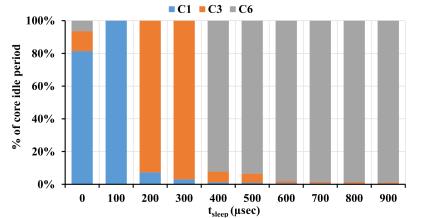

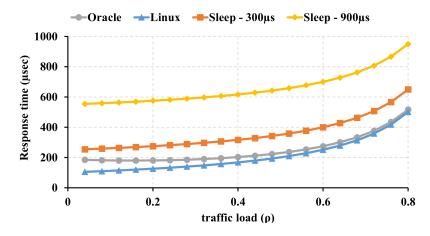

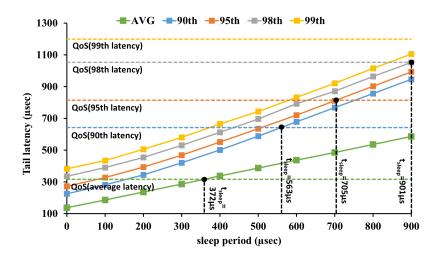

Besides the difficulties for the idle period prediction, another issue for idle power management lies in the *frequent and random* ON/OFF pattern of network and datacenter applications, which greatly affect the effectiveness of using C-states. Fig. 3.3 gives the experimental results of the power consumption of a network application under different traffic loads. There are three scenarios in Fig. 3.3: *"Linux"* represents the power consumption of using Linux prediction-based C-state selection algorithms (menu idle governor), and the results are measured using on-chip energy sensors; *"Oracle"* represents the case when all idle durations are known beforehand so the core can enter the most energy efficient C-state with no prediction error, and "Ideal" gives the power consumption with perfect energy proportionality, where all CPU cores go into deepest sleep state during all of its idle time with zero transition overhead. One should notice that the Ideal scheme serves as a theoretical lower bound of the power consumption that can be achieved. In Fig. 3.3, we can see that when the system has highly activity ( $\rho > 0.7$ ), the difference between Linux and Oracle cases are small, because the idle period is mostly short, which make shallowest C-state the most energy efficient. However, due to the inaccurate prediction, the Linux prediction algorithm becomes less effective when the traffic activity decreases, 16% and 25% more power consumption than the Oracle case at = 0.4 and 0.1, respectively. Furthermore, despite the perfect idle state selection of the Oracle case, the existence of short idle periods will prevent the system from going into deep C-state. For this reason, even with low activity, the system operates far from being energy proportional - i.e., consumes power proportionally to its utilization, as shown in the Ideal case. Moreover, the high idle power consumption in the existing idle power management scheme also lead to poor thermal behavior, since the degree of cool down during the idle period is dependent on the idle period power consumption.

### 3.3 Vacation Thermal and Power Management Schemes

In the original system, servers are busy processing packets as long as there are packets in the queue, and become idle when the queue is empty. Although servers spend most of their time idle, conventional power management techniques are unable to exploit these brief idle periods. As a result, the CPU cores still consume high power during these idle periods and generate heat. To address this issue, we propose an approach to reshape the packet processing pattern that creates longer idle period and allows the processors to enter low-power state which consumes less power and reduces heat generation. We call this approach vacation.

In this section, we first propose a vacation scheme with the fixed active period, where the core state changes only when the timer expires. Then, we propose a dynamic vacation scheme, where the state changes dynamically with different events.

#### 3.3.1 Fixed Vacation Scheme

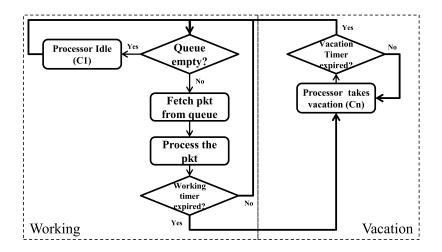

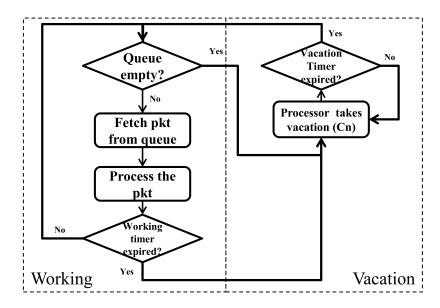

Figure 3.4 shows the flow chart of the vacation approach. We define two states that CPU can be: *working* and *vacation*. In the working state, the core works as in the original scheme, but only goes into the shallowest sleep state (C1) when idle. A working timer,  $t_{work}$ , is set when the core enters working state, and the core will transit to vacation state when this timer expires. The purpose of the working timer is to prevent the processor from

Figure 3.4: Flowchart of the fixed vacation scheme.

being active for too long and exceeding the given temperature threshold. In the sleep state, the server takes a vacation for time  $t_{vac}$ , when the server buffers all the incoming packets in the queue and enters deep sleep state. After  $t_{vac}$  expires, the server wakes up and goes back to the working state, and continues serving packets in the queue. The approach is similar to the "buffer and burst approach", described in [100], except that the details of the sleep approach here are different. In buffer and burst approach, the incoming packets are buffered during the buffer period, and these buffered packets are transmitted only in the burst period. We process those packets if they arrive during the working period  $t_{work}$ . Also, the buffer and burst approach did not include any thermal consideration like temperature threshold. Finally, we implement the system in real multicore system instead of verifying through simulation [100].

In the fixed vacation scheme, the incoming traffic from processors perspective, is reshaped into short bursts of arrival. CPU cores wake up to process bursts of packets, and then sleep for a long time. The intent is to provide sufficient time for processors to enter the deep sleep states (C3 and C6) with lower power consumption, and faster temperature cool down. Figure 3.5a shows the amount of work in the queue while time advances with the fixed vacation scheme. Compared with figure 3.2a, we can see that the amount of work increases due to the buffering during the vacation. In the working state, instead of many short packet processing time periods, it is now a long busy period.

The effectiveness of the vacation scheme relies on the capability of CPU core to cut down the heat generation and power consumption when it is idle [75]. Although the idle periods between packet processing provides natural thermal modulation, the idle period is

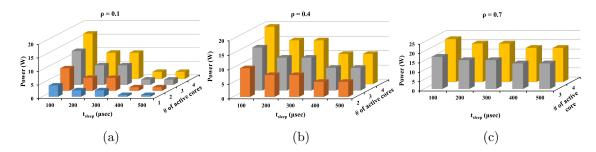

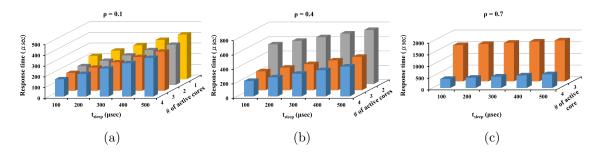

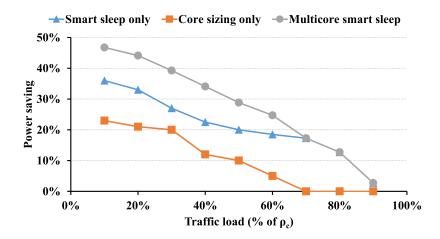

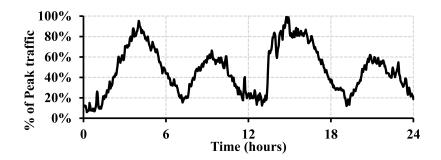

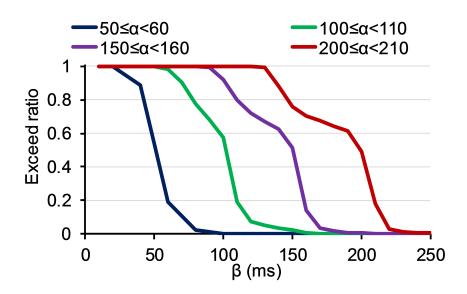

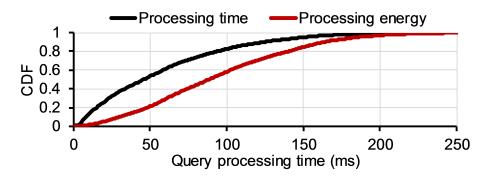

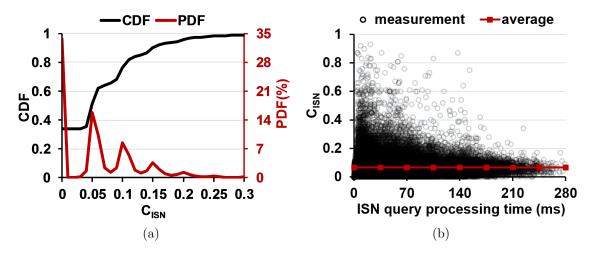

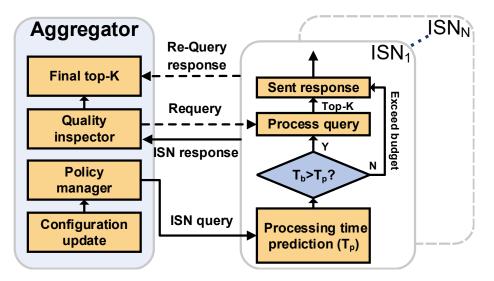

Figure 3.5: (a) Packets processing pattern. (b) Power consumption and thermal behavior under fixed vacation scheme.