## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

### **Title**

Moneta: A Storage System for Fast Non-Volatile Memories

### **Permalink**

https://escholarship.org/uc/item/06s0k62k

### **Author**

Caulfield, Adrian Michael

## **Publication Date**

2013

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Moneta: A Storage System for Fast Non-Volatile Memories

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Adrian Michael Caulfield

### Committee in charge:

Professor Steven Swanson, Chair Professor Rajesh Gupta Professor Paul Siegel Professor Dean Tullsen Professor Geoff Voelker

Copyright

Adrian Michael Caulfield, 2013

All rights reserved.

| The Dissertation of Adrian Michael Caulfield is approved and is accept-   |

|---------------------------------------------------------------------------|

| able in quality and form for publication on microfilm and electronically: |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

|                                                                           |

| Chair                                                                     |

University of California, San Diego 2013

## TABLE OF CONTENTS

| Signature               | Page                                                                                | iii                        |

|-------------------------|-------------------------------------------------------------------------------------|----------------------------|

| Table of C              | Contents                                                                            | iv                         |

| List of Fig             | gures                                                                               | vii                        |

| List of Tab             | oles                                                                                | ix                         |

| Acknowle                | dgements                                                                            | X                          |

| Vita                    | x                                                                                   | iii                        |

| Abstract o              | of the Dissertation                                                                 | ΧV                         |

| Chapter 1               | Introduction                                                                        | 1                          |

| 2.2 N<br>2.3 F<br>2.4 S | Hard Disks  NAND Flash Memory  Phase Change RAM  Spin-Torque MRAM and the Memristor | 8<br>9<br>11<br>12         |

| Chapter 3               |                                                                                     | 17                         |

| 3.1 T                   | The Moneta prototype                                                                | 18<br>19<br>21             |

| 3.3 S<br>3<br>3         | Software Optimizations                                                              | 22<br>24<br>24<br>27<br>28 |

| 3.4 T<br>3<br>3<br>3    | Funing the Moneta hardware                                                          | 29<br>29<br>30<br>31       |

| 3                       | Evaluation                                                                          | 34<br>36<br>37             |

| 3.6 R                   | 11                                                                                  | 40                         |

| 3.7     | Summa   | ary                                      | 42  |

|---------|---------|------------------------------------------|-----|

| Chapter | 4 Use   | er Space Access                          | 44  |

| 4.1     | System  | overview                                 | 46  |

|         | 4.1.1   | Channels                                 | 48  |

|         | 4.1.2   | The user space driver                    | 50  |

|         | 4.1.3   | The file system                          | 50  |

| 4.2     | Related | d Work                                   | 52  |

|         | 4.2.1   | Virtualization                           | 52  |

|         | 4.2.2   | User space IO                            | 54  |

|         | 4.2.3   | Protection and translation               | 55  |

| 4.3     | Moneta  | a-D Implementation                       | 56  |

|         | 4.3.1   | The baseline Moneta hardware             | 58  |

|         | 4.3.2   | Virtual channels                         | 60  |

|         | 4.3.3   | Translation and protection               | 62  |

|         | 4.3.4   | Completing requests and reporting errors | 68  |

| 4.4     | Results | S                                        | 72  |

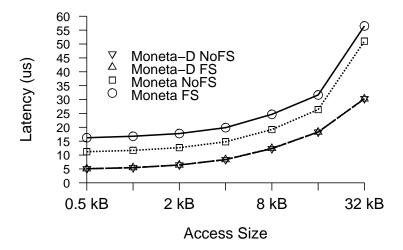

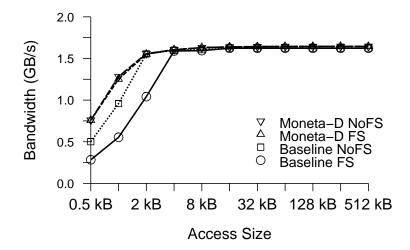

|         | 4.4.1   | Operation latency                        | 72  |

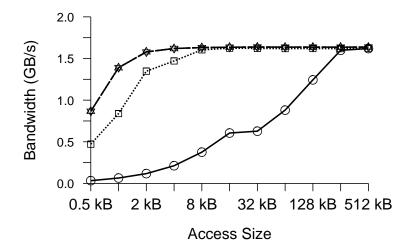

|         | 4.4.2   | Raw bandwidth                            | 73  |

|         | 4.4.3   | Application level performance            | 76  |

|         | 4.4.4   | Asynchronous IO                          | 79  |

| 4.5     | Summa   | ary                                      | 80  |

| Chapter | 5 Dis   | tributed Storage                         | 83  |

| 5.1     |         | tion                                     | 85  |

|         | 5.1.1   | Storage overheads                        | 86  |

|         | 5.1.2   | The Impact of Fast SSDs                  | 87  |

| 5.2     | QuickS  | SAN                                      | 89  |

|         | 5.2.1   | QuickSAN Overview                        | 89  |

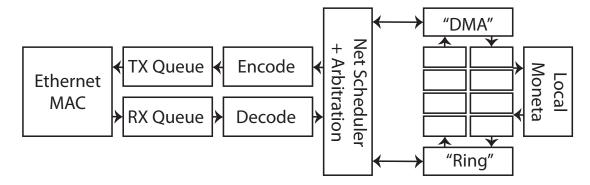

|         | 5.2.2   | The QuickSAN SSD and NIC                 | 91  |

|         | 5.2.3   | QuickSAN software                        | 95  |

| 5.3     | Related |                                          | 96  |

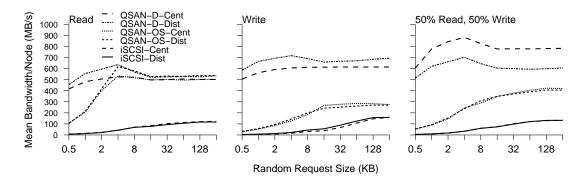

| 5.4     | Results | S                                        | 98  |

|         | 5.4.1   | Configurations                           | 98  |

|         | 5.4.2   | Latency                                  | 99  |

|         | 5.4.3   | Bandwidth                                | 101 |

|         | 5.4.4   | Scaling                                  | 102 |

|         | 5.4.5   | Replication                              | 103 |

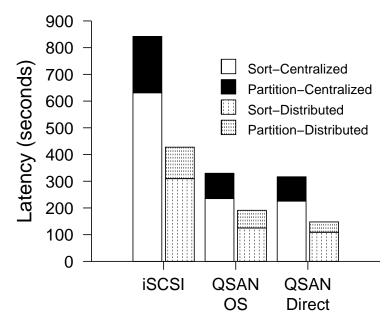

|         | 5.4.6   | Sorting on QuickSAN                      | 104 |

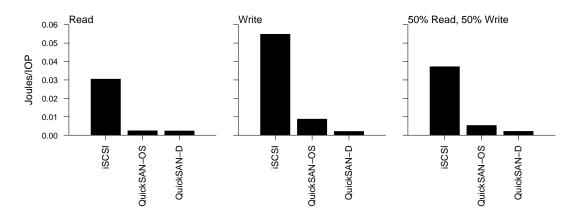

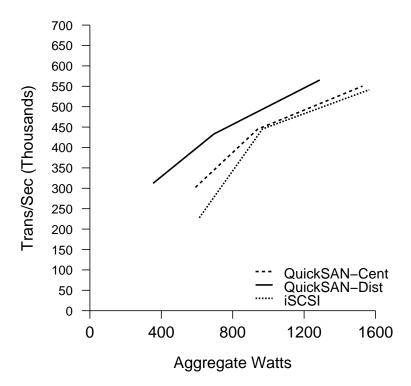

|         | 5.4.7   | Energy efficiency                        | 107 |

|         | 5.4.8   | Workload consolidation                   | 107 |

| 5.5     |         | ary                                      | 109 |

| Chapter     | 6 Su   | mmary                           | 111 |

|-------------|--------|---------------------------------|-----|

| Appendi     | x A Mo | oneta Hardware                  | 117 |

| <b>A.</b> 1 | Monet  | a Overview                      | 117 |

|             | A.1.1  | Registers                       | 119 |

|             | A.1.2  | DMA                             | 122 |

| A.2         | Reque  | st Pipeline                     | 123 |

|             | A.2.1  | Virtualization                  | 124 |

|             | A.2.2  | Protection                      | 124 |

|             | A.2.3  | Request Queues                  | 125 |

|             | A.2.4  | Transfer Buffers and Scheduler  | 126 |

| A.3         | Host-I | nterface                        | 126 |

|             | A.3.1  | Completing Requests in Hardware | 127 |

| A.4         |        | Network                         | 127 |

| A.5         | _      | ry Controllers                  | 129 |

|             | A.5.1  | Non-Volatile Memory Emulation   | 129 |

| A.6         | Ethern | et Network                      | 131 |

| A.7         |        | ary                             | 133 |

| Rihliogr    | anhv   |                                 | 136 |

## LIST OF FIGURES

| Figure 2.1.  | Technology Software Overheads                           | 13 |

|--------------|---------------------------------------------------------|----|

| Figure 2.2.  | Software Contribution to Latency                        | 14 |

| Figure 3.1.  | The Moneta System                                       | 19 |

| Figure 3.2.  | Moneta Bandwidth Measurements                           | 23 |

| Figure 3.3.  | Latency Savings from Software Optimizations             | 26 |

| Figure 3.4.  | Managing Long-latency Non-volatile Memories             | 30 |

| Figure 3.5.  | Storage Array Performance Comparison                    | 35 |

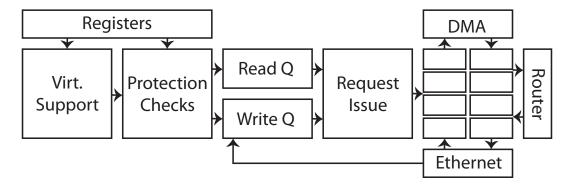

| Figure 4.1.  | System Overview                                         | 47 |

| Figure 4.2.  | Controller Architecture                                 | 58 |

| Figure 4.3.  | Component Latencies                                     | 59 |

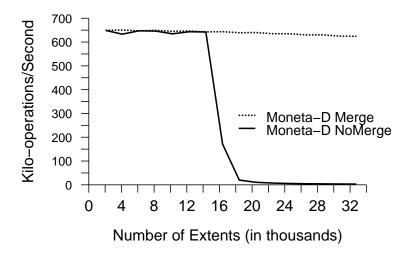

| Figure 4.4.  | Extent Merging to Alleviate Permission Table Contention | 67 |

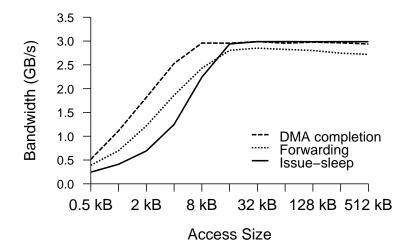

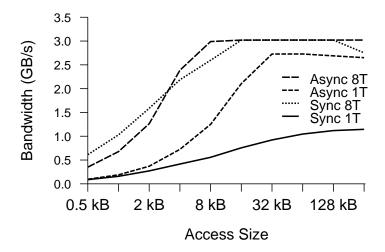

| Figure 4.5.  | Completion Technique Bandwidth                          | 70 |

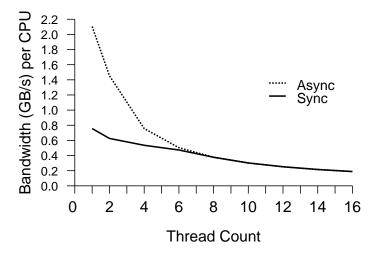

| Figure 4.6.  | Completion Technique Efficiency                         | 71 |

| Figure 4.7.  | Write Access Latency                                    | 72 |

| Figure 4.8.  | File System Performance - Reads                         | 75 |

| Figure 4.9.  | File System Performance - Writes                        | 75 |

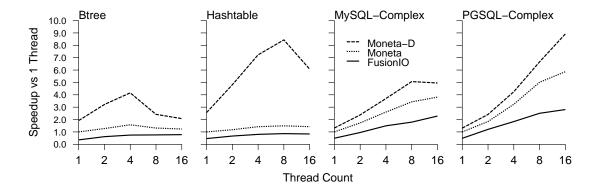

| Figure 4.10. | Workload Scalability                                    | 78 |

| Figure 4.11. | Asynchronous Bandwidth                                  | 79 |

| Figure 4.12. | Asynchronous CPU Efficiency                             | 80 |

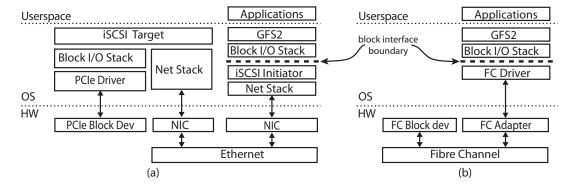

| Figure 5.1.  | Existing SAN Architectures                              | 87 |

| Figure 5.2.  | Shifting Bottlenecks                                    | 88 |

| Figure 5.3.  | OuickSAN Configurations                                 | 90 |

| Figure 5.4.  | QuickSAN's Internal Architecture       | 92  |

|--------------|----------------------------------------|-----|

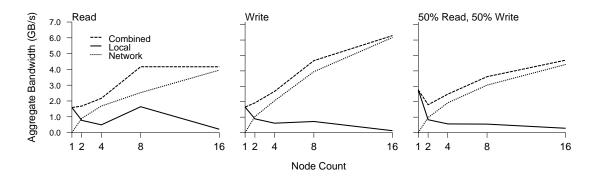

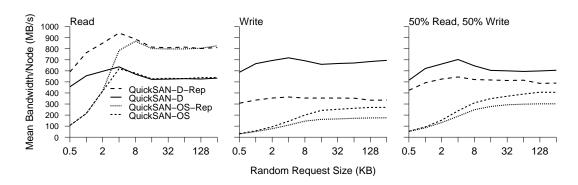

| Figure 5.5.  | QuickSAN Bandwidth                     | 100 |

| Figure 5.6.  | QuickSAN Bandwidth Scaling             | 100 |

| Figure 5.7.  | The Impact of Replication on Bandwidth | 100 |

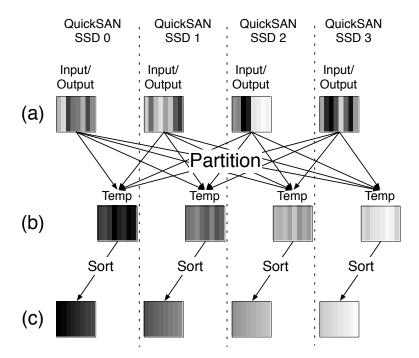

| Figure 5.8.  | Sorting on QuickSAN                    | 103 |

| Figure 5.9.  | Sorting on QuickSAN                    | 106 |

| Figure 5.10. | QuickSAN Energy Efficiency             | 106 |

| Figure 5.11. | Application-level Efficiency           | 108 |

| Figure A.1.  | The Moneta System                      | 118 |

| Figure A.2.  | Request Pipeline Components            | 123 |

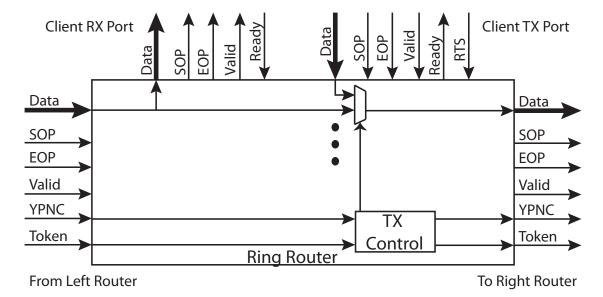

| Figure A.3.  | Router Component                       | 128 |

| Figure A 4   | Network Interface                      | 131 |

## LIST OF TABLES

| Table 3.1. | Latency Savings from Software Optimizations | 25  |

|------------|---------------------------------------------|-----|

| Table 3.2. | Moneta Power Model                          | 34  |

| Table 3.3. | Storage Arrays                              | 35  |

| Table 3.4. | IO Operation Performance                    | 36  |

| Table 3.5. | Benchmarks and Applications                 | 38  |

| Table 3.6. | Workload Performance                        | 39  |

| Table 4.1. | Moneta-D Control Interfaces                 | 57  |

| Table 4.2. | Component Latencies                         | 64  |

| Table 4.3. | Benchmarks and Applications                 | 74  |

| Table 4.4. | Workload Performance                        | 77  |

| Table 5.1. | Software and Block Transport Latencies      | 85  |

| Table 5.2. | QuickSAN Latency                            | 99  |

| Table A.1. | Moneta PCIe Registers - Channel 0           | 119 |

| Table A.2. | Moneta PCIe Registers - Untrusted Channels  | 120 |

| Table A.3. | Packet Format                               | 133 |

#### **ACKNOWLEDGEMENTS**

I would like to acknowledge Professor Steven Swanson for his support as the chair of my committee. Throughout my entire graduate school experience, including many papers and long nights, his guidance and encouragement has brought the best out of me and helped me to achieve my goals.

I would also like to acknowledge the other members of the Non-volatile Systems Lab, without whom my research would have no doubt taken fives times as long. Special thanks to Todor Mollov, Joel Coburn, Ameen Akel, Arup De, Alex Eisner, and Trevor Bunker for their extensive help with the Moneta hardware.

Thanks also to Professor Goeff Voelker for his guidance and support on several of the key works that make up this dissertation. The rest of my committee also provided valueable comments and feedback, for which I am greatful.

I want to thank my parents and brother for their support and advice. They always made sure I had everything I needed throughout all of my schooling.

My wonderful wife, Laura Caulfield, has provided immesurable support and encouragement during our shared adventure through graduate school.

Chapters 1 and 2 and Appendix A contain material from "Understanding the Impact of Emerging Non-Volatile Memories on High-Performance, IO-Intensive Computing", by Adrian M. Caulfield, Joel Coburn, Todor Mollov, Arup De, Ameen Akel, Jiahua He, Arun Jagatheesan, Rajesh K. Gupta, Allan Snavely, and Steven Swanson, which appears in *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*, (SC '10). The dissertation author was the primary investigator and author of this paper. The material in Chapters 1 and 2 and Appendix A is copyright ©2010 by the IEEE.

Chapters 1, 2, and 5 and Appendix A contain material from "QuickSAN: A Storage Area Network for Fast, Distributed, Solid State Disks", by Adrian M. Caulfield

and Steven Swanson, which appears in *ISCA '13: Proceeding of the 40th Annual International Symposium on Computer Architecture.* The dissertation author was the primary investigator and author of this paper. The material in Chapters 1, 2, and 5, and Appendix A is copyright ©2013 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

Chapters 1, 2, and 4 and Appendix A contain material from "Providing Safe, User Space Access to Fast, Solid State Disks", by Adrian M. Caulfield, Todor I. Mollov, Louis Eisner, Arup De, Joel Coburn, and Steven Swanson, which appears in *ASPLOS '12: Proceedings of the 17th International Conference on Architectural Support for Programming Languages and Operating Systems*. The dissertation author was the primary investigator and author of this paper. The material in Chapters 1, 2, and 4 and Appendix A is copyright ©2012 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or

permissions@acm.org.

Chapters 1, 2, and 3, and Appendix A contain material from "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", by Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson, which appears in *Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture*, (MICRO '43). The dissertation author was the primary investigator and author of this paper. The material in Chapters 1, 2, and 3 and Appendix 3 is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

#### VITA

| 2007      | Bachelor of Arts, University of Washington                   |

|-----------|--------------------------------------------------------------|

| 2007–2013 | Research Assistant, University of California, San Diego      |

| 2010      | Master of Science, University of California, San Diego       |

| 2011      | Candidate of Philosophy, University of California, San Diego |

| 2013      | Doctor of Philosophy, University of California, San Diego    |

#### **PUBLICATIONS**

Adrian M. Caulfield and Steven Swanson. "QuickSAN: A Storage Area Network for Fast, Distributed, Solid State Disks", In *ISCA '13: Proceeding of the 40th Annual International Symposium on Computer Architecture*, June 2013.

Adrian M. Caulfield, Todor I. Mollov, Louis Eisner, Arup De, Joel Coburn, and Steven Swanson. "Providing Safe, User Space Access to Fast, Solid State Disks", In *Proceeding of the 17th International Conference on Architectural Support for Programming Languages and Operating Systems*, March 2012.

Ameen Akel, Adrian M. Caulfield, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson. "Onyx: A Prototype Phase-Change Memory Storage Array", In *Proceedings of the 3rd USENIX conference on Hot topics in storage and file systems*, HotStorage'11, June 2011.

Joel Coburn, Adrian M. Caulfield, Ameen Akel, Laura M. Grupp, Rajesh K. Gupta, Ranjit Jhala, and Steven Swanson. "NV-Heaps: Making Persistent Objects Fast and Safe with Next-Generation, Non-Volatile Memories", In *ASPLOS '11: Proceeding of the 16th International Conference on Architectural Support for Programming Languages and Operating Systems*, March 2011.

Adrian M. Caulfield, Joel Coburn, Todor Mollov, Arup De, Ameen Akel, Jiahua He, Arun Jagatheesan, Rajesh K. Gupta, Allan Snavely, and Steven Swanson. "Understanding the Impact of Emerging Non-Volatile Memories on High-Performance, IO-Intensive Computing", In *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*, SC '10, 2010.

Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson. "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", In *Proceedings of the 2010 43rd Annual IEEE/ACM*

International Symposium on Microarchitecture, MICRO '43, 2010.

Sungjin Lee, Kermin Fleming, Jihoon Park, Keonsoo Ha, Adrian M. Caulfield, Steven Swanson, Arvind, and Jihong Kim. "BlueSSD: An Open Platform for Cross-layer Experiments for NAND Flash-based SSDs", In *Proceedings of the 2010 Workshop on Architectural Research Prototyping*, 2010.

Laura M. Grupp and Adrian M. Caulfield and Joel Coburn and John Davis and Steven Swanson. "Beyond the Datasheet: Using Test Beds to Probe Non-Volatile Memories' Dark Secrets", In *IEEE Globecom 2010 Workshop on Application of Communication Theory to Emerging Memory Technologies (ACTEMT 2010)*, 2010.

Adrian M. Caulfield, Laura M. Grupp, and Steven Swanson. "Gordon: An Improved Architecture for Data-Intensive Applications", *IEEE Micro*, 30(1):121–130, 2010.

Adrian M. Caulfield, Laura M. Grupp, and Steven Swanson. "Gordon: Using Flash Memory to Build Fast, Power-Efficient Clusters for Data-Intensive Applications", In ASPLOS '09: Proceeding of the 14th International Conference on Architectural Support for Programming Languages and Operating Systems, 2009.

Laura M. Grupp, Adrian M. Caulfield, Joel Coburn, Steven Swanson, Eitan Yaakobi, Paul H. Siegel, and Jack K. Wolf. "Characterizing Flash Memory: Anomalies, Observations, and Applications", In *MICRO 42: Proceedings of the 42nd Annual IEEE/ACM International Symposium on Microarchitecture*, December 2009.

### ABSTRACT OF THE DISSERTATION

Moneta: A Storage System for Fast Non-Volatile Memories

by

### Adrian Michael Caulfield

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2013

Professor Steven Swanson, Chair

Over the last few decades, storage performance has stagnated in comparison to the performance of the rest of the system. Over this time, system designers have continued to add additional layers of abstraction and optimization to the storage hierarchy in an attempt to hide and optimize accesses to high-latency storage. Emerging non-volatile memory technologies promise many orders of magnitude increases in storage array performance compared to existing storage technologies, but the thick layers of software built on the assumption that storage is slow risk squandering the full potential of these new devices.

XV

This dissertation describes a prototype high-performance storage array, called Moneta, designed for next-generation non-volatile memories, such as phase-change memory, that offer near-DRAM performance. Moneta allows us to explore the architecture of the storage array, the impact of software overheads on performance, the effects of non-volatile technology parameters on bandwidth and latency, and the ultimate benefit to applications.

Using Moneta, we show that system software can be optimized to expose fast storage with minimal latency overheads. Moneta reduces software overheads by 62% for 4 KB operations through the operating system, speeding up a range of file system, paging, and database workloads by up to  $8.7\times$  compared to flash-based SSDs.

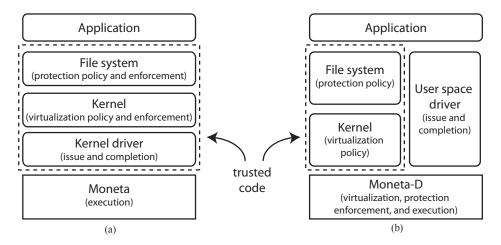

Moneta-Direct extends Moneta by refactoring trusted code throughout the IO stack. This allows applications to bypass the operating system and file system entirely on most accesses, further reducing IO overheads by 58% and increasing throughput by 7.6×. Moneta-Direct demonstrates the importance of redesigning the IO stack to work efficiently with emerging fast non-volatile storage.

Finally, a further modification to Moneta allows us to explore the performance of distributed storage networks. These networks are integral parts of building scalable storage solutions. By integrating a low-latency network directly into the SSD, we can reduce the costs of accessing remote storage by up to 95% compared to commonly used higher-latency remote storage and network protocol layers.

Overall, Moneta demonstrates the critical need to continue to redesign system architectures to make the best use of fast non-volatile memory technologies.

# Chapter 1

## Introduction

Emerging fast, non-volatile technologies such as phase change, spin-transfer torque, and memristor memories make it possible to build storage devices that are orders of magnitude faster than even the fastest flash-based solid-state disks (SSDs). These technologies will rewrite the rules governing how storage hardware and software interact to determine overall storage system performance. In particular, software overheads that used to contribute marginally to latency (because storage hardware was slow) will potentially squander the performance that these new memories can provide.

For many years, the performance of persistent storage (i.e., disks) has lagged far behind that of microprocessors. Since 1970, microprocessor performance grew by roughly  $200,000\times$ . During the same period, disk access latency has fallen by only  $9\times$  while bandwidth has risen by only  $163\times[104,43]$ .

The emergence of non-volatile, solid-state memories (such as NAND flash and phase-change memories, among others) has signaled the beginning of the end for painfully slow non-volatile storage. These technologies will potentially reduce latency and increase bandwidth for non-volatile storage by many orders of magnitude, but fully harnessing their performance will require overcoming the legacy of disk-based storage systems. Chapter 2 provides some background on the various storage technologies and the trends driven by these new technologies.

Emerging storage technologies beyond flash have several note-worthy benefits when compared against both disk drives and flash based SSDs. First, the performance potential of the new technologies is far greater than both disks and flash, with SSD level accesses shrinking to just a few microseconds, compared to hundreds of microseconds for flash and milliseconds for disk based storage. Second, these devices have much higher endurance than flash memory and require very limited management and wear-leveling algorithms. Finally, the new memories offer the possibility of byte-addressable, in-place updates, potentially changing the way we access and treat storage. In many ways, one can think of these new technologies as non-volatile DRAM, with similar interfaces and projected performance within 2-3 × of DRAM.

In order to fully exploit these technologies, we must overcome the decades of hardware and software design decisions that assume that storage is slow. The hardware interfaces that connect individual disks to computer systems are sluggish (~300 MB/s for SATA II and SAS, 600 MB/s for SATA 600) and connect to the slower "south bridge" portion of the CPU chip set [46]. RAID controllers connect via high-bandwidth PCIe, but the low-performance, general-purpose microprocessors they use to schedule IO requests limit their throughput and add latency [38].

Software also limits IO performance. Overheads in the operating system's IO stack are large enough that, for solid-state storage technologies, they can exceed the hardware access time. Since it takes  $\sim 20,000$  instructions to issue and complete a 4 KB IO request under standard Linux, the computational overhead of performing hundreds of thousands of IO requests per second can limit both IO and application performance.

This dissertation explores the design of both a prototype storage array, called Moneta, targeting these emerging non-volatile memory technologies, as well as the system-software design necessary to fully utilize such a device. Moneta allows us to explore the architecture of the storage array, the impact of software overheads on

performance, the effects of non-volatile technology parameters on bandwidth and latency, and the ultimate benefit to applications. We have implemented Moneta using a PCIe-attached array of FPGAs and DRAM. The FPGAs implement a scheduler and a distributed set of configurable memory controllers. The controllers allow us to emulate fast non-volatile memories by accurately modeling memory technology parameters such as device read and write times, array geometry, and internal buffering. The Moneta hardware design is discussed through the dissertation and covered in extensive detail in Appendix A.

Achieving high performance in Moneta requires simultaneously optimizing its hardware and software components. In Chapter 3, we characterize the overheads in the existing Linux IO stack in detail, and show that a redesigned IO stack combined with an optimized hardware/software interface reduces IO latency by nearly  $2\times$  and increases bandwidth by up to  $18\times$ . Tuning the Moneta hardware improves bandwidth by an additional 75% for some workloads.

Chapter 3 also explores the impact of non-volatile memory performance and organization on Moneta's performance and energy efficiency. Using a range of IO benchmarks and applications, we characterize Moneta's performance and energy efficiency, and compare them to several other storage arrays.

While Chapter 3 explores the operating system level performance of Moneta, application and file-system performance still leave much room for improvement. Chapter 4 introduces Moneta Direct (Moneta-D), a second iteration of our prototype SSD that removes operating- and file-system costs by transparently bypassing both, while preserving their management and protection functions. These costs account for as much as 30% of the total latency of a 4 KB request, and can reduce sustained throughput by 85%.

Using a virtualized device interface, untrusted user space library and refactored kernel I/O stack, Moneta-D allows any unmodified application to directly talk to the

storage array for most file data accesses. Moneta-D maintains the operating and file-system control over protection policy by moving the policy enforcement into the hardware, but requiring the trusted operating system code to setup and maintain the protection policy for the hardware.

Chapter 4 also includes an evaluation of the performance of Moneta-D and some of the key design decisions it includes. For example, we explore several ways in which Moneta-D trades off between CPU overhead and performance using different notification techniques to signal to applications that I/O requests have completed. We use a set of I/O benchmarks and database workloads and show that Moneta-D provides up to  $5.7 \times$  performance improvements for small databases and can reduce small I/O overheads by as much as 64%.

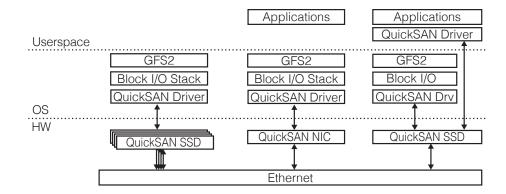

Modern storage systems rely on complex software and interconnects to provide scalable, reliable access to large amounts of data across multiple machines. In conventional, disk-based storage systems the overheads from file systems, remote block device protocols (e.g., iSCSI and Fibre Channel), and network stacks are tiny compared to the storage media access time, so software overheads do not limit scalability or performance.

Systems like Moneta and Moneta-D change this landscape completely by dramatically improving storage media performance. As a result, software shifts from being the least important component in overall storage system performance to being a critical bottleneck.

The software costs in scalable storage systems arise because, until recently, designers could freely compose existing system components to implement new and useful storage system features. For instance, the software stack running on a typical, commodity storage area network (SAN) will include a file system (e.g., GFS [94]), a logical volume manager (e.g., LVM), remote block transport layer client (e.g., the iSCSI initiator), the client side TCP/IP network stack, the server network stack, the remote

block device server (e.g., the iSCSI target), and the block device driver. The combination of these layers (in addition to the other operating system overheads) adds 288  $\mu$ s of latency to a 4 kB read. Hardware accelerated solutions (e.g., Fibre Channel) eliminate some of these costs, but still add over 90  $\mu$ s per access.

Chapter 5 extends Moneta's low latency direct, user-space access into large distributed storage area networks. It describes a new SAN architecture called *QuickSAN*. QuickSAN re-examines the hardware and software structure of distributed storage systems to minimize software overheads and let the performance of the underlying storage technology shine through.

QuickSAN improves SAN performance in two ways. First, it provides a very low-latency, hardware-accelerated block transport mechanism (based on 10 Gbit ethernet) and integrates it directly into an SSD. Second, it extends Moneta-D's OS bypass mechanism to allow an application to access remote data without (in most cases) any intervention from the operating system while still enforcing file system protections.

Finally, Chapter 6 concludes this dissertation and summarizes the findings from the preceding chapters.

## Acknowledgements

This chapter contains material from "Understanding the Impact of Emerging Non-Volatile Memories on High-Performance, IO-Intensive Computing", by Adrian M. Caulfield, Joel Coburn, Todor Mollov, Arup De, Ameen Akel, Jiahua He, Arun Jagatheesan, Rajesh K. Gupta, Allan Snavely, and Steven Swanson, which appears in *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*, (SC '10). The dissertation author was the primary investigator and author of this paper.

This chapter contains material from "Moneta: A High-Performance Storage Array

Architecture for Next-Generation, Non-Volatile Memories", by Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson, which appears in *Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture*, (MICRO '43). The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

This chapter contains material from "Providing Safe, User Space Access to Fast, Solid State Disks", by Adrian M. Caulfield, Todor I. Mollov, Louis Eisner, Arup De, Joel Coburn, and Steven Swanson, which appears in ASPLOS '12: Proceedings of the 17th International Conference on Architectural Support for Programming Languages and Operating Systems. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2012 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM,

Inc., fax +1 (212) 869-0481, or permissions@acm.org.

This chapter contains material from "QuickSAN: A Storage Area Network for Fast, Distributed, Solid State Disks", by Adrian M. Caulfield and Steven Swanson, which appears in *ISCA '13: Proceeding of the 40th Annual International Symposium on Computer Architecture*. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2013 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

# Chapter 2

# **Technologies and Trends**

This chapter provides background on current and future storage technologies, and the trends in performance that motivate the rest of the work in this dissertation. We begin with brief introductions to the relevant technologies, and then discuss the broader bandwidth, latency, and energy trends present across the devices.

### 2.1 Hard Disks

Hard disks have been the mass storage technology of choice for the last four decades. Disks provide high-density, high-reliability storage with good sequential access performance. However, disk performance has not kept pace with increases in processor performance. Since 1970 processor performance has increased nearly  $200,000 \times$  while disk bandwidth increased by  $163 \times$  and disk latency improved by only  $9 \times [43, 104]$ .

Disks store data on stacks of rotating magnetic platters. Disks store and retrieve data from each side of the platters using a sensor, or head, on the end of an arm. The head detects the polarity of the magnetic field on the platter and translates it into bits of data. Similarly, during a write, the head alters the polarity of the field to store data. The arm moves linearly across the platters and, in combination with the rotation of the platters, allows data storage at all points on the surface. The delay during the linear movement of the arm is known as the seek latency of a disk drive, while the disk rotation is known as

the rotational delay.

The notable characteristics of disks for this dissertation are their large access latencies (typically 5 to 7 ms) resulting from rotational delay and linear arm movement (seek time) as the head pans to the correct track. Disk bandwidth is also an important characteristic: bandwidth for a single disk ranges between 500 KB/s on random accesses to 138 MB/s during large sequential accesses [106].

Disk characteristics are now well understood and optimizations throughout the IO stack make performance slightly better, but most applications treat storage as something to access as infrequently as possible. For those applications that must access large amounts of data, such as databases, disk performance severely limits application performance. More recent memory technologies eliminate the fundamentally slow aspects of disk storage since they have no moving parts enabling uniform access latencies regardless of the ordering of requests.

## 2.2 NAND Flash Memory

Flash memory, specifically NAND flash memory, is a non-volatile solid state storage technology. Flash has been around for many years, but only within the last 5 to 7 years has its density increased sufficiently to make it a viable primary storage medium. NAND flash forms the basis of most commercial solid-state storage devices including solid-state disks, USB "thumb" drives, and storage media for cameras and portable devices.

Flash stores bits by trapping electrons on a "floating" gate in a transistor. The trapped charge alters the voltage required to "turn on" the transistor. To trap electrons on the gate, a large voltage is applied, causing electrons to tunnel through the insulator onto the gate. Current flash can use two, four, or eight charge levels on the floating gate. In the first case, each cell stores one bit of data, this is known as a Single Level Cell (SLC).

The later two are Multi-Level Cell (MLC) and Triple-Level Cell (TLC) and store two and three bits per cell, respectively.

NAND flash typically groups from 2 KB to 8 KB into a page and then 64 to 256 pages into a block. Reads and programs operate at page granularity, while erases occur at the block level. To maintain data integrity flash requires that each page receives at most one programming operation between erases.

Programming and erasing flash puts significant stress on the cells, which can eventually cause programming or erasing to fail. Modern NAND flash chips have a maximum erase count of between 3,000 (TLC) and 100,000 (SLC) cycles per block. This is the number of erase-program cycles that the chip can sustain before an unacceptable level of wear occurs and too many bit errors occur.

Flash Translation Layers (FTL) provide a wear management scheme to balance the number of erases each block performs. The FTL adds a layer of indirection between the sectors requested by the operating system and the physical address of the data stored in memory. This enables blocks of data to be moved around on the flash device to distribute wear. Without the FTL, blocks could potentially wear out at uneven rates, necessitating capacity decreases or device failure.

Several types of mass storage devices using flash memory are currently available. One is a direct hard disk replacement, connecting to a Serial ATA (SATA) or Serially Attached SCSI (SAS) bus. The other connects flash memory to a PCI express (PCIe) bus, enabling higher bandwidth and lower latency accesses [29, 47].

We have measured PCIe attached flash SSDs sustaining latencies of 68  $\mu$ s and bandwidth of 250 MB/s on a random 4 KB read workload.

In summary, the main differences between flash memory and disks are three fold. First, the solid state nature of flash eliminates the address dependent seek latencies found in disks due to the mechanical motion of the disk arm. Second, flash requires the use

of a FTL to manage the lifetime of each of the blocks of data in a flash device. Finally, access latencies in flash are operation dependent, affecting the way requests should be scheduled for flash memory.

## 2.3 Phase Change RAM

Phase Change Random Access Memory (PCRAM) stores bits not with electrical charge, but by manipulating the resistive properties of a material. To program a bit, PCRAM memory heats a small amount of chalcogenide (the material used in recordable CD-ROMs) and then cools it either slowly or quickly, depending on the value being programmed [9]. The different cooling rates create different structural patterns in the material, each with differing electrical resistance. To read a bit back, PCRAM passes current through the material, and depending on how quickly the chalcogenide cooled, encounters either high resistance or low resistance. PCRAM is bit alterable, meaning that each of the bits can be toggled independently, removing the need for the extra erase operation needed for flash memory.

PCRAM is projected to eventually match DRAM's latency and bandwidth, continuing recent trends of fast density and performance increases, and may become a viable technology to replace DRAM as a main memory technology [53]. The ITRS roadmap projects a PCRAM write time of less than 50 ns by 2024 [2]. For this work we assume PCRAM latencies of 69.5 ns and 215 ns as projected by [6].

PCRAM's bit alterability makes it better suited for replacing main memory in systems. However, since writes to storage often occur in larger blocks, having byte addressable memory is not necessarily a benefit when used as storage, especially if it incurs additional costs.

PCRAM removes many of the restrictions that flash imposes and eases others. Unlike Flash, PCRAM is byte addressable and requires no erase operation. Al-

though PCRAM's durability is  $10-100 \times$  that of flash, it still requires some wear levelling. PCRAM's lack of an erase operation and hence the avoidance of the read/write vs erase granularity disparity found in flash, makes wear levelling in PCRAM much simpler. Schemes such as start-gap [77] transparently handle wear levelling with minimal overhead. Similar to flash, PCRAM's write operations are longer than its reads, however the differences are much smaller (less than  $4\times$ ). In most respects PCRAM is best thought of as a slightly slower DRAM.

## 2.4 Spin-Torque MRAM and the Memristor

Other technologies such as Spin-Torque MRAMs and the Memristor are also on the horizon, albeit a few years farther out than PCRAM. These technologies promise most of the same benefits as PCRAM with lower energy costs, higher endurance and improved latencies and bandwidth.

ST-MRAM uses layers of magnetic material that can be easily integrated with traditional chip production processes. Stacking a fixed layer of magnetic material with a free magnetic layer creates a magnetic tunnel junction (MJT). By changing the orientation of the free layer the resistance of the MTJ can be altered depending on whether the magnetic moment of the layers are in a parallel (low resistance) or anti-parallel (high resistance) configuration. The first, low density sample parts will be available within a year, offering latencies of 35 ns for both reads and writes [27].

The Memristor is another promising future non-volatile storage technology. Memristors are a passive circuit element that alters its resistance based on the direction of current flow through the device. When current ceases, the resistance is remembered. By building arrays of these circuit elements we can construct storage devices just like ST-MRAMs and PCRAM [40]. These devices are much less mature than either PCRAM or ST-MRAM so their characteristics are less clear, but they should be useful in many of

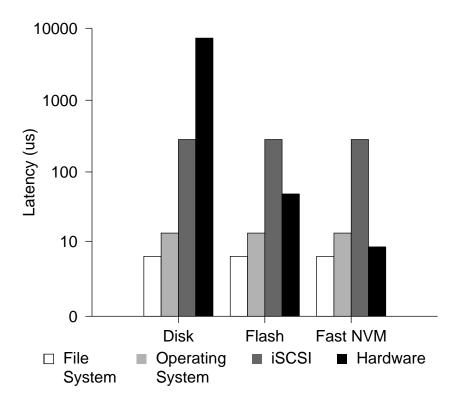

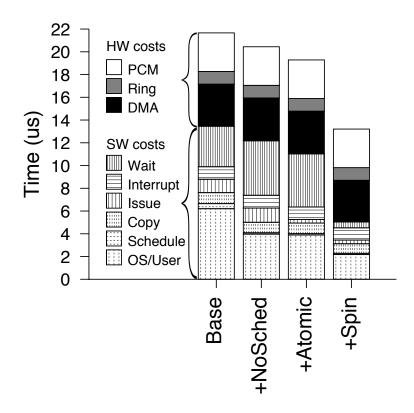

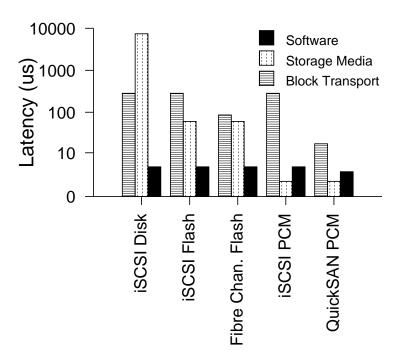

**Figure 2.1.** As the hardware access latency for storage technologies shrinks, software overheads will become the dominant latency cost in accessing storage.

the same applications.

## 2.5 Trends in Storage Technology

The new memory technologies introduced in the preceding sections show multiple paths forward towards non-volatile memory technologies that come within a small factor of DRAM performance. These technologies will drive storage latency from the 7 ms average hard disk access time to 8-10  $\mu$ s with a device like the one described in this dissertation based on PCRAM or ST-MRAM.

Figure 2.1 illustrates the effect of decreasing hardware latencies. It shows several of the main components of I/O device latency: the file system, operating system, iSCSI latency (for remote storage accesses), and the hardware latency. Hardware latencies

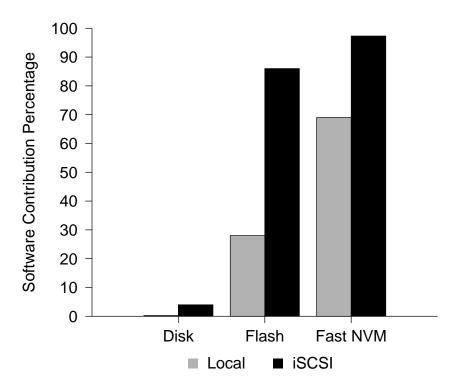

**Figure 2.2.** The graph shows the percentage of the total request latency contributed by software, for both local accesses and remote accesses through a software iSCSI stack. As memory latency decreases, software's contribution becomes larger, accounting for as much as 97% of the total latency.

for flash based storage are about two orders of magnitude smaller than for disks, but software overheads remain the same. This means as storage gets faster, the percentage of an I/O request accounted for by software components is increasing rapidly - from about 4% for disks to 84% for flash. A further reduction in latency from technologies such as PCRAM and ST-MRAM will drive software latencies to account for as much as 97% of the total request latency. Figure 2.2 depicts this trend, showing the software overheads as a percentage of the total request latency.

## **Acknowledgements**

This chapter contains material from "Understanding the Impact of Emerging Non-Volatile Memories on High-Performance, IO-Intensive Computing", by Adrian M. Caulfield, Joel Coburn, Todor Mollov, Arup De, Ameen Akel, Jiahua He, Arun Jagatheesan, Rajesh K. Gupta, Allan Snavely, and Steven Swanson, which appears in *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*, (SC '10). The dissertation author was the primary investigator and author of this paper.

This chapter contains material from "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", by Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson, which appears in *Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture*, (MICRO '43). The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

This chapter contains material from "Providing Safe, User Space Access to Fast, Solid State Disks", by Adrian M. Caulfield, Todor I. Mollov, Louis Eisner, Arup De, Joel Coburn, and Steven Swanson, which appears in *ASPLOS '12: Proceedings of the*

17th International Conference on Architectural Support for Programming Languages and Operating Systems. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2012 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

This chapter contains material from "QuickSAN: A Storage Area Network for Fast, Distributed, Solid State Disks", by Adrian M. Caulfield and Steven Swanson, which appears in *ISCA '13: Proceeding of the 40th Annual International Symposium on Computer Architecture*. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2013 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

# Chapter 3

## The Moneta Kernel Stack

The Moneta prototype SSD introduced in the introduction offers the potential to dramatically alter the storage performance seen by the operating system. By replacing spinning disks and flash based storage, with latencies of 7 ms and 100s of microseconds respectively, with emerging fast non-volatile memories that are orders of magnitude faster, Moneta offers much potential, but decades of legacy storage system designs pose a risk of squandering any significant gains.

Over the last four decades, storage system designs were driven by the fundamental assumption that storage is slow. This led to the addition of many layers of latency intensive software optimizations, to reorder, schedule, and prioritize the sequence of IO requests sent the hardware. Even though these optimizations potentially slow individual accesses by 100s of microseconds, they still account for less than a few percent of the total IO request latency, and often reduce the total latency of a sequence of requests.

This chapter covers the kernel level design and implementation of the Moneta system. We first characterize the overheads in the existing Linux IO stack in detail, and show that a redesigned IO stack combined with an optimized hardware/software interface reduces IO latency by nearly  $2\times$  and increases bandwidth by up to  $18\times$ . Tuning the Moneta hardware improves bandwidth by an additional 75% for some workloads.

We present two findings on the impact of non-volatile memory performance and

organization on Moneta's performance and energy efficiency. First, some optimizations that improve PCM's performance and energy efficiency as a main memory technology do not apply in storage applications because of different usage patterns and requirements. Second, for 4 KB accesses, Moneta provides enough internal parallelism to completely hide memory access times of up to 1  $\mu$ s, suggesting that memory designers could safely trade off performance for density in memory devices targeted at storage applications.

Results for a range of IO benchmarks demonstrate that Moneta outperforms existing storage technologies by a wide margin. Moneta can sustain up to 2.2 GB/s on random 4 KB accesses, compared to 250 MB/s for a state-of-the-art flash-based SSD. It can also sustain over 1.1 M 512-byte random IO operations per second. While Moneta is nearly 10× faster than the flash drive, software overhead beyond the IO stack (e.g., in the file system and in application) limit application-level speedups: Compared to the same flash drive, Moneta speeds up applications by a harmonic mean of just 2.1×, demonstrating that further work is necessary to fully realize Moneta's potential at the application level.

The remainder of the chapter is organized as follows. Section 3.1 briefly describes the Moneta prototype. Sections 3.2, 3.3, and 3.4 analyze the baseline Moneta system performance and describe software and hardware optimizations. Section 3.5 compares Moneta to existing storage technologies, and Section 3.6 describes related work. Finally, Section 3.7 summarizes this chapter.

## 3.1 The Moneta prototype

This section describes the baseline Moneta architecture and the hardware system we use to emulate it. Appendix A contains more implementation details of the Moneta prototype.

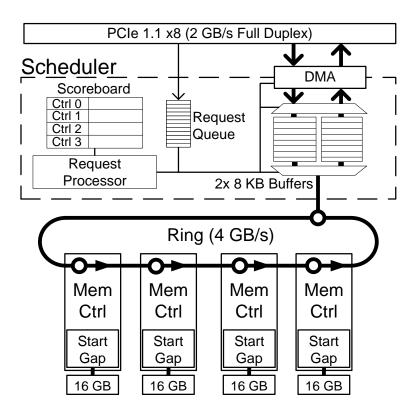

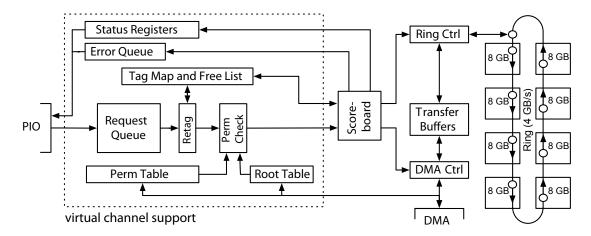

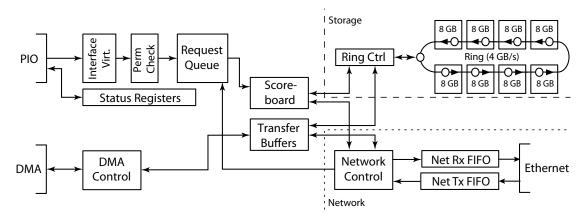

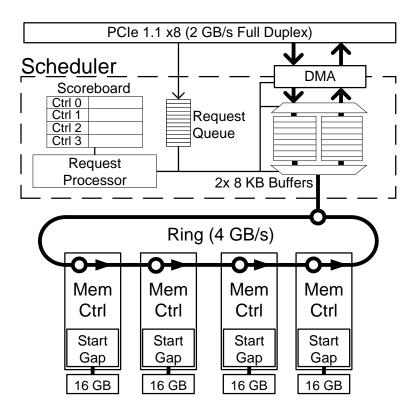

**Figure 3.1.** Moneta's PCM memory controllers connect to the scheduler via a 4 GB/s ring. A 2 GB/s full duplex PCIe link connects the scheduler and DMA engine to the host. The scheduler manages 8 KB buffers as it processes IO requests in FIFO order. A scoreboard tracks the state of the memory controllers.

## 3.1.1 Moneta array architecture

Figure 3.1 shows the architecture of the Moneta storage array. Moneta's architecture provides low-latency access to a large amount of non-volatile memory spread across four memory controllers. A scheduler manages the entire array by coordinating data transfers over the PCIe interface and the ring-based network that connects the independent memory controllers to a set of input/output queues. Moneta attaches to the computer system via an eight-lane PCIe 1.1 interface that provides a 2 GB/s full-duplex connection (4 GB/s total).

The Moneta scheduler The scheduler orchestrates Moneta's operation. It contains a DMA controller and a Programmed IO (PIO) interface to communicate with the host machine, a set of internal buffers for incoming and outgoing data, several state machines, and an interface to the 128-bit token-ring network. The Moneta scheduler stripes internal storage addresses across the memory controllers to extract parallelism from large requests. The baseline stripe size is 8 KB.

Requests arrive on the PCIe interface as PIO writes from the software driver. Each request comprises three 64-bit words that contain a sector address, a DMA memory address (in host memory), a 32-bit transfer length, and a collection of control bits that includes a tag number and an op code (read or write). Sectors are 512 bytes. The tag is unique across outstanding requests and allows for multiple in-flight requests, similar to SATA's Native Command Queuing [42].

The scheduler places requests into a FIFO queue as they arrive and processes them in order. Depending on the request's size and alignment, the scheduler breaks it into one or more transfers of up to 8 KB. It then allocates a buffer for each transfer from two 8 KB buffers in the scheduler. If buffer space is not available, the scheduler stalls until another transfer completes.

For write transfers, the scheduler issues a DMA command to transfer data from the host's memory into its buffer. When the DMA transfer completes, the scheduler checks an internal scoreboard to determine whether the target memory controller has space to receive the data, and waits until sufficient space is available. Once the transfer completes, the scheduler's buffer is available for another transfer. The steps for a read transfer are similar except that the steps are reversed.

Once the scheduler completes all transfers for a request, it raises an interrupt and sets a tag status bit. The operating system receives the interrupt and completes the request by reading and then clearing the status bit using PIO operations.

The DMA controller manages Moneta's 2 GB/s full-duplex (4 GB/s total) channel to the host system. The DMA interleaves portions of bulk data transfers from Moneta to the host's memory (read requests) with DMA requests that retrieve data from host's memory controller (write requests). This results in good utilization of the bandwidth between the host and Moneta because bulk data transfers can occur in both directions simultaneously.

**Memory controllers** Each of Moneta's four memory controllers manages an independent bank of non-volatile storage. The controllers connect to the scheduler via the ring and provide a pair of 8 KB queues to buffer incoming and outgoing data. The memory array at each controller comprises four DIMM-like memory modules that present a 72 bit (64 + 8 for ECC) interface.

Like DRAM DIMMs, the memory modules perform accesses in parallel across multiple chips. Each DIMM contains four internal banks and two ranks, each with an internal row buffer. The banks and their row buffers are 8 KB wide, and the DIMM reads an entire row from the memory array into the row buffer. Once that data is in the row buffer, the memory controller can access it at 250 MHz DDR (500M transfers per second), so the peak bandwidth for a single controller is 4 GB/s.

The memory controller implements the start-gap wear-leveling and address randomization scheme [76] to evenly distribute wear across the memory it manages.

## **3.1.2** Implementing the Moneta prototype

We have implemented a Moneta prototype using the BEE3 FPGA prototyping system designed by Microsoft Research for use in the RAMP project [79]. The BEE3 system holds 64 GB of 667 MHz DDR2 DRAM under the control of four Xilinx Virtex 5 FPGAs, and it provides a PCIe link to the host system. The Moneta design runs at

250 MHz, and we use that clock speed for all of our results.

Moneta's architecture maps cleanly onto the BEE3. Each of the four FPGAs implement a memory controller, while one also implements the Moneta scheduler and the PCIe interface. The Moneta ring network runs over the FPGA-to-FGPA links that the BEE3 provides.

The design is very configurable. It can vary the effective number of memory controllers without reducing the amount of memory available, and it supports configurable buffer sizes in the scheduler and memory controllers.

Moneta memory controllers emulate PCM devices on top of DRAM using a modified version of the Xilinx Memory Interface Generator DDR2 controller. It adds latency between the read address strobe and column address strobe commands during reads and extends the precharge latency after a write. The controller can vary the apparent latencies for accesses to memory from 4 ns to over 500  $\mu$ s. We use the values from [53] (48 ns and 150 ns for array reads and writes, respectively) to model PCM in this work, unless otherwise stated.

The width of memory arrays and the corresponding row buffers are important factors in the performance and energy efficiency of PCM memory [53]. The memory controller can vary the effective width of the arrays by defining a virtual row size and inserting latencies to model opening and closing rows of that size. The baseline configuration uses 8 KB rows.

# 3.2 Baseline Moneta performance

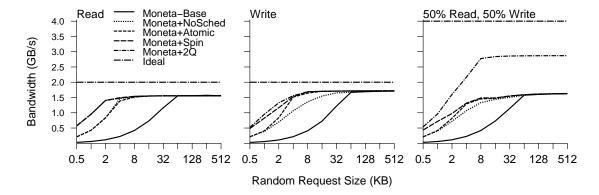

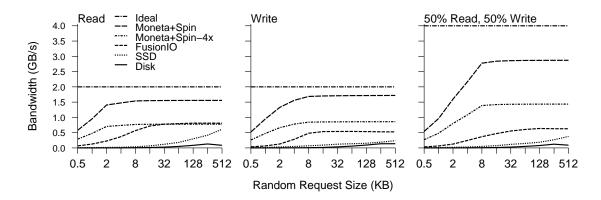

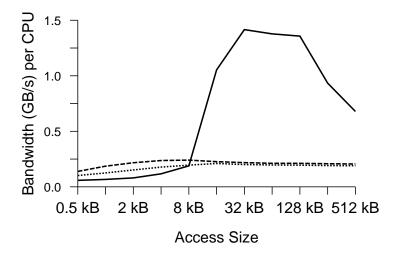

We use three metrics to characterize Moneta's performance. The first, shown in Figure 3.2, is a curve of sustained bandwidth for accesses to randomly selected locations over a range of access sizes. The second measures the average latency for a 4 KB access to a random location on the device. The final metric is the number of random access

**Figure 3.2.** The PCIe link bandwidth (labeled "ideal") limits performance for large accesses, but for small accesses software overheads are the bottleneck for the baseline Moneta design (the solid black line). The other lines measure results for optimized version described in Section 3.3 and 3.4.

4 KB IO operations per second (IOPS) the device can perform with multiple threads.

Our test system is a two-socket, Core i7 Quad (a total of 8 cores) machine running at 2.26 GHz with 8 GB of physical DRAM and two 8 MB L2 caches. All measurements in this section are for a bare block device without a file system. We access Moneta via a low-level block driver and the standard Linux IO stack configured to use the No-op scheduler, since it provided the best performance. Each benchmark reports results for reads, writes, and a 50/50 combination of the two. We use XDD [109], a configurable IO performance benchmark for these measurements.

Figure 3.2 shows bandwidth curves for the baseline Moneta array and the optimized versions we discuss in future sections. The "ideal" curve shows the bandwidth of the 2 GB/s PCIe connection.

The baseline Moneta design delivers good performance, but there is room for improvement for accesses smaller than 64KB. For these, long access latency limits bandwidth, and much of this latency is due to software. Figure 3.3 and Table 3.1 breaks down the latency for 4 KB read and write accesses into 14 components. The data show that software accounts for 13  $\mu$ s of the total 21  $\mu$ s latency, or 62%. For comparison,

the software overheads for issuing a request to the SSD- and disk-based RAID arrays described in Section 3.5 are just 17% and 1%, respectively. Although these data do not include a file system, other measurements show file system overhead adds an additional 4 to 5  $\mu$ s of delay to each request.

These software overheads limit the number of IOPS that a single processor can issue to 47K, so it would take 10.5 processors to achieve Moneta's theoretical peak of 500K 4 KB read IOPS. As a result, IO-intensive applications running on Moneta with fewer than 11 processors will become CPU bound before they saturate the PCIe connection to Moneta.

These overheads demonstrate that software costs are the main limiter on Moneta performance. The next section focuses on minimizing these overheads.

# 3.3 Software Optimizations

#### 3.3.1 IO scheduler

Linux IO schedulers sort and merge requests to reduce latencies and provide fair access to IO resources under load. Reordering requests can provide significant reductions in latency for devices with non-uniform access latencies such as disks, but for Moneta it just adds software overheads. Even the no-op scheduler, which simply passes requests directly to the driver without any scheduling, adds 2  $\mu$ s to each request. This cost arises from context switches between the thread that requested the operation and the scheduler thread that actually performs the operation.

Moneta+NoSched bypasses the scheduler completely. It uses the thread that entered the kernel from user space to issue the request without a context switch. Removing the scheduler provides several ancillary benefits, as well. The no-op scheduler is single-threaded so it removes any parallelism in request handling. Under Moneta+NoSched

**Table 3.1.** The table breaks down baseline Moneta latency by component. Total latency is smaller than the sum of the components, due to overlap among components.

| Label       | Description                             | Baseline l | atency (µs) |

|-------------|-----------------------------------------|------------|-------------|

| Label       | Description                             | Write      | Read        |

| OS/User     | OS and userspace overhead               | 1.98       | 1.95        |

| OS/User     | Linux block queue and no-op scheduler   | 2.51       | 3.74        |

| Schedule    | Get request from queue and assign tag   | 0.44       | 0.51        |

| Copy        | Data copy into DMA buffer               | 0.24/KB    | -           |

| Issue       | PIO command writes to Moneta            | 1.18       | 1.15        |

| DMA         | DMA from host to Moneta buffer          | 0.93/KB    | -           |

| Ring        | Data from Moneta buffer to mem ctrl     | 0.28/KB    | -           |

| PCM         | 4 KB PCM memory access                  | 4.39       | 5.18        |

| Ring        | Data from mem ctrl to Moneta buffer     | -          | 0.43/KB     |

| DMA         | DMA from Moneta buffer to host          | -          | 0.65/KB     |

| Wait        | Thread sleep during hw                  | 11.8       | 12.3        |

| Interrupt   | Driver interrupt handler                | 1.10       | 1.08        |

| Copy        | Data copy from DMA buffer               | -          | 0.27/KB     |

| OS/User     | OS return and userspace overhead        | 1.98       | 1.95        |

| Hardware    | total for 4 KB (accounting for overlap) | 8.2        | 8.0         |

| Software t  | otal for 4 KB (accounting for overlap)  | 13.3       | 12.2        |

| File system | n additional overhead                   | 5.8        | 4.2         |

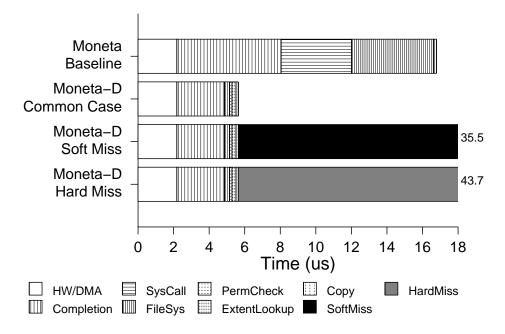

**Figure 3.3.** The figure shows that software optimizations reduce overall access latency by 9  $\mu$ s between Moneta-Base and Moneta+Spin.

each request has a dedicated thread and those threads can issue and complete requests in parallel. Moneta+NoSched reduces per-request latency by 2  $\mu$ s and increases peak bandwidth by 4× for 4 KB requests.

#### 3.3.2 Issuing and completing IO requests

Moneta+NoSched allows some parallelism, but threads still contend for access to two locks that protect Moneta's hardware interface and shared data structures, limiting effective parallelism in the driver. The first lock protects the hardware interface during multi-word reads and writes to Moneta's PIO interface. The second lock protects shared data structures in the software.

To safely remove the lock that protects Moneta's hardware/software interface, we modify the interface so that issuing and completing a request requires a single, atomic PIO write or read. The baseline interface requires several PIO writes to issue a request. Moneta+Atomic reduces this to one by removing bits from the internal address and length fields to align them to 512-byte boundaries and completely removing the DMA address field. These changes allow a request to fit into 64 bits – 8 for the tag, 8 for the command, 16 for the length, and 32 for the internal address.

To specify the target address for DMA transfers, the Moneta+Atomic driver pre-allocates a DMA buffer for each tag and writes the host DRAM address of each buffer into a register in the hardware. The tag uniquely identifies which DMA buffer to use for each request.

A second change to Moneta's hardware/software interface allows multiple threads to process interrupts in parallel. When a request completes and Moneta raises an interrupt, the driver checks the status of all outstanding operations by reading the tag status register. In Moneta+NoSched the tag status register indicates whether each tag is busy or idle and the driver must read the register and then update it inside a critical section protected by

a lock. In Moneta+Atomic the tag status bits indicate whether a request using that tag finished since the last read of the register, and reading the register clears it. Atomically reading and clearing the status register allows threads to service interrupts in parallel without the possibility of two threads trying to complete the same request.

The second lock protects shared data structures (e.g., the pool of available tags). To remove that lock, we reimplemented the tag pool data as a lock-free data structure, and allocate other structures on a per-tag basis.

By removing all the locks from the software stack, Moneta+Atomic reduces latency by 1  $\mu$ s over Moneta+NoSched and increases bandwidth by 460 MB/s for 4 KB writes. The disproportionate gain in bandwidth versus latency results from increased concurrency.

### 3.3.3 Avoiding interrupts

Responding to the interrupt that signals the completion of an IO request requires a context switch to wake up the thread that issued the request. This process adds latency and limits performance, especially for small requests. Allowing the thread to spin in a busy-loop rather than sleeping removes the context switch and the associated latency. Moneta+Spin implements this optimization.

Spinning reduces latency by 6  $\mu$ s, but it increases per-request CPU utilization. It also means that the number of thread-contexts available bounds the number of outstanding requests. Our data show that spinning only helps for write requests smaller than 4 KB, so the driver spins for those requests and sleeps for larger requests. Moneta+Spin improves bandwidth for 512-4096 byte requests by up to 250 MB/s.

#### 3.3.4 Other overheads

The remaining overheads are from the system call/return and the copies to and from userspace. These provide protection for the kernel. Optimizing the system call interface is outside the scope of this chapter, but removing copies to and from userspace by directing DMA transfers into userspace buffers is a well-known optimization in high-performance drivers. For Moneta, however, this optimization is not profitable, because it requires sending a physical address to the hardware as the target for the DMA transfer. This would make issuing requests atomically impossible. Our measurements show that this hurts performance more than removing the copy to or from userspace helps. One solution would be to extend the processor's ISA to support 128 bit atomic writes. This would allow an atomic write to include the full DMA target address.

# 3.4 Tuning the Moneta hardware

With Moneta's optimized hardware interface and IO stack in place, we shift our focus to four aspects of the Moneta hardware – increasing simultaneous read/write bandwidth, increasing fairness between large and small transfers, adapting to memory technologies with longer latencies than PCM, and power consumption.

#### 3.4.1 Read/Write bandwidth

Figure 3.2 shows that Moneta+Spin nearly saturates the PCIe link for read- and write-only workloads. For the mixed workload, performance is similar, but performance should be better since the PCIe link is full duplex.

Moneta+Spin uses a single hardware queue for read and write requests which prevents it from fully utilizing the PCIe link. Moneta+2Q solves this problem by providing separate queues for reads and writes and processing the queues in round-robin order. When reads and writes are both present, half of the requests to the DMA engine will be

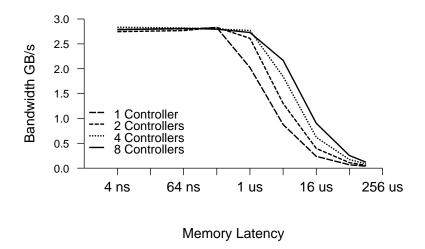

**Figure 3.4.** Additional controllers allow Moneta to hide longer memory latencies without sacrificing bandwidth. The curves measure bandwidth for 4 KB read and write accesses.

reads and half will be writes. The DMA engine interleaves the requests to transfer data in both directions simultaneously.

Figure 3.2 includes performance for Moneta+2Q. It increases mixed read/write performance by 75% and consumes 71% of the total PCIe bandwidth.

The new scheduler adds some complexity to the design and requires a change to how we implement IO barriers. IO barriers prevent the storage system from moving requests across the barrier, and some applications (e.g. file systems) use barriers to enforce ordering. The baseline Moneta design enforces this constraint by processing requests in order. Moneta+2Q's scheduler keeps track of outstanding barriers and synchronizes the read and write queue as needed to implement them. Requests that enter either queue after a barrier will wait for the barrier to complete before issuing.

## 3.4.2 Balancing bandwidth

Real-world application access patterns are more complex and varied than the workloads we have tested so far. Multiple applications will run concurrently placing different demands on Moneta simultaneously. Ideally, Moneta would prevent one access

or access pattern from unduly degrading performance for other accesses.

The scheduler in Moneta+2Q processes the requests in each queue in order, so large requests can significantly delay other requests in the same queue. For a mixture of large and small requests, both sizes perform the same number of *accesses* per second, but bandwidth will be much smaller for the smaller accesses. For instance, if four threads issuing 4 KB reads run in parallel with four threads issuing 512 KB reads, the 4 KB threads realize just 16 MB/s, even though a 4 KB thread running in isolation can achieve 170 MB/s. The 512 KB threads receive a total 1.5 GB/s.

To reduce this imbalance, we modified the scheduler to service requests in the queue in round-robin order. The scheduler allocates a single buffer to the request at the front of the queue and then places the remainder of the request back on the queue before moving on to the next request. Round-robin queuing improves performance for the 4 KB threads in our example by  $12\times$ , and reduces large request bandwidth by 190 MB/s. Aggregate bandwidth remains the same.

The modified scheduler implements barriers by requiring that all in-progress requests complete before inserting any operations that follow the barrier into the scheduling queues.

## 3.4.3 Non-volatile memory latency

It is difficult to predict the latencies that non-volatile memories will eventually achieve, and it is possible that latencies will be longer than those we have modeled.

Figure 3.4 explores the impact of memory latency on Moneta's performance. It plots Moneta+Balance performance with memory latencies between 4 ns to 128  $\mu$ s and with 1 to 8 memory controllers. The data show that adding parallelism in the form of memory controllers can completely hide latencies of up to 1  $\mu$ s and that 4  $\mu$ s memories would only degrade performance by 20% with eight controllers. The data also show

that at 4  $\mu$ s, doubling the number of controllers increases bandwidth by approximately 400 MB/s.

These results suggest that, for bandwidth-centric applications, it makes sense to optimize non-volatile memories for parallelism and interface bandwidth rather than latency. Furthermore, Moneta's memory controller only accesses a single bank of memory at a time. A more advanced controller could leverage inter-bank parallelism to further hide latency. Flash-based SSDs provide a useful case study: FusionIO's ioDrive, a state-of-the-art SSD, has many independent memory controllers to hide the long latencies of flash memory. In Section 3.5 we show that while a FusionIO drive can match Moneta's performance for large transfers, its latency is much higher.

#### 3.4.4 Moneta power consumption

Non-volatile storage reduces power consumption dramatically compared to hard drives. To understand Moneta's power requirements we use the power model in Table 3.2. For the PCM array, we augment the power model in [53] to account for a power-down state for the memory devices. Active background power goes to clocking the PCM's internal row buffers and other peripheral circuitry when the chip is ready to receive commands. Each PCM chip dissipates idle background power when the clock is off, but the chip is still "on." The value here is for a commercially available PCM device [26]. We model the time to "wake up" from this state based on values in [26]. The model does not include power regulators or other on-board overheads.

The baseline Moneta array with four memory controllers, but excluding the memory itself, consumes a maximum of 3.19 W. For 8 KB transfers, the memory controller bandwidth limits memory power consumption to 0.6 W for writes, since transfer time over the DDR pins limits the frequency of array writes. Transfer time and power for reads is the same, but array power is lower. The PCIe link limits total

array active memory power to 0.4 W (2 GB/s writes at 16.82 pJ/bit and 2 GB/s reads at 2.47 pJ/bit, plus row buffer power). Idle power for the array is also small – 0.13 W or 2 mW/GB. Total power for random 8 KB writes is 3.47 W, according to our model.

For small writes (e.g., 512 bytes), power consumption for the memory at a single controller could potentially reach 8.34 W since the transfer time is smaller and the controller can issue writes more frequently. For these accesses, peak controller bandwidth is 1.4 GB/s. Total Moneta power in this case could be as high as 11 W. As a result, efficiency for 512-byte writes in terms of MB/s/W drops by 85% compared to 8 KB writes.